19-3597; Rev 6; 3/09

EVALUATION KIT AVAILABLE

# 60mW, DirectDrive, Stereo Headphone Amplifier with Low RF Susceptibility and Shutdown

#### **General Description**

Applications

**DVD** Players

**PDAs**

Smart Phones

The MAX9724A/MAX9724B stereo headphone ampli-

fiers are designed for portable equipment where board

space is at a premium. These devices use a unique

DirectDrive<sup>®</sup> architecture to produce a ground-refer-

enced output from a single supply, eliminating the need

for large DC-blocking capacitors, saving cost, board

space, and component height. The MAX9724 sup-

presses RF radiation received by input and supply traces acting as antennas and prevents the amplifier

from demodulating the coupled noise. The MAX9724A

offers an externally adjustable gain while the

MAX9724B has an internally preset gain of -1.5V/V. The

MAX9724A/MAX9724B deliver up to 60mW per channel into a 32Ω load and have low 0.02% THD+N. An 80dB

at 1kHz power-supply rejection ratio (PSRR) allows

these devices to operate from noisy digital supplies without an additional linear regulator. Comprehensive

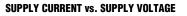

click-and-pop circuitry suppresses audible clicks and

The MAX9724A/MAX9724B operate from a single 2.7V to 5.5V supply, consume only 3.5mA of supply current, feature short-circuit and thermal-overload protection, and are specified over the extended -40°C to +85°C temperature range. The devices are available in tiny 12bump UCSP™ (1.5mm x 2mm) and 12-pin thin QFN

pops on startup and shutdown.

(3mm x 3mm x 0.8mm) packages.

Handheld Gaming Consoles

DirectDrive is a registered trademark of Maxim Integrated

**Cellular Phones**

MP3 Players

Products, Inc.

Notebook PCs

Features

- Improved RF Noise Rejection (Up to 67dB Over **Typical Amplifiers)**

- No Bulky DC-Blocking Capacitors Required

- ♦ Low-Power Shutdown Mode, < 0.1µA</p>

- Adjustable Gain (MAX9724A) or Fixed -1.5V/V Gain (MAX9724B)

- ♦ Low 0.02% THD+N

- High PSRR (80dB at 1kHz) Eliminates LDO

- Integrated Click-and-Pop Suppression

- ♦ 2.7V to 5.5V Single-Supply Operation

- Low Quiescent Current (3.5mA)

- Available in Space-Saving Packages 12-Bump UCSP (1.5mm x 2mm) 12-Pin Thin QFN (3mm x 3mm x 0.8mm)

#### **Ordering Information**

| PART             | GAIN<br>(V/V) | PIN-<br>PACKAGE | TOP<br>MARK |

|------------------|---------------|-----------------|-------------|

| MAX9724AEBC+TG45 | Adj.          | 12 UCSP         | +ADH        |

| MAX9724AETC+     | Adj.          | 12 TQFN-EP*     | +AAT        |

| MAX9724BEBC+TG45 | -1.5          | 12 UCSP         | +ADI        |

| MAX9724BETC+     | -1.5          | 12 TQFN-EP*     | +AAU        |

Note: All devices specified over the -40°C to +85°C operating range

+Denotes lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

\*EP = Exposed paddle.

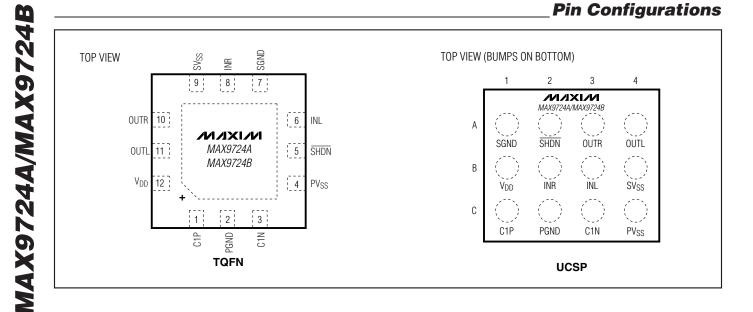

Pin Configurations appear at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

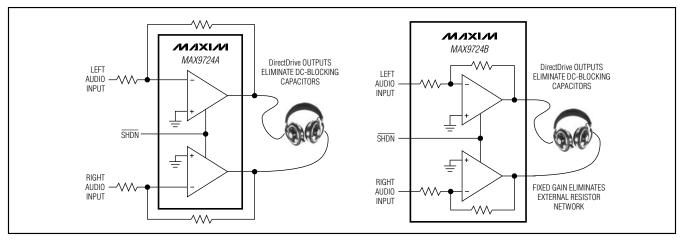

### **Block Diagrams**

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

|   |                                       | 0.3V to +6V<br>0.3V to +0.3V                              | Continuous Input Current in<br>Continuous Input Current (a |

|---|---------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|

|   |                                       | -0.3V to +0.3V                                            | Continuous Power Dissipati                                 |

|   | C1P to PGND                           | 0.3V to (V <sub>DD</sub> + 0.3V)                          | 12-Bump UCSP (derate 6.                                    |

|   | C1N to PGND                           | (PV <sub>SS</sub> - 0.3V) to +0.3V                        | θJA                                                        |

|   | PVss and SVss to PGND                 | 6V to +0.3V                                               | 12-Pin TQFN (derate 16.7r                                  |

|   | IN_ to SGND (MAX9724A)                | 0.3V to (V <sub>DD</sub> + 0.3V)                          | θJA                                                        |

|   | IN_ to SGND (MAX9724B)                | (SV <sub>SS</sub> - 0.3V) to (V <sub>DD</sub> + 0.3V)     | θJC                                                        |

|   | OUT_ to SV <sub>SS</sub> (Note 1)0.3V | to Min ( $V_{DD}$ - $SV_{SS}$ + 0.3V, +9V)                | Operating Temperature Rar                                  |

|   | OUT_ to V <sub>DD</sub> (Note 2)+0.3V | / to Max (SV <sub>SS</sub> - V <sub>DD</sub> - 0.3V, -9V) | Storage Temperature Rang                                   |

|   | SHDN to _GND                          | 0.3V to +6V                                               | Junction Temperature                                       |

| • |                                       | Continuous                                                | Lead Temperature (solderin                                 |

|   | Short Circuit between OUTL and        | d OUTRContinuous                                          | Bump Temperature (solderi                                  |

|   |                                       |                                                           |                                                            |

Note 1: OUTR and OUTL should be limited to no more than 9V above SV<sub>SS</sub>, or above V<sub>DD</sub> + 0.3V, whichever limits first.

Note 2: OUTR and OUTL should be limited to no more than 9V below VDD, or below SVSS - 0.3V, whichever limits first.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 5V, PGND = SGND, \overline{SHDN} = 5V, C1 = C2 = 1\mu F, R_L = \infty$ , resistive load reference to ground; for MAX9724A gain = -1.5V/V (R<sub>IN</sub> = 20k $\Omega$ , R<sub>F</sub> = 30k $\Omega$ ); for MAX9724B gain = -1.5V/V (internally set), T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 3)

| PARAMETER                                               | SYMBOL          | CONDITIONS                                                |                              | MIN   | ТҮР   | MAX   | UNITS |  |

|---------------------------------------------------------|-----------------|-----------------------------------------------------------|------------------------------|-------|-------|-------|-------|--|

| GENERAL                                                 |                 | ·                                                         |                              |       |       |       |       |  |

| Supply Voltage Range                                    | V <sub>DD</sub> | Guaranteed by PS                                          | RR test                      | 2.7   |       | 5.5   | V     |  |

| Quiescent Current                                       | ICC             |                                                           |                              |       | 3.5   | 5.5   | mA    |  |

| Shutdown Current                                        | ISHDN           | SHDN = SGND =                                             | PGND                         |       | 0.1   | 1     | μA    |  |

| Shutdown to Full Operation                              | tson            |                                                           |                              |       | 180   |       | μs    |  |

| Input Impedance                                         | RIN             | MAX9724B, meas                                            | ured at IN_                  | 12    | 19    | 28    | kΩ    |  |

| Output Offset Voltage                                   | VOS             | (Note 4)                                                  |                              |       | ±1.5  | ±10   | mV    |  |

|                                                         |                 | $V_{DD} = 2.7V$ to 5.5V                                   | /, T <sub>A</sub> = +25°C    | 69    | 86    |       |       |  |

| Power-Supply Rejection Ratio                            | PSRR            | $f = 1 kHz$ , $100 mV_P$ .                                | P (Note 4)                   |       | 80    |       | dB    |  |

|                                                         |                 | f = 20kHz, 100mV                                          | P-P (Note 4)                 |       | 65    |       |       |  |

|                                                         | Dour            | $R_L = 32\Omega$ , THD+N                                  | = 1%                         | 30    | 63    |       | mW    |  |

| Output Power (TQFN)                                     | Pout            | $R_L = 16\Omega$ , THD+N = 1%                             |                              |       | 42    |       |       |  |

| Output Dawler (LICCD)                                   | Davie           | $R_L = 32\Omega$ , THD+N = 1%                             |                              | 25    | 45    |       | mW    |  |

| Output Power (UCSP)                                     | Роит            | $R_L = 16\Omega$ , THD+N = 1%                             |                              |       | 35    |       |       |  |

| Voltage Gain                                            | Av              | MAX9724B (Note 5)                                         |                              | -1.52 | -1.5  | -1.48 | V/V   |  |

| Channel-to-Channel Gain Tracking                        |                 | MAX9724B                                                  |                              |       | ±0.15 |       | %     |  |

| T                                                       |                 | $R_L = 1k\Omega$ , $V_{OUT} = 2V_{RMS}$ , $f_{IN} = 1kHz$ |                              |       | 0.003 |       |       |  |

| Total Harmonic Distortion Plus                          | THD+N           | $R_L = 32\Omega$ , $P_{OUT} = 50$ mW, $f_{IN} = 1$ kHz    |                              |       | 0.02  | %     |       |  |

| Noise (TQFN) (Note 6)                                   |                 | $R_L = 16\Omega$ , $P_{OUT} = 35$ mW, $f_{IN} = 1$ kHz    |                              |       | 0.04  |       |       |  |

|                                                         |                 | $R_L = 1k\Omega$ , $V_{OUT} = 2V_{RMS}$ , $f_{IN} = 1kHz$ |                              |       | 0.003 |       |       |  |

| Total Harmonic Distortion Plus<br>Noise (UCSP) (Note 6) | THD+N           | $R_L = 32\Omega$ , $P_{OUT} = 45$ mW, $f_{IN} = 1$ kHz    |                              |       | 0.03  |       | %     |  |

|                                                         |                 | $R_L = 16\Omega$ , $P_{OUT} =$                            | 32mW, f <sub>IN</sub> = 1kHz |       | 0.05  |       |       |  |

|                                                         |                 | $R_L = 1k\Omega$ ,                                        | BW = 22Hz to 22kHz           |       | 102   |       |       |  |

| Signal to Noise Patio                                   | SNR             | $V_{OUT} = 2V_{RMS}$                                      | A-weighted                   |       | 105   |       | dB    |  |

| Signal-to-Noise Ratio                                   |                 | $R_L = 32\Omega$ ,                                        | BW = 22Hz to 22kHz           |       | 98    |       | uр    |  |

|                                                         |                 | $P_{OUT} = 50 mW$                                         | A-weighted                   |       | 101   |       |       |  |

MAX9724A/MAX9724B

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V, PGND = SGND, \overline{SHDN} = 5V, C1 = C2 = 1\mu F, R_L = \infty$ , resistive load reference to ground; for MAX9724A gain = -1.5V/V (R\_{IN} = 20k\Omega, R\_F = 30k\Omega); for MAX9724B gain = -1.5V/V (internally set), T\_A = -40°C to +85°C, unless otherwise noted. Typical values are at T\_A = +25°C, unless otherwise noted.) (Note 3)

| PARAMETER                           | SYMBOL           | CONDITIONS                                                                           | ;                  | MIN | ТҮР | MAX | UNITS |

|-------------------------------------|------------------|--------------------------------------------------------------------------------------|--------------------|-----|-----|-----|-------|

| Slew Rate                           | SR               |                                                                                      |                    |     | 0.5 |     | V/µs  |

| Capacitive Drive                    | CL               | No sustained oscillations                                                            |                    |     | 100 |     | pF    |

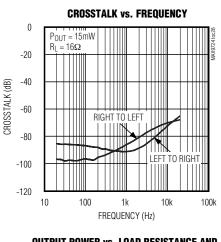

| Crosstalk                           |                  | L to R, R to L, f = 10kHz, R <sub>L</sub> = 16 $\Omega$ ,<br>P <sub>OUT</sub> = 15mW |                    |     | -70 |     | dB    |

| Charge-Pump Oscillator<br>Frequency | fosc             |                                                                                      |                    | 190 | 270 | 400 | kHz   |

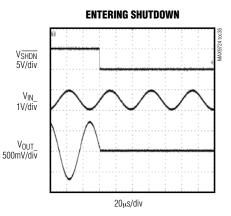

|                                     |                  | $R_L = 32\Omega$ , peak voltage,                                                     | Into shutdown      |     | -67 |     |       |

| Click-and-Pop Level                 | KCP              | A-weighted, 32 samples per second (Notes 4, 7)                                       | Out of<br>shutdown |     | -64 |     | dB    |

| DIGITAL INPUTS (SHDN)               |                  |                                                                                      | ·                  |     |     |     |       |

| Input-Voltage High                  | VINH             | (TQFN only)                                                                          |                    | 2   |     |     | V     |

| Input-Voltage Low                   | VINL             | (TQFN only)                                                                          |                    |     |     | 0.8 | V     |

| Input-Voltage High                  | VINH             | (UCSP only)                                                                          |                    | 1.4 |     |     | V     |

| Input-Voltage Low                   | V <sub>INL</sub> | (UCSP only)                                                                          |                    |     |     | 0.9 | V     |

| Input Leakage Current               |                  |                                                                                      |                    |     |     | ±1  | μA    |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 3V, PGND = SGND, \overline{SHDN} = 3V, C1 = C2 = 1\mu F, R_L = \infty$ , resistive load reference to ground; for MAX9724A gain = -1.5V/V (R<sub>IN</sub> = 20k $\Omega$ , R<sub>F</sub> = 30k $\Omega$ ); for MAX9724B gain = -1.5V/V (internally set), T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 3)

| PARAMETER                                               | SYMBOL | CONDITIONS                                                | MIN | ТҮР   | MAX | UNITS |  |

|---------------------------------------------------------|--------|-----------------------------------------------------------|-----|-------|-----|-------|--|

| Quiescent Current                                       | ICC    |                                                           |     | 3.0   |     | mA    |  |

| Shutdown Current                                        | ISHDN  | $\overline{\text{SHDN}} = \text{SGND} = \text{PGND}$      |     | 0.1   |     | μA    |  |

| Power-Supply Rejection Ratio                            | PSRR   | $f = 1 \text{kHz}, 100 \text{mV}_{P-P}$                   |     | 80    |     | dB    |  |

| (Note 4)                                                | Fonn   | f = 20kHz, 100mV <sub>P-P</sub>                           |     | 65    |     | uБ    |  |

|                                                         |        | $R_L = 32\Omega$ , THD+N = 1%                             |     | 20    |     | m\//  |  |

| Output Power (TQFN)                                     | Pout   | $R_L = 16\Omega$ , THD+N = 1%                             |     | 14    |     | mW    |  |

|                                                         | Davia  | $R_L = 32\Omega$ , THD+N = 1%                             |     | 17    |     |       |  |

| Output Power (UCSP)                                     | Pout   | $R_L = 16\Omega$ , THD+N = 1%                             |     | 12    |     | mW    |  |

| T                                                       |        | $R_L = 1k\Omega$ , $V_{OUT} = 2V_{RMS}$ , $f_{IN} = 1kHz$ |     | 0.05  |     |       |  |

| Total Harmonic Distortion Plus                          | THD+N  | $R_L = 32\Omega$ , $P_{OUT} = 15$ mW, $f_{IN} = 1$ kHz    |     | 0.03  |     | %     |  |

| Noise (TQFN) (Note 6)                                   |        | $R_L = 16\Omega$ , $P_{OUT} = 10$ mW, $f_{IN} = 1$ kHz    |     | 0.06  |     |       |  |

|                                                         |        | $R_L = 1k\Omega$ , $V_{OUT} = 2V_{RMS}$ , $f_{IN} = 1kHz$ |     | 0.003 |     |       |  |

| Total Harmonic Distortion Plus<br>Noise (UCSP) (Note 6) | THD+N  | $R_L = 32\Omega$ , $P_{OUT} = 15$ mW, $f_{IN} = 1$ kHz    |     | 0.04  |     | %     |  |

|                                                         |        | $R_L = 16\Omega$ , $P_{OUT} = 10$ mW, $f_{IN} = 1$ kHz    |     | 0.06  |     |       |  |

Note 3: All specifications are 100% tested at  $T_A = +25$ °C; temperature limits are guaranteed by design.

**Note 4:** The amplifier inputs are AC-coupled to GND.

Note 5: Gain for the MAX9724A is adjustable.

Note 6: Measurement bandwidth is 22Hz to 22kHz.

Note 7: Test performed with a 32Ω resistive load connected to GND. Mode transitions are controlled by SHDN. K<sub>CP</sub> level is calculated as 20log[(peak voltage during mode transition, no input signal)/(peak voltage under normal operation at rated power level)]. Units are expressed in dB.

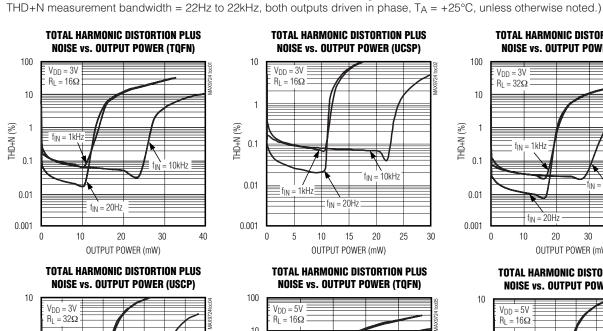

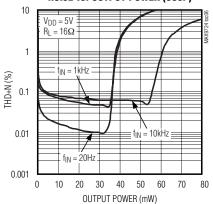

$(V_{DD} = 5V, PGND = SGND = 0V, \overline{SHDN} = V_{DD}, C1 = C2 = 1\mu F, R_L = \infty, gain = -1.5V/V (R_{IN} = 20k\Omega, R_F = 30k\Omega for the MAX9724A),$

MAX9724A/MAX9724B

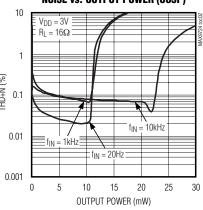

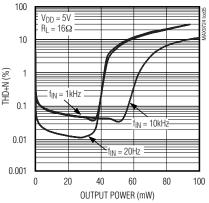

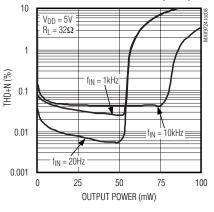

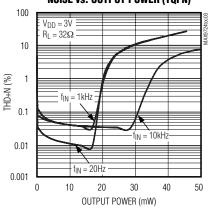

#### TOTAL HARMONIC DISTORTION PLUS **NOISE vs. OUTPUT POWER (TQFN)**

#### **TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (UCSP)**

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (TQFN)**

#### TOTAL HARMONIC DISTORTION PLUS **NOISE vs. OUTPUT POWER (UCSP)**

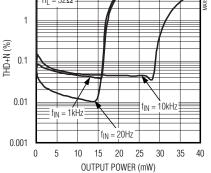

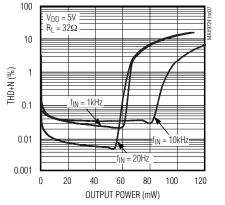

#### **Typical Operating Characteristics**

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (TQFN)**

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. OUTPUT POWER (UCSP)**

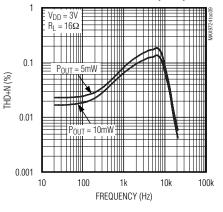

**TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY (TQFN)**

MXXIM

#### **Typical Operating Characteristics (continued)**

$(V_{DD} = 5V, PGND = SGND = 0V, \overline{SHDN} = V_{DD}, C1 = C2 = 1\mu F, R_L = \infty, gain = -1.5V/V (R_{IN} = 20k\Omega, R_F = 30k\Omega for the MAX9724A),$

# MAX9724A/MAX9724B

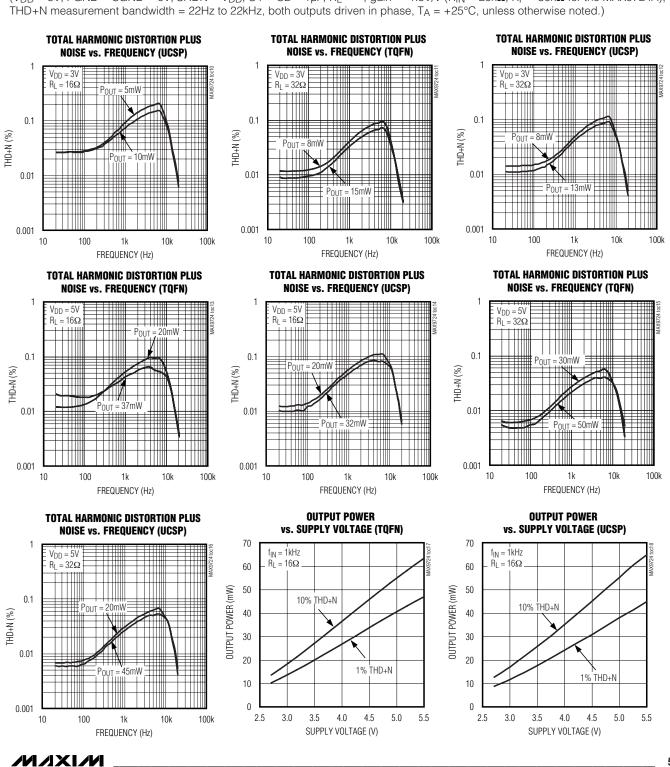

#### **Typical Operating Characteristics (continued)**

M/XX/M

$(V_{DD} = 5V, PGND = SGND = 0V, \overline{SHDN} = V_{DD}, C1 = C2 = 1\mu F, R_L = \infty, gain = -1.5V/V (R_{IN} = 20k\Omega, R_F = 30k\Omega for the MAX9724A), THD+N measurement bandwidth = 22Hz to 22kHz, both outputs driven in phase, T_A = +25°C, unless otherwise noted.)$

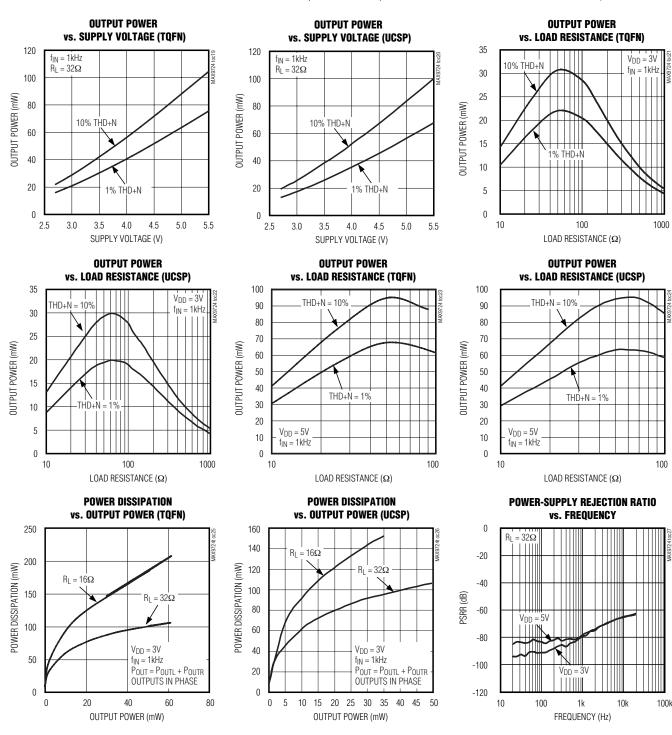

#### **Typical Operating Characteristics (continued)**

$(V_{DD} = 5V, PGND = SGND = 0V, \overline{SHDN} = V_{DD}, C1 = C2 = 1\mu F, R_L = \infty, gain = -1.5V/V (R_{IN} = 20k\Omega, R_F = 30k\Omega for the MAX9724A), THD+N measurement bandwidth = 22Hz to 22kHz, both outputs driven in phase, T_A = +25°C, unless otherwise noted.)$

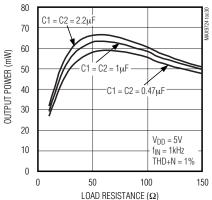

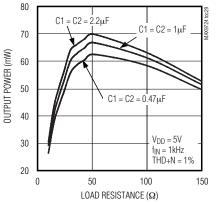

OUTPUT POWER vs. LOAD RESISTANCE AND CHARGE-PUMP CAPACITOR SIZE (UCSP)

#### OUTPUT POWER vs. LOAD RESISTANCE AND CHARGE-PUMP CAPACITOR SIZE (TQFN)

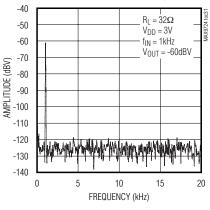

**OUTPUT SPECTRUM vs. FREQUENCY**

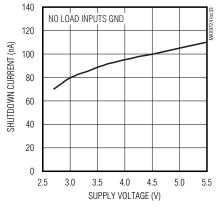

#### SHUTDOWN CURRENT vs. SUPPLY VOLTAGE (TQFN)

#### **Typical Operating Characteristics (continued)**

$(V_{DD} = 5V, PGND = SGND = 0V, \overline{SHDN} = V_{DD}, C1 = C2 = 1\mu F, R_L = \infty, gain = -1.5V/V (R_{IN} = 20k\Omega, R_F = 30k\Omega for the MAX9724A), THD+N measurement bandwidth = 22Hz to 22kHz, both outputs driven in phase, T_A = +25°C, unless otherwise noted.)$

#### **Pin Description**

| F    | PIN  |                 | FUNCTION                                                                                         |

|------|------|-----------------|--------------------------------------------------------------------------------------------------|

| TQFN | UCSP | NAME            | FUNCTION                                                                                         |

| 1    | C1   | C1P             | Flying Capacitor Positive Terminal. Connect a 1µF ceramic capacitor from C1P to C1N.             |

| 2    | C2   | PGND            | Power Ground. Connect to SGND.                                                                   |

| 3    | C3   | C1N             | Flying Capacitor Negative Terminal. Connect a 1µF ceramic capacitor from C1P to C1N.             |

| 4    | C4   | PVSS            | Charge-Pump Output. Connect to SV <sub>SS</sub> and bypass with a 1µF ceramic capacitor to PGND. |

| 5    | A2   | SHDN            | Active-Low Shutdown Input                                                                        |

| 6    | B3   | INL             | Left-Channel Input                                                                               |

| 7    | A1   | SGND            | Signal Ground. Connect to PGND.                                                                  |

| 8    | B2   | INR             | Right-Channel Input                                                                              |

| 9    | B4   | SVSS            | Amplifier Negative Supply. Connect to PVSS.                                                      |

| 10   | A3   | OUTR            | Right-Channel Output                                                                             |

| 11   | A4   | OUTL            | Left-Channel Output                                                                              |

| 12   | B1   | V <sub>DD</sub> | Positive Power-Supply Input. Bypass with a 1µF capacitor to PGND.                                |

| EP   | _    | EP              | Exposed Paddle. Internally connected to SVSS. Connect to SVSS or leave unconnected.              |

M/IXI/M

#### **Detailed Description**

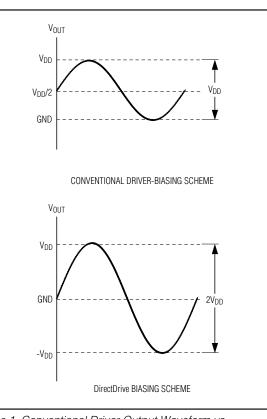

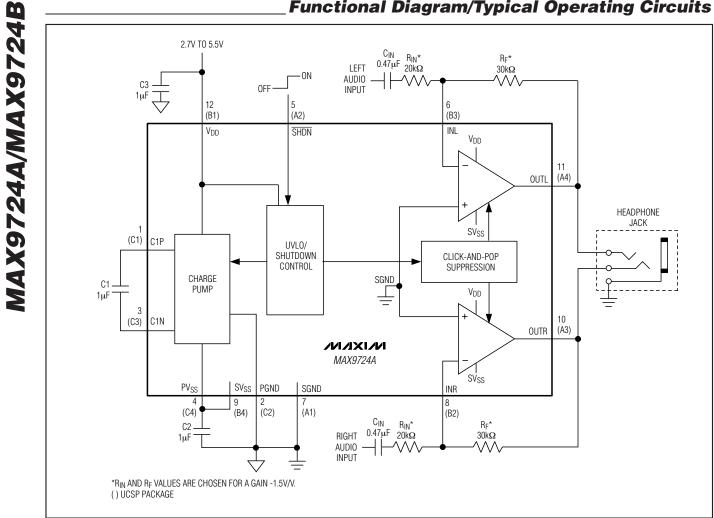

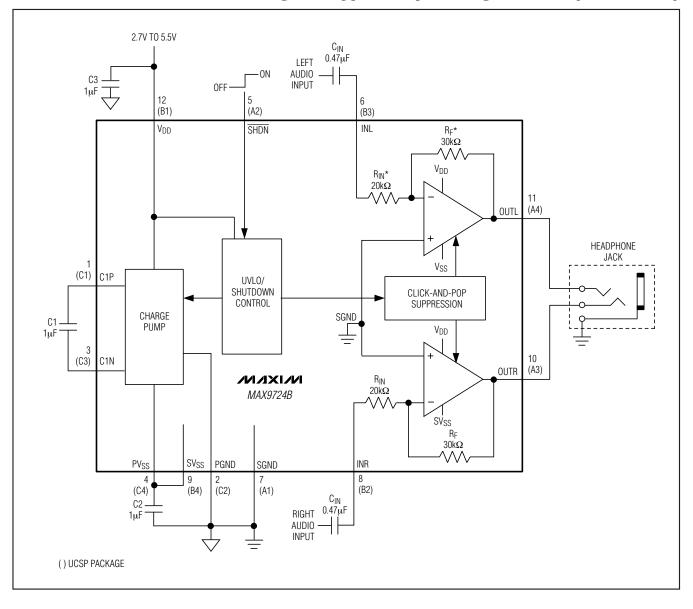

The MAX9724A/MAX9724B stereo headphone amplifiers feature Maxim's DirectDrive architecture, eliminating the large output-coupling capacitors required by conventional single-supply headphone amplifiers. The device consists of two 60mW Class AB headphone amplifiers, undervoltage lockout (UVLO)/shutdown control, charge pump, and comprehensive click-and-pop suppression circuitry (see the Functional Diagram/Typical Operating Circuits). The charge pump inverts the positive supply (V<sub>DD</sub>), creating a negative supply (PV<sub>SS</sub>). The headphone amplifiers operate from these bipolar supplies with their outputs biased about PGND (Figure 1). The benefit of this PGND bias is that the amplifier outputs do not have a DC component. The large DC-blocking capacitors required with conventional headphone amplifiers are unnecessary, conserving board space, reducing system cost, and improving freguency response. The MAX9724A/MAX9724B feature an undervoltage lockout that prevents operation from an insufficient power supply and click-and-pop suppression that eliminates audible transients on startup and shutdown. The MAX9724A/MAX9724B also feature thermal-overload and short-circuit protection.

#### **DirectDrive**

Conventional single-supply headphone amplifiers have their outputs biased about a nominal DC voltage (typically half the supply) for maximum dynamic range. Large-coupling capacitors are needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone amplifier.

Maxim's DirectDrive architecture uses a charge pump to create an internal negative supply voltage, allowing the MAX9724A/MAX9724B outputs to be biased about GND. With no DC component, there is no need for the large DC-blocking capacitors. The MAX9724A/ MAX9724B charge pumps require two small ceramic capacitors, conserving board space, reducing cost, and improving the frequency response of the headphone amplifier. See the Output Power vs. Load Resistance and Charge-Pump Capacitor Size graph in the Typical Operating Characteristics for details of the possible capacitor sizes. There is a low DC voltage on the amplifier outputs due to amplifier offset. However, the offsets of the MAX9724A/MAX9724B are typically 1.5mV, which, when combined with a  $32\Omega$  load, results in less than 47µA of DC current flow to the headphones.

Figure 1. Conventional Driver Output Waveform vs. MAX9724A/MAX9724B Output Waveform

#### Charge Pump

MAX9724A/MAX9724B

The MAX9724A/MAX9724B feature a low-noise charge pump. The 270kHz switching frequency is well beyond the audio range and does not interfere with audio signals. The switch drivers feature a controlled switching speed that minimizes noise generated by turn-on and turn-off transients. The di/dt noise caused by the parasitic bond wire and trace inductance is minimized by limiting the switching speed of the charge pump. Although not typically required, additional high-frequency noise attenuation can be achieved by increasing the value of C2 (see the *Functional Diagram/Typical Operating Circuits*).

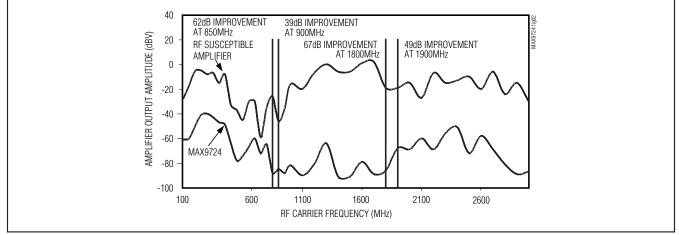

#### **RF Susceptibility**

Modern audio systems are often subject to RF radiation from sources like wireless networks and cellular phone networks. Although the RF radiation is out of the audio band, many signals, in particular GSM signals, contain bursts or modulation at audible frequencies. Most analog amplifiers demodulate the low-frequency envelope, adding noise to the audio signal. The architecture of

M/X//M

the MAX9724 addresses the problem of the RF susceptibility by rejecting RF noise and preventing it from coupling into the audio band.

The RF susceptibility of an amplifier can be measured by placing the amplifier in an isolated chamber and subjecting it to an electric field of known strength. If the electric field is modulated with an audio band signal, a percentage of the modulated signal will be demodulated and amplified by the device in the chamber. Figure 2 shows the signal level at the outputs of an unoptimized amplifier and the MAX9724. The test conditions are shown in Table 1.

#### Table 1. RF Susceptibility Test Conditions

| TEST PARAMETER          | SETTING   |

|-------------------------|-----------|

| RF Field Strength       | 50V/m     |

| RF Modulation Type      | Sine wave |

| RF Modulation Index     | 100%      |

| RF Modulation Frequency | 1kHz      |

#### **Click-and-Pop Suppression**

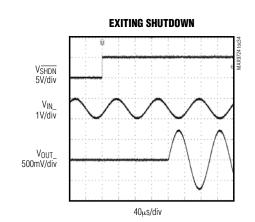

In conventional single-supply audio amplifiers, the output-coupling capacitor contributes significantly to audible clicks and pops. Upon startup, the amplifier charges the coupling capacitor to its bias voltage, typically half the supply. Likewise, on shutdown, the capacitor is discharged. This results in a DC shift across the capacitor, which appears as an audible transient at the speaker. Since the MAX9724A/ MAX9724B do not require outputcoupling capacitors, this problem does not arise. Additionally, the MAX9724A/MAX9724B feature extensive click-and-pop suppression that eliminates any audible transient sources internal to the device. Typically, the output of the device driving the MAX9724A/MAX9724B has a DC bias of half the supply voltage. At startup, the input-coupling capacitor, C<sub>IN</sub>, is charged to the preamplifier's DC bias voltage through the MAX9724A/MAX9724B input resistor, R<sub>IN</sub>, and a series 15k $\Omega$  resistor. This DC shift across the capacitor results in an audible click-and-pop. Delay the rise of SHDN 4 to 5 time constants based on R<sub>IN</sub> x 15k $\Omega$  x C<sub>IN</sub> to eliminate clicks-and-pops caused by the input filter.

#### Shutdown

The MAX9724A/MAX9724B feature  $a < 0.1 \mu A$ , low-power shutdown mode that reduces quiescent current consumption and extends battery life for portable applications. Drive  $\overline{SHDN}$  low to disable the amplifiers and the charge pump. In shutdown mode, the amplifier output impedance is set to  $14 k \Omega IIR_F$  (RF is  $30 k \Omega$  for the MAX9724B). The amplifiers and charge pump are enabled once  $\overline{SHDN}$  is driven high.

#### **Applications Information**

#### **Power Dissipation**

Under normal operating conditions, linear power amplifiers can dissipate a significant amount of power. The maximum power dissipation for each package is given in the *Absolute Maximum Ratings* section under Continuous Power Dissipation or can be calculated by the following equation:

$$P_{\text{DISSPKG}(\text{MAX})} = \frac{T_{\text{J}(\text{MAX})} - T_{\text{A}}}{\theta_{\text{JA}}}$$

where  $T_{J(MAX)}$  is +150°C,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the reciprocal of the derating factor in

Figure 2. RF Susceptibility of the MAX9724 and a Typical Headphone Amplifier

°C/W as specified in the Absolute Maximum Ratings section. For example,  $\theta_{JA}$  of the thin QFN package is +68°C/W, and 154.2°C/W for the UCSP package.

The MAX9724A/MAX9724B have two power dissipation sources; a charge pump and the two output amplifiers. If power dissipation for a given application exceeds the maximum allowed for a particular package, reduce  $V_{DD}$ , increase load impedance, decrease the ambient temperature, or add heatsinking to the device. Large output, supply, and ground traces decrease  $\theta_{JA}$ , allowing more heat to be transferred from the package to the surrounding air.

Thermal-overload protection limits total power dissipation in the MAX9724A/MAX9724B. When the junction temperature exceeds +150°C, the thermal protection circuitry disables the amplifier output stage. The amplifiers are enabled once the junction temperature cools by approximately 12°C. This results in a pulsing output under continuous thermal-overload conditions.

#### **Output Dynamic Range**

Dynamic range is the difference between the noise floor of the system and the output level at 1% THD+N. Determine the system's dynamic range before setting the maximum output gain. Output clipping occurs if the output signal is greater than the dynamic range of the system. The DirectDrive architecture of the MAX9724A/ MAX9724B has increased the dynamic range compared to other single-supply amplifiers.

#### **Maximum Output Swing**

#### $V_{DD} < 4.35V$

If the output load impedance is greater than  $1k\Omega$ , the MAX9724A/MAX9724B can swing within a few millivolts of their supply rail. For example, with a 3.3V supply, the output swing is  $2V_{RMS}$ , or 2.83V peak while maintaining a low 0.003% THD+N. If the supply voltage drops to 3V, the same 2.83V peak has only 0.05% THD+N.

#### $V_{DD} > 4.35V$

Internal device structures limit the maximum voltage swing of the MAX9724A/MAX9724B when operated at supply voltages greater than 4.35V. The output must not be driven such that the peak output voltage exceeds the opposite supply voltage by 9V. For example, if  $V_{DD} = 5V$ , the charge pump sets  $PV_{SS} = -5V$ . Therefore, the peak output swing must be less than ±4V to prevent exceeding the absolute maximum ratings.

#### UVLO

The MAX9724A/MAX9724B feature an undervoltage lockout (UVLO) function that prevents the device from operating if the supply voltage is less than 2.7V. This feature ensures proper operation during brownout conditions and prevents deep battery discharge. Once the supply voltage exceeds the UVLO threshold, the MAX9724A/MAX9724B charge pump is turned on and the amplifiers are powered, provided that SHDN is high.

#### **Component Selection**

#### Input-Coupling Capacitor

The input capacitor (C<sub>IN</sub>), in conjunction with the input resistor (R<sub>IN</sub>), forms a highpass filter that removes the DC bias from an incoming signal (see the *Functional Diagram/Typical Operating Circuits*). The AC-coupling capacitor allows the device to bias the signal to an optimum DC level. Assuming zero-source impedance, the - 3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Choose the  $C_{IN}$  such that  $f_{-3dB}$  is well below the lowest frequency of interest. Setting  $f_{-3dB}$  too high affects the device's low-frequency response. Use capacitors whose dielectrics have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, can result in increased distortion at low frequencies.

#### **Charge-Pump Capacitor Selection**

Use ceramic capacitors with a low ESR for optimum performance. For optimal performance over the extended temperature range, select capacitors with an X7R dielectric. Table 2 lists suggested manufacturers.

#### Flying Capacitor (C1)

The value of the flying capacitor (see the *Functional Diagram/Typical Operating Circuits*) affects the charge

| Table 2. Suggested | Capacitor | Manufacturers |

|--------------------|-----------|---------------|

|--------------------|-----------|---------------|

| SUPPLIER    | PHONE        | FAX          | WEBSITE               |

|-------------|--------------|--------------|-----------------------|

| Taiyo Yuden | 800-348-2496 | 847-925-0899 | www.t-yuden.com       |

| ТДК         | 847-803-6100 | 847-390-4405 | www.component.tdk.com |

| Murata      | 770-436-1300 | 770-436-3030 | www.murata.com        |

pump's load regulation and output resistance. A C1 value that is too small degrades the device's ability to provide sufficient current drive, which leads to a loss of output voltage. Increasing the value of C1 improves load regulation and reduces the charge-pump output resistance to an extent. See the Output Power vs. Load Resistance and Charge-Pump Capacitor Size graph in the *Typical Operating Characteristics*. Above 1 $\mu$ F, the on-resistance of the switches and the ESR of C1 and C2 dominate.

#### Hold Capacitor (C2)

The hold capacitor value (see the *Functional Diagram/Typical Operating Circuits*) and ESR directly affect the ripple at PVss. Increasing the value of C2 reduces output ripple. Likewise, decreasing the ESR of C2 reduces both ripple and output resistance. Lower capacitance values can be used in systems with low maximum output power levels. See the Output Power vs. Load Resistance and Charge-Pump Capacitor Size graph in the *Typical Operating Characteristics*.

#### Power-Supply Bypass Capacitor (C3)

The power-supply bypass capacitor (see the *Functional Diagram/Typical Operating Circuits*) lowers the output impedance of the power supply, and reduces the impact of the MAX9724A/MAX9724B's charge-pump switching transients. Bypass V<sub>DD</sub> with C3, the same value as C1, and place it physically close to the V<sub>DD</sub> and PGND pins.

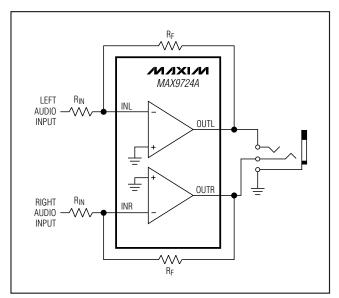

#### **Amplifier Gain**

The gain of the MAX9724B amplifier is internally set to -1.5V/V. All gain-setting resistors are integrated into the device, reducing external component count. The internally set gain, in combination with DirectDrive, results in a headphone amplifier that requires only five small capacitors to complete the amplifier circuit: two for the charge pump, two for audio input coupling, and one for power-supply bypassing (see the *Functional Diagram/Typical Operating Circuits*).

The gain of the MAX9724A amplifier is set externally as shown in Figure 3, the gain is:

#### $A_V = -R_F/R_{IN} (V/V)$

Choose feedback resistor values in the tens of  $\ensuremath{k\Omega}$ range. Lower values may cause excessive power dissipation and require impractically small values of RIN for large gain settings. The high-impedance state of the outputs can also be degraded during shutdown mode if an inadequate feedback resistor is used since the equivalent output impedance during shutdown is  $14k\Omega IIR_f$  (RF is equal to  $30k\Omega$  for the MAX9724B). The source resistance of the input device may also need to be taken into consideration. Since the effective value of RIN is equal to the sum of the source resistance of the input device and the value of the input resistor connected to the inverting terminal of the headphone amplifier  $(20k\Omega \text{ for the MAX9724B})$ , the overall closed-loop gain of the headphone amplifier can be reduced if the input resistor is not significantly larger than the source resistance of the input device.

Figure 3. Gain Setting for the MAX9724A

#### **Lineout Amplifier and Filter Block**

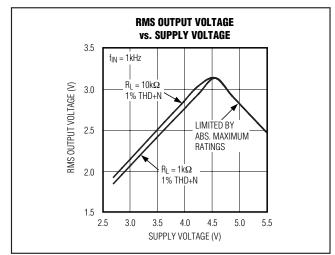

The MAX9724A can be used as an audio line driver capable of providing  $2V_{RMS}$  into  $10k\Omega$  loads with a single 5V supply (see Figure 4 for the RMS Output Voltage vs. Supply Voltage plot).  $2V_{RMS}$  is a popular audio line level, first used in CD players, but now common in DVD and set-top box (STB) interfacing standards. A  $2V_{RMS}$

Figure 4. RMS Output Voltage vs. Supply Voltage

sinusoidal signal equates to approximately 5.7VP-P, which means that the audio system designer cannot simply run the lineout stage from a (typically common) 5V supply—the resulting output swing would be inadequate. A common solution to this problem is to use op amps driven from split supplies (±5V typically), or to use a high-voltage supply rail (9V to 12V). This can mean adding extra cost and complexity to the system power supply to meet this output level requirement. Having the ability to derive 2V<sub>RMS</sub> from a 5V supply, or even 3.3V supply, can often simplify power-supply design in some systems.

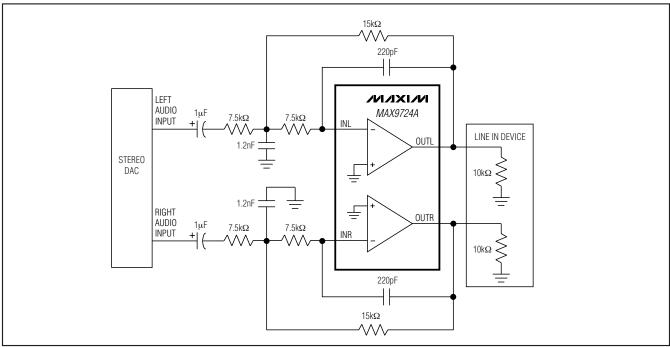

When the MAX9724A is used as a line driver to provide outputs that feed stereo equipment (receivers, STBs, notebooks, and desktops) with a digital-to-analog converter (DAC) used as an audio input source, it is often desirable to eliminate any high-frequency quantization noise produced by the DAC output before it reaches the load. This high-frequency noise can cause the input stages of the line-in equipment to exceed slew-rate limitations or create excessive EMI emissions on the cables between devices.

Figure 5. MAX9724A Line Out Amplifier and Filter Block Configuration

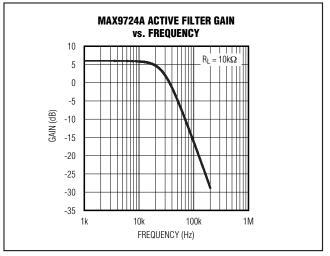

To suppress this noise, and to provide a 2V<sub>RMS</sub> standard audio output level from a single 5V supply, the MAX9724A can be configured as a line driver and active lowpass filter. Figure 5 shows the MAX9724A connected as 2-pole Rauch/multiple feedback filter with a passband gain of 6dB and a -3dB (below passband) cutoff frequency of approximately 27kHz (see Figure 6 for the Gain vs. Frequency plot).

#### Layout and Grounding

Proper layout and grounding are essential for optimum performance. Connect PGND and SGND together at a single point on the PC Board. Connect PVss to SVss and bypass with a 1µF capacitor. Place the power-supply bypass capacitor and the charge-pump hold capacitor as close to the MAX9724 as possible. Route PGND and all traces that carry switching transients away from SGND and the audio signal path. The thin QFN package features an exposed paddle that improves thermal efficiency. Ensure that the exposed paddle is electrically isolated from PGND, SGND, and VDD. Connect the exposed paddle to SVss only when the board layout dictates that the exposed paddle cannot be left floating.

#### **UCSP** Applications Information

For the latest application details on UCSP construction, dimensions, tape carrier information, printed circuit board techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, refer to the Application Note UCSP—A Wafer-Level Chip-Scale Package available on Maxim's website at www.maximic.com/ucsp.

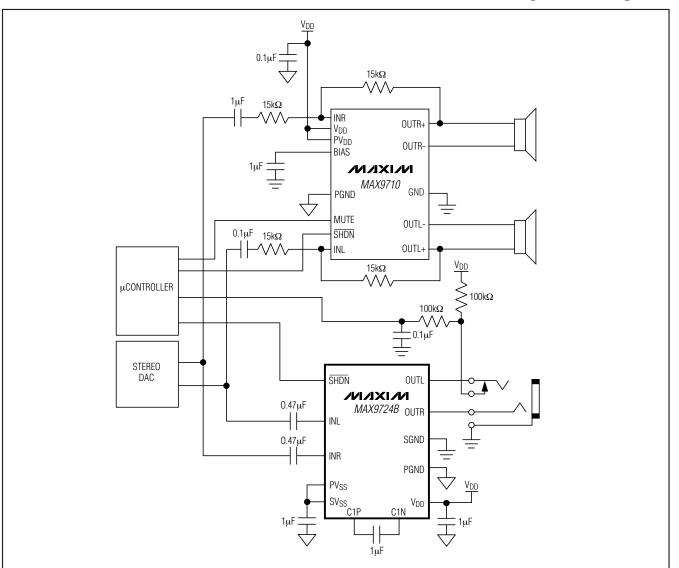

\_System Diagram

#### Functional Diagram/Typical Operating Circuits

#### Functional Diagram/Typical Operating Circuits (continued)

MAX9724A/MAX9724B

**Chip Information**

PROCESS: BICMOS

#### **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 12 UCSP      | B12-1        | <u>21-0104</u> |

| 12 TQFN      | T1233-1      | <u>21-0136</u> |

#### Revision History

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                 | PAGES<br>CHANGED     |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------|

| 0                  | 5/05             | Initial release                                                                                                             | _                    |

| 1                  | 1/06             | Added RF immunity to <i>General Description</i> , <i>Features</i> , and <i>Detailed Description</i> .                       | 1, 7                 |

| 2                  | 11/06            | Added UCSP package.                                                                                                         | 1–3, 6, 9, 12, 14–16 |

| 3                  | 3/07             | Updated <i>Electrical Characteristics</i> table and <i>Typical Operating Characteristics</i> .                              | 1–6, 17, 18          |

| 4                  | 6/07             | Corrected Pin Description, Pin Configuration, and Functional Diagrams/Typical Operating Circuits with new UCSP information. | 1–6, 12, 14–16       |

| 5                  | 3/08             | Updated Absolute Maximum Ratings and Click-and-Pop Suppression section.                                                     | 2, 10                |

| 6                  | 3/09             | Updated Ordering Information, style changes                                                                                 | 1, 10, 18, 19        |

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio Amplifiers category:

Click to view products by Maxim manufacturer:

Other Similar products are found below :

LV47002P-E NCP2811AFCT1G NCP2890AFCT2G SSM2377ACBZ-R7 IS31AP4915A-QFLS2-TR NCP2820FCT2G TDA1591T TDA7563AH SSM2529ACBZ-R7 MAX9890AETA+T TS2012EIJT NCP2809BMUTXG NJW1157BFC2 SSM2375CBZ-REEL7 IS31AP4996-GRLS2-TR STPA002OD-4WX NCP2823BFCT1G MAX9717DETA+T MAX9717CETA+T MAX9724AEBC+TG45 LA4450L-E IS31AP2036A-CLS2-TR MAX9723DEBE+T TDA7563ASMTR AS3561-DWLT SSM2517CBZ-R7 MP1720DH-12-LF-P SABRE9601K THAT1646W16-U MAX98396EWB+ PAM8965ZLA40-13 BD37532FV-E2 BD5638NUX-TR BD37512FS-E2 BD37543FS-E2 BD3814FV-E2 TPA3140D2PWPR TS2007EIJT IS31AP2005-DLS2-TR SSM2518CPZ-R7 AS3410-EQFP-500 FDA4100LV MAX98306ETD+T TS4994EIJT NCP2820FCT1G NCP2823AFCT2G NCS2211MNTXG CPA2233CQ16-A1 OPA1604AIPWR OPA1612AQDRQ1