#### MAX98050

# Low-Power, High-Performance Audio Codec

#### **General Description**

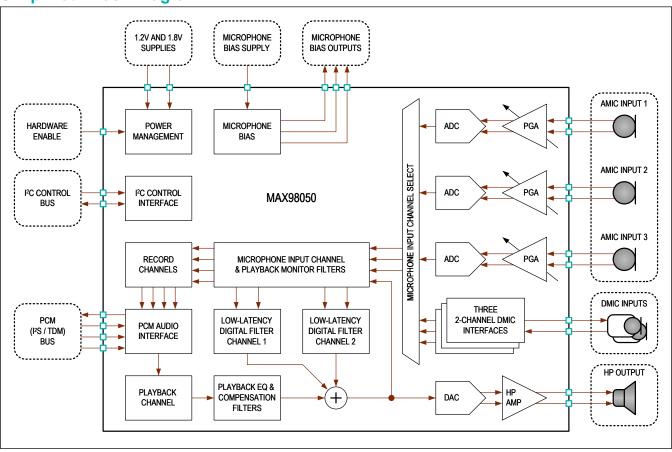

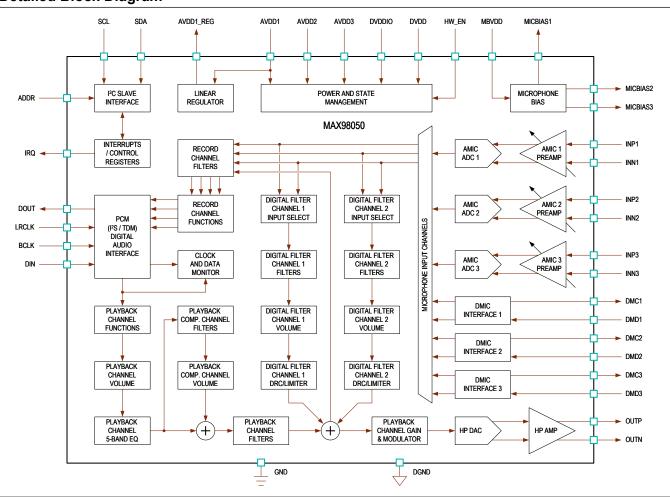

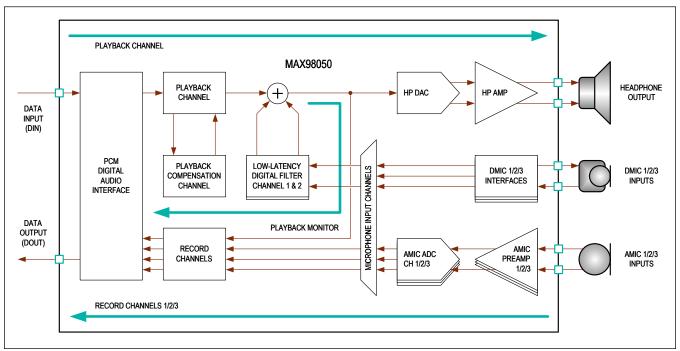

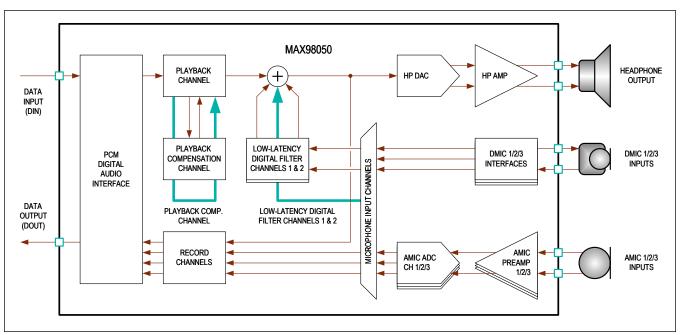

The MAX98050 is a low-power, high-performance audio CODEC with integrated low-latency digital filters for wireless hearables, headsets, and headphones.

The device features a mono playback channel with a 5-band biquad equalizer and a high-efficiency, fully differential hybrid class-AB/class-D headphone amplifier. The playback headphone amplifier is optimized for extremely low output noise levels and minimized quiescent power consumption while maximizing output power efficiency.

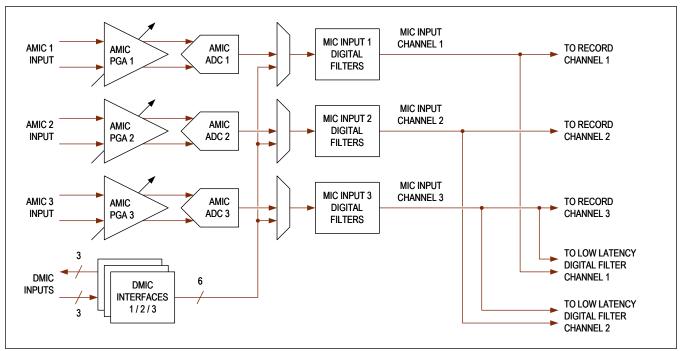

The device includes three microphone input channels capable of supporting voice, ambient, and anti-noise record use cases. Each channel can individually record from either an external analog or digital microphone, and then can route audio data to both the record channels (to the digital audio interface) and the internal low-latency digital filter channels. A fourth record channel to the digital audio interface is provided to allow the host to monitor the playback channel output digital data.

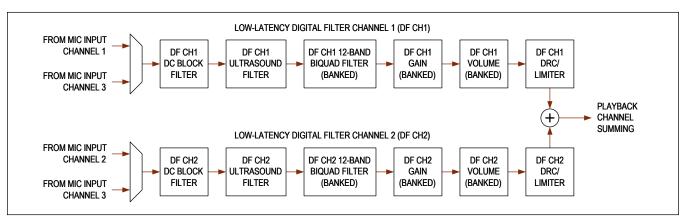

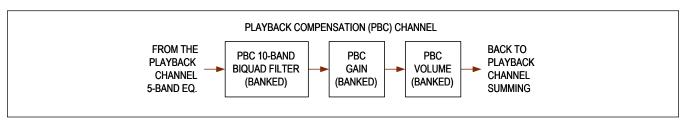

Two low-latency, digital filter channels are provided that can support a variety of use cases. These include noise cancellation applications (feed-forward, feedback, and hybrid filter profiles), both voice and ambient enhancement and transparency applications, and sidetone applications. Each channel provides a 12-band digital biquad filter, a DRC or Limiter stage, a digital volume control block, and an ultrasound filter. In addition, a third internal digital filter channel is provided in the playback channel that is structured for playback compensation and/or general feedback compensation filters. This channel includes a 10-band biquad filter and a digital volume control block. To support dynamic or adaptive filter and use case transitions, the biquad filters and volume controls provide banked profiles that can be updated/swapped without disruption to audio playback.

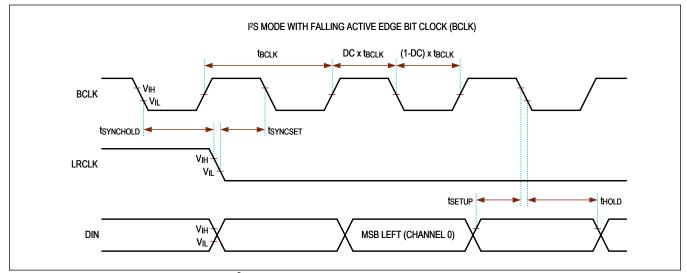

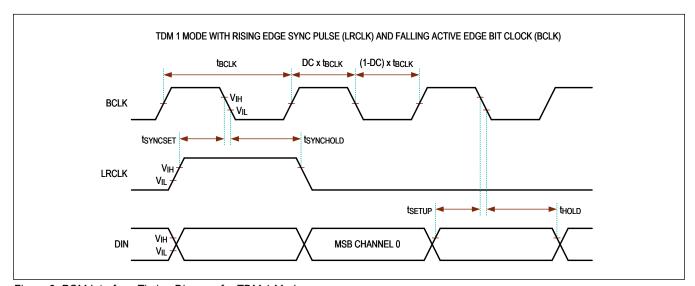

The flexible digital audio interface supports common PCM audio data formats such as I<sup>2</sup>S, left-justified, and TDM timing with 16-bit, 24-bit, or 32-bit data word and channel lengths. The PCM interface supports playback sample rates from 8kHz to 192kHz and record sample rates from 8kHz to 48kHz. The device requires external bit and frame clocks but eliminates the need for a high-speed external master clock.

The device is available in a small 6.7mm<sup>2</sup> 36-bump WLP package (0.4mm pitch) with a low 0.5mm height ideal for tight form factors. The device operates over the extended -40°C to +85°C temperature range.

#### **Applications**

- True Wireless Hearables and Headsets

- Stereo Bluetooth Headsets and Headphones

- Mono Bluetooth Earpieces

- PSAP Devices and Hearing Assist Devices

- VR/AR Headsets and Head-Mounted Devices

#### **Benefits and Features**

- Low-Latency Digital Filter Channels

- 96kHz/192kHz/384kHz Sample Rate Options

- Channel Support Applications Including Feed-Forward (FF) and Feedback (FB) ANC, Ambient/ Voice Enhancement and Transparency, and Playback Compensation

- Filters Allowing Smooth, Dynamic Transitions / Updates without Playback Disruption

- Mono Headphone Playback Channel

- · High-Efficiency Hybrid Class-AB/D Amplifier

- 114dB Playback Dynamic Range

- 2.55mW P<sub>Q</sub> (f<sub>S</sub> = 48kHz, No Noise Gate)

- 1.9mW P<sub>Q</sub> (f<sub>S</sub> = 48kHz, With Noise Gate)

- Three Microphone Record Channels

- · Analog or Digital Microphone Inputs

- 107dB Dynamic Range (AMIC Single-Ended)

- 113dB Dynamic Range (AMIC Differential))

- 5.3mW P<sub>Q</sub> (f<sub>S</sub> = 16kHz, 2 AMIC Record)

- 2.1mW P<sub>Q</sub> (f<sub>S</sub> = 16kHz, 2 DMIC Record)

- Playback with ANC Filter Profile (f<sub>S</sub> = 192kHz)

- 9.85mW PQ (AMIC FF+FB Profile)

- 6.7mW PO (AMIC FF Only Profile)

- 7mW PQ (DMIC FF+FB Profile)

- Full-Scale Playback Power at 1% THD+N:

- 31mW into 32Ω (1V<sub>RMS</sub> Full-Scale Mode)

- 15mW into 32Ω (Reduced Swing Mode)

- 61mW into 16Ω (1V<sub>RMS</sub> Full-Scale Mode)

- Flexible I<sup>2</sup>S/TDM Digital Audio Interface

- · Support for 16/24/32-Bit Audio Data

- Playback Sample Rates of 8kHz to 192kHz

- · No High-Speed Master Clock Required

- Audio CODEC Evaluation Platform Available

- Includes Maxim Reference Headset Design

- 6.7mm<sup>2</sup> 36-Bump WLP Package

- 0.4mm Pitch with a 0.5mm Height

Ordering Information appears at end of data sheet.

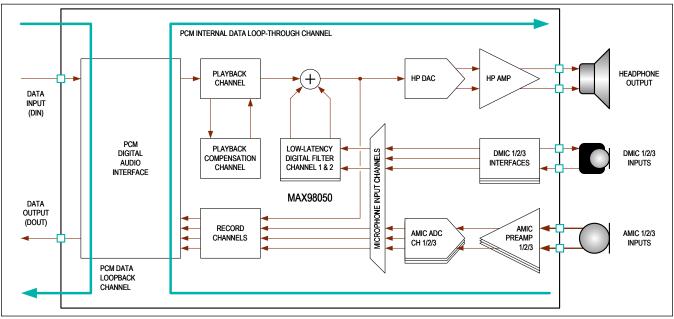

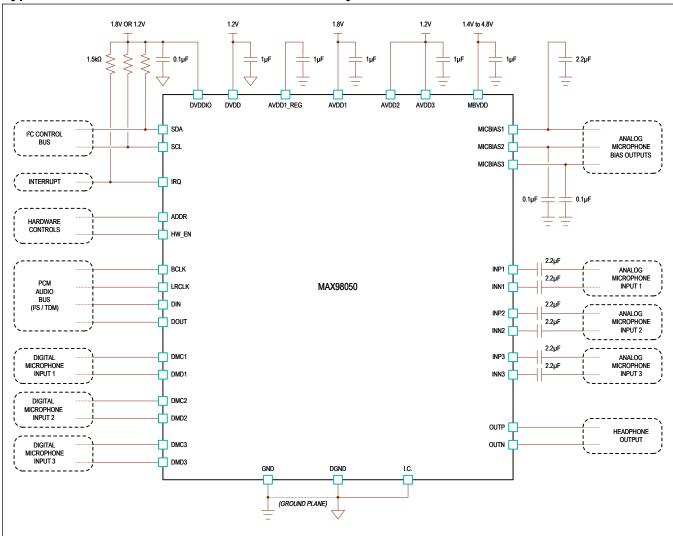

# **Simplified Block Diagram**

# **TABLE OF CONTENTS**

| General Description.                                                          |    |

|-------------------------------------------------------------------------------|----|

| Applications                                                                  | 1  |

| Benefits and Features                                                         | 1  |

| Simplified Block Diagram                                                      | 2  |

| Absolute Maximum Ratings                                                      |    |

| Package Information                                                           | 9  |

| 36-WLP                                                                        | 9  |

| Electrical Characteristics                                                    | 9  |

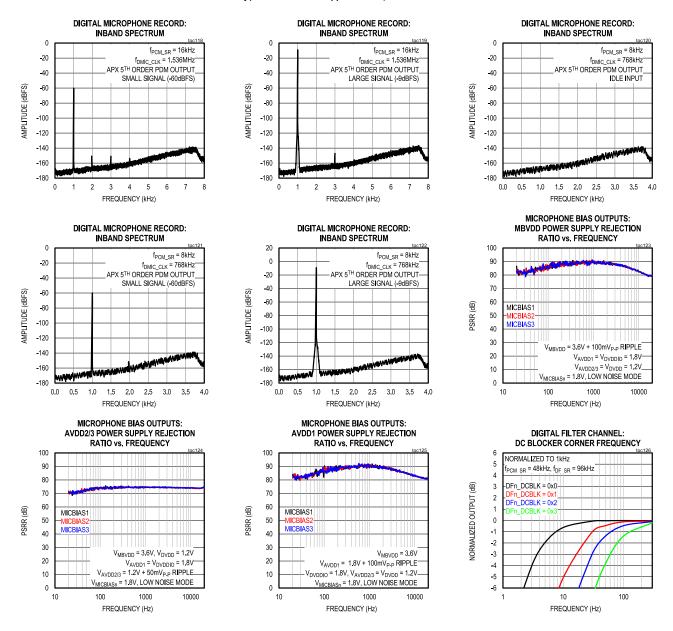

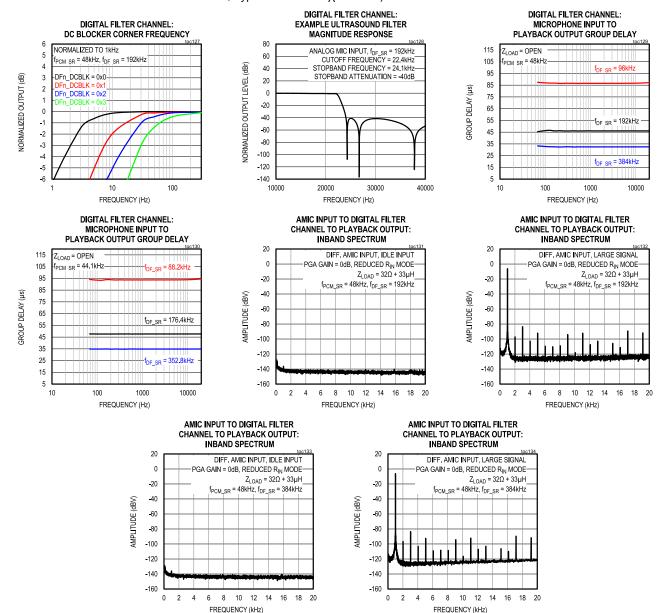

| Typical Operating Characteristics                                             |    |

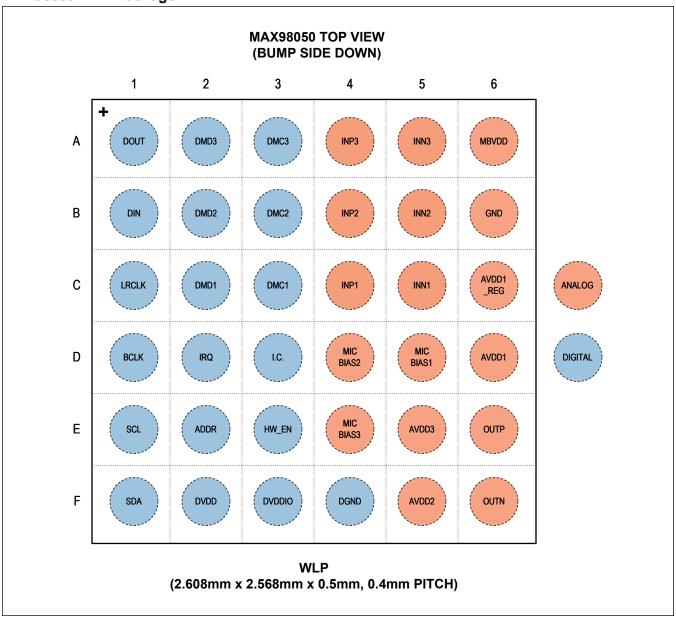

| Pin Configuration                                                             | 48 |

| MAX98050 WLP Package                                                          | 48 |

| Pin Description                                                               | 49 |

| Functional Diagrams                                                           | 51 |

| Detailed Block Diagram                                                        | 51 |

| Detailed Description                                                          | 52 |

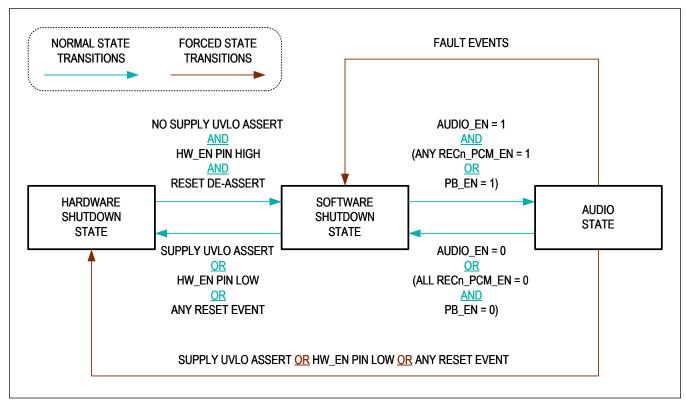

| Device State Control                                                          | 52 |

| Hardware Shutdown State                                                       | 52 |

| Software Shutdown State                                                       | 52 |

| Audio State                                                                   | 53 |

| Audio State Quiescent Power Consumption                                       | 53 |

| State Transition Diagram                                                      | 55 |

| Device Sequencing                                                             | 56 |

| Example Sequencing for Audio Playback and/or Record                           | 56 |

| Example Sequencing for Audio Playback with Low-Latency Digital Filters Active | 58 |

| PCM Digital Audio Interface                                                   | 60 |

| PCM Clock Configuration                                                       | 61 |

| PCM Data Format Configuration                                                 | 62 |

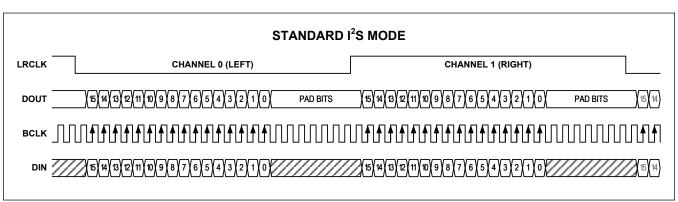

| I <sup>2</sup> S and Left-Justified Mode                                      | 62 |

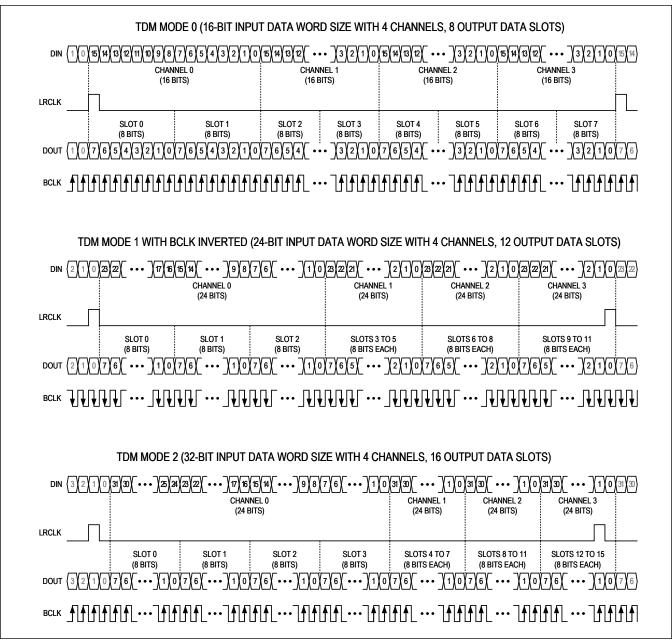

| TDM Modes                                                                     | 64 |

| PCM Data Channel Configuration                                                | 65 |

| PCM Data Input                                                                |    |

| PCM Data Output                                                               | 66 |

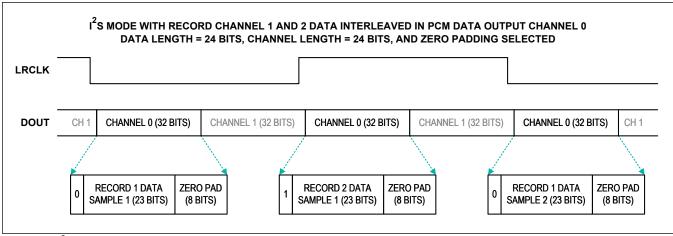

| PCM Data Output Channel Interleaving                                          | 67 |

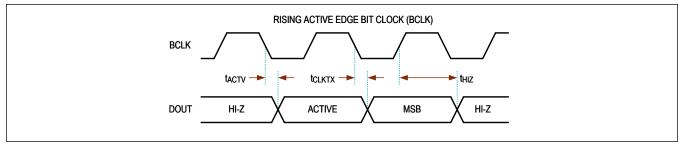

| PCM Data Output Drive Strength                                                | 67 |

| PCM Data Loopback and Loop-Through Modes                                      |    |

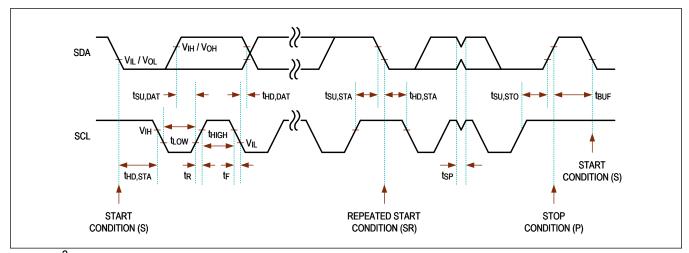

| I <sup>2</sup> C Slave Control Interface                                      |    |

| I <sup>2</sup> C Interface Address                                            | 69 |

| I <sup>2</sup> C Interface Bit Transfer Protocol                              | 69 |

# TABLE OF CONTENTS (CONTINUED)

| <u> </u>                                                                     |      |

|------------------------------------------------------------------------------|------|

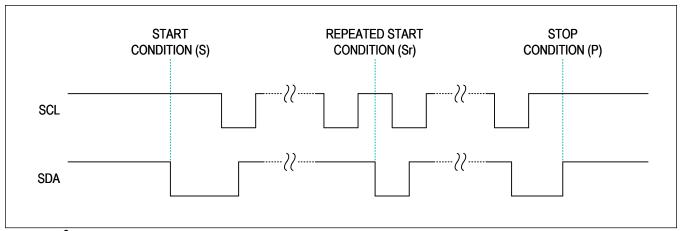

| I <sup>2</sup> C Interface START and STOP Conditions                         | . 69 |

| I <sup>2</sup> C Interface Early STOP Condition                              | . 70 |

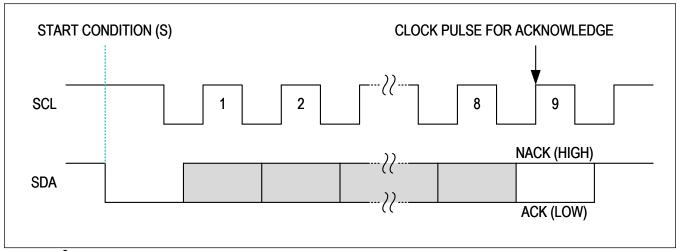

| I <sup>2</sup> C Interface Acknowledge Bit                                   | . 70 |

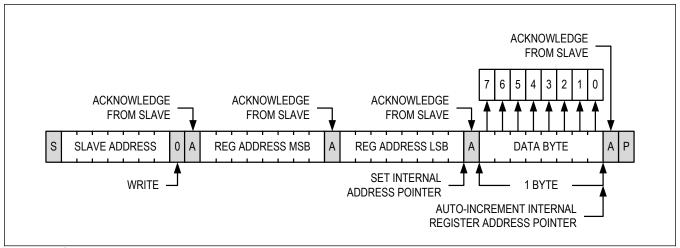

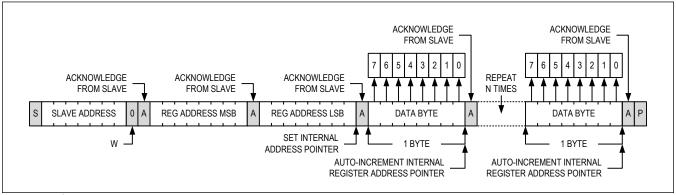

| I <sup>2</sup> C Interface Write Data Format                                 | . 71 |

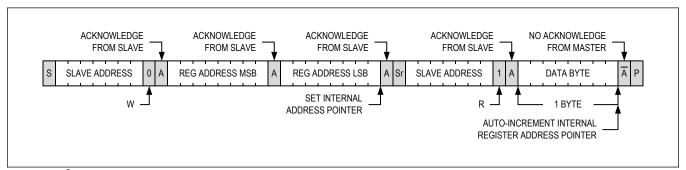

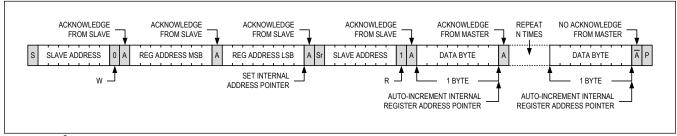

| I <sup>2</sup> C Interface Read Data Format                                  | . 72 |

| Interrupts                                                                   | . 73 |

| Interrupt Bit Field Composition                                              | . 73 |

| Interrupt IRQ Output Configuration                                           | . 73 |

| Interrupt Event Sources                                                      | . 74 |

| Microphone Input Channels                                                    | . 76 |

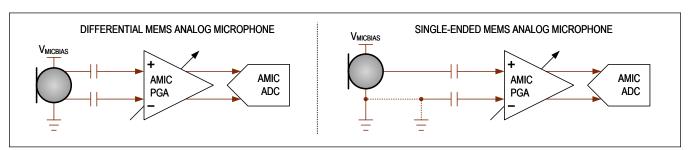

| Analog Microphone Inputs                                                     | . 77 |

| Analog Microphone Control Sequencing                                         | . 77 |

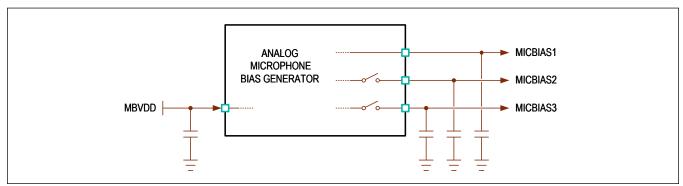

| Analog Microphone Bias Generator                                             | . 78 |

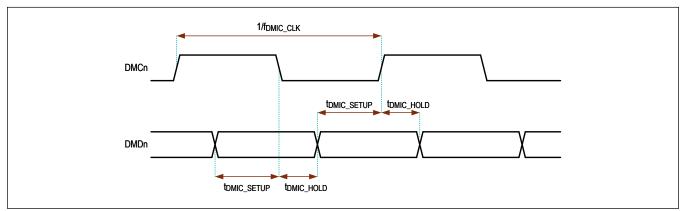

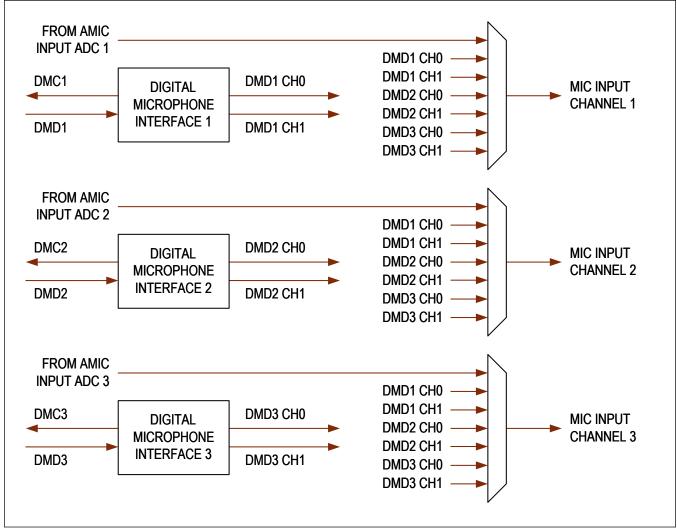

| Digital Microphone Interface                                                 | . 79 |

| Digital Microphone Control Sequencing                                        | . 80 |

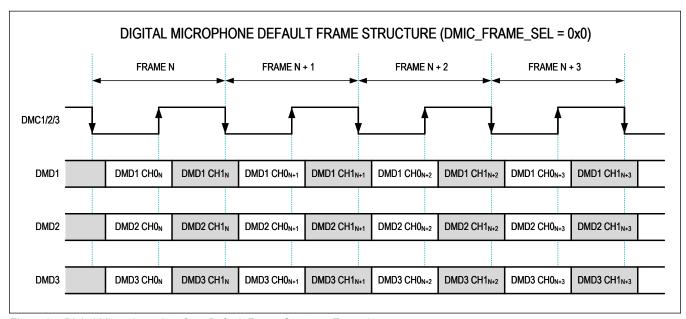

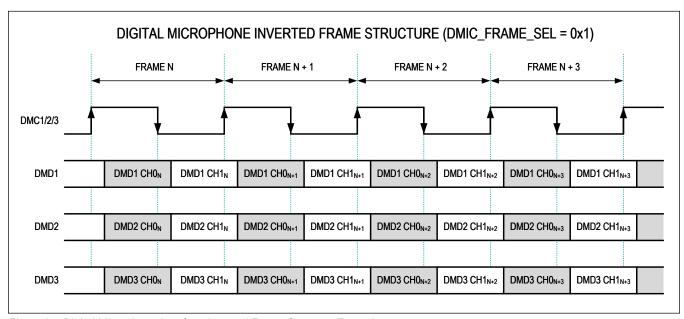

| Digital Microphone Interface Frame Configuration                             | . 80 |

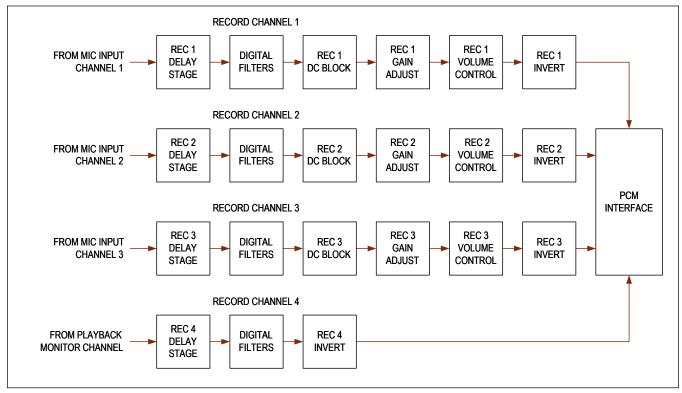

| Record Channel Configuration                                                 | . 82 |

| Record Channel Control Sequencing                                            | . 82 |

| Record Channel Data Inversion                                                | . 83 |

| Record Channel DC Blocking Filters                                           | . 83 |

| Record Channel Digital Volume Control                                        | . 83 |

| Record Channel Digital Gain Adjust                                           | . 83 |

| Record Channel Delay Stage                                                   | . 83 |

| Internal Digital Filter Channel Configuration.                               | . 84 |

| Low-Latency Digital Filter Channel 1 (DF1) and Channel 2 (DF2) Configuration |      |

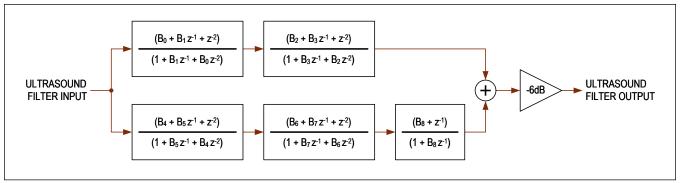

| DF1/DF2 Channel Ultrasound Polyphase Elliptical Filter                       | . 85 |

| DF1/DF2 Channel Ultrasound Filter Coefficient Registers                      | . 86 |

| DF1/DF2 Channel Ultrasound Filter Example Coefficients                       | . 87 |

| DF1/DF2 Channel 12-Band Biquad Filter                                        |      |

| DF1/DF2 Channel Biquad Filter Coefficient Registers                          | . 91 |

| DF1/DF2 Channel DC Blocking Filter                                           | . 93 |

| DF1/DF2 Channel Digital Gain Adjust                                          | . 94 |

| DF1/DF2 Channel Digital Volume Control                                       | . 94 |

| DF1/DF2 Channel Dynamic Range Compression (DRC) and Limiter Stage            | . 94 |

| DF1/DF2 Channel DRC and Limiter Stage RMS Level Calculations                 | . 95 |

| Playback Compensation (PBC) Digital Filter Channel                           | . 96 |

| PBC Channel 10-Band Biquad Filter                                            | . 97 |

| PBC Channel Biguad Filter Coefficient Registers                              | . 97 |

| TABLE OF CONTENTS (CONTINUED)                      |     |

|----------------------------------------------------|-----|

| PBC Channel Digital Gain Adjust                    | 101 |

| PBC Channel Digital Volume Control                 | 101 |

| Internal Digital Filter Channel Sequencing         | 102 |

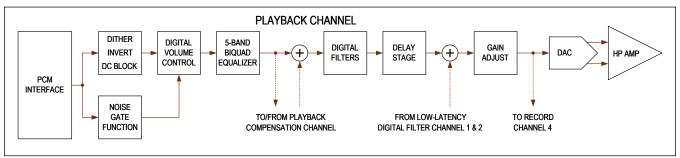

| Playback Channel Configuration                     | 103 |

| Playback Channel Dither                            | 103 |

| Playback Channel Data Inversion                    | 103 |

| Playback Channel DC Blocking Filter                | 103 |

| Playback Channel Digital Volume Control            | 103 |

| Playback Channel 5-Band Equalizer                  | 104 |

| Playback Channel Equalizer Coefficient Registers   | 104 |

| Playback Channel Delay Stage                       | 105 |

| Playback Channel Digital Gain Adjust               | 105 |

| Playback Channel Wide Band Mode                    | 106 |

| Playback Channel Digital Headroom Adjustment       | 106 |

| Playback Channel Noise Gate                        | 106 |

| Playback Amplifier                                 | 106 |

| Playback Amplifier Mode Configuration              | 107 |

| Playback Amplifier Class-D Mode Settings           | 107 |

| Playback Amplifier Overcurrent Limit Protection    | 107 |

| Clock and Data Monitors                            | 108 |

| Clock Monitor                                      | 108 |

| Clock Activity and Frequency Detection             | 108 |

| Clock Frame Error Detection                        | 109 |

| Input Data Monitor                                 | 110 |

| Data Stuck Error Detection                         | 110 |

| Data Magnitude Error Detection                     | 111 |

| Device and Revision Identification Number          | 111 |

| Device Register Map Description                    | 111 |

| Control Bit Write Access Restrictions              | 112 |

| Register Map                                       | 113 |

| User Control Registers                             | 113 |

| Register Details                                   | 119 |

| Гурісаl Application Circuits                       | 178 |

| Typical Use Case with PCM Mode Record and Playback | 178 |

| Ordering Information                               | 178 |

| Revision History                                   | 179 |

# LIST OF FIGURES

| Figure 1. Hardware Enable and Disable Timing Diagram                                        | 31  |

|---------------------------------------------------------------------------------------------|-----|

| Figure 2. PCM Interface Timing Diagram for I <sup>2</sup> S Mode                            | 31  |

| Figure 3. PCM Interface Timing Diagram for TDM 1 Mode                                       | 31  |

| Figure 4. PCM Interface Data Output Timing Diagram                                          | 32  |

| Figure 5. I <sup>2</sup> C Slave Control Interface Timing Diagram                           | 32  |

| Figure 6. Digital Microphone Interface Timing Diagram                                       | 32  |

| Figure 7. Device State Transition Diagram                                                   | 55  |

| Figure 8. PCM Input and Output Audio Data Channels                                          | 60  |

| Figure 9. I <sup>2</sup> S Timing Mode Example                                              | 62  |

| Figure 10. Left-Justified Mode Timing Examples                                              | 63  |

| Figure 11. TDM Mode Timing Examples                                                         | 65  |

| Figure 12. I <sup>2</sup> S Mode PCM Data Output Channel Interleaving Example               | 67  |

| Figure 13. PCM Data Loopback and Loop-Through Channels                                      | 68  |

| Figure 14. I <sup>2</sup> C Slave Interface START and STOP Condition Example                | 70  |

| Figure 15. I <sup>2</sup> C Slave Interface Acknowledge Bit Example                         | 70  |

| Figure 16. I <sup>2</sup> C Master Writing One Byte of Data to the Slave Device             | 71  |

| Figure 17. I <sup>2</sup> C Master Writing n-Bytes of Data to the Slave Device              | 71  |

| Figure 18. I <sup>2</sup> C Master Reading One Byte of Data from the Slave Device           | 72  |

| Figure 19. I <sup>2</sup> C Master Reading n-Bytes of Data from the Slave Device            | 72  |

| Figure 20. Microphone Input Channel Detailed Block Diagram                                  | 76  |

| Figure 21. Differential and Single-Ended Analog Microphone Connections                      | 77  |

| Figure 22. Analog Microphone Bias Generator Diagram                                         | 78  |

| Figure 23. Digital Microphone Input Channel Detailed Block Diagram                          | 80  |

| Figure 24. Digital Microphone Interface Default Frame Structure Example                     | 81  |

| Figure 25. Digital Microphone Interface Inverted Frame Structure Example                    | 81  |

| Figure 26. Record Channel Detailed Block Diagram                                            | 82  |

| Figure 27. Internal Playback Compensation and Low-Latency Digital Filter Channels           | 84  |

| Figure 28. Low-Latency Digital Filter Channel 1 and 2 Detailed Block Diagram                | 85  |

| Figure 29. Low-Latency Digital Filter Channel Ultrasound Filter Structure                   | 86  |

| Figure 30. Playback Compensation Channel Detailed Block Diagram                             | 96  |

| Figure 31. Playback Channel Detailed Block Diagram                                          | 103 |

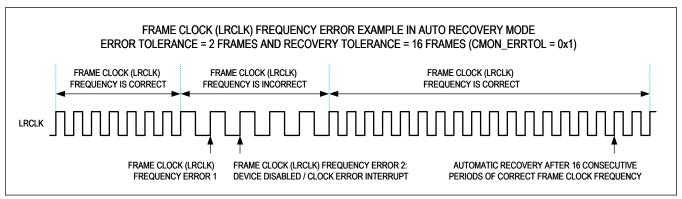

| Figure 32. Clock Monitor Frame Clock (LRCLK) Frequency Error Example with CMON_ERRTOL = 0x1 | 109 |

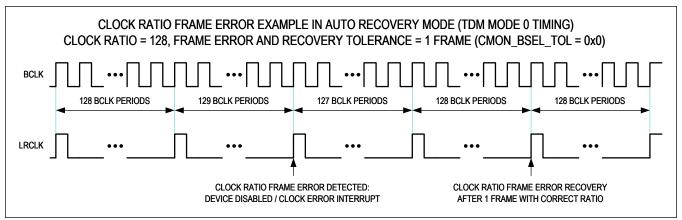

| Figure 33. Clock Monitor Clock Ratio Frame Error Example with TDM Mode 0 Timing             | 110 |

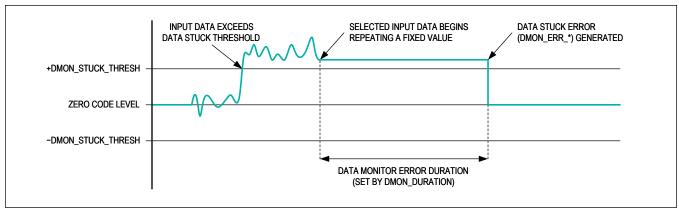

| Figure 34. Data Monitor Error Generation Due to Input Data Stuck Error Detection            | 110 |

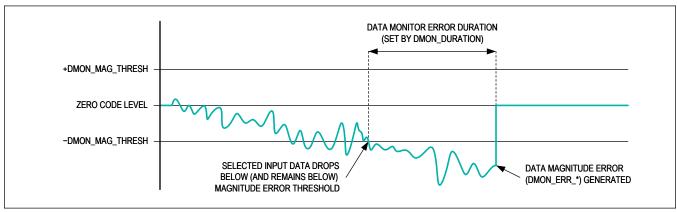

| Figure 35. Data Monitor Error Generation Due to Input Data Magnitude Error Detection        | 111 |

# **LIST OF TABLES**

| Table 1. PCM Interface Playback Only Quiescent Power                                                       | . 53 |

|------------------------------------------------------------------------------------------------------------|------|

| Table 2. PCM Interface Record Only Quiescent Power                                                         | . 54 |

| Table 3. PCM Interface Record and Playback Quiescent Power                                                 | . 54 |

| Table 4. PCM Interface Playback with Digital Filter Channels Quiescent Power                               | . 54 |

| Table 5. Recommended Power-Up Sequence: Audio Record and/or Playback                                       | . 56 |

| Table 6. Recommended Power-Down Sequence: Audio Record and/or Playback                                     | . 57 |

| Table 7. Recommended Typical Power-Up Sequence: Audio Playback with Low-Latency Digital Filter Channels    | . 58 |

| Table 8. Recommended Typical Power-Down Sequence: Audio Playback with Low-Latency Digital Filter Channels. | . 59 |

| Table 9. Supported Playback to Record Sample Rate Ratios                                                   | . 61 |

| Table 10. Supported I <sup>2</sup> S and Left-Justified Mode Configurations                                | . 62 |

| Table 11. Supported TDM Mode Configurations                                                                | . 64 |

| Table 12. PCM Record Output Data Sources                                                                   | . 66 |

| Table 13. Example Record Output Data Slot Assignments                                                      | . 66 |

| Table 14. Available I <sup>2</sup> C Slave Addresses                                                       |      |

| Table 15. Device Interrupt Event Sources 1                                                                 |      |

| Table 16. Device Interrupt Event Sources 2                                                                 | . 75 |

| Table 17. Microphone Input Channel Connections                                                             | . 76 |

| Table 18. Supported Digital Microphone Interface Sample Rates                                              | . 79 |

| Table 19. Digital Microphone to Channel Sample Rate Combinations                                           | . 79 |

| Table 20. Low-Latency Digital FIlter Channel Dynamic Bank Select Restrictions                              | . 85 |

| Table 21. Ultrasound Filter Register Address Ranges                                                        |      |

| Table 22. Digital Filter Channel 1 Ultrasound Filter Coefficient Register Addresses                        |      |

| Table 23. Digital Filter Channel 2 Ultrasound Filter Coefficient Register Addresses                        | . 87 |

| Table 24. Example Ultrasound Filters for f <sub>S</sub> = 384kHz with Low Cutoff Frequencies               |      |

| Table 25. Example Ultrasound Filters for f <sub>S</sub> = 384kHz with High Cutoff Frequencies              | . 88 |

| Table 26. Example Ultrasound Filters for f <sub>S</sub> = 192kHz with Low Cutoff Frequencies               | . 88 |

| Table 27. Example Ultrasound Filters for $f_S$ = 192kHz with High Cutoff Frequencies                       |      |

| Table 28. Example Ultrasound Filters for f <sub>S</sub> = 96kHz with Low Cutoff Frequencies                | . 89 |

| Table 29. Example Ultrasound Filters for f <sub>S</sub> = 96kHz with High Cutoff Frequencies               | . 90 |

| Table 30. Digital Filter Channel Biquad Filter Register Address Ranges                                     | . 91 |

| Table 31. Digital Filter Channel and Bank Biquad Filter Coefficient Register Addresses                     | . 92 |

| Table 32. Playback Compensation Channel Dynamic Bank Select Restrictions                                   |      |

| Table 33. Playback Compensation Channel Biquad Filter Register Addresses                                   | . 97 |

| Table 34. Playback Compensation Channel Biquad Filter Bank A Coefficient Register Addresses                | . 98 |

| Table 35. Playback Compensation Channel Biquad Filter Bank B Coefficient Register Addresses                |      |

| Table 36. Playback Channel Equalizer Coefficient Register Addresses                                        |      |

| Table 37. Noise Gate Threshold LSB Location                                                                |      |

| Table 38. Playback Amplifier Output Operating Mode and Supply Configuration                                | 107  |

# MAX98050

# Low-Power, High-Performance Audio Codec

| LIST OF TABLES (CONTINUED)                                |       |

|-----------------------------------------------------------|-------|

| Table 39. Recommended Clock Monitor Modes                 | . 108 |

| Table 40. Control Register Map Bit Field Types            | . 111 |

| Table 41. Control Bit Types and Write Access Restrictions | . 112 |

#### **Absolute Maximum Ratings**

| DGND to GND       | 0.1V to +0.1V                     | SCL, SDA, ADDR to DGND0.3V to +2.2V                                      |

|-------------------|-----------------------------------|--------------------------------------------------------------------------|

| MBVDD to GND      | 0.3V to +5.5V                     | All Other Pins0.3V to V <sub>DVDDIO</sub> + 0.3V                         |

| MICBIAS to GND    | 0.3V to V <sub>MBVDD</sub> + 0.3V | Short-Circuit of OUTP/OUTN and AVDDnContinuous                           |

| AVDD1 to GND      | 0.3V to +2.2V                     | Short-Circuit of OUTP/OUTN and AVDD1_REGContinuous                       |

| AVDD2 to GND      | 0.3V to +1.85V                    | Short-Circuit of OUTP/OUTN and GND/DGNDContinuous                        |

| AVDD3 to DGND     | 0.3V to +1.85V                    | Short-Circuit of OUTP and OUTNContinuous                                 |

| AVDD1_REG to GND  | 0.3V to +1.85V                    | Continuous Power Dissipation (Multilayer Board) (T <sub>A</sub> = +70°C, |

| DVDDIO to DGND    | 0.3V to +2.2V                     | derate 21.87mW/°C above +70°C)1.75W                                      |

| DVDD to DGND      | 0.3V to +1.85V                    | Junction Temperature+150°C                                               |

| INPn, INNn to GND |                                   | Operating Temperature Range40°C to +85°C                                 |

| OUTP, OUTN to GND | 0.3V to V <sub>AVDD1</sub> + 0.3V | Storage Temperature Range65°C to +150°C                                  |

| MICBIASn to GND   | 0.3V to V <sub>MBVDD</sub> + 0.3V | Soldering Temperature (reflow)+260°C                                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **36-WLP**

| Package Code                           | N362F2+1                              |  |  |  |  |

|----------------------------------------|---------------------------------------|--|--|--|--|

| Outline Number                         | <u>21-100518</u>                      |  |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891        |  |  |  |  |

| Thermal Resistance, Four-Layer Board:  | Thermal Resistance, Four-Layer Board: |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 45.72°C/W                             |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | N/A                                   |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, \ V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, \ V_{MBVDD} = 3.6V, \ GND = DGND = 0V, \ C_{MBVDD} = C_{MICBIASn} = 2.2\mu\text{F}, \ C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1\mu\text{F}, \ C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1\mu\text{F}, \ High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, $Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC Measurement Bandwidth = 20Hz to 20kHz, $T_A = -40^{\circ}$C to +85^{\circ}$C unless otherwise noted, Typical values at $T_A = +25^{\circ}$C, Note 1)$

| PARAMETER                               | SYMBOL              | CONDITIONS                  | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------|---------------------|-----------------------------|------|-----|------|-------|

| SYSTEM / POWER SUPI                     | PLIES               |                             | ·    |     |      |       |

| Power Supply Voltage<br>Range           | V <sub>MBVDD</sub>  |                             | 1.3  | 3.6 | 4.8  |       |

|                                         | V <sub>AVDD1</sub>  |                             | 1.71 | 1.8 | 1.95 |       |

|                                         | V <sub>AVDD2</sub>  |                             | 1.1  | 1.2 | 1.3  | V     |

|                                         | V <sub>AVDD3</sub>  |                             | 1.1  | 1.2 | 1.3  |       |

|                                         | .,,                 | 1.8V digital interface mode | 1.65 | 1.8 | 1.95 |       |

|                                         | V <sub>DVDDIO</sub> | 1.2V digital interface mode | 1.1  | 1.2 | 1.3  | 1     |

|                                         | V <sub>DVDD</sub>   |                             | 1.1  | 1.2 | 1.3  | 1     |

| AVDD1 Undervoltage<br>Lockout Threshold |                     | V <sub>AVDD1</sub> falling  | 1.24 |     | 1.46 | V     |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, V_{MBVDD} = 3.6V, GND = DGND = 0V, C_{MBVDD} = C_{MICBIASn} = 2.2μF, C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1μF, C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1μF, High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC Measurement Bandwidth = 20Hz to 20kHz, <math>T_{A} = -40$ °C to +85°C unless otherwise noted, Typical values at  $T_{A} = +25$ °C, Note 1)

| PARAMETER                                | SYMBOL                | CONDITIONS                                                                                                                                        | MIN  | TYP   | MAX  | UNITS |

|------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| AVDD2 Undervoltage<br>Lockout Threshold  |                       | V <sub>AVDD2</sub> falling                                                                                                                        | 0.85 |       | 1.01 | V     |

| AVDD3 Undervoltage<br>Lockout Threshold  |                       | V <sub>AVDD3</sub> falling                                                                                                                        | 0.85 |       | 1.01 | V     |

| DVDD Undervoltage<br>Lockout Threshold   |                       | V <sub>DVDD</sub> falling                                                                                                                         | 0.85 |       | 1.01 | V     |

| DVDDIO Undervoltage<br>Lockout Threshold |                       | V <sub>DVDDIO</sub> falling                                                                                                                       | 0.85 |       | 1.01 | V     |

| AVDD1 UVLO<br>Hysteresis                 |                       | (Note 2)                                                                                                                                          | 90   |       |      | mV    |

| AVDD2 UVLO<br>Hysteresis                 |                       | (Note 2)                                                                                                                                          | 24   |       |      | mV    |

| AVDD3 UVLO<br>Hysteresis                 |                       | (Note 2)                                                                                                                                          | 24   |       |      | mV    |

| DVDD UVLO Hysteresis                     |                       | (Note 2)                                                                                                                                          | 24   |       |      | mV    |

| DVDDIO UVLO<br>Hysteresis                |                       | (Note 2)                                                                                                                                          | 24   |       |      | mV    |

| SYSTEM / QUIESCENT F                     | OWER CONSU            | MPTION / AUDIO PLAYBACK                                                                                                                           |      |       |      |       |

|                                          | 1                     | High-performance mode, playback at 48kHz, audio playback silent (dither disabled), $P_{OUT}$ = 0mW, $Z_{LOAD}$ = 32 $\Omega$ + 33 $\mu$ H         |      | 1.6   | 2.2  |       |

| Quiescent Supply                         | IQ_DVDD               | High-performance mode, playback at 48kHz, audio playback silent, clock and data monitor enable, $P_{OUT} = 0$ mW, $Z_{LOAD} = 32\Omega + 33\mu$ H |      | 1.7   |      |       |

| Current                                  | I <sub>Q_DVDDIO</sub> |                                                                                                                                                   |      | 0.01  |      | mA    |

|                                          | I <sub>Q_AVDD1</sub>  | High-performance mode, playback at 48kHz, audio playback silent, P <sub>OUT</sub> =                                                               |      | 0.03  | 0.06 |       |

|                                          | I <sub>Q_AVDD2</sub>  | $_{\perp}$ 0mW, Z <sub>LOAD</sub> = 32Ω + 33μH                                                                                                    |      | 0.45  | 0.75 |       |

|                                          | I <sub>Q_AVDD3</sub>  |                                                                                                                                                   |      | 0.012 | 0.04 |       |

|                                          | I <sub>Q_AVDD2</sub>  | Low-power mode, playback at 48kHz, audio playback silent, $P_{OUT}$ = 0mW, $Z_{LOAD}$ = $32\Omega$ + $33\mu$ H                                    |      | 0.37  |      |       |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, \ V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, \ V_{MBVDD} = 3.6V, \ GND = DGND = 0V, \ C_{MBVDD} = C_{MICBIASn} = 2.2 \mu F, \ C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1 \mu F, \ C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1 \mu F, \ High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, \ f_{LRCLK} = 48kHz, \ f_{S_DF} = 192kHz, \ f_{BCLK} = 3.072MHz, \ f_{DMIC_CLK} = 3.072MHz, \ AC \ Measurement Bandwidth = 20Hz to 20kHz, \ T_A = -40 °C to +85 °C unless otherwise noted, Typical values at T_A = +25 °C, Note 1)$

| PARAMETER                   | SYMBOL                | CONDITIONS                                                                                                                                                                                                                                                                                                                | MIN      | TYP         | MAX     | UNITS |

|-----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|---------|-------|

| SYSTEM / QUIESCENT          | POWER CONSU           | MPTION / AUDIO PLAYBACK WITH LOW-L                                                                                                                                                                                                                                                                                        | ATENCY [ | DIGITAL FIL | TER CHA | NNELS |

|                             | I <sub>Q_DVDD</sub>   | High-performance playback and record,                                                                                                                                                                                                                                                                                     |          | 5.16        | 7.6     |       |

|                             | I <sub>Q_DVDDIO</sub> | playback at 48kHz, stereo AMIC to low-<br>latency digital filter channels at 192kHz,                                                                                                                                                                                                                                      |          | 0.013       |         |       |

|                             | I <sub>Q_AVDD1</sub>  | hybrid ANC tuning profile with typical                                                                                                                                                                                                                                                                                    |          | 2.18        | 3.6     | ]     |

|                             | I <sub>Q_AVDD2</sub>  | number of biquad filter bands active (8                                                                                                                                                                                                                                                                                   |          | 0.45        | 0.75    |       |

| Quiescent Supply            | I <sub>Q_AVDD3</sub>  | bands in DF1/DF2 and 6 bands in PBC), audio playback silent (dither disabled), AMIC record silent, $P_{OUT}$ = 0mW, $Z_{LOAD}$ = $32\Omega + 33\mu H$                                                                                                                                                                     |          | 0.012       | 0.04    | - mA  |

| Current                     | I <sub>Q_AVDD1</sub>  | Low-power playback and record,                                                                                                                                                                                                                                                                                            |          | 1.7         |         |       |

|                             | IQ_AVDD2              | playback at 48kHz, stereo AMIC to low-latency digital filter channels at 192kHz, hybrid ANC tuning profile with typical number of biquad filter bands active (8 bands in DF1/DF2 and 6 bands in PBC), audio playback silent (dither disabled), AMIC record silent, P <sub>OUT</sub> = 0mW, Z <sub>LOAD</sub> = 32Ω + 33μH |          | 0.37        |         |       |

| SYSTEM / QUIESCENT          | POWER CONSU           | MPTION / AUDIO PLAYBACK WITH STERE                                                                                                                                                                                                                                                                                        | O RECOR  | D           |         |       |

|                             | I <sub>Q_DVDD</sub>   | High performance record and playback                                                                                                                                                                                                                                                                                      |          | 2.85        | 4       |       |

|                             | I <sub>Q_DVDDIO</sub> | High-performance record and playback modes, playback and stereo AMIC record                                                                                                                                                                                                                                               |          | 0.013       |         |       |

|                             | I <sub>Q_AVDD1</sub>  | at 48kHz, audio playback silent (dither                                                                                                                                                                                                                                                                                   |          | 2.18        | 3.6     |       |

| Outroped Committee          | I <sub>Q_AVDD2</sub>  | disabled), record silent, $P_{OUT}$ = 0mW, $Z_{LOAD}$ = 32 $\Omega$ + 33 $\mu$ H                                                                                                                                                                                                                                          |          | 0.45        | 0.75    |       |

| Quiescent Supply<br>Current | I <sub>Q_AVDD3</sub>  | - 2LOAD - 32Ω + 33μH                                                                                                                                                                                                                                                                                                      |          | 0.012       | 0.04    | mA    |

|                             | I <sub>Q_AVDD1</sub>  | Low-power record and playback modes, playback and stereo AMIC record at 48kHz, audio playback silent (dither disabled), record silent, P <sub>OUT</sub> = 0mW, Z <sub>LOAD</sub> = 32Ω + 33μH                                                                                                                             |          | 1.7         |         |       |

|                             | I <sub>Q_AVDD2</sub>  |                                                                                                                                                                                                                                                                                                                           |          | 0.37        |         |       |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, V_{MBVDD} = 3.6V, GND = DGND = 0V, C_{MBVDD} = C_{MICBIASn} = 2.2μF, C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1μF, C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1μF, High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC Measurement Bandwidth = 20Hz to 20kHz, <math>T_{A} = -40$ °C to +85°C unless otherwise noted, Typical values at  $T_{A} = +25$ °C, Note 1)

| PARAMETER                           | SYMBOL                 | CONDITIONS                                                                                                       | MIN TYP | MAX | UNITS        |

|-------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------|---------|-----|--------------|

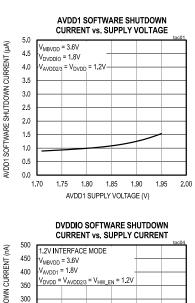

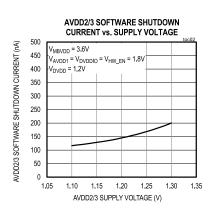

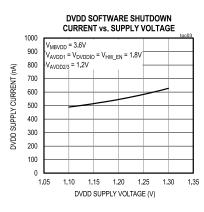

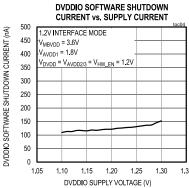

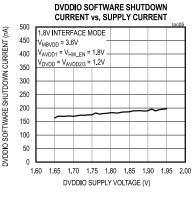

| SYSTEM / SOFTWARE                   | SHUTDOWN PO            | WER CONSUMPTION                                                                                                  |         |     |              |

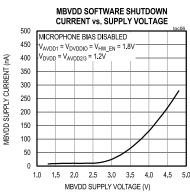

|                                     | I <sub>MBVDD_SW</sub>  | V <sub>MBVDD</sub> = 3.6V, software shutdown state, digital interfaces not driven, T <sub>A</sub> = +25°C        | 0.08    | 3   |              |

|                                     | I <sub>DVDDIO_SW</sub> | V <sub>DVDDIO</sub> = 1.8V, software shutdown state, digital interfaces not driven, T <sub>A</sub> = +25°C       | 0.18    | 3   |              |

| Software Shutdown<br>Supply Current | I <sub>DVDD_</sub> sw  | V <sub>DVDD</sub> = 1.2V, software shutdown state, digital interfaces not driven, T <sub>A</sub> = +25°C         | 0.55    | 2   | μΑ           |

|                                     | I <sub>AVDD1_SW</sub>  | V <sub>AVDD1</sub> = 1.8V, software shutdown state, digital interfaces not driven, T <sub>A</sub> = +25°C        | 1       | 3   |              |

|                                     | I <sub>AVDD2_SW</sub>  | V <sub>AVDD2</sub> = 1.2V, software shutdown state, digital interfaces not driven, T <sub>A</sub> = +25°C        | 0.05    | 2   |              |

|                                     | I <sub>AVDD3_SW</sub>  | V <sub>AVDD3</sub> = 1.2V, software shutdown state, digital interfaces not driven, T <sub>A</sub> = +25°C        | 0.09    | 2   |              |

| SYSTEM / HARDWARE                   | SHUTDOWN PO            | WER CONSUMPTION                                                                                                  |         |     |              |

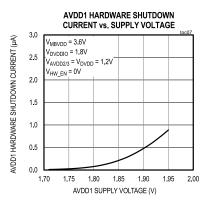

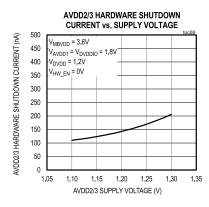

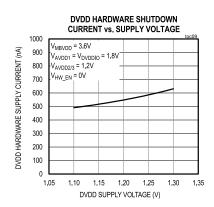

|                                     | I <sub>MBVDD_</sub> HW | V <sub>MBVDD</sub> = 3.6V, hardware shutdown state, digital audio interfaces not driven, T <sub>A</sub> = +25°C  | 0.01    | 3   |              |

|                                     | IDVDDIO_HW             | V <sub>DVDDIO</sub> = 1.8V, hardware shutdown state, digital audio interfaces not driven, T <sub>A</sub> = +25°C | 0.01    | 3   |              |

| Hardware Shutdown                   | I <sub>DVDD_HW</sub>   | V <sub>DVDD</sub> = 1.2V, hardware shutdown state, digital audio interfaces not driven, T <sub>A</sub> = +25°C   | 0.55    | 2   |              |

| Supply Current                      | I <sub>AVDD1_HW</sub>  | V <sub>AVDD1</sub> = 1.8V, hardware shutdown state, digital audio interfaces not driven, T <sub>A</sub> = +25°C  | 0.1     | 3   | - μ <b>A</b> |

|                                     | I <sub>AVDD2_HW</sub>  | V <sub>AVDD2</sub> = 1.2V, hardware shutdown state, digital audio interfaces not driven, T <sub>A</sub> = +25°C  | 0.05    | 2   | -            |

|                                     | I <sub>AVDD3</sub> _HW | V <sub>AVDD3</sub> = 1.2V, hardware shutdown state, digital audio interfaces not driven, T <sub>A</sub> = +25°C  | 0.09    | 2   |              |

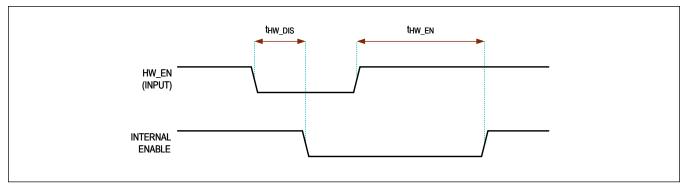

| ENABLE / DISABLE TIN                | IING                   |                                                                                                                  |         |     |              |

| Hardware Enable Time                | thw_en                 | Transition time from hardware shutdown to software shutdown (Initialization Done interrupt) (Note 3)             |         | 2.5 | ms           |

| Hardware Disable<br>Assert Time     | t <sub>HW_DIS</sub>    | Minimum time HW_EN must be asserted low to ensure the device transitions to hardware shutdown (Note 3)           | 1       |     | μs           |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, V_{MBVDD} = 3.6V, GND = DGND = 0V, C_{MBVDD} = C_{MICBIASn} = 2.2μF, C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1μF, C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1μF, High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC Measurement Bandwidth = 20Hz to 20kHz, <math>T_{A} = -40$ °C to +85°C unless otherwise noted, Typical values at  $T_{A} = +25$ °C, Note 1)

| PARAMETER                                                  | SYMBOL           | COND                                                                                    | OITIONS                                                                                                                                                                                               | MIN | TYP  | MAX | UNITS |

|------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

|                                                            |                  | Transition time from software                                                           | AMIC_CT_SEL = 0x0                                                                                                                                                                                     |     | 3.7  | 4   |       |

|                                                            |                  | shutdown to audio record and playback with                                              | AMIC_CT_SEL = 0x1                                                                                                                                                                                     |     | 5.2  | 6   |       |

| Audio Turn-On Time                                         | t <sub>ON</sub>  | digital filter channels active                                                          | AMIC_CT_SEL = 0x2                                                                                                                                                                                     |     | 9.2  | 10  | ms    |

|                                                            |                  | (Record and<br>Playback Power-<br>Up Done                                               | AMIC_CT_SEL = 0x3                                                                                                                                                                                     |     | 17.2 | 18  |       |

| Audio Turn-On Time with Ramping                            | ton              | to audio playback wi<br>channels disabled o<br>Power-Up Done inte<br>volume ramping ena | Transition time from software shutdown to audio playback with digital filter channels disabled or muted (Playback Power-Up Done interrupt), playback volume ramping enabled at 4ms, AMIC_CT_SEL = 0x1 |     | 9.2  | 10  | ms    |

| Audio Turn-On Time for<br>Dynamic Record<br>Channel Enable | ton_rec          |                                                                                         | idio state, time from<br>RECn_PCM_EN high<br>active with valid data                                                                                                                                   |     | 1.3  | 2   | ms    |

| Audio Turn-Off Time                                        | t <sub>OFF</sub> | playback with digital into software shutdo                                              | Transition time from audio record and/or playback with digital filter channels active into software shutdown (Power Down Done interrupt), volume ramping disabled                                     |     | 0.01 | 0.1 | ms    |

| Audio Turn-Off Time with Ramping                           | t <sub>OFF</sub> |                                                                                         | interrupt), playback                                                                                                                                                                                  |     | 4.4  | 4.5 | ms    |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, \ V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, \ V_{MBVDD} = 3.6V, \ GND = DGND = 0V, \ C_{MBVDD} = C_{MICBIASn} = 2.2 \mu F, \ C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1 \mu F, \ C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1 \mu F, \ High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, \ f_{LRCLK} = 48kHz, \ f_{S\_DF} = 192kHz, \ f_{BCLK} = 3.072MHz, \ f_{DMIC\_CLK} = 3.072MHz, \ AC \ Measurement Bandwidth = 20Hz to 20kHz, \ T_A = -40 °C to +85 °C unless otherwise noted, Typical values at T_A = +25 °C, Note 1)$

| PARAMETER                      | SYMBOL             | CONDITIONS                                                                                                                       | MIN TYP      | MAX | UNITS            |

|--------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|-----|------------------|

| ANALOG MICROPHONE              | INPUT TO ADO       | RECORD                                                                                                                           |              |     |                  |

|                                |                    | PGA gain = +6dB, single-ended or<br>differential input, AMICn_PGA_RIN = 1,<br>DRE enabled (Note 5)                               | 104          |     |                  |

|                                |                    | PGA gain = +3dB, single-ended or<br>differential input, AMICn_PGA_RIN = 0,<br>DRE enabled (Note 5)                               | 104          |     |                  |

| Dynamic Range DR               | DR                 | PGA gain = +3dB, single-ended or<br>differential input, AMICn_PGA_RIN = 1,<br>DRE enabled (Note 5)                               | 107          |     | dB               |

|                                |                    | PGA gain = 0dB, differential input,<br>AMICn_PGA_RIN = 1, DRE enabled<br>(Note 5)                                                | 110          |     |                  |

|                                |                    | PGA gain = -3dB, differential input,<br>AMICn_PGA_RIN = 1, DRE enabled<br>(Note 5)                                               | 113          |     |                  |

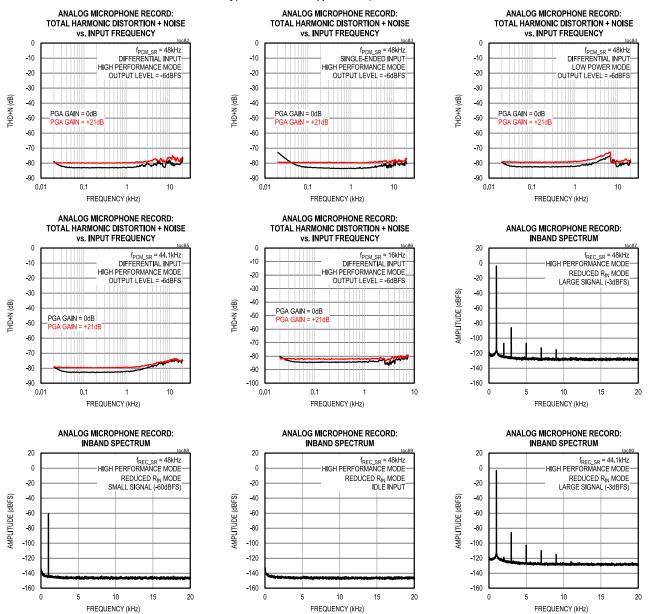

|                                |                    | PGA gain = +6dB, single-ended or<br>differential input, f <sub>IN</sub> = 1kHz, -6dBFS<br>digital output, high-performance mode  | -82          | -75 |                  |

| Total Harmonic                 | THD+N              | PGA gain = +6dB, single-ended or<br>differential input, f <sub>IN</sub> = 1kHz, -6dBFS<br>digital output, low-power mode         | -80          |     | dB               |

| Distortion + Noise             | THOTN              | PGA gain = +0dB, differential input, f <sub>IN</sub> = 1kHz, -6dBFS digital output, high performance mode (Note 2)               | -82          | -75 | - ub             |

|                                |                    | PGA gain = +21dB, single-ended or<br>differential input, f <sub>IN</sub> = 1kHz, -6dBFS<br>digital output, high performance mode | -78          |     |                  |

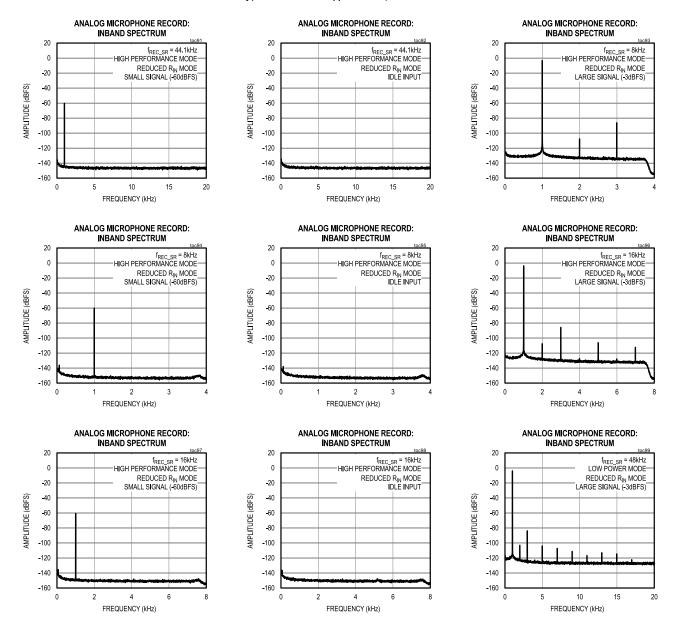

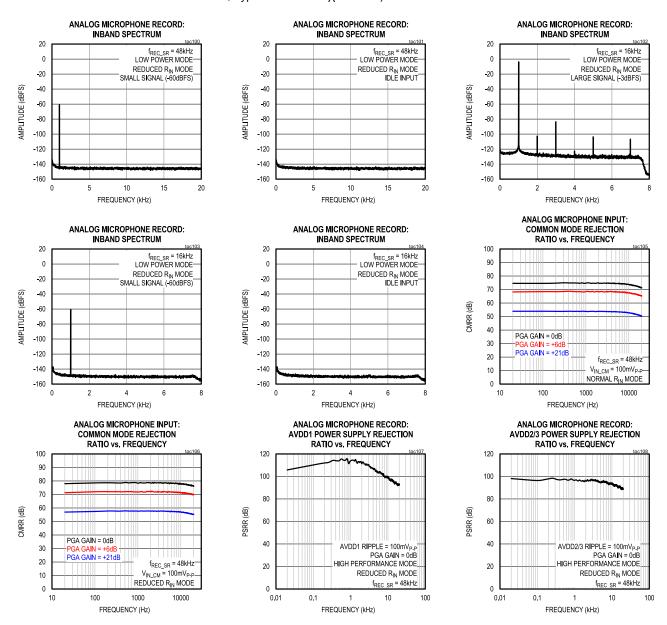

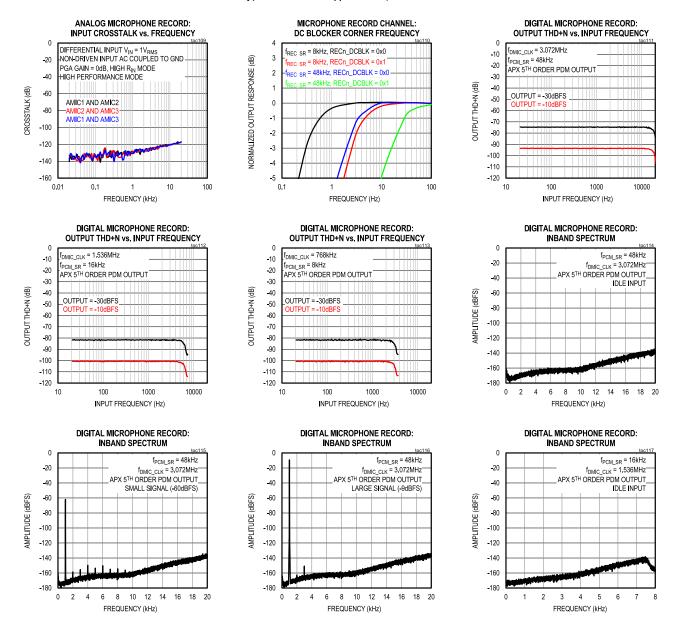

| Crosstalk                      |                    | Between any pair of record channels, f <sub>IN</sub> = 1kHz                                                                      | -120         |     | dB               |

| Common Mode<br>Rejection Ratio | CMRR               | PGA Gain = 0dB, $V_{IN\_CM}$ = 100m $V_{PP}$ , $f_{IN\_CM}$ = 217Hz                                                              | 75           |     | dB               |

| ANALOG MICROPHONE              | INPUT TO ADO       | RECORD / PROGRAMMABLE GAIN AMPL                                                                                                  | LIFIER (PGA) |     |                  |

|                                |                    | PGA gain = +6dB, single-ended or differential input, THD+N ≤ -40dB                                                               | 0.5          |     |                  |

| Full-Scale Input Voltage       | ge V <sub>FS</sub> | PGA gain = +3dB, single-ended or differential input, THD+N ≤ -40dB                                                               | 0.707        |     | \/               |

|                                |                    | PGA gain = 0dB, differential input,<br>THD+N ≤ -40dB                                                                             | 1            |     | V <sub>RMS</sub> |

|                                |                    | PGA gain = -3dB, differential input,<br>THD+N ≤ -40dB                                                                            | 1.414        |     |                  |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, V_{MBVDD} = 3.6V, GND = DGND = 0V, C_{MBVDD} = C_{MICBIASn} = 2.2μF, C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1μF, C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1μF, High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC Measurement Bandwidth = 20Hz to 20kHz, <math>T_{A} = -40$ °C to +85°C unless otherwise noted, Typical values at  $T_{A} = +25$ °C, Note 1)

| PARAMETER                                | SYMBOL                 | CONE                                                                                         | DITIONS                                                                                                                   | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Disabled AMIC Preamp<br>Input Resistance | R <sub>IN_PA_OFF</sub> | in software shutdow                                                                          | ded to ground, device<br>on or AMIC preamp<br>GA_HIZ_EN = 1 (Note                                                         | 100  | 200  |      | kΩ    |

| Active AMIC Preamp                       | Б                      | in active state and A                                                                        | ded to ground, device<br>AMIC preamp<br>GA_RIN = 0 (Note 5)                                                               | 28   | 35   |      | 1.0   |

| Input Resistance                         | R <sub>IN_PA_ON</sub>  | in active state and A                                                                        | ided to ground, device<br>AMIC preamp<br>GA_RIN = 1 (Note 5)                                                              | 8    | 10   |      | - kΩ  |

| Minimum PGA Gain                         |                        | AMICn_PGA_GAIN                                                                               | = 0x0 (Note 5)                                                                                                            | -6.5 | -6   | -5.5 | dB    |

| Maximum PGA Gain                         |                        | AMICn_PGA_GAIN                                                                               | = 0x9 (Note 5)                                                                                                            | 20.5 | 21   | 21.5 | dB    |

| ANALOG MICROPHONE                        | INPUT TO ADC           | RECORD / POWER                                                                               | SUPPLY REJECTION                                                                                                          |      |      |      |       |

|                                          |                        | V <sub>AVDD1</sub> = 1.71V to                                                                | 1.95V                                                                                                                     |      | 90   |      |       |

|                                          |                        | V <sub>RIPPLE</sub> =                                                                        | f <sub>RIPPLE</sub> = 217Hz                                                                                               |      | 110  |      |       |

|                                          |                        | 100mV <sub>P-P</sub> on                                                                      | f <sub>RIPPLE</sub> = 1kHz                                                                                                |      | 110  |      |       |

| Power Supply Rejection                   | · · · · · PSRR ·       | AVDD1                                                                                        | f <sub>RIPPLE</sub> = 20kHz                                                                                               |      | 95   |      | 4D    |

| Ratio                                    | PSRR                   | V <sub>AVDD2</sub> = 1.71V to                                                                | 1.95V                                                                                                                     |      | 95   |      | dB    |

|                                          |                        | V <sub>RIPPLE</sub> =                                                                        | f <sub>RIPPLE</sub> = 217Hz                                                                                               |      | 95   |      |       |

|                                          |                        | 100mV <sub>P-P</sub> on                                                                      | f <sub>RIPPLE</sub> = 1kHz                                                                                                |      | 95   |      |       |

|                                          |                        | AVDD2                                                                                        | f <sub>RIPPLE</sub> = 20kHz                                                                                               |      | 90   |      |       |

| MICROPHONE BIAS GE                       | NERATOR                |                                                                                              |                                                                                                                           |      |      |      |       |

|                                          |                        | AMIC_BIAS_SEL =                                                                              | 0x0                                                                                                                       | 1.1  | 1.2  | 1.3  |       |

|                                          |                        | AMIC_BIAS_SEL =                                                                              | 0x1 (Note 2)                                                                                                              | 1.4  | 1.5  | 1.6  | ]     |

|                                          |                        | AMIC_BIAS_SEL =                                                                              | 0x2                                                                                                                       | 1.7  | 1.8  | 1.9  |       |

| Output Valtage                           |                        | AMIC_BIAS_SEL =                                                                              | 0x3 (Note 2)                                                                                                              | 1.9  | 2    | 2.1  | V     |

| Output Voltage                           | VMICBIAS               | AMIC_BIAS_SEL =                                                                              | 0x4 (Note 2)                                                                                                              | 2.15 | 2.25 | 2.35 | ]     |

|                                          |                        | AMIC_BIAS_SEL =                                                                              | 0x5                                                                                                                       | 2.4  | 2.5  | 2.6  |       |

|                                          |                        | AMIC_BIAS_SEL =                                                                              | 0x6 (Note 2)                                                                                                              | 2.65 | 2.75 | 2.85 | ]     |

|                                          |                        | AMIC_BIAS_SEL =                                                                              | 0x7 (Note 2)                                                                                                              | 2.9  | 3    | 3.1  |       |

| Dropout Voltage                          |                        | V <sub>MB</sub> VDD - V <sub>MI</sub> CBIAS                                                  | Sn (Note 2)                                                                                                               | 200  |      |      | mV    |

| Enable Charge Time                       |                        | $C_{\text{MICBIAS1}} = 2.2 \mu F$                                                            | VMBVDD - VMICBIASn (Note 2)  VMICBIASn = 1.8V (90% charged),  CMICBIAS1 = 2.2μF, three microphones connected (0.1μF each) |      | 15   |      | μs    |

| Disable Discharge Time                   |                        | V <sub>MICBIASn</sub> = 3V, mi<br>disabled (90% disch<br>2.2µF, three microp<br>(0.1µF each) | narged), C <sub>MICBIAS1</sub> =                                                                                          |      | 7    |      | ms    |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, V_{MBVDD} = 3.6V, GND = DGND = 0V, C_{MBVDD} = C_{MICBIASn} = 2.2μF, C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1μF, C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1μF, High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC$  Measurement Bandwidth = 20Hz to 20kHz,  $T_A = -40$ °C to +85°C unless otherwise noted, Typical values at  $T_A = +25$ °C, Note 1)

| PARAMETER                           | SYMBOL                                                                 | COND                                                                                                           | ITIONS                                          | MIN | TYP | MAX | UNITS |

|-------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|-----|-------|

|                                     |                                                                        | V <sub>MICBIASn</sub> changed<br>(90% transition), C <sub>M</sub><br>three microphones c<br>each)              | ICBIAS1 = 2.2µF,                                |     | 15  |     | μs    |

|                                     |                                                                        | V <sub>MICBIASn</sub>                                                                                          | Low-noise mode                                  |     | 24  |     |       |

| Transition Time                     |                                                                        | changed from 3V to 1.2V (90% transition), CMICBIAS1 = 2.2µF, three microphones connected (0.1µF each) (Note 6) | Low-power mode                                  |     | 51  |     | ms    |

| MICROPHONE BIAS GE                  | NERATOR / QU                                                           | IESCENT CURRENT                                                                                                |                                                 |     |     |     | •     |

|                                     |                                                                        |                                                                                                                | V <sub>MICBIASn</sub> = 1.2V,<br>low-power mode |     | 22  |     |       |

| MBVDD Quiescent                     | ıt ,                                                                   | No microphones connected                                                                                       | V <sub>MICBIASn</sub> = 1.8V,<br>low-noise mode |     | 74  |     | μΑ    |

| Current                             | MBVDD                                                                  |                                                                                                                | V <sub>MICBIASn</sub> = 1.8V,<br>low-power mode |     | 33  |     | μΑ    |

|                                     |                                                                        |                                                                                                                | V <sub>MICBIASn</sub> = 2.5V,<br>low-power mode |     | 47  |     |       |

| AVDD1 Additive                      | l                                                                      | No microphones connected, additional current when enabled in software shutdown                                 | Low-power mode                                  |     | 70  |     | - μA  |

| Quiescent Current                   | I <sub>AVDD1</sub>                                                     | No microphones                                                                                                 | Low-noise mode                                  |     | 65  |     | J μΑ  |

|                                     | connected,<br>additional current<br>when enabled in<br>the audio state | Low-power mode                                                                                                 |                                                 | 50  |     |     |       |

| AVDD2 Additive<br>Quiescent Current | l <sub>AVDD2</sub>                                                     | No microphones connected, additional current when enabled in software shutdown                                 |                                                 |     | 40  |     | μΑ    |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, V_{MBVDD} = 3.6V, GND = DGND = 0V, C_{MBVDD} = C_{MICBIASn} = 2.2μF, C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1μF, C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1μF, High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC$  Measurement Bandwidth = 20Hz to 20kHz,  $T_A = -40$ °C to +85°C unless otherwise noted, Typical values at  $T_A = +25$ °C, Note 1)

| PARAMETER               | SYMBOL                                         | CONE                                                                    | ITIONS                                                                        | MIN | TYP  | MAX  | UNITS             |

|-------------------------|------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|------|------|-------------------|

| MICROPHONE BIAS GE      | NERATOR / OU                                   | TPUT NOISE                                                              |                                                                               |     |      |      | 1                 |

|                         |                                                | A-weighted, f =                                                         | Low-noise mode                                                                |     | 3.4  |      |                   |

|                         |                                                | 20Hz to 20kHz,<br>V <sub>MICBIASn</sub> = 1.2V                          | Low-power mode                                                                |     | 4.1  |      |                   |

|                         |                                                | A-weighted, f =                                                         | Low-noise mode                                                                |     | 5.2  |      | ]                 |

| Integrated Output Noise |                                                | 20Hz to 20kHz,<br>V <sub>MICBIASn</sub> = 1.8V                          | Low-power mode                                                                |     | 6.7  |      | μV <sub>RMS</sub> |

|                         | A-weighted, f =                                | Low-noise mode                                                          |                                                                               | 7.6 |      |      |                   |

|                         | 20Hz to 20kHz,<br>V <sub>MICBIASn</sub> = 2.5V | Low-power mode                                                          |                                                                               | 9.6 |      |      |                   |

| MICROPHONE BIAS GE      | NERATOR / OU                                   | TPUTS CHARACTER                                                         | ISTICS                                                                        |     |      |      |                   |

| Output Current Drive    | I <sub>MICBIAS</sub>                           | Any combination of MICBIAS2, and MIC three analog microp total (Note 2) | 3                                                                             |     |      | mA   |                   |

|                         |                                                | Morrison                                                                | V <sub>MICBIAS1</sub> = 1.8V,<br>0mA ≤ I <sub>MICBIAS</sub> ≤<br>1mA (Note 2) |     | ±0.5 | ±3.5 |                   |

| Load Doculation         |                                                | MICBIAS1 output                                                         | V <sub>MICBIAS1</sub> = 1.8V,<br>1mA < I <sub>MICBIAS</sub> ≤<br>3mA (Note 2) |     | ±1.1 | ±6.5 |                   |

| Load Regulation         |                                                | MICBIAS2 or                                                             | V <sub>MICBIASn</sub> = 1.8V,<br>0mA ≤ I <sub>MICBIAS</sub> ≤<br>1mA (Note 2) |     | ±1.5 | ±4.5 | - mV              |

|                         |                                                | MICBIAS3 output                                                         | V <sub>MICBIASn</sub> = 1.8V,<br>1mA ≤ I <sub>MICBIAS</sub> ≤<br>3mA (Note 2) |     | ±3.1 | ±9   |                   |

| Line Regulation         |                                                | V <sub>MICBIASn</sub> = 1.8V, \((Note 2))                               | / <sub>MBVDD</sub> = 2V to 4.8V                                               |     | ±0.1 |      | mV                |

$(V_{AVDD1} = V_{DVDDIO} = 1.8V, V_{AVDD2} = V_{AVDD3} = V_{DVDD} = 1.2V, V_{MBVDD} = 3.6V, GND = DGND = 0V, C_{MBVDD} = C_{MICBIASn} = 2.2μF, C_{AVDD1} = C_{AVDD1}_{REG} = C_{AVDD2} = C_{AVDD3} = C_{DVDD} = 1μF, C_{DVDDIO} = C_{MICBIAS2} = C_{MICBIAS3} = 0.1μF, High-Performance Record and Playback Modes, Low-Noise Microphone Bias Mode, <math>Z_{LOAD} = OPEN, f_{LRCLK} = 48kHz, f_{S_DF} = 192kHz, f_{BCLK} = 3.072MHz, f_{DMIC_CLK} = 3.072MHz, AC Measurement Bandwidth = 20Hz to 20kHz, <math>T_{A} = -40$ °C to +85°C unless otherwise noted, Typical values at  $T_{A} = +25$ °C, Note 1)

| PARAMETER                           | SYMBOL       | COND                                                                                                                    | ITIONS                                                                  | MIN TYP            | MAX         | UNITS    |

|-------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|-------------|----------|

| MICROPHONE BIAS GEN                 | ERATOR / POV | VER SUPPLY REJEC                                                                                                        | TION                                                                    |                    |             | 1        |

|                                     |              | MDVDD DC DCDD                                                                                                           | V <sub>MICBIASn</sub> = 1.2V,<br>V <sub>MBVDD</sub> = 1.4V to<br>4.8V   | 90                 |             |          |

|                                     |              | MBVDD DC PSRR                                                                                                           | V <sub>MICBIASn</sub> = 1.8V,<br>V <sub>MBVDD</sub> = 2V to<br>4.8V     | 90                 |             |          |

|                                     |              | V <sub>RIPPLE</sub> =                                                                                                   | f <sub>RIPPLE</sub> = 217Hz                                             | 90                 |             |          |

|                                     |              | 100mV <sub>P-P</sub> on MBVDD,                                                                                          | f <sub>RIPPLE</sub> = 1kHz                                              | 90                 |             |          |