#### **General Description**

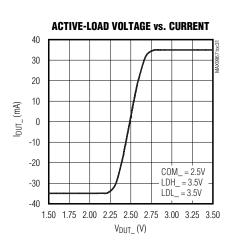

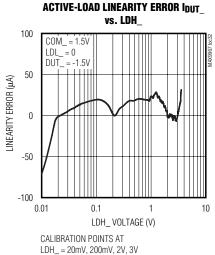

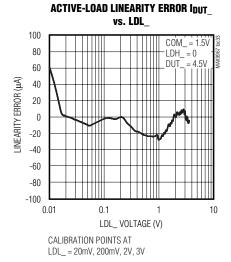

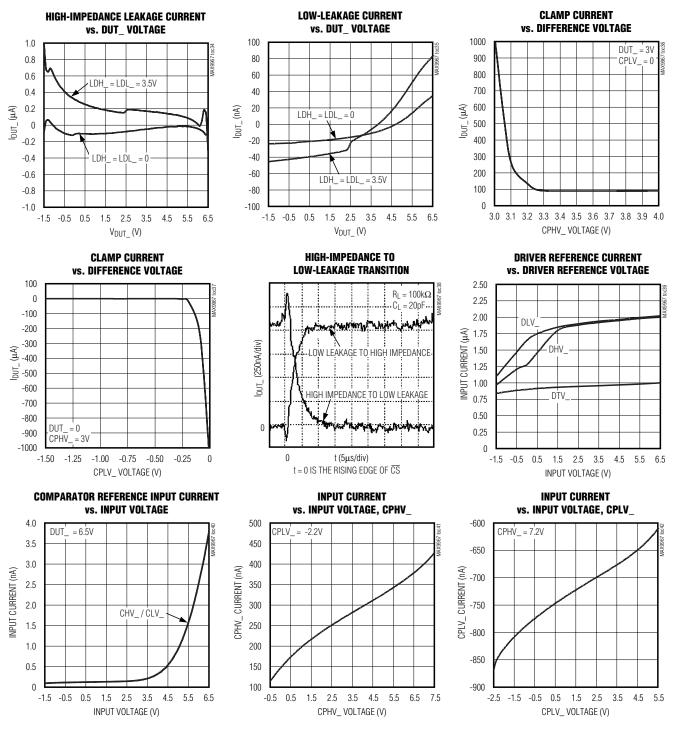

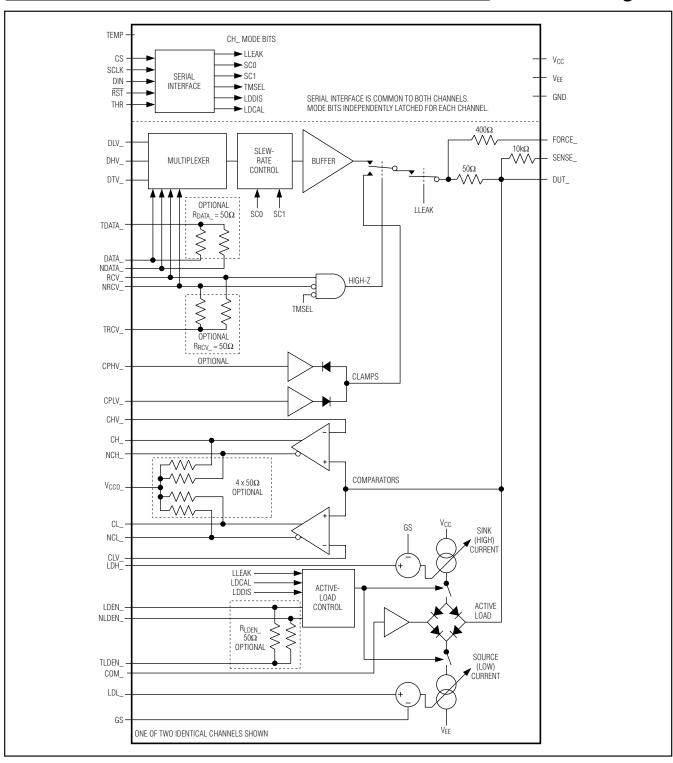

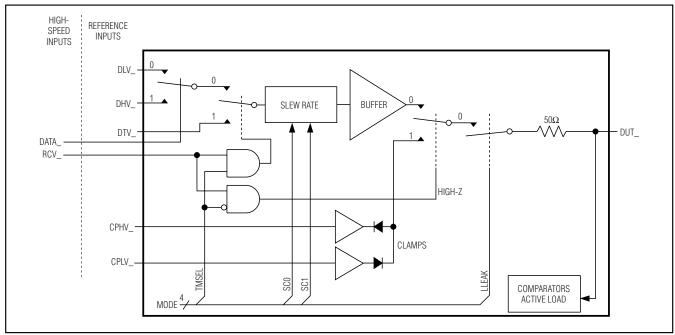

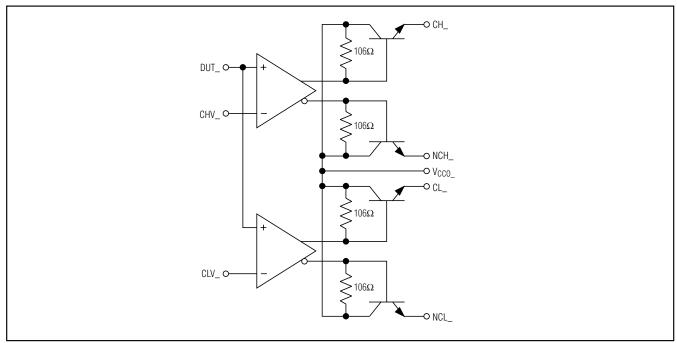

The MAX9967 dual, low-power, high-speed, pin electronics driver/comparator/load (DCL) IC includes, for each channel, a three-level pin driver, a dual comparator, variable clamps, and an active load. The driver features a wide voltage range and high-speed operation, includes high-impedance and active-termination (3rd-level drive) modes, and is highly linear even at low-voltage swings. The dual comparator provides low dispersion (timing variation) over a wide variety of input conditions. The clamps provide damping of high-speed device-undertest (DUT) waveforms when the device is configured as a high-impedance receiver. The programmable load supplies up to 35mA of source and sink current. The load facilitates contact/continuity testing, at-speed parametric testing of IOH and IOL, and pullup of high-output-impedance devices.

The MAX9967A provides tight matching of gain and offset for the drivers, and offset for the comparators and active load, allowing reference levels to be shared across multiple channels in cost-sensitive systems. Use the MAX9967B for system designs that incorporate independent reference levels for each channel.

The MAX9967 provides high-speed, differential control inputs with optional internal termination resistors that are compatible with ECL, LVPECL, LVDS, and GTL. ECL/LVPECL or flexible open-collector outputs with optional internal pullup resistors are available for the comparators. These features significantly reduce the discrete component count on the circuit board.

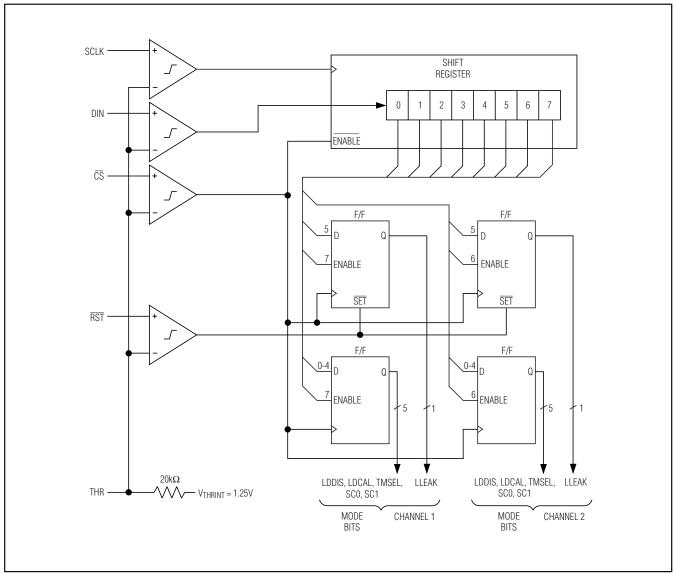

A 3-wire, low-voltage, CMOS-compatible serial interface programs the low-leakage, slew-rate limit, and tristate/terminate operational configurations of the MAX9967.

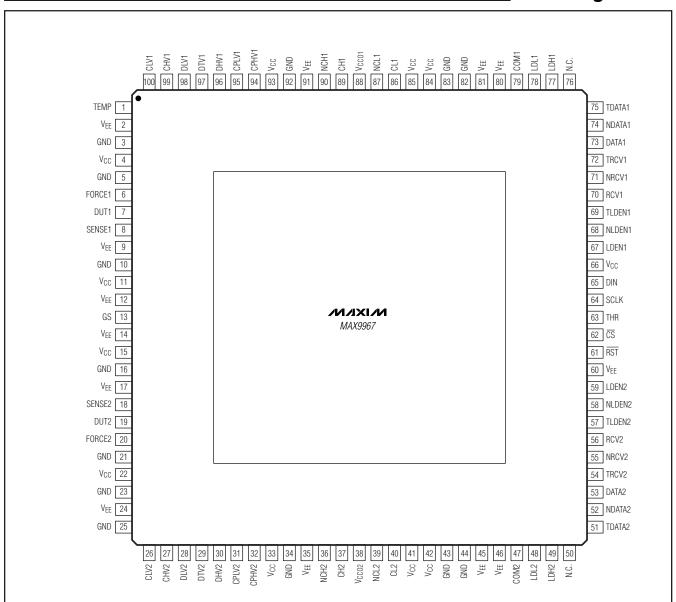

The MAX9967's operating range is -1.5V to +6.5V with power dissipation of only 1.15W per channel. The device is available in a 100-pin, 14mm x 14mm body, and 0.5mm pitch TQFP. An exposed 8mm x 8mm die pad on the top of the package facilitates efficient heat removal. The device is specified to operate with an internal die temperature of +70°C to +100°C, and features a die temperature monitor output.

#### **Applications**

Low-Cost Mixed-Signal/System-on-Chip ATE Commodity Memory ATE PCI or VXI Programmable Digital Instruments

#### **Features**

- **♦** Low Power Dissipation: 1.15W/Channel (typ)

- ♦ High Speed: 500Mbps at 3Vp-p

- ♦ Programmable 35mA Active-Load Current

- **♦ Low Timing Dispersion**

- ♦ Wide -1.5V to +6.5V Operating Range

- **♦** Active Termination (3rd-Level Drive)

- ♦ Low Leakage Mode: 60nA

- **♦ Integrated Clamps**

- ♦ Interfaces Easily with Most Logic Families

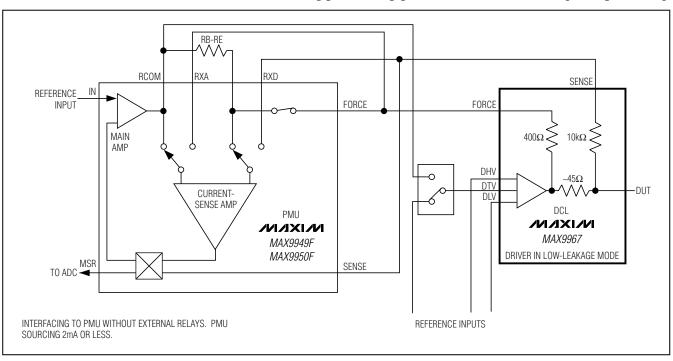

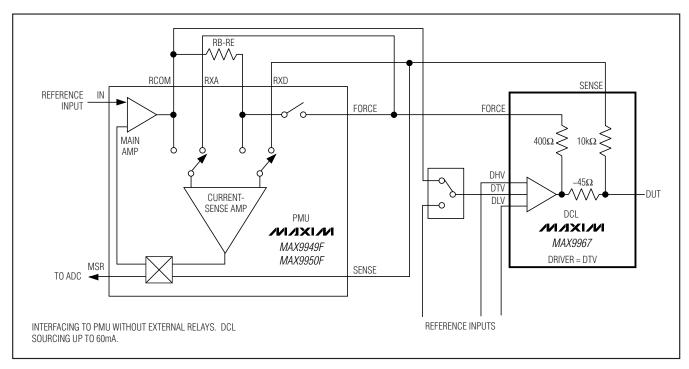

- **♦ Integrated PMU Connection**

- **♦ Digitally Programmable Slew Rate**

- ♦ Internal Termination Resistors

- Low Gain and Offset Error

#### **Ordering Information**

| PART          | TEMP RANGE   | PIN-PACKAGE    |

|---------------|--------------|----------------|

| MAX9967ADCCQ* | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967AGCCQ* | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967ALCCQ  | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967AMCCQ* | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967AQCCQ* | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967ARCCQ* | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967BDCCQ  | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967BGCCQ  | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967BLCCQ  | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967BMCCQ  | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967BQCCQ* | 0°C to +70°C | 100 TQFP-EPR** |

| MAX9967BRCCQ  | 0°C to +70°C | 100 TQFP-EPR** |

<sup>\*</sup>Future product—contact factory for availability.

Pin Configuration and Typical Application Circuits appear at end of data sheet.

Selector Guide appears at end of data sheet.

<sup>\*\*</sup>EPR = Exposed pad reversed (TOP).

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND              | 0.3V to +11.5V | DHV_ to DTV±10V                                                        |

|-------------------------------------|----------------|------------------------------------------------------------------------|

| VEE to GND                          | 7.0V to +0.3V  | DLV_ to DTV±10V                                                        |

| V <sub>CC</sub> - V <sub>EE</sub>   | 0.3V to +18V   | CHV_ or CLV_ to DUT±10V                                                |

| GS to GND                           |                | CH_, NCH_, CL_, NCL_ to GND (open collector)2.5V to +5V                |

| DUT_, LDH_, LDL_ to GND             | 2.5V to +7.5V  | CH_, NCH_, CL_, NCL_ to GND (open emitter) (V <sub>CCO</sub> _ + 1.0V) |

| DATA_, NDATA_, RCV_, NRCV_,         |                | All Other Pins to GND(VEE - 0.3V) to (VCC + 0.3V)                      |

| LDEN_, NLDEN_ to GND                | 2.5V to +5.0V  | Current Out of CH_, NCH_, CL_, NCL_ (open emitter)+50mA                |

| DATA_ to NDATA_, RCV_ to NRCV_,     |                | DHV_, DLV_, DTV_, CHV_, CLV_,                                          |

| LDEN_ to NLDEN                      | ±1.5V          | CPHV_, CPLV_ Current±10mA                                              |

| V <sub>CCO</sub> to GND             |                | TEMP Current0.5mA to +20mA                                             |

| SCLK, DIN, CS, RST, TDATA_,         |                | DUT_ Short Circuit to -1.5V to +6.5VContinuous                         |

| TRCV_, TLDEN_ to GND                | 1.0V to +5V    | Power Dissipation ( $T_A = +70^{\circ}C$ )                             |

| DHV_, DLV_, DTV_, CHV_, CLV_, COM_, |                | MAX9967CCQ (derate 167mW/°C above +70°C)13.3W*                         |

| FORCE_, SENSE_ to GND               | 2.5V to +7.5V  | Storage Temperature Range65°C to +150°C                                |

| CPHV_ to GND                        | 2.5V to +8.5V  | Junction Temperature+125°C                                             |

| CPLV_ to GND                        | 3.5V to +7.5V  | Lead Temperature (soldering, 10s)+300°C                                |

| DHV_ to DLV                         | ±10V           |                                                                        |

|                                     |                |                                                                        |

<sup>\*</sup>Dissipation wattage values are based on still air with no heat sink. Actual maximum allowable power dissipation is a function of heat extraction technique and may be substantially higher.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +9.75V, \ V_{EE} = -5.25V, \ V_{CCO} = +2.5V, \ SC1 = SC0 = 0, \ V_{CPHV} = +7.2V, \ V_{CPLV} = -2.2V, \ V_{LDH} = V_{LDL} = 0, \ V_{GS} = 0, \ T_J = +85^{\circ}C, \ unless \ otherwise \ noted.) \ (Note 1)$

| PARAMETER                              | SYMBOL           | CONDITIONS                                                                                                        | MIN  | TYP   | MAX  | UNITS |

|----------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| POWER SUPPLIES                         |                  |                                                                                                                   |      |       |      |       |

| Positive Supply                        | Vcc              |                                                                                                                   | 9.5  | 9.75  | 10.5 | V     |

| Negative Supply                        | VEE              |                                                                                                                   | -6.5 | -5.25 | -4.5 | V     |

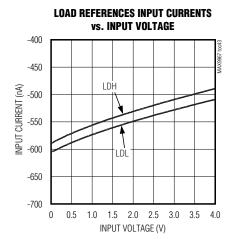

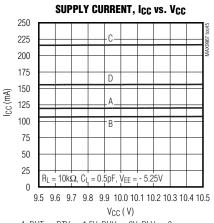

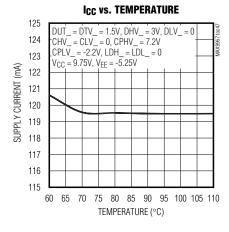

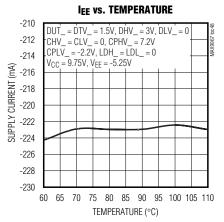

|                                        |                  | $V_{LDH} = V_{LDL} = 0$                                                                                           |      | 120   | 155  |       |

| Positive Supply Current (Note 2)       | Icc              | V <sub>LDH</sub> _ = V <sub>LDL</sub> _ = 3.5V, load enabled, driver = high impedance                             |      | 220   | 255  | mA    |

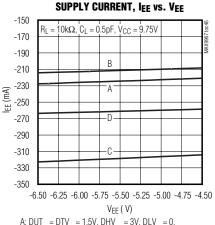

|                                        |                  | $V_{LDH} = V_{LDL} = 0$                                                                                           |      | -220  | -265 |       |

| Negative Supply Current (Note 2)       | I <sub>EE</sub>  | V <sub>LDH</sub> _ = V <sub>LDL</sub> _ = 3.5V, load enabled,<br>driver = high impedance                          |      | -320  | -365 | mA    |

| Power Dissipation                      | PD               | (Notes 2, 3)                                                                                                      |      | 2.3   | 2.9  | W     |

| DUT_ CHARACTERISTICS                   |                  |                                                                                                                   |      |       |      |       |

| Operating Voltage Range                | V <sub>DUT</sub> | (Note 4)                                                                                                          | -1.5 |       | +6.5 | V     |

| Leakage Current in High-               | lour             | LLEAK = 0; $0 \le V_{DUT} \le 3V$                                                                                 |      |       | ±1.5 | μΑ    |

| Impedance Mode                         | IDUT             | LLEAK = 0; $V_{DUT}$ = -1.5V, +6.5V                                                                               |      |       | ±3   | μΑ    |

|                                        |                  | LLEAK = 1; $0 \le V_{DUT} \le 3V$ , $T_{J} < +90^{\circ}C$                                                        |      |       | ±60  |       |

|                                        |                  | LLEAK = 1; $V_{DUT}$ = -1.5V, +6.5V; $T_{J}$ < +90°C                                                              |      |       | ±110 |       |

| Leakage Current in Low-Leakage<br>Mode |                  | LLEAK = 1; $0 \le V_{DUT} \le 3V$ , $V_{LDL} = V_{LDH} = 3.5V$ ; $T_{J} < +90^{\circ}C$                           |      |       | ±80  | nA    |

|                                        |                  | LLEAK = 1; V <sub>DUT</sub> = -1.5V, +6.5V;<br>V <sub>LDL</sub> = V <sub>LDH</sub> = 3.5V; T <sub>J</sub> < +90°C |      |       | ±160 |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, \ V_{EE} = -5.25V, \ V_{CCO} = +2.5V, \ SC1 = SC0 = 0, \ V_{CPHV} = +7.2V, \ V_{CPLV} = -2.2V, \ V_{LDH} = V_{LDL} = 0, \ V_{GS} = 0, \ T_{J} = +85^{\circ}C, \ unless \ otherwise \ noted.) \ (Note 1)$

| Combined Capacitance  CDUT  Driver in term mode (DUT_ = DTV_) Driver in high-impedance mode  (Notes 5, 6)  Low-Leakage Disable Time  (Notes 6, 7)  Time to return to the specified maximum leakage after a 3V, 4V/ns step at DUT_  LEVEL PROGRAMMING INPUTS (DHV_, DLV_, DTV_, CHV_, CLV_, CPHV_, CPLV_, COM_ Input Bias Current  Settling time  To 0.1% of full-scale change (Note 7)  DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage  VIH Input Low Voltage  VIL Differential Input Voltage  Input Bias Current  MAX9967_DCCQ, MAX9967_MCCQ  Input Termination Voltage  VTDATA_, VTRCV_, MAX9967_GCCQ, MAX9967_LCCQ, and MAX9967_CCCQ, MAX9967_LCCQ, and MAX9967_DCCQ, MAX9967_LCCQ, and MAX9967_DCCQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | , LDH_, L              | 4.0<br>8.0<br>20<br>20<br>4 |                        | pF<br>µs<br>µs |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|------------------------|----------------|

| Low-Leakage Enable Time (Notes 5, 6)  Low-Leakage Disable Time (Notes 6, 7)  Low-Leakage Recovery Time to return to the specified maximum leakage after a 3V, 4V/ns step at DUT_  LEVEL PROGRAMMING INPUTS (DHV_, DLV_, DTV_, CHV_, CLV_, CPHV_, CPLV_, COM_ Input Bias Current IBIAS  Settling time To 0.1% of full-scale change (Note 7)  DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage VIH Input Low Voltage VIL Differential Input Voltage VDIFF  Input Bias Current MAX9967_DCCQ, MAX9967_MCCQ  Input Tarmination Voltage VTDATA_, MAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | , LDH_, L              | 20 20 4                     |                        | μs             |

| Low-Leakage Disable Time  Low-Leakage Recovery  Time to return to the specified maximum leakage after a 3V, 4V/ns step at DUT_  LEVEL PROGRAMMING INPUTS (DHV_, DLV_, DTV_, CHV_, CLV_, CPHV_, CPLV_, COM_ Input Bias Current  IBIAS  Settling time  To 0.1% of full-scale change (Note 7)  DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage  VIH Input Low Voltage  VIL Differential Input Voltage  Input Bias Current  MAX9967_DCCQ, MAX9967_MCCQ  VTDATA_, MAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | , LDH_, L              | 20                          |                        |                |

| Low-Leakage Recovery  Time to return to the specified maximum leakage after a 3V, 4V/ns step at DUT_  LEVEL PROGRAMMING INPUTS (DHV_, DLV_, DTV_, CHV_, CLV_, CPHV_, CPLV_, COM_ Input Bias Current  IBIAS  Settling time  To 0.1% of full-scale change (Note 7)  DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage  VIH  Input Low Voltage  VIL  Differential Input Voltage  Input Bias Current  MAX9967_DCCQ, MAX9967_MCCQ  VTDATA_, MAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | , LDH_, L              | 4                           |                        | μs             |

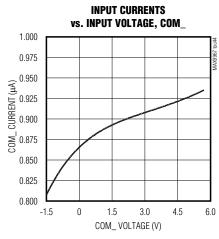

| LEVEL PROGRAMMING INPUTS (DHV_, DLV_, DTV_, CHV_, CPHV_, CPLV_, COM_ Input Bias Current IBIAS  Settling time To 0.1% of full-scale change (Note 7)  DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage VIH Input Low Voltage VIL  Differential Input Voltage VDIFF  Input Bias Current MAX9967_DCCQ, MAX9967_MCCQ  Input Termination Voltage VTDATA_, MAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | , LDH_, L              |                             |                        |                |

| Input Bias Current  Settling time  To 0.1% of full-scale change (Note 7)  DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage  VIH  Input Low Voltage  VIL  Differential Input Voltage  Input Bias Current  MAX9967_DCCQ, MAX9967_MCCQ  VTDATA_, VTDATA_, VAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | , LDH_, L              | DL )                        |                        | μs             |

| Settling time  To 0.1% of full-scale change (Note 7)  DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage  VIH  Input Low Voltage  VIL  Differential Input Voltage  Input Bias Current  VTDATA_,  VT |                        | ,                           |                        |                |

| DIFFERENTIAL CONTROL INPUTS (DATA_, NDATA_, RCV_, NRCV_, LDEN_, NLDEN_)  Input High Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |                             | ±25                    | μΑ             |

| Input High Voltage  VIH  Input Low Voltage  VIL  Differential Input Voltage  Input Bias Current  VTDATA_,  |                        | 1                           |                        | μs             |

| Input Low Voltage  VIL  Differential Input Voltage  Input Bias Current  MAX9967_DCCQ, MAX9967_MCCQ  VTDATA_, VT |                        |                             |                        |                |

| Differential Input Voltage  Input Bias Current  MAX9967_DCCQ, MAX9967_MCCQ  VTDATA_,  VTDATA_,  MAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1.6                   |                             | +3.5                   | ٧              |

| Input Bias Current  MAX9967_DCCQ, MAX9967_MCCQ  VTDATA_, MAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -2.0                   |                             | +3.1                   | V              |

| VTDATA_, MAX9967_GCCQ, MAX9967_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ±0.15                  |                             | ±1.0                   | V              |

| Input Termination Valtage WAX9907_GCCQ, WAX9907_LCCQ, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |                             | ±25                    | μΑ             |

| VIRCV_, VILDEN_ MAX9967_QCCQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -2.1                   |                             | +3.5                   | ٧              |

| Input Termination Resistor  MAX9967_GCCQ, MAX9967_LCCQ, and MAX9967_QCCQ, between signal and corresponding termination voltage input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48                     |                             | 52                     | Ω              |

| SINGLE-ENDED CONTROL INPUTS (CS, SCLK, DIN, RST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |                             |                        |                |

| Internal Threshold Reference VTHRINT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.05                   | 1.25                        | 1.45                   | V              |

| Internal Reference Output Rosistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        | 20                          |                        | kΩ             |

| External Threshold Reference V <sub>THR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.43                   |                             | 1.73                   | V              |

| Input High Voltage VIH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>THR</sub> + 0.2 |                             | 3.5                    | V              |

| Input Low Voltage V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -0.1                   |                             | V <sub>THR</sub> - 0.2 | V              |

| Input Bias Current I <sub>B</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |                             | ±25                    | μΑ             |

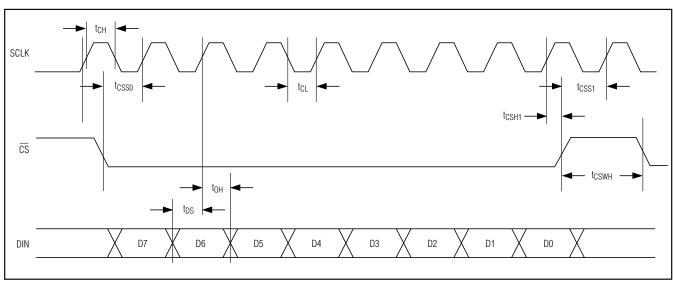

| SERIAL INTERFACE TIMING (Figure 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |                             | !                      |                |

| SCLK Frequency fSCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |                             | 50                     | MHz            |

| SCLK Pulse-Width High t <sub>CH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                      |                             |                        | ns             |

| SCLK Pulse-Width Low t <sub>CL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |                             | -                      |                |

| CS Low to SCLK High Setup t <sub>CSS0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                      |                             |                        | ns             |

| CS High to SCLK High Setup t <sub>CSS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.5                    |                             |                        | ns<br>ns       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, \ V_{EE} = -5.25V, \ V_{CCO} = +2.5V, \ SC1 = SC0 = 0, \ V_{CPHV} = +7.2V, \ V_{CPLV} = -2.2V, \ V_{LDH} = V_{LDL} = 0, \ V_{GS} = 0, \ T_{J} = +85^{\circ}C, \ unless \ otherwise \ noted. \ All \ temperature \ coefficients \ are \ measured \ at \ T_{J} = +70^{\circ}C \ to \ +100^{\circ}C, \ unless \ otherwise \ noted.) \ (Note 1)$

| PARAMETER                                               | SYMBOL                   | CONDITIONS                                                                                   |                      | MIN   | TYP   | MAX   | UNITS  |

|---------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------|----------------------|-------|-------|-------|--------|

| SCLK High to CS High Hold                               | tCSH1                    |                                                                                              |                      | 3.5   |       |       | ns     |

| DIN to SCLK High Setup                                  | tDS                      |                                                                                              |                      | 3.5   |       |       | ns     |

| DIN to SCLK High Hold                                   | tDH                      |                                                                                              |                      | 3.5   |       |       | ns     |

| CS Pulse Width High                                     | tcswh                    |                                                                                              |                      | 20    |       |       | ns     |

| TEMPERATURE MONITOR (TEM                                | P)                       |                                                                                              |                      |       |       |       |        |

| Nominal Voltage                                         |                          | $T_J = +70^{\circ}C, R_L \ge 10M\Omega$                                                      |                      |       | 3.43  |       | V      |

| Temperature Coefficient                                 |                          |                                                                                              |                      |       | +10   |       | mV/°C  |

| Output Resistance                                       |                          |                                                                                              |                      |       | 15    |       | kΩ     |

| DRIVERS (Note 8)                                        |                          |                                                                                              |                      |       |       |       |        |

| DC OUTPUT CHARACTERISTICS                               | 6 (R <sub>L</sub> ≥ 10MΩ | )                                                                                            |                      |       |       |       |        |

| DHV_, DLV_, DTV_, Output Offset Voltage                 | Vos                      | At DUT_ with V <sub>DHV</sub> _, V <sub>DTV</sub> _, V <sub>DLV</sub> _ independently tested | MAX9967A             |       |       | ±15   | mV     |

| <b>9</b>                                                |                          | at +1.5V                                                                                     | at +1.5V MAX9967B    |       |       | ±100  |        |

| DHV_, DLV_, DTV_, Output Offset Temperature Coefficient |                          |                                                                                              |                      |       | ±65   |       | μV/°C  |

| DHV_, DLV_, DTV_, Gain                                  | Av                       | Measured with V <sub>DHV</sub> , V <sub>DLV</sub> , and V <sub>DTV</sub> at 0 and 4.5V       | MAX9967A<br>(Note 9) | 0.999 | 1.00  | 1.001 | V/V    |

|                                                         |                          | MAX9967B                                                                                     | 0.96                 |       | 1.001 |       |        |

| DHV_, DLV_, DTV_, Gain<br>Temperature Coefficient       |                          |                                                                                              |                      |       | -35   |       | ppm/°C |

|                                                         |                          | V <sub>DUT</sub> = 1.5V, 3V (Note 10)                                                        |                      |       |       | ±5    | .,     |

| Linearity Error                                         |                          | Full range (Notes 10, 11)                                                                    |                      |       |       | ±15   | mV     |

| DHV_ to DLV_ Crosstalk                                  |                          | V <sub>DLV</sub> = 0;<br>V <sub>DHV</sub> = 200mV, 6.5V                                      |                      |       |       | ±2    | mV     |

| DLV_ to DHV_ Crosstalk                                  |                          | V <sub>DHV</sub> = 5V;<br>V <sub>DLV</sub> = -1.5V, +4.8V                                    |                      |       |       | ±2    | mV     |

| DTV_ to DLV_ and DHV_<br>Crosstalk                      |                          | V <sub>DHV</sub> = 3V; V <sub>DLV</sub> = 0;<br>V <sub>DTV</sub> = -1.5V, +6.5V              |                      |       |       | ±2    | mV     |

| DHV_ to DTV_ Crosstalk                                  |                          | V <sub>DTV</sub> _ = 1.5V; V <sub>DLV</sub> _ = 0;<br>V <sub>DHV</sub> _ = 1.6V, 3V          |                      |       |       | ±3    | mV     |

| DLV_ to DTV_ Crosstalk                                  |                          | V <sub>DTV</sub> _ = 1.5V; V <sub>DHV</sub> _ = 3V; V <sub>DI</sub>                          | LV_ = 0, 1.4V        |       |       | ±3    | mV     |

| DHV_, DTV_, DLV_ DC Power-<br>Supply Rejection Ratio    | PSRR                     | (Note 12)                                                                                    |                      | 40    |       |       | dB     |

| Maximum DC Drive Current                                | I <sub>DUT</sub> _       |                                                                                              |                      | ±60   |       | ±120  | mA     |

| DC Output Resistance                                    | R <sub>DUT</sub> _       | I <sub>DUT</sub> _ = ±30mA (Note 13)                                                         |                      | 49    | 50    | 51    | Ω      |

| DC Output Resistance Variation                          |                          | $I_{DUT} = \pm 1$ mA to $\pm 8$ mA                                                           |                      |       | 0.5   |       | Ω      |

| DO Output Hesistance Valiation                          | ∆R <sub>DUT</sub> _      | $I_{DUT}$ = ±1mA to ±40mA                                                                    |                      |       | 1     | 2.5   | 32     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +9.75V, \ V_{EE} = -5.25V, \ V_{CCO} = +2.5V, \ SC1 = SC0 = 0, \ V_{CPHV} = +7.2V, \ V_{CPLV} = -2.2V, \ V_{LDH} = V_{LDL} = 0, \ V_{GS} = 0, \ T_{J} = +85^{\circ}C, \ unless \ otherwise \ noted.) \ (Note 1)$

| PARAMETER                                             | SYMBOL                            | CONDITIONS                                                                             | MIN  | TYP   | MAX   | UNITS |

|-------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------|------|-------|-------|-------|

| Sense Resistance                                      | RSENSE                            |                                                                                        | 7.50 | 10    | 13.75 | kΩ    |

| Force Resistance                                      | RFORCE                            |                                                                                        | 320  | 400   | 500   | Ω     |

| Force Capacitance                                     | CFORCE                            |                                                                                        |      | 2     |       | pF    |

| DYNAMIC OUTPUT CHARACTER                              | RISTICS (Z <sub>L</sub> =         | : 50Ω)                                                                                 |      |       |       |       |

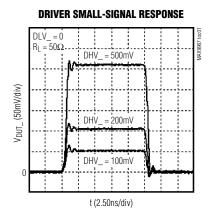

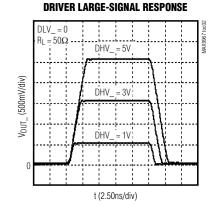

|                                                       |                                   | $V_{DLV} = 0, V_{DHV} = 0.1V$                                                          |      | 30    |       |       |

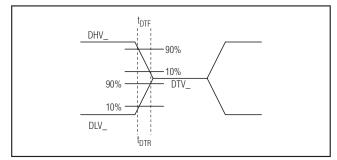

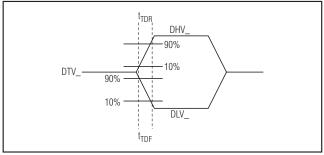

| Drive-Mode Overshoot                                  |                                   | V <sub>DLV</sub> _ = 0, V <sub>DHV</sub> _ = 1V                                        |      | 40    |       | mV    |