# Data Sheet Dual 13A or Single 26A Power Module

MxL7213

## **General Description**

The MxL7213 is a dual channel, 13A step-down power module. It includes a wide 4.5V to 16V input voltage range and supports two outputs each with an output voltage range of 0.6V to 5.3V, set by a single external resistor. The MxL7213 requires just a few input and output capacitors, which simplifies design and shortens time-to-market. The module supplies either two 13A outputs, a single 26A or up to 100A when paralleled with additional MxL7213 modules. Attention to thermal design, component selection and internal construction results in higher efficiency and extended operating range relative to devices with the same industry standard pinout.

The complete switch mode DC/DC power supply integrates the control, drivers, bootstrap diodes, bootstrap capacitors, inductors, MOSFETs and HF bypass capacitors in a single package for point-of-load conversions.

The MxL7213 includes a temperature diode that enables device temperature monitoring. It also has an adjustable switching frequency and utilizes a peak current mode architecture which allows fast line and load transient response.

A host of protection features, including overcurrent, overtemperature, short-circuit and UVLO, help this module achieve safe operation under abnormal operating conditions.

The MxL7213 is available in two space saving, RoHS compliant and thermally enhanced packages: a 15mm x 15mm x 4.41mm LGA package and a 15mm x 15mm x 5.01mm BGA package.

#### Features

- Dual 13A or single 26A output

- Input voltage range: 4.5V to 16V

- Output voltage range: 0.6V to 5.3V

- Multiphase current sharing with multiple MxL7213s for up to 100A output

- Frequency synchronization

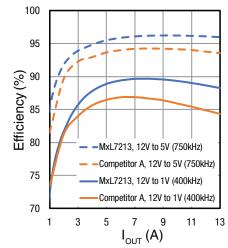

- Higher efficiency than competitive devices with the same industry standard pinout

- Differential remote sense amplifier

- Peak current mode architecture for fast transient response

- Adjustable switching frequency (250kHz to 780kHz)

- Overcurrent protection

- Output overvoltage protection

- Internal temperature monitor and thermal shutdown protection

- Thermally enhanced packages:

- 15mm x 15mm x 4.41mm LGA package

- 15mm x 15mm x 5.01mm BGA package

### **Applications**

- Telecom and Networking Equipment

- Industrial Equipment

- Test Equipment

#### Ordering Information - page 34

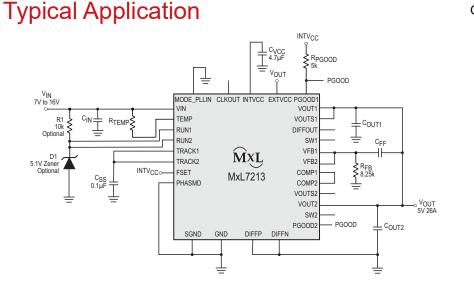

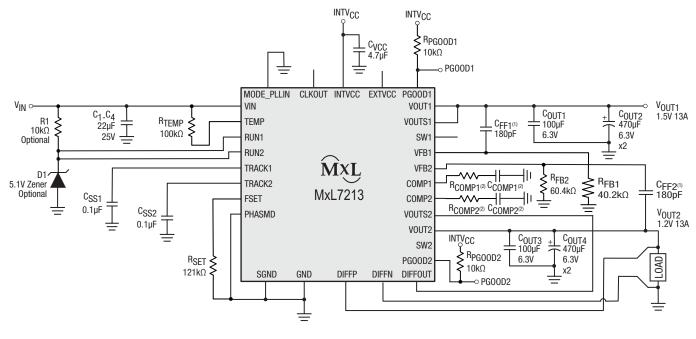

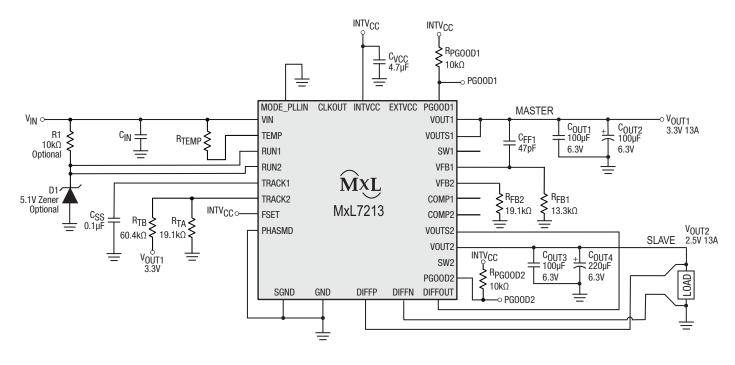

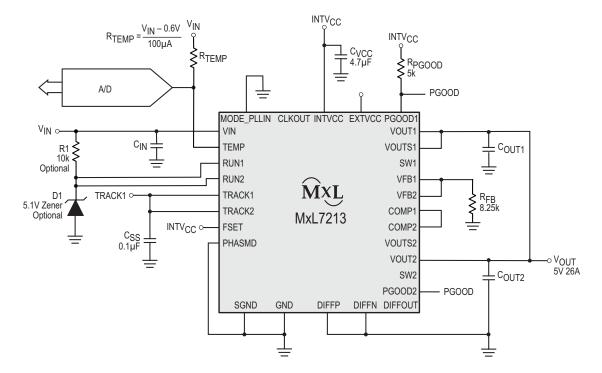

Figure 1: Typical Application: 26A, 5V Output DC/DC Power Module

Figure 2: Efficiency Advantage vs. Competition

## response Adjustable switchin

# **Revision History**

| Document No. | Release Date | Change Description                                                                                                                                                                                                                                                                                 |

|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 074DSR01     | 4/1/19       | Initial release.                                                                                                                                                                                                                                                                                   |

| 074DSR02     | 5/16/19      | Remove stray line from Recommended PCB Layout. Correct number of phases sentence under Multiphase Operation and current source and external lock sentences under Frequency Selection and Phase-Lock Loop. Correct SGND to GND in INTVCC pin description. Changed TC <sub>VTEMP</sub> to -2.2mV/°C. |

| 074DSR03     | 9/19/19      | Update efficiency, power loss, and de-rating graphs. Removed output voltage noise graph.<br>Update compensation section, thermal resistances, and capacitor table. V <sub>OUT</sub> maximum changed to 16V. Update ordering information.                                                           |

# **Table of Contents**

| General Description                                  | i  |

|------------------------------------------------------|----|

| Features                                             | i  |

| Applications                                         | i  |

| Specifications                                       | 1  |

| Absolute Maximum Ratings                             | 1  |

| ESD Ratings                                          | 1  |

| Operating Conditions                                 | 2  |

| Electrical Characteristics                           | 3  |

| Pin Information                                      | 6  |

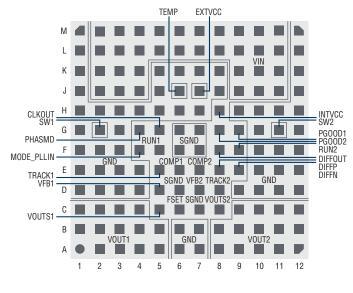

| Pin Configuration                                    | 6  |

| Pin Description                                      | 6  |

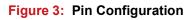

| Typical Performance Characteristics                  | 9  |

| Functional Block Diagram                             | 13 |

| Operation                                            |    |

| Power Module Description                             |    |

| Applications Information                             |    |

| Typical Application Circuit                          |    |

| V <sub>IN</sub> to V <sub>OUT</sub> Step-Down Ratios |    |

| Output Voltage Programming                           | 15 |

| Input Capacitors                                     | 15 |

| Output Capacitors                                    |    |

| Pulse-Skipping Mode Operation                        |    |

| Forced Continuous Operation                          |    |

| Multiphase Operation                                 |    |

| Input RMS Ripple Current Cancellation                |    |

| Frequency Selection and Phase-Lock Loop              |    |

| Minimum On-Time                                      | 19 |

| Soft Start and Output Voltage Tracking               | 19 |

| Power Good                                           |    |

| Stability and Compensation                           |    |

| Additional Compensation Information                  | 21 |

| Enabling the Channels                                |    |

| INTV <sub>CC</sub> and EXTV <sub>CC</sub>            |    |

| Differential Remote Sense Amplifier                  |    |

| SW Pins                                            | 22 |

|----------------------------------------------------|----|

| Temperature Monitoring (TEMP)                      | 22 |

| Fault Protection                                   | 23 |

| Thermal Considerations and Output Current Derating |    |

| Power Derating                                     | 24 |

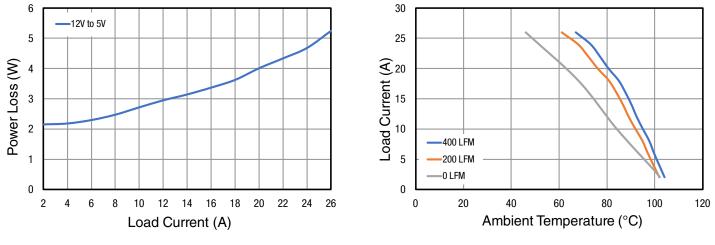

| Layout Guidelines and Example                      | 28 |

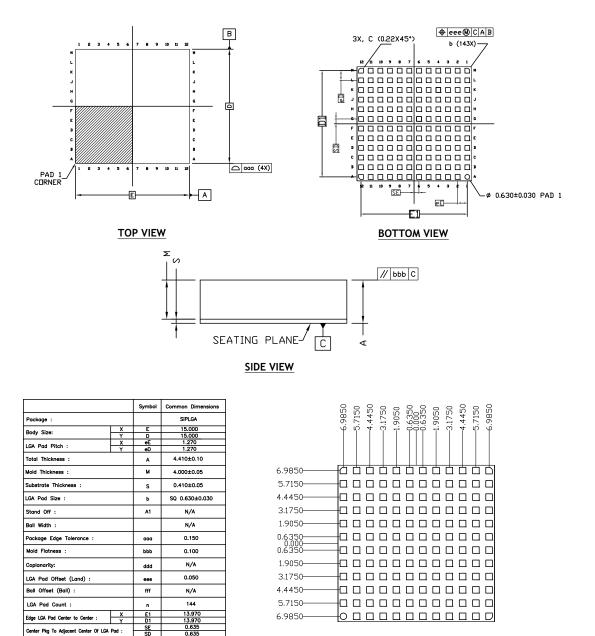

| Mechanical Dimensions                              | 29 |

| 15mm x 15mm x 4.41mm LGA                           | 29 |

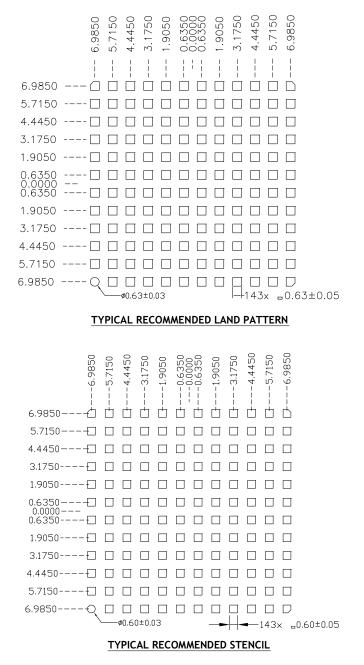

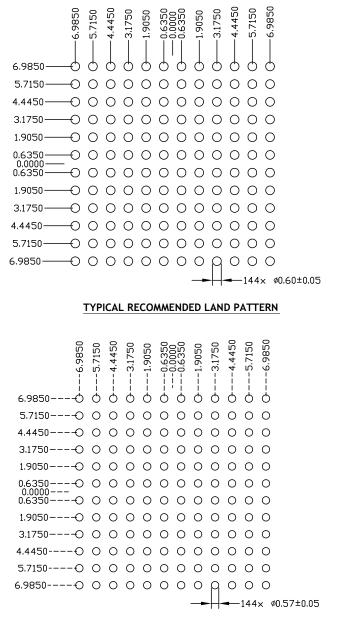

| Recommended Land Pattern and Stencil               | 30 |

| 15mm x 15mm x 4.41mm LGA                           | 30 |

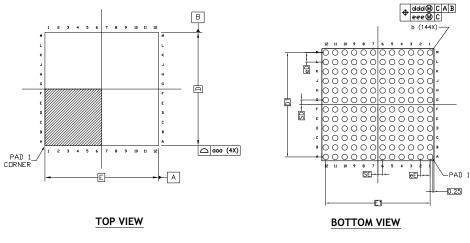

| Mechanical Dimensions                              | 31 |

| 15mm x 15mm x 5.01mm BGA                           | 31 |

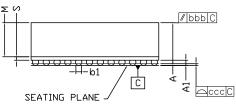

| Recommended Land Pattern and Stencil               | 32 |

| 15mm x 15mm x 5.01mm BGA                           | 32 |

| MxL7213 Component Pinout                           | 33 |

| Ordering Information                               | 34 |

# List of Figures

| Figure 1: Typical Application: 26A, 5V Output DC/DC Power Module                 | i  |

|----------------------------------------------------------------------------------|----|

| Figure 2: Efficiency Advantage vs. Competition                                   | i  |

| Figure 3: Pin Configuration                                                      | 6  |

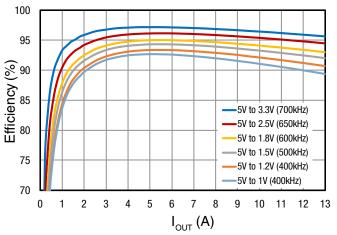

| Figure 4: Efficiency: Single Phase, V <sub>IN</sub> = 5V                         | 9  |

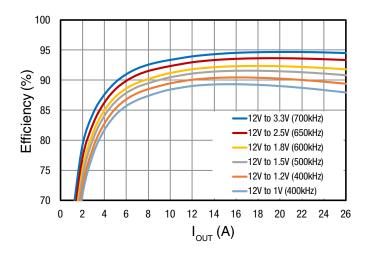

| Figure 5: Efficiency: Single Phase, V <sub>IN</sub> = 12V                        | 9  |

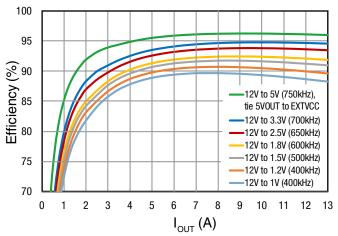

| Figure 6: Efficiency: Dual Phase, V <sub>IN</sub> = 12V                          | 9  |

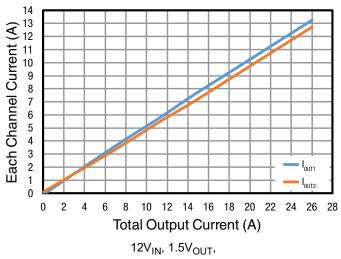

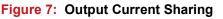

| Figure 7: Output Current Sharing                                                 | 9  |

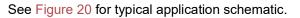

| Figure 8: 12V to 1V Load Step Response                                           | 10 |

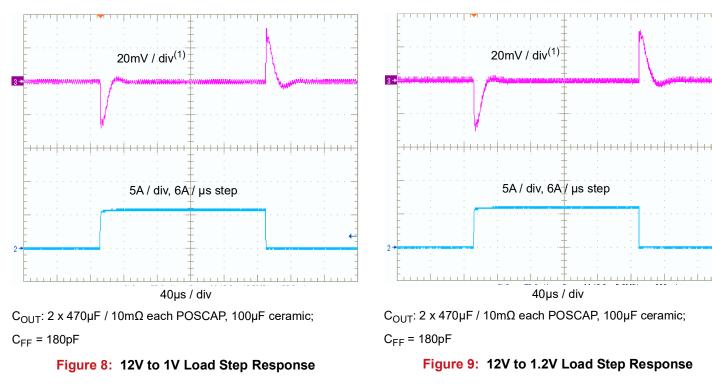

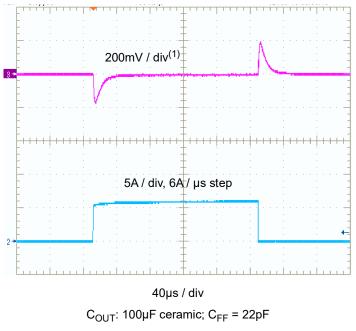

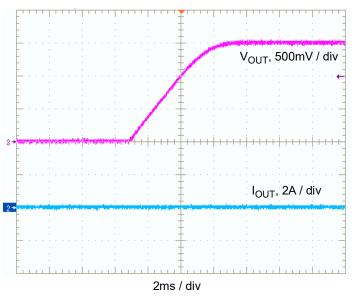

| Figure 9: 12V to 1.2V Load Step Response                                         | 10 |

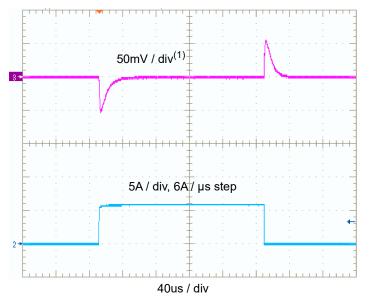

| Figure 10: 12V to 1.5V Load Step Response                                        | 10 |

| Figure 11: 12V to 1.8V Load Step Response                                        | 10 |

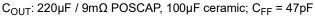

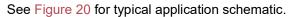

| Figure 12: 12V to 2.5V Load Step Response                                        | 11 |

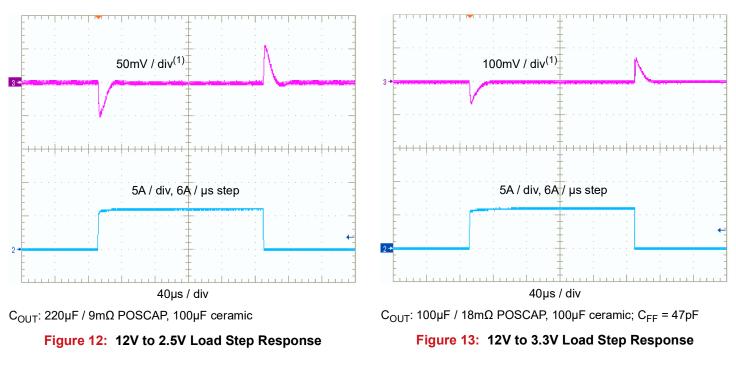

| Figure 13: 12V to 3.3V Load Step Response                                        | 11 |

| Figure 14: 12V to 5V Load Step Response                                          | 11 |

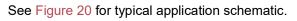

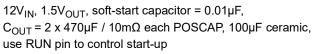

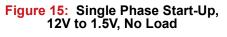

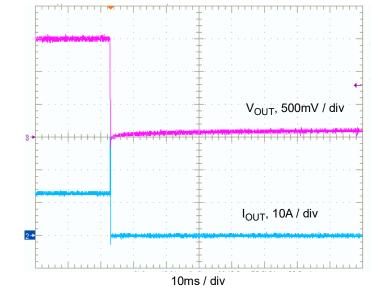

| Figure 15: Single Phase Start-Up, 12V to 1.5V, No Load                           | 12 |

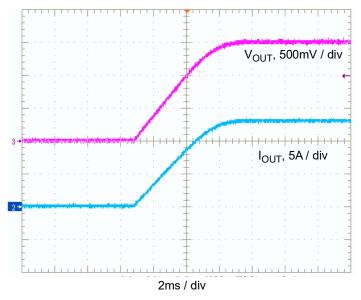

| Figure 16: Single Phase Start-Up, 12V to 1.5V, 13A Load                          | 12 |

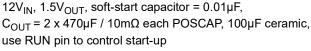

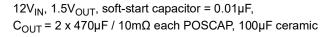

| Figure 17: Short-Circuit, 12V to 1.5V, 0A Load                                   | 12 |

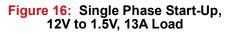

| Figure 18: Short-Circuit, 12V to 1.5V, 13A Load                                  | 12 |

| Figure 19: Functional Block Diagram                                              | 13 |

| Figure 20: Typical $5V_{IN}$ to $16V_{IN}$ , 1.5V and 1.2V Outputs               | 15 |

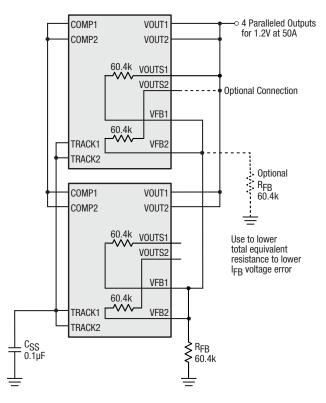

| Figure 21: 4-Phase Parallel Configuration                                        | 16 |

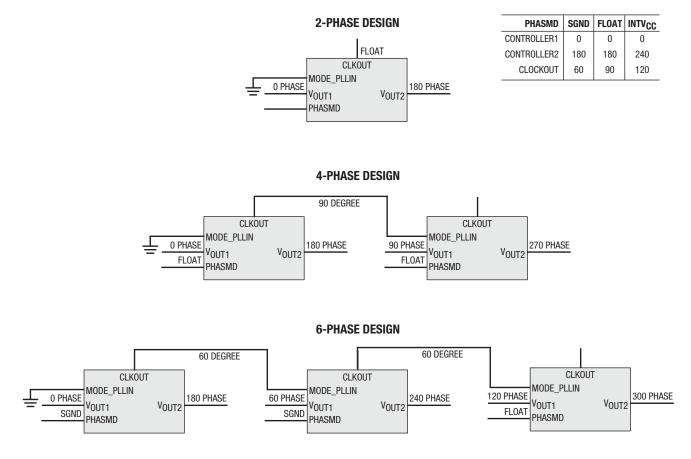

| Figure 22: Examples of 2-Phase, 4-Phase and 6-Phase Operation with PHASMD Table  | 17 |

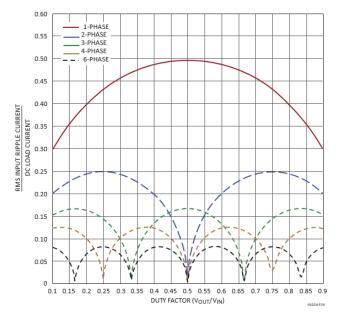

| Figure 23: Normalized Input RMS Ripple Current vs. Duty Cycle, One to Six Phases | 18 |

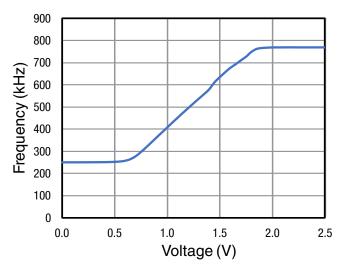

| Figure 24: Operating Frequency vs. FSET Pin Voltage                              | 18 |

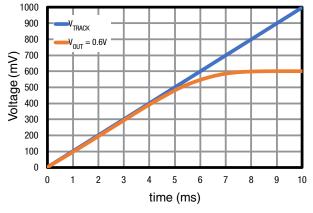

| Figure 25: V <sub>OUT</sub> and V <sub>TRACK</sub> versus Time                   | 19 |

| Figure 26: Example of Output Tracking Application Circuit                        | 20 |

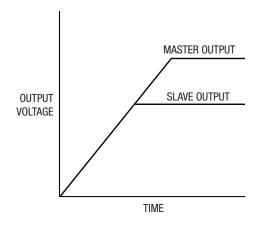

| Figure 27: Output Coincident Tracking Waveform                                   | 20 |

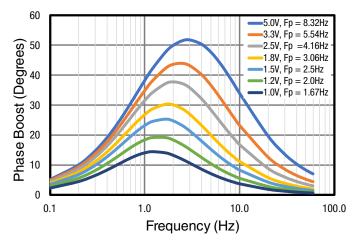

| Figure 28: C <sub>FF</sub> Phase Boost vs. Frequency Fzero Normalized to 1       | 21 |

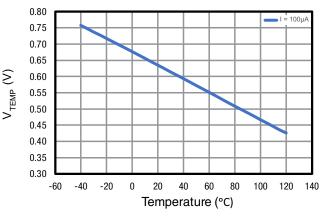

| Figure 29: Diode Voltage vs. Temperature                                         | 22 |

| Figure 30: 2-Phase, 5V at 26A with Temperature Monitoring                        | 22 |

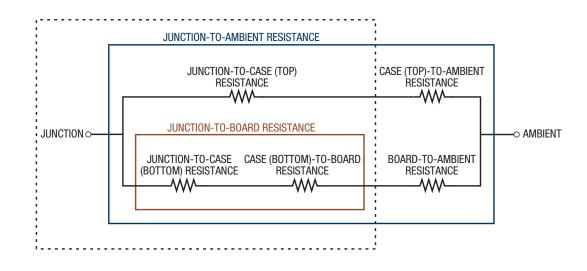

| Figure 31: Graphical Representation of Thermal Coefficients                      | 24 |

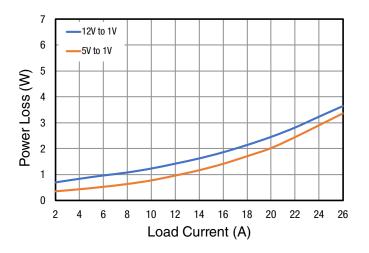

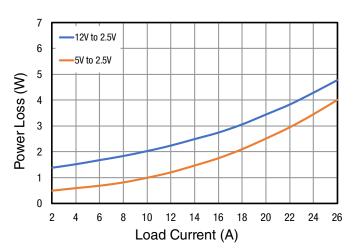

| Figure 32: Power Loss, V <sub>OUT</sub> = 1.0V                                   | 25 |

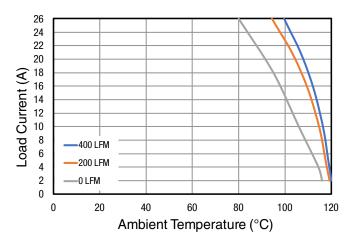

| Figure 33: Current Derating, V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 1.0V       | 25 |

| Figure 34: Current Derating, V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.0V | 25 |

|-----------------------------------------------------------------------------|----|

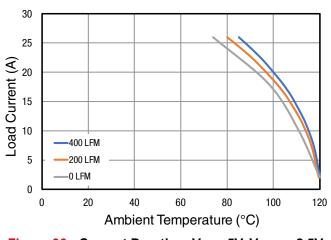

| Figure 35: Power Loss, V <sub>OUT</sub> = 2.5V                              | 25 |

| Figure 36: Current Derating, V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 2.5V  | 25 |

| Figure 37: Current Derating, V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 2.5V | 25 |

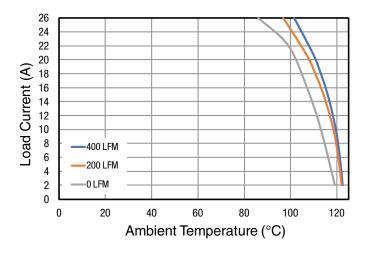

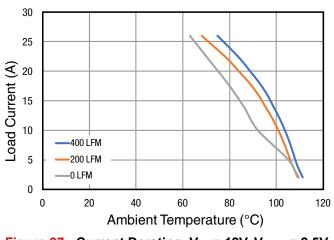

| Figure 38: Power Loss, V <sub>OUT</sub> = 5V                                | 26 |

| Figure 39: Current Derating, V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 5V   | 26 |

| Figure 40: Recommended PCB Layout                                           | 28 |

| Figure 41: Mechanical Dimensions, LGA                                       | 29 |

| Figure 42: Recommended Land Pattern and Stencil, LGA                        | 30 |

| Figure 43: Mechanical Dimensions, BGA                                       | 31 |

| Figure 44: Recommended Land Pattern and Stencil, BGA                        | 32 |

# List of Tables

| Table 1: Absolute Maximum Ratings                                         | 1  |

|---------------------------------------------------------------------------|----|

| Table 2: ESD Ratings                                                      | 1  |

| Table 3: Operating Conditions                                             | 2  |

| Table 4: Electrical Characteristics                                       | 3  |

| Table 5: Pin Description                                                  | 6  |

| Table 6: VFB Resistor Table vs. Various Output Voltages                   | 15 |

| Table 7: Θ <sub>JA</sub> and Derating Curves Corresponding to 1.0V Output | 24 |

| Table 8: Θ <sub>JA</sub> and Derating Curves Corresponding to 2.5V Output | 24 |

| Table 9: O <sub>JA</sub> and Derating Curves Corresponding to 5V Output   | 24 |

| Table 10: Capacitors Used for Output Voltage Response Matrix              | 27 |

| Table 11: Output Voltage Response vs. Component Matrix                    | 27 |

| Table 12: MxL7213 Component Pinout                                        | 33 |

| Table 13: Ordering Information                                            | 34 |

# **Specifications**

## Absolute Maximum Ratings

**Important:** The stresses above what is listed under Table 1 may cause permanent damage to the device. This is a stress rating only—functional operation of the device above what is listed under Table 1 or any other conditions beyond what MaxLinear recommends is not implied. Exposure to conditions above what is listed under Table 3 for extended periods of time may affect device reliability. Solder reflow profile is specified in the IPC/JEDEC J-STD-020C standard.

#### Table 1: Absolute Maximum Ratings

| Parameter                                                                       | Minimum | Maximum                   | Units |

|---------------------------------------------------------------------------------|---------|---------------------------|-------|

| V <sub>IN</sub>                                                                 | -0.3    | 18                        | V     |

| V <sub>SW1</sub> , V <sub>SW2</sub>                                             | -1      | 23                        | V     |

| PGOOD1, PGOOD2, COMP1, COMP2                                                    | -0.3    | 6                         | V     |

| INTV <sub>CC</sub> , EXTV <sub>CC</sub>                                         | -0.3    | 6                         | V     |

| MODE/PLLIN, f <sub>SET</sub> , TRACK1, TRACK2                                   | -0.3    | INTV <sub>CC</sub>        | V     |

| DIFFOUT                                                                         | -0.3    | INTV <sub>CC</sub> - 1.1V | V     |

| PHASMD                                                                          | -0.3    | INTV <sub>CC</sub>        | V     |

| V <sub>OUT1</sub> , V <sub>OUT2</sub> , V <sub>OUTS1</sub> , V <sub>OUTS2</sub> | -0.3    | 6                         | V     |

| DIFFP, DIFFN                                                                    | -0.3    | INTV <sub>CC</sub>        | V     |

| RUN1, RUN2, V <sub>FB1</sub> , V <sub>FB2</sub>                                 | -0.3    | INTV <sub>CC</sub>        | V     |

| INTV <sub>CC</sub> Peak Output Current                                          |         | 100                       | mA    |

| Storage Temperature Range                                                       | -65     | 150                       | °C    |

| Peak Package Body Temperature                                                   |         | 245                       | °C    |

## **ESD** Ratings

#### Table 2: ESD Ratings

| Parameter                  | Minimum | Maximum | Units |

|----------------------------|---------|---------|-------|

| HBM (Human Body Model)     |         | 2k      | V     |

| CDM (Charged Device Model) |         | 500     | V     |

# **Operating Conditions**

#### Table 3: Operating Conditions

| Parameter                                                                         | Minimum | Typical | Maximum            | Units |

|-----------------------------------------------------------------------------------|---------|---------|--------------------|-------|

| V <sub>IN</sub>                                                                   | 4.5     |         | 16                 | V     |

| INTV <sub>CC</sub>                                                                | 4.5     |         | 5.5                | V     |

| EXTV <sub>CC</sub>                                                                | 4.7     |         | 6                  | V     |

| PGOOD                                                                             | 0       |         | INTV <sub>CC</sub> | V     |

| Switching Frequency                                                               | 250     |         | 780                | kHz   |

| Junction Temperature Range (T <sub>J</sub> )                                      | -40     |         | 125                | °C    |

| Thermal Resistance from Junction to Ambient ( $\Theta_{JA}$ )                     |         | 7       |                    | °C/W  |

| Thermal Resistance from Junction to Bottom of Module Case ( $\Theta_{JCbottom}$ ) |         | 1.5     |                    | °C/W  |

| Thermal Resistance from Junction to Top of Module Case ( $\Theta_{JCtop}$ )       |         | 3.86    |                    | °C/W  |

#### **Electrical Characteristics**

Specifications are for Operating Junction Temperature of  $T_J = 25^{\circ}C$  only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$  and are provided for reference purposes only. Unless otherwise indicated,  $V_{IN} = 12V$  and  $V_{RUN1}$ ,  $V_{RUN2} = 5V$ . Per Figure 20.

#### Table 4: Electrical Characteristics

| Symbol                                                               | Parameter                                              | Conditions                                                                                                                                                                                                                                                  | •        | Min   | Тур   | Max   | Units            |

|----------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|-------|------------------|

| DC Specifications                                                    |                                                        |                                                                                                                                                                                                                                                             |          |       |       |       |                  |

| V <sub>IN(DC)</sub>                                                  | Input DC voltage                                       |                                                                                                                                                                                                                                                             | •        | 4.5   |       | 16    | V                |

| V <sub>OUT1(RANGE)</sub><br>V <sub>OUT2(RANGE)</sub>                 | Output DC range                                        | V <sub>IN</sub> = 5.5V to 16.0V                                                                                                                                                                                                                             | •        | 0.6   |       | 5.3   | V                |

| V <sub>OUT1 (DC)</sub><br>V <sub>OUT2 (DC)</sub>                     | V <sub>OUT</sub> total variation<br>with line and load | $C_{IN} = 22 \ \mu\text{F x 3}$ $C_{OUT} = 100 \ \mu\text{F x 1 Ceramic, } 220 \ \mu\text{F}$ POSCAP,<br>MODE_PLLIN = GND<br>$V_{IN} = 12V, \ V_{OUT} = 1.5V$                                                                                               | •        | 1.477 | 1.5   | 1.523 | v                |

| Input Specifications                                                 |                                                        |                                                                                                                                                                                                                                                             |          |       | I     | 1     |                  |

| V <sub>RUN1</sub> , V <sub>RUN2</sub>                                | RUN pin on/off<br>threshold                            | RUN rising                                                                                                                                                                                                                                                  |          | 1.1   | 1.25  | 1.40  | V                |

| V <sub>RUN1HYS</sub> , V <sub>RUN2HYS</sub>                          | RUN pin ON<br>hysteresis                               |                                                                                                                                                                                                                                                             |          |       | 170   |       | mV               |

| I <sub>INRUSH(VIN)</sub>                                             | Input inrush current at start-up                       | $\begin{split} &I_{OUT} = 0\text{A}, \ C_{\text{IN}} = 3 \times 22 \mu\text{F}, \ C_{\text{SS}} = 0.01 \mu\text{F}, \\ &C_{OUT} = 3 \times 100 \mu\text{F}, \ V_{OUT1} = 1.5\text{V}, \\ &V_{OUT2} = 1.5\text{V}, \ V_{\text{IN}} = 12\text{V} \end{split}$ |          |       | 0.5   |       | A                |

|                                                                      | Input supply bias current                              | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V,<br>pulse-skipping mode                                                                                                                                                                                      |          |       | 5     |       | mA               |

| I <sub>Q(VIN)</sub>                                                  |                                                        | $V_{IN}$ = 12V, $V_{OUT}$ = 1.5V, switching CCM                                                                                                                                                                                                             |          |       | 85    |       |                  |

|                                                                      |                                                        | Shutdown, RUN = 0, V <sub>IN</sub> = 12V                                                                                                                                                                                                                    |          |       | 50    |       | μA               |

| l                                                                    |                                                        | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 1.5V, I <sub>OUT</sub> = 13A                                                                                                                                                                                       |          |       | 4.34  |       | ۸                |

| I <sub>S(VIN)</sub>                                                  | Input supply current                                   | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V, I <sub>OUT</sub> = 13A                                                                                                                                                                                      |          |       | 1.82  |       | A                |

| Output Specifications                                                | -                                                      |                                                                                                                                                                                                                                                             | <b>I</b> |       | ł     | 44    |                  |

| I <sub>OUT1(DC)</sub> , I <sub>OUT2(DC)</sub>                        | Output continuous current range <sup>(1)</sup>         | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V                                                                                                                                                                                                              |          | 0     |       | 13    | А                |

| $\Delta V_{OUT1(LINE)}/V_{OUT1}$<br>$\Delta V_{OUT2(LINE)}/V_{OUT2}$ | Line regulation<br>accuracy                            | $V_{OUT}$ = 1.5V, $V_{IN}$ from 4.75V to 16V<br>$I_{OUT}$ = 0A for each output                                                                                                                                                                              | •        |       | 0.016 | 0.025 | %/V              |

| $\Delta V_{OUT1(LOAD)} V_{OUT1} \Delta V_{OUT2(LOAD)} V_{OUT2}$      | Load regulation<br>accuracy <sup>(1)</sup>             | V <sub>OUT</sub> = 1.5V, 0A to 13A, V <sub>IN</sub> = 12V                                                                                                                                                                                                   | •        |       | 0.35  | 0.5   | ±%               |

| Vout1(ac), Vout2(ac)                                                 | Output ripple voltage                                  | For each output; $I_{OUT} = 0A$ ,<br>$C_{OUT} = 100\mu F \times 3 / X7R / ceramic$ ,<br>$470\mu F POSCAP$ , $V_{IN} = 12V$ , $V_{OUT} = 1.5V$ ,<br>frequency = 400kHz                                                                                       |          |       | 26    |       | mV <sub>PP</sub> |

| f <sub>S</sub> (each channel)                                        | Output ripple voltage frequency <sup>(2)</sup>         | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V, f <sub>SET</sub> = 1.25V                                                                                                                                                                                    |          |       | 500   |       | kHz              |

| f <sub>SYNC</sub> (each channel)                                     | SYNC capture range                                     |                                                                                                                                                                                                                                                             |          | 400   |       | 780   | kHz              |

| Table 4: | (Continued) Electrical Characteristics |

|----------|----------------------------------------|

|----------|----------------------------------------|

| Symbol                                               | Parameter                                                                                              | Conditions                                                                                                                                                         | • | Min      | Тур   | Max      | Units |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-------|----------|-------|

| $\Delta V_{OUT1START}$<br>$\Delta V_{OUT2START}$     | Turn-on overshoot                                                                                      | $C_{OUT}$ = 100µF / X5R / ceramic, 470µF<br>POSCAP, V <sub>OUT</sub> = 1.5V, I <sub>OUT</sub> = 0A,<br>V <sub>IN</sub> = 12V<br>Each channel                       |   |          | 10    |          | mV    |

| t <sub>START1</sub> , t <sub>START2</sub>            | Turn-on time                                                                                           | C <sub>OUT</sub> = 100μF / X5R / ceramic,<br>470μF POSCAP, No load,<br>TRACK/SS with 0.01μF to GND, V <sub>IN</sub> = 12V<br>Each channel                          |   |          | 4.8   |          | ms    |

| $\Delta V_{OUT1(LS)}$<br>$\Delta V_{OUT2(LS)}$       | Peak deviation for<br>dynamic load                                                                     | Load: 0% to 50% to 0% of full load<br>C <sub>OUT</sub> = 22µF x 3 / X5R / ceramic,<br>470µF POSCAP, V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V<br>Each channel |   |          | 30    |          | mV    |

| t <sub>SETTLE1</sub> , t <sub>SETTLE2</sub>          | Settling time for dynamic load step                                                                    | Load: 0% to 50% to 0% of full load,<br>V <sub>IN</sub> = 12V, C <sub>OUT</sub> = 100µF, 470µF POSCAP<br>Each channel                                               |   |          | 20    |          | μs    |

| I <sub>OUT1(PK)</sub><br>I <sub>OUT2(PK)</sub>       | Output current limit                                                                                   | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.5V<br>Each channel                                                                                                     |   |          | 20    |          | А     |

| Control Section                                      |                                                                                                        |                                                                                                                                                                    | 1 | <u>I</u> | 1     | 1        |       |

| $V_{FB1}, V_{FB2}$                                   | Voltage at V <sub>FB</sub> pins                                                                        | I <sub>OUT</sub> = 0A, V <sub>OUT</sub> = 1.5V                                                                                                                     | • | 0.594    | 0.600 | 0.606    | V     |

| I <sub>FB</sub>                                      | Current at V <sub>FB</sub> pins                                                                        |                                                                                                                                                                    |   |          | -5    | -20      | nA    |

| V <sub>OVL</sub>                                     | Feedback overvoltage lockout                                                                           |                                                                                                                                                                    | • | 0.64     | 0.66  | 0.68     | V     |

| TRACK1 (I),<br>TRACK2 (I)                            | Track pin soft-start<br>pull-up current                                                                | TRACK1 (I), TRACK2 (I) start at 0V                                                                                                                                 |   | 1.1      | 1.25  | 1.4      | μA    |

| UVLO                                                 | Undervoltage lockout                                                                                   | V <sub>IN</sub> falling                                                                                                                                            |   |          | 3.66  |          | V     |

| 0010                                                 | Undervoltage lockout                                                                                   | V <sub>IN</sub> rising                                                                                                                                             |   |          | 4.25  |          | V     |

| UVLO Hysteresis                                      |                                                                                                        |                                                                                                                                                                    |   |          | 600   |          | mV    |

| t <sub>ON(MIN)</sub>                                 | Minimum on-time                                                                                        |                                                                                                                                                                    |   |          | 90    |          | ns    |

| R <sub>FBHI1</sub> , R <sub>FBHI2</sub>              | Resistor between<br>V <sub>OUTS1</sub> , V <sub>OUTS2</sub> and<br>V <sub>FB1</sub> , V <sub>FB2</sub> | Each output                                                                                                                                                        |   | 60.05    | 60.4  | 60.75    | kΩ    |

| V <sub>PGOOD1 LOW</sub> ,<br>V <sub>PGOOD2 LOW</sub> | PGOOD voltage low                                                                                      | I <sub>PGOOD</sub> = 2mA                                                                                                                                           |   |          | 35    | 50       | mV    |

| I <sub>PGOOD</sub>                                   | PGOOD leakage current                                                                                  | V <sub>PGOOD</sub> = 5V                                                                                                                                            |   |          |       | ±5       | μA    |

| V <sub>PGOOD</sub>                                   |                                                                                                        | V <sub>FB</sub> with respect to set output voltage<br>V <sub>FB</sub> ramping negative                                                                             |   |          | -10   |          | %     |

|                                                      | PGOOD trip level                                                                                       | V <sub>FB</sub> with respect to set output voltage<br>V <sub>FB</sub> ramping positive                                                                             |   |          | 10    |          |       |

| INTV <sub>CC</sub> Linear Regul                      | lator                                                                                                  |                                                                                                                                                                    | 1 |          |       | <u> </u> |       |

| V <sub>INTVCC</sub>                                  | Internal V <sub>CC</sub> voltage                                                                       | 6V < V <sub>IN</sub> < 16V                                                                                                                                         |   | 4.8      | 5     | 5.2      | V     |

| V <sub>INTVCC</sub><br>Load Regulation               | INTV <sub>CC</sub> load<br>regulation                                                                  | I <sub>CC</sub> = 0mA to 50mA                                                                                                                                      |   |          | 1     | 2        | %     |

| Symbol                    | Parameter                                 | Conditions                                                                        | • | Min                         | Тур   | Max                                                | Units |

|---------------------------|-------------------------------------------|-----------------------------------------------------------------------------------|---|-----------------------------|-------|----------------------------------------------------|-------|

| V <sub>EXTVCC</sub>       | EXTV <sub>CC</sub> switchover voltage     | EXTV <sub>CC</sub> ramping positive                                               | • | 4.5                         | 4.7   |                                                    | V     |

| V <sub>EXTVCC(DROP)</sub> | EXTV <sub>CC</sub> dropout                | I <sub>CC</sub> = 20mA, V <sub>EXTVCC</sub> = 5V                                  |   |                             | 19    | 50                                                 | mV    |

| V <sub>EXTVCC(HYST)</sub> | EXTV <sub>CC</sub> hysteresis             |                                                                                   |   |                             | 156   |                                                    | mV    |

| Oscillator and Phase-I    | Locked Loop                               | 1                                                                                 |   |                             |       | 1                                                  |       |

| Frequency Nominal         | Nominal frequency                         | FSET = 1.2V                                                                       |   | 450                         | 500   | 550                                                | kHz   |

| Frequency Low             | Lowest frequency                          | FSET = 0V                                                                         |   | 210                         | 250   | 290                                                | kHz   |

| Frequency High            | Highest frequency                         | FSET > 2.4V, up to INTV <sub>CC</sub>                                             |   | 700                         | 780   | 860                                                | kHz   |

| I <sub>FSET</sub>         | Frequency set current                     |                                                                                   |   | 9                           | 10    | 11                                                 | μA    |

| f <sub>SYNC</sub>         | SYNC capture range                        | Each channel                                                                      |   | 250                         |       | 780                                                | kHz   |

| R <sub>MODE_PLLIN</sub>   | MODE_PLLIN input resistance               |                                                                                   |   |                             | 250   |                                                    | kΩ    |

|                           |                                           | PHASMD = GND                                                                      |   |                             | 60    |                                                    | Deg   |

| CLKOUT                    | Phase (relative to<br>V <sub>OUT1</sub> ) | PHASMD = float                                                                    |   |                             | 90    | 50<br>550<br>290<br>860<br>11<br>780<br>0.2<br>0.2 | Deg   |

|                           | VOUT1)                                    | PHASMD = INTV <sub>CC</sub>                                                       |   |                             | 120   |                                                    | Deg   |

| CLK High                  | Clock High output voltage                 |                                                                                   |   | 2                           |       |                                                    | V     |

| CLK Low                   | Clock Low output voltage                  |                                                                                   |   |                             |       | 0.2                                                | V     |

| Differential Amplifier    |                                           |                                                                                   |   |                             |       | 1                                                  | 1     |

| A <sub>V</sub>            | Gain                                      |                                                                                   |   |                             | 1     |                                                    | V/V   |

| R <sub>IN</sub>           | Input resistance                          | Measured at DIFFP Input                                                           |   |                             | 80    |                                                    | kΩ    |

| V <sub>OS</sub>           | Input offset voltage                      | V <sub>DIFFP</sub> = V <sub>DIFFOUT</sub> = 1.5V, I <sub>DIFFOUT</sub> =<br>100µA |   |                             |       | 2                                                  | mV    |

| PSRR                      | Power Supply<br>Rejection Ratio           | 5V < V <sub>IN</sub> < 16V                                                        |   |                             | 90    |                                                    | dB    |

| I <sub>CL</sub>           | Maximum Output<br>current                 |                                                                                   |   |                             | 3     |                                                    | mA    |

| V <sub>DIFFOUT(MAX)</sub> | Maximum output<br>voltage                 | I <sub>DIFFOUT</sub> = 300µA                                                      |   | INTV <sub>CC</sub><br>- 1.4 |       |                                                    | V     |

| GBW                       | Gain Bandwidth<br>Product                 |                                                                                   |   |                             | 3     |                                                    | MHz   |

| V <sub>TEMP</sub>         | Diode Connected PNP                       | Ι = 100μΑ                                                                         |   |                             | 0.636 |                                                    | V     |

| TC <sub>VTEMP</sub>       | Temperature<br>Coefficient                |                                                                                   | • |                             | -2.2  |                                                    | mV/°C |

| ОТ                        | Thermal shutdown threshold                | Rising temperature                                                                |   |                             | 145   |                                                    | °C    |

|                           | Thermal hysteresis                        |                                                                                   |   |                             | 15    |                                                    | °C    |

1. See output current derating curves for different V<sub>IN</sub>, V<sub>OUT</sub> and T<sub>A</sub>. 2. The switching frequency is programmable from 250kHz to 780kHz.

INTVCC SW2

PGOOD1 PGOOD2 RUN2

DIFFOUT DIFFP DIFFN

GND

VOUT2

12

# **Pin Information**

# **Pin Configuration**

LGA, Top View 144-Lead 15mm x 15mm x 4.41mm

10 11 BGA, Top View 144-Lead 15mm x 15mm x 5.01mm

TEMP

SGND

COMP1 COMP2

SGND VFB2 TRACK2

FSET SGND VOUTS

GND

6 7 8 q

RUN1

5

Μ

G

F

F

D

С

В

1 2 3 4

VOUT1

CLKOUT SW1 Н

PHASMD

TRACK1 VFB1

VOUTS1

MODE\_PLLIN

EXTVCC

## **Pin Description**

#### Table 5: Pin Description

| Pin Number                                                                                                                                                                                                                                                                   | Pin Name | Description                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2, A3, A4, A5,<br>B1, B2, B3, B4, B5,<br>C1, C2, C3, C4                                                                                                                                                                                                                 | VOUT1    | Output of the channel 1 power stage. Connect the corresponding output load from the VOUT1 pins to the PGND pins. Direct output decoupling capacitance from VOUT1 to PGND is recommended. |

| A6, A7, B6, B7,<br>D1, D2, D3, D4,<br>D9, D10, D11, D12,<br>E1, E2, E3, E4,<br>E10, E11, E12,<br>F1, F2, F3,<br>F10, F11, F12,<br>G1, G3, G10, G12,<br>H1, H2, H3, H4, H5, H6,<br>H7, H9, H10, H11, H12,<br>J1, J5, J8, J12,<br>K1, K5, K6, K7, K8, K12,<br>L1, L12, M1, M12 | GND      | Ground for the power stage. Connect to the application's power ground plane.                                                                                                             |

| A8, A9, A10, A11, A12,<br>B8, B9, B10, B11, B12,<br>C9, C10, C11, C12                                                                                                                                                                                                        | VOUT2    | Output of the channel 2 power stage. Connect the corresponding output load from the VOUT2 pins to the PGND pins. Direct output decoupling capacitance from VOUT2 to PGND is recommended. |

#### Table 5: Pin Description (Continued)

| Pin Number             | Pin Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C5, C8                 | VOUTS1,<br>VOUTS2 | These pins are connected internally to the top of the feedback resistor for each output.<br>Connect this pin directly to its specific output or to DIFFOUT when using the remote sense<br>amplifier. When paralleling modules, connect one of the VOUTS pins to DIFFOUT when<br>remote sensing or directly to VOUT when not remote sensing. These pins must be<br>connected to either DIFFOUT or VOUT. This connection provides the feedback path and<br>cannot be left open.              |

| C6                     | FSET              | <ul> <li>This pin is used to set the operating frequency via two methods:</li> <li>Connect a resistor from this pin to ground</li> <li>Drive this pin with a DC voltage</li> <li>This pin sources a 10µA current. See Figure 24 for frequency of operation vs. FSET voltage.</li> </ul>                                                                                                                                                                                                    |

| C7, D6, G6, G7, F6, F7 | SGND              | Ground pin for all analog signals and low power circuits. Connect to GND in one place. See layout guidelines in Figure 40.                                                                                                                                                                                                                                                                                                                                                                 |

| D5, D7                 | VFB1, VFB2        | Feedback input to the negative side of the error amplifier for each channel. These pins are each internally connected to VOUTS1 and VOUTS2 via a precision $60.4k\Omega$ resistor. Vary each output voltage by adding a feedback resistor from VFB to SGND. Tie VFB1 and VFB2 together for parallel operation.                                                                                                                                                                             |

| E5, D8                 | TRACK1,<br>TRACK2 | Soft-Start and Output Voltage Tracking pins. Each channel has a 1.25µA pull-up current source. When one channel is configured as a master, adding a capacitor from this pin to ground sets a soft-start ramp rate. The other channel can be set up as the slave and have the master output applied through a voltage divider to the slave's output TRACK pin. For coincidental tracking, this voltage divider is equal to the slave's output feedback divider.                             |

| E6, E7                 | COMP1,<br>COMP2   | Current control threshold and error amplifier compensation point for each channel. The current comparator threshold increases with this control voltage. The MxL7213 is internally compensated, however a feed-forward $C_{FF}$ is frequently required (see Table 11). $R_{COMP}$ and $C_{COMP}$ may be required for certain operating conditions (see Figure 20). When paralleling both channels, connect the COMP1 and COMP2 pins together.                                              |

| E8                     | DIFFP             | This pin is the remote sense amplifier's positive input and is connected to the output voltage's remote sense point. If the remote sense amplifier is not used, connect this pin to SGND. Important: The differential amplifier cannot be used for outputs > 3.3V.                                                                                                                                                                                                                         |

| E9                     | DIFFN             | This pin is the remote sense amplifier's negative input and is connected to the remote sense point GND. If the remote sense amplifier is not used, connect this pin to SGND. Important: The differential amplifier cannot be used for outputs >3.3V.                                                                                                                                                                                                                                       |

| F4                     | MODE_PLLIN        | <ul> <li>Selects between Forced Continuous Mode or Pulse-Skipping Mode and provides the external synchronization input to the Phase Detector Pin. There are three connection options:</li> <li>1. Connect this pin to SGND to force both channels into Forced Continuous Mode.</li> <li>2. Connect this pin to INTVCC or leave it floating to enable Pulse-Skipping Mode.</li> <li>3. Connect this pin to an external clock to force both channels into Forced Continuous Mode.</li> </ul> |

| F5, F9                 | RUN1, RUN2        | <ul> <li>The RUN1 and RUN2 pins enable and disable the module's two channels:</li> <li>A voltage above 1.4V will turn on the related channel.</li> <li>A voltage below 1.1V will turn off the related channel.</li> <li>Each RUN pin has a 1µA pull-up current; once the RUN pin reaches ~1.25V, an additional 4.5µA pull-up current is added to the RUN pin.</li> </ul>                                                                                                                   |

| F8                     | DIFFOUT           | Output of the internal remote sense amplifier. If remote sensing on channel 1, connect to VOUTS1. If remote sensing on channel 2, connect to VOUTS2. When paralleling modules, connect one of the VOUTS pins to DIFFOUT when remote sensing. Important: The differential amplifier cannot be used for outputs >3.3V.                                                                                                                                                                       |

#### Table 5: Pin Description (Continued)

| Pin Number                                                                                                                                            | Pin Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G2, G11                                                                                                                                               | SW1, SW2          | Use these pins to access the switching node of each channel. An RC snubber can be connected to reduce switch node ringing. Otherwise, leave these pins floating.                                                                                                                                                                                                                                                                                                                                                               |

| G4                                                                                                                                                    | PHASMD            | <ul> <li>This pin selects the CLKOUT phase as follows:</li> <li>Connect to SGND for 60 degrees</li> <li>Connect to INTVCC for 120 degrees</li> <li>Leave floating for 90 degrees</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

| G5                                                                                                                                                    | CLKOUT            | This is the clock output. Its phase is set with the PHASMD pin. It is also used during Multiphase Operation. Refer to the Application Section on Multiphase Operation for more details.                                                                                                                                                                                                                                                                                                                                        |

| G9, G8                                                                                                                                                | PGOOD1,<br>PGOOD2 | Power Good outputs. This open-drain output is pulled low when the $V_{OUT}$ of its respective channel is more than ±10% outside regulation.                                                                                                                                                                                                                                                                                                                                                                                    |

| H8                                                                                                                                                    | INTVCC            | Internal 5V Regulator Output. This voltage powers the control circuits and internal gate driver. Decouple to GND with a $4.7\mu$ F ceramic capacitor. INTVCC is activated when either RUN1 or RUN2 is activated.                                                                                                                                                                                                                                                                                                               |

| J6                                                                                                                                                    | TEMP              | The internal temperature sensing diode monitors the temperature change with voltage change on $V_{BE}$ . Connect to VIN through a resistor to limit the current to 100µA.<br>R = ( $V_{IN}$ - 0.6V) / 100µA                                                                                                                                                                                                                                                                                                                    |

| J7                                                                                                                                                    | EXTVCC            | External power input that is enabled through a switch to INTVCC whenever EXTVCC is >4.7V. Do not exceed 6V on this input. Connect this pin to $V_{IN}$ when operating $V_{IN}$ on 5V. An efficiency increase that is a function of ( $V_{IN}$ - INTV <sub>CC</sub> ) multiplied by the power MOSFET driver current occurs when the feature is used. $V_{IN}$ must be applied before EXTV <sub>CC</sub> , and EXTV <sub>CC</sub> must be removed before $V_{IN}$ . To increase efficiency, a 5V output can be tied to this pin. |

| M2, M3, M4, M5, M6, M7,<br>M8, M9, M10, M11,<br>L2, L3, L4, L5, L6, L7, L8,<br>L9, L10, L11,<br>J2, J3, J4, J9, J10, J11,<br>K2, K3, K4, K9, K10, K11 | VIN               | Power input pins. Connect input voltage from these pins to GND. Direct input decoupling capacitance from VIN to GND is recommended.                                                                                                                                                                                                                                                                                                                                                                                            |

1. Use test points to monitor signal pin connections.

# **Typical Performance Characteristics**

See Figure 20 for typical application schematic.

**Figure 4:** Efficiency: Single Phase,  $V_{IN} = 5V$

Figure 6: Efficiency: Dual Phase, V<sub>IN</sub> = 12V

Figure 5: Efficiency: Single Phase, V<sub>IN</sub> = 12V

$C_{OUT} = 2 \times 470 \mu F / 10 m \Omega$  each POSCAP, 100  $\mu$ F ceramic

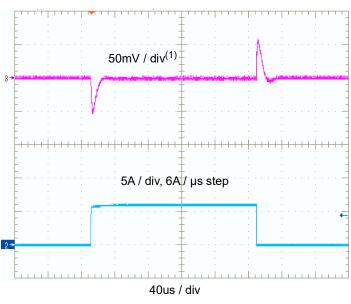

$C_{OUT}$ : 220µF / 9m $\Omega$  POSCAP, 100µF ceramic;  $C_{FF}$  = 100pF,

#### Figure 10: 12V to 1.5V Load Step Response

1. Waveform averaged to remove high frequency ripple.

Figure 11: 12V to 1.8V Load Step Response

Figure 14: 12V to 5V Load Step Response

1. Waveform averaged to remove high frequency ripple.

Figure 18: Short-Circuit, 12V to 1.5V, 13A Load

$12V_{IN},~1.5V_{OUT},~soft-start~capacitor$  =  $0.01\mu F,$   $C_{OUT}$  = 2 x 470 $\mu F$  /  $10m\Omega$  each POSCAP, 100 $\mu F$  ceramic

Figure 17: Short-Circuit, 12V to 1.5V, 0A Load

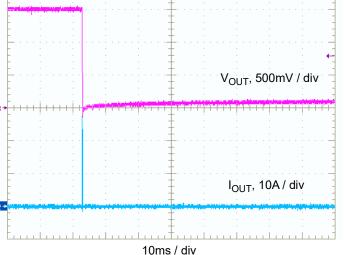

## **Functional Block Diagram**

Figure 19: Functional Block Diagram

# Operation

#### **Power Module Description**

The MxL7213 is a dual-channel, standalone, synchronous step-down power module that provides two 13A outputs or one 26A output. This power module has a continuous input voltage range of 4.5V to 16V and has been optimized for 12V conversions. It provides precisely regulated output voltages from 0.6V to 5.3V that are set by a single external resistor. See typical application schematic in Figure 20.

The module employs a constant frequency, peak current mode control loop architecture. It also has an internal feedback loop compensation. These features ensure the MxL7213 has sufficient stability margins as well as good transient performance over a wide range of output capacitors, including low ESR ceramic capacitors.

The peak current mode control supports cycle-by-cycle fast current limit and current limit hiccup in overcurrent or output short circuit conditions. The open-drain PGOOD outputs are pulled low when the output voltage exceeds  $\pm 10\%$  of its set point. Once the output voltage exceeds  $\pm 10\%$ , the high side MOSFET is kept off while the low side MOSFET turns on, clamping the output voltage. The overvoltage and undervoltage detection are referenced to the feedback pin.

The RUN1 and RUN2 pins enable and disable the module's two channels. Pulling a RUN pin below 1.1V forces the respective regulator into shutdown mode and turns off both the high side and low side MOSFETs. The TRACK pins are used for either programming the output voltage ramp and voltage tracking during start-up, or for soft-starting the channels.

The MxL7213 includes a differential remote sense amplifier (with a gain of +1). This amplifier can be used to accurately sense the voltage at the load point on one of the module's two outputs or on a single parallel output.

The switching frequency is programmed from 250kHz to 780kHz using an external resistor on the FSET pin. For noise sensitive applications, the module can be synchronized to an external clock.

The MxL7213 module can be configured to current share between channels. It can also be set to current share between modules (multiphase or ganged operation). Using the MODE\_PLLIN, PHASMD and CLKOUT pins, multiphase operation of up to 8 phases is possible with multiple MxL7213s running in parallel.

Using the the MODE\_PLLIN pin to operate in pulseskipping mode results in high efficiency performance at light loads. This light load feature extends battery life.

The EXTVCC pin allows an external 5V supply to power the module and reduce the power dissipation in the internal 5V LDO. EXTVCC has a threshold of 4.7V for activation and a max rating of 6V. It must sequence on after  $V_{IN}$  and sequence off before  $V_{IN}$ .

Monitor the internal die temperature by using the TEMP pin. Pull the anode up to  $V_{\text{IN}}$  through an external resistor to set the bias current in the diode. Thermal simulation has shown that the thermal monitor on the controller die is within 5°C of the MOSFETs.

## **Applications Information**

## **Typical Application Circuit**

The typical MxL7213 application circuit is shown in Figure 20. External component selection is primarily determined by the maximum load current and output voltage. Refer to Table 11 for a selection of various design solutions. Additional information about selecting external compensation components can be found in the Stability and Compensation section.

## $V_{IN}$ to $V_{OUT}$ Step-Down Ratios

For a given input voltage, there are limitations to the maximum possible  $V_{\rm IN}$  and  $V_{\rm OUT}$  stepdown ratios.

The MxL7213 has a maximum duty cycle of 90% at 500kHz, meaning the maximum output voltage will be approximately 0.9 x V<sub>IN</sub>. When running at high duty cycle, output current can be limited by the power dissipation in the high-side MOSFET. The minimum output voltage from a given input is controlled by the minimum on-time which is 90ns. The minimum output voltage is V<sub>IN</sub> x f<sub>SW</sub>(MHz) x 0.09 $\mu$ s. To get a lower output voltage, reduce the switching frequency.

1. See Table 11.

2. May be necessary for certain operating conditions.

## **Output Voltage Programming**

The PWM controller has an internal 0.6V reference. A resistor R<sub>FB</sub> between the VFB and SGND pins programs the output voltage. A 60.4k $\Omega$  internal feedback resistor is connected from VOUTS1 to VFB1 and from VOUTS2 to VFB2, as illustrated in the functional block diagram.

$R_{FB}$  values for corresponding standard  $V_{OUT}$  values are shown in Table 6. Use the following equation to determine the RFB value for other VOUT levels:

$$V_{OUT} = \frac{0.6 \times (60.4 + R_{FB})}{R_{FB}}$$

When paralleling multiple channels and devices, a common  $R_{FB}$  resistor may be used. Select the  $R_{FB}$  as explained above. Note that VFB pins have an  $I_{FB}$  max of 20nA per channel. To reduce  $V_{OUT}$  error due to  $I_{FB}$ , use an additional  $R_{FB}$  and connect corresponding VOUTS to VOUT as shown in Figure 21.

When paralleling multiple channels and devices:

Tie all COMP pins together for current sharing between the phases.

- Tie the TRACK pins together and use a single soft-start capacitor to soft-start the regulator.

- Increase the soft-start current parameter by the number of paralleled channels when solving the softstart equation. (Refer to the Soft Start and Output Voltage Tracking section).

| Table 6: VFB Resistor Table vs. | Various Output Voltages |

|---------------------------------|-------------------------|

|---------------------------------|-------------------------|

| V <sub>OUT</sub> | 0.6V | 1.0V  | 1.2V  | 1.5V  | 1.8V  | 2.5V  | 3.3V  | 5V    |

|------------------|------|-------|-------|-------|-------|-------|-------|-------|

| $R_{FB}$         | Open | 90.9k | 60.4k | 40.2k | 30.2k | 19.1k | 13.3k | 8.25k |

## **Input Capacitors**

Connect the MxL7213 to a low impedance DC source. Use four  $22\mu$ F ceramic input capacitors to reduce RMS ripple current on the regulator input.

A bulk input capacitor is required if the source impedance is high or the source capacitance is low. For additional bulk input capacitance, use a surface mount  $47\mu$ F to  $100\mu$ F aluminum electrolytic bulk capacitor.

## **Output Capacitors**

The bulk output capacitors, denoted as  $C_{OUT}$ , need to have low enough effective series resistance (ESR) to meet output voltage ripple and transient requirements. The MxL7213 can use low ESR tantalum capacitors, low ESR polymer capacitors, ceramic capacitors or a combination for  $C_{OUT}$ . Refer to Table 11 for  $C_{OUT}$  recommendations that optimize performance for different output voltages.

## Pulse-Skipping Mode Operation

Pulse-skipping mode enables the module to skip cycles at light loads which reduces switching losses and increases efficiency at low to intermediate currents. To enable this mode, connect the MODE\_PLLIN pin to the INTVCC pin.

## Forced Continuous Operation

Forced continuous operation is recommended when fixed frequency is more important than light load efficiency, and when the lowest output ripple is desired. To enable this mode, connect the MODE\_PLLIN pin to GND.

## **Multiphase Operation**

Multiphase operation is used to achieve output currents greater than 13A. It can be used with both MxL7213 channels to achieve one 26A output. It can also be used by paralleling multiple MxL7213s and running them out of phase to attain one single high current output, up to 100A. Ripple current in both the input and output capacitors is substantially lower using a multiphase design when the number of phases multiplied by the output voltage is less than the input voltage. Input RMS ripple current and output ripple amplitude is reduced by the number of phases used while the effective ripple frequency is multiplied by the number of phases used. The MxL7213 is a peak current mode controlled device which results in very good current sharing between parallel modules and balances the thermal loading.

Up to 8 phases can be paralleled by using each MxL7213 channel's PHASMD, MODE\_PLLIN and CLKOUT pins. When the CLKOUT pin is connected to the following stage's MODE\_PLLIN pin, the frequency and the phase of both devices are locked. Phase difference can be obtained between MODE\_PLLIN and CLKOUT of 120 degrees, 60 degrees or 90 degrees respectively by connecting the PHASMD pin to INTVCC, SGND or left floating. Figure 21

shows an example of parallel operation and Figure 22 shows examples of 2-phase, 4-phase and 6-phase designs.

Figure 21: 4-Phase Parallel Configuration

Figure 22: Examples of 2-Phase, 4-Phase and 6-Phase Operation with PHASMD Table

# Input RMS Ripple Current Cancellation

Figure 23 illustrates the RMS ripple current reduction that is expected as a function of the number of interleaved phases.

Figure 23: Normalized Input RMS Ripple Current vs. Duty Cycle, One to Six Phases

# Frequency Selection and Phase-Lock Loop

To increase efficiency, the MxL7213 works over a range of frequencies. For lower output voltages or duty cycles, lower frequencies are recommended to lower MOSFET switching losses and improve efficiency. For higher output voltages or duty cycles, higher frequencies are recommended to limit inductor ripple current. Refer to the efficiency graphs and their operating frequency, keep the highest output voltage in mind.

Use an external resistor between the FSET pin and SGND to set the switching frequency. An accurate  $10\mu$ A current source into the resistor sets a voltage that programs the frequency. Alternately, a DC voltage can be applied to FSET to program the frequency. Figure 24 illustrates the operating frequency versus FSET pin voltage.

An external clock with a frequency range of 250kHz to 780kHz and a voltage range of 0V to  $INTV_{CC}$  can be connected to the MODE\_PLLIN pin. The high level threshold of the clock input is 1.6V and the low level threshold of the clock input is 1V.

The MxL7213 integrates the PLL loop filter components. Ensure that the initial switching frequency is set with an external resistor before locking to an external clock. Both regulators will operate in continuous mode while being synchronized to an external clock signal.

The PLL phase detector output charges and discharges the internal filter network with a pair of complementary current sources. When an external clock is connected, an internal switch disconnects the external FSET frequency resistor. The switching frequency then locks to the incoming external clock. If no external clock is connected, then the internal switch is on, which connects the external FSET frequency set resistor.

Figure 24: Operating Frequency vs. FSET Pin Voltage

#### Minimum On-Time

Minimum On-Time  $t_{ON(MIN)}$  is the shortest time the controller can turn on the high-side MOSFET of either channel. Approaching this time may be more of an issue in low duty cycle applications. Use the following equation to make sure the on-time is above this minimum:

$$\frac{V_{OUT}}{V_{IN} \times FREQ} > t_{ON(MIN)}$$

If the on-time falls below this minimum, the channel will start to skip cycles. In this case, the output voltage continues to regulate, however output ripple increases. Lowering the switching frequency increases on-time. Minimum on-time specified in the electrical characteristics is 90ns.

# Soft Start and Output Voltage Tracking

A capacitor  $C_{SS}$  can be connected from the TRACK pin to ground to implement soft start. The TRACK pin is charged by a 1.25µA current source up to the reference voltage and then on to INTV<sub>CC</sub>. The MxL7213 has a smooth transition from TRACK to V<sub>OUT</sub> as shown in Figure 25. If the RUN pin is below 1.2V, the TRACK pin is pulled low. The following equation can be used to calculate soft-start time, defined as when PGOOD asserts:

$$t_{SOFTSTART} = \left(\frac{C_{SS}}{1.25\mu A}\right) \times 0.65 V$$

Figure 25: V<sub>OUT</sub> and V<sub>TRACK</sub> versus Time

The MODE\_PLLIN pin selects between forced continuous mode or pulse-skipping mode during steady-state operation. Regardless of the mode selected, the module channels will always start in pulse-skipping mode up to TRACK = 0.5V. Between TRACK = 0.5V and 0.54V, it will operate in forced continuous mode. Once TRACK > 0.54V, it will follow the selected mode.

The TRACK pins can be used to externally program the output voltage tracking. The output may be tracked up and down with another regulator. The master regulator's output is divided down with an external resistor divider that is the same as the slave regulator's feedback divider to implement coincident tracking. Note that each MxL7213 channel has an internal accurate  $60.4k\Omega$  for the top feedback resistor. Refer to the equation below, which is applicable for V<sub>TRACK(SLAVE)</sub> < 0.8V. An example of coincident tracking is shown in Figure 26.

$$V_{OUT(SLAVE)} = \left(1 + \frac{60.4k}{R_{TA}}\right) \times V_{TRACK(SLAVE)}$$

Figure 26: Example of Output Tracking Application Circuit

#### Figure 27: Output Coincident Tracking Waveform

The ramping voltage is applied to the track pin of the slave. Since the same resistor values are used to divide down the output of the master and to set the output of the slave, the slave tracks with the master coincidentally until its final value it achieved. The master continues from the slave's regulation point to its final value. In Figure 26,  $R_{TA}$  is equal to  $R_{FB2}$  for coincident tracking.

Ratiometric power up can be implemented by tying the TRACK pins together and connecting a capacitor from TRACK to ground. For existing designs where this is not

possible, populate  $R_{TA}$  with the same capacitor as the master's TRACK capacitor and do not populate  $R_{TB}$ . Capacitors with 10% accuracy are recommended.

## Power Good

Each channel's open drain PGOOD pin can be used to monitor if its respective  $V_{OUT}$  is outside ±10% of the set point. The PGOOD pin is pulled low when the output of either channel is outside the monitoring window, the RUN pin is below its threshold (1.25V), or the MxL7213 is in the soft start or tracking phase. The PGOOD pin will flag power good immediately when both VFB pins are within the monitoring window. Note that there is an internal 20µs delay when VFB voltage goes out of the monitoring window.

If desired, a pull up resistor can be connected from the PGOOD pins to a supply voltage with a maximum level of  $\leq 6V$ .

## Stability and Compensation

The MxL7213 is internally compensated across the range of all input and output voltages so additional compensation is not typically required. Table 11 covers most application requirements.

For low output capacitance or low output voltage applications, sometimes a reasonable loop bandwidth and improved phase margin can be obtained by adding a series R-C circuit between the COMP pin and SGND.

#### Additional Compensation Information

When the loop gain crosses 0dB at a slope steeper than -20dB / decade, the phase margin sometimes can be inadequate. This is when a small  $C_{FF}$  capacitor may offer some help. This  $C_{FF}$  capacitor is connected between the VOUTS and FB pins and is in parallel with the 60.4k $\Omega$  internal upper feedback resistor. The  $C_{FF}$ , together with the upper and lower feedback resistors, form a lead compensation network that inserts a "Zero" in the loop at a frequency followed by a "Pole" at a higher frequency. This gives the loop a phase boost mainly between the Zero and Pole frequencies.

$C_{FF}$ , in conjunction with the upper 60.4k feedback resistor located inside the module, creates a feedback "Zero" (Fz).

$$Fz = \frac{1}{2 \times \pi \times 60400 \times C_{FF}}$$

This added zero makes it easier for high frequency signals to pass from the output back to the FB pin which helps boost the loop's phase margin.

The "Pole" in the lead compensation network can be calculated as:

$$Fp = \frac{60400 + R_{FB}}{2\pi \times 60400 \times R_{FB} \times C_{FF}}$$