**JANUARY 2020**

## **GENERAL DESCRIPTION**

The SP510E is a highly integrated physical layer solution that is configurable to support multiple serial standards. It incorporates eight drivers and eight receivers (8TX/8RX), configurable for differential (V.11 or V.35) or single ended (V.28 and V.10) signaling.

SP510E enables a Serial Communications Controller to implement a variety of serial port types including V.24, V.25, V.36, EIA-530, EIA-530-A, X.21, RS-232. The device architecture is designed to support the data and clock signals used in HDLC or SDLC serial ports as either DTE or DCE.

Operating configuration is programmable in system using the mode-select pins. The V.11 and V.35 modes include internal bus termination that may be switched in or out using the TERM\_OFF pin.

The SP510E is ideal for space constrained applications. It requires only a single 5V supply for full operation. The V<sub>I</sub> pin determines the receiver output voltage (V<sub>OH</sub>, down to 1.65V), for interfacing with lower voltage CPUs and FPGAs. For single supply operation at 5V the  $V_1$  pin will be connected to  $V_{CC}$ .

Fully compliant V.28 and V.10 driver output voltages are generated using the onboard charge pump. Special power sequencing is not required during system startup. Charge pump outputs are internally regulated to minimize power consumption. The SP510E requires only four 1µF capacitors for complete functionality. The device may be put into a low power shutdown mode when not in active use.

All receivers have fail-safe protection to put outputs into an output-high state when inputs are open, shorted, or terminated but idle.

#### **FEATURES**

Up to 52Mbps Differential Transmission Rates

**ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER**

- ±15kV HBM ESD Tolerance for Analog I/O Pins

- Integrated Termination Resistors for V.11/V.35

- Eight Drivers and Eight Receivers (8TX/8RX)

- Adjustable Logic Level Pin V<sub>I</sub> (Down to 1.65V)

- Software Selectable Protocols with 3-Bit Word:

- RS-232 (V.28)

- EIA-530 (V.10 & V.11)

- EIA-530A (V.10 & V.11)

- X.21 (V.11)

- RS-449/V.36

- Internal Line or Digital Loopback Testing

- Adheres to NET1/NET2 and TBR2 Requirements

- Easy Flow-Through Pinout

- Single +5V Supply Voltage

- Individual Driver/Receiver Enable/Disable Controls

- Operates in DTE or DCE Mode

- Pin Compatible Upgrade for SP509, SP508

#### TYPICAL APPLICATIONS

- Data Communication Networks

- Telecommunication Equipment

- Secured Data Communication

- CSU and DSU

- Data Routers

- Network Switches

- WAN Access Equipment

- VoIP-PBX Gateways

### ORDERING INFORMATION(1)

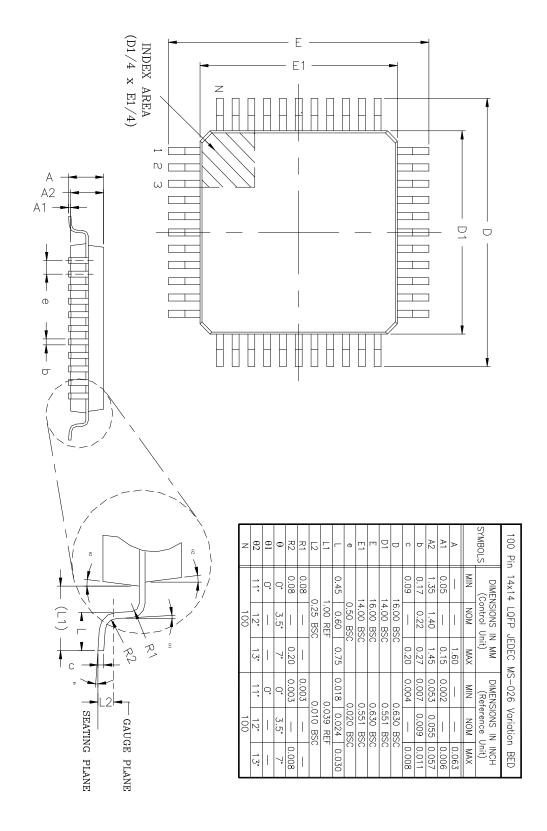

| PART NUMBER | OPERATING TEMPERATURE RANGE | PACKAGE      | PACKAGING METHOD | LEAD-FREE <sup>(2)</sup> |

|-------------|-----------------------------|--------------|------------------|--------------------------|

| SP510EEF-L  | -40°C to +85°C              | 100-pin LQFP | Tray             | Yes                      |

| SP510ECF-L  | 0°C to +70°C                | 100-pin LQFP | Tray             | Yes                      |

#### Notes:

- Refer to http://www.maxlinear.com/SP510E for most up-to-date Ordering Information.

- 2. Visit www.maxlinear.com for additional information on Environmental Rating.

## **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| Supply Voltage V <sub>CC</sub>                                                                                                                | +7.0V                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Logic-Interface Voltage (V <sub>L</sub> )                                                                                                     | $V_L \le V_{CC}$                  |

| Receiver DC Input Voltage                                                                                                                     | ±15.5V                            |

| Input Voltage at TTL Input Pins                                                                                                               | -0.3V to (V <sub>CC</sub> + 0.5V) |

| Driver Output Voltage (from Ground)                                                                                                           | -7.5V to +12.5V                   |

| Short Circuit Duration, TxOUT to GND                                                                                                          | Continuous                        |

| Storage Temperature Range                                                                                                                     | -65°C to +150°C                   |

| Lead Temperature (soldering, 10s)                                                                                                             | +300°C                            |

| Continuous Power Dissipation at $T_{AMB}$ = +70°C 100-Pin LQFP (derate 19mW/°C above +70°C) $\theta_{JA}$ = 52.7°C/W, $\theta_{JC}$ = 6.5°C/W | 1520mW                            |

## **ESD PROTECTION**

| TX Output & RX Input Pins | ±15 | kV | Human Body Model |

|---------------------------|-----|----|------------------|

| All Other Pins            | ±2  | kV | Human Body Model |

## TABLE 1: DC ELECTRICAL CHARACTERISTICS

| PARAMETERS                               | SYMBOL            | TEST CONDITIONS                                  | Min                 | Түр   | Max                 | Unit |

|------------------------------------------|-------------------|--------------------------------------------------|---------------------|-------|---------------------|------|

| V <sub>CC</sub> Supply Voltage           | V <sub>CC</sub>   |                                                  | 4.75                |       | 5.25                | V    |

| Logic Interface Voltage                  | V <sub>L</sub>    | $V_L \le V_{CC}$                                 | 1.65                |       | 5.25                | V    |

| I <sub>CC</sub> Supply Current           | I <sub>CC</sub>   |                                                  |                     |       | 300                 | mA   |

| I <sub>CC</sub> Shutdown                 | I <sub>CCSD</sub> |                                                  |                     | 200   |                     | μA   |

| DRIVER INPUT AND LOGIC INPUT PI          | NS                |                                                  |                     |       |                     |      |

| Logic Input High                         | V <sub>IH</sub>   |                                                  | 1.6                 |       |                     | V    |

| Logic Input Low                          | V <sub>IL</sub>   |                                                  |                     |       | 0.4                 | V    |

| RECEIVER OUTPUTS                         |                   |                                                  |                     |       |                     |      |

| Receiver Logic Output Low                | V <sub>OL</sub>   | I <sub>OUT</sub> = -3.2 mA                       |                     |       | 0.4                 | V    |

| Receiver Logic Output High               | V <sub>OH</sub>   | I <sub>OUT</sub> = 1 mA                          | V <sub>L</sub> -0.3 |       | V <sub>L</sub> +0.3 | V    |

| Receiver Output<br>Short-Circuit Current | I <sub>OSS</sub>  | 0V < V <sub>O</sub> < V <sub>CC</sub>            |                     | ±20   | ±60                 | mA   |

| Receiver Output<br>Leakage Current       | l <sub>OZ</sub>   | Receivers disabled 0.4V < V <sub>O</sub> < 5.25V |                     | ±0.05 | ±1                  | μA   |

| V.28 / RS-232 DRIVERS                    |                   |                                                  | 1                   |       |                     |      |

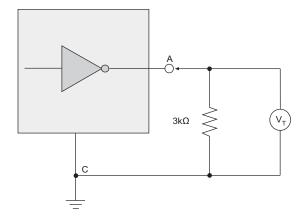

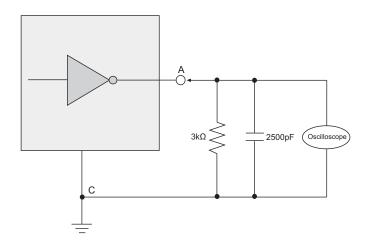

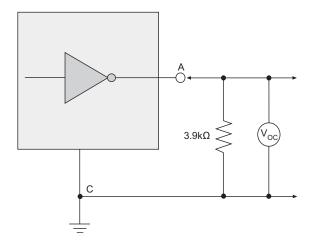

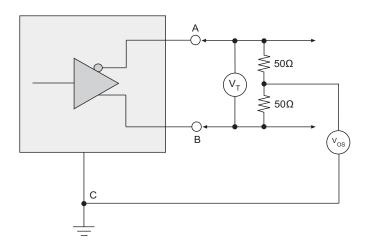

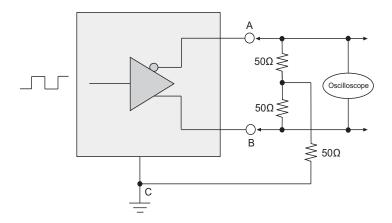

|                                          | V <sub>T</sub>    | Output load = $3k\Omega$ to GND Figure 3         | ±5                  | ±6    | ±15                 | V    |

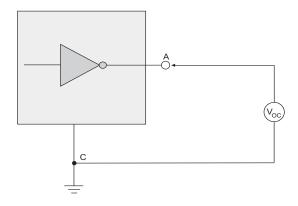

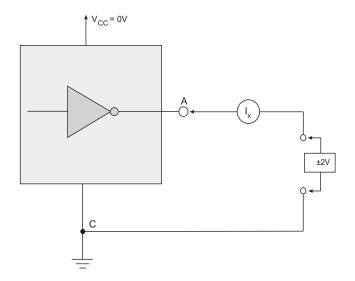

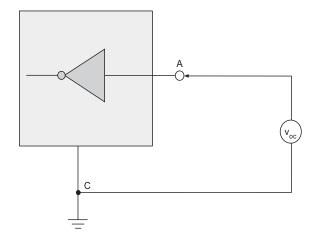

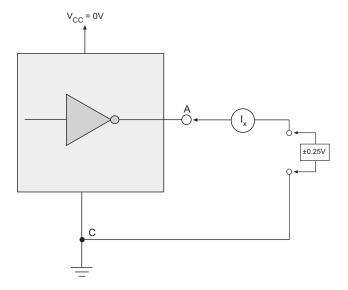

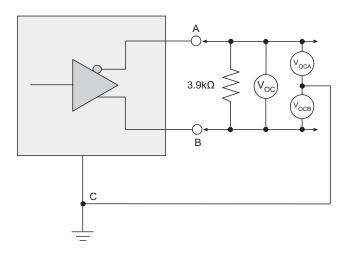

| Output Voltage Swing                     | V <sub>OC</sub>   | Open Circuit Output<br>Figure 2                  |                     |       | ±15                 | V    |

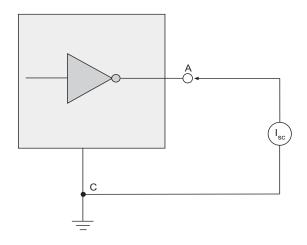

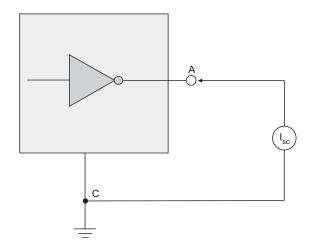

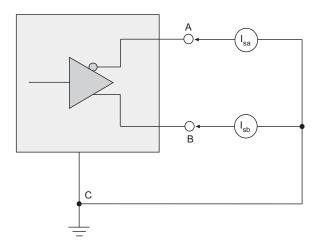

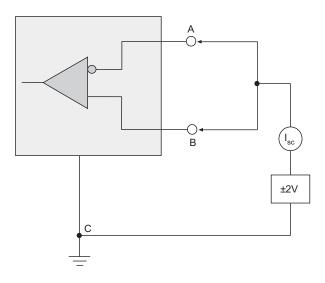

| Short Circuit Current                    | I <sub>SC</sub>   | V <sub>OUT</sub> = 0V, Figure 5                  |                     |       | ±100                | mA   |

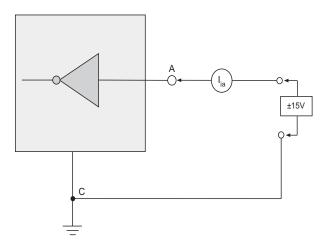

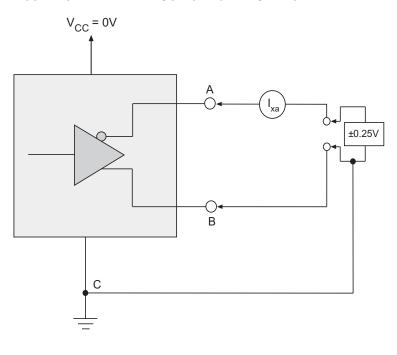

| Power-Off Impedance                      |                   | Figure 6                                         | 300                 | 10M   |                     | Ω    |

| V.28 / RS-232 Receivers                  |                   |                                                  |                     |       |                     |      |

| Input Voltage Range                      |                   |                                                  | -15                 |       | 15                  | V    |

| Input Threshold Low                      |                   |                                                  | 0.8                 | 1.2   |                     | V    |

| Input Threshold High                     |                   |                                                  |                     | 1.7   | 3                   | V    |

| Input Hysteresis                         |                   |                                                  |                     | 500   |                     | mV   |

| Input Resistance                         |                   | Figure 8                                         | 3                   | 5     | 7                   | kΩ   |

| Open Circuit Bias                        | V <sub>OC</sub>   | Figure 9                                         |                     |       | ±2                  | V    |

Receiver Input Hysteresis

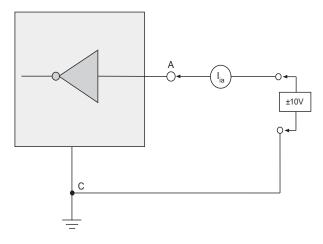

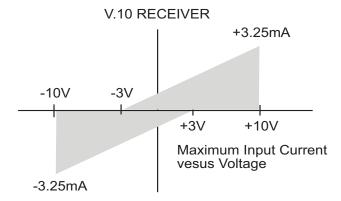

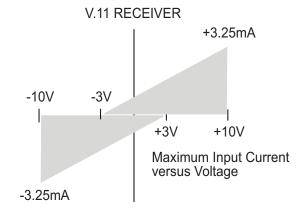

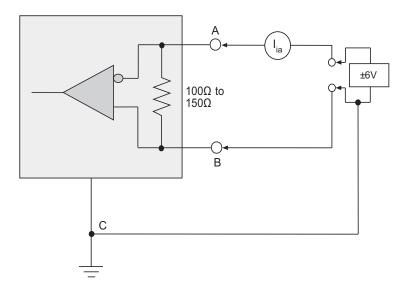

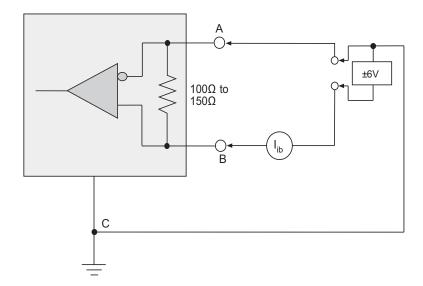

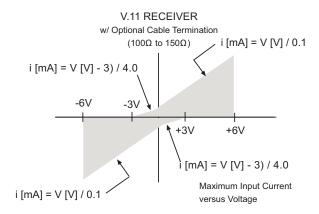

DC ELECTRICAL CHARACTERISTICS Vcc = +4.75V to +5.25V, C1-C4 = 1 $\mu$ F. T<sub>AMB</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>AMB</sub> = +25°C **PARAMETERS** SYMBOL **TEST CONDITIONS** MIN TYP Max UNIT V.10 / RS-423 DRIVERS Figure 10 ٧ Open Circuit Voltage  $V_{OC}$ ±4 ±6 **Test Terminated Voltage**  $V_{\mathsf{T}}$ Figure 11  $0.9V_{OC}$ V **Short Circuit Current** Figure 12 ±150 mΑ  $I_{SC}$ Power-Off Current Figure 13 ±100 μΑ V.10 / RS-423 RECEIVERS Input Current Figure 15 and Figure 16 -3.25 +3.25  $I_{IA}$ mA Input Impedance 4 15 kΩ Sensitivity ±0.2 V V.11 / RS-422 DRIVERS ٧ Open Circuit Voltage  $V_{OCA}, V_{OCB}$ Figure 17 ±6 Test Terminated Voltage  $V_{\mathsf{T}}$ Figure 18 ±2 V Balance  $\Delta V_{\mathsf{T}}$ Figure 18 V ±0.4 Driver DC Offset  $V_{OS}$ Figure 18 3 V Offset Balance Figure 18 ±0.4 V  $\Delta V_{OS}$ Short Circuit Output Current I<sub>SA</sub>, I<sub>SB</sub> Figure 19 ±150 mΑ Power-Off Current Figure 20 ±100 μΑ V.11 / RS-422 RECEIVERS Receiver Input Range  $\mathsf{V}_{\mathsf{CM}}$ -7 +7 ٧ Input Current Figure 21 and Figure 23 ±3.25 mV  $I_{IA}$ ,  $I_{IB}$ Input Current with Termination Figure 24 and Figure 25  $I_{IA}$ ,  $I_{IB}$ ±60.75 mΑ  $-10V \le V_{CM} \le +10V$ Receiver Input Impedance  $R_{IN}$ 4 15  $k\Omega$ Receiver Sensitivity  $V_{\mathsf{TH}}$ ±0.2 ٧

$V_{CM} = 0 V$

15

mV

$\Delta V_{TH}$

REV. 1.0.2

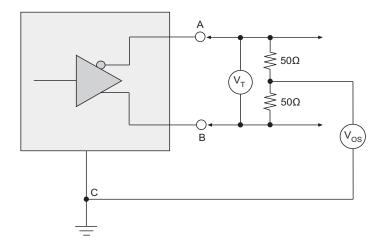

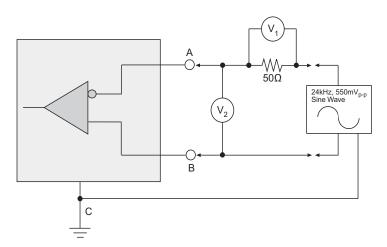

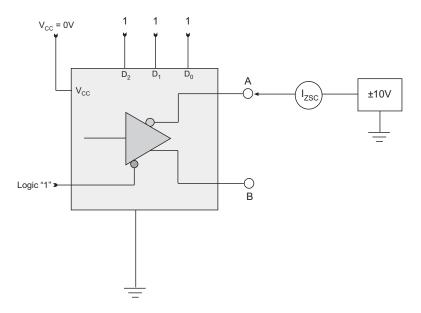

| PARAMETERS                                     | SYMBOL          | TEST CONDITIONS                                                               | MIN                 | ТҮР  | MAX                 | Unit |

|------------------------------------------------|-----------------|-------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| V.35 DRIVERS (ALL VALUES MEASUR                | ED WITH TERM    | _OFF = '0')                                                                   |                     |      |                     |      |

| Test Terminated Voltage                        | V <sub>T</sub>  | Figure 26                                                                     | ±0.44               |      | ±0.66               | V    |

| Offset                                         | V <sub>OS</sub> | Figure 26                                                                     |                     |      | ±0.6                | V    |

| Output Overshoot                               |                 | Figure 26,<br>V <sub>ST</sub> = Steady State Voltage                          | -0.2V <sub>ST</sub> |      | +0.2V <sub>ST</sub> | V    |

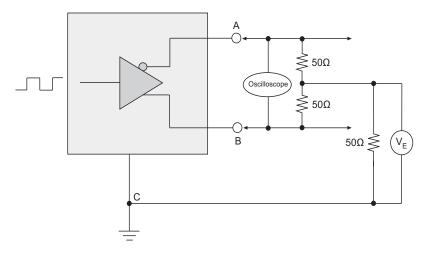

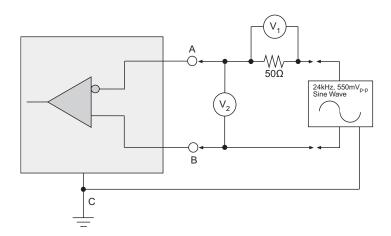

| Source Impedance                               |                 | Figure 29 $Z_S = V_2 / V_1 \times 50\Omega$                                   | 50                  |      | 150                 | Ω    |

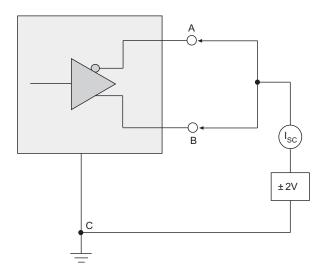

| Short Circuit Impedance                        | -               | Figure 28                                                                     | 135                 |      | 165                 | Ω    |

| V.35 RECEIVERS (ALL VALUES MEAS<br>Sensitivity | URED WITH TER   | RM_OFF = '0')                                                                 |                     | ±100 | ±200                | mV   |

| Source Impedance                               |                 | Figure 30 $Z_S = V_2 / V_1 \times 50\Omega$                                   | 90                  |      | 110                 | Ω    |

| Short-Circuit Impedance                        |                 | Figure 31                                                                     | 135                 |      | 165                 | Ω    |

| TRANSCEIVER LEAKAGE CURRENT                    |                 |                                                                               |                     |      |                     |      |

| Driver Output Tri-state Current                |                 | Drivers disabled, Figure 32                                                   |                     | 500  |                     | μA   |

| Receiver Output Tri-state Current              |                 | Tx and Rx Disabled, $0.4 \text{V} \leq \text{V}_{\text{O}} \leq 2.4 \text{V}$ |                     | 10   | μA                  |      |

Charge Pump Rise Time

2

ms

| Table 2: AC Timing Characteristics                       |                                       |                                                               |            |                        |       |      |  |  |

|----------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|------------|------------------------|-------|------|--|--|

| TIMING CHARACTERISTICS                                   |                                       |                                                               |            |                        |       |      |  |  |

| $V_{CC}$ = +4.75 to 5.25V, C1-C4 = 1 $\mu$ F;            | $T_{AMB} = T_{MIN}$ to                | T <sub>MAX</sub> , unless noted. Typical va                   | lues are a | t T <sub>AMB</sub> = - | +25°C |      |  |  |

| PARAMETERS                                               | SYMBOL                                | TEST CONDITIONS                                               | Min        | ТҮР                    | Max   | Unit |  |  |

| V.28 / RS-232 DRIVER                                     |                                       |                                                               |            |                        |       |      |  |  |

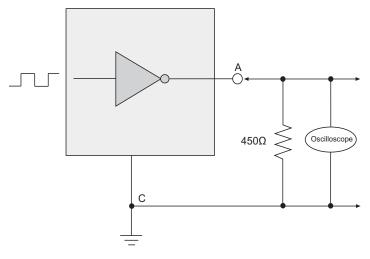

| Maximum Transmission Rate                                |                                       | Figure 7                                                      | 250        |                        |       | kbps |  |  |

| Driver Propagation Delay                                 | t <sub>DPHL</sub> , t <sub>DPLH</sub> |                                                               | 0.5        | 1                      | 5     | μs   |  |  |

| Driver Transition Time                                   |                                       | +3V to -3V, Figure 7                                          | 0.2        |                        | 1.5   | μs   |  |  |

| Instantaneous Slew Rate                                  |                                       | +3V to -3V, Figure 4                                          | 4          |                        | 30    | V/µs |  |  |

| Driver Skew                                              |                                       | t <sub>DPHL</sub> - t <sub>DPLH</sub>  <br>at zero crossing   |            | 100                    | 800   | ns   |  |  |

| Driver Channel to Channel Skew                           |                                       |                                                               |            | 20                     |       | ns   |  |  |

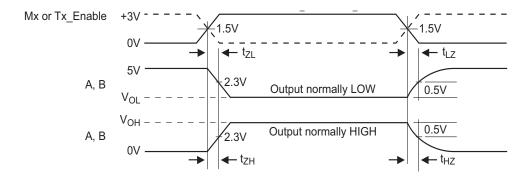

| Driver Output Enable Time<br>Tri-state to Output Low     | t <sub>DZL</sub>                      | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 34 and Figure 40 |            |                        | 2     | μs   |  |  |

| Driver Output Enable Time<br>Tri-state to Output High    | t <sub>DZH</sub>                      | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 34 and Figure 40 |            |                        | 2     | μs   |  |  |

| Driver Output Disable Time<br>Output Low to Tri-state    | t <sub>DLZ</sub>                      | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 34 and Figure 40  |            |                        | 2     | μs   |  |  |

| Driver Output Disable Time<br>Output High to Tri-state   | t <sub>DHZ</sub>                      | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 34 and Figure 40  |            |                        | 2     | μs   |  |  |

| V.28 / RS-232 Receiver                                   |                                       |                                                               |            |                        |       |      |  |  |

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub>   | R_IN to R_OUT, C <sub>L</sub> = 15 pF                         | 50         | 100                    | 500   | ns   |  |  |

| Receiver Skew                                            |                                       | t <sub>PHL</sub> - t <sub>PLH</sub>   at 1.5V                 |            | 50                     |       | ns   |  |  |

| Receiver Channel to Channel Skew                         |                                       |                                                               |            | 20                     |       | ns   |  |  |

| Receiver Output Rise / Fall Time                         | t <sub>R</sub> , t <sub>F</sub>       | C <sub>L</sub> = 15 pF                                        |            | 15                     |       | ns   |  |  |

| Receiver Output Enable Time<br>Tri-state to Output Low   | t <sub>ZL</sub>                       | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 35 and Figure 40 |            |                        | 2     | μs   |  |  |

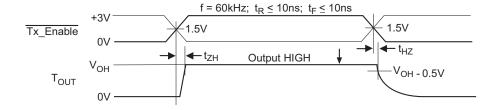

| Receiver Output Enable Time<br>Tri-state to Output High  | t <sub>ZH</sub>                       | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 35 and Figure 40 |            |                        | 2     | μs   |  |  |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub>                       | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 35 and Figure 40  |            |                        | 2     | μs   |  |  |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub>                       | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 35 and Figure 40  |            |                        | 2     | μs   |  |  |

Shutdown to operational

REV. 1.0.2

| TIMING CHARACTERISTICS                                    | T -T 40                               | T wales a set of Trainely                                     |     | <b>.</b> | 25°0 |      |

|-----------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|-----|----------|------|------|

| $V_{CC}$ = +4.75 to 5.25V, C1-C4 = 1 $\mu$ F;  PARAMETERS | SYMBOL                                | Test Conditions                                               | Min | TYP      | MAX  | Unit |

| V.10 / RS-423 DRIVER                                      |                                       |                                                               |     | 1        |      |      |

| Maximum Transmission Rate                                 |                                       |                                                               | 250 |          |      | kbps |

| Driver Propagation Delay                                  | t <sub>DPHL</sub> , t <sub>DPLH</sub> |                                                               | 30  | 150      | 500  | ns   |

| Driver Rise / Fall Time                                   | t <sub>DR</sub> , t <sub>DF</sub>     | 10% to 90%, Figure 14                                         |     |          | 500  | ns   |

| Driver Skew                                               |                                       | t <sub>DPHL</sub> - t <sub>DPLH</sub>  <br>at zero crossing   |     |          | 100  | ns   |

| Driver Channel to Channel Skew                            |                                       |                                                               |     | 5        |      | ns   |

| Driver Output Enable Time<br>Tri-state to Output Low      | t <sub>DZL</sub>                      | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 34 and Figure 40 |     |          | 2    | μs   |

| Driver Output Enable Time<br>Tri-state to Output High     | t <sub>DZH</sub>                      | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 34 and Figure 40 |     |          | 2    | μs   |

| Driver Output Disable Time<br>Output Low to Tri-state     | t <sub>DLZ</sub>                      | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 34 and Figure 40  |     |          | 2    | μs   |

| Driver Output Disable Time<br>Output High to Tri-state    | t <sub>DHZ</sub>                      | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 34 and Figure 40  |     |          | 2    | μs   |

| V.10 / RS-423 Receiver                                    |                                       |                                                               |     |          |      |      |

| Receiver Propagation Delay                                | t <sub>PHL</sub> , t <sub>PLH</sub>   |                                                               |     | 100      | 500  | ns   |

| Receiver Output Rise / Fall Time                          | t <sub>R</sub> , t <sub>F</sub>       | C <sub>L</sub> = 15 pF                                        |     | 15       |      | ns   |

| Receiver Skew                                             |                                       | t <sub>PHL</sub> - t <sub>PLH</sub>   at 1.5V                 |     | 5        |      | ns   |

| Receiver Channel to Channel Skew                          |                                       |                                                               |     | 5        |      | ns   |

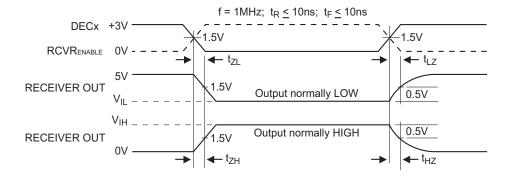

| Receiver Output Enable Time<br>Tri-state to Output Low    | t <sub>ZL</sub>                       | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 35 and Figure 40 |     |          | 2    | μs   |

| Receiver Output Enable Time<br>Tri-state to Output High   | t <sub>ZH</sub>                       | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 35 and Figure 40 |     |          | 2    | μs   |

| Receiver Output Disable Time<br>Output Low to Tri-state   | t <sub>LZ</sub>                       | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 35 and Figure 40  |     |          | 2    | μs   |

| Receiver Output Disable Time<br>Output High to Tri-state  | t <sub>HZ</sub>                       | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 35 and Figure 40  |     |          | 2    | μs   |

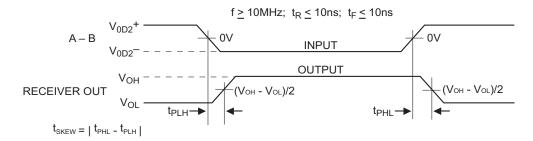

#### TIMING CHARACTERISTICS $V_{CC}$ = +4.75 to 5.25V, C1-C4 = 1 $\mu$ F; $T_{AMB}$ = $T_{MIN}$ to $T_{MAX}$ , unless noted. Typical values are at $T_{AMB}$ = +25°C. **PARAMETERS** SYMBOL **TEST CONDITIONS** MIN TYP Max UNIT HIGH SPEED V.11 / RS-422 (DRIVERS 1, 2 & 3) Maximum Bit Rate 52 Mbps 10-90% Driver Rise and Fall Time $t_{DR}, t_{DF}$ 6 ns Figure 22 and Figure 36 $C_1 = 50 pF$ **Driver Propagation Delay Time** $t_{DPHL}, t_{DPLH}$ 20 50 ns Figure 33 and Figure 36 $|t_{DPHL} - t_{DPLH}| C_L = 50 pF$ **Driver Skew** 3.8 Figure 33 and Figure 36 Driver Channel to Channel Skew 2 ns C<sub>L</sub> = 100 pF, S1 closed **Driver Output Enable Time** $t_{DZL}$ 100 ns Tri-state to Output Low Figure 34 and Figure 37 C<sub>L</sub> = 100 pF, S2 closed **Driver Output Enable Time** 100 ns $t_{DZH}$ Tri-state to Output High Figure 34 and Figure 37 **Driver Output Disable Time** $C_1 = 15 pF, S1 closed$ 100 $t_{DLZ}$ ns Output Low to Tri-state Figure 34 and Figure 37 C<sub>I</sub> = 15 pF, S2 closed **Driver Output Disable Time** 100 ns t<sub>DHZ</sub> Output High to Tri-state Figure 34 and Figure 37 HIGH SPEED V.11 / RS-422 (RECEIVERS 1, 2 & 3) $C_{L} = 50 \text{ pF}$ Receiver Output Rise / Fall Time $t_R, t_F$ 6 ns $C_1 = 50 \text{ pF}$ Receiver Propagation Delay $t_{PHL}, t_{PLH}$ 20 50 ns Figure 33 and Figure 38 $|t_{PHL} - t_{PLH}|$ $C_L = 50 pF$ Receiver Skew 3.8 ns Figure 33 and Figure 38 Receiver Channel to Channel Skew 2 ns C<sub>I</sub> = 100 pF, S1 closed Receiver Output Enable Time $t_{ZL}$ 100 ns Tri-state to Output Low Figure 35 and Figure 39 C<sub>I</sub> = 100 pF, S2 closed Receiver Output Enable Time 100 $t_{ZH}$ ns Tri-state to Output High Figure 35 and Figure 39 $C_1 = 15 pF, S1 closed$ Receiver Output Disable Time 100 $t_{LZ}$ ns Output Low to Tri-state Figure 35 and Figure 39 Receiver Output Disable Time C<sub>L</sub> = 15 pF, S2 closed $t_{HZ}$ 100 ns Output High to Tri-state Figure 35 and Figure 39

| PARAMETERS                                               | SYMBOL                                | TEST CONDITIONS                                                                            | Min | Түр | Max | Unit |

|----------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V.11 / RS-422 Handshake Signals                          | (DRIVERS 4, 5 &                       | k 6)                                                                                       |     |     |     |      |

| Maximum Bit Rate                                         |                                       | Figure 33                                                                                  | 10  |     |     | Mbps |

| Driver Rise and Fall Time                                | t <sub>DR</sub> , t <sub>DF</sub>     | Figure 22 and Figure 36                                                                    |     | 2   | 10  | ns   |

| Driver Propagation Delay Time                            | t <sub>DPHL</sub> , t <sub>DPLH</sub> | C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 36                                          |     | 20  | 50  | ns   |

| Driver Skew                                              |                                       | t <sub>DPHL</sub> - t <sub>DPLH</sub>  , C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 36 |     |     | 10  | ns   |

| Driver Channel to Channel Skew                           |                                       |                                                                                            |     | 2   |     | ns   |

| Driver Output Enable Time<br>Tri-state to Output Low     | t <sub>DZL</sub>                      | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 34 and Figure 37                              |     |     | 100 | ns   |

| Driver Output Enable Time<br>Tri-state to Output High    | t <sub>DZH</sub>                      | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 34 and Figure 37                              |     |     | 100 | ns   |

| Driver Output Disable Time<br>Output Low to Tri-state    | t <sub>DLZ</sub>                      | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 34 and Figure 37                               |     |     | 100 | ns   |

| Driver Output Disable Time<br>Output High to Tri-state   | t <sub>DHZ</sub>                      | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 34 and Figure 37                               |     |     | 100 | ns   |

| V.11 / RS-422 HANDSHAKE SIGNALS                          | (RECEIVERS 4,                         | 5 & 6)                                                                                     | 1   | 1   |     | 1    |

| Receiver Output Rise / Fall Time                         | t <sub>R</sub> , t <sub>F</sub>       | C <sub>L</sub> = 50 pF                                                                     |     |     | 20  | ns   |

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub>   | C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 38                                          |     | 20  | 50  | ns   |

| Receiver Skew                                            |                                       | t <sub>PHL</sub> - t <sub>PLH</sub>   C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 38    |     |     | 10  | ns   |

| Receiver Channel to Channel Skew                         |                                       |                                                                                            |     | 2   |     | ns   |

| Receiver Output Enable Time<br>Tri-state to Output Low   | t <sub>ZL</sub>                       | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 35 and Figure 39                              |     |     | 100 | ns   |

| Receiver Output Enable Time<br>Tri-state to Output High  | t <sub>ZH</sub>                       | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 35 and Figure 39                              |     |     | 100 | ns   |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub>                       | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 35 and Figure 39                               |     |     | 100 | ns   |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub>                       | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 35 and Figure 39                               |     |     | 100 | ns   |

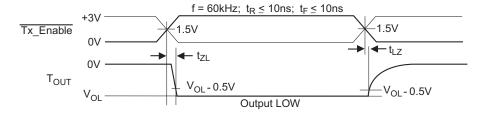

TIMING CHARACTERISTICS  $V_{CC}$  = +4.75 to 5.25V, C1-C4 = 1 $\mu$ F;  $T_{AMB}$  =  $T_{MIN}$  to  $T_{MAX}$ , unless noted. Typical values are at  $T_{AMB}$  = +25°C. **PARAMETERS** SYMBOL **TEST CONDITIONS** MIN TYP Max UNIT V.35 (DRIVERS 1, 2 & 3) Maximum Bit Rate f<sub>MAX</sub> = 20 MHz, Figure 33 Mbps 40 Driver Rise and Fall Time Figure 29 10  $t_{DR}, t_{DF}$ ns  $C_1 = 50 pF$ **Driver Propagation Delay Time**  $t_{DPHL}, t_{DPLH}$ 25 50 ns Figure 33 and Figure 36  $|t_{DPHL} - t_{DPLH}| C_L = 50 pF$ **Driver Skew** 2 5 ns Figure 33 and Figure 36 Driver Channel to Channel Skew 2 ns C<sub>I</sub> = 100 pF, S1 closed **Driver Output Enable Time** 200  $t_{DZL}$ ns Tri-state to Output Low Figure 34 and Figure 37 C<sub>I</sub> = 100 pF, S2 closed **Driver Output Enable Time** 200 t<sub>DZH</sub> ns Tri-state to Output High Figure 34 and Figure 37 C<sub>I</sub> = 15 pF, S1 closed **Driver Output Disable Time**  $t_{DLZ}$ 200 ns Output Low to Tri-state Figure 34 and Figure 37 C<sub>I</sub> = 15 pF, S2 closed **Driver Output Disable Time** 200  $t_{DHZ}$ Output High to Tri-state Figure 34 and Figure 37 V.35 (RECEIVERS 1, 2 & 3)  $C_1 = 50 pF$ Receiver Propagation Delay t<sub>PHL</sub>, t<sub>PLH</sub> 30 50 ns Figure 33 and Figure 38  $|t_{PHL} - t_{PLH}| C_L = 50 pF$ Receiver Skew 5 ns Figure 33 and Figure 38 2 Receiver Channel to Channel Skew ns C<sub>L</sub> = 100 pF, S1 closed Receiver Output Enable Time 200  $t_{ZL}$ ns Tri-state to Output Low Figure 35 and Figure 39 C<sub>L</sub> = 100 pF, S2 closed Receiver Output Enable Time 200  $t_{ZH}$ Tri-state to Output High Figure 35 and Figure 39 C<sub>I</sub> = 15 pF, S1 closed Receiver Output Disable Time 200  $t_{LZ}$ ns Output Low to Tri-state Figure 35 and Figure 39 C<sub>I</sub> = 15 pF, S2 closed Receiver Output Disable Time 200  $t_{HZ}$ ns Output High to Tri-state Figure 35 and Figure 39

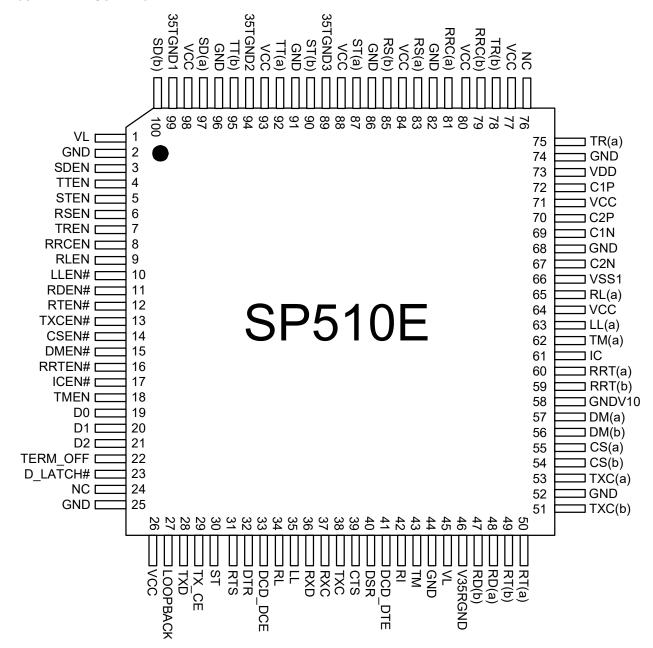

#### FIGURE 1. PIN OUT DIAGRAM

## TABLE 3: PIN DESCRIPTIONS BY FUNCTION

| PIN NAME             | PIN NUMBER | I/O |     | DESCRIPTION                                                            |  |  |  |  |

|----------------------|------------|-----|-----|------------------------------------------------------------------------|--|--|--|--|

| DIFFERENTIAL DRIVERS |            |     |     |                                                                        |  |  |  |  |

| TxD                  | 28         | I   | TTL | TxD Driver Input                                                       |  |  |  |  |

| SD(b) / SD(a)        | 100, 97    | 0   | TTL | Differential Transmit data non-inverting (b) and inverting (a) outputs |  |  |  |  |

| V35TGND1             | 99         | I   |     | SD Termination Reference                                               |  |  |  |  |

| SDEN                 | 3          | I   | TTL | TxD Driver Enable                                                      |  |  |  |  |

| TxCE                 | 29         | ļ   | TTL | TxCE Driver Input                                                      |  |  |  |  |

| TT(b) / TT(a)        | 95, 92     | 0   | TTL | Differential TxCE non-inverting (b) and inverting (a) outputs          |  |  |  |  |

| V35TGND2             | 94         | I   |     | TT Termination Reference                                               |  |  |  |  |

| TTEN                 | 4          | Į.  | TTL | TxCE Driver Enable                                                     |  |  |  |  |

| ST                   | 30         | I   | TTL | ST Driver Input                                                        |  |  |  |  |

| ST(b) / ST(a)        | 90, 87     | 0   | TTL | Differential ST non-inverting (b) and inverting (a) outputs            |  |  |  |  |

| V35TGND3             | 89         | I   |     | ST Termination Reference                                               |  |  |  |  |

| STEN                 | 5          | I   | TTL | ST Driver Enable                                                       |  |  |  |  |

| RTS                  | 31         | I   | TTL | RTS Driver Input                                                       |  |  |  |  |

| RS(b) / RS(a)        | 85, 83     | 0   | TTL | Differential RTS non-inverting (b) and inverting (a) outputs           |  |  |  |  |

| RSEN                 | 6          | I   | TTL | RTS Driver Enable                                                      |  |  |  |  |

| DTR                  | 32         | I   | TTL | DTR Driver Input                                                       |  |  |  |  |

| TR(b) / TR(a)        | 78, 75     | 0   | TTL | Differential DTR non-inverting (b) and inverting (a) outputs           |  |  |  |  |

| TREN                 | 7          | I   | TTL | DTR Driver Enable                                                      |  |  |  |  |

| DCD_DCE              | 33         | I   | TTL | DCD_DCE Driver Input                                                   |  |  |  |  |

| RRC(b) / RRC(a)      | 79, 81     | 0   | TTL | Differential DCD non-inverting (b) and inverting (a) outputs           |  |  |  |  |

| RRCEN                | 8          | I   | TTL | DCD Driver Enable                                                      |  |  |  |  |

| SINGLE ENDED DRIV    | /ERS       |     |     |                                                                        |  |  |  |  |

| RL                   | 34         | I   | TTL | RL Driver Input                                                        |  |  |  |  |

| RL(a)                | 65         | 0   | TTL | RL Driver Output                                                       |  |  |  |  |

| RLEN                 | 9          | I   | TTL | RL Driver Enable                                                       |  |  |  |  |

| LL                   | 35         | I   | TTL | LL Driver Input                                                        |  |  |  |  |

| LL(a)                | 63         | 0   | TTL | LL Driver Output                                                       |  |  |  |  |

| LLEN#                | 10         | I   | TTL | LL Driver Enable, active low                                           |  |  |  |  |

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

| PIN NAME               | PIN NUMBER | I/O |     | DESCRIPTION                                                     |  |  |  |  |

|------------------------|------------|-----|-----|-----------------------------------------------------------------|--|--|--|--|

| DIFFERENTIAL RECEIVERS |            |     |     |                                                                 |  |  |  |  |

| RxD                    | 36         | 0   | TTL | RxD Receiver Output                                             |  |  |  |  |

| RD(b) / RD(a)          | 47, 48     | I   | TTL | Differential RXD non-inverting (b) and inverting (a) inputs     |  |  |  |  |

| RDEN#                  | 11         | I   | TTL | RxD Receiver Enable, active low                                 |  |  |  |  |

| RxC                    | 37         | 0   | TTL | RxC Receiver Output                                             |  |  |  |  |

| RT(b) / RT(a)          | 49, 50     | I   | TTL | Differential RXC non-inverting (b) and inverting (a) inputs     |  |  |  |  |

| RTEN#                  | 12         | I   | TTL | RxC Receiver Enable, active low                                 |  |  |  |  |

| TxC                    | 38         | 0   | TTL | TxC Receiver Output                                             |  |  |  |  |

| TxC(b) / TxC(a)        | 51, 53     | I   | TTL | Differential TxC non-inverting (b) and inverting (a) inputs     |  |  |  |  |

| TxCEN#                 | 13         | I   | TTL | TxC Receiver Enable, active low                                 |  |  |  |  |

| CTS                    | 39         | 0   | TTL | CTS Receiver Output                                             |  |  |  |  |

| CS(b) / CS(a)          | 54, 55     | I   | TTL | Differential CTS non-inverting (b) and inverting (a) inputs     |  |  |  |  |

| CSEN#                  | 14         | I   | TTL | CTS Receiver Enable, active low                                 |  |  |  |  |

| DSR                    | 40         | 0   | TTL | DSR Receiver Output                                             |  |  |  |  |

| DM(b) / DM(a)          | 56, 57     | I   | TTL | Differential DSR non-inverting (b) and inverting (a) inputs     |  |  |  |  |

| DMEN#                  | 15         | I   | TTL | DSR Receiver Enable, active low                                 |  |  |  |  |

| DCD_DTE                | 41         | 0   | TTL | DCD_DTE Receiver Output                                         |  |  |  |  |

| RRT(b) / RRT(a)        | 59, 60     | I   | TTL | Differential DCD_DTE non-inverting (b) and inverting (a) inputs |  |  |  |  |

| RRTEN#                 | 16         | I   | TTL | DCD_DTE Receiver Enable, active low                             |  |  |  |  |

| SINGLE ENDED REC       | EIVERS     |     |     |                                                                 |  |  |  |  |

| IC                     | 61         | I   | TTL | RI Receiver Input                                               |  |  |  |  |

| RI                     | 42         | 0   | TTL | RI Receiver Output                                              |  |  |  |  |

| ICEN#                  | 17         | I   | TTL | RI Receiver Enable, active low                                  |  |  |  |  |

| TM(a)                  | 62         | I   | TTL | TM Receiver Input                                               |  |  |  |  |

| TM                     | 43         | 0   | TTL | TM Receiver Output                                              |  |  |  |  |

| TMEN                   | 18         | I   | TTL | TM Receiver Enable                                              |  |  |  |  |

| PIN NAME        | PIN NUMBER                                  | I/O |     | DESCRIPTION                                                                            |

|-----------------|---------------------------------------------|-----|-----|----------------------------------------------------------------------------------------|

| PROTOCOL & MODI | E SEI ECTION PINS                           |     |     |                                                                                        |

|                 |                                             |     | T   | T.,                                                                                    |

| D2, D1, D0      | 21, 20, 19                                  | I   | TTL | Mode Select - Refer to Table 5 and Table 6                                             |

| CHARGE PUMP PIN | s                                           |     |     |                                                                                        |

| C1P, C1N        | 72, 69                                      | I   |     | Charge Pump Capacitor 1 +/- inputs. Connect a 1 μF capacitor between C1P and C1N pins. |

| C2P, C2N        | 70, 67                                      | I   |     | Charge Pump Capacitor 2 +/- inputs. Connect a 1 µF capacitor between C2P and C2N pins. |

| VSS1            | 66                                          | -   |     | -2xV <sub>CC</sub> Charge Pump                                                         |

| VDD             | 73                                          | I   |     | 2xV <sub>CC</sub> Charge Pump                                                          |

| GENERAL CONTROL | L PINS                                      | I   | TTL | Loopback mode enable, active low                                                       |

| D_LATCH#        | 23                                          | 1   |     | Decoder Latch, active low                                                              |

| TERM OFF        | 22                                          | I   |     | Termination disable                                                                    |

| RESERVED PINS   |                                             |     |     |                                                                                        |

| NC              | 24, 76                                      |     |     | No Connect                                                                             |

| Power and Group | ND PINS                                     |     |     |                                                                                        |

| VCC             | 26, 64, 71, 77,<br>80, 84, 88, 98           | I   |     | 5V supply                                                                              |

| VL              | 1, 45                                       | I   |     | Logic I/O Power Supply Input                                                           |

| GND             | 2, 25, 44, 52,<br>68, 74, 82, 86,<br>91, 96 | I   |     | Ground                                                                                 |

| GNDV10          | 58                                          | -   |     | V.10 Receiver Ground Reference                                                         |

| V35RGND         | 46                                          | 0   |     | Receiver Termination Reference                                                         |

*Note:* Pin type: I = Input, O = Output, I/O = Input/output.

TABLE 4: PIN DESCRIPTIONS BY PIN NUMBER

| PIN DESCRIPTIONS BY PIN NUMBER |                |                               |    |         |                                |  |  |  |

|--------------------------------|----------------|-------------------------------|----|---------|--------------------------------|--|--|--|

| 1                              | VL             | Logic I/O Power Supply Input  | 32 | DTR     | DTR Driver TTL Input           |  |  |  |

| 2                              | GND            | Ground                        | 33 | DCD_DCE | DCD_DCE Driver TTL Input       |  |  |  |

| 3                              | SDEN           | TxD Driver Enable Input       | 34 | RL      | RL Driver TTL Input            |  |  |  |

| 4                              | TTEN           | TxCE Driver Enable Input      | 35 | LL      | LL Driver TTL Input            |  |  |  |

| 5                              | STEN           | ST Driver Enable Input        | 36 | RxD     | RxD Receiver TTL Output        |  |  |  |

| 6                              | RSEN           | RTS Driver Enable Input       | 37 | RxC     | RxC Receiver TTL Output        |  |  |  |

| 7                              | TREN           | DTR Driver Enable Input       | 38 | TxC     | TxC Receiver TTL Output        |  |  |  |

| 8                              | RRCEN          | DCD Driver Enable Input       | 39 | CTS     | CTS Receiver TTL Output        |  |  |  |

| 9                              | RLEN           | RL Driver Enable Input        | 40 | DSR     | DSR Receiver TTL Output        |  |  |  |

| 10                             | LLEN#          | LL Driver Enable Input        | 41 | DCD_DTE | DCD_DTE Receiver TTL Output    |  |  |  |

| 11                             | RDEN#          | RxD Receiver Enable Input     | 42 | RI      | RI Receiver TTL Output         |  |  |  |

| 12                             | RTEN#          | RxC Receiver Enable Input     | 43 | TM      | TM Receiver TTL Output         |  |  |  |

| 13                             | TxCEN#         | TxC Receiver Enable Input     | 44 | GND     | Ground                         |  |  |  |

| 14                             | CSEN#          | CTS Receiver Enable Input     | 45 | VL      | Logic I/O Power Supply Input   |  |  |  |

| 15                             | DMEN#          | DSR Receiver Enable Input     | 46 | V35RGND | Receiver Termination Reference |  |  |  |

| 16                             | RRTEN#         | DCD_DTE Receiver Enable Input | 47 | RD(b)   | RXD Non-Inverting Input        |  |  |  |

| 17                             | ICEN#          | RI Receiver Enable Input      | 48 | RD(a)   | RXD Inverting Input            |  |  |  |

| 18                             | TMEN           | TM Receiver Enable Input      | 49 | RT(b)   | RxC Non-Inverting Input        |  |  |  |

| 19                             | D0             | Mode Select Input - Bit 0     | 50 | RT(a)   | RxC Inverting Input            |  |  |  |

| 20                             | D1             | Mode Select Input - Bit 1     | 51 | TxC(b)  | TxC Non-Inverting Input        |  |  |  |

| 21                             | D2             | Mode Select Input - Bit 2     | 52 | GND     | Ground                         |  |  |  |

| 22                             | TERM_OFF       | Termination Disable Input     | 53 | TxC(a)  | TxC Inverting Input            |  |  |  |

| 23                             | D_LATCH#       | Decoder Latch Input           | 54 | CS(b)   | CTS Non-Inverting Input        |  |  |  |

| 24                             | N/C            | No Connect                    | 55 | CS(a)   | CTS Inverting Input            |  |  |  |

| 25                             | GND            | Ground                        | 56 | DM(b)   | DSR Non-Inverting Input        |  |  |  |

| 26                             | VCC            | 5V Power Supply Input         | 57 | DM(a)   | DSR Inverting Input            |  |  |  |

| 27                             | LOOP-<br>BACK# | Loopback Mode Enable Input    | 58 | GNDV10  | V.10 Rx Ground Reference       |  |  |  |

| 28                             | TxD            | TxD Driver TTL Input          | 59 | RRT(b)  | DCD_DTE Non-Inverting Input    |  |  |  |

| 29                             | TxCE           | TxCE Driver TTL Input         | 60 | RRT(a)  | DCD_DTE Inverting Input        |  |  |  |

| 30                             | ST             | ST Driver TTL Input           | 61 | IC      | RI Receiver Input              |  |  |  |

| 31                             | RTS            | RTS Driver TTL Input          | 62 | TM(a)   | TM Receiver Input              |  |  |  |

| Pin [ | PIN DESCRIPTIONS BY PIN NUMBER |                                  |     |          |                           |  |  |

|-------|--------------------------------|----------------------------------|-----|----------|---------------------------|--|--|

| 63    | LL(a)                          | LL Driver Output                 | 82  | GND      | Ground                    |  |  |

| 64    | VCC                            | 5V Power Supply Input            | 83  | RS(a)    | RTS Inverting Output      |  |  |

| 65    | RL(a)                          | RL Driver Output                 | 84  | VCC      | 5V Power Supply Input     |  |  |

| 66    | VSS1                           | -2 x V <sub>CC</sub> Charge Pump | 85  | RS(b)    | RTS Non-Inverting Output  |  |  |

| 67    | C2N                            | Charge Pump Capacitor            | 86  | GND      | Ground                    |  |  |

| 68    | GND                            | Ground                           | 87  | ST(a)    | ST Inverting Output       |  |  |

| 69    | C1N                            | Charge Pump Capacitor            | 88  | VCC      | 5V Power Supply Input     |  |  |

| 70    | C2P                            | Charge Pump Capacitor            | 89  | V35TGND3 | ST Termination Reference  |  |  |

| 71    | VCC                            | 5V Power Supply Input            | 90  | ST(b)    | ST Non-Inverting Output   |  |  |

| 72    | C1P                            | Charge Pump Capacitor            | 91  | GND      | Ground                    |  |  |

| 73    | VDD                            | 2 x V <sub>CC</sub> Charge Pump  | 92  | TT(a)    | TxCE Inverting Output     |  |  |

| 74    | GND                            | Ground                           | 93  | VCC      | 5V Power Supply Input     |  |  |

| 75    | TR(a)                          | DTR Inverting Output             | 94  | V35TGND2 | TT Termination Reference  |  |  |

| 76    | NC                             | No Connect                       | 95  | TT(b)    | TxCE Non-Inverting Output |  |  |

| 77    | VCC                            | 5V Power Supply Input            | 96  | GND      | Ground                    |  |  |

| 78    | TR(b)                          | DTR Non-Inverting Output         | 97  | SD(a)    | TxD Inverting Output      |  |  |

| 79    | RRC(b)                         | DCD Non-Inverting Output         | 98  | VCC      | 5V Power Supply Input     |  |  |

| 80    | VCC                            | 5V Power Supply Input            | 99  | V35TGND1 | SD Termination Reference  |  |  |

| 81    | RRC(a)                         | DCD Inverting Output             | 100 | SD(b)    | TxD Non-Inverting Output  |  |  |

REV. 1.0.2

## **TABLE 5: DRIVER MODE SELECTION**

| DRIVER OUTPUT PIN     | EIA-530A<br>MODE | EIA-530<br>Mode | X.21<br>Mode<br>(V.11) | V.35<br>Mode | RS-449<br>MODE<br>(V.36) | RS-232<br>Mode<br>(V.28) | SHUT-<br>DOWN | SUGGESTED<br>SIGNAL |

|-----------------------|------------------|-----------------|------------------------|--------------|--------------------------|--------------------------|---------------|---------------------|

| MODE (D2, D1, D0)     | 001              | 010             | 011                    | 100          | 101                      | 110                      | 111           |                     |

| T <sub>1</sub> OUT(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxD(a)              |

| T <sub>1</sub> OUT(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxD(b)              |

| T <sub>2</sub> OUT(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxCE(a)             |

| T <sub>2</sub> OUT(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxCE(b)             |

| T <sub>3</sub> OUT(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxC_DCE(a)          |

| T <sub>3</sub> OUT(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxC_DCE(b)          |

| T <sub>4</sub> OUT(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | RTS(a)              |

| T <sub>4</sub> OUT(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | RTS(b)              |

| T <sub>5</sub> OUT(a) | V.10             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DTR(a)              |

| T <sub>5</sub> OUT(b) | High-Z           | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DTR(b)              |

| T <sub>6</sub> OUT(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DCD_DCE(a)          |

| T <sub>6</sub> OUT(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DCD_DCE(b)          |

| T <sub>7</sub> OUT(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | RL                  |

| T <sub>8</sub> OUT(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | LL                  |

## TABLE 6: RECEIVER MODE SELECTION

| RECEIVER INPUT PIN   | EIA-530A<br>MODE | EIA-530<br>Mode | X.21<br>Mode<br>(V.11) | V.35<br>Mode | RS-449<br>MODE<br>(V.36) | RS-232<br>MODE<br>(V.28) | SHUT-<br>DOWN | SUGGESTED<br>SIGNAL |

|----------------------|------------------|-----------------|------------------------|--------------|--------------------------|--------------------------|---------------|---------------------|

| MODE (D2, D1, D0)    | 001              | 010             | 011                    | 100          | 101                      | 110                      | 111           |                     |

| R <sub>1</sub> IN(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | RxD(a)              |

| R <sub>1</sub> IN(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | RxD(b)              |

| R <sub>2</sub> IN(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | RxCE(a)             |

| R <sub>2</sub> IN(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | RxCE(b)             |

| R <sub>3</sub> IN(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxC_DTE(a)          |

| R <sub>3</sub> IN(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxC_DTE(b)          |

| R <sub>4</sub> IN(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | CTS(a)              |

| R <sub>4</sub> IN(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | CTS(b)              |

| R <sub>5</sub> IN(a) | V.10             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DSR(a)              |

| R <sub>5</sub> IN(b) | High-Z           | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DSR(b)              |

| R <sub>6</sub> IN(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DCD_DTE(a)          |

| R <sub>6</sub> IN(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DCD_DTE(b)          |

| R <sub>7</sub> IN(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | RI                  |

| R <sub>8</sub> IN(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | TM                  |

REV. 1.0.2

### **TABLE 7: V.11 & V.35 DRIVERS**

| INP    | UTS   | Оитритѕ |       |  |

|--------|-------|---------|-------|--|

| Tx_EN# | Tx_IN | Tx(A)   | Тх(в) |  |

| 1      | 1     | 0       | 1     |  |

| 1      | 0     | 1       | 0     |  |

### TABLE 8: V.28 DRIVERS

| INP    | UTS   | Оитритѕ |         |  |

|--------|-------|---------|---------|--|

| Tx_EN# | Tx_IN | Tx(A)   | Тх(в)   |  |

| 1      | 1     | < -5V   | > 30 kΩ |  |

| 1      | 0     | > +5V   | > 30 kΩ |  |

TABLE 9: V.10 DRIVERS

| INP    | UTS   | Оитритѕ |         |  |

|--------|-------|---------|---------|--|

| Tx_EN# | Tx_IN | Tx(A)   | Тх(в)   |  |

| 1      | 1     | < -4V   | > 30 kΩ |  |

| 1      | 0     | > +4V   | > 30 kΩ |  |

### TABLE 10: V.11 & V.35 RECEIVERS

| INPUTS         | OUTPUTS |  |

|----------------|---------|--|

| Rx(a) - Rx(b)  | RO      |  |

| ≥ 200 mV       | 1       |  |

| ≤ –200 mV      | 0       |  |

| Open / shorted | 1       |  |

### TABLE 11: V.28 RECEIVERS

| INPUTS        | Оитритѕ |  |

|---------------|---------|--|

| Rx(a) - Rx(b) | RO      |  |

| ≥ <b>+</b> 3V | 0       |  |

| ≤ <b>-3V</b>  | 1       |  |

| Open / ground | 1       |  |

TABLE 12: V.10 RECEIVERS

| INPUTS        | Оитритѕ |  |

|---------------|---------|--|

| Rx(a) - Rx(b) | RO      |  |

| ≥ +0.3V       | 0       |  |

| ≤-0.3V        | 1       |  |

| Open / ground | 1       |  |

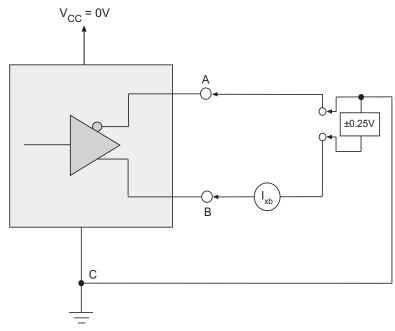

## FIGURE 2. V.28 DRIVER OUTPUT OPEN CIRCUIT VOLTAGE

FIGURE 3. V.28 DRIVER OUTPUT LOADED VOLTAGE

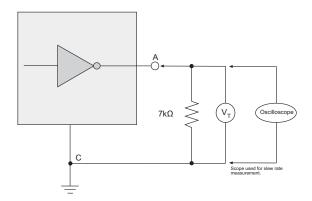

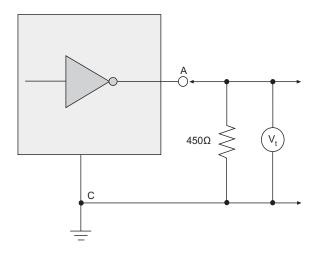

FIGURE 4. V.28 DRIVER OUTPUT SLEW RATE

FIGURE 5. V.28 DRIVER OUTPUT SHORT CIRCUIT CURRENT

FIGURE 6. V.28 DRIVER OUTPUT POWER-OFF IMPEDANCE

FIGURE 7. V.28 DRIVER OUTPUT RISE/FALL TIME

## FIGURE 8. V.28 RECEIVER INPUT IMPEDANCE

FIGURE 9. V.28 RECEIVER INPUT OPEN-CIRCUIT BIAS

FIGURE 10. V.10 DRIVER OUTPUT OPEN-CIRCUIT VOLTAGE

FIGURE 11. V.10 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 12. V.10 DRIVER OUTPUT SHORT-CIRCUIT CURRENT

FIGURE 13. V.10 DRIVER OUTPUT POWER-OFF IMPEDANCE

## FIGURE 14. V.10 DRIVER OUTPUT TRANSITION TIME

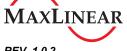

FIGURE 15. V.10 RECEIVER INPUT CURRENT

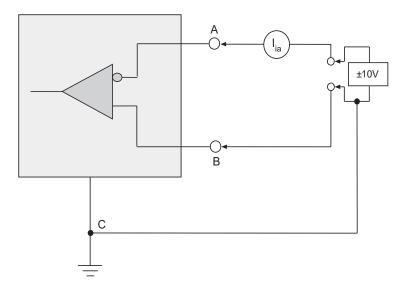

FIGURE 16. V.10 RECEIVER INPUT IV GRAPH

## FIGURE 17. V.11 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 18. V.11 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 19. V.11 DRIVER OUTPUT SHORT-CIRCUIT CURRENT

## FIGURE 20. V.11 DRIVER OUTPUT POWER-OFF CURRENT

## FIGURE 21. V.11 RECEIVER INPUT CURRENT

## FIGURE 22. V.11 DRIVER OUTPUT RISE/FALL TIME

FIGURE 23. V.11 RECEIVER INPUT IV GRAPH

## FIGURE 24. V.11 RECEIVER INPUT CURRENT WITH TERMINATION

## FIGURE 25. V.11 RECEIVER INPUT IV GRAPH WITH TERMINATION

FIGURE 26. V.35 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 27. V.35 DRIVER OUTPUT SOURCE IMPEDANCE

FIGURE 28. V.35 DRIVER OUTPUT SHORT-CIRCUIT IMPEDANCE

FIGURE 29. V.35 DRIVER OUTPUT RISE/FALL TIME

FIGURE 30. V.35 RECEIVER INPUT SOURCE IMPEDANCE

## FIGURE 31. V.35 RECEIVER INPUT SHORT-CIRCUIT IMPEDANCE

FIGURE 32. DRIVER OUTPUT CURRENT LEAKAGE TEST

Any one of the three conditions for disabling the driver.

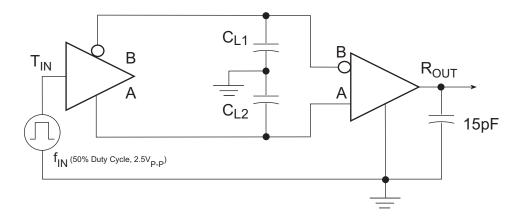

## FIGURE 33. DRIVER / RECEIVER TIMING TEST CIRCUIT

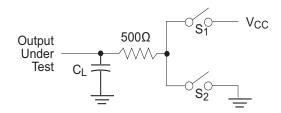

### FIGURE 34. DRIVER TIMING TEST LOAD CIRCUIT

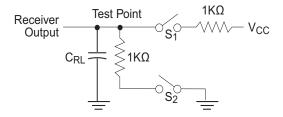

## FIGURE 35. RECEIVER TIMING TEST LOAD CIRCUIT

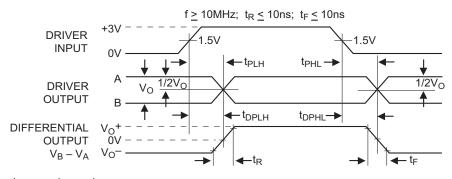

#### FIGURE 36. DRIVER PROPAGATING DELAYS

t<sub>SKEW</sub> = | t<sub>DPLH</sub> - t<sub>DPHL</sub> |

### FIGURE 37. DRIVER ENABLE AND DISABLE TIMES

### FIGURE 38. RECEIVER PROPAGATION DELAYS

### FIGURE 39. RECEIVER ENABLE AND DISABLE TIMES

# FIGURE 40. V.28 (RS-232) AND V.10 (RS-423) DRIVER ENABLE AND DISABLE TIMES

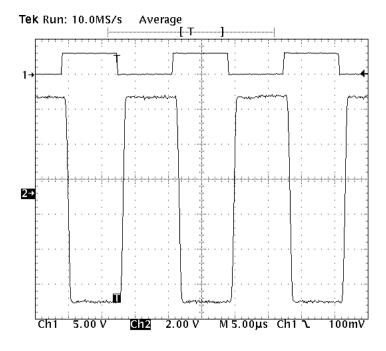

## FIGURE 41. TYPICAL V.28 DRIVER OUTPUT WAVEFORM

## FIGURE 42. TYPICAL V.10 DRIVER OUTPUT WAVEFORM

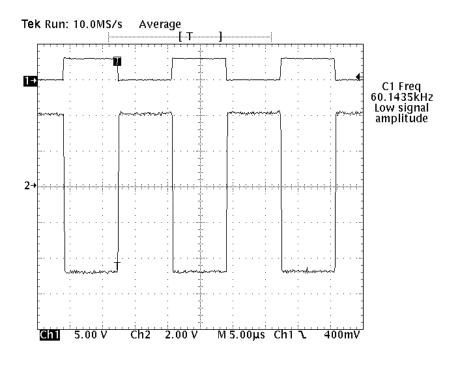

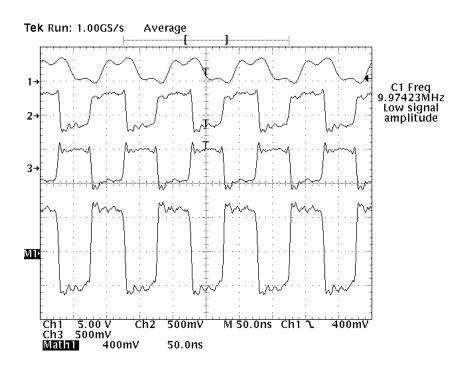

FIGURE 43. TYPICAL V.11 DRIVER OUTPUT WAVEFORM

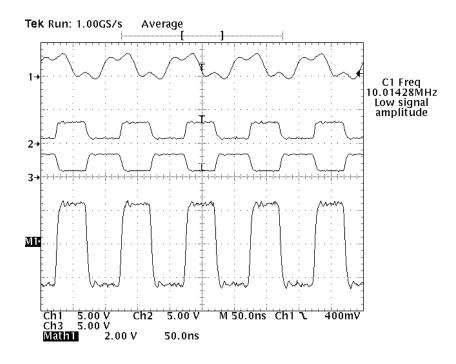

MAXLINEAR

## FIGURE 44. TYPICAL V.35 DRIVER OUTPUT WAVEFORM

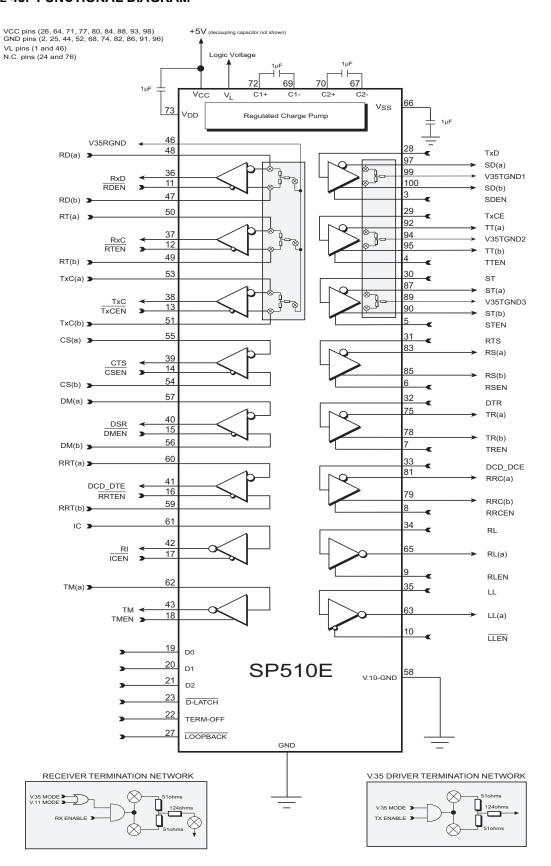

### FIGURE 45. FUNCTIONAL DIAGRAM

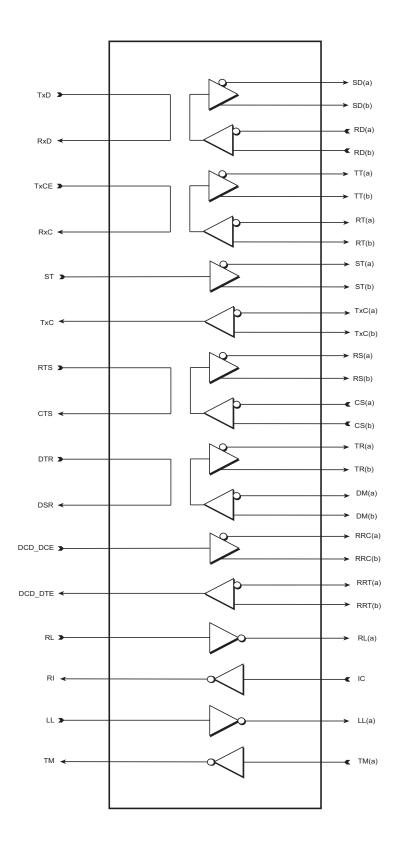

## FIGURE 46. SP510E LOOPBACK PATH

FIG#RE

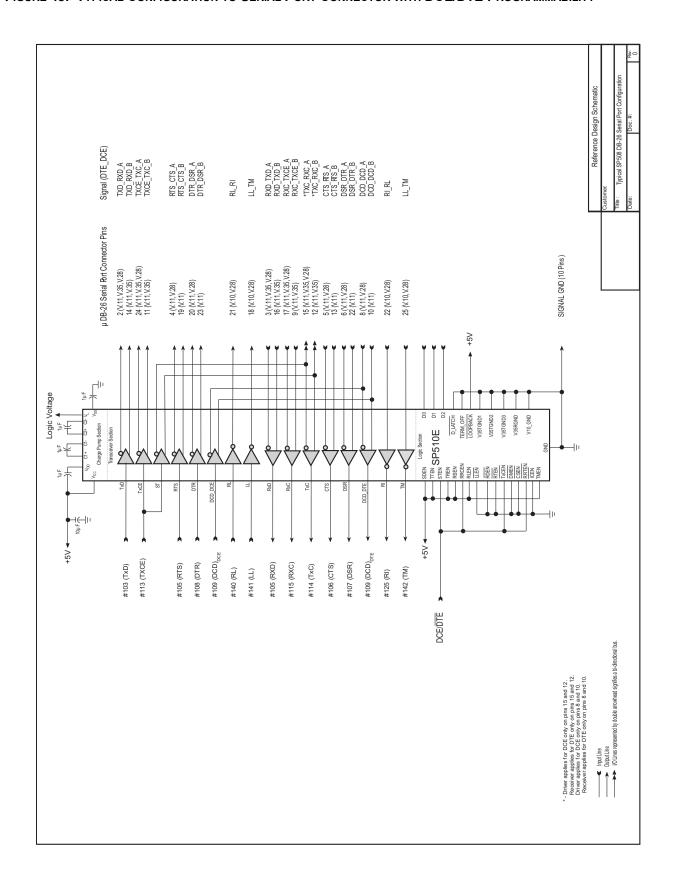

### FIGURE 48. TYPICAL CONFIGURATION TO SERIAL PORT CONNECTOR WITH DCE/DTE PROGRAMMABILITY

#### **Thermal Considerations**

High speed devices like the SP510E dissipate heat during normal operation. Actual power dissipation is a function of the switching frequency and loading. For maximum system performance and reliability designers should ensure sufficient air flow. Other commonly used methods for managing heat include heat sinks for higher powered devices, forced air flow (fans) and lower density board stuffing.

## **PCB Design**

The use of multi layer printed circuit boards is recommended to provide both a better ground plane and a thermal path for heat dissipation. If possible, the ground plane should face the bottom of the package to form the thermal conduction plane. Two-sided printed circuit boards may be used where board dimensions and package count are small, but multi-layer boards allow for improved signal routing as well as improved signal integrity. A multi-layer board allows microstrip line techniques for high speed signal interconnections when the high speed signal lines on the inner layers.

#### **ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER**

#### **REVISION HISTORY**

| DATE          | REVISION | DESCRIPTION                                                            |

|---------------|----------|------------------------------------------------------------------------|

| July 2012     | 1.0.0    | Production Release                                                     |

| February 2014 | 1.0.1    | Updated Exar logo and package drawing, corrected typo in tables 5 & 6. |

| January 2020  | 1.0.2    | Update to MaxLinear logo. Update ordering information.                 |

MaxLinear, Inc. 5966 La Place Court, Suite 100 Carlsbad, CA 92008 760.692.0711 p. 760.444.8598 f. www.maxlinear.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, and any MaxLinear trademarks, MxL, Full-Spectrum Capture, FSC, G.now, AirPHY and the MaxLinear logo are all on the products sold, are all trademarks of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved. Other company trademarks and product names appearing herein are the property of their respective owners.

© 2012 - 2020 MaxLinear, Inc. All rights reserved.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - Specialised category:

Click to view products by MaxLinear manufacturer:

Other Similar products are found below:

CY7C910-51LMB MEC1632-AUE RKSAS4 HMC677G32 LPC47N207-JV FTP-637DSL633R SM712GX04LF04-BA MCW1001A-I/SS HOA6241-001 SC74HC4066ADTR2G NCN5120MNTWG NCN5150DR2G NCN8025MTTBG C100N50Z4A DG407AK/883B SRT2-ATT01 TDA8035HN/C1/S1J LTC1694CS5#TRMPBF DS90UB947TRGCRQ1 SP510ECF-L NCS2300MUTAG ADG1404YCPZ-REEL HMC677LP5E HMC677LP5ETR LTC1756EGN#PBF LTC1955EUH#PBF LT3669EUFD-2#PBF LTC6820HMS#3ZZTRPBF MXL1543BCAI MAX3170CAI+ XL1192D CP82C59AZ KTU1109EFAA-TR CH368L CH7307C-DEF LTC1694-1IS5#TRMPBF LTC1694CS5#TRPBF LTC1694IS5#TRM LTS 25-NP 73S8024RN-20IMF 73S8024RN-IL/F DS2413P+ DS2413P+T&R DS28E17Q+ DS8113-RNG+ MAX13036ATI+ MAX13174ECAG+ MAX216CWN+ MAX3172CAI+ AS8222-HSSM