# ST16C552 ST16C552A

DUAL UART WITH 16-BYTE FIFO AND PARALLEL PRINTER PORT

#### December 2003

# DESCRIPTION

The ST16C552/ST16C552A (552/552A) is a dual universal asynchronous receiver and transmitter (UART) with an added bi-directional parallel port that is directly compatible with a CENTRONICS type printer. The parallel port is designed such that the user can configure it as general purpose I/O interface, or for connection to other printer devices. The 552/552A provides enhanced UART functions with 16 byte FIFO's, a modem control interface, and data rates up to 1.5Mbps. Onboard status registers provide the user with error indications and operational status. The system interrupts and control may be tailored to meet user requirements. An internal loop-back capability allows onboard diagnostics. A programmable baud rate generator is provided to select transmit and receive clock rates from 50 bps to 1.5 Mbps. The 552/552A is available in a 68 pin PLCC package. The 552/552A is compatible with the 16C450 and 16C550. The difference between the ST16C552 and ST16C552A is the logic state of the printer port, INTP interrupt. The INTP interrupt is active high (logic 1) on the ST16C552 whereas INTP is active low (logic 0) on the ST16C552A part when the interrupt latch mode is selected. The 552/552A is fabricated in an advanced CMOS process with power down mode to reduce the power consumption. The 552A does not support the power down mode.

/ / / / / / /

# **FEATURES**

Added features in device revision "F" and newer:

- <u>5V Tolerant Inputs</u>

- Pin to pin and functional compatible to ST16C452/ 452PS, TL16C552

- 2.97 to 5.5 volt operation

- Software compatible with INS8250, NS16C550

- 1.5 Mbps transmit/receive operation (24MHz)

- 16 byte transmit FIFO

- 16 byte receive FIFO with error flags

- Independent transmit and receive control

- Modem and printer status registers

- UART port and printer port Bi-directional

- Printer port direction set by single control bit or 8 bit pattern (AA/55)

- Modem control signals (-CTS, -RTS, -DSR, -DTR, -RI, -CD)

- Programmable character lengths (5, 6, 7, 8)

- Even, odd, or no parity bit generation and detection

- TTL compatible inputs, outputs

- Power down mode

PLCC Package

# ORDERING INFORMATION

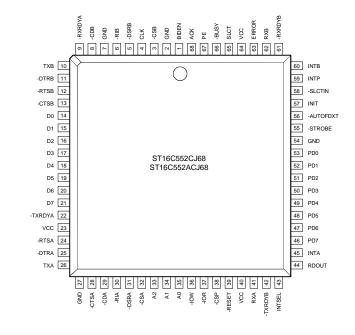

Part number Pins Package **Operating temperature Device Status** ST16C552CJ68 68 PLCC 0° C to + 70° C Active ST16C552ACJ68 68 PLCC 0° C to + 70° C Active ST16C552IJ68 PLCC -40° C to + 85° C 68 Active ST16C552AIJ68 PLCC -40° C to + 85° C 68 Active Rev. 3.40

EXAR Corporation, 48720 Kato Road, Fremont, CA 94538 • (510) 668-7000 • FAX (510) 668-7017

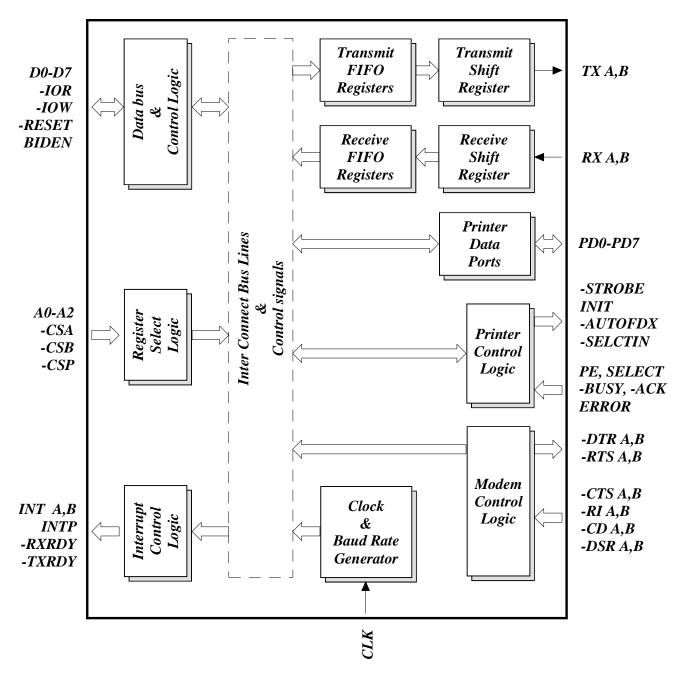

Figure 1, Block Diagram

Rev. 3.40

**XPEXAR**

ST16C552/552A

# SYMBOL DESCRIPTION

| Symbol    | Pin   | Signal Type | Pin Description                                                                                                                                                                                                                                 |

|-----------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0        | 35    | I           | Address-0 Select Bit - Internal registers address selection.                                                                                                                                                                                    |

| A1        | 34    | I           | Address-1 Select Bit - Internal registers address selection.                                                                                                                                                                                    |

| A2        | 33    | I           | Address-2 Select Bit - Internal registers address selection.                                                                                                                                                                                    |

| -ACK      | 68    | I           | Acknowledge (with internal pull-up) - General purpose input<br>or line printer acknowledge (active low). a logic 0 from the<br>printer, indicates successful data transfer to the print buffer.                                                 |

| -AutoFDXT | 56    | I/O         | General purpose I/O (open drain, with internal pull-up) or<br>automatic line feed (open drain input with internal pull-up).<br>When this signal is low the printer should automatically line<br>feed after each line is printed.                |

| BIDEN     | 1     | I           | Bi-Direction Enable - PD7-PD0 direction select. A logic 0<br>sets the parallel port for I/O Select Register Control. A logic<br>1 sets the parallel port for Control Register Bit-5 Control.                                                    |

| BUSY      | 66    | I           | Busy (with internal pull-up) - General purpose input or line<br>printer busy (active high). can be used as an output from the<br>printer to indicate printer is not ready to accept data.                                                       |

| CLK       | 4     | I           | Clock Input An external clock must be connected to this<br>pin to clock the baud rate generator and internal circuitry<br>(see Programmable Baud Rate Generator). This input is not<br>5V tolerant.                                             |

| -CSA      | 32    | I           | Chip Select A - A logic 0 at this pin enables the serial channel-A UART registers for CPU data transfers.                                                                                                                                       |

| -CSB      | 3     | I           | Chip Select B - A logic 0 at this pin enables the serial channel-B UART registers for CPU data transfers.                                                                                                                                       |

| -CSP      | 38    | I           | Printer Port Chip Select - (active low). A logic 0 at this pin<br>enables the parallel printer port registers and/or PD7-PD0<br>for external CPU data transfers.                                                                                |

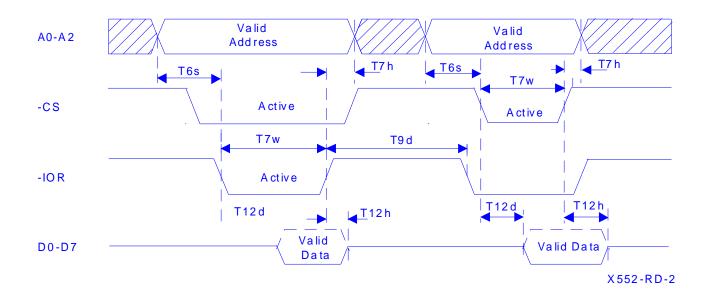

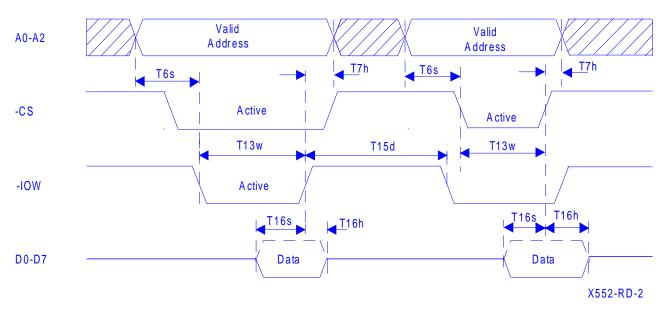

| D0-D7     | 14-21 | I/O         | Data Bus (Bi-directional) - These pins are the eight bit, three state data bus for transferring information to or from the controlling CPU. D0 is the least significant bit and the first data bit in a transmit or receive serial data stream. |

Rev. 3.40

# SYMBOL DESCRIPTION

| Symbol  | Pin          | Signal Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -ERROR  | 63           | I           | Error, Printer (with internal pull-up) - General purpose input<br>or line printer error. This pin may be connected to the active<br>low (logic 0) output of a printer to indicate an error condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GND     | 2,7,54<br>27 | Pwr         | Signal and Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| INIT    | 57           | I/O         | Initialize (open drain, with internal pull-up) - General pur-<br>pose I/O signal. This pin may be connected for initialization<br>service of a connected line printer. Generally when this<br>signal is a logic 0, any connected printer will be initialized.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

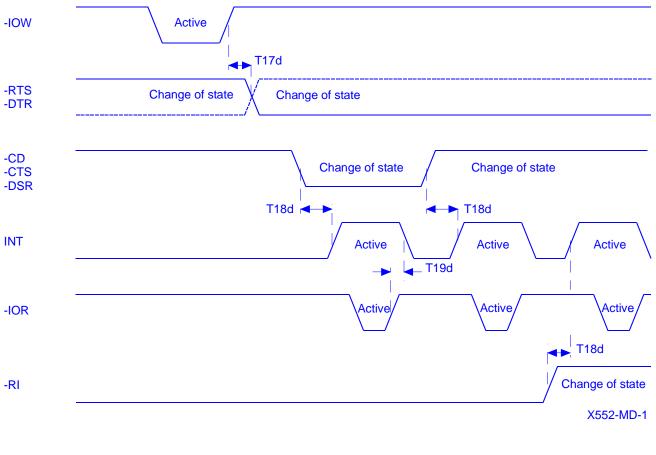

| INT A/B | 45,60        | Ο           | Interrupt output A/B (three state active high) - These pins<br>provide individual channel interrupts, INT A-B. INT A-B are<br>enabled when MCR bit-3 is set to a logic 1, interrupts are<br>enabled in the interrupt enable register (IER), and when an<br>interrupt condition exists. Interrupt conditions include: re-<br>ceiver errors, available receiver buffer data, transmit buffer<br>empty, or when a modem status flag is detected.                                                                                                                                                                                                                                                    |

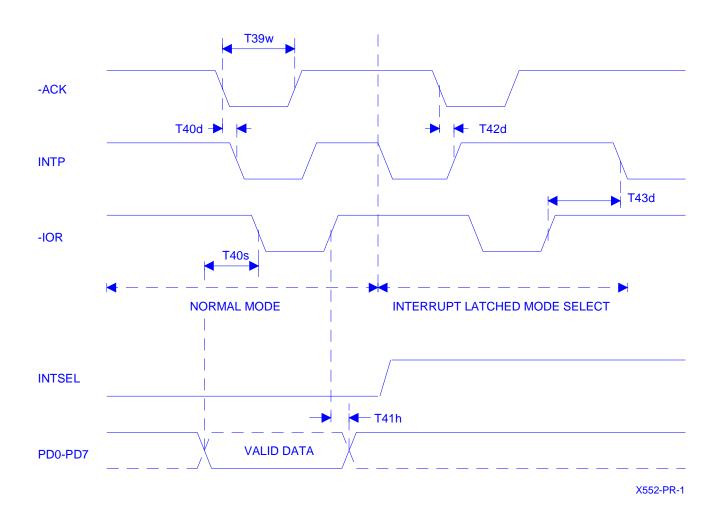

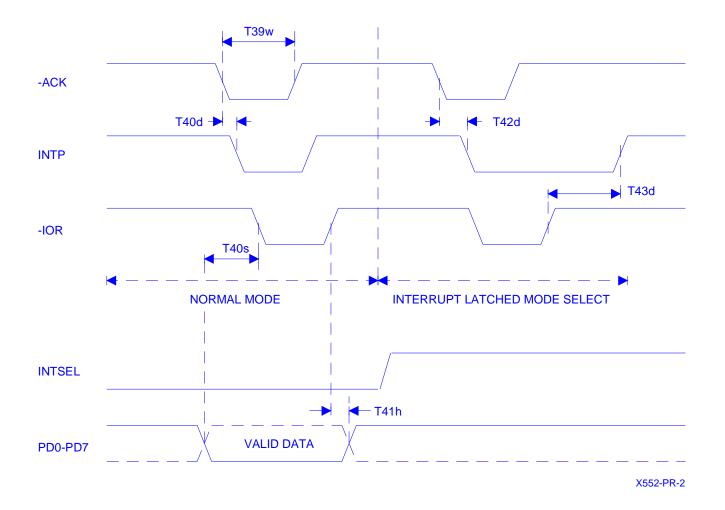

| -INTP   | 59           | Ο           | Printer Interrupt, - This pin can be used to signal the interrupt status of a connected printer. This pin basically tracks the -ACK input pin, When INTSEL is a logic 0 and interrupts are enabled by bit-4 in the control register. A latched mode can be selected by setting INTSEL to a logic 1. In this case the interrupt -INTP is generated normally but does not return to the inactive state until the trailing edge of the read cycle (-IOR pin)INTP is three stated until CON bit-4 is set to a logic 1. The difference between the ST16C552 and ST16C552A is the output state of INTP. INTP is active high (logic 1) on the ST16C552A part when the interrupt latch mode is selected. |

| INTSEL  | 43           | 1           | Interrupt Select mode - This pin selects the interrupt type for<br>the printer port (-INTP). When this pin is a logic 0, the<br>external -ACK signal state is generally followed, minus<br>some minor propagation delay. Making this pin a logic 1 or<br>connecting it to VCC will set the interrupt latched mode. In this<br>case the printer interrupt (-INTP) will not return to a logic 0 on<br>the 552 or a logic 1 on the 552A (552A is inverted), until the                                                                                                                                                                                                                               |

**XPEXAR**

Rev. 3.40

# SYMBOL DESCRIPTION

| Symbol     | Pin   | Signal Type                                                                                                                                                                                                                                                  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |       |                                                                                                                                                                                                                                                              | trailing edge of -IOR (end of the external CPU read cycle).                                                                                                                                                                                                                                                                                                                                                                            |

| -IOR       | 37    | I                                                                                                                                                                                                                                                            | Read strobe A logic 0 transition on this pin will place the contents of an Internal register defined by address bits A0-A2 for either UART channels A/B or A0-A1 for the printer port, onto D0-D7 data bus for a read cycle by an external CPU.                                                                                                                                                                                        |

| -IOW       | 36    | I                                                                                                                                                                                                                                                            | Write strobe A logic 0 transition on this pin will transfer the data on the internal data bus (D0-D7), as defined by either address bits A0-A2 for UART channels A/B or A0-A1 for the printer port, into an internal register during a write cycle from an external CPU.                                                                                                                                                               |

| PD7-PD0    | 46-53 | I/O Printer Data port (Bi-directional three state) - These<br>the eight bit, three state data bus for transferring info<br>to or from an external device (usually a printer). I<br>least significant bit. PD7-PD0 are latched during<br>cycle (output mode). |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PE         | 67    | I                                                                                                                                                                                                                                                            | Paper Empty - General purpose input or line printer paper<br>empty (Internal pull-up). This pin can be connected to<br>provide a printer out of paper indication.                                                                                                                                                                                                                                                                      |

| RDOUT      | 44    | Ο                                                                                                                                                                                                                                                            | Read Out (active high) - This pin goes to a logic 1 when the<br>external CPU is reading data from the 552/552A. This signal<br>can be used to enable/disable external transceivers or other<br>logic functions.                                                                                                                                                                                                                        |

| -RESET     | 39    | I Master Reset (active low) - a logic 0 on this pin will<br>internal registers and all the outputs. The UART tra<br>output and the receiver input will be disabled dur<br>time. (See ST16C552/552A External Reset Cond<br>initialization details.)           |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -RXRDY A/B | 9,61  | Ο                                                                                                                                                                                                                                                            | Receive Ready A/B (active low). This function is associated<br>with the dual channel UARTs and provide the RX FIFO/<br>RHR status for individual receive channels (A-B). A logic 0<br>indicates there is receive data to read/unload, i.e., receive<br>ready status with one or more RX characters available in the<br>FIFO/RHR. This pin is a logic 1 when the FIFO/RHR is<br>empty or when the programmed trigger level has not been |

Rev. 3.40

# SYMBOL DESCRIPTION

| Symbol     | Pin      | Signal Type                                                                                                                              | Pin Description                                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          |                                                                                                                                          | reached.                                                                                                                                                                                                                                                                                                                                                                        |

| SLCT       | 65       | I                                                                                                                                        | Select (with internal pull-up) - General purpose input or line<br>printer select status. Normally this pin is connected to a<br>printer output (active low) that indicates the ready status of<br>a printer, i.e., on-line and/or on-line and ready.                                                                                                                            |

| -SLCTIN    | 58       | I/O                                                                                                                                      | Select In (open drain, with internal pull-up) - General purpose I/O or line printer select. This pin can be read via Bit-3 in the printer command register, or written via bit-3 in the printer control register. As this pin is open-drain, it can be wire-or'd with other outputs. Normally this signal is connected with a printer to select the printer with an active low. |

| -STROBE    | 55       | I/O                                                                                                                                      | Strobe (open drain, with internal pull-up) - General purpose I/O or data strobe output. Normally this output is connected to a printer and indicates that valid data is available at the printer port (PD0-PD7).                                                                                                                                                                |

| -TXRDY A/B | 22,42    | Ο                                                                                                                                        | Transmit Ready A/B (active low). These outputs provide the TX FIFO/THR status for individual transmit channels (A-B). As such, an individual channel's -TXRDY A-B buffer ready status is indicated by logic 0, i.e., at least one location is empty and available in the FIFO or THR. This pin goes to a logic 1 when there are no more empty locations in the FIFO or THR.     |

| vcc        | 23,40,64 | Pwr 2.97 to 5.5V power supply input. All inputs are 5<br>except for XTAL1 and all printer port inputs for dev<br>revision "F" and newer. |                                                                                                                                                                                                                                                                                                                                                                                 |

| -CD A/B    | 29,8     | I                                                                                                                                        | Carrier Detect (active low) - These inputs are associated<br>with individual UART channels A through B. A logic 0 on this<br>pin indicates that a carrier has been detected by the modem<br>for that channel.                                                                                                                                                                   |

| -CTS A/B   | 28,13    | I                                                                                                                                        | Clear to Send (active low) - These inputs are associated with<br>individual UART channels, A through B. A logic 0 on this pin(s)<br>indicates the modem or data set is ready to accept transmit<br>data from the 552/552A for the given channel. Status can be<br>tested by reading MSR bit-4 for that channel(s)CTS has no                                                     |

**XPEXAR**

Rev. 3.40

/ / / / / / / / / / / / / / /

# SYMBOL DESCRIPTION

| Symbol   | Pin   | Signal Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -DSR A/B | 31,5  | I           | effect on the transmit or receive operation.<br>Data Set Ready (active low) - These inputs are associated<br>with individual UART channels, A through B. A logic 0 on<br>this pin(s) indicates the modem or data set is powered-on<br>and is ready for data exchange with the UART. This pin has<br>no effect on the UART's transmit or receive operation.                                                                                                                                                                                       |

| -DTR A/B | 25,11 | Ο           | Data Terminal Ready (active low) - These outputs are<br>associated with individual UART channels, A through B. A<br>logic 0 on this pin(s) indicates that the 552/552A is powered-<br>on and ready. This pin can be controlled via the modem<br>control register for channel(s) A-B. Writing a logic 1 to MCR<br>bit-0 will set the -DTR output to logic 0, enabling the modem.<br>This pin will be a logic 1 after writing a logic 0 to MCR bit-<br>0, or after a reset. This pin has no effect on the UART's<br>transmit or receive operation. |

| -RI A/B  | 30,6  | I           | Ring Indicator (active low) - These inputs are associated<br>with individual UART channels, A through B. A logic 0 on<br>this pin(s) indicates the modem has received a ringing<br>signal from the telephone line(s). A logic 1 transition on this<br>input pin will generate an interrupt for the ringing channel(s).<br>This pin does not have any effect on the transmit or receive<br>operation.                                                                                                                                             |

| -RTS A/B | 24,12 | Ο           | Request to Send (active low) - These outputs are associated<br>with individual UART channels, A through B. A logic 0 on the<br>-RTS pin(s) indicates the transmitter has data ready and<br>waiting to send for the given channel(s). Writing a logic 1 in<br>the modem control register (MCR bit-1) will set this pin to a<br>logic 0 indicating data is available. After a reset this pin will<br>be set to a logic 1. This pin does not have any effect on the<br>transmit or receive operation.                                               |

| RX A/B   | 41,62 | Ι           | Receive Data Input, RX A-B These inputs are associated<br>with individual serial channel(s) to the 552. The RX signal will<br>be a logic 1 during reset, idle (no data), or when the transmitter<br>is disabled. During the local loop-back mode, the RX input<br>pins are disabled and TX data is internally connected to the                                                                                                                                                                                                                   |

Rev. 3.40

| Symbol | Pin   | Signal Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX A/B | 26,10 | Ο           | UARTRX Inputs, internally.<br>Transmit Data, TX A-B - These outputs are associated with<br>individual serial transmit channel(s) from the 552/552A.<br>The TX signal will be a logic 1 during reset, idle (no data),<br>or when the transmitter is disabled. During the local loop-<br>back mode, the TX output pins are disabled and TX data is<br>internally connected to the UART RX Inputs. |

# **GENERAL DESCRIPTION**

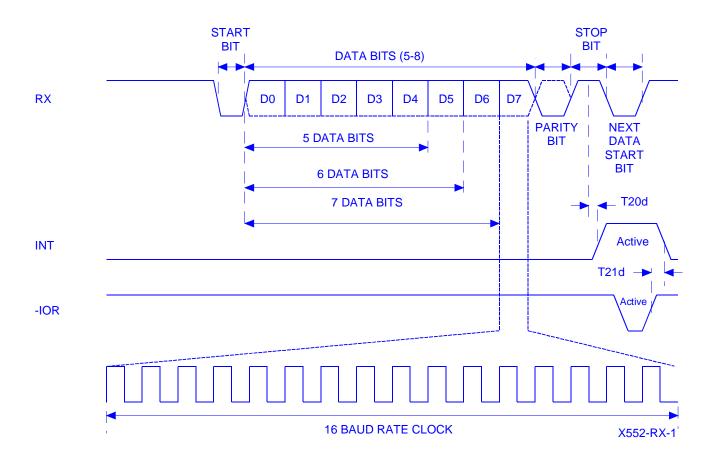

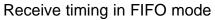

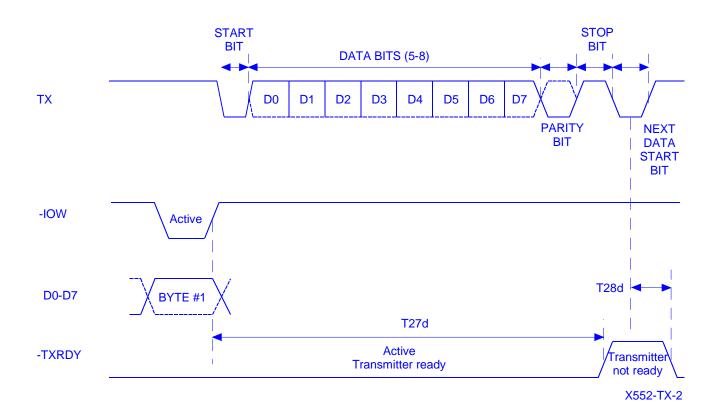

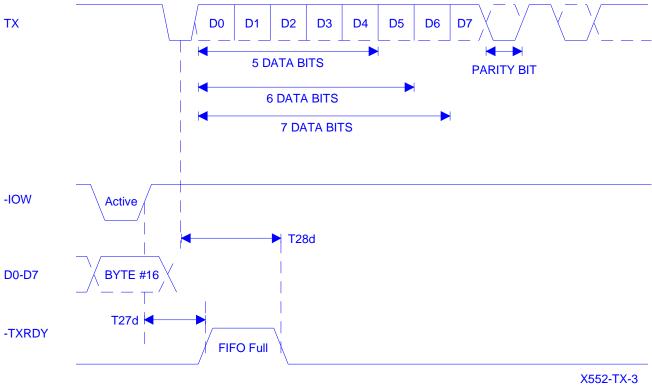

The 552/552A provides serial asynchronous receive data synchronization, parallel-to-serial and serial-toparallel data conversions for both the transmitter and receiver sections. These functions are necessary for converting the serial data stream into parallel data that is required with digital data systems. Synchronization for the serial data stream is accomplished by adding start and stops bits to the transmit data to form a data character (character orientated protocol). Data integrity is insured by attaching a parity bit to the data character. The parity bit is checked by the receiver for any transmission bit errors. The electronic circuitry to provide all these functions is fairly complex especially when manufactured on a single integrated silicon chip. The 552/552A represents such an integration with greatly enhanced features. The 552/552A is fabricated with an advanced CMOS process.

The 552/552A is an upward solution that provides 16 bytes of transmit and receive FIFO memory, instead of none in the 16C452. The 552/552A is designed to work with high speed modems and shared network environments, that require fast data processing time. Increased performance is realized in the 552/552A by the transmit and receive FIFO's. This allows the external processor to handle more networking tasks within a given time. For example, the ST16C452 without a receive FIFO, will require unloading of the RHR in 95.5 microseconds (This example uses a character length of 11 bits, including start/stop bits at 115.2Kbps). This means the external CPU will have to service the receive FIFO every 100 microseconds.

However with the 16 byte FIFO in the 552/552A, the data buffer will not require unloading/loading for 1.53 ms. This increases the service interval giving the external CPU additional time for other applications and reducing the overall UART interrupt servicing time. In addition, the 4 selectable levels of FIFO trigger interrupt is uniquely provided for maximum data throughput performance especially when operating in a multi-channel environment. The FIFO memory greatly reduces the bandwidth requirement of the external controlling CPU, increases performance, and reduces power consumption.

**XP EXAR**

The 552/552A combines the package functions of a dual UART and a printer interface on a single integrated chip. The 552/552A UART is indented to be software compatible with the INS8250/NS16C550 while the bi-directional printer interface mode is intended to operate with a CENTRONICS type parallel printer. However, the printer interface is designed such that it may be configured to operate with other parallel printer interface. The 552/552A is available in two versions, the ST16C552 and the ST16C552A. The 552A provides a active low (logic 0) interrupt for the printer port (INTP) while the 552 provides an active high (logic 1) INTP interrupt. Additionally, the 552A does not support the power down feature.

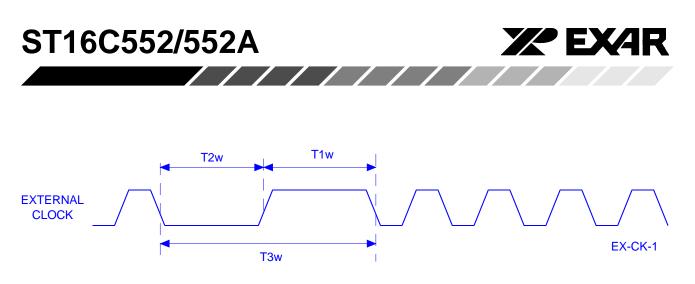

The 552/552A is capable of operation to 1.5Mbps with a 24 MHz external clock input. With an external clock input of 1.8432 MHz the user can select data rates up to 115.2 Kbps.

///////

Rev. 3.40

The rich feature set of the 552/552A is available through internal registers. Selectable receive FIFO trigger levels, selectable TX and RX baud rates, modem interface controls, and a power-down mode are all standard features. Following a power on reset or an external reset, the 552/552A is software compatible with the previous generation, 16C452.

## **FUNCTIONAL DESCRIPTIONS**

## **Functional Modes**

Two functional user modes are selectable for the 552/ 552A package. The first of these provides the dual UART functions, while the other provides the functions of a parallel printer interface. These features are available through selection at the package interface select pins.

### **UARTA-BFunctions**

The UART mode provides the user with the capability to transfer information between an external CPU and the 552/552A package. A logic 0 on chip select pins - CSA or -CSB allows the user to configure, send data, and/or receive data via the UART channels A-B.

## **Printer Port Functions**

The Printer mode provides the user with the capability to transfer information between an external CPU and the 552/552A parallel printer port. A logic 0 on chip select pin -CSP allows the user to configure, send data, and/ or receive data via the bi-directional parallel 8-bit data bus, PD0-PD7.

### **Internal Registers**

The 552/552A provides 12 internal registers for monitoring and control of the UART functions and another 6 registers for monitoring and controlling the printer port. These resisters are shown in Table 4 below. The UART registers function as data holding registers (THR/RHR), interrupt status and control registers (IER/ISR), a FIFO control register (FCR), line status and control registers (LCR/LSR), modem status and control registers (MCR/ MSR), programmable data rate (clock) control registers (DLL/DLM), and a user assessable scratchpad register (SPR). The printer port registers functions data holding registers (PR), I/O status register (SR), I/O select register (IOSEL), and a command and control register (COM/CON). Register functions are more fully described in the following paragraphs.

Rev. 3.40

# Table 4, INTERNAL REGISTER DECODE

| A2               | A1                                                                      | A0               | READMODE                                                                                    | WRITEMODE                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Gen              | General Register Set (THR/RHR, IER/ISR, MCR/MSR, LCR/LSR, SPR): Note 1* |                  |                                                                                             |                                                                                                          |  |  |  |  |  |  |

| 0<br>0<br>0      | 0<br>0<br>1<br>1                                                        | 0<br>1<br>0<br>1 | Receive Holding Register<br>Interrupt Status Register                                       | Transmit Holding Register<br>Interrupt Enable Register<br>FIFO Control Register<br>Line Control Register |  |  |  |  |  |  |

| 1<br>1<br>1<br>1 | 0<br>0<br>1<br>1                                                        | 0<br>1<br>0<br>1 | Line Status Register<br>Modem Status Register<br>Scratchpad Register                        | Modem Control Register<br>Scratchpad Register                                                            |  |  |  |  |  |  |

| Bau              | d Rate F                                                                | Register         | · Set (DLL/DLM): Note *2                                                                    |                                                                                                          |  |  |  |  |  |  |

| 0<br>0           | 0<br>0                                                                  | 0<br>1           | LSB of Divisor Latch<br>MSB of Divisor Latch                                                | LSB of Divisor Latch<br>MSB of Divisor Latch                                                             |  |  |  |  |  |  |

| Prin             | Printer Port Set (PR/SR/IOSEL/COM/CON): Note *3                         |                  |                                                                                             |                                                                                                          |  |  |  |  |  |  |

| X<br>X<br>X      | 0<br>0<br>1                                                             | 0<br>1<br>0      | PORT REGISTERPORT REGISTERSTATUS REGISTERI/O SELECT REGISTECOMMAND REGISTERCONTROL REGISTER |                                                                                                          |  |  |  |  |  |  |

Note 1\* The General Register set is accessible only when CS A or CS B is a logic 0.

Note 2\* The Baud Rate register set is accessible only when CS A or CS B is a logic 0 and LCR bit-7 is a logic 1. Note 3\*: Printer Port Register set is accessible only when -CSP is a logic 0 in conjunction with the states of the interface signal BIDEN and Printer Control Register bit-5 or IOSEL register.

/ / / / / / / / / / / / / / /

## **FIFO Operation**

The 16 byte transmit and receive data FIFO's are enabled by the FIFO Control Register (FCR) bit-0. The user can set the receive trigger level via FCR bits 6/ 7 but not the transmit trigger level. The transmit interrupt trigger level is set to 16 following a reset. The receiver FIFO section includes a time-out function to ensure data is delivered to the external CPU. An interrupt is generated whenever the Receive Holding Register (RHR) has not been read following the loading of a character or the receive trigger level has not been reached.

## Hardware/Software and Time-out Interrupts

The interrupts are enabled by IER bits 0-3. Care must be taken when handling these interrupts. Following a reset the transmitter interrupt is enabled, the 552/552A will issue an interrupt to indicate that transmit holding register is empty. This interrupt must be serviced prior to continuing operations. The LSR register provides the current singular highest priority interrupt only. It could be noted that CTS and RTS interrupts have lowest interrupt priority. A condition can exist where a higher priority interrupt may mask the lower priority CTS/RTS interrupt(s). Only after servicing the higher pending interrupt will the lower priority CTS/RTS interrupt (s) be reflected in the status register. Servicing the interrupt without investigating further interrupt conditions can result in data errors.

When two interrupt conditions have the same priority, it is important to service these interrupts correctly. Receive Data Ready and Receive Time Out have the same interrupt priority (when enabled by IER bit-3). The receiver issues an interrupt after the number of characters have reached the programmed trigger level. In this case the 552/552A FIFO may hold more characters than the programmed trigger level. Following the removal of a data byte, the user should recheck LSR bit-0 for additional characters. A Receive Time Out will not occur if the receive FIFO is empty. The time out counter is reset at the center of each stop bit received or each time the receive holding register (RHR) is read (see Figure 4, Receive Time-out Interrupt). The actual time out value is T (Time out length in bits) = 4 X

P (**P**rogrammed word length) + 12. To convert the time out value to a character value, the user has to consider the complete word length, including data information length, start bit, parity bit, and the size of stop bit, i.e., 1X, 1.5X, or 2X bit times.

Example -A: If the user programs a word length of 7, with no parity and one stop bit, the time out will be: T = 4 X 7(programmed word length) +12 = 40 bit times. The character time will be equal to 40 / 9 = 4.4 characters, or as shown in the fully worked out example: T = [(programmed word length = 7) + (stop bit = 1) + (start bit = 1) = 9]. 40 (bit times divided by 9) = 4.4 characters.

Example -B: If the user programs the word length = 7, with parity and one stop bit, the time out will be:  $T = 4 \times 7$ (programmed word length) + 12 = 40 bit times. Character time = 40 / 10 [ (programmed word length = 7) + (parity = 1) + (stop bit = 1) + (start bit = 1) = 4 characters.

## Programmable Baud Rate Generator

The 552/552A supports high speed modem technologies that have increased input data rates by employing data compression schemes. For example a 33.6Kbps modem that employs data compression may require a 115.2Kbps input data rate. A 128.0Kbps ISDN modem that supports data compression may need an input data rate of 460.8Kbps. The 552/552A can support a standard data rate of 921.6Kbps.

Single baud rate generator is provided for the transmitter and receiver, allowing independent TX/RX channel control. The programmable Baud Rate Generator is capable of accepting an input clock up to 24 MHz, as required for supporting a 1.5Mbps data rate. The 552/552A requires that an external clock source be connected to the CLK input pin to clock the internal baud rate generator for standard or custom rates. (see Baud Rate Generator Programming below).

The generator divides the input 16X clock by any divisor from 1 to  $2^{16}$ -1. The 552/552A divides the basic external clock by 16. The basic 16X clock provides table rates to support standard and custom applications using the

Rev. 3.40

same system design. The rate table is configured via the DLL and DLM internal register functions. Customized Baud Rates can be achieved by selecting the proper divisor values for the MSB and LSB sections of baud rate generator.

for selecting the desired final baud rate. The example in Table 5 below, shows the selectable baud rate table available when using a 1.8432 MHz external clock input.

Programming the Baud Rate Generator Registers DLM (MSB) and DLL (LSB) provides a user capability

| Output<br>Baud Rate<br>MCR | Output<br>16 x Clock<br>Divisor<br>(Decimal) | 16 x Clock 16 x Clock<br>Divisor Divisor |    | DLL<br>Program<br>Value<br>(HEX) |

|----------------------------|----------------------------------------------|------------------------------------------|----|----------------------------------|

| 50                         | 2304                                         | 900                                      | 09 | 00                               |

| 110                        | 1047                                         | 417                                      | 04 | 17                               |

| 150                        | 768                                          | 300                                      | 03 | 00                               |

| 300                        | 384                                          | 180                                      | 01 | 80                               |

| 600                        | 192                                          | C0                                       | 00 | C0                               |

| 1200                       | 96                                           | 60                                       | 00 | 60                               |

| 2400                       | 48                                           | 30                                       | 00 | 30                               |

| 4800                       | 24                                           | 18                                       | 00 | 18                               |

| 7200                       | 16                                           | 10                                       | 00 | 10                               |

| 9600                       | 12                                           | 0C                                       | 00 | 0C                               |

| 19.2k                      | 6                                            | 06                                       | 00 | 06                               |

| 38.4k                      | 3                                            | 03                                       | 00 | 03                               |

| 57.6k                      | 2                                            | 02                                       | 00 | 02                               |

| 115.2k                     | 1                                            | 01                                       | 00 | 01                               |

## Table 5, BAUD RATE GENERATOR PROGRAMMING TABLE (1.8432 MHz CLOCK):

## Rev. 3.40

## **DMA Operation**

The 552/552A FIFO trigger level provides additional flexibility to the user for block mode operation. LSR bits 5-6 provide an indication when the transmitter is empty or has an empty location(s). The user can optionally operate the transmit and receive FIFO's in the DMA mode (FCR bit-3). When the transmit and receive FIFO's are enabled and the DMA mode is deactivated (DMA Mode "0"), the 552/552A activates the interrupt output pin for each data transmit or receive operation. When DMA mode is activated (DMA Mode "1"), the user takes the advantage of block mode operation by loading or unloading the FIFO in a block sequence determined by the receive trigger level and the transmit FIFO. In this mode, the 552/552A sets the interrupt output pin when characters in the transmit FIFO is below 16, or the characters in the receive FIFO's are above the receive trigger level.

## **Power Down Mode**

The 552 is designed to operate with low power consumption. The 552 (only) is designed with a special power down mode to further reduce power consumption when the chip is not being used. When MCR bit-7 and IER bit-5 are enabled (set to a logic 1), the 552 powers down. The use of two power down enable bits helps to prevent accidental software shut-down. The 552 will remain powered down until disabled by setting either IER bit-5 or MCR bit-7 to a logic 0.

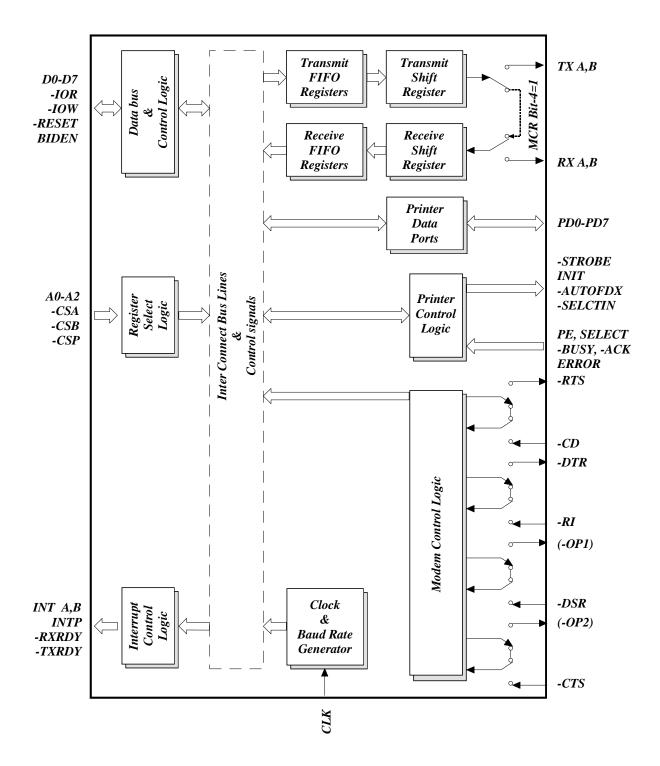

### Loop-back Mode

The internal loop-back capability allows onboard diagnostics. In the loop-back mode the normal modem interface pins are disconnected and reconfigured for loop-back internally. MCR register bits 0-3 are used for controlling loop-back diagnostic testing. In the loop-back mode INT enable and MCR bit-2 in the MCR register (bits 2,3) control the modem -RI and -CD inputs respectively. MCR signals -DTR and -RTS (bits 0-1) are used to control the modem -CTS and -DSR inputs respectively. The transmitter output (TX) and the receiver input (RX) are disconnected from their associated interface pins, and instead are connected together internally (See Figure 6). The -CTS, -DSR, -CD, and -RI are disconnected from their normal modem control inputs pins, and instead are connected internally to -DTR, -RTS, INT enable and MCR bit-2. Loopback test data is entered into the transmit holding register via the user data bus interface, D0-D7. The transmit UART serializes the data and passes the serial data to the receive UART via the internal loop-back connection. The receive UART converts the serial data back into parallel data that is then made available at the user data interface, D0-D7. The user optionally compares the received data to the initial transmitted data for verifying error free operation of the UART TX/RX circuits.

In this mode, the receiver and transmitter interrupts are fully operational. The Modem Control Interrupts are also operational. However, the interrupts can only be read using lower four bits of the Modem Control Register (MCR bits 0-3) instead of the four Modem Status Register bits 4-7. The interrupts are still controlled by the IER.

## Figure 6, INTERNAL LOOP-BACK MODE DIAGRAM

Rev. 3.40

## **Printer Port**

The 552/552A contains a general purpose 8-bit parallel interface port that is designed to directly interface with a CENTRONICS Printer. A number of the control/ interrupt signals and the 8-bit data bus have been designed as bi-directional data buses. This allows the interface to function with other device parallel data bus applications. Signal -ACK is used to generate an -INTP interface interrupt that would normally be connected to the user CPU. -INTP can be made to follow the -ACK signal, normal mode (see Figure 7) or it can be configured for the latch mode. In the latch mode the interrupt is not cleared until printer status register (SR) is read. Another signal (INIT) can be made to function as an outgoing or incoming interrupt, or combined with other interrupts to provide a common wire-or interrupt output. Interface signals -STROBE, -AutoFDXT, and -SLCTIN are bi-directional and can be used as combinations of input and/or output functions. The signals have internal pull-up resistors and can be wire-or'd. Normally, -STROBE is used to strobe PD0-PD7 bus data into a printer input buffer. -SLCTIN normally selects the printer while AutoFDXT signals the printer to auto-linefeed. Other signals provide similar printer functions but are not bi-directional. The printer functions for these signals are described in table 1, Symbol Description.

The interface provides a mode steering signal called BIDEN. BIDEN controls the bi-directional 8-bit data bus (PD0-PD7) direction, input or output. When BIDEN is a logic 1 a single control bit (D5) in the control register sets the input or output mode. Setting BIDEN to a logic 0 however sets an IBM interface compatible mode. In this mode the bus direction (input/output) is set by eight data bits in the IOSEL register. An AA (Hex) pattern sets the input mode while a 55 (hex) pattern sets the output mode. I/O direction is depicted in Table 6 below.

| PORTDIRECTION | BIDEN | CONTROL REGISTER (D5) | I/O SELECT REGISTER |

|---------------|-------|-----------------------|---------------------|

| Input mode    | 0     | X (Note 4)            | AA Hex              |

| Output mode   | 0     | X (Note 4)            | 55 Hex              |

| Output mode   | 1     | 0                     | X (Note 4)          |

| Input mode    | 1     | 1                     | X (Note 4)          |

## Table 6, PD0-PD7 I/O DIRECTION MODE SELECTION

Note: 4 = don't care

Rev. 3.40

# **REGISTER FUNCTIONAL DESCRIPTIONS**

The following table delineates the assigned bit functions for the eighteen 552/552A internal registers. The assigned bit functions are more fully defined in the following paragraphs.

| A2 | A1       | A0    | Register<br>[Default] | BIT-7                      | BIT-6                    | BIT-5                     | BIT-4              | BIT-3                        | BIT-2                                  | BIT-1                                        | BIT-0                          |

|----|----------|-------|-----------------------|----------------------------|--------------------------|---------------------------|--------------------|------------------------------|----------------------------------------|----------------------------------------------|--------------------------------|

|    | <u> </u> | norol | Note 5*               | ot: Noto                   | 4*                       |                           |                    |                              |                                        |                                              |                                |

|    | Ge       | neral | Register S            | et: Note                   | 1 <sup></sup>            |                           | •                  | 1                            |                                        |                                              |                                |

| 0  | 0        | 0     | RHR [XX]              | bit-7                      | bit-6                    | bit-5                     | bit-4              | bit-3                        | bit-2                                  | bit-1                                        | bit-0                          |

| 0  | 0        | 0     | THR [XX]              | bit-7                      | bit-6                    | bit-5                     | bit-4              | bit-3                        | bit-2                                  | bit-1                                        | bit-0                          |

| 0  | 0        | 1     | IER [00]              | 0                          | 0                        | En<br>Pwr<br>down<br>mode | 0                  | Modem<br>Status<br>Interrupt | Receive<br>Line<br>Status<br>interrupt | Transmit<br>Holding<br>Register<br>interrupt | Receive<br>Holding<br>Register |

| 0  | 1        | 0     | FCR [00]              | RCVR<br>trigger<br>(MSB)   | RCVR<br>trigger<br>(LSB) | 0                         | 0                  | DMA<br>mode<br>select        | XMIT<br>FIFO<br>reset                  | RCVR<br>FIFO<br>reset                        | FIFO<br>enable                 |

| 0  | 1        | 0     | ISR [01]              | FIFO's<br>enabled          | FIFO's<br>enabled        | 0                         | 0                  | INT<br>priority<br>bit-2     | INT<br>priority<br>bit-1               | INT<br>priority<br>bit-0                     | INT<br>status                  |

| 0  | 1        | 1     | LCR [00]              | divisor<br>latch<br>enable | set<br>break             | set<br>parity             | even<br>parity     | parity<br>enable             | stop<br>bits                           | word<br>length<br>bit-1                      | word<br>length<br>bit-0        |

| 1  | 0        | 0     | MCR [00]              | Pwr<br>down                | 0                        | 0                         | loop<br>back       | INT A/B<br>enable            | [X]                                    | -RTS                                         | -DTR                           |

| 1  | 0        | 1     | LSR [60]              | FIFO<br>data<br>error      | THR &<br>TSR<br>empty    | THR.<br>empty             | break<br>interrupt | framing<br>error             | parity<br>error                        | overrun<br>error                             | receive<br>data<br>ready       |

| 1  | 1        | 0     | MSR [X0]              | CD                         | RI                       | DSR                       | CTS                | delta<br>-CD                 | delta<br>-RI                           | delta<br>-DSR                                | delta<br>-CTS                  |

| 1  | 1        | 1     | SPR [FF]              | bit-7                      | bit-6                    | bit-5                     | bit-4              | bit-3                        | bit-2                                  | bit-1                                        | bit-0                          |

|    | Sp       | ecial | Register Se           | et: Note *                 | 2                        |                           |                    |                              |                                        |                                              |                                |

| 0  | 0        | 0     | DLL[XX]               | bit-7                      | bit-6                    | bit-5                     | bit-4              | bit-3                        | bit-2                                  | bit-1                                        | bit-0                          |

| 0  | 0        | 1     | DLM [XX]              | bit-15                     | bit-14                   | bit-13                    | bit-12             | bit-11                       | bit-10                                 | bit-9                                        | bit-8                          |

16

# Table 7, ST16C552/552A INTERNAL REGISTERS

Rev. 3.40

| A2 A1 A0 | Register<br>[Default]<br>Note 5* | BIT-7        | BIT-6        | BIT-5            | BIT-4           | BIT-3          | BIT-2 | BIT-1         | BIT-0        |

|----------|----------------------------------|--------------|--------------|------------------|-----------------|----------------|-------|---------------|--------------|

| Printer  | Port Regist                      | er Set: N    | ote 3*       | _                | _               |                |       |               |              |

| [X] 0 0  | PR[00]                           | bit-7        | bit-6        | bit-5            | bit-4           | bit-3          | bit-2 | bit-1         | bit-0        |

| [X] 0 0  | PR[00]                           | bit-7        | bit-6        | bit-5            | bit-4           | bit-3          | bit-2 | bit-1         | bit-0        |

| [X] 0 1  | SR[4F]                           | -Busy        | -ACK         | PE               | SLCT            | Error<br>State | -IRQ  | logic<br>"1"  | logic<br>"1" |

| [X] 0 1  | IOSEL                            | bit-7        | bit-6        | bit-5            | bit-4           | bit-3          | bit-2 | bit-1         | bit-0        |

| [X] 1 0  | COM[E0]                          | logic<br>"1" | logic<br>"1" | logic<br>"1"     | -INTP<br>Enable | -SLCTIN        | INIT  | -Auto<br>FDXT | -STROBE      |

| [X] 1 0  | CON[00]                          | [X]          | [X]          | PD 0-7<br>IN/OUT | -INTP<br>Enable | -SLCTIN        | INIT  | -Auto<br>FDXT | -STROBE      |

Note 1\* The General Register set is accessible only when CS A or CS B is a logic 0.

Note 2\* The Baud Rate register set is accessible only when CS A or CS B is a logic 0 and LCR bit-7 is a logic 1. Note 3\*: Printer Port Register set is accessible only when -CSP is a logic 0 in conjunction with the states of the interface signal BIDEN and Printer Control Register bit-5 or IOSEL register.

Note 5\* The value between the square brackets represents the register's initialized HEX value, X =N/A.

## MODEM (UART) REGISTER DESCRIPTIONS

## Transmit (THR) and Receive (RHR) Holding Registers

The serial transmitter section consists of an 8-bit Transmit Hold Register (THR) and Transmit Shift Register (TSR). The status of the THR is provided in the Line Status Register (LSR). Writing to the THR transfers the contents of the data bus (D7-D0) to the THR, providing that the THR or TSR is empty. The THR empty flag in the LSR register will be set to a logic 1 when the transmitter is empty or when data is transferred to the TSR. Note that a write operation can be performed when the transmit holding register empty flag is set (logic 0 = FIFO full, logic 1= at least one FIFO location available).

The serial receive section also contains an 8-bit Receive Holding Register, RHR. Receive data is removed from the 552/552A and receive FIFO by reading the RHR register. The receive section provides a mechanism to prevent false starts. On the falling edge of a start or false start bit, an internal receiver counter starts counting clocks at the 16x clock rate. After 7 1/2 clocks the start bit time should be shifted to the center of the start bit. At this time the start bit is sampled and if it is still a logic 0 it is validated. Evaluating the start bit in this manner prevents the receiver from assembling a false character. Receiver status codes will be posted in the LSR.

Rev. 3.40

## Interrupt Enable Register (IER)

The Interrupt Enable Register (IER) masks the interrupts from receiver ready, transmitter empty, line status and modem status registers. These interrupts would normally be seen on the INT A,B output pins.

## IER Vs Receive FIFO Interrupt Mode Operation

When the receive FIFO (FCR BIT-0 = a logic 1) and receive interrupts (IER BIT-0 = logic 1) are enabled, the receive interrupts and register status will reflect the following:

A) The receive data available interrupts are issued to the external CPU when the FIFO has reached the programmed trigger level. It will be cleared when the FIFO drops below the programmed trigger level.

B) FIFO status will also be reflected in the user accessible ISR register when the FIFO trigger level is reached. Both the ISR register status bit and the interrupt will be cleared when the FIFO drops below the trigger level.

C) The data ready bit (LSR BIT-0) is set as soon as a character is transferred from the shift register to the receive FIFO. It is reset when the FIFO is empty.

# IER Vs Receive/Transmit FIFO Polled Mode Operation

When FCR BIT-0 equals a logic 1; resetting IER bits 0-3 enables the 552/552A in the FIFO polled mode of operation. Since the receiver and transmitter have separate bits in the LSR either or both can be used in the polled mode by selecting respective transmit or receive control bit(s).

A) LSR BIT-0 will be a logic 1 as long as there is one byte in the receive FIFO.

B) LSR BIT 1-4 will provide the type of errors encountered, if any.

C) LSR BIT-5 will indicate when the transmit FIFO is empty.

D) LSR BIT-6 will indicate when both the transmit FIFO and transmit shift register are empty.

**XPEXAR**

E) LSR BIT-7 will indicate any FIFO data errors.

## IER BIT-0:

This interrupt will be issued when the FIFO has reached the programmed trigger level or is cleared when the FIFO drops below the trigger level in the FIFO mode of operation.

Logic 0 = Disable the receiver ready interrupt. (normal default condition)

Logic 1 = Enable the receiver ready interrupt.

### IER BIT-1:

This interrupt will be issued whenever the THR is empty and is associated with bit-1 in the LSR register. Logic 0 = Disable the transmitter empty interrupt. (normal default condition)

Logic 1 = Enable the transmitter empty interrupt.

## IER BIT-2:

This interrupt will be issued whenever a fully assembled receive character is transferred from the RSR to the RHR/FIFO, i.e., data ready, LSR bit-0. Logic 0 = Disable the receiver line status interrupt. (normal default condition)

Logic 1 = Enable the receiver line status interrupt.

### IER BIT-3:

Logic 0 = Disable the modem status register interrupt. (normal default condition)

Logic 1 = Enable the modem status register interrupt.

# IER BIT -4:

/ / / / / / / / / / / / / / / /

Not Used - initialized to a logic 0.

## IER BIT-5: (ST16C552 only)

Logic 0 = Disable the power down mode. (normal default condition). The ST16C552A does not support the power down mode and this bit is set to "0".

Logic 1 = Enable the power down mode (MCR bit-7 must also be a logic 1 before power down will be activated).

Rev. 3.40

*IER BIT 6-7:* Not Used - initialized to a logic 0.

## **FIFO Control Register (FCR)**

This register is used to enable the FIFO's, clear the FIFO's, set the receive FIFO trigger levels, and select the DMA mode. The DMA, and FIFO modes are defined as follows:

## DMA MODE

<u>Mode 0</u> Set and enable the interrupt for each single transmit or receive operation, and is similar to the ST16C450 mode. Transmit Ready (-TXRDY) will go to a logic 0 when ever an empty transmit space is available in the Transmit Holding Register (THR). Receive Ready (-RXRDY) will go to a logic 0 whenever the Receive Holding Register (RHR) is loaded with a character.

<u>Mode 1</u> Set and enable the interrupt in a block mode operation. The transmit interrupt is set when the transmit FIFO is below the programmed trigger level. -TXRDY remains a logic 0 as long as one empty FIFO location is available. The receive interrupt is set when the receive FIFO fills to the programmed trigger level. However the FIFO continues to fill regardless of the programmed level until the FIFO is full. -RXRDY remains a logic 0 as long as the FIFO fill level is above the programmed trigger level.

## FCR BIT-0:

Logic 0 = Disable the transmit and receive FIFO. (normal default condition)

Logic 1 = Enable the transmit and receive FIFO. <u>This</u> bit must be a "1" when other FCR bits are written to or they will not be programmed.

## FCR BIT-1:

Logic 0 = No FIFO receive reset. (normal default condition)

Logic 1 = Clears the contents of the receive FIFO and resets the FIFO counter logic (the receive shift register is not cleared or altered). This bit will return to a logic 0 after clearing the FIFO.

## FCR BIT-2:

Logic 0 = No FIFO transmit reset. (normal default condition)

Logic 1 = Clears the contents of the transmit FIFO and resets the FIFO counter logic (the transmit shift register is not cleared or altered). This bit will return to a logic 0 after clearing the FIFO.

## FCR BIT-3:

Logic 0 = Set DMA mode "0". (normal default condition)

Logic 1 = Set DMA mode "1."

### Transmit operation in mode "0":

When the 552/552A is in the ST16C450 mode (FIFO's disabled, FCR bit-0 = logic 0) or in the FIFO mode (FIFO's enabled, FCR bit-0 = logic 1, FCR bit-3 = logic 0) and when there are no characters in the transmit FIFO or transmit holding register, the -TXRDY pin will be a logic 0. Once active the -TXRDY pin will go to a logic 1 after the first character is loaded into the transmit holding register.

### Receive operation in mode "0":

When the 552/552A is in mode "0" (FCR bit-0 = logic 0) or in the FIFO mode (FCR bit-0 = logic 1, FCR bit-3 = logic 0) and there is at least one character in the receive FIFO, the -RXRDY pin will be a logic 0. Once active the -RXRDY pin will go to a logic 1 when there are no more characters in the receiver.

### Transmit operation in mode "1":

When the 552/552A is in FIFO mode (FCR bit- $0 = \log c 1$ , FCR bit- $3 = \log c 1$ ), the -TXRDY pin will be a logic 1 when the transmit FIFO is completely full. It will be a logic 0 if one or more FIFO locations are empty.

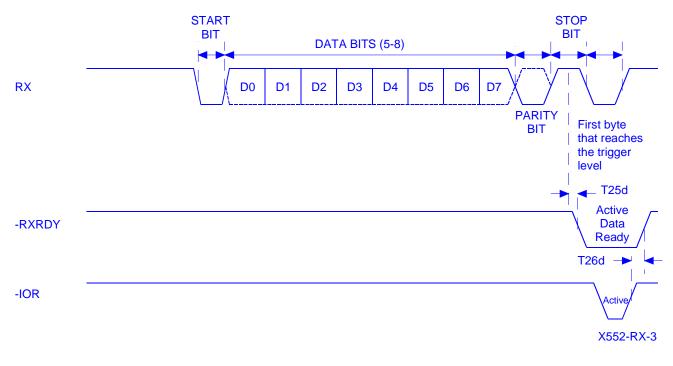

### Receive operation in mode "1":

When the 552/552A is in FIFO mode (FCR bit-0 = logic 1, FCR bit-3 = logic 1) and the trigger level has been reached, or a Receive Time Out has occurred, the -RXRDY pin will go to a logic 0. Once activated, it will go to a logic 1 after there are no more characters in the FIFO.

Rev. 3.40

FCR BIT 4-5: Not Used - initialized to a logic 0.

FCR BIT 6-7: (logic 0 or cleared is the default condition, RX trigger level = 1)

These bits are used to set the trigger level for the receive FIFO interrupt.

An interrupt is generated when the number of characters in the FIFO equals the programmed trigger level. However the FIFO will continue to be loaded until it is full.

| BIT-7 | BIT-6 | RX FIFO trigger level |

|-------|-------|-----------------------|

| 0     | 0     | 01                    |

| 0     | 1     | 04                    |

| 1     | 0     | 08                    |

| 1     | 1     | 14                    |

### Interrupt Status Register (ISR)

The 552/552A provides four levels of prioritized interrupts to minimize external software interaction. The Interrupt Status Register (ISR) provides the user with four interrupt status bits. Performing a read cycle on the ISR will provide the user with the highest pending interrupt level to be serviced. No other interrupts are acknowledged until the pending interrupt is serviced. Whenever the interrupt status register is read, the interrupt status is cleared. However it should be noted that only the current pending interrupt is cleared by the read. A lower level interrupt may be seen after rereading the interrupt status bits. The Interrupt Source Table 8 (below) shows the data values (bits 0-3) for the four prioritized interrupt levels and the interrupt sources associated with each of these interrupt levels:

## Table 8, INTERRUPT SOURCE TABLE

| Priority<br>Level | [ISR BITS]<br>Bit-3 Bit-2 Bit-1 Bit-0 |   |   |   | Source of the interrupt                    |

|-------------------|---------------------------------------|---|---|---|--------------------------------------------|

| 1                 | 0                                     | 1 | 1 | 0 | LSR (Receiver Line Status Register)        |

| 2                 | 0                                     | 1 | 0 | 0 | RXRDY (Received Data Ready)                |

| 2                 | 1                                     | 1 | 0 | 0 | RXRDY (Receive Data time out)              |

| 3                 | 0                                     | 0 | 1 | 0 | TXRDY (Transmitter Holding Register Empty) |

| 4                 | 0                                     | 0 | 0 | 0 | MSR (Modem Status Register)                |

|                   |                                       |   |   |   |                                            |

## ISR BIT-0:

Logic 0 = An interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt service routine.

Logic 1 = No interrupt pending. (normal default condition)

*ISR BIT 1-3: (logic 0 or cleared is the default condition)* These bits indicate the source for a pending interrupt at interrupt priority levels 1, 2, and 3 (See Interrupt Source Table).

*ISR BIT 4-5: (logic 0 or cleared is the default condition)* Not Used - initialized to a logic 0.

*ISR BIT 6-7: (logic 0 or cleared is the default condition)* These bits are set to a logic 0 when the FIFO's are not being used in the 16C450 mode. They are set to a logic 1 when the FIFO's are enabled in the 16C552/552A mode.

## Line Control Register (LCR)

The Line Control Register is used to specify the asynchronous data communication format. The word length, the number of stop bits, and the parity are selected by writing the appropriate bits in this register.

LCR BIT 0-1: (logic 0 or cleared is the default condition)

These two bits specify the word length to be transmitted or received.

| BIT-1 | BIT-0 | Word length |

|-------|-------|-------------|

| 0     | 0     | 5           |

| 0     | 1     | 6           |

| 1     | 0     | 7           |

| 1     | 1     | 8           |

*LCR BIT-2: (logic 0 or cleared is the default condition)* The length of stop bit is specified by this bit in conjunction with the programmed word length.

| I | BIT-2 | Word length | Stop bit<br>length<br>(Bit time(s)) |

|---|-------|-------------|-------------------------------------|

|   | 0     | 5,6,7,8     | 1                                   |

|   | 1     | 5           | 1-1/2                               |

|   | 1     | 6,7,8       | 2                                   |

## LCR BIT-3:

Parity or no parity can be selected via this bit. Logic 0 = No parity. (normal default condition) Logic 1 = A parity bit is generated during the transmission, receiver checks the data and parity for transmission errors.

## LCR BIT-4:

If the parity bit is enabled with LCR bit-3 set to a logic 1, LCR BIT-4 selects the even or odd parity format. Logic 0 = ODD Parity is generated by forcing an odd number of logic 1's in the transmitted data. The receiver must be programmed to check the same format. (normal default condition)

Logic 1 = EVEN Parity is generated by forcing an even the number of logic 1's in the transmitted. The receiver must be programmed to check the same format.

## LCR BIT-5:

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5 = logic 0, parity is not forced. (normal default condition)

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 0, parity bit is forced to a logical 1 for the transmit and receive data.

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 1, parity bit is forced to a logical 0 for the transmit and receive data.

Rev. 3.40

| LCR<br>Bit-5     | LCR<br>Bit-4          |                  |                                                                                         |  |  |

|------------------|-----------------------|------------------|-----------------------------------------------------------------------------------------|--|--|

| X<br>0<br>1<br>1 | X<br>0<br>1<br>0<br>1 | 0<br>1<br>1<br>1 | No parity<br>Odd parity<br>Even parity<br>Force parity odd parity<br>Forced even parity |  |  |

## LCR BIT-6:

When enabled the Break control bit causes a break condition to be transmitted (the TX output is forced to a logic 0 state). This condition exists until disabled by setting LCR bit-6 to a logic 0.

Logic 0 = No TX break condition. (normal default condition)

Logic 1 = Forces the transmitter output (TX) to a logic 0 for alerting the remote receiver to a line break condition.

## LCR BIT-7:

The internal baud rate counter latch and Enhance Feature mode enable.

Logic 0 = Divisor latch disabled. (normal default condition)

Logic 1 = Divisor latch and enhanced feature register enabled.

## Modem Control Register (MCR)

This register controls the interface with the modem or a peripheral device.

## MCR BIT-0:

Logic 0 = Force -DTR output to a logic 1. (normal default condition) Logic 1 = Force -DTR output to a logic 0.

MCR BIT-1:

Logic 0 = Force -RTS output to a logic 1. (normal default condition) Logic 1 = Force -RTS output to a logic 0.

## MCR BIT-2:

This bit is used in the Loop-back mode only. In the

loop-back mode this bit is use to write the state of the modem -RI interface signal.

**XPEXAR**

# *MCR BIT-3:* (Used to control the modem -CD signal in the loop-back mode.)

Logic 0 = Forces INT (A-B) outputs to the three state mode. (normal default condition) In the Loop-back mode, sets -CD internally to a logic 1.

Logic 1 = Forces the INT (A-B) outputs to the active mode. In the Loop-back mode, sets -CD internally to a logic 0.

## MCR BIT-4:

Logic 0 = Disable loop-back mode. (normal default condition)

Logic 1 = Enable local loop-back mode (diagnostics).

MCR BIT 5-6:

Not Used - initialized to a logic 0.

## MCR BIT-7:

Logic 0 = Disable power down mode. (normal, default condition, 552 only)

Logic 1 = Enable power down mode (IER bit-5 must also be a logic 1 before power down will be activated).

## Line Status Register (LSR)

This register provides the status of data transfers between. the 552/552A and the CPU.

## LSR BIT-0:

Logic 0 = No data in receive holding register or FIFO. (normal default condition)

Logic 1 = Data has been received and is saved in the receive holding register or FIFO.

## LSR BIT-1:

Logic 0 = No overrun error. (normal default condition) Logic 1 = Overrun error. A data overrun error occurred in the receive shift register. This happens when additional data arrives while the FIFO is full. In this case the previous data in the shift register is overwritten. Note that under this condition the data byte in the receive shift register is not transferred into the FIFO, therefore the data in the FIFO is not corrupted by the error.

Rev. 3.40

## LSR BIT-2:

Logic 0 = No parity error. (normal default condition) Logic 1 = Parity error. The receive character does not have correct parity information and is suspect. In the FIFO mode, this error is associated with the character at the top of the FIFO.

### LSR BIT-3:

Logic 0 = No framing error. (normal default condition) Logic 1 = Framing error. The receive character did not have a valid stop bit(s). In the FIFO mode this error is associated with the character at the top of the FIFO.

### LSR BIT-4:

Logic 0 = No break condition. (normal default condition)

Logic 1 = The receiver received a break signal (RX was a logic 0 for one character frame time). In the FIFO mode, only one break character is loaded into the FIFO.

## LSR BIT-5:

This bit is the Transmit Holding Register Empty indicator. This bit indicates that the UART is ready to accept a new character for transmission. In addition, this bit causes the UART to issue an interrupt to CPU when the THR interrupt enable is set. The THR bit is set to a logic 1 when a character is transferred from the transmit holding register into the transmitter shift register. The bit is reset to logic 0 concurrently with the loading of the transmitter holding register by the CPU. In the FIFO mode this bit is set when the transmit FIFO is empty; it is cleared when at least 1 byte is written to the transmit FIFO.

### LSR BIT-6:

This bit is the Transmit Empty indicator. This bit is set to a logic 1 whenever the transmit holding register and the transmit shift register are both empty. It is reset to logic 0 whenever either the THR or TSR contains a data character. In the FIFO mode this bit is set to one whenever the transmit FIFO and transmit shift register are both empty.

## LSR BIT-7:

Logic 0 = No Error. (normal default condition) Logic 1 = At least one parity error, framing error or break indication is in the current FIFO data. This bit is cleared when RHR register is read.

## Modem Status Register (MSR)