### E3/DS3/STS-1 LINE INTERFACE UNIT

MAY 2011 REV. 1.1.2

### GENERAL DESCRIPTION

The XRT7300 DS3/E3/STS-1 Line Interface Unit is designed to be used in DS3, E3 or SONET STS-1 applications and consists of a line transmitter and receiver integrated on a single chip.

XRT7300 can be configured to support the E3 (34.368 Mbps), DS3 (44.736 Mbps) or the SONET STS-1 (51.84 Mbps) rates.

In the transmit direction, the XRT7300 encodes input data to either B3ZS (for DS3/STS-1 applications) or HDB3 (for E3 applications) format and converts the data into the appropriate pulse shapes for transmission over coaxial cable via a 1:1 transformer.

In the receive direction the XRT7300 performs equalization on incoming signals, performs Clock Recovery, decodes data from either B3ZS or HDB3 format, converts the receive data into TTL/CMOS format, checks for LOS or LOL conditions and detects and declares the occurrence of line code violations.

The XRT7300 also contains a 4-Wire Microprocessor Serial Interface for accessing the on-chip Command registers.

#### **FEATURES**

- Meets E3/DS3/STS-1 Jitter Tolerance Requirements

- Full Loop-Back Capability

- Transmit and Receive Power Down Modes

- Full Redundancy Support

- Contains a 4-Wire Microprocessor Serial Interface

- · Uses Minimum External components

- Requires Single +5V Power Supply

- -40°C to +85°C Operating Temperature Range

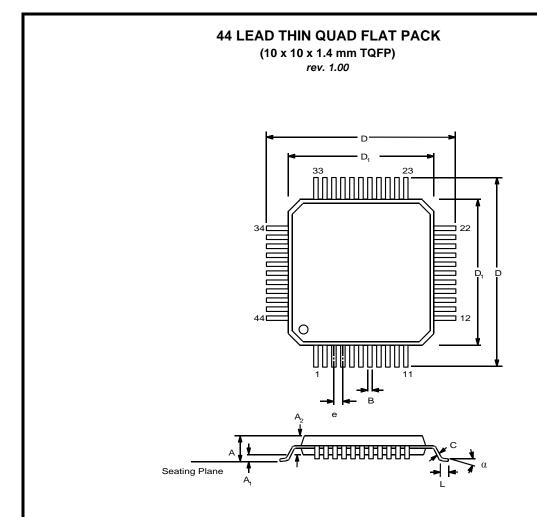

- Available in a 44 pin TQFP package

### **APPLICATIONS**

- Interfaces to E3. DS3 or SONET STS-1 Networks

- CSU/DSU Equipment

- PCM Test Equipment

- Fiber Optic Terminals

- Multiplexers

NOTE: This Device is Protected by US Patent # 6,157,270

# **ORDERING INFORMATION**

| PART NUMBER | PACKAGE TYPE              | OPERATING TEMPERATURE RANGE |

|-------------|---------------------------|-----------------------------|

| XRT7300IV   | 44 Pin TQFP (10mm x 10mm) | -40°C to +85°C              |

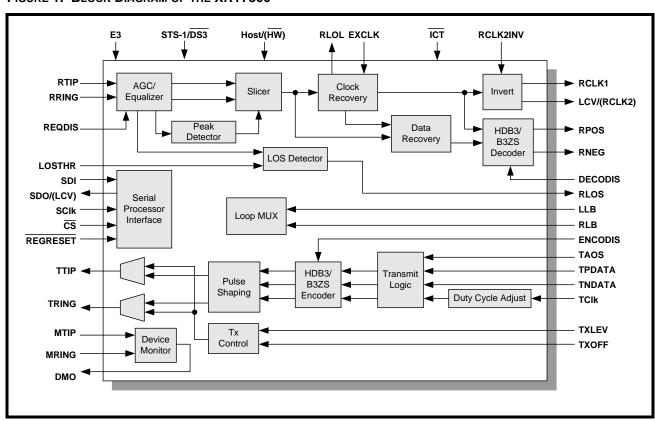

FIGURE 2. PIN OUT OF THE XRT7300 IN THE 44 PIN TQFP

# E3/DS3/STS-1 LINE INTERFACE UNIT

# **TABLE OF CONTENTS**

| General description                                                                                                                      | 1    |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| FEATURESAPPLICATIONS                                                                                                                     | 1    |

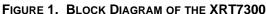

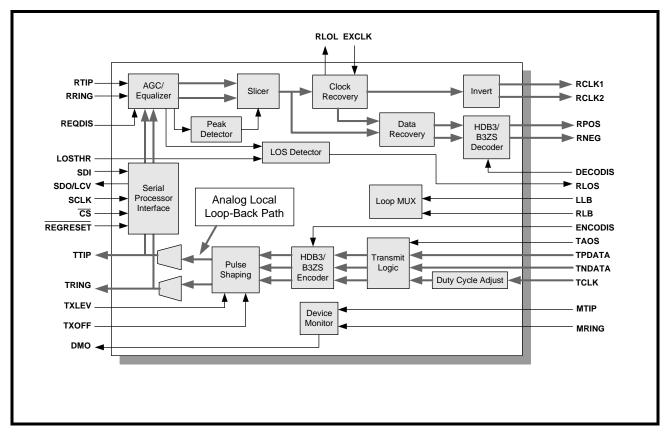

| Figure 1.Block Diagram of the XRT7300                                                                                                    |      |

| Ordering Information                                                                                                                     | 2    |

| Figure 2.Pin Out of the XRT7300 in the 44 Pin TQFP                                                                                       | 2    |

| TABLE OF CONTENTS                                                                                                                        |      |

| Pin Description                                                                                                                          | 3    |

| Electrical Characteristics                                                                                                               |      |

| DC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHERWISE SPI                                                          | ECI- |

| FIED)                                                                                                                                    | 10   |

| AC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHERWISE SPEFIED)                                                     | 10   |

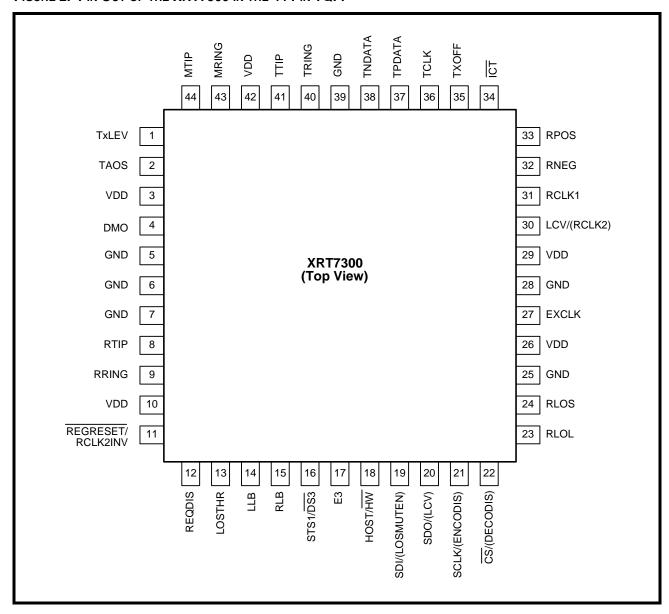

| Figure 3. Timing Diagram of the Transmit Terminal Input Interface                                                                        |      |

| Figure 4.Timing Diagram of the Receive Terminal Output Interface                                                                         | HER  |

| AC ELECTRICAL CHARACTERISTICS (CONTINUED) (TA = 25°C, VDD = 5.0V + 5%, UNLESS OT WISE SPECIFIED)                                         | HER  |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                 |      |

| Figure 5.Transmit Pulse Amplitude Test Circuit for DS3, E3 and STS-1 Rates                                                               | 15   |

| Figure 6.ITU-T G.703 Transmit Output Pulse Template for E3 Applications                                                                  |      |

| Figure 7.Bellcore GR-499-CORE Transmit Output Pulse Template for DS3 Applications                                                        |      |

| Figure 8.Bellcore GR-253-CORE Transmit Output Pulse Template for SONET STS-1 Applications                                                |      |

| Figure 9. Timing Diagram for the Microprocessor Serial Interface                                                                         |      |

| System Description                                                                                                                       | 18   |

| THE TRANSMIT SECTION                                                                                                                     |      |

| THE RECEIVE SECTION                                                                                                                      | 18   |

| THE MICROPROCESSOR SERIAL INTERFACE                                                                                                      |      |

| Table 1:Role of Microprocessor Serial Interface pins when the XRT7300 is operating in the Hardware Mo                                    |      |

| 1.0 SELECTING THE DATA RATE                                                                                                              |      |

| Table 2:Selecting the Data Rate for the XRT7300 via the E3 and STS-1/DS3 input pins (Hardware Mode COMMAND REGISTER CR4 (ADDRESS = 0X04) | 19   |

| Table 3:Selecting the Data Rate for the XRT7300 Via the STS-1/DS3 and the E3 Bit-fields Within Comm. Register CR4 (HOST Mode)            |      |

| 2.0 THE TRANSMIT SECTION                                                                                                                 | 20   |

| 2.1 THE TRANSMIT LOGIC BLOCK                                                                                                             |      |

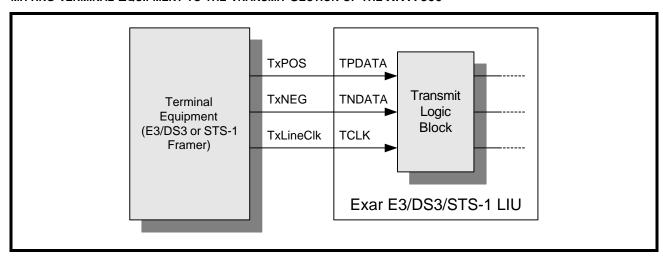

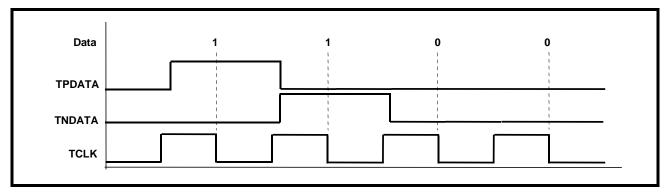

| Figure 10.The Typical Interface for the Transmission of Data in a Dual-Rail Format From the Transmitting                                 | _    |

| minal Equipment to the Transmit Section of the XRT7300                                                                                   |      |

| Accepting Single-Rail Data from the Terminal Equipment                                                                                   |      |

| COMMAND REGISTER CR1 (ADDRESS = 0X01)                                                                                                    |      |

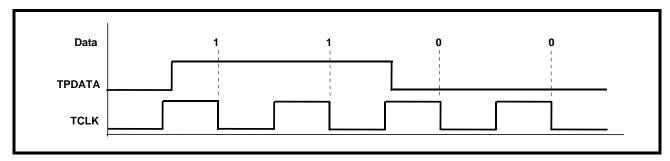

| Figure 12. The Behavior of the TPDATA and TCLK Input Signals While the Transmit Logic Block is Accept                                    |      |

| Single-Rail Data From the Terminal Equipment                                                                                             |      |

# E3/DS3/STS-1 LINE INTERFACE UNIT

| 2.2 THE TRANSMIT CLOCK DUTY CYCLE ADJUST CIRCUITRY                                                                 | 21   |

|--------------------------------------------------------------------------------------------------------------------|------|

| 2.3 THE HDB3/B3ZS ENCODER BLOCK                                                                                    | 22   |

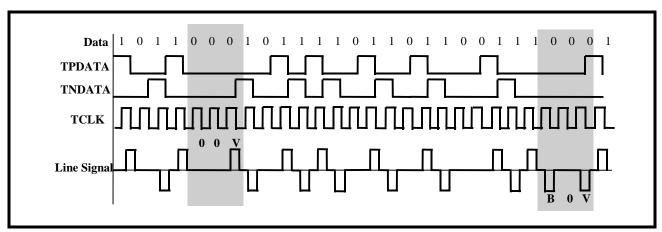

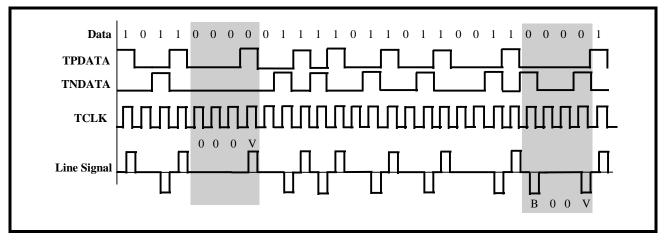

| B3ZS Encoding                                                                                                      | 22   |

| Figure 13.An Example of B3ZS Encoding                                                                              | 22   |

| HDB3 Encoding                                                                                                      |      |

| Figure 14.An Example of HDB3 Encoding                                                                              | 23   |

| Enabling/Disabling the HDB3/B3ZS Encoder                                                                           | 23   |

| COMMAND REGISTER CR2 (ADDRESS = 0X02                                                                               | 23   |

| 2.4 THE TRANSMIT PULSE SHAPER CIRCUITRY                                                                            |      |

| Enabling the Transmit Line Build-Out Circuit                                                                       |      |

| COMMAND REGISTER CR1 (ADDRESS = 0X01)                                                                              |      |

| Disabling the Transmit Line Build-Out Circuit                                                                      |      |

| COMMAND REGISTER CR1 (ADDRESS = 0X01)                                                                              |      |

| Design Guideline for Setting the Transmit Line Build-Out Circuit                                                   |      |

| The Transmit Line Build-Out Circuit and E3 Applications                                                            |      |

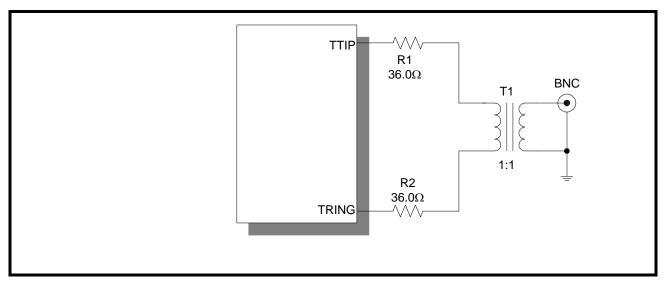

| 2.5 Interfacing the Transmit Section of the XRT7300 to the Line                                                    |      |

| Figure 15.Recommended Schematic for Interfacing the Transmit Section of the XRT7300 to the Line                    | 24   |

| TRANSFORMER RECOMMENDATIONS                                                                                        | 25   |

| 3.0 THE RECEIVE SECTION                                                                                            | 25   |

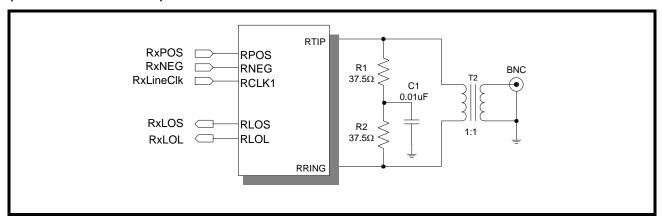

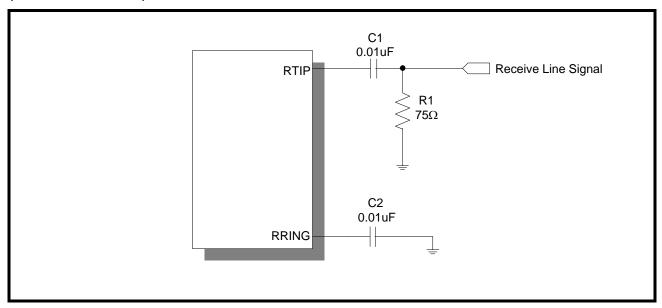

| 3.1 Interfacing the Receive Section of the XRT7300 to the Line                                                     | 25   |

| Figure 16.Recommended Schematic for Interfacing the Receive Section of the XRT7300 to the Line (Transfer-Coupling) |      |

| Figure 17.Recommended Schematic for Interfacing the Receive Section of the XRT7300 to the Line (Cap                |      |

| tive-Coupling)                                                                                                     |      |

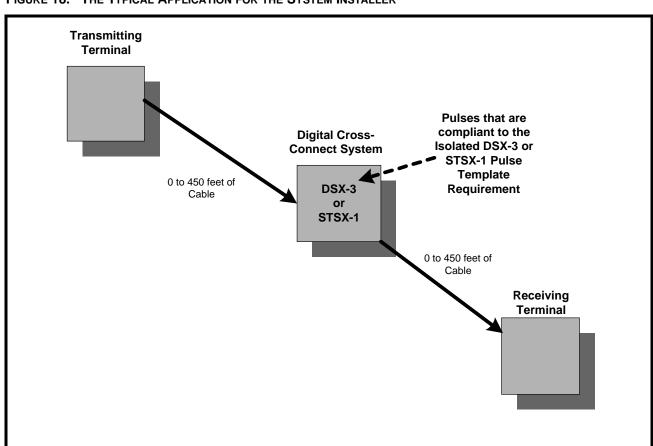

| 3.2 THE RECEIVE EQUALIZER BLOCK                                                                                    | 26   |

| Figure 18. The Typical Application for the System Installer                                                        | 27   |

| COMMAND REGISTER CR2 (ADDRESS = 0X02)                                                                              |      |

| 3.3 PEAK DETECTOR AND SLICER                                                                                       |      |

| 3.4 CLOCK RECOVERY PLL                                                                                             |      |

| 3.5 THE HDB3/B3ZS DECODER                                                                                          |      |

| B3ZS Decoding DS3/STS-1 Applications                                                                               |      |

| Figure 19.An Example of B3ZS Decoding                                                                              |      |

| HDB3 Decoding E3 Applications                                                                                      |      |

| Figure 20.An Example of HDB3 Decoding                                                                              |      |

| Enabling/Disabling the HDB3/B3ZS Decoder                                                                           |      |

| COMMAND REGISTER CR2 (ADDRESS = 0X02)                                                                              |      |

| 3.6 LOS DECLARATION/CLEARANCE                                                                                      |      |

| The LOS Declaration/Clearance Criteria for E3 Applications                                                         |      |

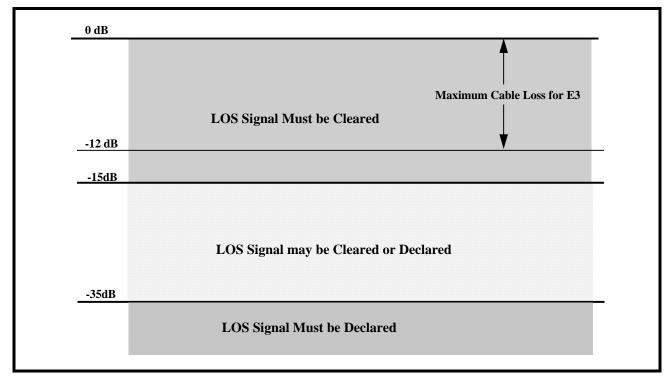

| Figure 21.The Signal Levels that the XRT7300 Declares and Clears LOS (E3 Mode Only)                                |      |

| Figure 22. The Behavior the LOS Output Indicator In Response to the Loss of Signal and the Restoration of nal      | _    |

| The LOS Declaration/Clearance Criteria for DS3 and STS-1 Applications                                              | 32   |

| Table 4:The ALOS Declaration and Clearance Thresholds for a Given Setting of LOSTHR (DS3 and STS-                  |      |

| plications) for Equalizer Enabled or Disabled                                                                      |      |

| COMMAND REGISTER CR3 (ADDRESS = 0X00)                                                                              |      |

| COMMAND REGISTER CR2 (ADDRESS = 0X02)                                                                              |      |

|                                                                                                                    | .4.4 |

# E3/DS3/STS-1 LINE INTERFACE UNIT

| DEV | - | _ | _ |  |

|-----|---|---|---|--|

| ₽FV | 7 | 7 | 7 |  |

| COMMAND REGISTER CR2 (ADDRESS = 0X02)                                                                     | 33   |

|-----------------------------------------------------------------------------------------------------------|------|

| Muting the Recovered Data while the LOS is being Declared                                                 | 33   |

| COMMAND REGISTER CR3 (ADDRESS = 0X03)                                                                     | 33   |

| 3.7 ROUTING THE RECOVERED TIMING AND DATA INFORMATION TO THE RECEIVING TERMINAL EQUIPMENT.                | 33   |

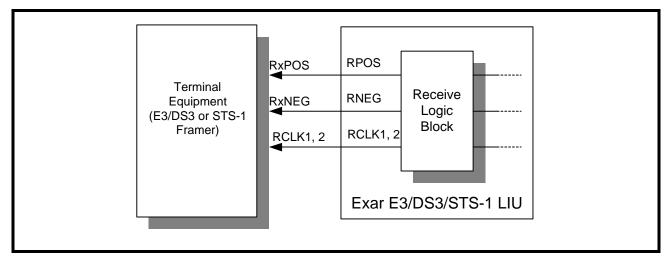

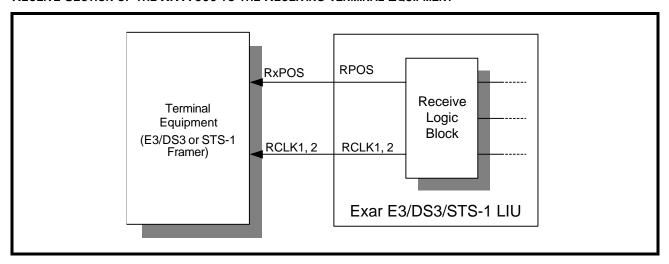

| Figure 23. The Typical Interface for the Transmission of Data in a Dual-Rail Format From the Receive Sec  |      |

| of the XRT7300 to the Receiving Terminal Equipment                                                        |      |

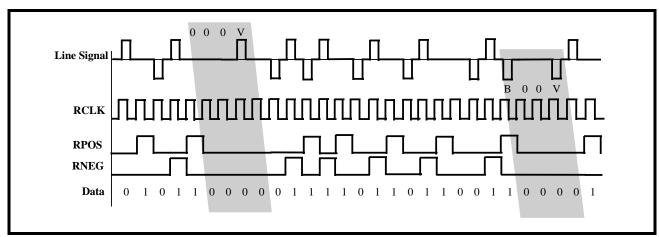

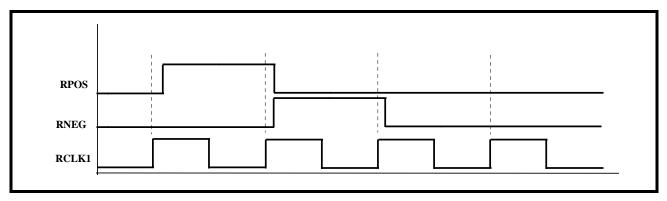

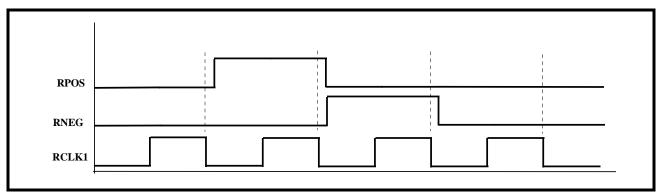

| Figure 24. How the XRT7300 Outputs Data on the RPOS and RNEG Output Pins                                  |      |

| Figure 25.The Behavior of the RPOS, RNEG and RCLK1 Signals When RCLK1 is Inverted                         |      |

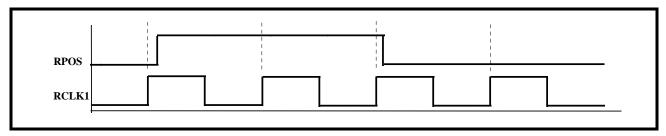

| Routing Single-Rail Format data (Binary Data Stream) to the Receive Terminal Equipment                    |      |

| COMMAND REGISTER CR3 (ADDRESS = 0X03)                                                                     |      |

| Figure 26.The Typical Interface for the Transmission of Data in a Single-Rail Format From the Receive Sec |      |

| of the XRT7300 to the Receiving Terminal Equipment                                                        | 36   |

| Figure 27. The Behavior of the RPOS and RCLK1 Output Signals While the XRT7300 is Transmitting Single-    |      |

| Data to the Receiving Terminal Equipment                                                                  |      |

| 4.0 DIAGNOSTIC FEATURES OF THE XRT7300                                                                    | 36   |

| 4.1 THE ANALOG LOCAL LOOP-BACK MODE                                                                       |      |

| Figure 28.The Analog Local Loop-Back in the XRT7300                                                       |      |

| COMMAND REGISTER CR4 (ADDRESS = 0X04)                                                                     |      |

| 4.2 THE DIGITAL LOCAL LOOP-BACK MODE                                                                      |      |

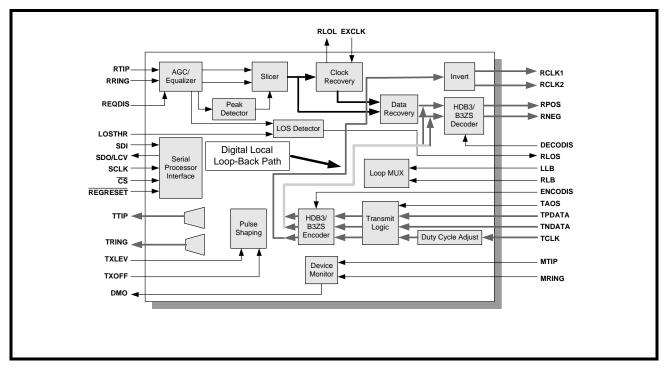

| Figure 29.The Digital Local Loop-Back path in the XRT7300                                                 | პგ   |

| 4.3 THE REMOTE LOOP-BACK MODE                                                                             |      |

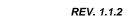

| Figure 30.The Remote Loop-Back Path in the XRT7300                                                        |      |

| COMMAND REGISTER CR4 (ADDRESS = 0X04)                                                                     |      |

| 4.4 TXOFF FEATURES                                                                                        | 40   |

| COMMAND REGISTER CR1 (ADDRESS = 0X01)                                                                     | 40   |

| 4.5 THE TRANSMIT DRIVE MONITOR FEATURES                                                                   | 40   |

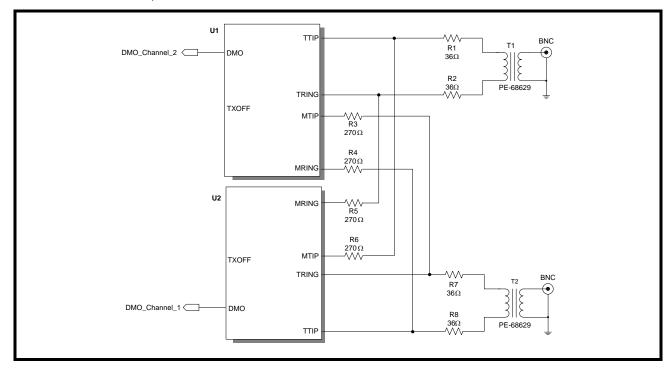

| Figure 31.The XRT7300 Employing the Transmit Drive Monitor Features                                       |      |

| Figure 32. Two LIU's, Each Monitoring the Transmit Output Signal of the Other LIU IC                      |      |

| 4.6 THE TAOS (TRANSMIT ALL ONES) FEATURE                                                                  |      |

| COMMAND REGISTER CR1 (ADDRESS = 0X01)                                                                     |      |

| 5.0 THE MICROPROCESSOR SERIAL INTERFACE                                                                   | 42   |

| 5.1 DESCRIPTION OF THE COMMAND REGISTERS                                                                  |      |

| Table 5:Addresses and Bit Formats of XRT7300 Command Registers                                            |      |

| DESCRIPTION OF BIT-FIELDS FOR EACH COMMAND REGISTER                                                       |      |

| Command Register - CR0                                                                                    |      |

| Command Register - CR1                                                                                    |      |

| Command Register - CR2                                                                                    |      |

| Command Register - CR3                                                                                    |      |

| Command Register - CR4                                                                                    |      |

| Table 6:Loop-Back Modes                                                                                   |      |

| 5.2 OPERATING THE MICROPROCESSOR SERIAL INTERFACE.                                                        |      |

| Figure 33.Microprocessor Serial Interface Data Structure                                                  | 46   |

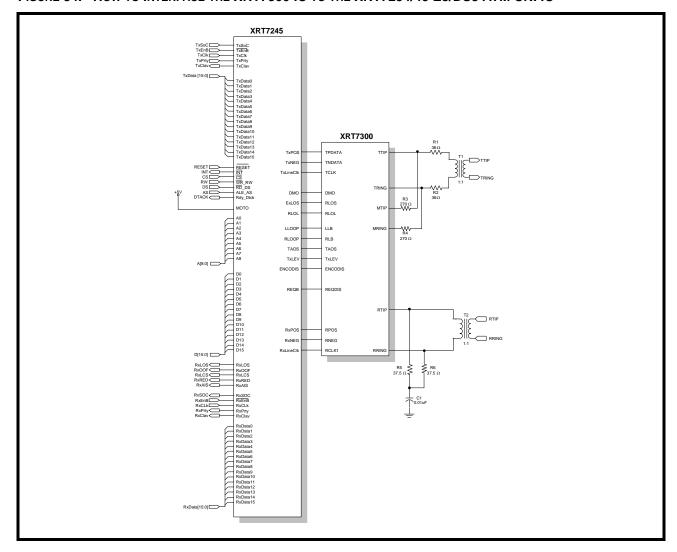

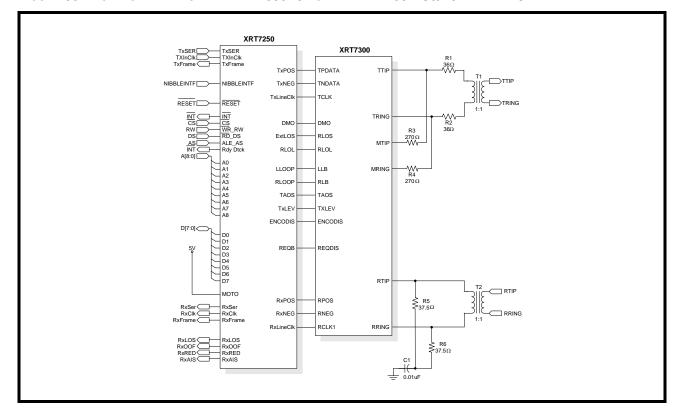

| Figure 35. How to Interface the XRT7300 IC to the XRT7250 DS3/E3 Framer IC                                |      |

| ORDERING INFORMATION                                                                                      | 49   |

| Package Dimensions                                                                                        | . 49 |

# E3/DS3/STS-1 LINE INTERFACE UNIT

REVISION HISTORY ......50

# **PIN DESCRIPTION**

| Pin# | SYMBOL | Түре | DESCRIPTION                                                                                                                                                                      |

|------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | TXLEV  | I    | Transmit Line Build-Out Enable/Disable Select:                                                                                                                                   |

|      |        |      | This input pin is used to enable or disable the Transmit Line Build-Out circuit in the XRT7300.                                                                                  |

|      |        |      | Setting this pin to "High" disables the Line Build-Out circuit. In this mode, the XRT7300 outputs partially shaped pulses onto the line via the TTIP and TRING output pins.      |

|      |        |      | Setting this pin to "Low" enables the Line Build-Out circuit. In this mode, the XRT7300 outputs partially-shaped pulses onto the line via the TTIP and TRING output pins.        |

|      |        |      | To comply with the isolated DSX-3/STSX-1 Pulse Template Requirements per Bellcore GR-499-Core or Bellcore GR-253-Core:                                                           |

|      |        |      | 1. Set this input pin to a "1" if the cable length between the Cross-Connect and the transmit output of the XRT7300 is greater than 225 feet.                                    |

|      |        |      | 2. Set this input pin to a "0" if the cable length between the Cross-Connect and the transmit output of the XRT7300 is less than 225 feet.                                       |

|      |        |      | This pin is active only if both of the following are true:  (a) The XRT7300 is configured to operate in either the DS3 or SONET STS-1                                            |

|      |        |      | modes and                                                                                                                                                                        |

|      |        |      | (b) The XRT7300 is configured to operate in the Hardware Mode.                                                                                                                   |

|      |        |      | <b>NOTE:</b> This pin should be tied to GND if the XRT7300 is to be operated in the HOST mode.                                                                                   |

| 2    | TAOS   | I    | Transmit All Ones Select:                                                                                                                                                        |

|      |        |      | A "High" on this pin causes a continuous AMI all "1's" pattern to be transmitted onto the line. The frequency of this "1's" pattern is determined by TCLK. <b>NOTES:</b>         |

|      |        |      | <ol> <li>This input pin is ignored if the XRT7300 is operating in the HOST Mode.</li> <li>Tie this pin to GND if the XRT7300 is going to be operating in the HOST</li> </ol>     |

|      |        |      | Mode.                                                                                                                                                                            |

| 3    | VDD    | **** | Transmit Digital Power Supply                                                                                                                                                    |

| 4    | DMO    | 0    | Drive Monitor Output:                                                                                                                                                            |

|      |        |      | If no transmitted AMI signal is present on MTIP and MRING input pins for 128±32 TCLK periods, then the DMO pin toggles and remains "High" until the next AMI signal is detected. |

| 5    | GND    | **** | Transmit Digital GND                                                                                                                                                             |

| 6    | GND    | ***  | Analog GND (Substrate)                                                                                                                                                           |

| 7    | GND    | ***  | Receive Analog GND                                                                                                                                                               |

| 8    | RTIP   | I    | Receive TIP Input:                                                                                                                                                               |

|      |        |      | This input pin along with RRING is used to receive the line signal from the Remote DS3/E3/STS-1 Terminal.                                                                        |

| 9    | RRING  | I    | Receive RING Input:                                                                                                                                                              |

|      |        |      | This input pin along with RTIP is used to receive the line signal from the Remote DS3/E3/STS-1 Terminal.                                                                         |

| 10   | VDD    | **** | Receive Analog VDD                                                                                                                                                               |

# E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.1.2

| Pin# | SYMBOL                  | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | REGRESET/<br>(RCLK2INV) | ı    | Register Reset Input pin (Invert RCLK2 Output - Select): The function of this pin depends upon whether the XRT7300 is operating in the HOST Mode or in the Hardware Mode. HOST Mode - Register Reset Input pin: Setting this input pin "Low" causes the XRT7300 to reset the contents of the Command Registers to their default settings and operating configuration. This pin is internally pulled "High". Hardware Mode - Invert RCLK2 Output Select: Setting this input pin "Low" configures the Receive Section of the XRT7300 to output the recovered data via the RPOS and RNEG output pins on the rising edge of the RCLK2 output signal. Setting this input pin "High" configures the Receive Section to output the recovered data on the falling edge of the RCLK2 output signal. |

| 12   | REQDIS                  | I    | Receive Equalization Disable Input:  Setting this input pin "High" disables the Internal Receive Equalizer in the XRT7300. Setting this pin "Low" enables the Internal Receive Equalizer. The guidelines for enabling and disabling the Receive Equalizer are described in Section 3.2.  Notes:  1. This input pin is ignored if the XRT7300 is operating in the HOST Mode. 2. Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.                                                                                                                                                                                                                                                                                                                               |

| 13   | LOSTHR                  | I    | Loss of Signal Threshold Control:  The voltage forced on this pin controls the input loss of signal (LOS) threshold.  Two settings are provided by forcing this signal to either GND or VDD.  Note: This pin is only applicable during DS3 or STS-1 operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14   | LLB                     | I    | Local Loop-Back Select: This input pin along with RLB dictates which Loop-Back mode the XRT7300 is operating in. A "High" on this pin with RLB being set to "Low" configures the XRT7300 to operate in the Analog Local Loop-Back Mode. A "High" on this pin with RLB also being set to "High" configures the XRT7300 to operate in the Digital Local Loop-Back Mode.  Notes:  1. This input pin is ignored if the XRT7300 is operating in the HOST Mode. 2. Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.                                                                                                                                                                                                                                                 |

| 15   | RLB                     | ı    | Remote Loop-Back Select: This input pin along with LLB dictates which Loop-Back mode the XRT7300 is be operating in. A "High" on this pin with LLB being set to "Low" configures the XRT7300 to operate in the Remote Loop-Back Mode. A "High" on this pin with LLB also being set to "High" configures the XRT7300 to operate in the Digital Local Loop-Back Mode.  Notes:  1. This input pin is ignored if the XRT7300 is operating in the HOST Mode. 2. Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.                                                                                                                                                                                                                                                   |

REV. 1.1.2

| Pin# | SYMBOL             | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16   | STS-1/DS3          | ı    | STS-1/DS3 Select Input:  A "High" on this pin configures the Clock Recovery Phase Locked Loop to set its VCO Center frequency to around 51.84 MHz (optimal for SONET STS-1 operations). A "Low" on this pin configures the Clock Recovery Phase Locked Loop to set its VCO Center frequency to around 44.736 MHz (optimal for DS3 operations).  Notes:  1. The XRT7300 ignores this pin if the E3 pin (pin 17) is set to "1".  2. This input pin is ignored if the XRT7300 is operating in the HOST Mode.  3. Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17   | E3                 | I    | E3 Select Input:  A "High" on this pin configures the XRT7300 to operate in the E3 Mode.  A "Low" on this pin configures the XRT7300 to check the state of the STS-1/DS3 input pin.  Notes:  1. This input pin is ignored if the XRT7300 is operating in the HOST Mode.  2. Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18   | HOST/HW            | ı    | HOST/HW Mode Select:  This input pin is used to enable or disable the Microprocessor Serial Interface (e.g., consisting of the SDI, SDO, SCLK, CS and REGRESET pins).  Setting this input pin "High" enables the Microprocessor Serial Interface (e.g. configures the XRT7300 to operate in the HOST Mode). In this mode, the XRT7300 is configured by writing data into the on-chip Command Registers via the Microprocessor Serial Interface. When the XRT7300 is operating in the HOST Mode, it ignores the states of many of the discrete input pins.  Setting this input pin "Low" disables the Microprocessor Serial Interface (e.g., configures the XRT7300 to operate in the Hardware Mode). In this mode, many of the external input control pins are functional.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19   | SDI/<br>(LOSMUTEN) |      | Serial Data Input for the Microprocessor Serial Interface (HOST Mode) or MUTE-upon-LOS Enable Input (Hardware Mode):  The function of this input pin depends upon whether the XRT7300 is operating in the HOST or the Hardware Mode.  Serial Data Input for the Microprocessor Serial Interface (HOST Mode):  This pin is used to read or write data into the Command Registers of the Microprocessor Serial Interface. The Read/Write bit, the Address Values of the Command Registers and Data Value to be written during Write Operations are applied to this pin.  This input is sampled on the rising edge of the SCLK pin (pin 21).  MUTE-upon-LOS Enable Input (Hardware Mode):  When in the Hardware Mode, this input pin is used to configure the XRT7300 to MUTE the recovered data via the RPOS and RNEG output pins whenever it declares an LOS condition.  Setting this input pin "High" configures the XRT7300 to automatically pull the RPOS and RNEG output pins to GND whenever it is declaring an LOS condition, thereby MUTing the data being output to the Terminal Equipment.  Setting this input pin "Low" configures the XRT7300 to NOT automatically MUTE the recovered data whenever an LOS condition is declared. |

# E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.1.2

| Pin# | SYMBOL              | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20   | SDO/(LCV)           | 0    | Serial Data Output from the Controller Port/(Line Code Violation Output (LCV) Indicator.):  The function of this input pin depends upon whether the XRT7300 is operating in the HOST or the Hardware Mode.  HOST Mode - Microprocessor Serial Interface - Serial Data Output.  This pin serially outputs the contents of the specified Command Register during Read Operations. The data on this pin is updated on the falling edge of the SCLK input signal. This pin is tri-stated upon completion of data transfer.  Hardware Mode - Line Code Violation Output Indicator.  This pin pulses "High" for one bit period any time the Receive Section of the XRT7300 detects a Line Code Violation in the incoming E3, DS3 or STS-1 Data Stream. |

| 21   | SCLK/(ENCO-<br>DIS) | I    | Microprocessor Serial Interface Clock Signal/Encoder Disable: HOST Mode - Microprocessor Serial Interface Clock Signal This signal is used to sample the data on the SDI pin on the rising edge of this signal. Additionally, during Read operations the Microprocessor Serial Interface updates the SDO output on the falling edge of this signal. Hardware Mode - B3ZS/HDB3 Encoder Disable Setting this input pin "High" disables the B3ZS/HDB3 Encoder and configures the XRT7300 to transmit the line signal in an AMI Format. Setting this input pin "Low" enables the B3ZS/HDB3 Encoder and configures the XRT7300 to transmit the line signal in the B3ZS format (for DS3/STS-1 operation) or in the HDB3 format (for E3 operation).     |

| 22   | CS/(DECODIS)        | I    | Microprocessor Serial Interface - Chip Select/Decoder Disable  The function of this input pin depends upon whether the XRT7300 is operating in the HOST or the Hardware Mode.  HOST Mode - Chip Select Input:  The Local Microprocessor must assert this pin (e.g., set it to "0") in order to enable communication with the XRT7300 via the Microprocessor Serial Interface.  Hardware Mode - (B3ZS/HDB3 Decoder Disable)  Setting this input pin "High" disables the B3ZS/HDB3 Decoder. Setting this input pin "Low" enables the B3ZS/HDB3 Decoder.                                                                                                                                                                                            |

| 23   | RLOL                | 0    | Receive Loss of Lock Output Indicator This output pin toggles "High" if the XRT7300 has detected a Loss of Lock Condition. The XRT7300 declares an LOL (Loss of Lock) Condition if the recovered clock frequency deviates from the Reference Clock frequency (available at the EXCLK input pin) by more than 0.5%.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 24   | RLOS                | 0    | Receive Loss of Signal Output Indicator  This output pin toggles "High" if the XRT7300 has detected a Loss of Signal Condition in the incoming line signal.  The criteria the XRT7300 uses to declare an LOS Condition depends upon whether the device is operating in the E3 or DS3/STS-1 Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 25   | GND                 | **** | Digital GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26   | VDD                 | **** | Digital VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

REV. 1.1.2

| PIN# | SYMBOL      | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27   | EXCLK       | I    | External Reference Clock Input:  Apply a 34.368MHz clock signal for E3 applications, a 44.736 MHz clock signal for DS3 applications or a 51.84 MHz clock signal for SONET STS-1 applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28   | GND         | ***  | Receiver Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 29   | VDD         | ***  | Receiver Digital VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30   | LCV/(RCLK2) | 0    | Line Code Violation Indicator/Receive Clock Output pin 2:  The function of this pin depends upon whether the XRT7300 is operating in the HOST Mode, the Hardware Mode or User selection.  HOST Mode - Line Code Violation Indicator Output:  If the XRT7300 is configured to operate in the HOST Mode, then this pin functions as the LCV output pin by default. However, by using the on-chip Command Registers, this pin can be configured to function as the second Receive Clock signal output pin (RCLK2).  Hardware Mode - Receive Clock Output pin 2:  This output pin is the Recovered Clock signal from the incoming line signal. The receive section of the XRT7300 outputs data via the RPOS and RNEG output pins on the rising edge of this clock signal.  Note: If the XRT7300 is operating in the HOST Mode and this pin is configured to function as the additional Receive Clock signal output pin, then the XRT7300 can be configured to update the data on the RPOS and RNEG output pins on the falling edge of this clock signal. |

| 31   | RCLK1       | 0    | Receive Clock Output pin 1:  This output pin is the Recovered Clock signal from the incoming line signal. The receive section of the XRT7300 outputs data via the RPOS and RNEG output pins on the rising edge of this clock signal.  Note: If the XRT7300 device is operating in the "Host" Mode, then the user can configure the device to update the data on the RPOS and RNEG output pins on the falling edge of this clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

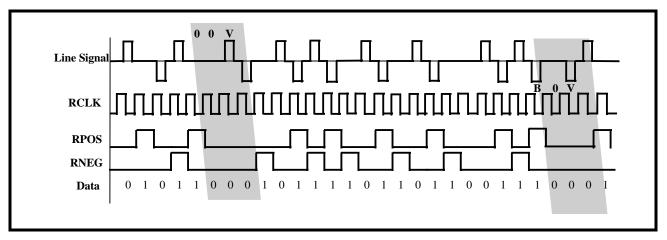

| 32   | RNEG        | 0    | Receive Negative Pulse Output: This output pin pulses "High" whenever the XRT7300 has received a Negative Polarity pulse in the incoming line signal at the RTIP/RRING inputs.  Note: If the B3ZS/HDB3 Decoder is enabled, then the zero suppression patterns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V") is not reflected at this output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 33   | RPOS        | 0    | Receive Positive Pulse Output: This output pin pulses "High" whenever the XRT7300 has received a Positive Polarity pulse in the incoming line signal at the RTIP/RRING inputs.  Note: If the B3ZS/HDB3 Decoder is enabled, then the zero suppression patterns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V") is not reflected at this output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 34   | ĪCT         | I    | In-Circuit Test Input: Setting this pin "Low" causes all digital and analog outputs to go into a high-impedance state to allow for in-circuit testing. This pin is internally pulled "High".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.1.2

| Pin# | SYMBOL | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35   | TXOFF  | ı    | Transmitter OFF Input: Setting this input pin "High" configures the XRT7300 to turn off the Transmitter in the device.  Notes:  1. This input pin is ignored if the XRT7300 is operating in the HOST Mode.  2. Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.                                                                                                                                                                                                                                             |

| 36   | TCLK   | ı    | Transmit Clock Input for TPDATA and TNDATA:  This input pin must be driven at 34.368 MHz for E3 applications, 44.736MHz for DS3 applications, or 51.84MHz for SONET STS-1 applications. The XRT7300 uses this signal to sample the TPDATA and TNDATA input pins. By default, the XRT7300 is configured to sample these two pins on the falling edge of this signal.  If the XRT7300 is operating in the HOST Mode, then the device can be configured to sample the TPDATA and TNDATA input pins on the rising edge of TCLK.              |

| 37   | TPDATA | ı    | Transmit Positive Data Input:  The XRT73L00 samples this pin on the falling edge of TCLK. If the device samples a "1" at this input pin, then it generates and transmits a positive polarity pulse to the line.  Notes:  1. The data should be applied to this input pin if the Transmit Section is configured to accept Single-Rail data from the Terminal Equipment.  2. If the XRT73L00 is operating in the HOST Mode, then the XRT73L00 can be configured to sample the TPDATA pin on either the rising or falling edge of TCLK.     |

| 38   | TNDATA | ı    | Transmit Negative Data Input:  The XRT7300 samples this pin on the falling edge of TCLK. If the device samples a "1" at this input pin, then it generates and transmits a negative polarity pulse to the line.  Notes:  1. This input pin is ignored and should be tied to GND if the Transmit Section is configured to accept Single-Rail data from the Terminal Equipment.  2. If the XRT7300 is operating in the HOST Mode, then the XRT7300 can be configured to sample the TNDATA pin on either the rising or falling edge of TCLK. |

| 39   | GND    | -    | Transmit Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 40   | TRING  | 0    | Transmit RING Output:  The XRT7300 uses this pin, along with TRING, to transmit a bipolar line signal via a 1:1 transformer.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 41   | TTIP   | 0    | Transmit TIP Output: The XRT7300 uses this pin, along with TTIP, to transmit a bipolar line signal via a 1:1 transformer.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 42   | VDD    | -    | Transmit Analog Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

REV. 1.1.2

| Pin# | SYMBOL | Түре | DESCRIPTION                                                                                                                                                                                             |

|------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43   | MRING  | I    | Monitor Ring Input: The bipolar line output signal from TRING can be connected to this pin via a 270 $\Omega$ resistor in order to check for line driver failure. This pin is internally pulled "High". |

| 44   | MTIP   | I    | Monitor Tip Input: The bipolar line output signal from TTIP can be connected to this pin via a 270 $\Omega$ resistor in order to check for line driver failure. This pin is internally pulled "High".   |

# **ELECTRICAL CHARACTERISTICS**

# DC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V ± 5%, UNLESS OTHERWISE SPECIFIED)

| SYMBOL          | PARAMETER                                                            | Min. | TYP. | Max. | Units |

|-----------------|----------------------------------------------------------------------|------|------|------|-------|

| $V_{DDD}$       | DC Supply Voltage                                                    | 4.75 | 5    | 5.25 | V     |

| $V_{DDA}$       | DC Supply Voltage                                                    | 4.75 | 5    | 5.25 | V     |

| I <sub>CC</sub> | Supply Current (Measured while Transmitting and Receiving all "1's") |      |      |      |       |

|                 | DS-3 Mode                                                            |      | 167  | 200  | mA    |

|                 | STS-1 Mode                                                           |      | 180  | 220  | mA    |

| V <sup>IL</sup> | Input Low Voltage                                                    |      |      | 0.8  | V     |

| V <sub>IH</sub> | Input High Voltage                                                   | 2.0  |      | VDD  | V     |

| V <sub>OL</sub> | Output Low Voltage, IOUT = -4.0mA                                    | 0    |      | 0.4  | V     |

| V <sub>OH</sub> | Output High Voltage, IOUT = 4.0mA                                    | 2.8  |      | VDD  | V     |

| IL              | Input Leakage Current*                                               |      |      | ±10  | mA    |

<sup>\*</sup> Not applicable to pins with pull-up/pull-down resistors.

# AC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V ± 5%, UNLESS OTHERWISE SPECIFIED)

| SYMBOL            | PARAMETER                                        | MIN. | TYP.   | Max. | Units |

|-------------------|--------------------------------------------------|------|--------|------|-------|

| Terminal          | Side Timing Parameters (See Figure 3 & Figure 4) |      |        |      |       |

|                   | TCLK Clock Duty Cycle (DS3/STS-1)                | 30   | 50     | 70   | %     |

|                   | TCLK Clock Duty Cycle (E3)                       | 30   | 50     | 70   | %     |

|                   | TCLK Frequency (SONET STS-1)                     |      | 51.84  |      | MHz   |

|                   | TCLK Frequency (DS3)                             |      | 44.736 |      | MHz   |

|                   | TCLK Frequency (E3)                              |      | 34.368 |      | MHz   |

| t <sub>RTX</sub>  | TCLK Clock Rise Time (10% to 90%)                |      |        | 4    | ns    |

| t <sub>FTX</sub>  | TCLK Clock Fall Time (90% to 10%)                |      |        | 4    | ns    |

| t <sub>TSU</sub>  | TPDATA/TNDATA to TCLK Falling Set up time        | 3    |        |      | ns    |

| t <sub>THO</sub>  | TPDATA/TNDATA to TCLK Falling Hold time          | 3    |        |      | ns    |

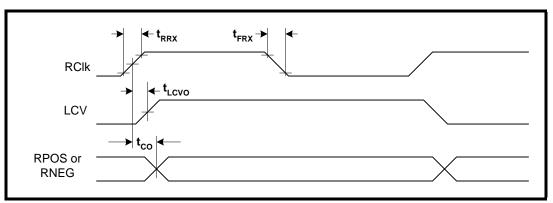

| t <sub>LCVO</sub> | RCLK to rising edge of LCV output delay          |      | 2.5    |      | ns    |

| t <sub>TDY</sub>  | TTIP/TRING to TCLK Rising Propagation Delay time | 0.6  |        | 14   | ns    |

|                   | RCLK Clock Duty Cycle                            | 45   | 50     | 55   | %     |

|                   | RCLK Frequency (SONET STS-1)                     |      | 51.84  |      | MHz   |

|                   | RCLK Frequency (DS3)                             |      | 44.736 |      | MHz   |

|                   | RCLK Frequency (E3)                              |      | 34.368 |      | MHz   |

REV. 1.1.2

# AC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V ± 5%, UNLESS OTHERWISE SPECIFIED)

| SYMBOL           | PARAMETER                         | MIN. | TYP. | Max. | Units |

|------------------|-----------------------------------|------|------|------|-------|

| t <sub>CO</sub>  | RCLK to RPOS/RNEG Delay Time      |      |      | 4    | ns    |

| t <sub>RRX</sub> | RCLK Clock Rise Time (10% to 90%) |      | 2    | 4    | ns    |

| t <sub>FRX</sub> | RCLK Clock Fall Time (10% to 90%) |      | 1.5  | 3    | ns    |

| C <sub>i</sub>   | Input Capacitance                 |      |      | 10   | pF    |

| C <sub>L</sub>   | Load Capacitance                  |      |      | 10   | pF    |

FIGURE 3. TIMING DIAGRAM OF THE TRANSMIT TERMINAL INPUT INTERFACE

FIGURE 4. TIMING DIAGRAM OF THE RECEIVE TERMINAL OUTPUT INTERFACE

# AC ELECTRICAL CHARACTERISTICS (CONTINUED) (TA = $25^{\circ}$ C, VDD = 5.0V $\pm$ 5%, UNLESS OTHERWISE SPECIFIED)

**Line Side Parameters**

| SYMBOL    | PARAMETER                                                       | MIN.  | TYP.  | Max.  | Units |

|-----------|-----------------------------------------------------------------|-------|-------|-------|-------|

|           | ication Parameters<br>Line Characteristics (See Figure 5)       |       |       |       |       |

|           | Transmit Output Pulse Amplitude (Measured at 0 feet, TXLEV = 0) | 0.68  | 0.75  | 0.85  | Vpk   |

|           | Transmit Output Pulse Amplitude (Measured at 0 feet, TXLEV = 1) | 0.90  | 1.0   | 1.1   | Vpk   |

|           | Transmit Output Pulse Width                                     | 10.10 | 11.18 | 12.28 | ns    |

|           | Transmit Output Pulse Amplitude Ratio                           | 0.9   | 1.0   | 1.1   |       |

|           | Transmit Output Jitter with jitter-free input clock at TCLK     |       | 0.02  | 0.05  | Ulpp  |

| Receive I | ine Characteristics                                             |       | •     | •     | •     |

|           | Receive Sensitivity (Length of Cable)                           | 900   | 1000  |       | feet  |

|           | Receive Intrinsic Jitter (All One's Pattern)                    |       | 0.01  |       | UI    |

|           | Receive Intrinsic Jitter (100 Pattern) (1)                      |       | 0.02  |       | UI    |

| LOS Leve  | el With Equalizer Enabled (Table 4)                             |       | ı     | l     | l     |

|           | Signal Level to Declare Loss of Signal (LOSTHR = 0)             |       |       | 55    | mV    |

|           | Signal Level to Clear Loss of Signal (LOSTHR = 0)               | 220   |       |       | mV    |

|           | Signal Level to Declare Loss of Signal (LOSTHR = 1)             |       |       | 22    | mV    |

|           | Signal Level to Clear Loss of Signal (LOSTHR = 1)               | 90    |       |       | mV    |

| LOS Leve  | el With Equalizer Disabled (Table 4)                            |       | ı     |       | l .   |

|           | Signal Level to Declare Loss of Signal (LOSTHR = 0)             |       |       | 35    | mV    |

|           | Signal Level to Clear Loss of Signal (LOSTHR = 0)               | 155   |       |       | mV    |

|           | Signal Level to Declare Loss of Signal (LOSTHR = 1)             |       |       | 17    | mV    |

|           | Signal Level to Clear Loss of Signal (LOSTHR = 1)               | 70    |       |       | mV    |

|           | Max Jitter Tolerance @ Jitter Frequency = 100Hz                 | 64    |       |       | UI    |

|           | Max Jitter Tolerance @ Jitter Frequency = 1KHz                  | 64    |       |       | UI    |

|           | Max Jitter Tolerance @ Jitter Frequency = 10KHz                 | 5     |       |       | UI    |

|           | Max Jitter Tolerance @ Jitter Frequency = 800KHz                | 0.4   |       |       | UI    |

<sup>(1)</sup> Measured at Nominal DSX3 level, Equalizer enabled, VDD=5V and  $TA=25^{\circ}C$

# AC ELECTRICAL CHARACTERISTICS (CONTINUED) (TA = $25^{\circ}$ C, VDD = 5.0V $\pm$ 5%, UNLESS OTHERWISE SPECIFIED)

**Line Side Parameters**

| SYMBOL    | PARAMETER                                                                     | MIN. | TYP.  | Max. | Units |

|-----------|-------------------------------------------------------------------------------|------|-------|------|-------|

| E3 Applic | ation Parameters                                                              |      | 1     |      | L     |

| Transmit  | Line Characteristics (See Figure 5)                                           |      |       |      |       |

|           | Transmit Output Pulse Amplitude (Measured at Secondary Output of Transformer) | 0.9  | 1.00  | 1.1  | Vpk   |

|           | Transmit Output Pulse Amplitude Ratio                                         | 0.95 | 1.00  | 1.05 |       |

|           | Transmit Output Pulse Width                                                   | 12.5 | 14.55 | 16.5 | ns    |

|           | Transmit Output Pulse Width Ratio                                             | 0.95 | 1.00  | 1.05 |       |

|           | Transmit Output Jitter with jitter-free input clock at TCLK                   |      | 0.02  | 0.05 | Ulpp  |

| Receive L | ine Characteristics                                                           |      | 1     | •    | •     |

|           | Receive Sensitivity (Length of cable)                                         | 1100 |       |      | feet  |

|           | Interference Margin                                                           | -20  | -17   |      | dB    |

|           | Signal Level to Declare Loss of Signal                                        |      |       | -35  | dB    |

|           | Signal Level to Clear Loss of Signal                                          | -15  |       |      | dB    |

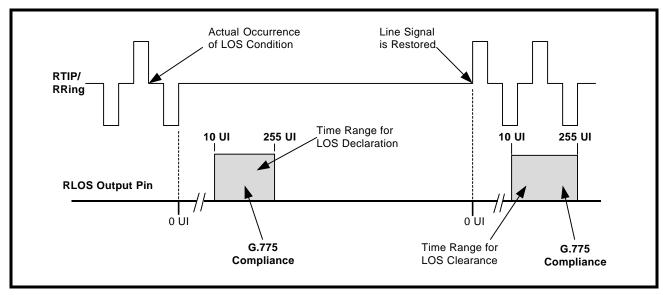

|           | Occurrence of LOS to LOS Declaration Time                                     | 10   | 100   | 255  | UI    |

|           | Termination of LOS to LOS Clearance Time                                      | 10   | 100   | 255  | UI    |

|           | Intrinsic Jitter (all "1's" Pattern) (1)                                      |      | 0.01  |      | UI    |

|           | Intrinsic Jitter (100 Pattern)                                                |      | 0.03  |      |       |

|           | Max Jitter Tolerance @ Jitter Frequency = 100Hz                               | 64   |       |      | UI    |

|           | Max Jitter Tolerance @ Jitter Frequency = 1KHz                                | 30   |       |      | UI    |

|           | Max Jitter Tolerance @ Jitter Frequency = 10KHz                               | 4    |       |      | UI    |

|           | Max Jitter Tolerance @ Jitter Frequency = 800KHz                              | 0.15 |       |      | UI    |

|           | TS-1 Application Parameters Line Characteristics (See Figure 5)               |      |       | 1    | 1     |

|           | Transmit Output Pulse Amplitude (Measured with TXLEV = 0)                     | 0.68 | 0.75  | 0.85 | Vpk   |

|           | Transmit Output Pulse Amplitude (Measured with TXLEV = 1)                     | 0.93 | 0.98  | 1.08 | Vpk   |

|           | Transmit Output Pulse Width                                                   | 8.6  | 9.65  | 10.6 | ns    |

|           | Transmit Output Pulse Amplitude Ratio                                         | 0.9  | 1.0   | 1.1  |       |

|           | Transmit Output Jitter with jitter-free clock input at TCLK                   |      | 0.02  | 0.05 | Ulpp  |

# E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.1.2

# AC ELECTRICAL CHARACTERISTICS (CONTINUED) (TA = $25^{\circ}$ C, VDD = 5.0V $\pm$ 5%, UNLESS OTHERWISE SPECIFIED)

**Line Side Parameters**

| SYMBOL    | PARAMETER                                                     | Min. | TYP. | Max. | Units |  |  |

|-----------|---------------------------------------------------------------|------|------|------|-------|--|--|

| Receive L | eceive Line Characteristics                                   |      |      |      |       |  |  |

|           | Receive Sensitivity (Length of cable)                         | 900  |      |      | feet  |  |  |

|           | Signal Level to Declare or Clear Loss of Signal (see Table 4) |      |      |      | mV    |  |  |

|           | Intrinsic Jitter (all "1's" Pattern) (2)                      |      | 0.03 |      | UI    |  |  |

|           | Intrinsic Jitter (100 Pattern)                                |      | 0.03 |      | UI    |  |  |

|           | Max Jitter Tolerance @ Jitter Frequency = 100Hz               | 64   |      |      | UI    |  |  |

|           | Max Jitter Tolerance @ Jitter Frequency = 1KHz                | 64   |      |      | UI    |  |  |

|           | Max Jitter Tolerance @ Jitter Frequency = 10KHz               | 5    |      |      | UI    |  |  |

|           | Max Jitter Tolerance @ Jitter Frequency = 800KHz              | 0.4  |      |      | UI    |  |  |

<sup>(1)</sup> Measured with Equalizer enabled, 12db cable attenuation, VDD = 5V and  $TA = 25^{\circ}C$

# **ABSOLUTE MAXIMUM RATINGS**

| POWER SUPPLY                     | -0.5 TO +6.5V      |

|----------------------------------|--------------------|

| STORAGE TEMPERATURE              | -65°С то 150°С     |

| INPUT VOLTAGE AT ANY PIN         | -0.5V TO VDD +0.5V |

| POWER DISSIPATION TQFP PACKAGE   | 1.2W               |

| INPUT CURRENT AT ANY PIN         | +100MA             |

| ESD RATING (MIL-STD-883, M-3015) | AT LEAST 1500V     |

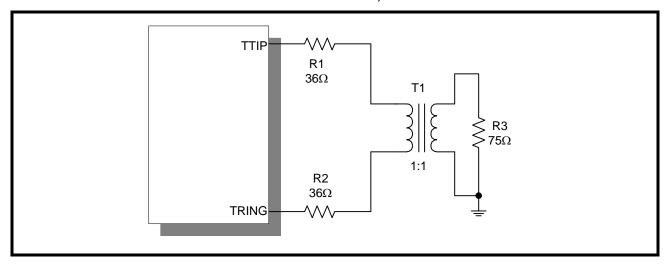

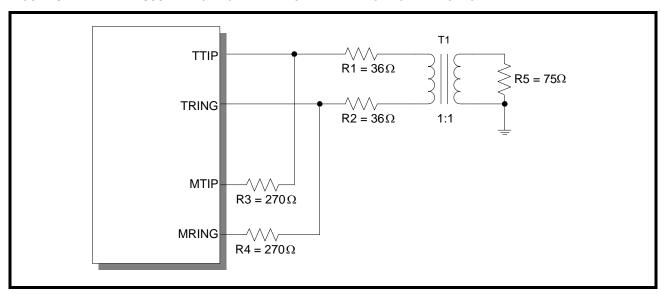

Figure 5 presents the test circuit that was used to test and measure the pulse amplitudes as listed in the ELECTRICAL CHARACTERISTICS tables.

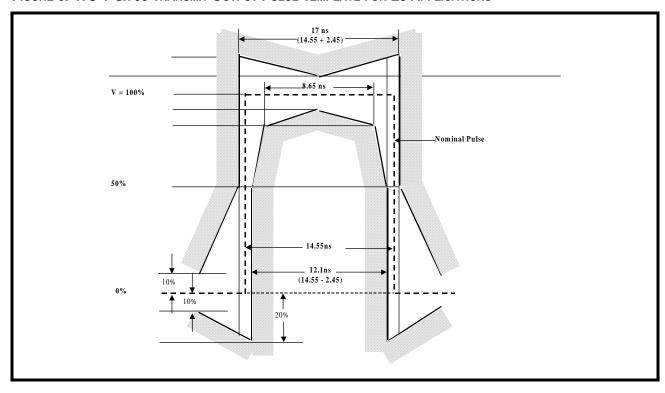

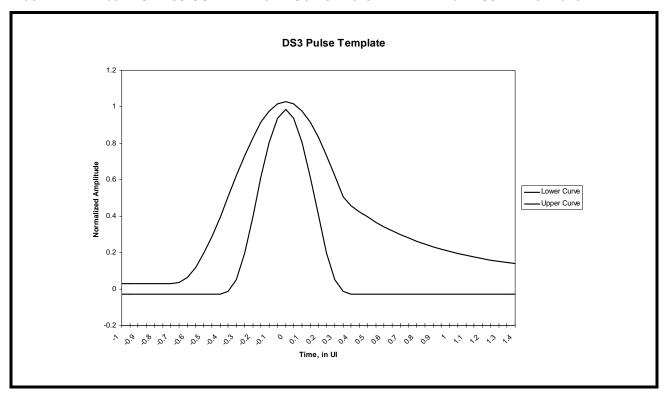

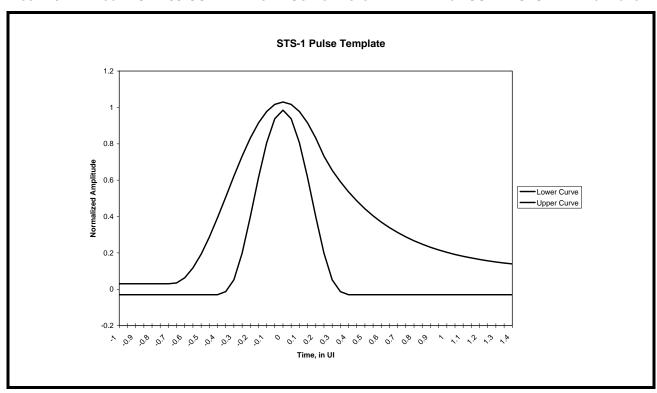

Figure 6, Figure 7 and Figure 8 present the Pulse Template requirements for the E3, DS3 and STS-1 Rates.

<sup>(2)</sup> Measured at nominal STSX-1 level with Equalizer enabled, VDD = 5V and  $TA = 25^{\circ}C$

FIGURE 5. TRANSMIT PULSE AMPLITUDE TEST CIRCUIT FOR DS3, E3 AND STS-1 RATES

FIGURE 6. ITU-T G.703 TRANSMIT OUTPUT PULSE TEMPLATE FOR E3 APPLICATIONS

FIGURE 7. BELLCORE GR-499-CORE TRANSMIT OUTPUT PULSE TEMPLATE FOR DS3 APPLICATIONS

FIGURE 8. BELLCORE GR-253-CORE TRANSMIT OUTPUT PULSE TEMPLATE FOR SONET STS-1 APPLICATIONS

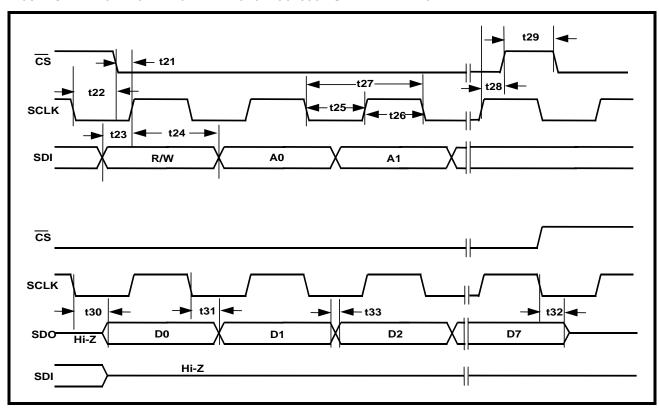

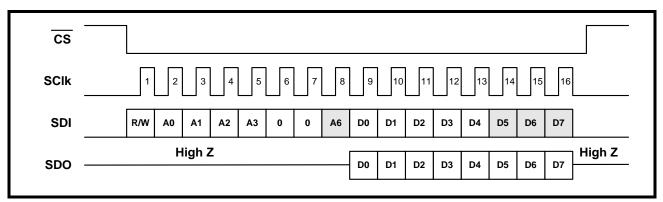

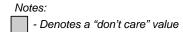

# MICROPROCESSOR SERIAL INTERFACE TIMING (SEE FIGURE 9)

| SYMBOL          | PARAMETER                                                               | Min. | TYP. | Max. | Units |

|-----------------|-------------------------------------------------------------------------|------|------|------|-------|

| t <sub>21</sub> | CS Low to Rising Edge of SCLK Setup Time                                | 50   |      |      | ns    |

| t <sub>22</sub> | CS High to Rising Edge of SCLK Hold Time                                | 20   |      |      | ns    |

| t <sub>23</sub> | SDI to Rising Edge of SCLK Setup Time                                   | 50   |      |      | ns    |

| t <sub>24</sub> | SDI to Rising Edge of SCLK Hold Time                                    | 50   |      |      | ns    |

| t <sub>25</sub> | SCLK "Low" Time                                                         | 240  |      |      | ns    |

| t <sub>26</sub> | SCLK "High" Time                                                        | 240  |      |      | ns    |

| t <sub>27</sub> | SCLK Period                                                             | 500  |      |      | ns    |

| t <sub>28</sub> | CS Low to Rising Edge of SCLK Hold Time                                 | 50   |      |      | ns    |

| t <sub>29</sub> | CS Inactive Time                                                        | 250  |      |      | ns    |

| t <sub>30</sub> | Falling Edge of SCLK to SDO Valid Time                                  |      |      | 200  | ns    |

| t <sub>31</sub> | Falling Edge of SCLK to SDO Invalid Time                                |      |      | 100  | ns    |

| t <sub>32</sub> | Falling Edge of SCLK or Rising Edge of $\overline{\text{CS}}$ to High Z |      | 100  |      | ns    |

| t <sub>33</sub> | Rise/Fall time of SDO Output                                            |      |      | 40   | ns    |

FIGURE 9. TIMING DIAGRAM FOR THE MICROPROCESSOR SERIAL INTERFACE

## E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.1.2

### SYSTEM DESCRIPTION

A functional block diagram of the XRT7300 E3/DS3/STS-1 Transceiver IC (see Figure 1) shows that the device contains three distinct sections:

- The Transmit Section

- The Receive Section

- The Microprocessor Serial Interface

#### THE TRANSMIT SECTION