# EVB71121

300 to 930MHz Receiver Evaluation Board Description

# **Features**

- Dual RF input for antenna space and frequency diversity, LNA cascading or differential feeding

- Fully integrated PLL-based synthesizer

- 2nd mixer with image rejection

- Reception of ASK or FSK modulated signals

- Wide operating voltage and temperature ranges

- Very low standby current consumption

- Low operating current consumption

- Internal IF filter

- Internal FSK demodulator

- Average or peak detection data slicer mode

- RSSI output with high dynamic range for RF level indication

- Output noise cancellation filter

- MCU clock output

- High over-all frequency accuracy

# **Ordering information**

Part No. (see also sec. 4)

EVB71121-315-C EVB71121-433-C EVB71121-868-C EVB71121-915-C

Note 1: Peak detection mode is default population.

# **General Description**

The MLX71121 is a multi-band, single-channel RF receiver based on a double-conversion superheterodyne architecture. It can receive FSK and ASK modulated signals. The IC is designed for general purpose applications for example in the European bands at 433MHz and 868MHz or for similar applications in North America or Asia, e.g. at 315MHz or 915MHz.

- General digital and analog RF receivers at 300 to 930MHz

- Tire pressure monitoring systems (TPMS)

- Remote keyless entry (RKE)

- Low power telemetry systems

- Alarm and security systems

- Active RFID tags

- Remote controls

- Garage door openers

- Home and building automation

#### EVB71121

300 to 930MHz Receiver Evaluation Board Description

# Contents

| Features1                                                          |

|--------------------------------------------------------------------|

| Application Examples1                                              |

| Ordering information1                                              |

| General Description1                                               |

| 1. Theory of Operation                                             |

| 1.1. General                                                       |

| 1.2. Technical Data Overview                                       |

| 1.3. Block Diagram                                                 |

| 1.4. Operating Modes                                               |

| 1.5. Frequency Range                                               |

| 1.6. LNA Selection                                                 |

| 1.7. Demodulation Selection                                        |

| 1.8. Data Slicer                                                   |

| 2. Frequency Planning                                              |

| 2.1. Calculation of Frequency Settings                             |

| 2.2. Standard Frequency Plans                                      |

| 2.3. 433/868MHz Frequency Diversity                                |

| 3. Dual-Channel Application Circuits for FSK & ASK Reception9      |

| 3.1. Peak Detector Data Slicer                                     |

| 3.1.1. Component Arrangement Top Side (Peak Detection Data Slicer) |

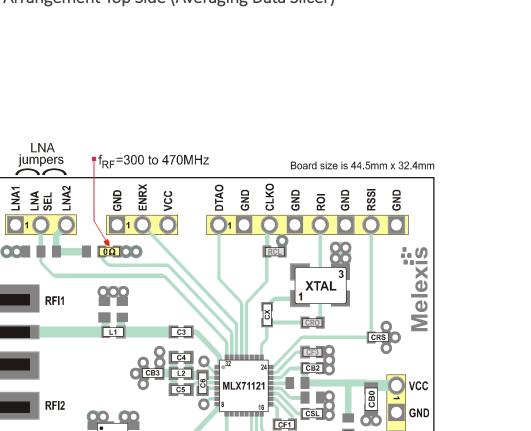

| 3.2. Averaging Data Slicer Configured for Bi-Phase Codes11         |

| 3.2.1. Component Arrangement Top Side (Averaging Data Slicer)      |

| 3.3. Component List for Antenna Space Diversity                    |

| 3.4. PCB Layouts for Antenna Space Diversity                       |

| 4. Board Versions                                                  |

| 5. Package Description                                             |

| 5.1. Soldering Information                                         |

| 6. Reliability Information                                         |

| 7. ESD Precautions                                                 |

| 8. Contact17                                                       |

| 9. Disclaimer                                                      |

### 1.1. General

The MLX71121 receiver architecture is based on a double-conversion super-heterodyne approach. The two LO signals are derived from an on-chip integer-N PLL frequency synthesizer. The PLL reference frequency is derived from a crystal (XTAL). As the first intermediate frequency (IF1) is very high, a reasonably high degree of image rejection is provided even without using an RF front-end filter. At applications asking for very high image rejections, cost-efficient RF front-end filtering can be realized by using a SAW filter in front of the LNA. The second mixer MIX2 is an image-reject mixer.

The receiver signal chain is setup by one (or two) low noise amplifier(s) (LNA1, LNA2), two down-conversion mixers (MIX1, MIX2), an on-chip IF filter (IFF) as well as an IF amplifier (IFA). By choosing the required modulation via an FSK/ASK switch (at pin MODSEL), either the on-chip FSK demodulator (FSK DEMOD) or the RSSI-based ASK detector is selected. A second order data filter (OA1) and a data slicer (OA2) follow the demodulator. The data slicer threshold can be generated from the mean-value of the data stream or by means of the positive and negative peak detectors (PKDET+/-). A digital post-processing of the sliced data signal can be performed by a noise filter (NF) building block.

The dual LNA configuration can be used for antenna space diversity or antenna frequency diversity or to setup an LNA cascade (to further improve the input sensitivity). The two LNAs can also be setup to feed the RF signal differentially.

A sequencer circuit (SEQ) controls the timing during start-up. This is to reduce start-up time and to minimize power dissipation.

A clock output, which is a divide-by-8 version of the crystal oscillator signal, can be used to drive a microcontroller. The clock output is open collector and gets activated through a load connected to positive supply.

### 1.2. Technical Data Overview

- Input frequency ranges: 300 to 470MHz 610 to 930MHz

- Power supply range: 2.1 to 5.5V

- Temperature range: -40 to +125°C

- Shutdown current: 50 nA

- Operating current: 10.0 to 11.1mA

- Internal IF: 1.8MHz with 300kHz 3dB bandwidth

- FM/FSK deviation range: ±10kHz to ±100kHz

- Image rejection:

65dB 1st IF (with external RF front-end filter)

25dB 2nd 15 (intermediates rejection)

- 25dB 2nd IF (internal image rejection)

- Maximum data rate: 50kps RZ (bi-phase) code, 100kps NRZ

- Spurious emission: < -54dBm

- Linear RSSI range: > 60dB

- Crystal reference frequency: 16 to 27MHz

- MCU clock frequency: 2.0 to 3.4MHz

| Input Sensitivity: at 4kbps NRZ, BER = $3 \cdot 10^{-3}$           |                                                            |         |         |         |         |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------|---------|---------|---------|---------|--|--|

| Frequency      315 MHz      433.92 MHz      868.3 MHz      915 MHz |                                                            |         |         |         |         |  |  |

| FSK                                                                | internal IF2=1.8MHz, 300kHz BW,<br>$\Delta f = \pm 20$ kHz | -107dBm | -107dBm | -104dBm | -102dBm |  |  |

| ASK                                                                | internal IF2=1.8MHz, 300kHz BW                             | -112dBm | -112dBm | -108dBm | -105dBm |  |  |

Note: - Sensitivities given for RF input 1 (without SAW filter)

- Sensitivity for RF input 2 is about 2 to 3dB worse (because of SAW filter loss)

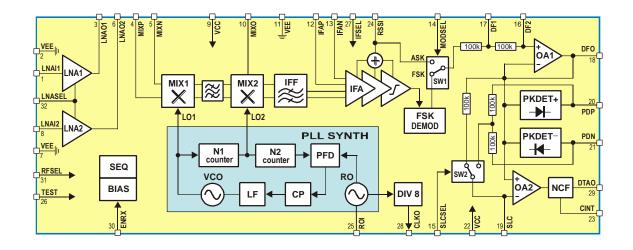

# 1.3. Block Diagram

Fig. 1: MLX71121 block diagram

The MLX71121 receiver IC consists of the following building blocks:

PLL synthesizer (PLL SYNTH) to generate the first and second local oscillator signals LO1 and LO2.

The PLL SYNTH consists of a fully integrated voltage-controlled oscillator (VCO), a distributed feedback divider chain (N1, N2), a phase-frequency detector (PFD) a charge pump (CP), a loop filter (LF) and a crystal-based reference oscillator (RO).

- Two low-noise amplifiers (LNA) for high-sensitivity RF signal reception

- First mixer (MIX1) for down-conversion of the RF signal to the first IF (intermediate frequency)

- Second mixer (MIX2) with image rejection for down-conversion from the first to the second IF

- IF Filter (IFF) with a 1.8MHz center frequency and a 300kHz 3dB bandwidth

- IF amplifier (IFA) to provide a high voltage gain and an RSSI signal output

- FSK demodulator (FSK DEMOD)

- Operational amplifiers OA1 and OA2 for low-pass filtering and data slicing, respectively

- Positive (PKDET+) and negative (PKDET-) peak detectors

- Switches SW1 to select between FSK and ASK as well as SW2 to chose between averaging or peak detection mode.

- Noise cancellation filter (NCF)

- Sequencer circuit (SEQ) and biasing (BIAS) circuit

- Clock output (DIV8)

# 1.4. Operating Modes

| ENRX | Description   |

|------|---------------|

| 0    | Shutdown mode |

| 1    | Receive mode  |

Note: ENRX is pulled down internally.

# 1.5. Frequency Range

Two different receive frequency ranges can be selected by the control signal RFSEL.

| RFSEL | Description                         |  |  |  |

|-------|-------------------------------------|--|--|--|

| 0     | Input frequency range 300 to 470MHz |  |  |  |

| 1     | Input frequency range 610 to 930MHz |  |  |  |

# 1.6. LNA Selection

| LNASEL | Description                |  |  |  |  |

|--------|----------------------------|--|--|--|--|

| 0      | LNA1 active, LNA2 shutdown |  |  |  |  |

| Hi-Z   | LNA1 and LNA2 active       |  |  |  |  |

| 1      | LNA1 shutdown, LNA2 active |  |  |  |  |

Note: Hi-Z state means pin LNASEL is left floating (pin is internally pulled to  $V_{CC}/2$  in this case).

# 1.7. Demodulation Selection

| MODSEL | Description      |  |  |  |

|--------|------------------|--|--|--|

| 0      | ASK demodulation |  |  |  |

| 1      | FSK demodulation |  |  |  |

# 1.8. Data Slicer

| SLCSEL | Description              |

|--------|--------------------------|

| 0      | Averaging detection mode |

| 1      | Peak detection mode      |

# 2. Frequency Planning

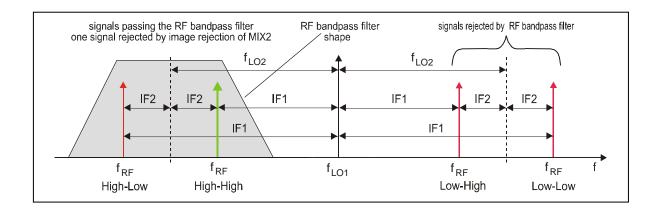

Because of the double conversion architecture that employs two mixers and two IF signals, there are four different combinations for injecting the LO1 and LO2 signals:

- LO1 high side and LO2 high side: receiving at f<sub>RF</sub>(high-high)

- LO1 high side and LO2 low side: receiving at f<sub>RF</sub>(high-low)

- LO1 low side and LO2 high side: receiving at  $f_{\rm RF}({\rm low-high})$

- LO1 low side and LO2 low side: receiving at  $f_{\mbox{\tiny RF}}(\mbox{low-low})$

As a result, four different radio frequencies (RFs) could yield one and the same second IF (IF2). Fig. 2 shows this for the case of receiving at  $f_{RF}$ (high-high). In the example of Fig. 2, the image signals at  $f_{RF}$ (low-high) and  $f_{RF}$ (low-low) are suppressed by the bandpass characteristic provided by the RF front-end. The bandpass shape can be achieved either with a SAW filter (featuring just a couple of MHz bandwidth), or by the tank circuits at the LNA input and output (this typically yields 30 to 60MHz bandwidth). In any case, the high value of the first IF (IF1) helps to suppress the image signals at  $f_{RF}$ (low-high) and  $f_{RF}$ (low-low).

The two remaining signals at IF1 resulting from  $f_{RF}$ (high-high) and  $f_{RF}$ (high-low) are entering the second mixer MIX2. This mixer features image rejection with so-called single-sideband (SSB) selection. This means either the upper or lower sideband of IF1 can be selected. In the example of Fig. 2, LO2 high-side injection has been chosen to select the IF2 signal resulting from  $f_{RF}$ (high-high).

#### *Fig. 2:* The four receiving frequencies in a double conversion superhet receiver

It can be seen from the block diagram of Fig. 1 that there is a fixed relationship between the LO signal frequencies ( $f_{LO1}$ ,  $f_{LO2}$ ) and the reference oscillator frequency  $f_{RO}$ .

$$\mathbf{f}_{\mathrm{LO1}} = \mathbf{N}_1 \cdot \mathbf{f}_{\mathrm{LO2}} \qquad \qquad \mathbf{f}_{\mathrm{LO2}} = \mathbf{N}_2 \cdot \mathbf{f}_{\mathrm{RO}}$$

The operating frequency of the internal IF filter (IFF) and FSK demodulator (FSK DEMOD) is 1.8MHz. Therefore the second IF (IF2) is set to 1.8MHz as well.

# 2.1. Calculation of Frequency Settings

The receiver has two predefined receive frequency plans which can be selected by the RFSEL control pin. Depending on the logic level of RFSEL pin the sideband selection of the second mixer and the counter settings for  $N_1$  and  $N_2$  are changed accordingly. (see in 1.5)

| RFSEL | Injection | f <sub>Rfmin</sub> [MHz] | f <sub>Rfmax</sub> [MHz] | N <sub>1</sub> | N <sub>2</sub> |

|-------|-----------|--------------------------|--------------------------|----------------|----------------|

| 0     | high-low  | 300                      | 470                      | 4              | 6              |

| 1     | low-high  | 610                      | 930                      | 2              | 12             |

The following table shows the relationships of several internal receiver frequencies for the two input frequency ranges.

| f <sub>RF</sub> [MHz] | f <sub>IF1</sub>                                                                            | f <sub>L01</sub>                            | f <sub>LO2</sub>                                 | f <sub>RO</sub>                                 |

|-----------------------|---------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------|-------------------------------------------------|

| 300 to 470            | $\frac{\mathbf{f}_{\text{RF}} + \mathbf{N}_{1}\mathbf{f}_{\text{IF2}}}{\mathbf{N}_{1} - 1}$ | $\frac{N_{1}(f_{RF}+f_{IF2})}{N_{1}-1}$     | $\frac{f_{\text{RF}}+f_{\text{IF2}}}{N_1-1}$     | $\frac{f_{\rm RF} + f_{\rm IF2}}{N_2(N_1 - 1)}$ |

| 610 to 930            | $\frac{f_{\text{RF}} - N_1 f_{\text{IF2}}}{N_1 + 1}$                                        | $\frac{N_{1}(f_{RF} + f_{IF2})}{N_{1} + 1}$ | $\frac{f_{\text{RF}} + f_{\text{IF2}}}{N_1 + 1}$ | $\frac{f_{\rm RF} + f_{\rm IF2}}{N_2(N_1 + 1)}$ |

Given IF2 = 1.8MHz and the corresponding  $N_1$ ,  $N_2$  counter settings, above equations can be transferred into the following table.

| f <sub>RF</sub> [MHz] | f <sub>IF1</sub>            | f <sub>L01</sub>               | f <sub>LO2</sub>   | f <sub>ro</sub>                    |

|-----------------------|-----------------------------|--------------------------------|--------------------|------------------------------------|

| 300 to 470            | $\frac{f_{RF} + 7.2MHz}{3}$ | $\frac{4(f_{RF} + 1.8MHz)}{3}$ | $f_{RF} + 1.8 MHz$ | $\frac{f_{\rm RF}+1.8MHz}{18}$     |

| 610 to 930            | $\frac{f_{RF} - 3.6MHz}{3}$ | $\frac{2(f_{RF} + 1.8MHz)}{3}$ | 3                  | $\frac{f_{\rm RF} + 1.8 M Hz}{36}$ |

#### EVB71121

300 to 930MHz Receiver Evaluation Board Description

# 2.2. Standard Frequency Plans

#### IF2 = 1.8MHz.

| RFSEL | f <sub>RF</sub> [MHz] | f <sub>IF1</sub> [MHz] | f <sub>LO1</sub> [MHz] | f <sub>LO2</sub> [MHz] | f <sub>RO</sub> [MHz] |

|-------|-----------------------|------------------------|------------------------|------------------------|-----------------------|

| 0     | 315                   | 107.40                 | 422.40                 | 105.60                 | 17.600000             |

|       | 433.92                | 147.04                 | 580.96                 | 145.24                 | 24.206667             |

| 1     | 868.3                 | 288.23                 | 580.07                 | 290.03                 | 24.169444             |

| 1     | 915                   | 303.80                 | 611.20                 | 305.60                 | 25.466667             |

# 2.3. 433/868MHz Frequency Diversity

The receiver's multi-band functionality can be used to operate at two different frequency bands just by changing the logic level at pin RFSEL and without changing the crystal. This feature is applicable for common use of the 433 and 868MHz bands. Below table shows the corresponding frequency plans.

#### IF2 = 1.8MHz.

| RFSEL | f <sub>RF</sub> [MHz] | f <sub>IF1</sub> [MHz] | f <sub>LO1</sub> [MHz] | f <sub>LO2</sub> [MHz] | f <sub>RO</sub> [MHz] |

|-------|-----------------------|------------------------|------------------------|------------------------|-----------------------|

| 0     | 433.25                | 146.82                 | 580.07                 | 145.02                 | 24.169444             |

| 1     | 868.3                 | 288.23                 | 580.07                 | 290.03                 | 24.109444             |

**EVB71121** 300 to 930MHz Receiver Evaluation Board Description

# **3. Dual-Channel Application Circuits for FSK & ASK Reception**

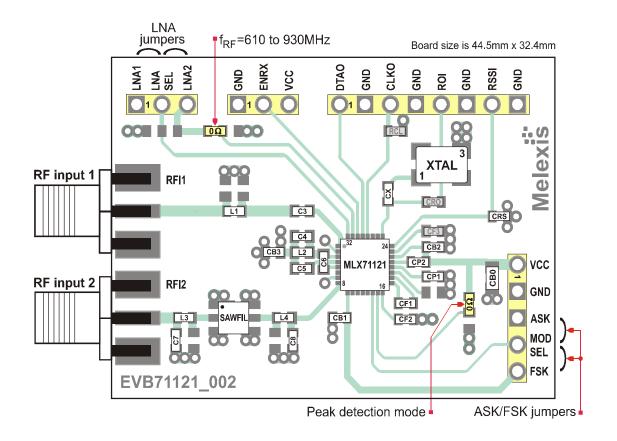

### 3.1. Peak Detector Data Slicer

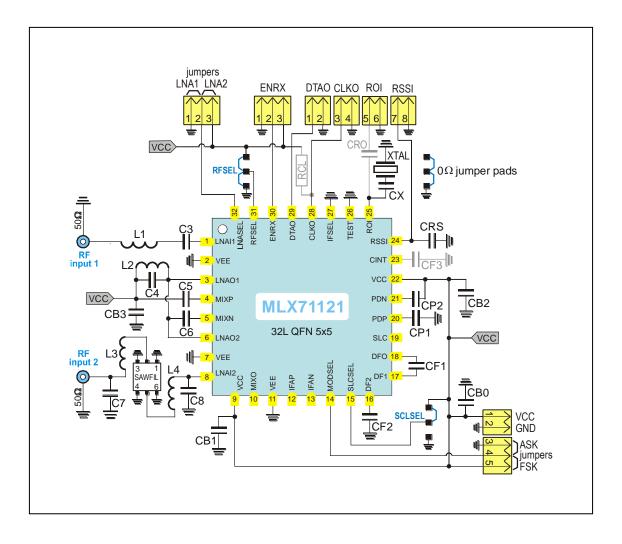

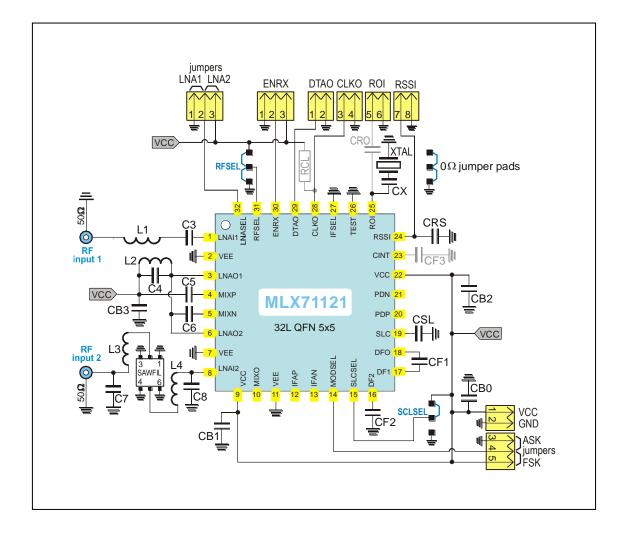

*Fig. 3: Circuit schematic*

### 3.1.1. Component Arrangement Top Side (Peak Detection Data Slicer)

*Fig. 4: PCB top-side view*

Fig. 5: Circuit schematic

ASK

MOD SEL FSK

ASK/FSK jumpers

CF2

св1 8

Averaging detection mode

SAWFIL

L3

C7

EVB71121\_002

L4

ő

RF input 1

**RF input 2**

300 to 930MHz Receiver Evaluation Board Description

# 3.3. Component List for Antenna Space Diversity

#### Below table is for all application circuits shown in Figures 3.1 and 3.2

| Part       | Size         | Value @<br>315 MHz                                                               | Value @<br>433.92 MHz                                 | Value @<br>868.3 MHz                                  | Value @<br>915 MHz                                        | Tol.                        | Description                                                        |  |

|------------|--------------|----------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------|-----------------------------|--------------------------------------------------------------------|--|

| C3         | 0603         | 100 pF                                                                           | 100 pF                                                | 100 pF                                                | 100 pF                                                    | ±5%                         | LNA input filtering capacitor                                      |  |

| C4         | 0603         | 4.7 pF                                                                           | 3.9 pF                                                | 2.2 pF                                                | 1.5 pF                                                    | ±5%                         | LNA output tank capacitor                                          |  |

| C5         | 0603         | 100 pF                                                                           | 100 pF                                                | 100 pF                                                | 100 pF                                                    | ±5%                         | MIX1 positive input matching capacitor                             |  |

| C6         | 0603         | 100 pF                                                                           | 100 pF                                                | 100 pF                                                | 100 pF                                                    | ±5%                         | MIX1 negative input matching capacitor                             |  |

| C7         | 0603         | NIP                                                                              | 4.7 pF                                                | 3.9 pF                                                | NIP                                                       | ±5%                         | matching capacitor                                                 |  |

| C8         | 0603         | NIP                                                                              | NIP                                                   | 1.0 pF                                                | NIP                                                       | ±5%                         | matching capacitor                                                 |  |

| CB0        | 0805         | 330 nF                                                                           | 330 nF                                                | 330 nF                                                | 330 nF                                                    | ±10%                        | decoupling capacitor,                                              |  |

| CB1        | 0603         | 330 pF                                                                           | 330 pF                                                | 330 pF                                                | 330 pF                                                    | ±10%                        | decoupling capacitor,                                              |  |

| CB2        | 0603         | 330 pF                                                                           | 330 pF                                                | 330 pF                                                | 330 pF                                                    | ±10%                        | decoupling capacitor,                                              |  |

| CB3        | 0603         | 330 pF                                                                           | 330 pF                                                | 330 pF                                                | 330 pF                                                    | ±10%                        | decoupling capacitor,                                              |  |

| CF1        | 0603         | 680 pF                                                                           | 680 pF                                                | 680 pF                                                | 680 pF                                                    | ±10%                        | data low-pass filter capacitor,<br>for data rate of 4 kbps NRZ     |  |

| CF2        | 0603         | 330 pF                                                                           | 330 pF                                                | 330 pF                                                | 330 pF                                                    | ±10%                        | data low-pass filter capacitor,<br>for data rate of 4 kbps NRZ     |  |

| CF3        | 0603         | value according to the date rate<br>connected to ground if noise filter not used |                                                       |                                                       |                                                           |                             | optional capacitance for noise filter                              |  |

| CP1        | 0603         | 33 nF                                                                            | 33 nF                                                 | 33 nF                                                 | 33 nF                                                     | ±10%                        | PKDET positive filtering capacitor,<br>for data rate of 4 kbps NRZ |  |

| CP2        | 0603         | 33 nF                                                                            | 33 nF F                                               | 33 nF                                                 | 33 nF                                                     | ±10%                        | PKDET negative filtering capacitor, for data rate of 4 kbps NRZ    |  |

| CRS        | 0603         | 1 nF                                                                             | 1 nF                                                  | 1 nF                                                  | 1 nF                                                      | ±10%                        | RSSI output low pass capacitor                                     |  |

| CRO        | 0603         | 1 nF                                                                             | 1 nF                                                  | 1 nF                                                  | 1 nF                                                      | ±5%                         | optional capacitor,<br>to couple external RO signal                |  |

| CSL        | 0603         | 100 nF 100 nF 100 nF                                                             |                                                       |                                                       | 100 nF                                                    | +10%                        | data slicer capacitor,                                             |  |

| CSL        |              |                                                                                  | for averaging dete                                    | ction mode only                                       | ±10%                                                      | for data rate of 4 kbps NRZ |                                                                    |  |

| СХ         | 0603         | 27 pF                                                                            | 27 pF                                                 | 27 pF                                                 | 27 pF                                                     | ±5%                         | crystal series capacitor                                           |  |

| L1         | 0603         | 56 nH                                                                            | 27 nH                                                 | 0 Ω                                                   | 0 Ω                                                       | ±5%                         | matching inductor                                                  |  |

| L2         | 0603         | 27 nH                                                                            | 15 nH                                                 | 3.9 nH                                                | 3.9 nH                                                    | ±5%                         | LNA output tank inductor                                           |  |

| L3         | 0603         | 0 Ω                                                                              | 47 nH                                                 | 22 nH                                                 | 0 Ω                                                       | ±5%                         | matching inductor                                                  |  |

| L4         | 0603         | 56 nH                                                                            | 68 nH                                                 | 22 nH                                                 | 0 Ω                                                       | ±5%                         | matching inductor                                                  |  |

| RCL        | 0603         | 3.3 kΩ                                                                           | 3.3 kΩ                                                | 3.3 kΩ                                                | 3.3 kΩ                                                    | ±5%                         | optional CLK output resistor,<br>to clock output signal generated  |  |

| SAW<br>FIL | SMD<br>3x3   | SAFDC315M<br>SM0T00<br>(315 MHz)                                                 | RF3446<br>(433.92 MHz)                                | SAFCC868M<br>SL0X00<br>(868.3 MHz)                    | SAFCC915M<br>ALON00<br>(915 MHz)                          |                             | low-loss SAW filter from Murata<br>or equivalent part              |  |

| XTAL       | SMD<br>5x3.2 | 17.60000<br>MHz                                                                  | 24.206667<br>MHz                                      | 24.169444<br>MHz                                      | 25.46667<br>MHz                                           |                             |                                                                    |  |

|            |              | HEX24-<br>17.6MHZ-12-<br>50-F-H20-<br>T2075-W2-T                                 | HEX24-<br>24.206667MHZ-<br>12-50-F-H20-<br>T2075-W2-T | HEX24-<br>24.169444MHZ<br>-12-50-F-H20-<br>T2075-W2-T | HEX24-<br>25.466667MH<br>Z-12-50-F-<br>H20-T2075-<br>W2-T |                             | crystal from Telcona,<br>or equivalent part                        |  |

|            |              |                                                                                  | $\pm$ 20ppm cal., $\pm$                               | 30ppm temp.                                           |                                                           |                             |                                                                    |  |

Note: NIP – not in place, may be used optionally

- **six**9l9M GND ASK MOD SEL FSK Š GNÐ 💽 00000 ISSN 🔘 GND CIND юя 🔘 GND 🔘 сгко GND CND OATO 🔘 umu 0 00 20A 🔘 00 хынэ 🔘 O GND 002 EVB71121 2ANJ 🔘 RFI2 RF11

- 00000 00 8 0 88 🖸 00 000 000 0 8 0 0 0 00 0 0 8 0 00 0 000 8 8 8 8 8 8 8 C 0 8

PCB top view

PCB bottom view

# 4. Board Versions

| Туре     | Frequency/MHz |      | Board Execution |                   |  |

|----------|---------------|------|-----------------|-------------------|--|

| EVB71121 | -315          | -315 |                 | antenna version   |  |

|          | -433          |      | -C              | connector version |  |

|          | -868          |      |                 |                   |  |

|          | -915          |      |                 |                   |  |

Board layout data in Gerber format is available, board size is 32.4mm x 44.5mm.

Note:

available EVB setups

**EVB71121** 300 to 930MHz Receiver Evaluation Board Description

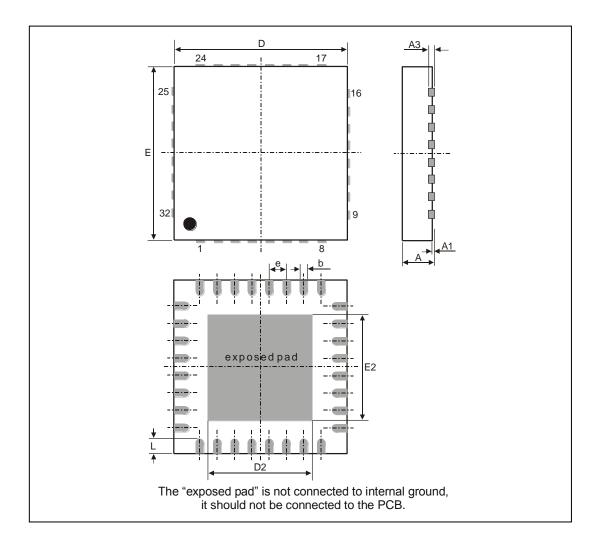

# 5. Package Description

The device MLX71121 is RoHS compliant.

#### Fig 5: 32L QFN 5x5 Quad

| all Dime              | nsion in r | nm    |       |       |        |       |        |        |        |        |

|-----------------------|------------|-------|-------|-------|--------|-------|--------|--------|--------|--------|

|                       | D          | E     | D2    | E2    | Α      | A1    | A3     | L      | е      | b      |

| min                   | 4.75       | 4.75  | 3.00  | 3.00  | 0.80   | 0     | 0.20   | 0.3    | 0.50   | 0.18   |

| max                   | 5.25       | 5.25  | 3.25  | 3.25  | 1.00   | 0.05  | 0.20   | 0.5    | 0.50   | 0.30   |

| all Dimension in inch |            |       |       |       |        |       |        |        |        |        |

| min                   | 0.187      | 0.187 | 0.118 | 0.118 | 0.0315 | 0     | 0.0079 | 0.0118 | 0.0197 | 0.0071 |

| max                   | 0.207      | 0.207 | 0.128 | 0.128 | 0.0393 | 0.002 | 0.0079 | 0.0197 |        | 0.0118 |

# 5.1. Soldering Information

• The device MLX71121 is qualified for MSL3 with soldering peak temperature 260 deg C according to JEDEC J-STD-20

# 6. Reliability Information

This Melexis device is classified and qualified regarding soldering technology, solderability and moisture sensitivity level, as defined in this specification, according to following test methods:

Reflow Soldering SMD's (Surface Mount Devices)

- IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices (classification reflow profiles according to table 5-2)"

- EIA/JEDEC JESD22-A113 "Preconditioning of Nonhermetic Surface Mount Devices Prior to Reliability Testing (reflow profiles a ccording to table 2)"

Wave Soldering SMD's (Surface Mount Devices) and THD's (Through Hole Devices)

- EN60749-20 "Resistance of plastic- encapsulated SMD's to combined effect of moisture and soldering heat"

- EIA/JEDEC JESD22-B106 and EN60749-15 "Resistance to soldering temperature for through-hole mounted devices"

Iron Soldering THD's (Through Hole Devices)

EN60749-15 "Resistance to soldering temperature for through-hole mounted devices"

Solderability SMD's (Surface Mount Devices) and THD's (Through Hole Devices)

• EIA/JEDEC JESD22-B102 and EN60749-21 "Solderability"

For all soldering technologies deviating from above mentioned standard conditions (regarding peak temperature, temperature gradient, temperature profile etc) additional classification and qualification tests have to be agreed upon with Melexis.

The application of Wave Soldering for SMD's is allowed only after consulting Melexis regarding assurance of adhesive strength between device and board.

Melexis is contributing to global environmental conservation by promoting **lead free** solutions. For more information on qualification of **RoHS** compliant products (RoHS = European directive on the Restriction Of the Use of Certain Hazardous Substances) please visit the quality page on our website:

http://www.melexis.com/quality\_leadfree.aspx

# 7. ESD Precautions

Electronic semiconductor products are sensitive to Electro Static Discharge (ESD). Always observe Electro Static Discharge control procedures whenever handling semiconductor products.

# 8. Contact

For the latest version of this document, go to our website at <u>www.melexis.com</u>.

For additional information, please contact our Direct Sales team and get help for your specific needs:

| Europe, Africa | Telephone: +32 13 67 04 95       |  |  |  |

|----------------|----------------------------------|--|--|--|

|                | Email : sales_europe@melexis.com |  |  |  |

| Americas       | Telephone: +1 603 223 2362       |  |  |  |

|                | Email : sales_usa@melexis.com    |  |  |  |

| Asia           | Email : sales_asia@melexis.com   |  |  |  |

# 9. Disclaimer

The information furnished by Melexis herein ("Information") is believed to be correct and accurate. Melexis disclaims (i) any and all liability in connection with or arising out of the furnishing, performance or use of the technical data or use of the product(s) as described herein ("Product") (ii) any and all liability, including without limitation, special, consequential or incidental damages, and (iii) any and all warranties, express, statutory, implied, or by description, including warranties of fitness for particular purpose, non-infringement and merchantability. No obligation or liability shall arise or flow out of Melexis' rendering of technical or other services.

The Information is provided "as is" and Melexis reserves the right to change the Information at any time and without notice. Therefore, before placing orders and/or prior to designing the Product into a system, users or any third party should obtain the latest version of the relevant information to verify that the information being relied upon is current. Users or any third party must further determine the suitability of the Product for its application, including the level of reliability required and determine whether it is fit for a particular purpose.

The Information is proprietary and/or confidential information of Melexis and the use thereof or anything described by the Information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights.

This document as well as the Product(s) may be subject to export control regulations. Please be aware that export might require a prior authorization from competent authorities. The Product(s) are intended for use in normal commercial applications. Unless otherwise agreed upon in writing, the Product(s) are not designed, authorized or warranted to be suitable in applications requiring extended temperature range and/or unusual environmental requirements. High reliability applications, such as medical life-support or lifesustaining equipment are specifically not recommended by Melexis.

The Product(s) may not be used for the following applications subject to export control regulations: the development, production, processing, operation, maintenance, storage, recognition or proliferation of 1) chemical, biological or nuclear weapons, or for the development, production, maintenance or storage of missiles for such weapons: 2) civil firearms, including spare parts or ammunition for such arms; 3) defense related products, or other material for military use or for law enforcement; 4) any applications that, alone or in combination with other goods, substances or organisms could cause serious harm to persons or goods and that can be used as a means of violence in an armed conflict or any similar violent situation.

The Products sold by Melexis are subject to the terms and conditions as specified in the Terms of Sale, which can be found at https://www.melexis.com/en/legal/terms-andconditions.

This document supersedes and replaces all prior information regarding the Product(s) and/or previous versions of this document.

Melexis NV © - No part of this document may be reproduced without the prior written consent of Melexis. (2016)

ISO/TS 16949 and ISO14001 Certified

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RF Development Tools category:

Click to view products by Melexis manufacturer:

Other Similar products are found below :

MAAP-015036-DIEEV2 EV1HMC1113LP5 EV1HMC252AQS24 EV1HMC6146BLC5A EV1HMC637ALP5 EVAL01-HMC1048LC3B EVAL01-HMC661LC4B EVAL-ADF7020-1DBZ4 EVAL-ADF7020-1DBZ5 EVAL-ADF7020-1DBZ6 EVAL-ADF7021DB9Z EVAL-ADF7021DBJZ EVAL-ADF7021DBZ2 EVAL-ADF7021DBZ6 EVAL-ADF7021-NDBZ2 EVAL-ADF7021-VDB3Z EVAL-ADF7023DB3Z EVAL-ADF7023-JDB3Z EVAL-ADF70XXEKZ1 EVAL-ADF7241DB1Z F0440EVBI F1241EVBI F1423EVB-DI F1423EVB-SI F1701EVBI F1751EVBI F2250EVBI MICRF219A-433 EV 122410-HMC686LP4E AD6679-500EBZ 126223-HMC789ST89E ADL5363-EVALZ ADL5369-EVALZ 130437-HMC1010LP4E 131352-HMC1021LP4E 131372-HMC951LP4E 130436-HMC1010LP4E DEMOBOARD-U2790B ATR2406-PNQW EKIT01-HMC1197LP7F Si4705-D60-EVB Si4835-Demo LMV228SDEVAL SKYA21001-EVB SMP1331-08-EVB EV1HMC618ALP3 EV1HMC641ALC4 EV1HMC8410LP2F EVAL\_PAN4555ETU EVAL01-HMC1041LC4