300 to 930MHz FSK/FM/ASK Receiver

Datasheet

# **Features**

- Programmable PLL synthesizer

- 8-channel preconfigured or fully programmable SPI mode

- Double super-heterodyne receiver architecture with 2<sup>nd</sup> mixer as image rejection mixer

- Reception of FSK, FM and ASK modulated signals

- Low shut-down and operating currents

- AGC automatic gain control

- On-chip IF filter

- Fully integrated FSK/FM demodulator

- RSSI for level indication and ASK detection

- 2<sup>nd</sup> order low-pass data filter

- Positive and negative peak detectors

- Data slicer (with averaging or peak-detector adaptive threshold)

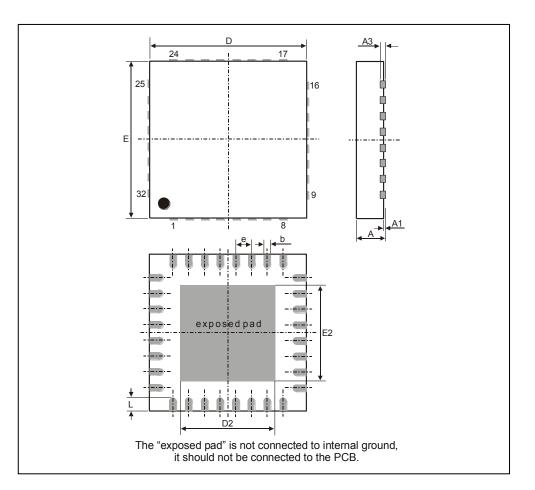

- 32-pin Quad Flat No-Lead Package (QFN)

- EVB programming software is available on Melexis web site

# **Ordering Information**

| Part Number | Temperature Code     | Package Code           | Delivery Form             |

|-------------|----------------------|------------------------|---------------------------|

| MLX71122    | R (-40 °C to 105 °C) | LQ (32 L QFN 5x5 Quad) | 73 pc/tube<br>5000 pc/T&R |

# **Application Examples**

- General digital and analog RF receivers at 300 to 930MHz

- Tire pressure monitoring systems (TPMS)

- Remote keyless entry (RKE)

- Low power telemetry systems

- Alarm and security systems

- Active RFID tags

- Remote controls

- Garage door openers

- Home and building automation

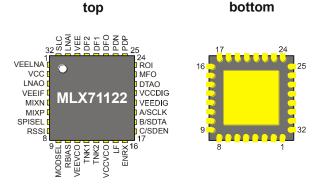

# **Pin Description**

# **General Description**

The MLX71122 is a multi-channel RF receiver IC based on a double-conversion super-heterodyne architectture. It is designed to receive FSK and ASK modulated RF signals either in 8 predefined frequency channels or frequency programmable via a 3-wire serial programming interface (SPI).

The IC is designed for a variety of applications, for example in the European bands at 433MHz and 868MHz or for the use in North America or Asia, e.g. at 315MHz, 447MHz or 915MHz.

# **Document Content**

| 1. Theory of Operation                                               | 6  |

|----------------------------------------------------------------------|----|

| 1.1. General                                                         | 6  |

| 1.2. Technical Data Overview                                         | 7  |

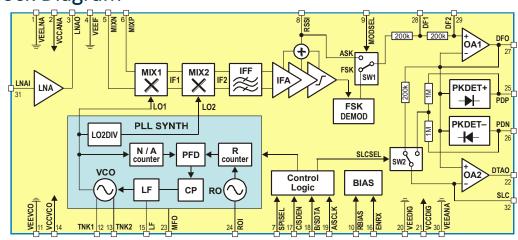

| 1.3. Block Diagram                                                   | 7  |

| 1.4. Enable/Disable in ABC Mode                                      |    |

| 1.5. Demodulation Selection in ABC Mode                              |    |

| 1.6. Programming Modes                                               |    |

| 1.7. Preconfigured Frequencies in ABC Mode                           |    |

| 2. Pin Definitions and Descriptions                                  |    |

|                                                                      |    |

| 2.1. Pin Schematics                                                  |    |

| 2.2. RF Pin Impedance Models                                         |    |

| 3. Functional Description                                            | 16 |

| 3.1. Frequency Planning                                              |    |

| 3.1.1. Calculation of Counter Settings                               |    |

| 3.1.2. Calculation of LO1 and IF1 frequency for Low Frequency Bands  |    |

| 3.1.3. Calculation of LO1 and IF1 frequency for High Frequency Bands |    |

| 3.1.4. Counter Setting Examples for SPI Mode                         |    |

| 3.1.5. Counter Settings in ABC Mode – 8+1 Preconfigured Channels     | 20 |

| 3.2. PLL Frequency Synthesizer                                       |    |

| 3.2.1. Pulse Swallow Counter                                         |    |

| 3.2.2. PLL Counter Ranges                                            |    |

| 3.2.3. Reference Oscillator (RO)                                     |    |

| 3.2.4. Phase-Frequency Detector (PFD)                                |    |

| 3.2.5. Charge Pump (CP)                                              |    |

| 3.2.6. Loop Filter (LF)                                              |    |

| 3.2.7. Lock Detector (LD)                                            |    |

| 3.2.8. Voltage Controlled Oscillator (VCO)                           |    |

| 3.2.9. Loop Filter Calculation                                       |    |

| 3.3. Receiver Front End                                              |    |

| 3.3.1. Low Noise Amplifier (LNA) and Mixer 1 (MIX1)                  |    |

| 3.3.2. Mixer 2 (MIX2)                                                |    |

| 3.3.3. IF Filter (IFF)                                               |    |

| 3.3.4. FSK Demodulator                                               |    |

| 3.3.5. Autotuning Circuit                                            |    |

| 3.3.6. IF Amplifier (IFA)                                            |    |

| 3.3.7. Automatic Gain Control (AGC)                                  |    |

| 3.4. Data Path                                                       |    |

|    | 3.4.1. Data Filter (DF)                                                 | 22   |

|----|-------------------------------------------------------------------------|------|

|    | 3.4.2. Averaging Data Slicer Mode                                       |      |

|    | 3.4.3. Peak Detectors (PKDET)                                           |      |

|    | 3.4.4. Output Comparator                                                |      |

|    | 3.5. Frequency Acceptance Range                                         | . 35 |

|    | 3.6. Biasing System                                                     | . 35 |

|    | 3.7. Operating Modes                                                    | . 35 |

|    | 3.8. Multi Functional Output                                            | . 36 |

|    | 3.9. SPI Description                                                    | . 36 |

|    | 3.9.1. General                                                          | . 36 |

|    | 3.9.2. Read / Write Sequences                                           | . 37 |

|    | 3.9.3. Serial Programming Interface Timing                              | . 38 |

| 4. | Register Description                                                    | 39   |

|    | 4.1. Register Overview                                                  | . 39 |

|    | 4.1.1. Control Word R0                                                  | . 41 |

|    | 4.1.2. Control Word R1                                                  |      |

|    | 4.1.3. Control Word R2                                                  |      |

|    | 4.1.4. Control Word R3                                                  |      |

|    | 4.1.5. Control Word R4                                                  |      |

|    | 4.1.6. Control Word R5                                                  |      |

|    | 4.1.7. Control Word R6<br>4.1.8. Control Word R7 (Read-only Register)   |      |

| 5  | Technical Data                                                          |      |

| ٦. |                                                                         |      |

|    | 5.1. Absolute Maximum Ratings                                           |      |

|    | 5.2. Normal Operating Conditions                                        |      |

|    | 5.3. Crystal Parameters                                                 | . 47 |

|    | 5.4. Serial Programming Interface (SPI)                                 | . 47 |

|    | 5.5. DC Characteristics                                                 | . 48 |

|    | 5.6. AC System Characteristics                                          | . 50 |

| 6. | Test Circuits                                                           | 52   |

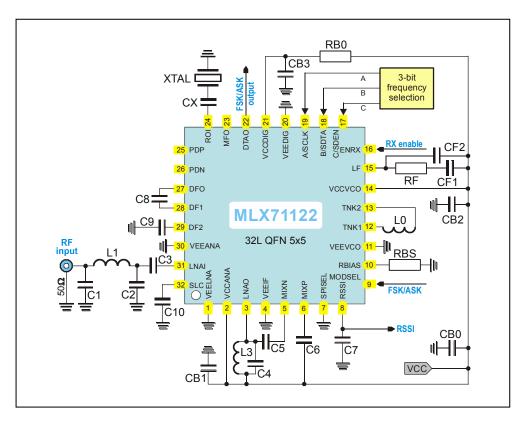

|    | 6.1. Standard FSK & ASK Reception in 8-Channel Preconfigured (ABC) Mode | . 52 |

|    | 6.1.1. Averaging Data Slicer Configured for Bi-Phase Codes              | . 52 |

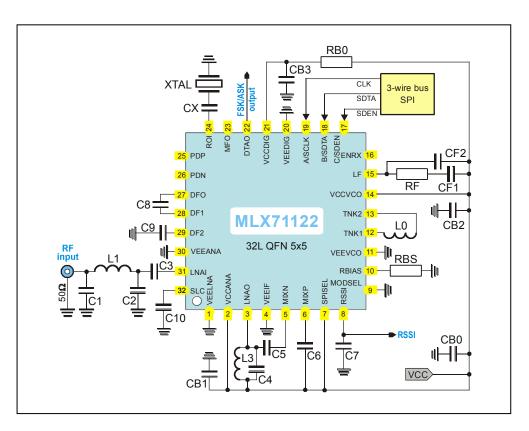

|    | 6.2. Standard FSK & ASK Reception in SPI Mode                           | . 53 |

|    | 6.2.1. Averaging Data Slicer Configured for Bi-Phase Codes              |      |

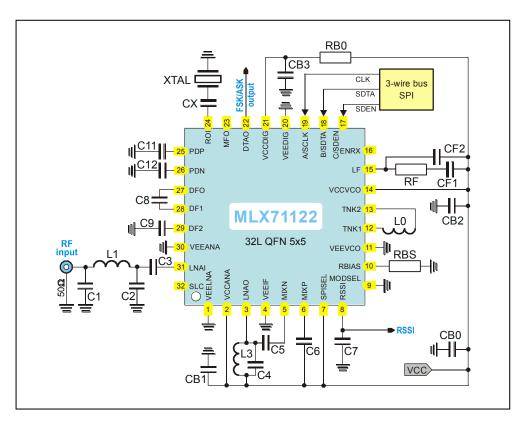

|    | 6.2.2. Peak Detector Data Slicer Configured for NRZ Codes               | . 54 |

|    | 6.3. Test Circuit Component List                                        | . 55 |

| 7. | Package Description                                                     | 56   |

|    | 7.1. Soldering Information                                              | . 56 |

| 8. Reliability Information | 57 |

|----------------------------|----|

| 9. ESD Precautions         | 57 |

| 10. Disclaimer             | 58 |

| 11. Contact                | 59 |

# **1. Theory of Operation**

# 1.1. General

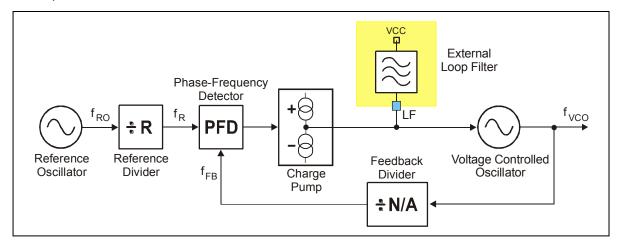

The MLX71122 receiver architecture is based on a double-conversion super-heterodyne approach. The two LO signals are derived from an on-chip integer-N PLL frequency synthesizer. The PLL reference frequency is derived from a crystal (XTAL). The PLL synthesizer consists of an integrated voltage-controlled oscillator with external inductor, a programmable feedback divider chain, a programmable reference divider, a phase-frequency detector with a charge pump and an external loop filter.

In the receiver's down-conversion chain, two mixers MIX1 and MIX2 are driven by the internal local oscillator signals LO1 and LO2, respectively. The second mixer MIX2 is an image-reject mixer. As the first intermediate frequency (IF1) is very high (typically above 100 MHz), a reasonably high degree of image rejection is provided even without using an RF front-end filter. At applications asking for very high image rejections, cost-efficient RF front-end filtering can be realized by using a SAW filter in front of the LNA.

The receiver signal chain is set up by a low noise amplifier (LNA), two down-conversion mixers (MIX1 and MIX2), an on-chip IF filter (IFF) as well as an IF amplifier (IFA). By choosing the required modulation via an FSK/ASK switch (at pin MODSEL), either the on-chip FSK demodulator (FSK DEMOD) or the RSSI-based ASK detector is selected. A second order data filter (OA1) and a data slicer (OA2) follow the demodulator. The data slicer threshold can be generated from the mean-value of the data stream or by means of the positive and negative peak detectors (PKDET+/-).

In general the MLX71122 can be set to shut-down mode, where all receiver functions are completely turned off, and to several other operating modes. There are two global operating modes that are selectable via the logic level at pin SPISEL:

- 8-channel pre-configured mode (ABC mode)

- fully programmable mode (**SPI mode**).

In ABC mode the number of frequency channels is limited to eight but no microcontroller programming is required. In this case the three lines of the serial programming interface (SPI) are used to select one of the eight predefined frequency channels via simple 3-bit parallel programming. Pins ENRX and MODSEL are used to enable/disable the receiver and to select FSK or ASK demodulation, respectively.

SPI mode is recommended for full programming flexibility. In this case the three lines of the SPI are configured as a standard 3-wire bus (SDEN, SDTA and SCLK). This allows changing many parameters of the receiver, for example more operating modes, channels, frequency resolutions, gains, demodulation types, data slicer settings and more. The pin MODSEL has no effect in this mode.

300 to 930MHz FSK/FM/ASK Receiver Datasheet

# 1.2. Technical Data Overview

- Input frequency ranges: 300 to 930MHz

- Power supply range: 3.0 to 5.5V

- Temperature range: -40 to +110°C

- Shutdown current: 50nA

- Operating current: 12mA (typ.)

- FSK input sensitivity: -107dBm (typ.)

- ASK input sensitivity: -112dBm (typ.)

- Internal IF2: 2MHz with 230kHz 3dB bandwidth

- Maximum data rate: 100kbps NRZ code, 50kbps bi-phase code

- Minimum frequency resolution: 10kHz

- Total image rejection: > 65dB (with external RF front-end filter)

- FSK/FM deviation range: ±10 to ±50kHz

- Spurious emission: < -70dBm</p>

- Linear RSSI range: > 50dB

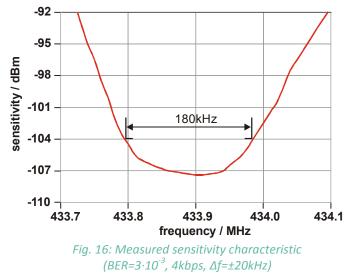

- FSK input frequency acceptance range:

- 180kHz (3dB sensitivity loss)

- Crystal reference frequency: 10MHz

#### Fig. 1: MLX71122 block diagram

The MLX71122 receiver IC consists of the following building blocks:

- PLL synthesizer (PLL SYNTH) to generate the first and second local oscillator signals LO1 and LO2, parts of the PLL SYNTH are the voltage-controlled oscillator (VCO), the feedback dividers N/A and R, the phase-frequency detector (PFD), the charge pump (CP) and the crystal-based reference oscillator (RO)

- Low-noise amplifier (LNA) for high-sensitivity RF signal reception

- First mixer (MIX1) for down-conversion of the RF signal to the first IF (intermediate frequency)

- Second mixer (MIX2) with image rejection for down-conversion from the first to the second IF

- IF Filter (IFF) with a 2MHz center frequency and a 230kHz 3dB bandwidth

- IF amplifier (IFA) to provide a large amount of voltage gain and an RSSI signal output

- FSK demodulator (FSK DEMOD)

- Operational amplifiers OA1 and OA2 for low-pass filtering and data slicing, respectively

- Positive (PKDET+) and negative (PKDET-) peak detectors

- Switches SW1 to select between FSK and ASK as well as SW2 to chose between averaging or peak detector data slicer

- Control logic with 3-wire bus serial programming interface (SPI)

- Biasing circuit with modes control

#### Page 7 of 59

## 1.3. Block Diagram

# 1.4. Enable/Disable in ABC Mode

| ENRX | Description   |

|------|---------------|

| 0    | Shutdown mode |

| 1    | Receive mode  |

Pin ENRX is pulled down internally. Device is in shutdown by default, after power supply on. If ENRX = 0 and SPISEL = 1 then operating modes according to OPMODE bit (refer to control word R0). If ENRX = 1 then OPMODE bit has no effect (hardwired receive mode).

## 1.5. Demodulation Selection in ABC Mode

| MODSEL                                                                                             | Description      |  |  |  |  |

|----------------------------------------------------------------------------------------------------|------------------|--|--|--|--|

| 0                                                                                                  | FSK demodulation |  |  |  |  |

| 1                                                                                                  | ASK demodulation |  |  |  |  |

| Pin MODSEL has no effect in SPI mode (SPISEL = 1). We recommend connecting it to ground to avoid a |                  |  |  |  |  |

Pin MODSEL has no effect in SPI mode (SPISEL = 1). We recommend connecting it to ground to avoid a floating CMOS gate.

## 1.6. Programming Modes

| SPISEL | Description                           |  |  |

|--------|---------------------------------------|--|--|

| 0      | ABC mode (8 channels preconfigured)   |  |  |

| 1      | SPI mode (programming via 3-wire bus) |  |  |

# 1.7. Preconfigured Frequencies in ABC Mode

| А | В | С | Receive Frequency |

|---|---|---|-------------------|

| 0 | 0 | 0 | FSK1: 369.5 MHz   |

| 0 | 1 | 0 | FSK5: 388.3 MHz   |

| 1 | 0 | 0 | FSK2: 371.1 MHz   |

| 1 | 1 | 0 | FSK4: 376.9 MHz   |

| 0 | 0 | 1 | FSK3: 375.3 MHz   |

| 0 | 1 | 1 | FSK7: 394.3 MHz   |

| 1 | 0 | 1 | FSK6: 391.5 MHz   |

| 1 | 1 | 1 | FSK8: 395.9 MHz   |

#### MLX71122 300 to 930MHz FSK/FM/ASK Receiver Datasheet

As all pins, pins A, B, and C are equipped with ESD protection diodes that are tied to VCC and to VEE. Therefore these pins should not be directly connected to positive supply (a logic "1") before the supply voltage is applied to the IC. Otherwise the IC will be supplied through these control lines and it may enter into an unpredictable mode. In case the user wants to apply a positive supply voltage to these pins before the supply voltage is applied to the IC, a protection resistor should be inserted in each control line.

# 2. Pin Definitions and Descriptions

# 2.1. Pin Schematics

| Pin No. | Name   | I/О Туре         | Functional Schematic                        | Description                                                                                        |

|---------|--------|------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1       | VEELNA | ground           |                                             | ground of LNA core                                                                                 |

| 31      | LNAI   | analog<br>input  |                                             | LNA input, approx.<br>27 $\Omega$ single-ended                                                     |

| 3       | LNAO   | analog<br>output |                                             | LNA open-collector output,<br>to be connected to external<br>LC tank that resonates at RF          |

| 2       | VCCANA | supply           |                                             | positive supply of<br>LNA, MIX1 MIX2, IFF, IFA,<br>FSK DEMOD, OA1, OA2,<br>PKDET+, PKDET- and BIAS |

| 4       | VEEIF  | ground           |                                             | negative supply of<br>LNA, MIX1 MIX2, IFF, IFA,<br>and FSK DEMOD                                   |

| 5       | MIXN   | analog<br>input  |                                             | mixer 1 negative input                                                                             |

| 6       | MIXP   | analog<br>input  |                                             | mixer 1 positive input                                                                             |

| 7       | SPISEL | CMOS<br>input    | SPISEL                                      | SPI select input                                                                                   |

| 8       | RSSI   | analog<br>output | RSSI<br>8<br>120<br>4<br>5<br>5<br>K<br>VEE | RSSI output, approx. 25kΩ                                                                          |

| 9       | MODSEL | CMOS<br>input    | MODSEL<br>9<br>9<br>VEE                     | demodulation select input<br>(FSK or ASK demodulation)                                             |

| Pin No. | Name   | I/О Туре      | Functional Schematic | Description                                                                                                                                            |

|---------|--------|---------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      | RBIAS  | analog I/O    | RBIAS<br>10<br>VEE   | external resistor for voltage<br>and current biasing, 30kΩ<br>by default, to provide stable<br>parameters over<br>temperature and supply<br>variations |

| 11      | VEEVCO | ground        |                      | ground of VCO                                                                                                                                          |

| 12      | TNK1   | analog I/O    |                      | VCO collector output,<br>connection 1 to external<br>LC tank                                                                                           |

| 13      | TNK2   | analog I/O    |                      | VCO collector output,<br>connection 2 to external<br>LC tank                                                                                           |

| 15      | LF     | analog I/O    |                      | charge pump output,<br>connection to external loop<br>filter                                                                                           |

| 14      | VCCVCO | supply        |                      | positive supply of VCO                                                                                                                                 |

| 16      | ENRX   | CMOS<br>input | ENRX<br>16<br>VCC    | enable/disable control input<br>(with internal pull-down)                                                                                              |

| Pin No. | Name   | I/О Туре       | Functional Schematic | Description                                                                               |

|---------|--------|----------------|----------------------|-------------------------------------------------------------------------------------------|

| 17      | C/SDEN | CMOS<br>input  | C/SDEN<br>17<br>VCC  | frequency control line C or<br>SPI control line SDEN                                      |

| 18      | B/SDTA | CMOS<br>input  | B/SDTA<br>120<br>VEE | frequency control line B or<br>SPI control line SDTA                                      |

| 19      | A/SCLK | CMOS<br>input  | A/SCLK               | frequency control line A or<br>SPI control line SCLK                                      |

| 20      | VEEDIG | ground         |                      | ground of PLL SYNT (except<br>of VCO), Control Logic,<br>and OA2 out stage                |

| 21      | VCCDIG | supply         |                      | positive supply of<br>PLL SYNT (except of VCO),<br>Control Logic, RO and OA2<br>out stage |

| 22      | DTAO   | CMOS<br>output |                      | data output, 2mA sink or<br>source capability                                             |

| Pin No. | Name | I/О Туре                                    | Functional Schematic                                            | Description                                                                                                                              |

|---------|------|---------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | MFO  | analog<br>output<br>(option 1)              | VCC VCC VCC VCC MFO<br>disable<br>23 def disable<br>vee vee ref | multifunctional output:<br>reference oscillator output<br>selected (default setting)<br>(see 4.1.4)                                      |

| 23      | MFO  | analog<br>output<br>(option 2)              | MFO<br>23<br>VEE VEE VEE VEE                                    | multifunctional output:<br>IF2 signal output selected<br>(see 4.1.4)                                                                     |

| 23      | MFO  | digital<br>output<br>tristate<br>(option 3) |                                                                 | multifunctional output:<br>digital output signal<br>selected<br>(see 4.1.4)                                                              |

| 24      | ROI  | analog<br>input                             | ROI<br>24<br>VCC<br>30p<br>30p<br>VEE                           | reference oscillator input<br>for connecting an external<br>crystal, Colpitts type<br>oscillator with internal<br>feedback<br>capacitors |

| Pin No. | Name   | I/О Туре         | Functional Schematic | Description                                                              |

|---------|--------|------------------|----------------------|--------------------------------------------------------------------------|

| 25      | PDP    | analog I/O       |                      | peak detector positive<br>output for connecting an<br>external capacitor |

| 26      | PDN    | analog I/O       |                      | peak detector positive<br>output for connecting an<br>external capacitor |

| 27      | DFO    | analog<br>output |                      | data filter output                                                       |

| 28      | DF1    | analog I/O       |                      | data filter connection 1 for<br>connecting an external<br>capacitor      |

| 29      | DF2    | analog I/O       |                      | data filter connection 2 for<br>connecting an external<br>capacitor      |

| 30      | VEEANA | ground           |                      | ground of RO, OA1, OA2,<br>PKD+, PKD- and BIAS                           |

| 32      | SLC    | analog I/O       |                      | slicer reference input for<br>connecting an external<br>capacitor        |

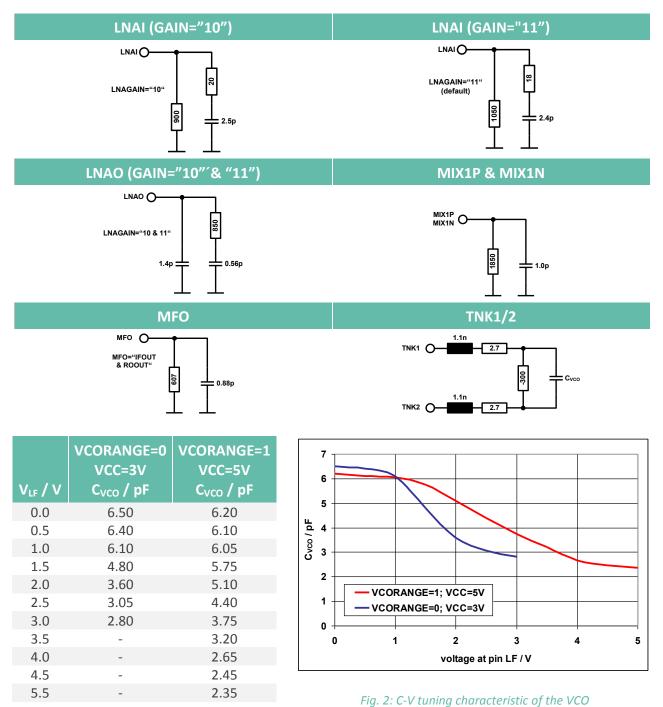

# 2.2. RF Pin Impedance Models

The following table gives the typical equivalent circuits modelling the impedance of the RF-pins including the package but without the PCB parasitics.

The LNA, MIX1 and TNK1/2 models are valid from 300 to 930MHz, the MFO model is valid from 1 to 10MHz.

. . . . . . . . . . . . . . . .

The C-V-characteristics for other supply voltages than given above can be derived by shifting the right end of the curves to the desired supply voltage, since the VCO frequency depends on  $V_{CC}-V_{LF}$ .

# **3. Functional Description**

# 3.1. Frequency Planning

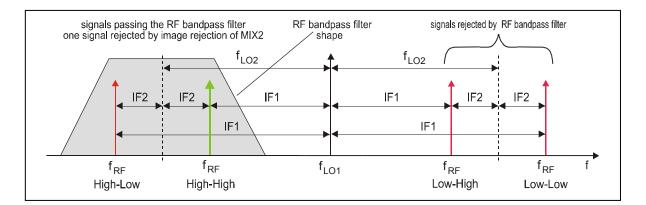

Because of the double conversion architecture that employs two mixers and two IF signals, there are four different combinations for injecting the LO1 and LO2 signals:

| LO1 high side and LO2 high side: | receiving at $f_{RF High-High}$       |

|----------------------------------|---------------------------------------|

| LO1 high side and LO2 low side:  | receiving at $f_{\text{RF High-Low}}$ |

| LO1 low side and LO2 high side:  | receiving at $f_{\text{RF Low-High}}$ |

| LO1 low side and LO2 low side:   | receiving at $f_{\text{RF Low-Low}}$  |

As a result, four different input frequencies could produce the same second IF (IF2). This may seem like a problem, but being able to select high or low side injection makes it possible to avoid interference from undesired signals. This can not be done with the more common receivers which are single conversion with a low IF frequency. It is also often possible with the MLX71122 to use a simple RF filter to get better image rejection than low IF receivers which have an image reject mixer.

Referring to the block diagram in fig.1, the following equations apply:

f

$$f_{IF2} = 2.0MHz, \quad N_{LO2} = \text{LO2DIV} = 4 \text{ or } 8 \qquad f_{IN} = \text{desired RF signal frequency}$$

$$\text{LO1 on high side: } f_{VCO} - f_{IN} = f_{IF1} \qquad \text{LO2 on high side: } \frac{f_{VCO}}{N_{LO2}} - f_{IF1} = 2.0MHz$$

$$\text{LO1 on low side: } f_{IN} - f_{VCO} = f_{IF1} \qquad \text{LO2 on low side: } f_{IF1} - \frac{f_{VCO}}{N_{LO2}} = 2.0MHz$$

$$\text{From these seven equations, we get:}$$

From these seven equations, we get:

LO1 high side and LO2 high side:

$$f_{VCO} = (f_{IN} - 2MHz) \frac{N_{LO2}}{N_{LO2} - 1}$$

(1)

LO1 low side and LO2 high side:

LO1 low side and LO2 low side:

$$V_{VCO} = (f_{IN} + 2MHz) \frac{N_{LO2}}{N_{LO2} - 1}$$

(2)

$$f_{VCO} = (f_{IN} + 2MHz) \frac{N_{LO2}}{N_{LO2} + 1}$$

(3)

$$f_{VCO} = (f_{IN} - 2MHz) \frac{N_{LO2}}{N_{LO2} + 1}$$

(4)

Fig. 3 on the next page shows the 4 possible RF frequencies when receiving at  $f_{RF High-High}$  is desired.

Example:

Let  $f_{IN} = 315MHz$  and  $N_{LO2} = 4$ . From (1) we get  $f_{VCO} = (315MHz - 2MHz)\frac{4}{4-1} = 417.33MHz$ and further  $f_{IF1} = 102.33MHz$ ,  $f_{LO2} = 104.33MHz$  and the 2<sup>nd</sup> IF frequency is 2.0MHz.

#### MLX71122 300 to 930MHz FSK/FM/ASK Receiver Datasheet

The image frequencies of the two mixers are now:

$f_{MIX1IMAGE} = 417.33 + 102.33 = 519.66MHz$ , RF response, suppressed by the RF bandpass filter,  $f_{MIX2IMAGE} = 104.33 + 2.0 = 106.33MHz$ , suppressed by the image rejection of mixer 2.

$f_{MIX2IMAGE}$  leads to two further RF response frequencies:

| 417.33 – 106.33 = 311.00 <i>MHz</i> : | suppressed by 30dB of the image rejection of mixer 2      |

|---------------------------------------|-----------------------------------------------------------|

| 417.33 + 106.33 = 523.66MHz:          | suppressed by 30dB of mixer 2 plus the RF bandpass filter |

In the example of Fig. 3, the image signals at 519.66 and 523.66 are suppressed by the bandpass characteristic provided by the RF front-end. The bandpass shape can be achieved either with a SAW filter (featuring just a couple of MHz bandwidth), or by the tank circuits at the LNA input and output (this typically yields 30 to 60MHz bandwidth). In any case, the high value of the first IF (IF1) helps to suppress the image signals at  $f_{RF Low-High}$  and  $f_{RF Low-Low}$ .

The two remaining signals at IF1 resulting from 102.33 and 106.33 enter the second mixer MIX2. This mixer features image rejection with so-called single-sideband (SSB) selection. This means either the upper or lower sideband of IF1 can be selected. In the example of Fig. 3, LO2 high-side injection has been chosen to select the IF2 signal resulting from  $f_{RF High-High}$ .

Fig. 3: The four receiving frequencies in a double conversion superhet receiver

It should be mentioned that each high-side injection mixing mirrors the frequency spectrum of the input signal. Only Low-Low and High-High injection mixing preserve the spectrum or in other words a higher frequency at RF remains a higher frequency at IF2. The polarity of the data slicer can be switched in order to compensate this for FSK reception of digital data.

It can be seen from the block diagram of Fig. 1 that there is a fixed relationship between the LO1 signal frequency  $f_{LO1}$  and the LO2 signal frequency  $f_{LO2}$ .

$$LO2DIV = N_{LO2} = \frac{f_{LO1}}{f_{LO2}}$$

(5)

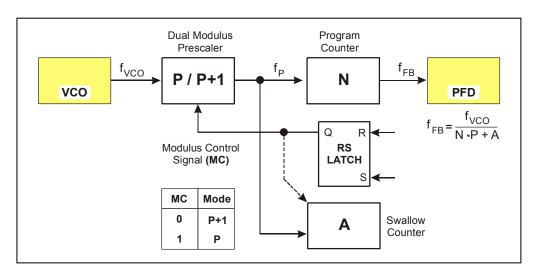

The LO1 signal frequency  $f_{LO1}$  is directly synthesized from the crystal reference oscillator frequency  $f_{RO}$  by means of an integer-N PLL synthesizer. The PLL consists of a dual-modulus prescaler (P/P+1) with P=32, a program counter N and a swallow counter A.

#### MLX71122 300 to 930MHz FSK/FM/ASK Receiver

Datasheet

$$f_{LO1} = \frac{f_{RO}}{R} (N \cdot P + A) = f_{PFD} (N \cdot P + A) = f_{PFD} \cdot N_{tot}$$

(6)

Since  $LO2 = \frac{LO1}{4 \text{ or } 8}$ , the channel frequency step,  $f_{CH}$ , is **not** equal to the phase-frequency detector (PFD)

frequency  $f_{PFD}$ .

For LO2 high-side injection, the channel step size  $f_{CH}$  is given by

$$f_{CH} = \frac{f_{RO}}{R} \frac{N_{LO2} - 1}{N_{LO2}} = f_{PFD} \frac{N_{LO2} - 1}{N_{LO2}} , \qquad (7)$$

while the following equation is valid for LO2 low-side injection:

$$f_{CH} = \frac{f_{RO}}{R} \frac{N_{LO2} + 1}{N_{LO2}} = f_{PFD} \frac{N_{LO2} + 1}{N_{LO2}}$$

(8)

#### 3.1.1. Calculation of Counter Settings

Frequency planning and the selection of the MLX71122's PLL counter settings are straightforward and can be laid out on the following procedure.

For this type of counter, it is necessary that A < N.

For discrete frequency tuning without equal channel steps:

Find a combination of R, A and N to obtain  $f_{VCO}$  from equations (1), (2), (3) or (4). A large value for R is not always necessary to get high resolution tuning. A combination of  $N_{TOT}$  and R can almost always be found which will give sufficient frequency accuracy even with a high PLL reference frequency. For example, 433.92MHz can be tuned with a 10MHz crystal with R = 17 and  $N_{TOT} = 979$  with an 8.3kHz error.

For equal channel steps without gaps:

It is necessary that

$$N \ge P$$

, it follows  $(NP + A) \ge P^2$ , so  $N \ge 32$  and  $NP + A = N_{tot} \ge 1024$ . (9)

## 3.1.2. Calculation of LO1 and IF1 frequency for Low Frequency Bands

High-high or high-low injection can be used for the low frequency bands. If equal channel steps are desired, choose a PFD frequency  $f_{PFD}$  according to the table below. The R counter values are valid for a 10MHz crystal reference frequency  $f_{RO}$ . The PFD frequency is given by  $f_{PFD} = f_{RO} / R$ .

| Injection Type | f <sub>cн</sub> [kHz] | f <sub>PFD</sub> [kHz] | R   |

|----------------|-----------------------|------------------------|-----|

| h-h            | 10                    | 13.3                   | 750 |

| h-h            | 12.5                  | 16.7                   | 600 |

| h-h            | 20                    | 26.7                   | 375 |

| h-h            | 25                    | 33.3                   | 300 |

| h-h            | 50                    | 66.7                   | 150 |

| h-h            | 100                   | 133.3                  | 75  |

| h-h            | 250                   | 333.3                  | 30  |

The second step is to calculate the missing parameters  $f_{LO1}$ ,  $f_{IF1}$ ,  $N_{tot}$ , N and A. While the second IF ( $f_{IF2}$ ), the N<sub>LO2</sub> divider ratio and the prescaler divider ratio P are bound to  $f_{IF2} = 2MHz$ , N<sub>LO2</sub> = 4 (or 8) and P = 32.

$$f_{LO1} = \frac{N_{LO2}}{N_{LO2} - 1} (f_{RF} - f_{IF2}) f_{LO1} = \frac{4}{3} (f_{RF} - 2MHz)$$

(10)

$$f_{IF1} = \frac{f_{RF} - N_{LO2} f_{IF2}}{N_{LO2} - 1} \qquad f_{IF1} = \frac{f_{RF} - 8MHz}{3}$$

(11)

Finally N and A can be calculated with equation (6).

#### 3.1.3. Calculation of LO1 and IF1 frequency for High Frequency Bands

Typical ISM band operating frequencies like 868.3 and 915MHz can be covered without changing the crystal or the VCO inductor. Low-low injection is usually used for the high frequency bands. If equal channel steps are desired, choose a PFD frequency  $f_{PFD}$  according to the table below. The R counter values are valid for a 10MHz crystal reference. The PFD frequency is given by  $f_{PFD} = f_{RO}/R$ .

| Injection Type | f <sub>cн</sub> [kHz] | f <sub>PFD</sub> [kHz] | R   |

|----------------|-----------------------|------------------------|-----|

| -              | 20                    | 16                     | 625 |

| -              | 25                    | 20                     | 500 |

| -              | 50                    | 40                     | 250 |

| -              | 100                   | 80                     | 125 |

| -              | 250                   | 200                    | 50  |

| -              | 500                   | 400                    | 25  |

The second step is to calculate the missing parameters  $f_{LO1}$ ,  $f_{IF1}$ ,  $N_{tot}$ , N and A. While the second IF ( $f_{IF2}$ ), the  $N_{LO2}$  divider ratio and the prescaler divider ratio P are bound to  $f_{IF2} = 2MHz$ ,  $N_{LO2} = 4$  (or 8) and P = 32.

$$f_{LO1} = \frac{N_{LO2}}{N_{LO2} + 1} (f_{RF} - f_{IF2}) f_{LO1} = \frac{4}{5} (f_{RF} - 2MHz)$$

(12)

REVISION 014 – AUGUST, 2016 390 10 71122 01

300 to 930MHz FSK/FM/ASK Receiver Datasheet

$$f_{IF1} = \frac{f_{RF} + N_{LO2}f_{IF2}}{N_{LO2} + 1} \qquad f_{IF1} = \frac{f_{RF} + 8MHz}{5}$$

(13)

Finally N and A can be calculated with equation (6).

### 3.1.4. Counter Setting Examples for SPI Mode

To provide some examples, the following table shows some counter settings for the reception of the wellknown ISM and SRD frequency bands. The channel spacing is assumed to be  $f_{CH} = 100$ kHz. In below table all frequency units are in MHz.

| Inj | <b>f</b> <sub>RF</sub> | f <sub>IF1</sub> | <b>f</b> LO1 | N <sub>tot</sub> | N   | Ρ  | Α  | <b>f</b> <sub>PFD</sub> | R   | <b>f</b> <sub>REF</sub> | f <sub>LO2</sub> | f <sub>IF2</sub> |

|-----|------------------------|------------------|--------------|------------------|-----|----|----|-------------------------|-----|-------------------------|------------------|------------------|

| h-h | 300                    | 97.3             | 397.3        | 2980             | 93  | 32 | 4  | 0.133                   | 75  | 10                      | 99.3             | 2                |

| h-h | 315                    | 102.3            | 417.3        | 3130             | 97  | 32 | 26 | 0.133                   | 75  | 10                      | 104.3            | 2                |

| h-h | 434                    | 142              | 576          | 4320             | 135 | 32 | 0  | 0.133                   | 75  | 10                      | 144              | 2                |

| h-h | 470                    | 154              | 624          | 4680             | 146 | 32 | 8  | 0.133                   | 75  | 10                      | 156              | 2                |

| -   | 850                    | 171.6            | 678.4        | 8480             | 256 | 32 | 0  | 0.08                    | 125 | 10                      | 169.6            | 2                |

| -   | 868                    | 175.2            | 692.8        | 8660             | 270 | 32 | 20 | 0.08                    | 125 | 10                      | 173.2            | 2                |

| -   | 915                    | 184.6            | 730.4        | 9130             | 285 | 32 | 10 | 0.08                    | 125 | 10                      | 182.6            | 2                |

| -   | 930                    | 187.6            | 742.4        | 9280             | 290 | 32 | 0  | 0.08                    | 125 | 10                      | 185.6            | 2                |

## 3.1.5. Counter Settings in ABC Mode – 8+1 Preconfigured Channels

In ABC mode (SPISEL=0), the counter settings are hard-wired. In below table all frequency units are in MHz.

| СН | Inj | f <sub>RF</sub> | f <sub>IF1</sub> | f <sub>LO1</sub> | N <sub>tot</sub> | N   | Ρ  | Α  | f <sub>PFD</sub> | R  | f <sub>REF</sub> | f <sub>LO2</sub> | f <sub>IF2</sub> |

|----|-----|-----------------|------------------|------------------|------------------|-----|----|----|------------------|----|------------------|------------------|------------------|

| 1  | h-l | 369.5           | 125.8            | 495.3            | 3715             | 116 | 32 | 3  | 0.133            | 75 | 10               | 123.8            | 2                |

| 2  | h-l | 371.1           | 126.4            | 497.5            | 3731             | 116 | 32 | 19 | 0.133            | 75 | 10               | 124.4            | 2                |

| 3  | h-l | 375.3           | 127.8            | 503.1            | 3773             | 117 | 32 | 29 | 0.133            | 75 | 10               | 125.8            | 2                |

| 4  | h-l | 376.9           | 128.3            | 505.2            | 3789             | 118 | 32 | 13 | 0.133            | 75 | 10               | 126.3            | 2                |

| 5  | h-l | 384.0           | 130.7            | 514.7            | 3860             | 120 | 32 | 20 | 0.133            | 75 | 10               | 128.7            | 2                |

| 6  | h-l | 388.3           | 132.1            | 520.4            | 3903             | 121 | 32 | 31 | 0.133            | 75 | 10               | 130.1            | 2                |

| 7  | h-l | 391.5           | 133.2            | 524.7            | 3935             | 122 | 32 | 31 | 0.133            | 75 | 10               | 131.2            | 2                |

| 8  | h-l | 394.3           | 134.1            | 528.4            | 3963             | 123 | 32 | 27 | 0.133            | 75 | 10               | 132.1            | 2                |

| 9  | h-l | 395.9           | 134.6            | 530.5            | 3979             | 124 | 32 | 11 | 0.133            | 75 | 10               | 132.6            | 2                |

# 3.2. PLL Frequency Synthesizer

The MLX71122 contains an integer-N PLL frequency synthesizer. The reference frequency  $f_R$  is derived from a stable crystal reference oscillator.

Fig. 4: Integer-N PLL Frequency Synthesizer Topology

The locked state of the PLL is defined by the following relations:

$$\frac{f_{\rm RO}}{R} = f_{\rm R} = f_{\rm PFD} = f_{\rm FB} = \frac{f_{\rm VCO}}{N_{\rm tot}} = \frac{f_{\rm VCO}}{N \cdot P + A}.$$

(14)

In this formula the total PLL feedback divider ratio is called  $N_{tot}$ . The synthesized output frequency  $f_{VCO}$  can be changed by reprogramming the reference divider or the feedback divider according to

$$f_{\rm VCO} = N_{\rm tot} \frac{f_{\rm RO}}{R} = \left(N \cdot P + A\right) \frac{f_{\rm RO}}{R}.$$

(15)

The R counter is used to set the channel spacing. Different channels can be selected by changing the total feedback divider ratio.

| List of Mathematical Acronyms      |                                                                                                                                 |  |  |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| А                                  | divider ratio of the swallow counter (part of feedback divider)                                                                 |  |  |  |  |

| $\mathbf{f}_{\mathrm{FB}}$         | frequency at the feedback divider output                                                                                        |  |  |  |  |

| floor (x)                          | The floor function gives the largest integer less than or equal to x.<br>For example, floor(5.4) gives 5, floor(-6.3) gives -7. |  |  |  |  |

| $f_{\text{PFD}}$                   | PFD frequency in locked state                                                                                                   |  |  |  |  |

| $\frac{f_{\rm RO}}{R} = f_{\rm R}$ | reference frequency of the PLL                                                                                                  |  |  |  |  |

| $f_{RO}$                           | frequency of the crystal reference oscillator                                                                                   |  |  |  |  |

| f <sub>vco</sub>                   | frequency of the VCO (equals the LO1 signal of the first mixer)                                                                 |  |  |  |  |

| $N_{tot} = N \cdot P + A$          | total divider ratio of the PLL feedback path                                                                                    |  |  |  |  |

| Ν                                  | divider ratio of the program counter (part of feedback divider)                                                                 |  |  |  |  |

| N <sub>LO2</sub>                   | LO2DIV divider ratio, to derive the LO2 signal from LO1 ( $N_1 = 4$ or 8)                                                       |  |  |  |  |

| Р                                  | divider ratio of the prescaler (part of feedback divider)                                                                       |  |  |  |  |

| R                                  | divider ratio of the reference divider R                                                                                        |  |  |  |  |

#### 3.2.1. Pulse Swallow Counter

The programmable feedback divider of the PLL is based on a pulse-swallow topology. Fig. 5 depicts its implementation, consisting of a dual-modulus prescaler, an RS latch and two programmable counters.

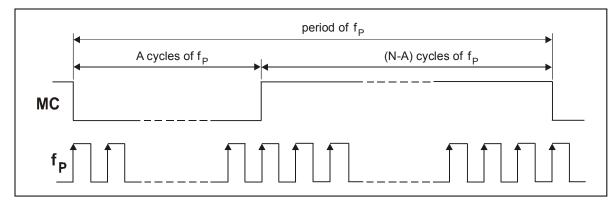

Fig. 5 Pulse Swallow Counter Topology

During one cycle of  $f_{FB}$  the prescaler begins the operation by dividing by P+1 until the swallow counter A is full. The RS latch is then set and changes the prescaler modulus to P (via the modulus control signal MC) and disables the swallow counter. The division process continues until the program counter N is full and the RS latch is reset.

Fig. 6 Pulse Swallow Divider Timing

Therefore the overall feedback divide ratio is:

$$(\mathbf{P}+\mathbf{1})\cdot\mathbf{A}+\mathbf{P}\cdot(\mathbf{N}-\mathbf{A})=\mathbf{N}\cdot\mathbf{P}+\mathbf{A}.$$

(16)

Further restrictions can be derived from above equation: A < P and A < N. Some math shows that for uniform frequency steps without gaps ( $N \ge P$ ) the following condition is necessary:

$$\mathbf{N} \cdot \mathbf{P} + \mathbf{A} \ge \mathbf{P} \cdot \mathbf{P} \,. \tag{17}$$

#### 3.2.2. PLL Counter Ranges

In order to cover the frequency range of about 300 to 930MHz the following counter values are implemented in the receiver:

| PLL Counter Ranges |                   |                   |    |  |  |  |

|--------------------|-------------------|-------------------|----|--|--|--|

| А                  | N                 | R                 | Р  |  |  |  |

| 0 to 31 (5bit)     | 3 to 2047 (11bit) | 3 to 2047 (11bit) | 32 |  |  |  |

Therefore the minimum and maximum divider ratios for uniform frequency steps are given by:

$$N_{totmax} = 32 \cdot 32 = 1024$$

$N_{totmax} = 2047 \cdot 32 + 31 = 65535$

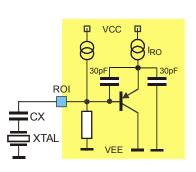

#### 3.2.3. Reference Oscillator (RO)

The reference oscillator is based on a Colpitts topology with two integrated functional capacitors as shown in figure 7. The circuitry is optimized for a load capacitance range of 10pF to 15pF. The equivalent input capacitance CRO offered by the oscillator input pin ROI is about 15pF. To ensure a fast and reliable start-up and a very stable frequency over the specified supply voltage and temperature range, the oscillator bias circuitry provides an amplitude regulation. Via SPI it is possible to adjust the typical core current with register ROCUR. There are four values available (see 4.1.7). At the default setting  $355\mu$ A, the amplitude at pin ROI is monitored in order to regulate the current of the oscillator core I<sub>RO</sub>.

Fig.7: RO schematic

## 3.2.4. Phase-Frequency Detector (PFD)

The phase-frequency detector (in conjunction with the charge pump) generates a voltage step at the loop filter pin LF. This voltage step is proportional to the phase difference between the digital input signals  $f_R$  and  $f_{FB}$ . The implementation of the phase detector is phase-frequency type. This circuitry is very useful because it decreases the acquisition time significantly even if both frequencies differ very much. The phase-frequency detector creates Up and Down signals that control the charge pump and that are also used for the lock de-tection circuit. The first rising edge of one of the input signals, after a reset of Up and Down, sets either the Up or the Down signal from LOW to HIGH. The following rising edge of the other signal resets Up and Down. If the register setting PFDPOL (see 4.1.2) is HIGH, the PFD polarity is positive. This means a rising edge of the signal  $f_R$  sets Up from LOW to HIGH and a rising edge of the signal  $f_{FB}$  sets Down from LOW to HIGH. If PFDPOL is LOW, the PFD polarity is negative and the assignment of Up and Down to the signals  $f_R$  and  $f_{FB}$  is swapped.

In the MLX71122 receiver the VCO frequency increases if the loop filter output voltage increases and vice versa. The PFD polarity needs to be positive to achieve the correct feedback in the PLL loop. If an external varactor diode is added to the VCO tank, the tuning characteristic may change from positive to negative depending on the particular varactor diode circuitry. Therefore the PFDPOL bit can be used to define the phase-frequency detector polarity.

## 3.2.5. Charge Pump (CP)

The Charge Pump is controlled by the Up and Down signals of the Phase-Frequency Detector. If the Up signal is HIGH, then the charge pump current  $I_{CP}$  is sourced from the positive supply rail to the loop filter pin LF (pin 15). If the Down signal is HIGH, then the current  $I_{CP}$  is drained from pin LF to ground. The gain of the phase detector in conjunction with the charge pump can be expressed as:

$$K_{\rm PD} = \frac{I_{\rm CP}}{2\pi} , \qquad (18)$$

whereas  $I_{CP}$  is the charge pump current which is set via register CPCUR (see 4.1.2). Default of  $I_{CP}$  is 100µA. The static Up and Down selections of  $I_{CP}$  can be used for test purposes.

## 3.2.6. Loop Filter (LF)

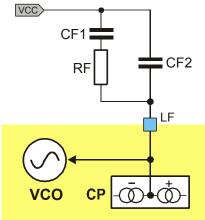

Since the loop filter has a strong impact on the function of the PLL, it must be chosen carefully. The suggested filter topology is shown in Fig. 8.

The loop filter of the PLL is set up by an external resistor and two external capacitors. It constitutes a 2nd order passive filter. This approach allows the user to easily adapt the loop filter bandwidth to different requirements. As a rule of thumb the loop filter bandwidth of an integer-N PLL should be set 10 times smaller than the PFD frequency. This is to achieve a stable PLL with a flat VCO noise floor.

The loop filter bandwidth depends on the external resistor and capacitors as well as on the VCO gain, the charge pump current and the so-called phase margin. A phase margin of 45° is commonly used for highest PLL stability. It is recommended to follow the component lists of section 6 for choosing appropriate values of the loop filter resistor and capacitors.

#### MLX71122 300 to 930MHz FSK/FM/ASK Receiver Datasheet

A good source for a detailed PLL analysis is: "Gardner, F.M., Phase-Locked Loop Techniques, John Wiley & Sons, 1980."

*Fig. 8: 2<sup>nd</sup> order Loop filter*

## 3.2.7. Lock Detector (LD)

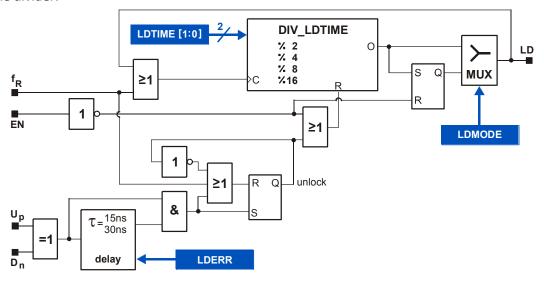

In SPI mode a lock-detect signal LD is available at pin 23 if MFO is set to 1000 (binary) in control word R3 (see 4.1.4). The pin output is HIGH when the PLL is locked in. Alternatively the lock-detect signal is visible in bit 10 of R7 (see 4.1.8) if bit SHOWLD in R1 (see 4.1.2) is HIGH. The lock detection circuitry uses the Up and Down signals from the phase-frequency detector to check them for phase coherency. Figure 9 shows an overview of the lock signal generation. The locked state and the unlock condition will be controlled by the register settings of LDTIME and LDERR. During the start-up phase of the PLL, Up and Down signals are quite unbalanced. Therefore the Lock Detector circuit waits the time span that is programmed in divider DIV\_LDTIME before a first lock can occur. The time span is dependent on the period of the reference signal f<sub>R</sub>. By default it is  $16/f_R$  (see 4.1.2). When the PLL approaches steady state, the signals Up and Down begin to overlap. The time span within which the signals are not overlapping is assessed by using a programmable delay gate. If it is shorter than programmed in LDERR (see 4.1.2) then the LD output is set to HIGH. By default the error time should be shorter than 15ns. A second option is shorter than 30ns. After LD is set to HIGH the divider is disabled and the lock state remains unchanged until the unlock signal resets the divider.

*Fig. 9: Lock Detection Circuit*

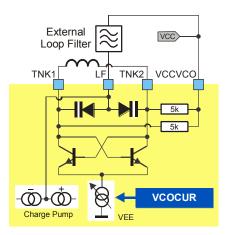

## 3.2.8. Voltage Controlled Oscillator (VCO)

The receiver includes an LC-based voltage controlled oscillator with an external inductor connected between pins TNK1 and TNK2. Two internal varactor diodes in series combination are forming the tuneable part of the oscillator tank. The oscillation frequency is adjusted by the DC voltage at pin LF. The tuning sensitivity of the VCO is approximately 83MHz/V for 433MHz operation and 105MHz/V at 868MHz, respectively. Since the cathodes of the varactors is tied to VCC, a higher voltage at pin LF or an Up-signal of the PFD forces the capacitance to decrease and the VCO frequency to increase. With positive phase detector polarity (PFDPOL = HIGH) the edges of the signal  $f_{FB}$  will catch up to the reference signal  $f_R$  (see Fig. 4).

The VCO current VCOCUR can be adjusted via the SPI in order to ensure stable oscillations over the whole frequency range. Also the bias current of the output buffer can be increased with VCOBUF to enhance its driving capability at the high frequency bands above 800MHz (see section 4.1.2). If the supply voltage is lower than 5V it is possible to adjust the tuning range of the VCO with VCORANGE (see 4.1.2). The minimum supply voltage is 3V.

Fig.10: VCO schematic

## 3.2.9. Loop Filter Calculation

The values of the loop filter elements depend on several parameters which are the:

- peak charge pump current, I<sub>CP</sub>

- VCO gain, K<sub>VCO</sub>

- desired phase margin of the open PLL loop transfer function,  $\Phi_M$

- desired closed PLL loop bandwidth, *f*<sub>C</sub>

- the feedback divider ratio, N

The peak charge pump current of the MLX71122 can be set to  $100\mu$ A or  $400\mu$ A (see 4.1.2).

The VCO gain depends on the external tank inductor LO and the VCORANGE setting (see 4.1.2). The following table gives typical VCO gain values of the evaluation boards together with the frequency band.

#### MLX71122 300 to 930MHz FSK/FM/ASK Receiver Datasheet

| Typical VCO Gain |                  |                                      |                                      |  |  |

|------------------|------------------|--------------------------------------|--------------------------------------|--|--|

| Band / MHz       | L0 inductor / nH | K <sub>vco</sub> / MHz/V, VCCRANGE=0 | K <sub>vco</sub> / MHz/V, VCCRANGE=1 |  |  |

| 315              | 33               | 128                                  | 60                                   |  |  |

| 434              | 22               | 188                                  | 85                                   |  |  |

| 868              | 5.6              | 222                                  | 108                                  |  |  |

| 915              | 5.6              | 250                                  | 116                                  |  |  |

The phase margin  $\Phi_M$  determines the stability of the PLL. It should be larger than 45°. A phase margin of 56.4° should be preferred.

The closed loop PLL bandwidth  $f_c$  of a receiver should be as large as possible in order to allow fast settling of the frequency. On the other hand it should be so low that the reference spurs at the PFD frequency are sufficiently suppressed. A good compromise is to make  $f_c$  1/10 of the PFD frequency. Therefore it is desirable to make  $f_{PFD}$  as large as possible or the R divider as small as possible but not smaller than 20. The feedback ratio between the VCO output frequency and the PFD frequency shall be called N.

The following empirically derived formulas are rules of thumb for a phase margin of 56.4° and for receivers.

$\omega_{\text{U}}$  shall be the unity gain bandwidth in rad/s of the open loop PLL transfer function.

$$\omega_U = \frac{2\pi f_C}{1.62} \tag{19}$$

$$a_0 = 3.3 \cdot \frac{I_{CP} \cdot K_{VCO}}{N \cdot \omega_U^2} \tag{20}$$

$$C_{F2} = \frac{a_0}{11}$$

(21)

$$C_{F1} = \frac{a_0 \cdot 10}{11}$$

(22)

$$R_F = \frac{3.63}{a_0 \cdot \omega_U} \tag{23}$$

The loop filter elements for 868 and 915MHz in the evaluation board list in section 6.3 are scaled values of the calculated values in order to reduce the capacitance value. If the capacitors are scaled down then the resistor needs to be scaled up by the same factor and vice versa.

## 3.3. Receiver Front End

The radio frequency (RF) front-end of the receiver is a double-superheterodyne configuration that converts the input RF signal via a first intermediate frequency (IF1) signal to a second intermediate frequency (IF2) signal. While the range of IF1 can vary between 100 and 200MHz, IF2 is fixed to 2MHz. Both signals are completely processed internally. According to the block diagram (see Fig. 1), the front-end consists of an LNA, a first mixer (MIX1), a second mixer (MIX2), an internal IF filter (IFF) and an IF limiting amplifier (IFA) with received signal strength indicator (RSSI). The local oscillator signal for mixer 1 (LO1) is directly generated in the PLL frequency synthesizer. The LO2 signal for mixer 2 is derived from the LO1 signal via a divider (see 4.1.4).

There is no inherent suppression of the first mixer's image frequency. It depends on the particular application and the system's environmental conditions whether an RF front-end filter should be added or not. If image rejection and/or good blocking immunity are relevant system parameters, a band-pass filter must be placed either in front or after the LNA. This filter can be a SAW (surface acoustic wave) or LC-based filter (e.g. helical type). Because mixer 2 is an image rejection mixer, the image frequencies of the second mixing process are suppressed (see Fig. 2). The advantage of a two stage mixing receiver is the higher gain that can be achieved in the front end.

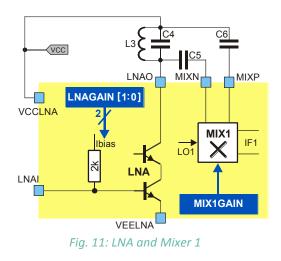

## 3.3.1. Low Noise Amplifier (LNA) and Mixer 1 (MIX1)

The LNA is based on a cascode topology for low-noise, high gain and good reverse isolation. The open collector output has to be connected to an external resonance circuit tuned to the receive frequency. The gain of the LNA can be changed to achieve a high dynamic range. There are four gain settings selectable by the control bits LNAGAIN (see 4.1.1). Default setting is the highest gain. The gain settings are automatically set if the automatic gain control (AGC) feature is activated (see 4.1.4).

The first mixer is a double-balanced mixer which converts the receive frequency to IF1. The default LO injection type for RF frequencies below 600MHz should be high side ( $f_{LO1} = f_{RX} + f_{IF1}$ ). Low side injection ( $f_{LO1} = f_{RX} - f_{IF1}$ ) is recommended for the higher frequency bands. Since the data polarity of an FSK modulated signal will be inverted by changing the injection side it is possible to change the data polarity at the data output (DTAO) via bit DTAPOL (see 4.1.1). Two gain settings of mixer 1 can be selected through MIX1GAIN (see 4.1.1): 14dB as a default value or 0dB optionally.

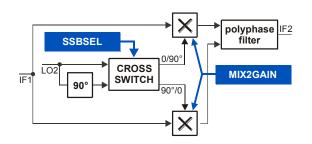

## 3.3.2. Mixer 2 (MIX2)

The second mixer is a double-balanced image rejection mixer in Hartley architecture using a complex polyphase filter that converts the IF1 to the IF2 signal. The default LO injection type is low side ( $f_{LO2} = f_{IF1} - f_{IF2}$ ), but also high side injection is possible ( $f_{LO2} = f_{IF1} + f_{IF2}$ ), by setting SSBSEL to LOW (see 4.1.1). As for mixer 1, the injection side determines the polarity of the output signal. Two gain settings of mixer 2 can be selected by MIX2GAIN (see 4.1.1), a setting at 9dB (default) and one at -2dB.

Fig. 12: Mixer 2 (Image Rejection Mixer)

#### 3.3.3. IF Filter (IFF)

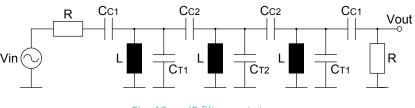

The MLX71122 comprises an internal IF filter with a -3dB bandwidth of 220kHz and a -40dB attenuation bandwidth of 1.6MHz. The filter contains three capacitively coupled bi-quad stages that represent resonant tanks close to the filter center frequency of 2MHz. The filter prototype is given in Fig.13. There exists an approximation formula to calculate the elements Ccx and Ctx when the center frequency, the -3dB bandwidth, the impedance level R and the inductivity L are given. The Ccx to Ctx ratio scales with the Q-factor of the bandpass filter. As a consequence of this the shape of the filter doesn't change in the Bodeplot if L is increased or decreased. This means the filter should always have about the same bandwidth if it is tuned to a certain center frequency.

Fig. 13: IF filter prototype

Each LC-tank is realized as a bi-quad stage using transconductance cells that can be tuned by changing the bias current. This allows tuning of the center frequency. The bandwidth is related to the center frequency by the ratio of the coupling and the tank capacitors. Accuracy of the bandwidth relies on matching of the capacitors. The internal control word in IFFVAL (see 4.1.8) determines the current consumption of the filter and therefore of the whole receiver. Higher values lead to higher current consumptions. The deviation from the nominal current consumption can be about  $\pm 0.75$ mA. Four gain settings of the IF filter are selectable via IFFGAIN in register R0 (see 4.1.1). The default value is 0dB, other options are -14dB, -6dB and +6dB. It is recommended to leave the value at 0dB.

#### 3.3.4. FSK Demodulator

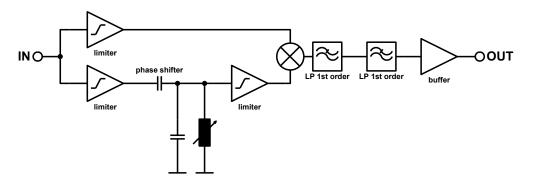

FSK reception is turned on if bit MODSEL in register R5 is set to LOW (default). The demodulator is completely internally implemented, so no external, expensive discriminator device is needed. The used FSK demodulator is based on a phase shifter and a mixer as depicted in Fig.14.

*Fig. 14:* Block diagram of FSK demodulator

The phase shifter provides a phase shift of 90 degrees to the original IF signal at exactly 2MHz. There is no AFC feature integrated since the frequency acceptance range of the demodulator is wide enough with about  $\pm 150$ kHz. The phase shift is regulated by the same control loop that controls the center frequency of the IF-filter. Tuning of the IF-filter will also change the DC value of the demodulator output. We recommend turning off the tuning during receive mode using IFFHLT (see 4.1.7) if small frequency deviations below  $\pm 20$ kHz have to be detected. The gain of the demodulator can be changed with bit DEMGAIN (see 4.1.1). It can be set to 12mV/kHz (default) or to 14.5mV/kHz.

#### 3.3.5. Autotuning Circuit

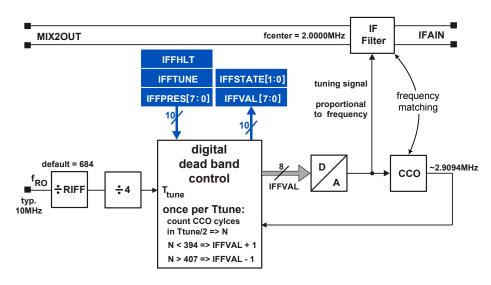

An auto-tuning mechanism is implemented that permanently adjusts the bias current of the transconductance cells of the IF filter and the FSK demodulator in order to eliminate process, temperature and supply voltage variations. For this purpose a matched master bi-quad is used as oscillator in a current controlled oscillator (CCO) at 3MHz embedded in a PLL structure. A more detailed view on the tuning circuit is shown in Fig.15.

*Fig.15: block diagram of digital tuning circuitry*

#### 300 to 930MHz FSK/FM/ASK Receiver Datasheet

The inputs are the RO frequency, output of the 2<sup>nd</sup> mixer, two register words (IFFPRES and RIFF, see 4.1.6 and 4.1.7) and 2 register bits (IFFHLT and IFFTUNE, see 4.1.7). The tuning circuit is working when IFFTUNE is HIGH and IFFHLT is LOW. If IFFHLT is HIGH then the digital tuning value IFFVAL remains at the last value. At falling transitions of IFFTUNE the preset value IFFPRES is loaded into the internal IFFVAL register and the tuning stops as well. IFFVAL and IFFSTATE (see 4.1.8) can be read out from register 7 if the MFO pin is programmed as SPI output (see 4.1.4). IFFSTATE shows the last action of the tuning circuit. It can show if the last value was increased, decreased or kept. A fourth state is indicating that the CCO is not running because of IFFHLT/IFFTUNE or a defect. It is possible to route the CCO output signal to the MFO pin for test purposes and to determining the ratio of the CCO and the filter.

The working principle of the digital tuning circuit is as follows. First the crystal frequency is divided by RIFF and then by 4. This is the tuning period with which the IFFVAL values can be changed. Now the digital control counts the positive edges of the CCO output in half of the tuning period. The typical count value for perfect tuning should be 400. Since the CCO shows phase noise it is necessary to define a certain dead band in which no tuning takes place. The limits are hardwired in the control logic and can not be changed. The lower dead band limit is 394 and the upper limit is 407. If the counts of CCO are smaller or larger than these values then the circuit increases or decreases IFFVAL by one. There is no change of IFFVAL if the count is inside the dead band.

Unfortunately glitches produced in the digital tuning circuit cause IFFVAL to be decreased even in the dead band. The glitches appear randomly but about 10 to 20 within one second. This causes the filter to be pushed towards the lower dead band limit. Once it is reached, IFFVAL will be decreased by 1 for one tuning period and be immediately increased in the next tuning period since the CCO count is smaller than 394. If the FSK frequency deviation is smaller than 15kHz and the peak detectors are used, then we recommend to disable the tuning with IFFHLT=1 during the reception period.

For typical process parameters, at room temperature and for 5V supply voltage the following assumptions can be made. One LSB of IFFVAL will shift the filter frequency by about 10.2kHz. The demodulator gain at low gain setting is about 12mV/kHz (leading to 120mV pulses due to the glitches!), one LSB of RIFF will shift the filter frequency by about 3kHz (reciprocal to RIFF!), one LSB of the CCO count shifts the frequency error of the filter by about 5kHz. The temperature drift of the filter is about 0.47 IFFVAL steps per Kelvin so the drift of the filter is about 4.8kHz per Kelvin.

## 3.3.6. IF Amplifier (IFA)

After passing the IF filter the receiving signal is amplitude limited by means of a high gain limiting amplifier. Its small signal gain is about 68dB. A received signal strength indicator (RSSI) voltage is generated in the IF amplifier. It is available at pin RSSI. The voltage at this pin is proportional to the input level of the receiver (in dB scales). There are two sensitivity settings selectable with RSSIGAIN (see 4.1.2), one with about 39mV/dB and the default setting with about 51mV/dB. By using this RSSI output signal the incoming signal strength of different transmitters can be determined. The same RSSI signal is used for receiving ASK modulated signals if MODSEL (see 4.1.6) is HIGH.

The IFA generates two digital signals RSSIL and RSSIH that indicate the level range of the RSSI voltage. If the level is in the lower quarter of the RSSI voltage range then both signals are LOW. If it is in the upper quarter of the RSSI range then both signals are HIGH. In between, the RSSIL signal is HIGH and RSSIH is LOW. Both values can be read out from register R7 of the IC (see 4.1.8). These two signals are also used for the AGC feature.

## 3.3.7. Automatic Gain Control (AGC)

The Automatic Gain Control (AGC) can be activated in SPI mode with AGCEN (see 4.1.4). By default, it is turned off. It uses the RSSIH and RSSIL signals of the IF amplifier to determine whether the gain has to be increased or decreased. The gain will be decreased beginning with the gain of the last stage. The gain increase works vice versa. The AGC circuit controls the gain of the LNA, and of mixer 1 and mixer 2. To avoid rapid gain switching, caused by short signal strength fluctuations or during ASK reception, the gain control operates with a time delay that can be programmed via AGCDEL (see 4.1.4). The time delay also depends on the PFD frequency of the IF filter auto-tuning circuit. There is no delay by default. AGCMODE (see 4.1.5), a second setting, determines whether the delay is applied for gain increase and decrease or only for gain increase. By default, a delay for increase and decrease is used.

# 3.4. Data Path

The data path contains all circuitry that is used to process the baseband signal. The MLX71122 comprises a second order Sallen-Key lowpass filter, two peak detectors and an output comparator as digital signal output.

## 3.4.1. Data Filter (DF)

The receive part of the MLX71122 contains a 2<sup>nd</sup> order Sallen-Key low-pass filter that can be configured by connecting two external capacitors C8 and C9 to the IC (see sec. 6). This data filter removes high frequency components and noise from the demodulated signal that may otherwise lower the signal to noise ratio at the comparator input. The filter bandwidth has to be adjusted to the maximum data rate. A good choice for the -3dB bandwidth is 85% of the data rate for NRZ codes and 170% for bi-phase or Manchester codes. A characteristic between Bessel and Butterworth is best used in the data filter.

Since the internal resistors of the filter are both  $200k\Omega$  and the overall gain is set to unity we obtain the following table for the capacitor values:

| Coding        | С8        | С9                                                    |

|---------------|-----------|-------------------------------------------------------|

| NRZ Code      | 1.47 · C9 | 640 p F<br>data rate / kbps                           |

| Bi-Phase Code | 1.47 · C9 | $\frac{320\mathrm{pF}}{\mathrm{data\ rate\ /\ kbps}}$ |

C9 should be rounded (down preferred) to the closest E-series value. C8 should be calculated from the rounded value before rounding it (down preferred) to the closest E-series value.

Example: base band signal 4kbps, NRZ coding

| $C9 = \frac{640 \text{pF}}{4[\text{kbps}]} = 160 \text{pF}$ | in E-series $\Rightarrow$ | C9 = 150 pF | (24) |

|-------------------------------------------------------------|---------------------------|-------------|------|

| $C8 = 1.47 \cdot 150 pF = 220.5 pF$                         | in E-series $\Rightarrow$ | C8 = 220 pF | (25) |

### 3.4.2. Averaging Data Slicer Mode

The averaging data slicer mode is the default setting for the data path of the MLX71122. Bit SLCSEL in register R0 (see 4.1.1) is LOW if it is active and switch SW2 connects the pin SLC with DFO via a  $200k\Omega$  resistor (see Fig. 1). With an external capacitor C10 at pin SLC, a simple low pass filter is formed that generates the threshold voltage for the output comparator. The value of C10 depends on the length of the packet preamble, the coding and the data rate. The larger the C10 value the longer the time until valid output data can be received at pin DTAO.

Averaging data slicer mode can be used for bi-phase or Manchester encoded bit streams since the DC-content of these codes is almost zero. The RC-time constant of the slicer can be calculated using:

$$t_{\rm SLC} = 200 k\Omega \cdot C10$$

(26)

We recommend that  $t_{SLC}$  is at least 25 times as long as the bit time of the equivalent NRZ signal.

Example: base band signal 4kbps, NRZ coding

$$C10 = \frac{25 \cdot 0.25 \text{ms}}{200 \text{k}\Omega} = 31.25 \text{nF} \qquad \text{in E-series} \implies C10 = 33 \text{nF}$$

### 3.4.3. Peak Detectors (PKDET)

Peak detector mode is recommended for fast acquisition of the received data and if NRZ code is used. We recommend turning off the IFF auto tuning after the PLL lock during FSK-reception in peak detector mode. The peak detectors can be activated by setting SLCSEL to HIGH in register R0 (see 4.1.1). This connects SLC (pin 32) with the resistive voltage divider between PDP (pin 25) and PDN (pin 26) (see Fig. 1). The peak detector at PDP is used to detect the maximum of the voltage at DFO and the peak detector at PDN detects the minimum of the voltage at DFO. Since the voltage divider is symmetric, the threshold voltage will be in the middle of the minimum and maximum voltages at DFO. The peak voltages are proportional to the charge that is stored on the peak detector capacitors at PDP (C11) and PDN (C12). All pull-up and pull-down currents are given in sec. 5.5. Because both pins are connected via a  $2M\Omega$  resistor, both peak detector capacitors will be discharged with a time constant depending on the value of the capacitors. For equal values of both capacitors (C = C11 = C12), the time constant will be:

$$t_{\rm DIS} = 2M\Omega \cdot 0.5 \cdot C$$

The minimum value of  $t_{DIS}$  is limited by the maximum number of equal consecutive bits. A value of  $t_{DIS}$  of at least 4 times the number of equal consecutive bits is a good choice.

Example: base band signal 4kbps, NRZ coding, max. 32 equal consecutive bits

$$C11 = C12 = \frac{32 \cdot 4 \cdot 0.25 \text{ms}}{0.5 \cdot 2 \text{M}\Omega} = 32 \text{nF} \qquad \text{in $E$-series} \implies C11 = C12 = 33 \text{nF}$$

(27)

The maximum capacitor value may also be limited by the pull-up and pull-down currents of the peak detectors given in sec. 5.5, because C11 and C12 have to be charged during the first bits of the preamble of the data packet. The capacitors C11 and C12 are discharged if the circuit is powered but not in receive mode (see 3.8). The capacitor C11 will be pre-charged with ground potential and C12 will be pre-charged with VCC potential in order to prepare the peak data slicer circuit for fast output of valid data.

#### 3.4.4. Output Comparator

The output comparator or data slicer decides whether the incoming signal is a digital LOW or HIGH by using the reference voltage at SLC (pin 32). If the internal voltage is larger than the reference then the output is HIGH and vice versa. Nevertheless, the polarity of the output comparator can be inverted. The driving capability of the comparator output is  $\pm 2$ mA and in standby mode the tri-state output is at high impedance.

Pin DTAO must not be connected by a low impedance to a fixed voltage supply or a stronger driver output! We recommend using a series resistance of  $10k\Omega$  to connect DTAO.

## 3.5. Frequency Acceptance Range

The frequency acceptance range is defined as the bandwidth where the input sensitivity can be degraded by 3dB at a maximum, compared to the sensitivity at the center frequency of the channel.

Typically, the frequency acceptance range of the MLX71122 is about 180kHz, see Fig.16.

The frequency acceptance range is mainly depending on the frequency deviation, and slightly on the modulation frequency. The larger the frequency deviation the smaller the acceptance range.

## 3.6. Biasing System

The biasing system needs an external  $30k'\Omega$  resistor that is connected between RBIAS (pin 10) and the PCB ground. The band-gap voltage at RBIAS causes a reference current flow of about  $42\mu$ A through this reference current resistor. The accuracy of the external resistor should be within ±2%. To minimize the temperature dependency it is recommended to use a metal film resistor.

# 3.7. Operating Modes

The MLX71122 has four operating modes having an impact on the receiver's current consumption. The OPMODE bits in register R0 (see 4.1.1) determine the operating mode. Selections are:

- 00 Shutdown all blocks deactivated, only SPI active (default)

- 01 Receive receiving data from LNAI at selected frequency

- 10 RO and bias only only biasing system and reference oscillator are working

- 11 Synthesizer only only biasing system, reference oscillator and PLL are working

The first operating mode consumes virtually no current. The circuit is dead except of the SPI that can listen to commands. In Receive mode all necessary blocks are turned on in order to receive data at the programmed frequency.

•

#### MLX71122 300 to 930MHz FSK/FM/ASK Receiver Datasheet

The last two operating modes can be used to accelerate the start-up time of the circuit after periods of silence. With RO and bias only, the start-up time of the reference oscillator (RO) can be circumvented. RO and biasing consume not as much current as the whole receiver. With Synthesizer only the full PLL is already working and locked. Current consuming blocks as the LNA, the IF-filter and the FSK-demodulator are turned off in this state. The last mode is useful if the receiver has to listen frequently.

## 3.8. Multi Functional Output

The Multi Functional Output (pin 23) can be used to read out the control register settings or to make other internal signals available at this pin. The output is controlled by the bits MFO in register R3 (see 4.1.4). The most important selections are:

- 0000 Z-State MFO pin is in high impedance mode

- 0001 SPI-out MFO pin is digital serial output for data of registers (default in SPI-mode)

- 0010 Logic-0 MFO pin is pulled to ground

- 0011 Logic-1 MFO pin is pulled to VCC

- 0100 RO-out MFO pin is buffered, analogue output of RO frequency (default in ABC-mode)

- 0101 IF-out MFO pin is buffered, analogue output of IF2 signal after the IF-filter

- 1000 LD-out MFO pin represents lock state of PLL

- 1011 CCO-out MFO pin represents CCO output

Z-State, Logic-0 and Logic-1 can be used to provide digital control signals to other circuits on the PCB. In state RO-out a 10MHz clock frequency is available at MFO, e.g. for driving a microcontroller. At IF-out pin MFO provides the IFF output, amplified by a factor of 5 (unloaded). In this case the output resistance is about  $610\Omega$ . The IF-out mode can be used for checking the IFF characteristics or for further signal processing, e.g. to add an external limiting amplifier and demodulator. With the LD-out setting the state of the PLL can be read out. All other selections are for test purposes. The CCO-out option can be used to check the ratio between the internal CCO and the IF filter frequency.

## 3.9. SPI Description

#### 3.9.1. General

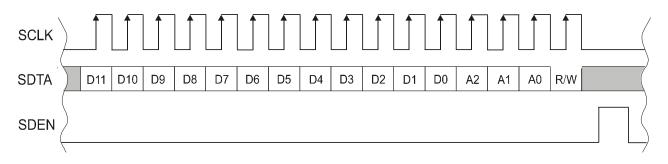

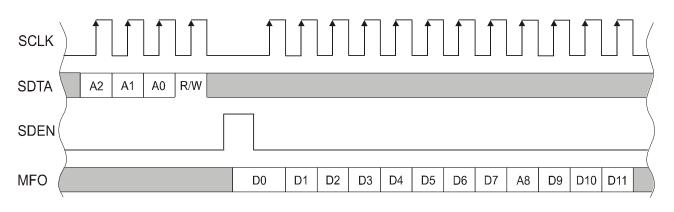

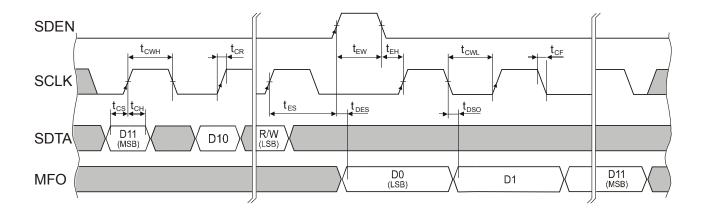

Serial programming interface (SPI) mode can be activated by choosing SPISEL = 1 (e.g. at positive supply voltage  $V_{cc}$ ). In this mode, the input pins 17, 18 and 19 are used as a 3-wire unidirectional serial bus interface (SDEN, SDTA, SCLK). The internal latches contain all user programmable variables including counter settings, mode bits etc.

In addition the MFO pin can be programmed as an output (see section 4.1.4) in order to read data from the internal latches and it can be used as an output for different test modes as well.

At each rising edge of the SCLK signal, the logic value at the SDTA terminal is written into a shift register. The programming information is taken over into internal latches with the rising edge of SDEN. Additional leading bits are ignored, only the last bits are serially clocked into the shift register. A normal write operation shifts 16 bits into the SPI, a normal read operation shifts 4 bits into the SPI and reads additional 12 bits from the MFO pin. If less than 12 data bits are shifted into SDTA during the write operation then the control register may contain invalid information.

#### MLX71122 300 to 930MHz FSK/FM/ASK Receiver Datasheet

In general a control word has the following format. Bit 0 is the Read/Write bit that determines whether it is a read (R/W = 1) or a write (R/W = 0) sequence. The R/W bit is preceding the latch address and the corresponding data bits.

|     | Control Word Format |    |    |    |    |    |    |    |    |    |     |     |       |      |       |

|-----|---------------------|----|----|----|----|----|----|----|----|----|-----|-----|-------|------|-------|