Two-Fold High Power LF Initiator With integrated Immobilizer

## **Features**

- 2 High power independent drivers (2.5Apeak in square and 1Apeak in sine mode)

- Full bridge drive capabilities

- Built-in protection features (antenna fault detection, over current and T°) for safe operation in all conditions

- Easy-to-use through SPI interface

- Built-in ASK and FSK immobilizers

# **Ordering Information**

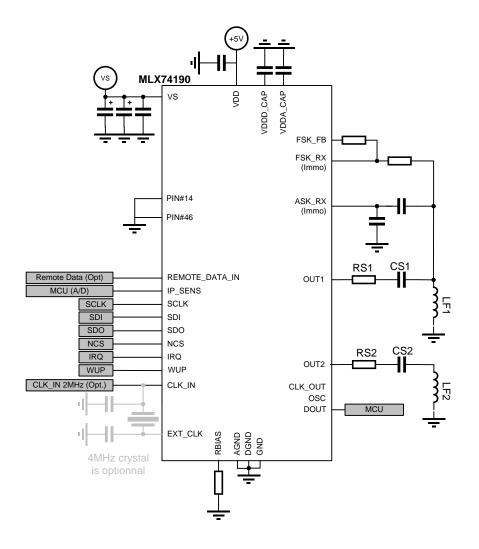

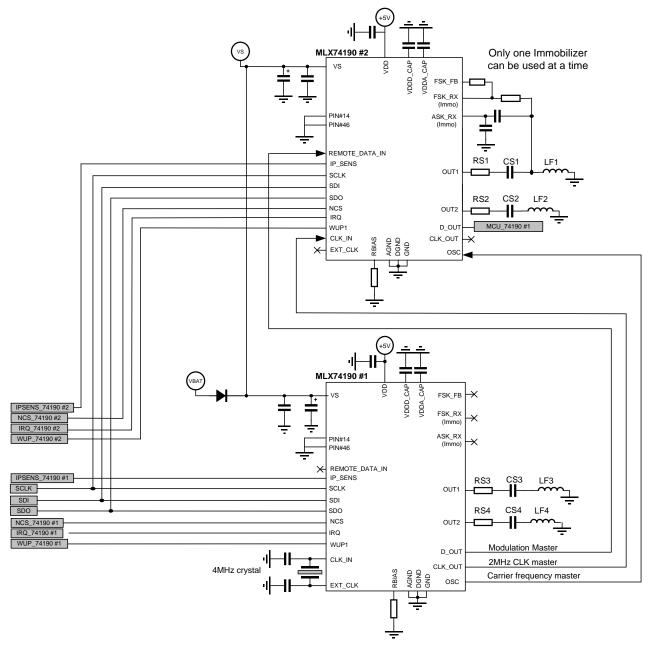

# **Application Examples**

- Passive Start system

- TPMS Initiator

- LF door opener

- Active RFID initiator

| Part Code | Temperature Code   | Package Code                     | Option<br>Code | Packing Form Code |

|-----------|--------------------|----------------------------------|----------------|-------------------|

| MLX74190  | R (-40°C to 105°C) | PF (Lead free TQFP 7x7 48 leads) | ABA-000        | RE                |

# Description

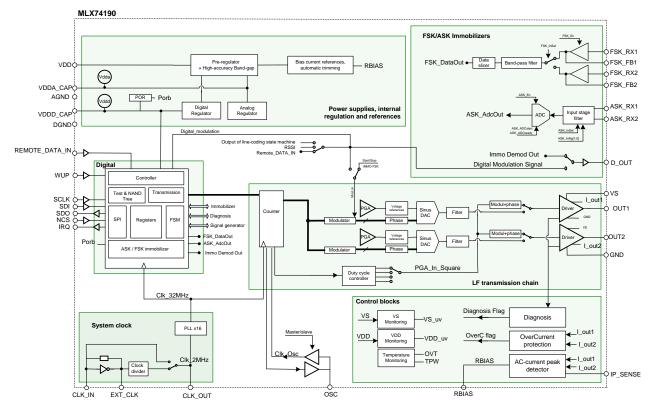

The MLX74190 low-frequency (LF) initiator IC consists in two high power LF drivers and built-in immobilizers (IMMO).

The main application for the MLX74190 is automotive remote passive start, where the IC transmits a high power LF telegram to wake-up the key inside the car. The key sends out its identification number to the car via an ultra-high frequency (UHF) signal, enabling the engine to start. The MLX74190 also features two built-in Immobilizers (for ASK and FSK communications), used when the battery of the key is depleted. In this

case, the key is placed in a specific zone close to the initiator and a full passive RFID communication is initiated. The load modulation signal returns by the key is received and demodulated by the MLX74190.

The MLX74190 can also serve for a similar purpose with other vehicles such as; motorcycles, scooters, all-terrain vehicle (ATV), jet skis, snowmobiles and motorboats, where the key holder can be detected when approaching the engine and will be able to activate it from a "Start" button, or as a 'dead man switch' so that if the driver falls off then the engine is automatically cut. In addition it may be incorporated into building access systems, tire pressure monitoring system (TPMS) initiators and pet identification system.

Both LF drivers are independently programmable to generate sine (max. 1Ap) or square (max. 2.5Ap) waves, with a frequency from 109kHz to 140kHz and an output amplitude from 0.25 to 32Vpp. The two drivers can be used in full or half bridge configuration and are protected against overload (over-current and over-temperature). A built-in diagnosis function allows detecting any wrong connection with the LF antenna (Short to GND, Short to Vbat, open load or wrong resonance frequency).

The MLX74190 is supplied by an external VS voltage from 6-40V and VDD voltage of typically 5V. The VS voltage can be generated by an external DC-DC converter or by DC voltage from vehicle supply.

The MLX74190 is controlled through a standard SPI interface (SDI, SDO, SCK and NCS) and an interrupt pin is generated on-purpose by the IC. The MLX74190 is clocked either with a 2 MHz clock frequency signal coming from the MCU or by an on-chip oscillator connected to an external 4 MHz crystal or ceramic resonator.

REVISION 004 - JUNE 20, 2017 3901074190

# Contents

| Features                                                |    |

|---------------------------------------------------------|----|

| Application Examples                                    |    |

| Ordering Information                                    | 1  |

| Description                                             | 1  |

| 1. Absolute Maximum Ratings                             | 5  |

| 2. Range of Functionality                               | 5  |

| 3. Pin out description                                  | 6  |

| 4. High Level Block Diagram                             |    |

| 5. Operating Modes                                      |    |

| 5.1. Sleep Mode                                         | 9  |

| 5.2. Standby Mode                                       | 9  |

| 5.3. Transmission Mode                                  | 9  |

| 5.4. Diagnosis Mode                                     | 9  |

| 6. Detailed Description                                 | 10 |

| 6.1. Power supplies, internal regulation and references |    |

| 6.2. System clock                                       | 11 |

| 6.3. LF transmission chain                              | 12 |

| 6.3.1. Frequency generation                             | 12 |

| 6.3.2. Sine wave generation                             | 13 |

| 6.3.3. Square wave generation                           | 14 |

| 6.3.4. Phase Generation                                 | 14 |

| 6.3.5. Selection of modulation source                   | 14 |

| 6.3.6. Modulator                                        | 15 |

| 6.3.7. Transmission of destroy bits                     | 15 |

| 6.3.8. LF Driver outputs                                | 16 |

| 6.3.9. Electrical parameters                            | 16 |

| 6.4. Immobilizer Function                               | 17 |

| 6.4.1. ASK demodulation                                 | 17 |

| 6.4.2. FSK demodulation                                 |    |

| 6.4.3. Electrical parameters                            | 20 |

| 6.5. Digital SPI Interface                              | 21 |

| Two-Fold High Power LF Initiator<br>With integrated Immobilizer |    |

|-----------------------------------------------------------------|----|

| 6.5.1. SPI signal frames                                        | 21 |

| 6.5.2. SPI Commands                                             | 23 |

| 6.5.3. Electrical characteristics and timings                   | 24 |

| 6.6. Control blocks                                             | 25 |

| 6.6.1. Failure Flags                                            | 25 |

| 6.6.2. Generating Interruption with IRQ pin                     | 25 |

| 6.6.3. Antenna diagnosis                                        | 26 |

| 6.6.4. Current Measurement                                      |    |

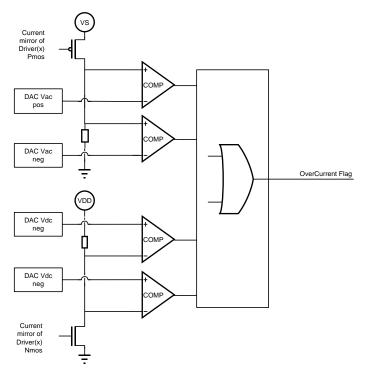

| 6.6.5. AC and DC Over current                                   |    |

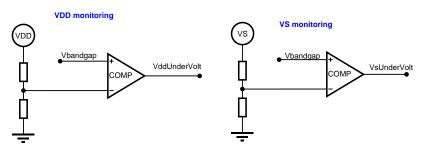

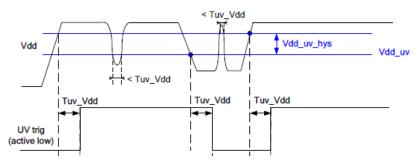

| 6.6.6. VDD and VS under voltage                                 |    |

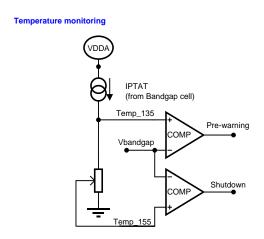

| 6.6.7. Pre-warning (PWT) and over Temperature (OVT)             |    |

| 6.6.8. Transmission aborted                                     |    |

| 6.6.9. SPI error                                                |    |

| 6.6.10. Unspecified SPI command                                 |    |

| 6.6.11. Overflow                                                |    |

| 6.7. Internal Registers                                         |    |

| 6.7.1. Summary of registers                                     |    |

| 6.7.2. Circular Buffer                                          |    |

| 6.7.3. Status Register                                          | 35 |

| 6.7.4. Configuration Register                                   |    |

| 6.7.5. Immobilizer Configuration Register                       | 41 |

| 6.7.6. Control Register                                         | 43 |

| 6.7.7. Transmission Data Format Register                        | 45 |

| 6.7.8. Transmission Data Register                               | 46 |

| 6.8. Transmission Sequence                                      | 46 |

| 7. General electrical characteristics                           |    |

| 7.1. Power On Reset                                             | 47 |

| 7.2. Frequencies specifications                                 | 47 |

| 7.3. Digital input-output specifications                        | 47 |

| 7.4. Current consumptions                                       |    |

| 7.5. Start-up time                                              |    |

| 8. Application Information                                      |    |

| 9. Package and marking information                              |    |

| MLX74190<br>Two-Fold High Power LF Initiator<br>With integrated Immobilizer |    |

|-----------------------------------------------------------------------------|----|

| 9.1. Package data TQFP eP 48L (7x7, 48 leads)                               | 51 |

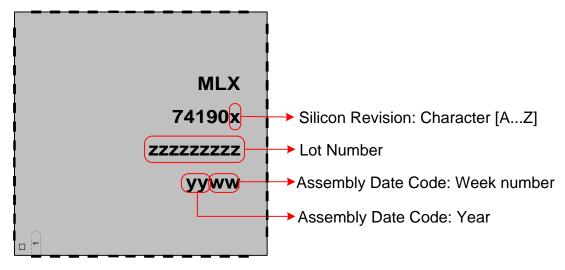

| 9.2. Marking instruction                                                    |    |

| 10. Standard information regarding manufacturability of Melexis processes   |    |

| 11. Contact                                                                 |    |

| 12. Disclaimer                                                              |    |

# **1. Absolute Maximum Ratings**

| Parameter                                          | Symbol                                        | Min    | Max | Units | Comment                             |

|----------------------------------------------------|-----------------------------------------------|--------|-----|-------|-------------------------------------|

| Driver Supply Voltage                              | VS                                            |        | 45  | V     |                                     |

| 5V Supply                                          | VDD                                           |        | 7   | V     |                                     |

| Storage Temperature Range                          | Ts                                            | -55    | 150 | °C    |                                     |

| Junction Temperature                               | Tj                                            | -40    | 165 | °C    |                                     |

| Static thermal resistance from Junction to Ambient | Rthja                                         |        | 28  | K/W   |                                     |

| ESD Sensitivity (HBM global pins)                  | $V_{ESDglobal}$                               | +/-3   |     | kV    | OUT1, OUT2, VS,<br>ASK_RXi, FSK_RXi |

| ESD Sensitivity (HBM local pins)                   | $V_{ESDlocal}$                                | +/-2   |     | kV    | All other pins                      |

| ESD Sensitivity (CDM)                              | V <sub>CDM_sens</sub><br>(HBM Global<br>pins) | +/-500 |     | V     |                                     |

Table 1: Absolute maximum ratings

Exceeding the absolute maximum ratings may cause permanent damage. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **2.** Range of Functionality

| Parameter                                                                              | Symbol         | Min Value | Typical | Max Value | Units |

|----------------------------------------------------------------------------------------|----------------|-----------|---------|-----------|-------|

| 5V Supply                                                                              | VDD            | 4.5       | 5       | 5.5       | V     |

| Driver Supply Voltage –<br>operating                                                   | VS             | 6         | -       | 40        | V     |

| Input voltage range on pins:<br>NCS, SCLK, SDI, WUP, CLK_IN<br>and REMOTE_DATA_IN, OSC | Vin_dig        | -0.5      | VDD     | 5.5       | V     |

| Operating Temperature Range                                                            | T <sub>A</sub> | -40       | -       | 105       | °C    |

Table 2: Range of functionality

#### Note:

Every electrical parameter specified in this document, except if specifically indicated, is valid in the complete temperature range: -40 to 105°C.

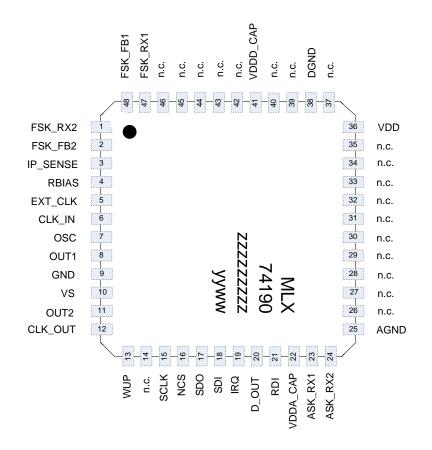

# 3. Pin out description

| Pin №                                                                     | Name     | Туре    | Function                                                                        |  |

|---------------------------------------------------------------------------|----------|---------|---------------------------------------------------------------------------------|--|

| 1                                                                         | FSK_RX2  | Analog  | FSK Immobilizer input pin 2                                                     |  |

| 2                                                                         | FSK_FB2  | Analog  | FSK Immobilizer feedback loop 2                                                 |  |

| 3                                                                         | IP_SENSE | Analog  | Current Measurement Output Voltage                                              |  |

| 4                                                                         | RBIAS    | Analog  | Reference Resistor connection for trimming the current reference                |  |

| 5                                                                         | EXT_CLK  | Digital | External clock used in combination with CLK_IN to connect an external resonator |  |

| 6                                                                         | CLK_IN   | Digital | Input clock coming from MCU or connected to external resonator                  |  |

| 7                                                                         | OSC      | Analog  | 125KHz clock input/output                                                       |  |

| 8                                                                         | OUT1     | Analog  | Antenna connection (driver output 1)                                            |  |

| 9                                                                         | GND      | Ground  | Power ground for driver outputs                                                 |  |

| 10                                                                        | VS       | Supply  | Supply for driver outputs                                                       |  |

| 11                                                                        | OUT2     | Analog  | Antenna connection (driver output 2)                                            |  |

| 12                                                                        | CLK_OUT  | Digital | 2MHz clock output                                                               |  |

| 13                                                                        | WUP      | Digital | Wake up pin                                                                     |  |

| 15                                                                        | SCLK     | Digital | Serial clock for SPI                                                            |  |

| 16                                                                        | NCS      | Digital | Not chip select for SPI                                                         |  |

| 17                                                                        | SDO      | Digital | Slave data output for SPI                                                       |  |

| 18                                                                        | SDI      | Digital | Slave data input for SPI                                                        |  |

| 19                                                                        | IRQ      | Digital | Interrupt signal output                                                         |  |

| 20                                                                        | D_OUT    | Digital | Immobilizer data / Digital modulation output signal                             |  |

| 21                                                                        | RDI      | Digital | Input signal for direct LF modulation (RDI = REMOTE_DATA_IN)                    |  |

| 22                                                                        | VDDA_CAP | Supply  | Analog internal regulator decoupling cap.                                       |  |

| 23                                                                        | ASK_RX1  | Analog  | ASK Immobilizer input 1                                                         |  |

| 24                                                                        | ASK_RX2  | Analog  | ASK Immobilizer input 2                                                         |  |

| 25                                                                        | AGND     | Ground  | Analog ground                                                                   |  |

| 36                                                                        | VDD      | Supply  | 5V supply                                                                       |  |

| 38                                                                        | DGND     | Ground  | Digital ground                                                                  |  |

| 41                                                                        | VDDD_CAP | Supply  | Digital internal regulator decoupling capacitor                                 |  |

| 47                                                                        | FSK_RX1  | Analog  | FSK Immobilizer input pin 1                                                     |  |

| 48                                                                        | FSK_FB1  | Analog  | FSK Immobilizer feedback loop 1                                                 |  |

| 14, 46                                                                    | Reserved | NA      | Must be externally connected to ground                                          |  |

| 26,27,28,29,3<br>0, 31,32, 33,<br>34, 35, 37,39,<br>40, 42, 43, 44,<br>45 | NC       | NA      | Not connected                                                                   |  |

| EXP                                                                       | EXP      | Ground  | Exposed PAD, to be connected to ground                                          |  |

Table 3: Pin out description

Figure 2: Top view of the package TQFP48

# 4. High Level Block Diagram

Figure 3: MLX74190 high level block diagram

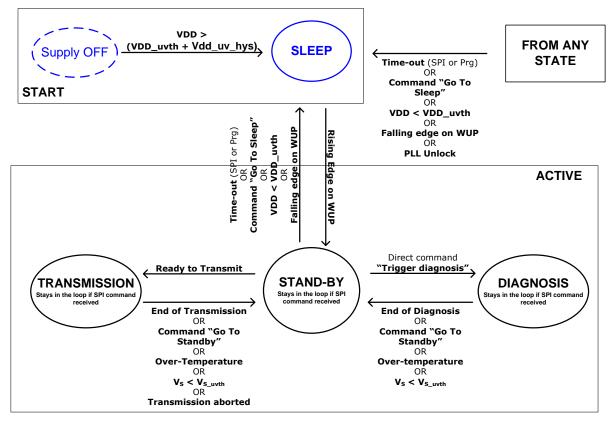

# 5. Operating Modes

Figure 4: MLX74190 operating modes transition diagram

## 5.1. Sleep Mode

In SLEEP mode, all internal registers are set to their default values, flags and pointer are reset. All antenna outputs are switched to Hi-Z mode, the PLL is switched OFF and the SPI interface is deactivated. The device exits SLEEP mode when a rising edge is applied on the pin WUP by the external host MCU.

## 5.2. Standby Mode

In STANDBY mode, all antenna outputs are switched to Hi-Z mode, all digital outputs are switched to their default values and the internal LF transmission chain is deactivated. The SPI interface is activated and the MLX74190 device is able to receive and answer SPI commands from the external host MCU.

## 5.3. Transmission Mode

In TRANSMISSION mode, the MLX74190 is busy transmitting LF sequence(s). All digital outputs are active; the LF driver outputs are configured according to the active configuration register. The SPI interface is activated and the MLX74190 device is able to receive and answer SPI commands from the external host MCU.

## 5.4. Diagnosis Mode

In DIAGNOSIS mode, the MLX74190 is busy with diagnosis procedure. All digital outputs are set in default states; the LF driver outputs are activated and ready for diagnosis process. The SPI interface is activated and the MLX74190 device is able to receive SPI command from the external host MCU.

# 6. Detailed Description

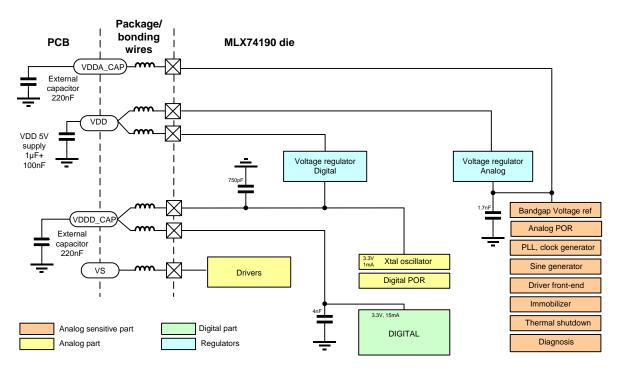

## 6.1. Power supplies, internal regulation and references

The MLX74190 is supplied with VDD voltage of typically +5V and VS voltage between 6 to 40V, used for the embedded drivers. Both voltages are internally monitored and the MLX74190 device enters the corresponding under-voltage conditions if VDD or VS is going below the VDD\_uv or Vs\_uv thresholds. For more information about the under-voltage condition, please refer to the chapter

#### VDD and VS under voltage.

A high accuracy band-gap is implemented, providing the internal reference current for the other built-in blocks of the MLX74190 device. An external high precision **1%** resistor of **5.23 kOhm** has to be connected to the pin **RBIAS**.

Two embedded regulators are included in the MLX74190. An external **220nF** decoupling capacitor will be placed on both pins **VDD\_CAP** and **VDDA\_CAP**. These two embedded regulators function as follows:

- "Analog regulator" provides a stable supply voltage to analog parts

- "Digital regulator" provides a stable supply voltage to digital parts

For VDD decoupling purposes a 1uF capacitor in parallel to a 100nF capacitor are recommended.

Figure 5: MLX74190 Power supplies, internal regulators and references

## 6.2. System clock

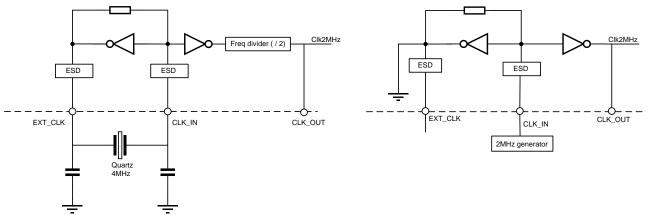

The 32MHz internal system clock frequency is generated either from an external 2MHz clock signal provided by an external device (usually coming from a microcontroller) or by using an external crystal resonator whose frequency value is 4MHz. The recognition of the input clock source is done automatically during the start-up phase. A 2MHz clock signal is available for external devices on the pin CLK\_OUT.

e 6: Dual system clock configuration, MCU (2MHz) or Crystal (4MHz)

Figur

The signal CLK2MHz is then driven to the built-in PLL, generating the internal system clock of 32MHz used for:

- The control logic

- The sampling of SPI data

- The Generation of the LF driver frequency (sine/square waves)

- The ASK Immobilizer block

## 6.3. LF transmission chain

The signal is transmitted to the antenna via the LF transmission chain

## 6.3.1. Frequency generation

The frequency generated by the LF driver can be set to a fixed value of 125 kHz or to a programmable value, according to the configuration register <u>CONF\_Byte9</u>. The value of the programmable frequency is defined in the <u>IMMO\_Byte0</u> configuration register. In programmable mode, the programmable frequency is generated from the 32MHz clock with a counter in the range from 225 (**110 kHz**) to 290 (**141.6 kHz**). The following table shows the different frequency steps allowed by the device. 125kHz is the default setting after power-up of the device.

| Counter Step (dec.) | Carrier freq. (in Hz) | Counter Step (dec.) | Carrier freq. (in Hz) |

|---------------------|-----------------------|---------------------|-----------------------|

| 225                 | 109863                | 258                 | 125977                |

| 226                 | 110352                | 259                 | 126465                |

| 227                 | 110840                | 260                 | 126953                |

| 228                 | 111328                | 261                 | 127441                |

| 229                 | 111816                | 262                 | 127930                |

| 230                 | 112305                | 263                 | 128418                |

| 231                 | 112793                | 264                 | 128906                |

| 232                 | 113281                | 265                 | 129395                |

| 233                 | 113770                | 266                 | 129883                |

| 234                 | 114258                | 267                 | 130371                |

| 235                 | 114746                | 268                 | 130859                |

| 236                 | 115234                | 269                 | 131348                |

| 237                 | 115723                | 270                 | 131836                |

| 238                 | 116211                | 271                 | 132324                |

| 239                 | 116699                | 272                 | 132813                |

| 240                 | 117188                | 273                 | 133301                |

| 241                 | 117676                | 274                 | 133789                |

| 242                 | 118164                | 275                 | 134277                |

| 243                 | 118652                | 276                 | 134766                |

| 244                 | 119141                | 277                 | 135254                |

| 245                 | 119629                | 278                 | 135742                |

| 246                 | 120117                | 279                 | 136230                |

| 247                 | 120605                | 280                 | 136719                |

| 248                 | 121094                | 281                 | 137207                |

| 249                 | 121582                | 282                 | 137695                |

| 250                 | 122070                | 283                 | 138184                |

| 251                 | 122559                | 284                 | 138672                |

| 252                 | 123047                | 285                 | 139160                |

| 253                 | 123535                | 286                 | 139648                |

| 254                 | 124023                | 287                 | 140137                |

| 255                 | 124512                | 288                 | 140625                |

| 256                 | 125000                | 289                 | 141113                |

| 257                 | 125488                | 290                 | 141602                |

Table 4: Programmable frequency step

32MHz  $Carrier_freq[Hz] = \frac{1}{Counter_Step}$

## 6.3.2. Sine wave generation

The sine wave generation mode is selected with the bit *Wave\_Mode* in the register <u>CONF Byte1</u>. In this mode, the generated output is a pure sinus signal, with a **DC** voltage value of **VS/2** and a frequency set according to the frequency generation values described above. The output voltage can also be adjusted from **0.25Vpp** up to **32Vpp** according to the **PGA** gain shown in the table below. This voltage amplitude is selected with the bits *Voltage\_Selection[5:0]* in the registers <u>CONF\_Byte5</u> and <u>CONF\_Byte6</u>. Special care should be taken to adjust the amplitude output with enough margins in respect to the VS driver supply voltage. This is required to avoid having generated harmonics due to sinus distortion. Please refer to the parameters *Vdrop\_sine\_LV* and *Vdrop\_sine\_HV* in **Table 8**.

| Configuration bits<br>(dec.) | Output voltage<br>(in Vpp) | Configuration bits<br>(dec.) | Output voltage<br>(in Vpp) |

|------------------------------|----------------------------|------------------------------|----------------------------|

| 0                            | 0                          | 23                           | 11                         |

| 1                            | 0.25                       | 24                           | 12                         |

| 2                            | 0.5                        | 25                           | 13                         |

| 3                            | 0.75                       | 26                           | 14                         |

| 4                            | 1                          | 27                           | 15                         |

| 5                            | 1.25                       | 28                           | 16                         |

| 6                            | 1.5                        | 29                           | 17                         |

| 7                            | 1.75                       | 30                           | 18                         |

| 8                            | 2                          | 31                           | 19                         |

| 9                            | 2.25                       | 32                           | 20                         |

| 10                           | 2.5                        | 33                           | 21                         |

| 11                           | 2.75                       | 34                           | 22                         |

| 12                           | 3                          | 35                           | 23                         |

| 13                           | 3.5                        | 36                           | 24                         |

| 14                           | 4                          | 37                           | 25                         |

| 15                           | 4.5                        | 38                           | 26                         |

| 16                           | 5                          | 39                           | 27                         |

| 17                           | 5.5                        | 40                           | 28                         |

| 18                           | 6                          | 41                           | 29                         |

| 19                           | 7                          | 42                           | 30                         |

| 20                           | 8                          | 43                           | 31                         |

| 21                           | 9                          | 44                           | 32                         |

| 22                           | 10                         |                              |                            |

#### Table 5: Programmable PGA gain

At the start and at the end of the LF transmission, a slope is performed respectively from 0V to VS/2 and from VS/2 to 0V. The slope is based on a fixed slew rate approaching a duration of 20  $\mu$ s for VS=40V (1V/ $\mu$ s). This is illustrated in the picture below.

Figure 7: Implementation of slopes at beginning and end of Sine transmission

## 6.3.3. Square wave generation

The square wave generation mode is selected with the bit *Wave\_Mode* in the register <u>CONF\_Byte1</u>. In this mode, the generated output is a square wave signal with amplitude fixed to the rail-to-rail value of the driver supply voltage VS.

The duty-cycle of the square wave signal can be configured to 4 values between **6.25%** up to **50%** with the bits *Duty\_Cycle[1:0]* in the register <u>CONF\_Byte6</u>.

## 6.3.4. Phase Generation

Each driver stage has an individual phase generation. Phase generation is performed in the digital part of the signal generator and can be selected independently for each output with the bits *Antenna Driver n configuration*[1:0] in the register <u>CONF Byte1</u>.

- 0°: the output signal is equivalent to the input signal with 0° phase shift.

- 180°: the output signal is equivalent to the input signal with 180° phase shift.

## 6.3.5. Selection of modulation source

The MLX74190 has a modulation source selector. The 2 bits *LF Mode[1:0]* in the register <u>CONF Byte9</u> are used to switch the selector between the different modulation sources:

| Digital inputs | Value (MSBLSB) | LF mode     | Output of the modulations source selector<br>(Digital modulation signal) |

|----------------|----------------|-------------|--------------------------------------------------------------------------|

|                | 00 (0dec)      | Normal mode | Line coded data from data register                                       |

| LF Mode        | 01 (1dec)      |             | RSSI only<br>(Output is "1" during transmission)                         |

| LF WOde        | 10 (2dec)      | Remote data | REMOTE_DATA_IN (Output corresponds to REMOTE_DATA_IN input)              |

|                | 11 (3dec)      |             | Default (No function)                                                    |

#### Table 6: Modulation source selection

The default mode is no selection (output is "0"). The digital modulation signal will be by default output to the digital pin DOUT. Before starting the transmission, DOUT is equal to "0".

#### 6.3.5.1. Specific case of Modulation through pin REMOTE\_DATA\_IN, chaining devices.

In case of modulation through the pin REMOTE\_DATA\_IN pin, i.e. when the IC is in slave mode for transmitting telegram, several hardware prerequisites are needed:

- OSC pin should be set as an input (see bit "Carrier Synchronization "<u>CONF\_Byte13</u>) and connected to the master IC which generates the LF frequency, for instance the OSC pin of a second device MLX74190.

- The LF frequency has to be synchronized with the 2MHz input CLK: this means the 4MHz ceramic resonator cannot be used and the 2MHz signal CLK used for master IC is applied on pin CLK\_IN.

For example: in case of two chained devices MLX74190: the first one - IC#1 – considered as master, will drive the second one - IC#2 – considered as slave:

- Both pins OSC are connected together

- The pin CLK\_OUT of IC#1 (master: a 4MHz ceramic resonator can be used in this case) is connected to the pin CLK\_IN of IC#2 (slave: no ceramic resonator needed)

- The pin D\_OUT of IC#1 is connected to the pin REMOTE\_DATA\_IN of IC#2

Once both devices are correctly configured, IC#2 will transmit synchronously on its output(s) the same modulated signal transmitted on the output(s) of IC#1

Two-Fold High Power LF Initiator With integrated Immobilizer

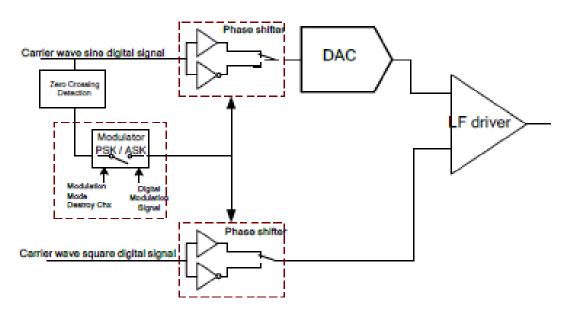

## 6.3.6. Modulator

Each driver stage is able to modulate the LF carrier signal in ASK and PSK mode. Selection of the modulation mode is done via the bit *Modulation\_mode[1:0]* in the register <u>CONF\_Byte11</u>:

- **ASK:** The amplitude of the carrier frequency is modulated from 0 to 100% according to the digital modulation data.

- PSK: The phase of the carrier frequency switches between 0° and 180° according to the digital modulation data.

Figure 8: Modulator block diagram

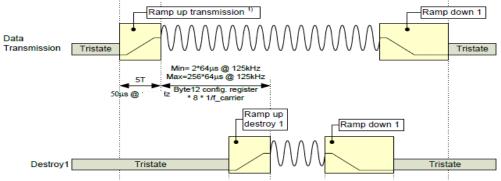

## 6.3.7. Transmission of destroy bits

The modulator can be configured to transmit DESTROY bits via the bit *Output\_Destroy* in the register <u>CONF\_Byte7</u>. In this case, two short LF sine bursts will be transmitted on the selected output, with the amplitude corresponding to the PGA gain.

The phase of the two DESTROY bits can be selected independently to 0° or 180°. The two DESTROY bits will be sent without any delay in-between and with a fixed duration time of 16 carrier periods for one DESTROY bit.

Transmitting destroy bits can be used to load the antenna before transmitting a real telegram.

## 6.3.8. LF Driver outputs

The MLX74190 features two LF drivers to amplify the sine/square wave provided by the LF generation stage.

According to the bits *Antenna Driver n configuration*[1:0] in the register <u>CONF Byte1</u>, the driver output can be configured as follows:

| Output_Configuration[1:0] | Driver output | Output Phase |

|---------------------------|---------------|--------------|

| 00                        | Hi-Z          | NA           |

| 01                        | LF transmit   | 180°         |

| 10                        | LF transmit   | 0°           |

| 11                        | Pull Down     | NA           |

#### Table 7: Driver output selection

At the end of any transmission frame or after sending a DESTROY bit, all driver outputs are automatically switched during 7 carrier periods to ground before finally switching to Hi-Z (i.e. 56us at 125kHz carrier). This automatic sequence is implemented to decrease the load current and occurs independently from the transmission mode even if another frame will follow.

## 6.3.9. Electrical parameters

| Parameter                                       | Symbol              | Min. | Тур. | Max. | Unit | Comment                                    |

|-------------------------------------------------|---------------------|------|------|------|------|--------------------------------------------|

| Outputs 1,2 current in sine mode                | I_out_sine          |      |      | 1    | Ар   |                                            |

| Outputs 1,2 current in square mode              | I_out_square        |      |      | 2.5  | Ар   |                                            |

| Output high side transistor on-resistance       | AD_Rdson_High       | 0.8  |      | 2.27 | Ω    | Including bonding wire                     |

| Output Low side transistor on-resistance        | AD_Rdson_Low        | 0.5  |      | 1.65 | Ω    | Including bonding wire                     |

| Output voltage drop in sine mode (VS-           | Vdrop_sine_LV       | 4.1  |      |      | V    |                                            |

| Vout), for low voltage (Vout ≤ 16Vpp)           |                     | 2.5  |      |      | V    | Max 15% of distortion                      |

| Output voltage drop in sine mode (VS-           | V/drop sing HV/     | 8.0  |      |      | V    |                                            |

| Vout), for high voltage (Vout > 16Vpp)          | Vdrop_sine_HV       | 4.0  |      |      | V    | Max 10% of distortion                      |

|                                                 | AD_sinus_Low_Error  | -0.7 |      | 0.4  | V    | 0.25Vpp < Vout < 4,5Vpp                    |

| Accuracy of output voltage in sine mode         | AD_sinus_Med_Error  | -11  |      | 11   | %    | 5Vpp < Vout < 7Vpp                         |

|                                                 | AD_sinus_High_Error | -5   |      | 5    | %    | 8Vpp < Vout < 32Vpp                        |

| Output peak to peak voltage sine                | Vout_sine           | 0.25 |      | 32   |      | See <u>Table 5</u> (PGA Gain<br>Selection) |

| Min. output peak to peak voltage square         | Vpp_square          | 32.1 |      | VS   | V    | For VS = 40V and with<br>I_out_square max  |

| Output switching time from Active to Hi-Z / GND | T_Switch_Hi-Z       |      |      | 1    | μs   |                                            |

| Output switching time from Hi-Z / GND to        | T. Guuitala antiura |      |      | 2.5  | μs   |                                            |

| Active                                          | T_Switch_active     |      |      | 0.2  | μs   |                                            |

| Total phase shift                               | Phase_Shift_AD      | 263  | 373  | 525  | ns   | Sine mode                                  |

| DC voltage level VS/2 accuracy                  | AD_Sinus_VS_2       | -6.5 |      | 6.5  | %    | Sine mode                                  |

Table 8: Antenna driver specifications

## 6.4. Immobilizer Function

The MLX74190 embeds two ASK and FSK immobilizer blocks. These Immobilizers are used to detect and demodulate data from a transponder via respectively amplitude-shift keying (ASK) or frequency-shift keying (FSK) modulation techniques. The MLX74190 includes 2 input pins for each ASK / FSK demodulators that cannot be activated simultaneously. The demodulated and digitized signal is then transmitted to the MCU via the **D\_OUT** output pin.

The immobilizer inputs can be connected to every driver through external hardware and can be enabled / disabled by register settings. They can be fully programmed through a set of registers available in chapter <u>Immobilizer Configuration</u> <u>Register</u>. One channel of either ASK or FSK can be used at a time.

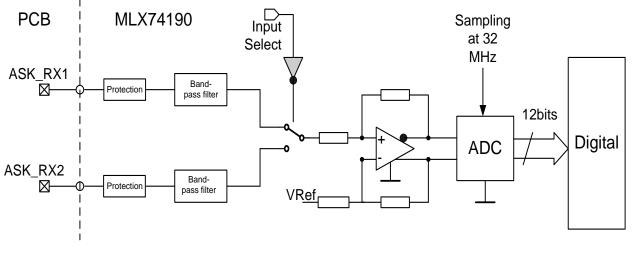

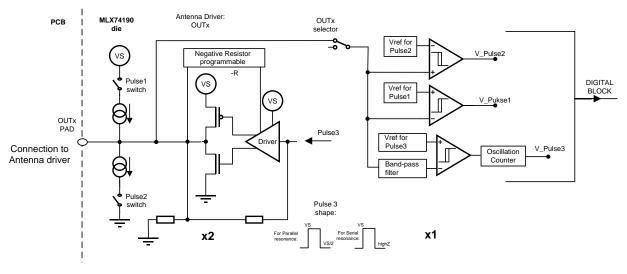

## 6.4.1. ASK demodulation

The ASK demodulator converts the amplitude-modulated analog signal received on ASK\_RXi pins from the transponder into digital data which are accessible by the MCU through the D\_OUT output pin.

If the immobilizer is deactivated, the ASK RXi input pins are connected to GND.

If the immobilizer is activated, the voltage swing at the ASK\_RXi inputs is internally clamped to 18Vpp. The ASK\_RXi inputs are connected to the LF antenna through an external capacitive divider. This capacitive divider should be calculated regarding the maximum voltage expected on the antenna, to avoid saturating the ASK input (i.e. 18V clamping voltage)

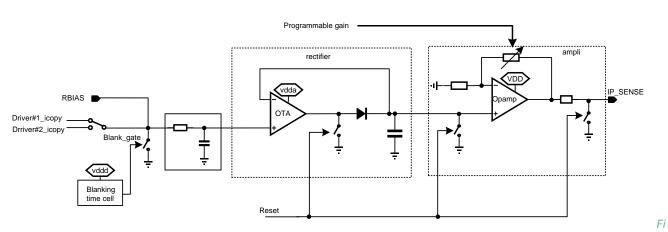

#### Figure 9: Immobilizer ASK, block diagram

Both ASK\_RXi inputs embed a band-pass filter which has to be set according to the incoming data-rate of the TAG. As shown in the table below, the maximum supported data-rate is of 8Kbit/s.

| IMMO_Byte1 [6:7] | Data Rate | Min. Modulation Frequency | Max. Modulation Frequency |  |  |  |  |  |

|------------------|-----------|---------------------------|---------------------------|--|--|--|--|--|

| 00               | 2 Kbit/s  | 1 KHz                     | 2 KHz                     |  |  |  |  |  |

| 01               | 4 Kbit/s  | 2 KHz                     | 4 KHz                     |  |  |  |  |  |

| 10               | 8 Kbit/s  | 4 KHz                     | 8 KHz                     |  |  |  |  |  |

| 11               | Reserved  |                           |                           |  |  |  |  |  |

Table 9: ASK data rate selection

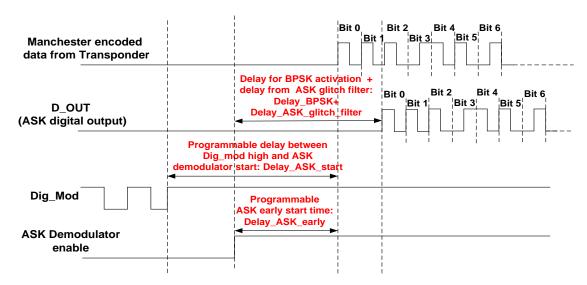

The time at which the demodulated signal is available at D\_OUT can be configured with two timings, available in

Two-Fold High Power LF Initiator

With integrated Immobilizer

Immobilizer Configuration Register (BYTE#2): the Programmable delay between signal Dig\_mod High and ASK demodulator

start, and the Programmable Early Start time.

The BPSK delay and the ASK Glitch filter configuration, in

Two-Fold High Power LF Initiator With integrated Immobilizer

Immobilizer Configuration Register, also impact the global timings, as shown in the picture below.

#### Figure 10: ASK demodulation signals

The formula below can be used to calculate the demodulator's delay: Demodulator\_delay\_D\_OUT = Delay\_ASK\_start - Delay\_ASK\_early + Delay\_BPSK + Delay\_ASK\_glitch\_filter

| Delays                                                                                 | Unit DataRate :<br>2 kbit/s |      | DataRate :<br>4 kbit/s | DataRate :<br>8 kbit/s |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------|------|------------------------|------------------------|--|--|--|--|--|

| Delay glitch filter: off                                                               | μs                          | 0    | 0                      | 0                      |  |  |  |  |  |

| Delay glitch filter: 01                                                                | μs                          | 48   | 24                     | 12                     |  |  |  |  |  |

| Delay glitch filter: 10                                                                | μs                          | 80   | 40                     | 20                     |  |  |  |  |  |

| Delay glitch filter: 11                                                                | μs                          | 144  | 72                     | 36                     |  |  |  |  |  |

| Delay_BPSK                                                                             | μs                          | 1616 | 808                    | 408                    |  |  |  |  |  |

| Delay_ASK_start and Delay_ASK_early are defined in BYTE#2 of Immobilizer Configuration |                             |      |                        |                        |  |  |  |  |  |

| Register                                                                               |                             |      |                        |                        |  |  |  |  |  |

Table 10: ASK signal: typical delays

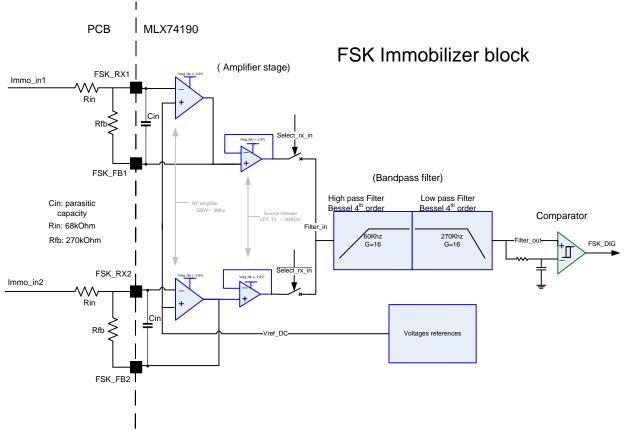

## 6.4.2. FSK demodulation

The FSK demodulation block is intended to detect and demodulate the response of the transponder compliant with FSK modulation (frequency shift keying). The demodulated data are accessible by the MCU through the D\_OUT output pin. The FSK signal is a modulated frequency signal, where high and low bits are coded with two different frequencies.

The frequency of the input signal is measured by counting the oscillation clock for the time period of the input signal. As the high-bit and low-bit frequencies are specified with wide tolerances, the demodulator distinguishes them using the difference between both frequencies and not by their absolute values. After the charge phase, the FSK demodulator measures the time period of its input signal and waits for the transponder resonance-frequency measurement to determine the threshold between high-bit and low-bit frequency.

Then the demodulator waits for the occurrence of the start bit.

The detection of the start bit is effective when the contents of the shift register matches a specific pattern, indicating 8 subsequent periods below the threshold (higher frequency) immediately followed by 4 subsequent periods above the threshold (lower frequency)

The bit stream detected by the digital demodulator passes through a digital filter before being evaluated. After demodulation, the serial bit flow received from the transponder is buffered byte-wise before being sent to the microcontroller.

The two external resistors **Rin** and **Rfb** are typically set to obtain an amplifier gain of 4 and limiting the input current to an absolute maximum of 2mA. These resistors might be adjusted according to the voltage swing on the external antenna.

# 6.4.3. Electrical parameters

| Parameter                                      | Symbol              | Min.  | Тур.  | Max. | Unit | Comment                                                                                    |

|------------------------------------------------|---------------------|-------|-------|------|------|--------------------------------------------------------------------------------------------|

| Input voltage range at ASK_RXi<br>pin          | Immo_ASK_range      | 0     |       | 18   | Vpp  |                                                                                            |

| ASK_RXi pin input positive<br>current range    | Immo_ASK_Ip         |       |       | 20   | mA   | Vdd = 5V, in the<br>specified input<br>range                                               |

| ASK_RXi pin input negative current range       | Immo_ASK_Im         | -20   |       |      | mA   | Vdd = 5V, in the<br>specified input<br>range                                               |

| ASK_RXi pin positive clamping voltage.         | Immo_VClamp_RX<br>p | 18    | 20    | 22   | V    |                                                                                            |

| ASK_RXi pin negative clamping voltage          | Immo_VClamp_RX<br>m | -1.50 | -0.85 | -0.5 | V    |                                                                                            |

| ASK_RXi pin input impedance <sup>(1)</sup>     | Immo_ASK_RX_Im<br>p | 50    |       |      | kOhm | Equivalent AC<br>resistor @ 125<br>KHz                                                     |

|                                                | Immo_ASK_RX_R       | 100   |       |      | kOhm | DC resistor                                                                                |

| Min. detectable modulation<br>depth at ASK-RXi | Immo_AM_ASK         |       | 1.35  |      | mVpp | measured @<br>BER=0.1% and<br>4Kbit/s, with<br>amplitude of min<br>0.9Vpp and max<br>18Vpp |

Table 11: ASK demodulator specifications

(1) In case of deactivated immobilizer, the pin is grounded via a switch with ca.  $200\Omega$  series resistance.

| Parameter                                            | Symbol          | Min.  | Тур.  | Max.  | Unit | Comment            |

|------------------------------------------------------|-----------------|-------|-------|-------|------|--------------------|

| Low bit frequency                                    | Freq_low_bit    | 130.2 | 134.7 | 139.5 | KHz  |                    |

| High bit frequency                                   | Freq_high_bit   | 118   | 123   | 128   | KHz  |                    |

| Input current range at<br>FSK_RXi in charge phase    | FSK_I_range     | -2    |       | +2    | mA   |                    |

| Phase Shift of RF amplifier <sup>(1)</sup>           | Phase_0         |       |       | 16    | 0    | Meas. @134kHz      |

| Sensitivity / Minimum peak-<br>to-peak input voltage | V_sfb           |       | 5     |       | mVpp |                    |

| Band Pass Filter                                     | Immo ESK Filtor | 24    | 60    | 100   | kHz  | Low cut off freq.  |

| Dallu Pass Fillel                                    | Immo_FSK_Filter | 160   | 270   | 500   | kHz  | High cut off freq. |

Table 12: FSK demodulator specifications

(1) With Rin=68kOhm, Rfb = 270kOhm and input voltage = 20mVpp

# 6.5. Digital SPI Interface

The MLX74190 is interfaced and configured through a standard Serial Peripheral Interface bus (SPI). The communication is full duplex: the host MCU (microcontroller) receives status information from the MLX74190 while sending configuration settings. Within the communication, the host MCU always acts as a Master and the MLX74190 always acts as a slave.

The microcontroller sends to the MLX74190:

- The configuration of the MLX74190 according to the application requirements

- The data of the telegram to be sent

- The control command

The microcontroller receives from the MLX74190:

- Status register content (default)

- Shift-In register content (after direct command "Set SDO to send SDI")

- Working register content (after direct command "Read working register")

The SPI consists of shift-in and shift-out registers controlled with the following signals:

- NCS: Not Chip Select

- SCLK: Serial Clock

- SDI: Serial Data In

- SDO Serial Data Out

#### Commands:

The MLX74190 understands two types of commands:

- Circular commands: will be understood within the same NCS cycle

- Direct commands: Requiring its own NCS cycle.

The direct commands are executed immediately whereas the circular commands are stored one after the other in the circular buffer and executed successively.

For more information on the implemented commands, please refer to the chapter

Two-Fold High Power LF Initiator With integrated Immobilizer

<u>SPI</u> Commands below. The length for the command is fixed to 8 bits and it is sent at the beginning of a communication frame.

#### Data area:

- Variable length from 0 byte till 15 bytes.

- The number of data bytes to be transmitted during one communication frame depends on the command. This is sent at the second position in the SPI communication, just after the command.

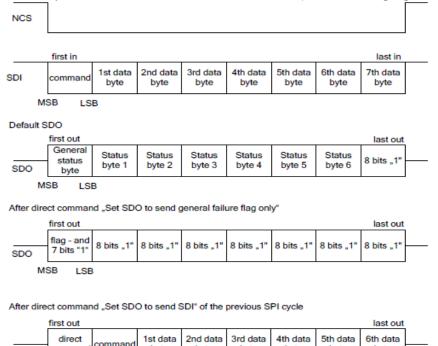

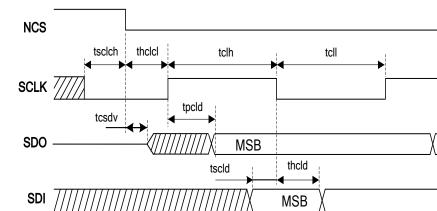

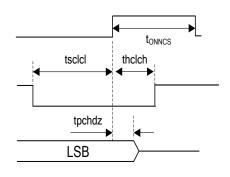

## 6.5.1. SPI signal frames

When NCS is high, the MLX74190 is not selected and any signal at the SCLK and SDI pins is ignored. Moreover, the pin SDO is forced into a high impedance state.

The MLX74190 is selected with the pin NCS set to zero by the master; this pin shall remain to zero during the complete SPI communication cycle. The MLX74190 is able to receive several bytes as one block without delay between the bytes.

SPI data are shifted-in from SDI at each falling edge of the SCK signal (with NCS set to low). SPI data are shifted-out on SDO at each rising edge of the SCK signal (with NCS set to low).

By default, the MLX74190 returns its status information as follows:

1st Byte: general status byte (see

Two-Fold High Power LF Initiator With integrated Immobilizer

- Status Register)

- 2nd to 7th Byte: status Byte 1 to status byte 6 (see

Two-Fold High Power LF Initiator With integrated Immobilizer

- Status Register)

- 8th and following bytes: "11111111

The information sent out by SDO will change after the following SPI-direct commands:

Send general failure flag:

Only the general failure flag (Bit 0 of the general status byte) is returned by the MLX74190. All other bits are set to "1". This is valid until another direct command is sent to change the setting of SDO pin or until the chip enters in sleep mode.

Set SDO to send SDI:

The data shifted in from SDI will be shifted out on SDO with 1 byte delay.

Read working register:

The content of the working register of the address defined in the command and the following bytes shall be sent on SDO.

The number of bytes depends on the length of the following frame. A complete frame shall be recognized by a low to high transition on NCS. If the number of bits transferred to SDI during one frame is not divisible by 8 (there is a low to high transition on NCS and the last byte transferred to SDI doesn't consist of 8 bits) a SPI-error flag is generated.

After direct command "Read working register" of the previous SPI cycle

byte

omman

LSB

MSB

SDO

|     | first out                 |                    |                   |                   |                   |                   |                  | last out          |  |

|-----|---------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|--|

|     | content of                | content of         | content of        | content of        | content of        | content of        | content of       | content of        |  |

| SDO | content of<br>start addr. | start addr.<br>+ 1 | start addr.<br>+2 | start addr.<br>+3 | start addr.<br>+4 | start addr.<br>+5 | start addr<br>+6 | start addr.<br>+7 |  |

| M   | SB LSE                    | 3                  |                   |                   |                   |                   |                  |                   |  |

byte

byte

byte

byte

byte

Figure 12: SPI communication frames

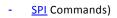

# 6.5.2. SPI Commands

| 7         6         5         4         a         2         1         0         code         Command description           1         Number of transmission data bit<br>(max=64,00000b=1)         -         Program Transmission Data Register         -         Program Transmission Data Register           0         0         0         -         Number of tytes<br>(max 14,000b=1)         IX         Program Configuration Register           0         0         1         L         L         L         L         X           0         1         0         1         Number of tytes<br>(max 4,000b=1)         XX         Program Transmission Data Format Register without IRQ<br>generation           0         1         0         1         L         L         L         X           0         1         0         1         L         L         X         Program Transmission Data Format Register with IRQ<br>generation           0         1         1         0         0         38         Continue with RSS until next "program transmission data           0         1         1         1         0         38         Continue with RSS until next "program transmission data           0         1         1         1         0         38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |   | Com | mand       | BYTE     |           |                |         | Неха |                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---|-----|------------|----------|-----------|----------------|---------|------|------------------------------------------------------------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7           | 6 |     | 1          | 3        | 2         | 1              | 0       | code | Command description                                        |

| Image: constraint of the second sec                                                                                                                                                                                                                                                                                                             |             |   |     |            |          |           |                |         |      |                                                            |

| 0         0         0         Number of bytes<br>(x) and (x) bytes<br>(x) an |             | 1 |     | (m         | -        | 00000b:   | =1)            |         | -    | Program Transmission Data Register                         |

| 0         0         0         0         (max 14, 0000b = 1)<br>(max 4, 0000b = 1)         0X         Program Configuration Register           0         0         1         L         L         L         L         L           0         1         L         L         L         L         L         L           0         1         0         0         1         L         L         L         L           0         1         0         0         1         L         L         L         L         Recertaion           0         1         0         1         Number of bytes (max<br>4,000b+1)         2X         Program Transmission Data Format Register with IRQ generation at start of the first data bit with this format           0         1         1         0         0         38         Continue with RSSI until next "program transmission data commad"           0         1         1         1         0         1         38         Resteread & write pointers of circular buffer           0         1         1         1         0         1         38         Resteread & write pointers of circular buffer           0         1         1         1         1         1         38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |   | L   | L          | L        | L         | L              |         |      |                                                            |

| O: Circular<br>command         I         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | 0 | 0   | 0          |          |           |                |         | 07   | Program Configuration Projector                            |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | 0 | 0   | 0          |          | 1110X 14, | 1              |         | 07   | riogram configuration register                             |

| 0         0         1 $(max 4, 0000 = 1)$ 1x         Program Immobilizer Configuration Register           0: Circular command         1         0         1         L         L         L         L           0: Circular command         0         1         0         1         L         L         L         L         L           0: Circular command         0         1         0         1         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L         L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |   |     |            | _        | Numbe     | r of byte      |         |      |                                                            |

| 0         1         0         0         Number of bytes (max<br>4,000b=1)         2x         Program Transmission Data Format Register without IRQ<br>generation           0: Circular<br>command         0         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | 0 | 0   | 1          |          |           |                |         | 1X   | Program Immobilizer Configuration Register                 |

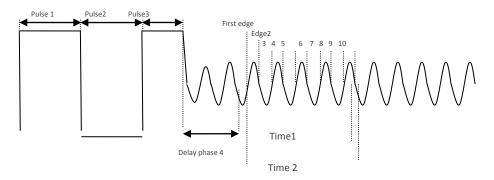

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |   |     |            | L        | L         | L              | L       |      |                                                            |