LIN System Basis ICs

Datasheet

# **Features**

- LIN 2.x / SAE J2602 compliant

- Operating voltage V<sub>SUP</sub> = 5 ... 27 V

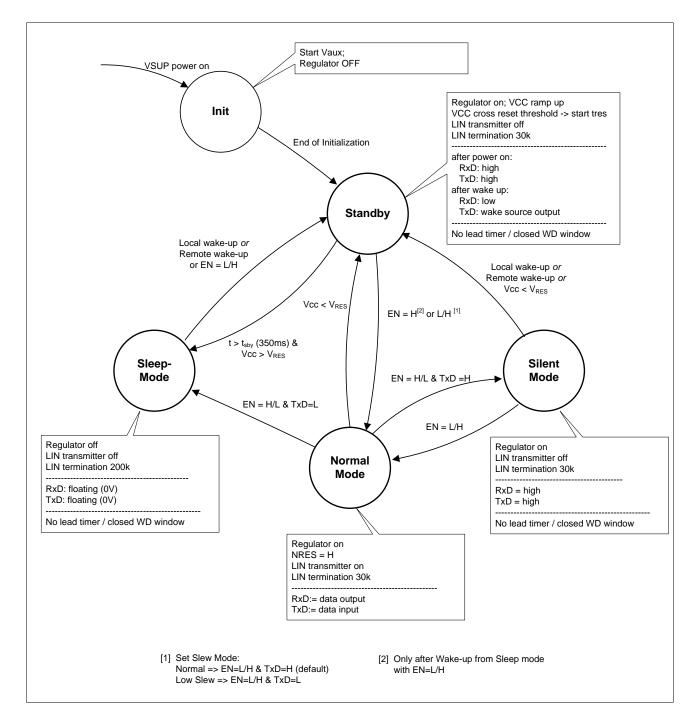

- 3 modes: Normal, Silent and Sleep

- Linear low drop voltage regulator: MLX80030/31:

- Normal mode 3.3V/70mA ±2%

- Silent mode 3.3V/20mA ±2%

- MLX80050/51:

- Normal mode 5V/70mA ±2%

- Silent mode 5V/20mA ±2

- Low current consumption (typ)

- Sleep mode 20 μA

- Silent mode "noload" 45 μA

- Output current limitation

- LIN-Bus Transceiver

- Baud rate up to 20 kBaud

- Slew rate control for best EME behaviour

- Low slew mode for optimized SAE J2602 transmission

- High impedance LIN pin in case of loss of ground or battery

- Remote and local wake up source recognition

- VCC undervoltage detection at NRES output (start-up delay 4ms)

- Vres threshold 3.0 V (MLX80030/31); Vres threshold 4.1V (MLX80050/51)

- Programmable Window Watchdog (only MLX80031/51)

- VSUP undervoltage detection (POR), Over temperature shutdown

- TxD dominant time out function, Standby mode time out after 350ms

- Automotive temperature range of –40°C to 125°C

- Interface I/O's independent from voltage regulator output

- Enhanced ESD robustness according to IEC 61000-4-2

- Direct discharge for pin LIN >20kV (only Lin cap connected) and for pin VBAT >15kV

- Indirect discharge for pin LIN >15kV

- Load dump protected (40V)

| Order Code             | Temp. Range  | Package      | Delivery | Remark              |

|------------------------|--------------|--------------|----------|---------------------|

| MLX80050KDC-CAA-100-RE | -40 - 125 °C | SOIC8        | Reel     | Silent Mode enabled |

| MLX80051KLW-CAA-100-RE | -40 - 125 °C | QFN_WF20/5x5 | Reel     | Silent Mode enabled |

| MLX80030KDC-CAA-100-RE | -40 - 125 °C | SOIC8        | Reel     | Silent Mode enabled |

| MLX80031KLW-CAA-100-RE | -40 - 125 °C | QFN_WF20/5x5 | Reel     | Silent Mode enabled |

# **Short Description**

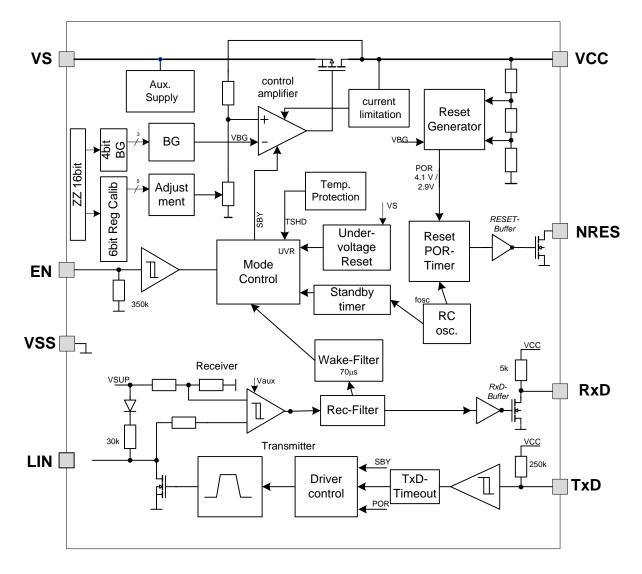

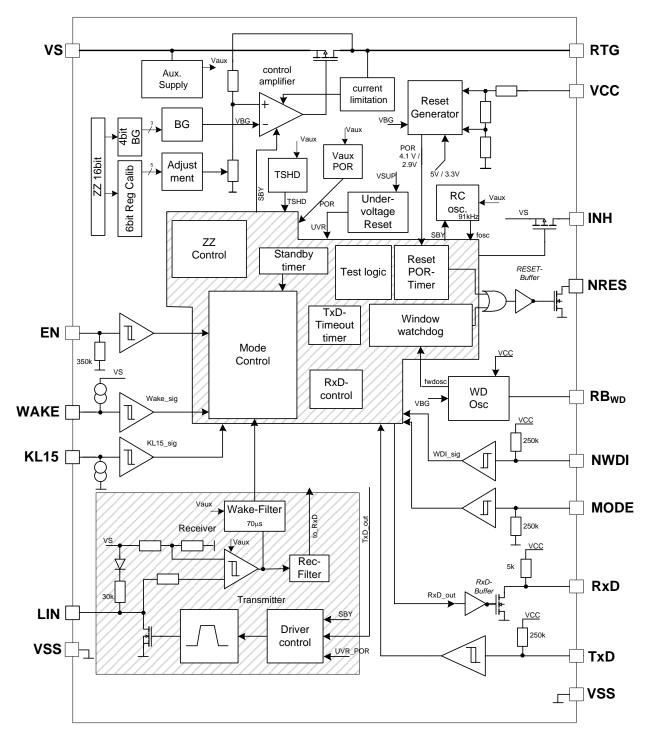

The MLX8005x/3x consist of a low-drop voltage regulator 5V/3.3V/70mA combined with a Reset/Watchdog unit and a LIN bus transceiver. The LIN transceiver is suitable for LIN bus systems conform to LIN specification revision 2.x and SAE J2602. The watchdog times of the integrated window watchdog can be adapted on application needs via external resistors. With the help of an external bipolar transistor it is possible to extend the output current of the integrated voltage regulator. The combination of voltage regulator and bus transceiver as well as watchdog unit makes it possible to develop simple, but powerful and cheap slave nodes in LIN Bus systems.

LIN System Basis ICs Datasheet

# Contents

| 1. LIST OF TABLES                                                                                                                                         | 4                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2. LIST OF FIGURES                                                                                                                                        | 4                    |

| 3. ELECTRICAL SPECIFICATION                                                                                                                               | 5                    |

| <ul><li>3.1. DC Characteristics</li><li>3.2. AC Characteristics</li><li>3.3. Timing diagrams</li></ul>                                                    | . 11                 |

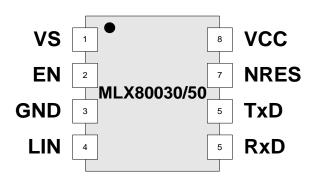

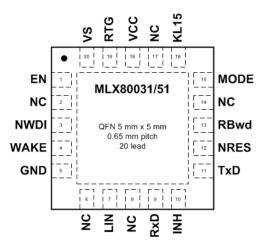

| 4. PIN CONFIGURATION                                                                                                                                      | . 15                 |

| 4.1. MLX80030 AND MLX80050 - SOIC8<br>4.2. MLX80031 AND MLX80051 IN QFN20                                                                                 |                      |

| 3. FUNCTIONAL DESCRIPTION                                                                                                                                 | . 17                 |

| <ul> <li>3.1. SUPPLY PIN VS</li></ul>                                                                                                                     | . 19<br>. 19<br>. 19 |

| <ul><li>3.5. Receiver Output RxD</li><li>3.6. Transmit Input TxD</li></ul>                                                                                |                      |

| 3.6.1. TxD dominant time-out feature<br>3.7. Оυтрит NRES                                                                                                  | . 19<br>. 20         |

| 3.8. VOLTAGE REGULATOR PINS VCC AND RTG                                                                                                                   |                      |

| 3.9. INH OUTPUT (ONLY MLX80031/51)<br>3.10. WAKE INPUT (ONLY MLX80031/51)                                                                                 |                      |

| 3.11. KL15 INPUT (ONLY MLX80031/51)                                                                                                                       |                      |

| 3.12. WATCHDOG TRIGGER INPUT NWDI (ONLY MLX80031/51)                                                                                                      |                      |

| 3.13. WATCHDOG OSCILLATOR RESISTOR RB <sub>WD</sub> (ONLY MLX80031/51)                                                                                    |                      |

| 3.14. Mode Input MODE (only MLX80031/51)                                                                                                                  |                      |

| 4. OPERATIONAL MODES                                                                                                                                      | . 21                 |

| <ul> <li>4.1. Modes Overview</li></ul>                                                                                                                    | 23<br>23<br>24<br>25 |

| 5. WAKE UP PROCEDURES                                                                                                                                     | . 28                 |

| 5.1. Wake Up Source Recognition in MLX80031/51                                                                                                            | 28                   |

| 6. FUNCTIONALITY                                                                                                                                          | . 29                 |

| <ul> <li>6.1. RESET behaviour of MLX8003x/5x</li> <li>6.2. Thermal Shutdown</li> <li>6.3. VS under voltage reset</li> <li>6.4. LIN-Transceiver</li> </ul> | 29<br>29             |

LIN System Basis ICs Datasheet

| 6.5. Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                      | 30                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 7. WINDOW-WATCHDOG (ONLY MLX80031/51)                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                           |

| <ul> <li>7.1. MLX80031/51 WATCHDOG BEHAVIOUR</li> <li>7.2. ALL WATCHDOG START-UP SCENARIOS</li> <li>7.2.1. After power-on and initialization</li> <li>7.2.2. Wake up indicated transition to Standby Mode from Sleep or Silent Mode</li> <li>7.2.3. Undervoltage reset on VCC on Normal Mode or Silent Mode</li> <li>7.2.4. EN indicated transition from Silent Mode to Normal Mode</li> <li>7.3. CALCULATION OF WATCHDOG PERIOD</li> </ul> | 32<br>32<br>32<br>32<br>32                   |

| 8. FAIL-SAFE FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                       | 35                                           |

| 9. APPLICATION HINTS                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                           |

| 9.1. Safe Operating Area                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

| 10. ESD AND EMC                                                                                                                                                                                                                                                                                                                                                                                                                             | 38                                           |

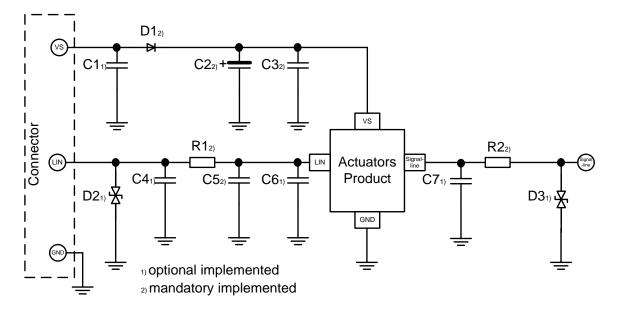

| <ul> <li>10.1. RECOMMENDATIONS FOR ACTUATOR PRODUCTS</li></ul>                                                                                                                                                                                                                                                                                                                                                                              | 38<br>39<br>39<br>40<br>41<br>42<br>42<br>42 |

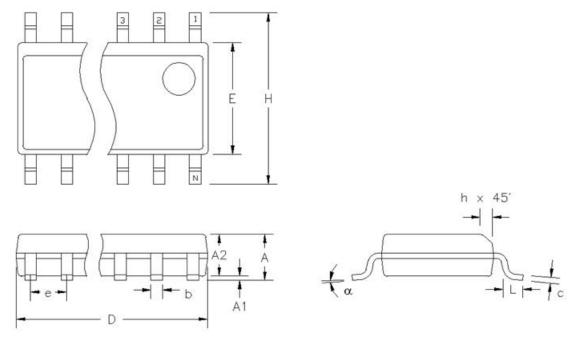

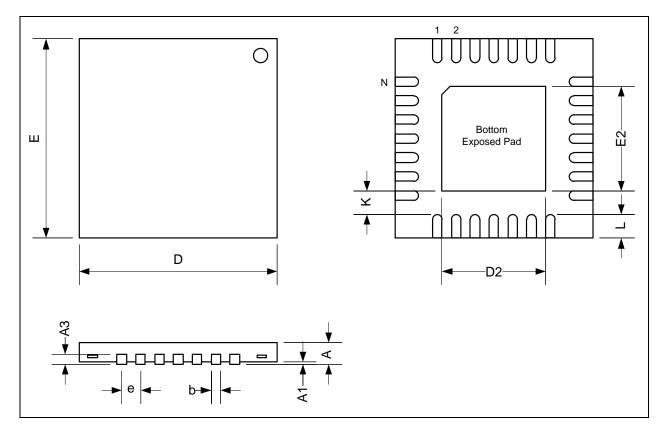

| 11. MECHANICAL SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                | 43                                           |

| 11.1. SOIC8 package<br>11.2. QFN20 5x5 package                                                                                                                                                                                                                                                                                                                                                                                              | 43<br>44                                     |

| 12. REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                           |

| 13. STANDARD INFORMATION REGARDING MANUFACTURABILITY OF MELEXIS PRODUCTS WITH<br>DIFFERENT SOLDERING PROCESSES                                                                                                                                                                                                                                                                                                                              |                                              |

| 15. CONTACT                                                                                                                                                                                                                                                                                                                                                                                                                                 | .49                                          |

LIN System Basis ICs Datasheet

# **1. List of Tables**

| TABLE 1: ABSOLUTE MAXIMUM RATINGS          |    |

|--------------------------------------------|----|

| TABLE 2: VOLTAGE REGULATOR AND RESET UNIT  | 6  |

| TABLE 3: LIN DC CHARACTERISTICS            | 10 |

| TABLE 4: AC CHARACTERISTICS                |    |

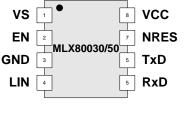

| TABLE 5: MLX80050/30 PIN LIST IN SOIC8     | 15 |

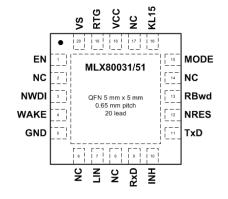

| TABLE 6: MLX80051/31 PIN LIST IN QFN20.    |    |

| TABLE 7: MLX80050/30 OPERATION MODES       | 22 |

| TABLE 8: MLX80051/31 OPERATION MODES       |    |

| TABLE 9: PARAMETERS OF WINDOW WATCHDOG     |    |

| TABLE 10: WINDOW WATCHDOG TIMING SELECTION |    |

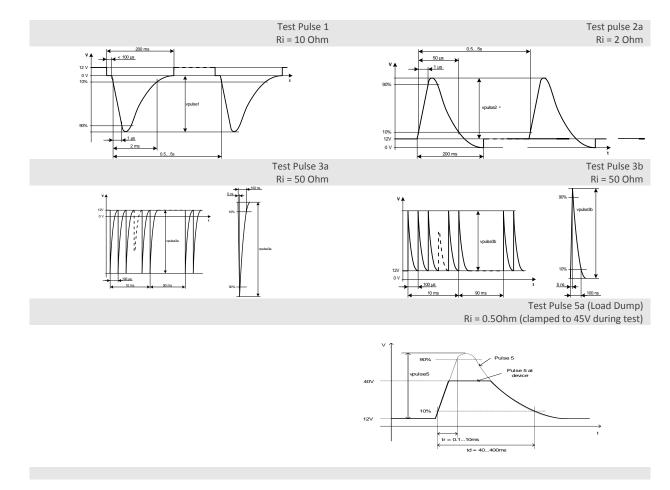

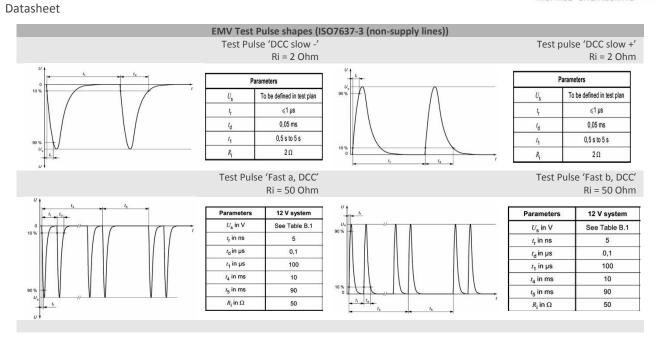

| TABLE 11: TEST PULSES SUPPLY LINE          | 38 |

| TABLE 12: TEST PULSES LIN                  |    |

| TABLE 13: TEST PULSES SIGNAL LINES         |    |

| TABLE 14: TEST PULSES SHAPES ISO7637-2     | 40 |

| TABLE 15: TEST PULSES SHAPES ISO7637-3     |    |

| TABLE 16: SOIC8 DIMENSIONS                 | 43 |

| TABLE 17: QFN20 PACKAGE DIMENSIONS         | 44 |

# **2. List of Figures**

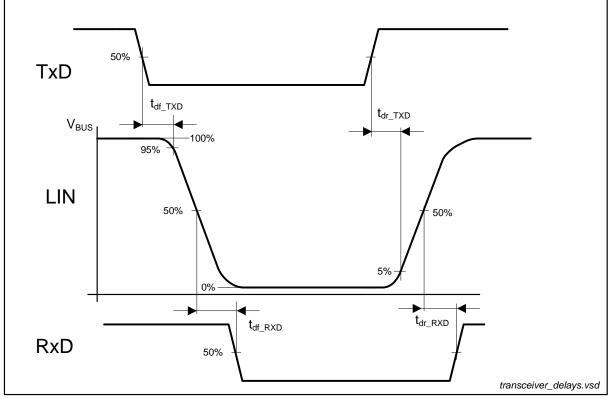

| FIGURE 1: LIN PROPAGATION DELAYS                                            |    |

|-----------------------------------------------------------------------------|----|

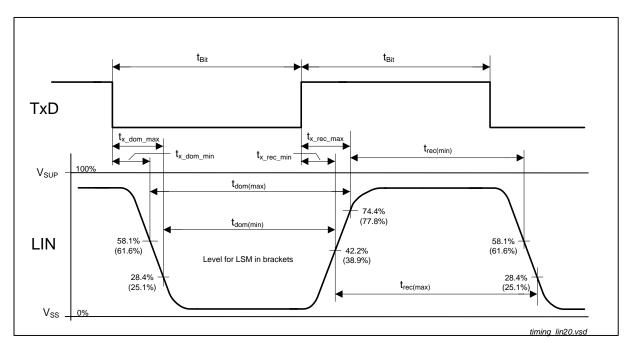

| FIGURE 2: LIN DUTY CYCLES                                                   |    |

| FIGURE 3: MLX80050/30 BLOCK DIAGRAM                                         | 17 |

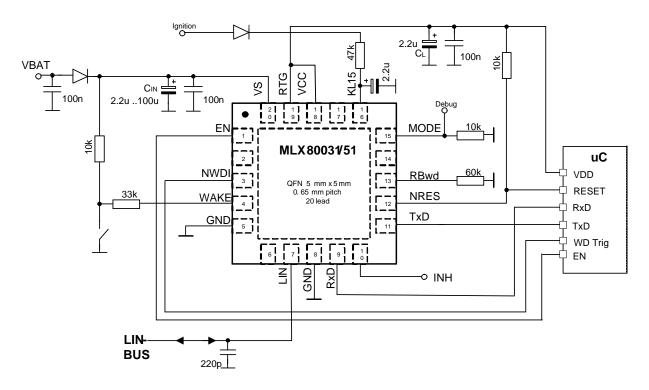

| FIGURE 4: MLX80051/31 BLOCK DIAGRAM                                         | 18 |

| FIGURE 5: MLX8005x3x STATE DIAGRAM OF MODES OF OPERATION                    | 21 |

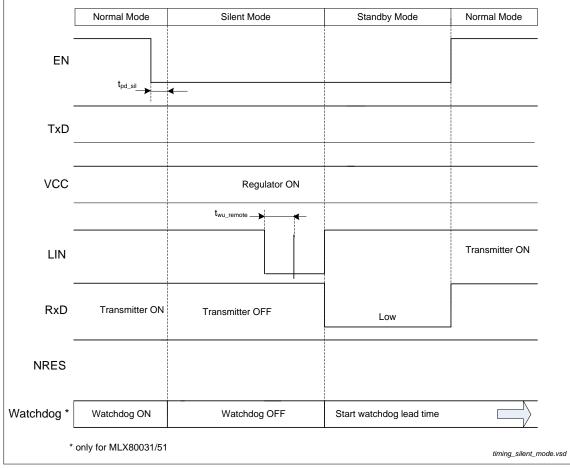

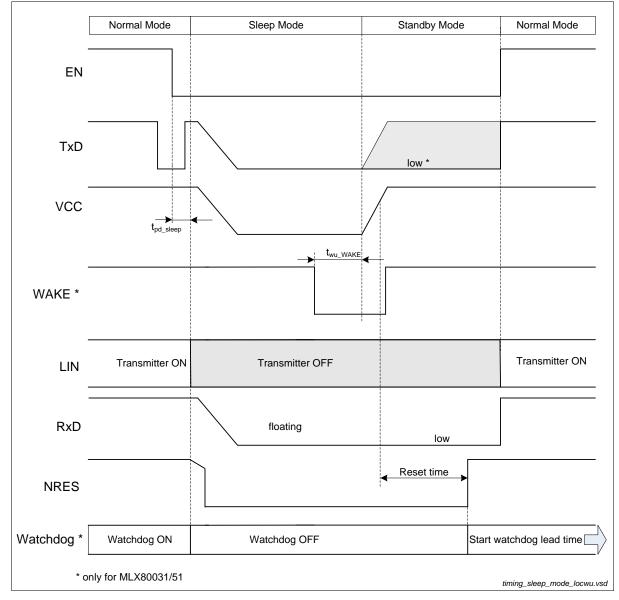

| FIGURE 6: LIN WAKE-UP FROM SILENT MODE                                      | 24 |

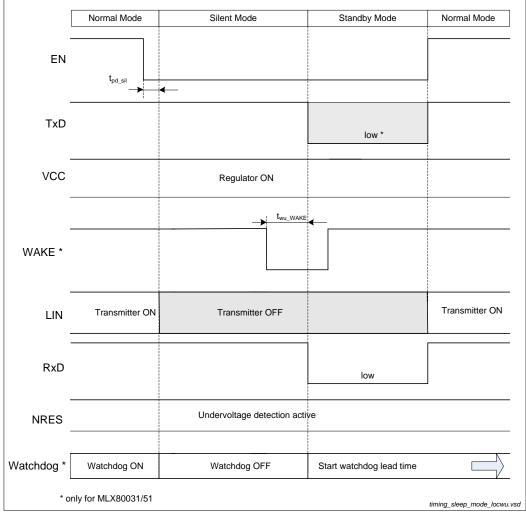

| FIGURE 7 LOCAL WAKE-UP FROM SILENT MODE VIA WAKE                            |    |

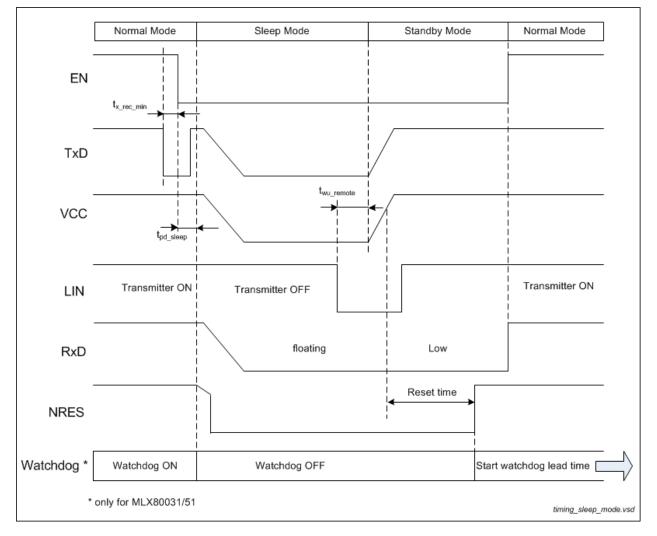

| FIGURE 8: REMOTE WAKE-UP FROM SLEEP MODE                                    |    |

| FIGURE 9: LOCAL WAKE-UP FROM SLEEP MODE                                     |    |

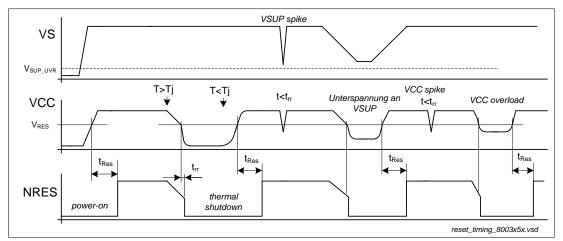

| FIGURE 10: VCC RESET BEHAVIOR                                               |    |

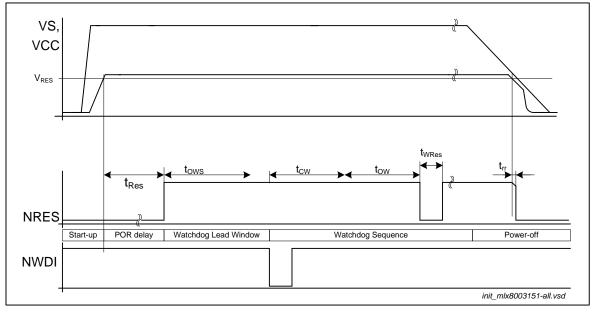

| FIGURE 11: MLX80031/51 WATCHDOG BEHAVIOR                                    |    |

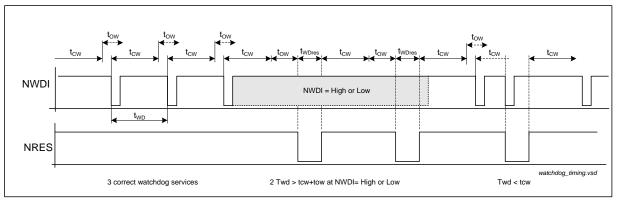

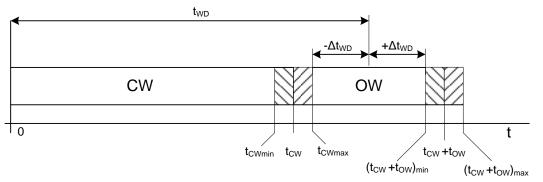

| FIGURE 12: WATCHDOG TIMING                                                  | 32 |

| FIGURE 13: WATCHDOG OPEN AND CLOSE WINDOW TOLERANCES                        | 33 |

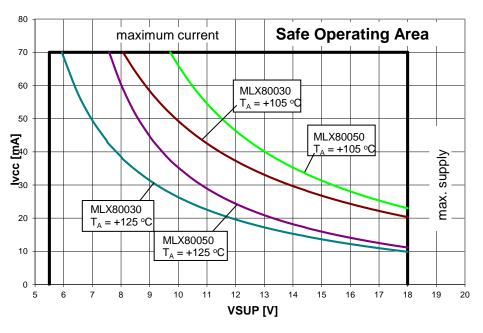

| FIGURE 14: SAFE OPERATING AREA FOR MLX80030/50 IN SOIC-8 FOR VSUP UP TO 18V | 36 |

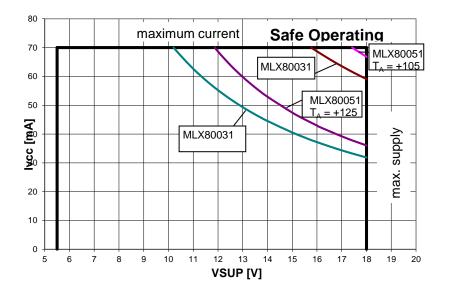

| FIGURE 15: SAFE OPERATING AREA FOR MLX80031/51 IN QFN20 FOR VSUP UP TO 18V  | 36 |

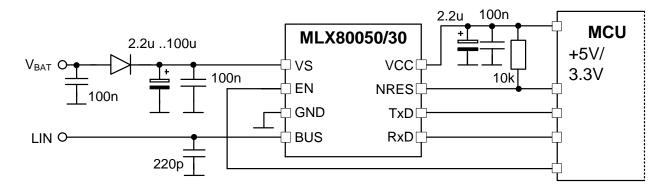

| FIGURE 16: APPLICATION CIRCUIT WITH MLX80050 OR MLX80030 (SLAVE NODE)       | 37 |

| FIGURE 17: APPLICATION CIRCUIT WITH MLX80031 OR MLX80051 (SLAVE NODE)       | 37 |

| FIGURE 18: SOIC8 DRAWING                                                    |    |

| FIGURE 19: QFN20 DRAWING                                                    | 44 |

LIN System Basis ICs Datasheet

# **3. Electrical Specification**

All voltages are referenced to ground (GND), positive currents flow into the IC.

### Absolute Maximum Ratings

| Parameter                                                                                | Symbol                  | Condition                                                                | Min            | Мах                         | Unit           |

|------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------|----------------|-----------------------------|----------------|

| Supply voltage at VS                                                                     | Vs                      | Respective to GND                                                        | -0.3           | 40                          | V              |

| Transient voltage ISO 7637/2                                                             |                         | pulse 1, 2                                                               | -100           | 100                         | V              |

| Transient voltage ISO 7637/2                                                             |                         | pulse 3A; 3B, coupling 1nF                                               | -150           | 100                         | V              |

| DC voltage LIN                                                                           | V <sub>LIN_DC</sub>     | Respective to GND and VS<br>Loss of Ground (VGND =<br>VS)                | -20<br>-30     | 40<br>40                    | V              |

| DC voltage WAKE                                                                          | V <sub>WAKE_DC</sub>    | Respective to GND and VS<br>Loss of Ground (VGND =<br>VS)                | -20<br>-30     | 40<br>40                    | V              |

| DC voltage INH                                                                           | V <sub>INH_DC</sub>     |                                                                          | -0.3           | V <sub>s</sub> +0.3         | V              |

| DC voltage VCC                                                                           | V <sub>VCC_DC</sub>     |                                                                          | -0.3           | 7                           | V              |

| DC voltage RTG                                                                           | V <sub>RTG_DC</sub>     |                                                                          | -0.3           | 7                           | V              |

| Input voltage at low voltage I/O's (EN, TxD,<br>RxD, NRES, WDI, RB <sub>WD</sub> , MODE) | V <sub>IN</sub>         |                                                                          | -0.3           | 7                           | V              |

|                                                                                          | V <sub>ESDIEC</sub>     | IEC 61000-4-2, direct ESD<br>Pin LIN with LIN cap 220pF<br>Pin VS to GND | 20<br>15       |                             | kV             |

|                                                                                          | V <sub>ESDIECind</sub>  | IEC 61000-4-2, indirect ESD<br>Pin LIN with LIN cap 220pF                | 15             |                             | kV             |

| ESD voltage                                                                              | V <sub>esdhbm</sub>     | HBM (CDF-AEC-Q100-002)<br>Pin LIN<br>Pin WAKE, KL15, VS<br>Other pins    | ±6<br>±4<br>±2 |                             | kV<br>kV<br>kV |

|                                                                                          | V <sub>esdcdm</sub>     | CDM (AEC-Q100-011)                                                       | ±500           |                             | V              |

| Power dissipation                                                                        | P <sub>0</sub>          |                                                                          | see also       | l limited'<br>chapter<br>.1 |                |

| Thermal resistance from junction to ambient                                              | R <sub>THJA_SOIC8</sub> | JEDEC 1s0p board, no air<br>flow                                         |                | 150                         | K/W            |

|                                                                                          | R <sub>thja_qfn20</sub> | JEDEC 1s0p board, no air flow                                            |                | 50                          | K/W            |

| Junction temperature                                                                     | TJ                      |                                                                          | -40            | 150                         | °C             |

| Storage temperature                                                                      | T <sub>STG</sub>        |                                                                          | -55            | 150                         | °C             |

Table 1: Absolute maximum ratings

LIN System Basis ICs Datasheet

## 3.1. DC Characteristics

Unless otherwise specified all values in the following tables are valid for  $V_s = 5$  to 27V and  $T_{AMB} = -40$  to  $125^{\circ}$ C. All voltages are referenced to ground (GND), positive currents flow into the IC. For MLX80031/51 apply: RTG connected to VCC.

#### Table 2: Voltage Regulator and Reset Unit

|        | Parameter                         | Symbol                | Condition                                                                                                                                                                                 | Min  | Тур | Max                    | Unit | <b>T</b> <sup>[1]</sup> |

|--------|-----------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------------------------|------|-------------------------|

| Supply | Voltage Pin VS                    |                       |                                                                                                                                                                                           |      |     |                        |      |                         |

|        | Nominal DC operating voltage      | Vs                    |                                                                                                                                                                                           | 5    |     | 27                     | V    | Α                       |

| 1.01   | Vs under voltage reset            | VSUVR_OFF             | Vs ramp up                                                                                                                                                                                | 4.1  |     | 5.0                    | V    | А                       |

| 1.02   | Vs under voltage reset            | VSUVR_ON              | Vs ramp down                                                                                                                                                                              | 3.7  |     | 4.8                    | V    | А                       |

| 1.03   | Vs under voltage reset hysteresis | V <sub>SUVR_HYS</sub> | VSUVR_OFF - VSUVR_ON                                                                                                                                                                      | 0.04 | 0.3 | 0.7                    | V    | A                       |

| Suppl  | y currents MLX80030, MLX800       | 50                    |                                                                                                                                                                                           |      |     |                        |      |                         |

| 2.00   | Supply current, normal mode       | Ivs_nor               | $V_S \leq 14V,  V_{EN} > 2V$ . LIN recessive, no load at VCC                                                                                                                              | 400  | 750 | 1500                   | μA   | A                       |

| 2.01   | Supply current, sleep mode        | Ivs_sleep             | $V_S \leq 14V$ $T_A = -40 \ ^{\circ}\text{C}$ $T_A = 25 \ ^{\circ}\text{C}$ $T_A \leq 85 \ ^{\circ}\text{C}$ $T_A \leq 125 \ ^{\circ}\text{C}$                                            |      | 15  | 30<br>20<br>30<br>45   | μΑ   | A                       |

| 2.02   | Supply current, silent mode       | I <sub>VS_sil</sub>   | $V_S \leq$ 14V, LIN recessive no load at VCC $T_A = -40 \ ^\circ C \\ T_A = 25 \ ^\circ C \\ T_A \leq 85 \ ^\circ C \\ T_A \leq 125 \ ^\circ C \\ T_A \leq 125 \ ^\circ C \\ \end{array}$ |      | 65  | 85<br>95<br>100<br>125 | μΑ   | A                       |

| Suppl  | y currents MLX80031, MLX800       | 51                    |                                                                                                                                                                                           |      |     |                        | 1    |                         |

| 2.00   | Supply current, normal mode       | I <sub>VS_nor</sub>   | $V_S \le 14V$ , $V_{EN} > 2V$ , $RB_{WD} = 60k$<br>LIN recessive, no load at VCC                                                                                                          | 400  | 750 | 1500                   | μΑ   | A                       |

| 2.01   | Supply current, sleep mode        | Ivs_sleep             | $V_S \leq 14V$ $\begin{array}{c} T_A = -40 \ ^\circ C \\ T_A = 25 \ ^\circ C \\ T_A \leq 85 \ ^\circ C \\ T_A \leq 125 \ ^\circ C \end{array}$                                            |      | 15  | 30<br>20<br>30<br>45   | μΑ   | A                       |

| 2.02   | Supply current, silent mode       | I <sub>VS_sil</sub>   | $V_S \leq$ 14V, LIN recessive no load at VCC $T_A = -40 \ ^\circ C \\ T_A = 25 \ ^\circ C \\ T_A \leq 85 \ ^\circ C \\ T_A \leq 125 \ ^\circ C \end{cases}$                               |      | 65  | 85<br>95<br>100<br>125 | μΑ   | A                       |

LIN System Basis ICs Datasheet

### Voltage Regulator Pin VCC

### MLX80050, MLX80051 (RTG connected to VCC)

| MLX80 | 050, MLX80051 (RTG connect                                     | ed to VCC)           |                                                                                                                                                                     |                |      |                |    |   |

|-------|----------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|----------------|----|---|

| 3.01  | Output voltage VCC                                             | V <sub>CCn5</sub>    | $\begin{array}{l} 6V \leq V_S \leq 18V \\ 1mA \leq I_{LOAD} \leq 70mA \\ T_A = 25^\circ C \\ T_A = -40^\circ C \text{ to } 125^\circ C \end{array}$                 | 4.90<br>4.85   | 5.0  | 5.10<br>5.15   | V  | A |

|       | Output voltage VCC under<br>disturbances functional state A    | V <sub>CCndis5</sub> | $\begin{array}{l} 6V \leq V_S \leq 18V, \ T_A = \\ 25^{\circ}C \\ R_{LOAD} = 330 \ \Omega \end{array}$                                                              | 4.75           |      | 5.25           | V  | С |

| 3.02  |                                                                | V <sub>D10_5</sub>   | $V_{\rm S} > 4V$ , $I_{\rm VCC}$ = 10mA                                                                                                                             |                | 75   | 120            | mV | С |

| 3.03  | Drop-out voltage [2]                                           | V <sub>D30_5</sub>   | $V_{\rm S} > 4V$ , $I_{\rm VCC}$ = 30mA                                                                                                                             |                | 220  | 350            | mV | С |

| 3.04  |                                                                | V <sub>D70_5</sub>   | $V_{\text{S}} > 4V$ , $I_{\text{VCC}}$ = 70mA                                                                                                                       |                | 500  | 800            | mV | С |

| 3.05  | Line regulation                                                | V <sub>LNR5</sub>    | $\begin{array}{l} 6V \leq V_S \leq 18V, \ I_{VCC} = \\ 30mA \\ 6V \leq V_S \leq 18V, \ I_{VCC} = \\ 70mA \end{array}$                                               |                |      | 20<br>100      | mV | A |

| 3.06  |                                                                | VLDR10_5             | $1 \text{ mA} < I_{LOAD} < 10 \text{ mA}$                                                                                                                           |                |      | 50             | mV | Α |

| 3.07  | Load regulation                                                | VLDR30_5             | 1 mA < I <sub>LOAD</sub> < 30 mA                                                                                                                                    |                |      | 90             | mV | Α |

| 3.08  |                                                                | V <sub>LDR70_5</sub> | 1 mA < I <sub>LOAD</sub> < 70 mA                                                                                                                                    |                |      | 150            | mV | Α |

| 3.09  | Output current limitation [3]                                  | IVCCLIM_5            | $V_{S} > 6V$ $T_{A} = -40 \ ^{\circ}C$ $25 \ ^{\circ}C \le T_{A} \le 125 \ ^{\circ}C$                                                                               | -135<br>-150   | -110 | -75<br>-80     | mA | A |

| 3.10  | Load capacity                                                  | CLOAD                |                                                                                                                                                                     | 2.2            | 22   |                | μF | D |

| MLX80 | 030, MLX80031 (RTG connect                                     | ed to VCC)           |                                                                                                                                                                     |                |      |                |    |   |

| 3.01  | Output voltage VCC                                             | V <sub>CCn3</sub>    | $\begin{array}{l} 4 \ V \leq V_S \leq 18 \ V \\ 1m \ A \leq I_{LOAD} \leq 70 \ mA \\ T_A = 25 \ ^\circ C \\ T_A = -40 \ ^\circ C \ to \ 125 \ ^\circ C \end{array}$ | 3.234<br>3.201 | 3.3  | 3.366<br>3.399 | V  | A |

|       | Output voltage VCC under<br>disturbances functional state<br>A | V <sub>CCndis3</sub> | $\begin{array}{l} 6 \mbox{ V} \leq V_S \leq 18 \mbox{ V}, \mbox{ T}_A = \\ 25 \mbox{ °C} \\ R_{LOAD} = 330 \ \Omega \end{array}$                                    | 3.135          |      | 3.465          | V  | С |

| 3.02  | Drop-out voltage [2]                                           | V <sub>D10_3</sub>   | $V_{\rm S} > 3~V$ , $I_{\rm VCC}$ = 10 mA                                                                                                                           |                |      | 100            | mV | С |

| 3.03  |                                                                | V <sub>D30_3</sub>   | $V_{\text{S}} > 3 \; \text{V}$ , $I_{\text{VCC}}$ = 30 mA                                                                                                           |                |      | 300            | mV | С |

| 3.04  |                                                                | V <sub>D70_3</sub>   | $V_{\text{S}} > 3 \; \text{V}$ , $I_{\text{VCC}}$ = 70 mA                                                                                                           |                |      | 700            | mV | С |

| 3.05  | Line regulation                                                | V <sub>LNR_3</sub>   | $5~V \leq V_S \leq 18~V,~I_{VCC}$ = 30mA $5V \leq V_S \leq 18V,~I_{VCC}$ = 70mA                                                                                     |                |      | 20<br>100      | mV | A |

| 3.06  | Load regulation                                                | VLDR10_3             | $1 \text{ mA} < I_{LOAD} < 10 \text{ mA}$                                                                                                                           |                |      | 50             | mV | Α |

| 3.07  |                                                                | VLDR30_3             | $1 \text{ mA} < I_{LOAD} < 30 \text{ mA}$                                                                                                                           |                |      | 90             | mV | Α |

| 3.08  |                                                                | VLDR70_3             | $1 \text{ mA} < I_{LOAD} < 70 \text{ mA}$                                                                                                                           |                |      | 150            | mV | A |

| 3.09  | Output current limitation [3]                                  | Ivcclim_3            | V <sub>S</sub> > 4 V<br>T <sub>A</sub> = -40 °C                                                                                                                     | -135           | -110 | -75            | mA | A |

LIN System Basis ICs Datasheet

|      |               |       | $25~^\circ\text{C} \le T_A~\le 125~^\circ\text{C}$ | -150 |    | -80 |    |   |

|------|---------------|-------|----------------------------------------------------|------|----|-----|----|---|

| 3.10 | Load capacity | CLOAD |                                                    | 2.2  | 22 |     | μF | D |

| Output  | t Pin NRES                                                                     |                             |                                     |                    |      |                      |    |   |

|---------|--------------------------------------------------------------------------------|-----------------------------|-------------------------------------|--------------------|------|----------------------|----|---|

| 4.01    | Output voltage low                                                             | Vol_nres                    | I <sub>NRES</sub> = 1 mA            |                    |      | 0.25                 | V  | A |

| 4.02    | Leakage current low                                                            | I <sub>leak_RxD</sub>       | V <sub>NRES</sub> = 0 V             | -5                 |      | 5                    | μΑ | А |

| 4.03    | Leakage current high                                                           | Ileak_RxD                   | V <sub>NRES</sub> = V <sub>CC</sub> | -5                 |      | 5                    | μΑ | A |

|         | Output voltage high NRES<br>under disturbances to fulfil<br>functional state A | V <sub>OH_NRES</sub>        | R <sub>load</sub> = 2.7 k to VCC    | V <sub>CC</sub> -1 |      |                      | V  | С |

| MLX8    | 0050, MLX80051                                                                 |                             |                                     |                    |      |                      |    |   |

| 5.01    | VCC reset threshold on NRES pin                                                | V <sub>RES5V</sub>          | t > tr                              | 3.9                | 4.10 | 4.3                  | V  | A |

| 5.02    | Vres Hysteresis<br>Vreshys =  Vres(on) - Vres(off)                             | Vreshys5v                   |                                     |                    |      | 200                  | mV | С |

| MLX8    | 0030, MLX80031                                                                 |                             |                                     |                    |      |                      |    |   |

| 5.01    | VCC reset threshold on NRES pin                                                | V <sub>RES3V</sub>          | t > trr                             | 2.75               | 2.95 | 3.15                 | V  | A |

| 5.02    | Vres H <b>ysteresis</b><br>Vreshys =  Vres(on) – Vres(off)                     | V <sub>RESHYS3V</sub>       |                                     |                    |      | 100                  | mV | С |

| nput P  | Pin EN                                                                         |                             |                                     |                    |      |                      |    |   |

| 6.01    | Input voltage low                                                              | VIL_EN                      |                                     |                    |      | 0.8                  | V  | A |

| 6.02    | Input voltage high                                                             | $V_{\text{IH}\_\text{EN}}$  |                                     | 2.0                |      |                      | V  | A |

| 6.03    | Hysteresis                                                                     | $V_{\text{HYS}\_\text{EN}}$ |                                     | 50                 | 100  | 700                  | mV | С |

| 6.04    | Pull-down resistor                                                             | $R_{\text{pd}\_\text{EN}}$  | V <sub>EN</sub> =VCC                | 50                 | 125  | 250                  | kΩ | A |

| nput P  | Pin WAKE (MLX80031, MLX8005                                                    | 51)                         |                                     |                    |      |                      |    |   |

| 7.01    | High level input voltage                                                       | VIH_WAKE                    | Sleep mode                          | Vs-1V              |      |                      | V  | A |

| 7.02    | Low level input voltage                                                        | VIL_WAKE                    | Sleep mode                          |                    |      | Vs-3.3V              | V  | A |

| 7.03    | Pull up current WAKE                                                           | I <sub>WAKE_PU</sub>        | Normal & sleep                      | -30                | -15  | -1                   | μΑ | A |

| 7.04    | Leakage current WAKE high                                                      | I <sub>WAKE_lk</sub>        | V <sub>S</sub> = 18V                | -5                 |      | 5                    | μΑ | A |

| Input   | Pin KL15 (MLX80031, MLX8005                                                    | 1)                          |                                     |                    |      |                      |    |   |

| 8.01    | High level input voltage                                                       | V <sub>IH_KL15</sub>        | Rv = 50kΩ                           | 4                  |      | V <sub>S</sub> +0.3V | V  | A |

| 8.02    | Low level input voltage                                                        | VIL_KL15                    | Rv = 50kΩ                           | -1                 |      | 2                    | V  | A |

| 8.03    | Pull down current KL15                                                         | I <sub>KL15_PD</sub>        |                                     |                    | 30   | 65                   | μΑ | A |

| Input I | Pin MODE (MLX80031, MLX800                                                     | )51)                        |                                     |                    |      |                      |    |   |

| 23.01   | Input voltage low                                                              | VIL_MODE                    |                                     |                    |      | 0.8                  | V  | A |

| 23.02   | Input voltage high                                                             | VIH_MODE                    |                                     | 2.0                |      |                      | V  | A |

LIN System Basis ICs Datasheet

| 23.03 | Hysteresis         | V <sub>HYS_MODE</sub>         |                         | 50  | 100 | 600 | mV | С |

|-------|--------------------|-------------------------------|-------------------------|-----|-----|-----|----|---|

| 23.04 | Pull-down resistor | $R_{\text{pd}_{\text{MODE}}}$ | V <sub>MODE</sub> = VCC | 200 |     | 600 | kΩ | А |

| Input P | in NWDI (MLX80031, MLX8005                                                 | 51)                    |                                          |     |     |     |    |   |

|---------|----------------------------------------------------------------------------|------------------------|------------------------------------------|-----|-----|-----|----|---|

| 9.01    | Input voltage low                                                          | VIL_NWDI               |                                          |     |     | 0.8 | V  | А |

| 9.02    | Input voltage high                                                         | VIH_NWDI               |                                          | 2.0 |     |     | V  | А |

| 9.03    | Hysteresis                                                                 | VHYS_NWDI              |                                          | 50  | 100 | 600 | mV | С |

| 9.04    | Pull-up resistor to VCC                                                    | R <sub>pu_NWDI</sub>   | VN <sub>WDI</sub> = 0V                   | 125 | 250 | 375 | kΩ | А |

| 9.05    | Min low pulse width                                                        | Tminlow_NWDI           | one WD_OSC clock period                  | 1   |     |     | 1  | D |

| Watcho  | dog Oscillator pin RBWD (MLX                                               | 30031, MLX             | 80051)                                   |     |     |     |    |   |

| 10.01   | Voltage at RB <sub>WD</sub>                                                | $V_{RBwd}$             | Ιουτ = -50 μΑ                            |     | 1.2 |     | V  | А |

| 10.02   | Range of RB <sub>WD</sub> resistance                                       | RBwd                   |                                          | 20  |     | 60  | kΩ | В |

| 10.03   | RB <sub>WD</sub> short resistance thresh-<br>old to enable fail-safe state | RBwdsh                 | see paragraph 7.3                        | 0   |     | 330 | Ω  | В |

| Output  | INH (MLX80031, MLX80051)                                                   |                        |                                          |     |     |     |    |   |

| 11.01   | ON Resistance                                                              | Ron_inh                | V <sub>S</sub> = 12V                     |     | 20  | 60  | Ω  | А |

| 11.02   | Leakage current INH high                                                   | IleakH_INH             | Sleep Mode, $V_{INH}$ = 18V, $V_S$ = 18V | -5  |     | 5   | μA | А |

| 11.03   | Leakage current INH low                                                    | I <sub>leakL_INH</sub> | Sleep Mode, $V_{INH}$ = 0V, $V_S$ = 18V  | -5  |     | 5   | μA | А |

| Therma  | al Protection                                                              |                        |                                          |     |     |     |    |   |

|         | Thermal shutdown                                                           | TJSHD                  |                                          | 155 | 170 | 190 | °C | D |

|         | Thermal hysteresis                                                         | TJHYS                  |                                          |     | 10  | 30  | °C | D |

#### Notes:

A = 100% serial test, B = Operating parameter, C = characterization data, D = Value guaranteed by design

[2] The nominal VCC voltage is measured at VSUP = 12V. If the VCC voltage is 100mV below its nominal value then the voltage drop is VD = VSUP – VCC

[3] Functionality range of current limitation at silent mode is limited by reset threshold VRES. Below them the IC change to normal mode.

Validity for IVCC\_MAXsil: VCCn (min) ≤ VCC ≤ VRES

LIN System Basis ICs Datasheet

### Table 3: LIN DC Characteristics

| Param  | eter                                                                                                            | Symbol                  | Condition                                                                                                                       | Min                  | Тур                 | Max                  | Unit | <b>T</b> [1] |

|--------|-----------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|----------------------|------|--------------|

| Genera | al                                                                                                              |                         |                                                                                                                                 |                      | 1                   |                      |      |              |

| 12.01  | Pull up current LIN (recessive)                                                                                 | IINLINpu                | $V_{LIN}$ = 18 V, $V_{S}$ = 6V                                                                                                  |                      |                     | 80                   | μΑ   | А            |

| 12.02  | Pull up resistor LIN                                                                                            | RLINpu                  | $V_S$ = 12V, $V_{LIN}$ = 0V                                                                                                     | 20                   | 30                  | 60                   | kΩ   | А            |

| 12.03  | Reverse current LIN<br>(dominant)                                                                               | I <sub>INLINdom</sub>   | $V_S$ = 12V, $V_{LIN}$ = 0V                                                                                                     | -400                 |                     |                      | μΑ   | А            |

| 12.04  | Reverse current LIN<br>(recessive)                                                                              | I <sub>INLINrec</sub>   | $\begin{array}{l} V_{LIN} \geq V_{S_i} \; 8V \leq \; V_{LIN} \leq \\ 18V, \\ 8V \leq \; V_S \leq 18V \end{array} \label{eq:VS}$ | 0                    |                     | 23                   | μA   | A            |

| 12.05  | Reverse current LIN<br>(loss of battery)                                                                        | INLIN_lob               | $\begin{array}{l} V_{\text{S}}  \text{=}  0  V,  0  V \leq \ V_{\text{LIN}} \leq \\ 18  V \end{array}$                          | 0                    |                     | 23                   | μA   | А            |

| 12.06  | Reverse current LIN<br>(loss of ground)                                                                         | I <sub>INLIN_log</sub>  | $\begin{array}{l} V_{\text{S}}\text{=}~12\text{V},~0\text{V} \leq ~V_{\text{LIN}} \leq \\ 18\text{V} \end{array}$               | -10                  |                     | 50                   | μA   | А            |

|        | Voltage drop serial Diode                                                                                       | $V_{\text{SerDiode}}$   |                                                                                                                                 | 0.4                  | 0.7                 | 1.0                  | V    | D            |

|        | Battery Shift                                                                                                   | $V_{Shift\_BAT}$        | related to VS                                                                                                                   | 0                    |                     | 11.5                 | %    | D            |

|        | Ground Shift                                                                                                    | V <sub>Shift_GND</sub>  | related to VS                                                                                                                   | 0                    |                     | 11.5                 | %    | D            |

|        | Ground-Battery shift difference                                                                                 | V <sub>Shift_diff</sub> | related to VS                                                                                                                   | 0                    |                     | 8                    | %    | D            |

| Receiv | er                                                                                                              |                         |                                                                                                                                 |                      |                     |                      |      |              |

| 12.07  | Receiver dominant voltage                                                                                       | $V_{BUSdom}$            |                                                                                                                                 |                      |                     | 0.4*Vs               |      | А            |

| 12.07  | Receiver recessive voltage                                                                                      | VBUSrec                 |                                                                                                                                 | 0.6*Vs               |                     |                      |      | А            |

| 12.08  | Centre point of receiver<br>threshold V <sub>thr_cnt</sub> =<br>(V <sub>thr_rec</sub> +V <sub>thr_dom</sub> )/2 | V <sub>thr_cnt</sub>    | $7.0~V \leq V_S \leq 18~V$                                                                                                      | 0.475*V <sub>S</sub> | 0.5*V <sub>S</sub>  | 0.525*V <sub>S</sub> | V    | A            |

| 12.09  | Receiver Hysteresis<br>V <sub>hys</sub> = V <sub>thr_rec</sub> -V <sub>thr_dom</sub>                            | V <sub>hys</sub>        |                                                                                                                                 |                      | 0.15*V <sub>S</sub> | 0.175*V <sub>S</sub> |      | A            |

| Transn | nitter                                                                                                          |                         |                                                                                                                                 |                      |                     |                      |      |              |

|        |                                                                                                                 |                         | $R_{\text{load}} = 500 \Omega,  V_S = 5 V$                                                                                      | 0                    |                     | 1.2                  |      | D            |

| 12.10  | Transmitter dominant voltage                                                                                    | Volbus                  | $R_{load}$ = 500 $\Omega$ , V <sub>S</sub> >= 7V                                                                                | 0                    |                     | 0.2*Vs               | V    | А            |

| 12.11  | Current limitation LIN                                                                                          | ILIM                    | $V_{LIN} = V_S$ , $TxD = 0V$                                                                                                    | 40                   | 120                 | 200                  | mA   | А            |

| 12.12  | Transmitter recessive voltage                                                                                   | Voh <sub>BUS</sub>      | No load, $V_{EN} = 0/5V$ ,<br>VTxD = 5V                                                                                         | 0.8*V <sub>S</sub>   |                     | Vs                   | V    | А            |

| Input/O | Input/Output Pin TxD    |                             |                       |     |     |     |    |   |  |

|---------|-------------------------|-----------------------------|-----------------------|-----|-----|-----|----|---|--|

| 13.01   | Input voltage low TxD   | $V_{\text{IL}\_\text{TxD}}$ | rising                |     |     | 0.8 | V  | А |  |

| 13.02   | Input voltage high TxD  | VIH_TxD                     |                       | 2   |     |     | V  | А |  |

| 13.03   | Hysteresis              | V <sub>HYS_TxD</sub>        |                       | 50  |     | 700 | mV | С |  |

| 13.04   | Pull-up resistor to VCC | R <sub>pu_TxD</sub>         | V <sub>TxD</sub> = 0V | 125 | 250 | 375 | kΩ | А |  |

LIN System Basis ICs Datasheet

| 13.06  | Low level output current                                                      | I <sub>OL_TxD</sub>   | local wake-up request; standby mode; $V_{TxD} = 0.4V$ | 1.5   |   |     | mA | A |

|--------|-------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------|-------|---|-----|----|---|

| Output | Pin RxD                                                                       |                       |                                                       |       |   |     |    |   |

| 14.01  | Output voltage low RxD                                                        | Vol_rxd               | I <sub>RxD</sub> = 2 mA                               |       |   | 0.6 | V  | А |

| 14.02  | Pull-up resistor to VCC                                                       | $R_{pu\_RxD}$         | $V_{RxD} = 0V$                                        | 3     | 5 | 7   | kΩ | А |

| 14.03  | Leakage current high                                                          | I <sub>leak_RxD</sub> | V <sub>RxD</sub> = VCC                                | -5    |   | 5   | μΑ | А |

|        | Output voltage high RxD<br>under disturbances to fulfil<br>functional state A | V <sub>OH_RxD</sub>   | R <sub>load</sub> = 2.7k to VCC                       | Vcc-1 |   |     | V  | С |

Notes:

A = 100% serial test, B = Operating parameter, C = characterization data, D = Value guaranteed by design

### 3.2. AC Characteristics

$6V \leq V_S \leq 27V,\,\text{-}40^\circ C \leq T_A \leq 125^\circ C,\,\text{RTG}$  connected to VCC, unless otherwise specified

| Table 4: AC Characteristics |                                |                  |                                  |      |       |      |        |                         |  |

|-----------------------------|--------------------------------|------------------|----------------------------------|------|-------|------|--------|-------------------------|--|

|                             | Parameter                      | Symbol           | Condition                        | Min  | Тур   | Мах  | Unit   | <b>T</b> <sup>[1]</sup> |  |

| Reset p                     | arameter on NRES               |                  |                                  |      |       |      |        |                         |  |

| 16.01                       | Reset time                     | t <sub>Res</sub> | V <sub>S</sub> = 14V             | 2.5  | 4     | 5.5  | ms     | А                       |  |

| 16.02                       | Reset rising time              | trr              | V <sub>S</sub> = 14V             | 3.0  | 6.5   | 12   | μs     | А                       |  |

| Watchd                      | og parameter on NRES (MLX80031 | , MLX80051)      |                                  |      |       |      |        |                         |  |

| 17.01                       | Watehdar Opeillater Davied     | twposc20         | $RB_{WD}$ = 20k $\Omega \pm 1\%$ | 7.0  | 8.05  | 9.0  | μs     | А                       |  |

| 17.02                       | Watchdog-Oscillator Period     | twposc60         | $RB_{WD}$ = 60k $\Omega$ ±1%     | 19.0 | 23.05 | 25.2 | μs     | А                       |  |

|                             | Watchdog Close Window          | tcw              | tCW = cycles *<br>tWDOSC         |      | 1053  |      | cycles | D                       |  |

|                             | Watchdog Open Window           | tow              | tOW = cycles *<br>tWDOSC         |      | 1105  |      | cycles | D                       |  |

| 17.05                       | Watchdog Reset Low Time        | twDres           |                                  | 3    | 4     | 5    | ms     | А                       |  |

|                             | Watchdog Lead Window           | <b>t</b> lot     | tOWS = cycles *<br>tWDOSC        |      | 7895  |      | cycles | D                       |  |

| 17.06                       | Watchdog Safety Oscillator     | twDsafety        | RBWD open /<br>RBWD gnd          | 30   | 50    | 75   | μs     | А                       |  |

**LIN System Basis ICs** Datasheet

| Wake-u  | p and Mode Control                                           |                                            |                                                              |     |     |     |    |   |

|---------|--------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|-----|-----|-----|----|---|

| 18.01   | Remote Wake-up filter time                                   | twu_remote                                 |                                                              | 30  | 70  | 150 | μs | А |

| 18.02   | Wake-up filter time on WAKE<br>(only MLX80051,MLX80031)      | t <sub>wu_WAKE</sub>                       | Sleep or Silent<br>Mode,<br>WAKE falling edge                | 10  |     | 50  | μs | А |

| 18.03   | Wake-up filter time on KL15<br>(only MLX80051,MLX80031)      | twu_KL15                                   | Sleep or Silent<br>Mode,<br>KL15 rising edge                 | 80  | 168 | 250 | μs | A |

| 18.04   | Propagation delay from Normal<br>Mode to Sleep Mode via EN   | tpd_sleep                                  | V <sub>EN</sub> = 0V                                         | 5   | 15  | 20  | μs | А |

| 18.05   | Propagation delay from Standby<br>Mode to Normal Mode via EN | tpd_norm                                   | V <sub>EN</sub> = 5V                                         | 5   | 15  | 20  | μs | А |

| 18.06   | Propagation delay from Silent<br>Mode to Normal Mode via EN  | t <sub>pd_sil_n</sub>                      | $V_{EN}$ = 5V<br>Silicon Revision C                          | 5   | 15  | 40  | μs | А |

| 18.07   | Propagation delay: go to silent mode after EN=H/L            | $t_{pd\_sil}$                              | check falling edge<br>on RBwd, EN = 0V<br>Silicon Revision C |     |     | 20  | μs | A |

|         | Setup time TxD to EN for low slew mode                       | tset_TxD_EN                                |                                                              | 5   |     |     | μs | В |

|         | Hold time TxD after EN for low slew mode                     | thold_TxD_EN                               |                                                              | 20  |     |     | μs | В |

|         | TXD hold time for mode change                                | thold_TxD_MCH                              |                                                              |     |     | 2   | μs | D |

| 18.08   | Debouncing time EN                                           | tdeb_EN                                    |                                                              | 2   | 5   | 20  | μs | А |

| 18.09   | TxD dominant time out                                        | t <sub>TxD_to</sub>                        | Normal Mode,<br>V <sub>TxD</sub> = 0V                        | 27  |     | 60  | ms | А |

| 18.10   | Standby time out                                             | t <sub>sby_to</sub>                        | Standby Mode,<br>V <sub>EN</sub> = 0V                        | 150 |     | 500 | ms | А |

| 18.11   | Wake up time vs. EN                                          | t <sub>wu_EN</sub>                         | Wake form sleep<br>via EN=L/H                                | 2   | 5   | 20  | μs | А |

| General | LIN Parameter                                                |                                            |                                                              |     |     |     |    |   |

| 19.01   | Receiver propagation delay<br>LIN -> RxD                     | t <sub>dr_RxD</sub><br>t <sub>df_RxD</sub> | $C_{L(RXD)}$ = 50 pF                                         |     |     | 6   | μs | А |

| 19.02   | Symmetry prop. delay LIN->RxD                                | t <sub>dsym_RxD</sub>                      | t <sub>dr_RXD</sub> - t <sub>df_RXD</sub>                    | -2  |     | 2   | μs | А |

| 19.03   | Receiver debouncing time                                     | t <sub>deb_LIN</sub>                       |                                                              | 1.5 | 2.8 | 4.0 | μs | D |

LIN System Basis ICs Datasheet

| 19.04                                                                         | slew rate rising edge LIN                                                                                                                                                                                                                                                                                                                                                                                                                | dV/dTrise                                                                                                                                                                       | Normal Mode<br>LIN-Load: 1kΩ/1nF                                                                                                   | 1.0               | 1.5         | 2.5                            | V/µs                 | С                |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|--------------------------------|----------------------|------------------|

| 19.05                                                                         | slew rate falling edge LIN                                                                                                                                                                                                                                                                                                                                                                                                               | dV/dTfall                                                                                                                                                                       |                                                                                                                                    | -2.5              | -1.5        | -1.0                           | V/µs                 | С                |

| 19.06                                                                         | slew rate rising edge LIN                                                                                                                                                                                                                                                                                                                                                                                                                | dV/dTrise                                                                                                                                                                       | Low Slew Mode                                                                                                                      | 0.3               | 0.8         | 1.3                            | V/µs                 | С                |

| 19.07                                                                         | slew rate falling edge LIN                                                                                                                                                                                                                                                                                                                                                                                                               | dV/dTfall                                                                                                                                                                       | LIN-Load: 1kΩ/1nF                                                                                                                  | -1.3              | -0.8        | -0.3                           | V/µs                 | С                |

|                                                                               | Internal capacity                                                                                                                                                                                                                                                                                                                                                                                                                        | C <sub>LIN</sub>                                                                                                                                                                | Pulse at LIN via<br>10kOhm with 0/10V;<br>VS = open                                                                                |                   | 25          | 35                             | pF                   | D                |

| LIN tran                                                                      | sceiver parameter according to LI                                                                                                                                                                                                                                                                                                                                                                                                        | N Physical La                                                                                                                                                                   | yer Spec. rev. 2.0, tabl                                                                                                           | e 3.4 (20kb       | it/s)       |                                |                      |                  |

| Conditio                                                                      | ns: Normal slew mode; V <sub>S</sub> =<br>TxD signal: t <sub>Bit</sub> = 50µs, t <sub>w</sub>                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                 |                                                                                                                                    | 2/6.8nF; 50       | 0Ω/10nF     |                                |                      |                  |

|                                                                               | Minimal recessive bit time                                                                                                                                                                                                                                                                                                                                                                                                               | t <sub>rec(min)</sub>                                                                                                                                                           |                                                                                                                                    | 40                | 50          | 58                             | μs                   |                  |

|                                                                               | Maximum recessive bit time                                                                                                                                                                                                                                                                                                                                                                                                               | trec(max)                                                                                                                                                                       |                                                                                                                                    | 40                | 50          | 58                             | μs                   |                  |

| 20.01                                                                         | Duty cycle 1                                                                                                                                                                                                                                                                                                                                                                                                                             | D1                                                                                                                                                                              | $D_1 = t_{rec(min)} / (2^*t_{Bit})$                                                                                                | 0.396             |             |                                |                      | А                |

| 20.02                                                                         | Duty cycle 2                                                                                                                                                                                                                                                                                                                                                                                                                             | D <sub>2</sub>                                                                                                                                                                  | $D_2 = t_{rec(max)} / (2^* t_{Bit})$                                                                                               |                   |             | 0.581                          |                      | А                |

| Transce                                                                       | eiver parameter according to LIN P                                                                                                                                                                                                                                                                                                                                                                                                       | hysical Layer                                                                                                                                                                   | Spec. rev. 2.0, table 3.                                                                                                           | 4 (10.4kbit/      | /s)         |                                |                      |                  |

| - Tunicou                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                 |                                                                                                                                    |                   |             |                                |                      |                  |

| Conditio                                                                      | ns: Low slew mode; V <sub>S</sub> =7.0 <sup>v</sup><br>TxD signal: t <sub>Bit</sub> = 96µs, t <sub>w</sub>                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                 |                                                                                                                                    | .8nF; 500Ω        | /10nF       |                                |                      |                  |