#### **Features**

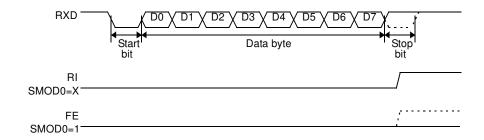

- 80C51 Core Architecture

- · 256 Bytes of On-chip RAM

- 1 KB of On-chip XRAM

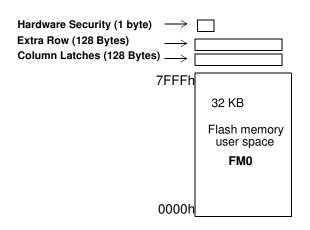

- 32 KB of On-chip Flash Memory

- Data Retention: 10 Years at 85 °C Read/Write Cycle: 10K

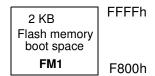

- · 2 KB of On-chip Flash for Bootloader

- 2 KB of On-chip EEPROM Read/Write Cycle: 100K

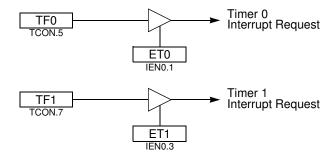

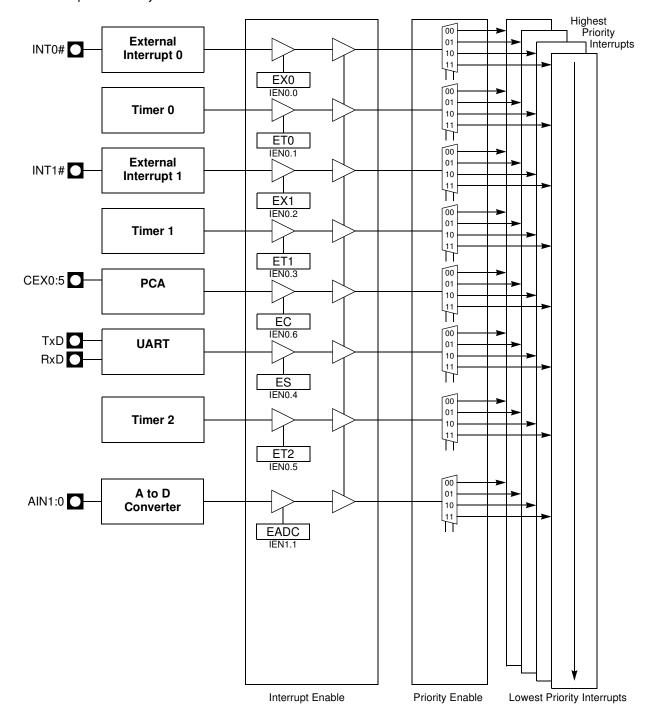

- 14-sources 4-level Interrupts

- Three 16-bit Timers/Counters

- Full Duplex UART Compatible 80C51

- Maximum Crystal Frequency 40 MHz, in X2 Mode, 20 MHz (CPU Core, 20 MHz)

- Five Ports: 32 + 2 Digital I/O Lines

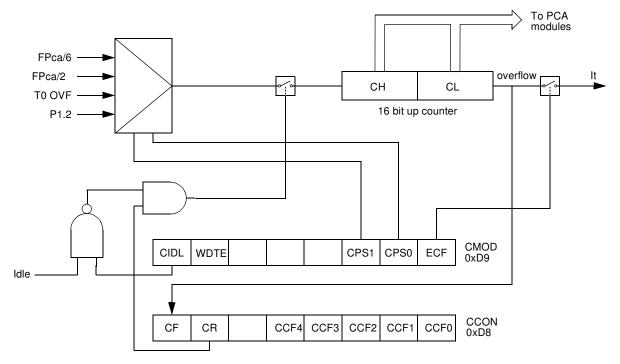

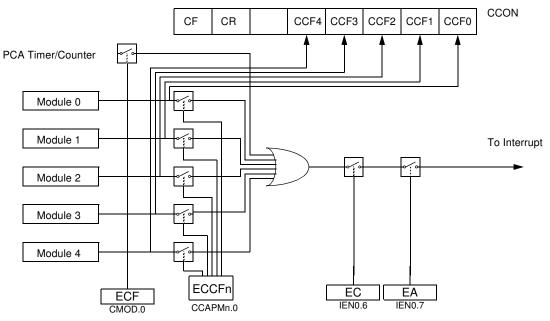

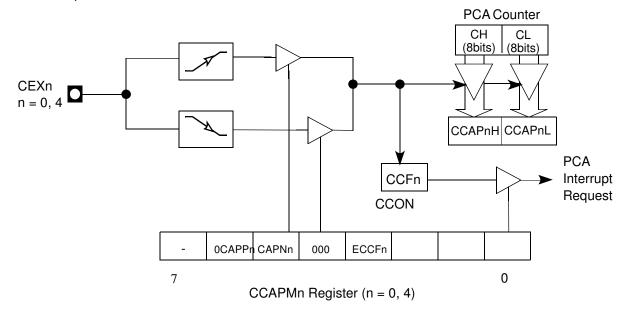

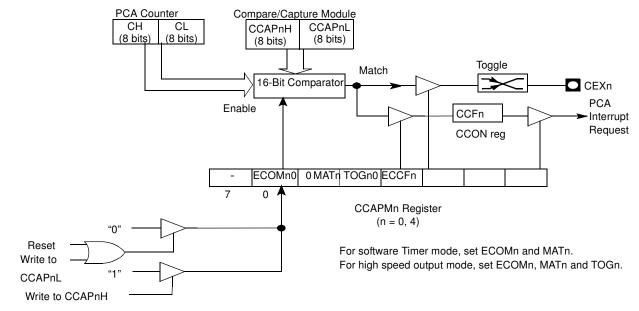

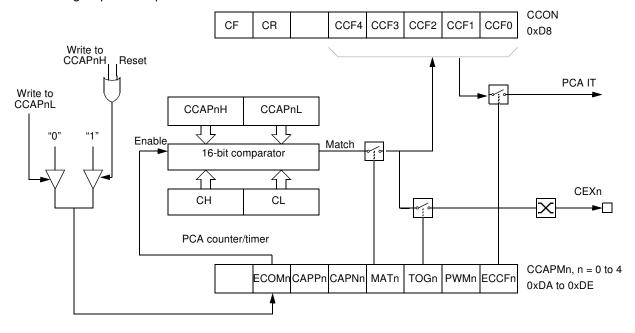

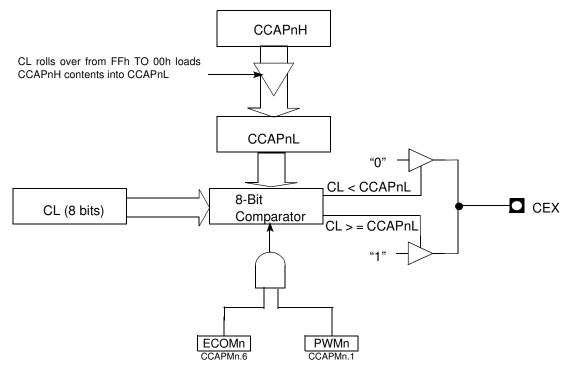

- · Five-channel 16-bit PCA with:

- PWM (8-bit)

- High-speed Output

- Timer and Edge Capture

- Double Data Pointer

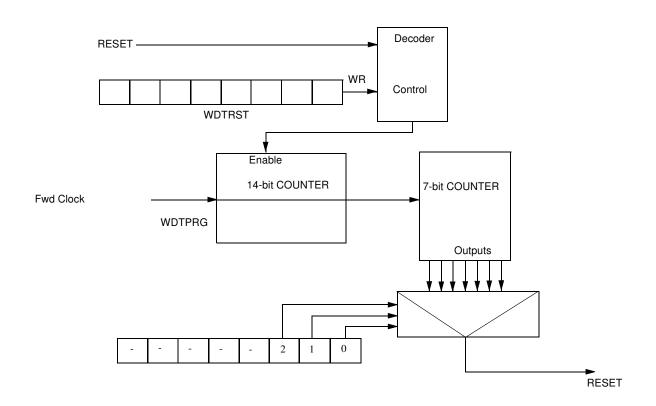

- 21-bit Watchdog Timer (7 Programmable Bits)

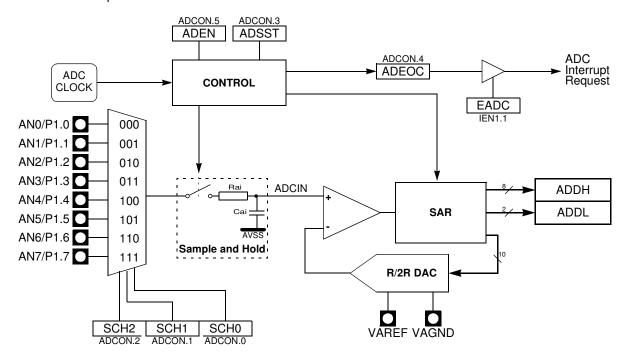

- 10-bit Resolution Analog to Digital Converter (ADC) with 8 Multiplexed Inputs

- · On-chip Emulation Logic (Enhanced Hook System)

- · Power Saving Modes:

- Idle Mode

- Power-down Mode

- · Power Supply: 3V to 5.5V

- Temperature Range: Industrial (-40° to +85°C)

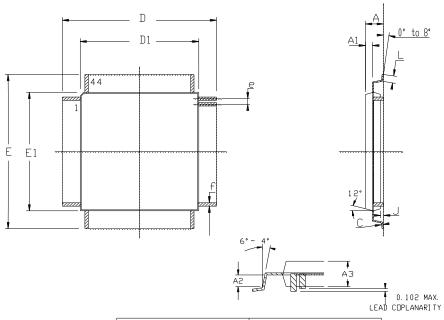

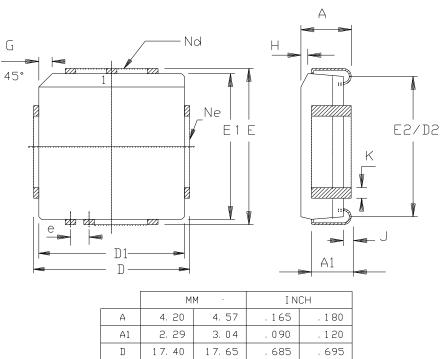

- Packages: VQFP44, PLCC44

## **Description**

The A/T89C51AC2 is a high performance Flash version of the 80C51 single chip 8-bit microcontrollers. It contains a 32 KB Flash memory block for program and data.

The 32 KB Flash memory can be programmed either in parallel mode or in serial mode with the ISP capability or with software. The programming voltage is internally generated from the standard VCC pin.

The A/T89C51AC2 retains all features of the 80C51 with 256 bytes of internal RAM, a 7-source 4-level interrupt controller and three timer/counters. In addition, the A/T89C51AC2 has a 10-bit A/D converter, a 2 KB Boot Flash memory, 2 KB EEPROM for data, a Programmable Counter Array, an XRAM of 1024 bytes, a Hardware Watch-Dog Timer, and a more versatile serial channel that facilitates multiprocessor communication (EUART). The fully static design of the A/T89C51AC2 reduces system power consumption by bringing the clock frequency down to any value, even DC, without loss of data.

The A/T89C51AC2 has two software-selectable modes of reduced activity and an 8-bit clock prescaler for further reduction in power consumption. In the idle mode the CPU is frozen while the peripherals and the interrupt system are still operating. In the Power-down mode the RAM is saved and all other functions are inoperative.

The added features of the A/T89C51AC2 make it more powerful for applications that need A/D conversion, pulse width modulation, high speed I/O and counting capabilities such as industrial control, consumer goods, alarms, motor control, among others. While remaining fully compatible with the 80C52, the T8C51AC2 offers a superset of this standard microcontroller. In X2 mode, a maximum external clock rate of 20 MHz reaches a 300 ns cycle time.

Enhanced 8-bit Microcontroller with 32 KB Flash Memory

AT89C51AC2 T89C51AC2

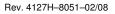

## **Block Diagram**

Notes: 1. 8 analog Inputs/8 Digital I/O

2. 2-Bit I/O Port

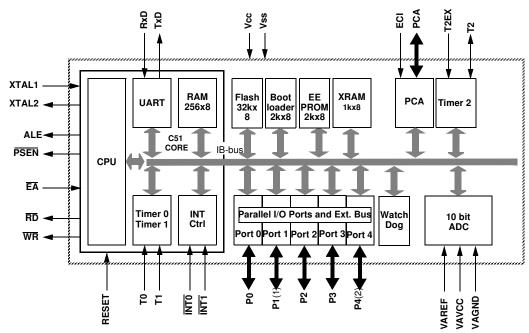

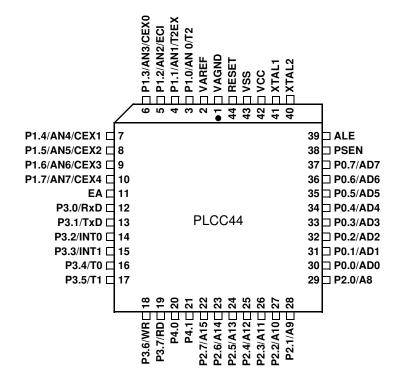

## **Pin Configuration**

Table 1. Pin Description

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | GND  | Circuit ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VCC      |      | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VAREF    |      | Reference Voltage for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VAGND    |      | Reference Ground for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P0.0:7   | I/O  | Port 0: Is an 8-bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in this state can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external Program and Data Memory. In this application it uses strong internal pull-ups when emitting 1's.  Port 0 also outputs the code Bytes during program validation. External pull-ups are required during program verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P1.0:7   | I/O  | Port 1:  Is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins can be used for digital input/output or as analog inputs for the Analog Digital Converter (ADC). Port 1 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 1 pins that are being pulled low externally will be the source of current (I <sub>IL</sub> . see section "Electrical Characteristic") because of the internal pull-ups. Port 1 pins are assigned to be used as analog inputs via the ADCCF register (in this case the internal pull-ups are disconnected).  As a secondary digital function, port 1 contains the Timer 2 external trigger and clock input; the PCA external clock input and the PCA module I/O.  P1.0/ANO/T2  Analog input channel 0,  External clock input for Timer/counter2.  P1.1/ANI/T2EX  Analog input channel 1,  Trigger input for Timer/counter2.  P1.2/AN2/ECI  Analog input channel 2,  PCA external clock input.  P1.3/AN3/CEX0  Analog input channel 3,  PCA module 0 Entry of input/PWM output.  P1.4/AN4/CEX1  Analog input channel 4,  PCA module 1 Entry of input/PWM output.  P1.5/ANS/CEX2  Analog input channel 5,  PCA module 2 Entry of input/PWM output.  P1.6/ANS/CEX3  Analog input channel 6,  PCA module 3 Entry of input/PWM output.  P1.7/AN7/CEX4  Analog input channel 6,  PCA module 4 Entry of input/PWM output.  P1.7/AN7/CEX4  Analog input channel 7,  PCA module 4 Entry of input/PWM output.  P1.7/AN7/CEX4  Analog input channel 7,  PCA module 4 Entry of input/PWM output.  P1.7/AN7/CEX4  Analog input channel 7,  PCA module 4 Entry of input/PWM output. |

| P2.0:7   | I/O  | Port 2: Is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 2 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , see section "Electrical Characteristic") because of the internal pull-ups. Port 2 emits the high-order address byte during accesses to the external Program Memory and during accesses to external Data Memory that uses 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1's. During accesses to external Data Memory that use 8 bit addresses (MOVX @Ri), Port 2 transmits the contents of the P2 special function register. It also receives high-order addresses and control signals during program validation. It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 1. Pin Description (Continued)

| Pin Name | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0:7   | I/O  | Port 3: Is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-up transistors and can be used as inputs in this state. As inputs, Port 3 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , see section "Electrical Characteristic") because of the internal pull-ups.  The output latch corresponding to a secondary function must be programmed to one for that function to operate (except for TxD and WR). The secondary functions are assigned to the pins of port 3 as follows: |

|          |      | P3.0/RxD: Receiver data input (asynchronous) or data input/output (synchronous) of the serial interface P3.1/TxD: Transmitter data output (asynchronous) or clock output (synchronous) of the serial interface                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |      | P3.2/NT0:  External interrupt 0 input/timer 0 gate control input P3.3/NT1:  External interrupt 1 input/timer 1 gate control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |      | P3.4/T0: Timer 0 counter input P3.5/T1: Timer 1 counter input P3.6/WR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |      | External Data Memory write strobe; latches the data byte from port 0 into the external data memory P3.7/RD: External Data Memory read strobe; Enables the external data memory. It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                             |

| P4.0:1   | I/O  | Port 4: Is an 2-bit bi-directional I/O port with internal pull-ups. Port 4 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 4 pins that are being pulled low externally will be a source of current (IIL, on the datasheet) because of the internal pull-up transistor. P4.0 P4.1: It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                      |

| RESET    | I/O  | Reset: A high level on this pin during two machine cycles while the oscillator is running resets the device. An internal pull-down resistor to VSS permits power-on reset using only an external capacitor to VCC.                                                                                                                                                                                                                                                                                                                                                                                              |

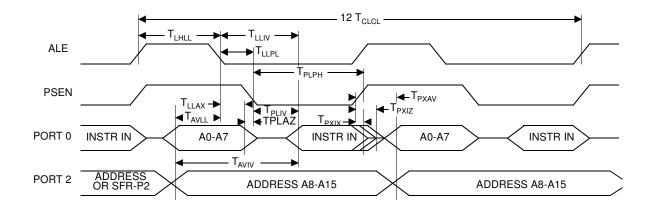

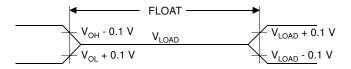

| ALE      | 0    | ALE: An Address Latch Enable output for latching the low byte of the address during accesses to the external memory. The ALE is activated every 1/6 oscillator periods (1/3 in X2 mode) except during an external data memory access. When instructions are executed from an internal Flash (EA = 1), ALE generation can be disabled by the software.                                                                                                                                                                                                                                                           |

| PSEN     | 0    | PSEN: The Program Store Enable output is a control signal that enables the external program memory of the bus during external fetch operations. It is activated twice each machine cycle during fetches from the external program memory. However, when executing from of the external program memory two activations of PSEN are skipped during each access to the external Data memory. The PSEN is not activated for internal fetches.                                                                                                                                                                       |

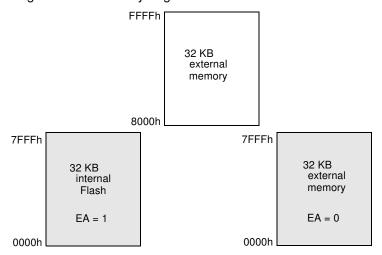

| EA       | I    | EA: When External Access is held at the high level, instructions are fetched from the internal Flash when the program counter is less then 8000H. When held at the low level, A/T89C51AC2 fetches all instructions from the external program memory.                                                                                                                                                                                                                                                                                                                                                            |

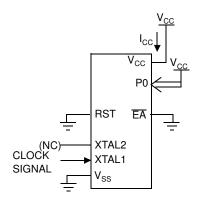

| XTAL1    | I    | XTAL1: Input of the inverting oscillator amplifier and input of the internal clock generator circuits. To drive the device from an external clock source, XTAL1 should be driven, while XTAL2 is left unconnected. To operate above a frequency of 16 MHz, a duty cycle of 50% should be maintained.                                                                                                                                                                                                                                                                                                            |

|          | İ    | XTAL2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

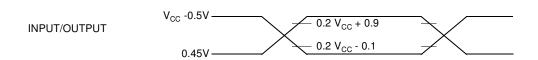

## I/O Configurations

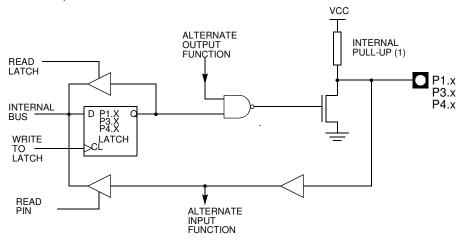

Each Port SFR operates via type-D latches, as illustrated in Figure 1 for Ports 3 and 4. A CPU "write to latch" signal initiates transfer of internal bus data into the type-D latch. A CPU "read latch" signal transfers the latched Q output onto the internal bus. Similarly, a "read pin" signal transfers the logical level of the Port pin. Some Port data instructions activate the "read latch" signal while others activate the "read pin" signal. Latch instructions are referred to as Read-Modify-Write instructions. Each I/O line may be independently programmed as input or output.

#### Port 1, Port 3 and Port 4

Figure 1 shows the structure of Ports 1 and 3, which have internal pull-ups. An external source can pull the pin low. Each Port pin can be configured either for general-purpose I/O or for its alternate input output function.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 1,3 or 4). To use a pin for general-purpose input, set the bit in the Px register. This turns off the output FET drive.

To configure a pin for its alternate function, set the bit in the Px register. When the latch is set, the "alternate output function" signal controls the output level (see Figure 1). The operation of Ports 1, 3 and 4 is discussed further in the "quasi-Bidirectional Port Operation" section.

Figure 1. Port 1, Port 3 and Port 4 Structure

Note: The internal pull-up can be disabled on P1 when analog function is selected.

#### Port 0 and Port 2

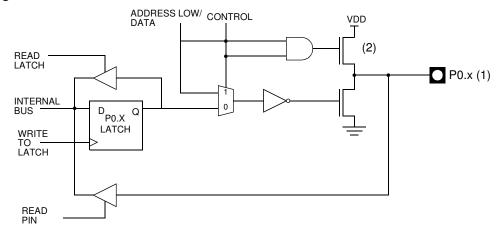

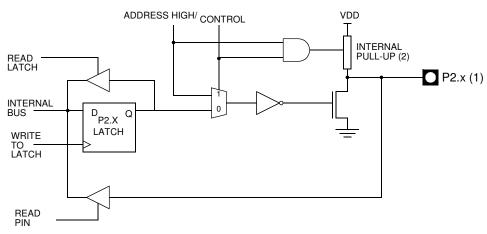

Ports 0 and 2 are used for general-purpose I/O or as the external address/data bus. Port 0, shown in Figure 3, differs from the other Ports in not having internal pull-ups. Figure 3 shows the structure of Port 2. An external source can pull a Port 2 pin low.

To use a pin for general-purpose output, set or clear the corresponding bit in the Px register (x = 0 or 2). To use a pin for general-purpose input, set the bit in the Px register to turn off the output driver FET.

Figure 2. Port 0 Structure

Notes: 1. Port 0 is precluded from use as general-purpose I/O Ports when used as address/data bus drivers.

2. Port 0 internal strong pull-ups assist the logic-one output for memory bus cycles only. Except for these bus cycles, the pull-up FET is off, Port 0 outputs are open-drain.

Figure 3. Port 2 Structure

Notes: 1. Port 2 is precluded from use as general-purpose I/O Ports when as address/data bus drivers.

2. Port 2 internal strong pull-ups FET (P1 in FiGURE) assist the logic-one output for memory bus cycle.

When Port 0 and Port 2 are used for an external memory cycle, an internal control signal switches the output-driver input from the latch output to the internal address/data line.

## Read-Modify-Write Instructions

Some instructions read the latch data rather than the pin data. The latch based instructions read the data, modify the data and then rewrite the latch. These are called "Read-Modify-Write" instructions. Below is a complete list of these special instructions (see Table ). When the destination operand is a Port or a Port bit, these instructions read the latch rather than the pin:

Table 2. Read-Modify-Write Instructions

| Instruction | Description                       | Example         |

|-------------|-----------------------------------|-----------------|

| ANL         | logical AND                       | ANL P1, A       |

| ORL         | logical OR                        | ORL P2, A       |

| XRL         | logical EX-OR                     | XRL P3, A       |

| JBC         | jump if bit = 1 and clear bit     | JBC P1.1, LABEL |

| CPL         | complement bit                    | CPL P3.0        |

| INC         | increment                         | INC P2          |

| DEC         | decrement                         | DEC P2          |

| DJNZ        | decrement and jump if not zero    | DJNZ P3, LABEL  |

| MOV Px.y, C | move carry bit to bit y of Port x | MOV P1.5, C     |

| CLR Px.y    | clear bit y of Port x             | CLR P2.4        |

| SET Px.y    | set bit y of Port x               | SET P3.3        |

It is not obvious the last three instructions in this list are Read-Modify-Write instructions. These instructions read the port (all 8 bits), modify the specifically addressed bit and write the new byte back to the latch. These Read-Modify-Write instructions are directed to the latch rather than the pin in order to avoid possible misinterpretation of voltage (and therefore, logic) levels at the pin. For example, a Port bit used to drive the base of an external bipolar transistor can not rise above the transistor's base-emitter junction voltage (a value lower than VIL). With a logic one written to the bit, attempts by the CPU to read the Port at the pin are misinterpreted as logic zero. A read of the latch rather than the pins returns the correct logic-one value.

## Quasi-Bidirectional Port Operation

Port 1, Port 2, Port 3 and Port 4 have fixed internal pull-ups and are referred to as "quasi-bidirectional" Ports. When configured as an input, the pin impedance appears as logic one and sources current in response to an external logic zero condition. Port 0 is a "true bidirectional" pin. The pins float when configured as input. Resets write logic one to all Port latches. If logical zero is subsequently written to a Port latch, it can be returned to input conditions by a logical one written to the latch.

Note: Port latch values change near the end of Read-Modify-Write instruction cycles. Output buffers (and therefore the pin state) update early in the instruction after Read-Modify-Write instruction cycle.

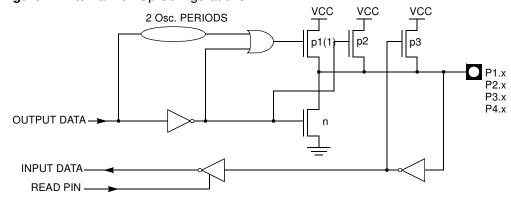

Logical zero-to-one transitions in Port 1, Port 2, Port 3 and Port 4 use an additional pull-up (p1) to aid this logic transition (see Figure 4.). This increases switch speed. This extra pull-up sources 100 times normal internal circuit current during 2 oscillator clock periods. The internal pull-ups are field-effect transistors rather than linear resistors. Pull-ups consist of three p-channel FET (pFET) devices. A pFET is on when the gate senses logical zero and off when the gate senses logical one. pFET #1 is turned on for two oscillator periods immediately after a zero-to-one transition in the Port latch. A logical one at the Port pin turns on pFET #3 (a weak pull-up) through the inverter. This inverter and pFET pair form a latch to drive logical one. pFET #2 is a very weak pull-up switched on whenever the associated nFET is switched off. This is traditional CMOS switch convention. Current strengths are 1/10 that of pFET #3.

Figure 4. Internal Pull-Up Configurations

Note: Port 2 p1 assists the logic-one output for memory bus cycles.

## **SFR Mapping**

The Special Function Registers (SFRs) of the A/T89C51AC2 fall into the following categories:

Table 3. C51 Core SFRs

| Mnemonic | Add | Name                                     | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator                              | _  | -  | _  | -   | -   | _  | -  | - |

| В        | F0h | B Register                               | _  | -  | _  | -   | -   | _  | -  | - |

| PSW      | D0h | Program Status Word                      | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer                            | _  | -  | _  | -   | -   | _  | -  | _ |

| DPL      | 82h | Data Pointer Low<br>byte<br>LSB of DPTR  | _  | _  | _  | _   | _   | -  | -  | - |

| DPH      | 83h | Data Pointer High<br>byte<br>MSB of DPTR | -  | -  | _  | -   | -   | _  | _  | _ |

## Table 4. I/O Port SFRs

| Mnemonic | Add | Name        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|-------------|---|---|---|---|---|---|---|---|

| P0       | 80h | Port 0      | - | - | _ | _ | _ | - | - | _ |

| P1       | 90h | Port 1      | - | _ | _ | - | _ | _ | - | - |

| P2       | A0h | Port 2      | - | _ | _ | _ | _ | - | - | _ |

| P3       | B0h | Port 3      | - | _ | _ | _ | _ | - | - | _ |

| P4       | C0h | Port 4 (x2) | - | _ | _ | _ | _ | - | - | _ |

## Table 5. Timers SFRs

| Mnemonic | Add | Name                          | 7     | 6     | 5   | 4   | 3     | 2     | 1   | 0   |

|----------|-----|-------------------------------|-------|-------|-----|-----|-------|-------|-----|-----|

| TH0      | 8Ch | Timer/Counter 0 High byte     | -     | -     | -   | -   | _     | -     | -   | -   |

| TL0      | 8Ah | Timer/Counter 0 Low byte      | 1     | 1     | ı   | -   | -     | ı     | 1   | ı   |

| TH1      | 8Dh | Timer/Counter 1 High byte     | 1     | 1     | 1   | ı   | -     | 1     | 1   | ı   |

| TL1      | 8Bh | Timer/Counter 1 Low byte      | 1     | 1     | 1   | ı   | -     | 1     | 1   | ı   |

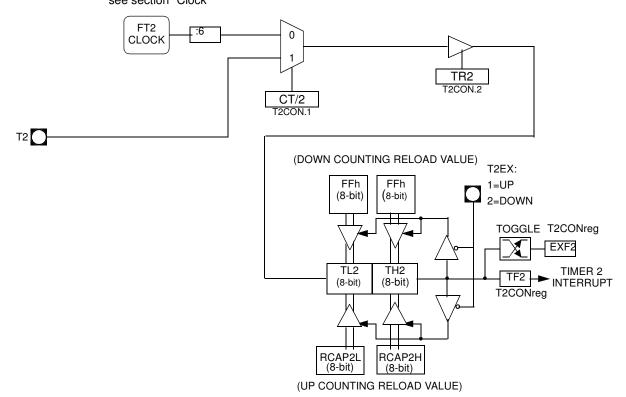

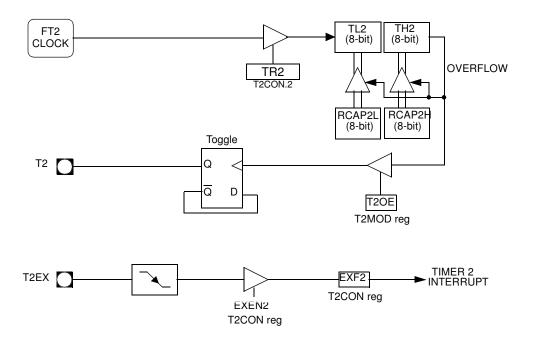

| TH2      | CDh | Timer/Counter 2 High byte     | 1     | 1     | ı   | -   | -     | ı     | 1   | ı   |

| TL2      | CCh | Timer/Counter 2 Low byte      | -     | -     | _   | _   | _     | -     | -   | 1   |

| TCON     | 88h | Timer/Counter 0 and 1 control | TF1   | TR1   | TF0 | TR0 | IE1   | IT1   | IE0 | IT0 |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes   | GATE1 | C/T1# | M11 | M01 | GATE0 | C/T0# | M10 | M00 |

Table 5. Timers SFRs (Continued)

| Mnemonic | Add | Name                                           | 7   | 6    | 5    | 4    | 3     | 2   | 1     | 0       |

|----------|-----|------------------------------------------------|-----|------|------|------|-------|-----|-------|---------|

| T2CON    | C8h | Timer/Counter 2 control                        | TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2<br>Mode                        | _   | _    | _    | _    | _     | _   | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2<br>Reload/Capture High<br>byte | _   | _    | _    | _    | _     | -   | -     | _       |

| RCAP2L   | CAh | Timer/Counter 2<br>Reload/Capture Low<br>byte  | _   | _    | _    | _    | _     | -   | -     | -       |

| WDTRST   | A6h | Watchdog Timer<br>Reset                        | _   | _    | _    | _    | _     | _   | -     | _       |

| WDTPRG   | A7h | Watchdog Timer<br>Program                      | _   | _    | _    | -    | _     | S2  | S1    | S0      |

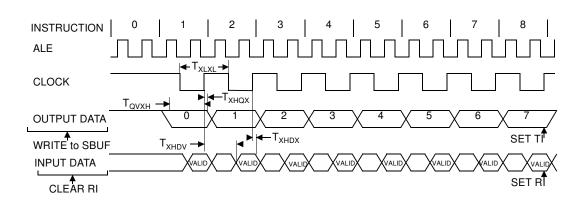

## Table 6. Serial I/O Port SFRs

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|----------|-----|--------------------|--------|-----|-----|-----|-----|-----|----|----|

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

| SBUF     | 99h | Serial Data Buffer | -      | -   | -   | -   | -   | _   | _  | _  |

| SADEN    | B9h | Slave Address Mask | -      | -   | -   | -   | -   | _   | _  | _  |

| SADDR    | A9h | Slave Address      | -      | -   | -   | -   | -   | _   | _  | -  |

#### Table 7. PCA SFRs

| Mnemonic                                       | Add               | Name                                                                                                                                                                   | 7                             | 6                                         | 5                                         | 4                                                   | 3                                    | 2                                                   | 1                                    | 0                                                   |

|------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------|-------------------------------------------|-----------------------------------------------------|--------------------------------------|-----------------------------------------------------|--------------------------------------|-----------------------------------------------------|

| CCON                                           | D8h               | PCA Timer/Counter Control                                                                                                                                              | CF                            | CR                                        | -                                         | CCF4                                                | CCF3                                 | CCF2                                                | CCF1                                 | CCF0                                                |

| CMOD                                           | D9h               | PCA Timer/Counter Mode                                                                                                                                                 | CIDL                          | WDTE                                      | -                                         | -                                                   | -                                    | CPS1                                                | CPS0                                 | ECF                                                 |

| CL                                             | E9h               | PCA Timer/Counter Low byte                                                                                                                                             | -                             | -                                         | -                                         | -                                                   | _                                    | -                                                   | -                                    | -                                                   |

| СН                                             | F9h               | PCA Timer/Counter High byte                                                                                                                                            | -                             | -                                         | -                                         | _                                                   | _                                    | -                                                   | -                                    | -                                                   |

| CCAPM0<br>CCAPM1<br>CCAPM2<br>CCAPM3<br>CCAPM4 | DBh<br>DCh<br>DDh | PCA Timer/Counter Mode 0 PCA Timer/Counter Mode 1 PCA Timer/Counter Mode 2 PCA Timer/Counter Mode 3 PCA Timer/Counter Mode 4                                           | -                             | ECOM0<br>ECOM1<br>ECOM2<br>ECOM3<br>ECOM4 | CAPP0<br>CAPP1<br>CAPP2<br>CAPP3<br>CAPP4 | CAPN0<br>CAPN1<br>CAPN2<br>CAPN3<br>CAPN4           | MAT0<br>MAT1<br>MAT2<br>MAT3<br>MAT4 | TOG0<br>TOG1<br>TOG2<br>TOG3<br>TOG4                | PWM0<br>PWM1<br>PWM2<br>PWM3<br>PWM4 | ECCF0<br>ECCF1<br>ECCF2<br>ECCF3<br>ECCF4           |

| CCAP0H<br>CCAP1H<br>CCAP2H<br>CCAP3H<br>CCAP4H | FDh               | PCA Compare Capture Module 0 H<br>PCA Compare Capture Module 1 H<br>PCA Compare Capture Module 2 H<br>PCA Compare Capture Module 3 H<br>PCA Compare Capture Module 4 H | CCAP1H7<br>CCAP2H7<br>CCAP3H7 | CCAP2H6<br>CCAP3H6                        | CCAP1H5<br>CCAP2H5<br>CCAP3H5             | CCAP0H4<br>CCAP1H4<br>CCAP2H4<br>CCAP3H4<br>CCAP4H4 | CCAP1H3<br>CCAP2H3<br>CCAP3H3        | CCAP0H2<br>CCAP1H2<br>CCAP2H2<br>CCAP3H2<br>CCAP4H2 | CCAP2H1<br>CCAP3H1                   | CCAP0H0<br>CCAP1H0<br>CCAP2H0<br>CCAP3H0<br>CCAP4H0 |

Table 7. PCA SFRs (Continued)

| Mnemonic | Add | Name                           | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|----------|-----|--------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| CCAP0L   | EAh | PCA Compare Capture Module 0 I | CCAP0L7 | CCAP0L6 | CCAP0L5 | CCAP0L4 | CCAP0L3 | CCAP0L2 | CCAP0L1 | CCAP0L0 |

| CCAP1L   | EBh | PCA Compare Capture Module 1 I | CCAP1L7 | CCAP1L6 | CCAP1L5 | CCAP1L4 | CCAP1L3 | CCAP1L2 | CCAP1L1 | CCAP1L0 |

| CCAP2L   | ECh | PCA Compare Capture Module 2 I | CCAP2L7 | CCAP2L6 | CCAP2L5 | CCAP2L4 | CCAP2L3 | CCAP2L2 | CCAP2L1 | CCAP2L0 |

| CCAP3L   | EDh | PCA Compare Capture Module 3 I | CCAP3L7 | CCAP3L6 | CCAP3L5 | CCAP3L4 | CCAP3L3 | CCAP3L2 | CCAP3L1 | CCAP3L0 |

| CCAP4L   | EEh | PCA Compare Capture Module 4 I | CCAP4L7 | CCAP4L6 | CCAP4L5 | CCAP4L4 | CCAP4L3 | CCAP4L2 | CCAP4L1 | CCAP4L0 |

Table 8. Interrupt SFRs

| Mnemonic | Add | Name                                 | 7  | 6    | 5    | 4   | 3    | 2    | 1     | 0    |

|----------|-----|--------------------------------------|----|------|------|-----|------|------|-------|------|

| IEN0     | A8h | Interrupt Enable<br>Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0   | EX0  |

| IEN1     | E8h | Interrupt Enable<br>Control 1        | _  | _    | _    | _   | _    | _    | EADC  | -    |

| IPL0     | B8h | Interrupt Priority<br>Control Low 0  | _  | PPC  | PT2  | PS  | PT1  | PX1  | PT0   | PX0  |

| IPH0     | B7h | Interrupt Priority<br>Control High 0 | -  | PPCH | PT2H | PSH | PT1H | PX1H | PT0H  | PX0H |

| IPL1     | F8h | Interrupt Priority<br>Control Low 1  | _  | _    | _    | _   | -    | -    | PADCL | -    |

| IPH1     | F7h | Interrupt Priority<br>Control High1  | -  | -    | _    | _   | -    | -    | PADCH | -    |

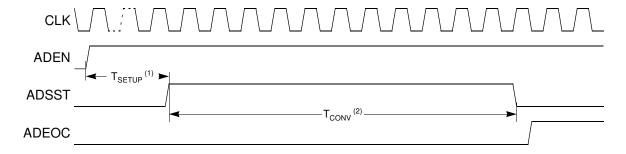

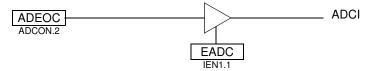

## Table 9. ADC SFRs

| Mnemonic | Add | Name               | 7     | 6      | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|--------------------|-------|--------|-------|-------|-------|-------|-------|-------|

| ADCON    | F3h | ADC Control        | _     | PSIDLE | ADEN  | ADEOC | ADSST | SCH2  | SCH1  | SCH0  |

| ADCF     | F6h | ADC Configuration  | CH7   | CH6    | CH5   | CH4   | СНЗ   | CH2   | CH1   | CH0   |

| ADCLK    | F2h | ADC Clock          | _     | -      | -     | PRS4  | PRS3  | PRS2  | PRS1  | PRS0  |

| ADDH     | F5h | ADC Data High byte | ADAT9 | ADAT8  | ADAT7 | ADAT6 | ADAT5 | ADAT4 | ADAT3 | ADAT2 |

| ADDL     | F4h | ADC Data Low byte  | _     | _      | _     | _     | _     | _     | ADAT1 | ADAT0 |

## Table 10. Other SFRs

| Mnemonic | Add | Name                 | 7     | 6     | 5      | 4     | 3    | 2     | 1      | 0      |

|----------|-----|----------------------|-------|-------|--------|-------|------|-------|--------|--------|

| PCON     | 87h | Power Control        | SMOD1 | SMOD0 | -      | POF   | GF1  | GF0   | PD     | IDL    |

| AUXR     | 8Eh | Auxiliary Register 0 | _     | _     | M0     | -     | XRS1 | XRS2  | EXTRAM | A0     |

| AUXR1    | A2h | Auxiliary Register 1 | -     | -     | ENBOOT | -     | GF3  | 0     | -      | DPS    |

| CKCON    | 8Fh | Clock Control        | -     | WDX2  | PCAX2  | SIX2  | T2X2 | T1X2  | T0X2   | X2     |

| FCON     | D1h | Flash Control        | FPL3  | FPL2  | FPL1   | FPL0  | FPS  | FMOD1 | FMOD0  | FBUSY  |

| EECON    | D2h | EEPROM Contol        | EEPL3 | EEPL2 | EEPL1  | EEPL0 | -    | -     | EEE    | EEBUSY |

Table 11. SFR Mapping

|     | 0/8 <sup>(1)</sup> | 1/9                | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                 |     |

|-----|--------------------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----|

| F8h | IPL1<br>xxxx xx0x  | CH<br>0000 0000    | CCAP0H<br>0000 0000 | CCAP1H<br>0000 0000 | CCAP2H<br>0000 0000 | CCAP3H<br>0000 0000 | CCAP4H<br>0000 0000 |                     | FFh |

| F0h | B<br>0000 0000     |                    | ADCLK<br>xxx0 0000  | ADCON<br>x000 0000  | ADDL<br>0000 0000   | ADDH<br>0000 0000   | ADCF<br>0000 0000   | IPH1<br>xxxx xx0x   | F7h |

| E8h | IEN1<br>xxxx xx0x  | CL<br>0000 0000    | CCAP0L<br>0000 0000 | CCAP1L<br>0000 0000 | CCAP2L<br>0000 0000 | CCAP3L<br>0000 0000 | CCAP4L<br>0000 0000 |                     | EFh |

| E0h | ACC<br>0000 0000   |                    |                     |                     |                     |                     |                     |                     | E7h |

| D8h | CCON<br>00x0 0000  | CMOD<br>00xx x000  | CCAPM0<br>x000 0000 | CCAPM1<br>x000 0000 | CCAPM2<br>x000 0000 | CCAPM3<br>x000 0000 | CCAPM4<br>x000 0000 |                     | DFh |

| D0h | PSW<br>0000 0000   | FCON<br>0000 0000  | EECON<br>xxxx xx00  |                     |                     |                     |                     |                     | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>xxxx xx00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000    | TH2<br>0000 0000    |                     |                     | CFh |

| C0h | P4<br>xxxx xx11    |                    |                     |                     |                     |                     |                     |                     | C7h |

| B8h | IPL0<br>x000 0000  | SADEN<br>0000 0000 |                     |                     |                     |                     |                     |                     | BFh |

| B0h | P3<br>1111 1111    |                    |                     |                     |                     |                     |                     | IPH0<br>x000 0000   | B7h |

| A8h | IEN0<br>0000 0000  | SADDR<br>0000 0000 |                     |                     |                     |                     |                     |                     | AFh |

| A0h | P2<br>1111 1111    |                    | AUXR1<br>xxxx 00x0  |                     |                     |                     | WDTRST<br>1111 1111 | WDTPRG<br>xxxx x000 | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>0000 0000  |                     |                     |                     |                     |                     |                     | 9Fh |

| 90h | P1<br>1111 1111    |                    |                     |                     |                     |                     |                     |                     | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000    | TH1<br>0000 0000    | AUXR<br>x00x 1100   | CKCON<br>0000 0000  | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                     |                     |                     | PCON<br>00x1 0000   | 87h |

| _   | 0/8 <sup>(1)</sup> | 1/9                | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                 | _   |

#### Reserved [

Note: 1. These registers are bit–addressable.

Sixteen addresses in the SFR space are both byte–addressable and bit–addressable. The bit–addressable SFR's are those whose address ends in 0 and 8. The bit addresses, in this area, are 0x80 through to 0xFF.

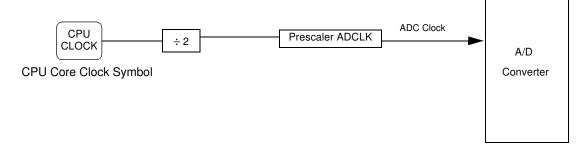

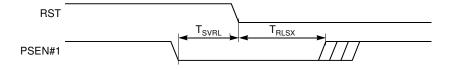

## Clock

The A/T89C51AC2 core needs only 6 clock periods per machine cycle. This feature, called "X2", provides the following advantages:

- Divides frequency crystals by 2 (cheaper crystals) while keeping the same CPU power.

- Saves power consumption while keeping the same CPU power (oscillator power saving).

- Saves power consumption by dividing dynamic operating frequency by 2 in operating and idle modes.

- Increases CPU power by 2 while keeping the same crystal frequency.

In order to keep the original C51 compatibility, a divider-by-2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by the software.

An extra feature is available to start after Reset in the X2 mode. This feature can be enabled by a bit X2B in the Hardware Security Byte. This bit is described in the section "In-System-Programming".

## **Description**

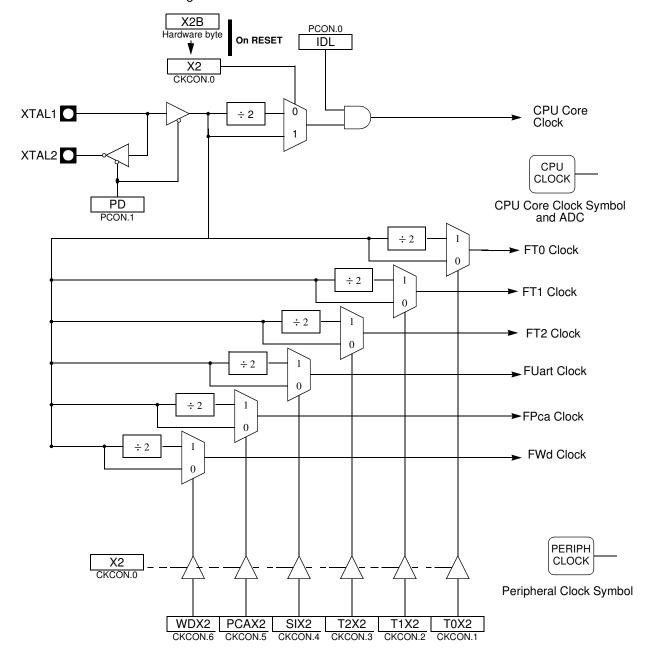

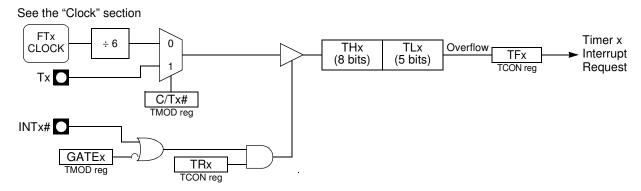

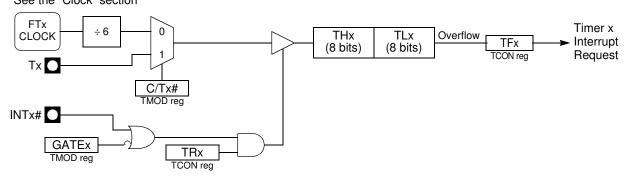

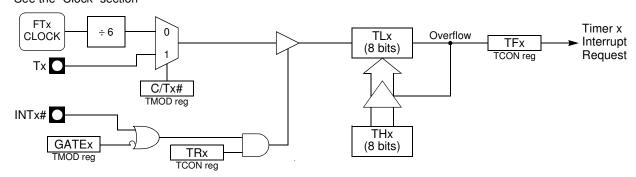

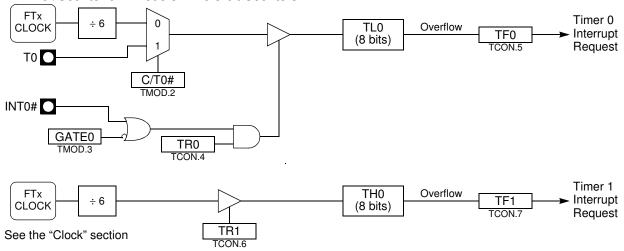

The X2 bit in the CKCON register (see Table 12) allows switching from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated (STD mode).

Setting this bit activates the X2 feature (X2 mode) for the CPU Clock only (see Figure 5.).

The Timers 0, 1 and 2, Uart, PCA, or Watchdog switch in X2 mode only if the corresponding bit is cleared in the CKCON register.

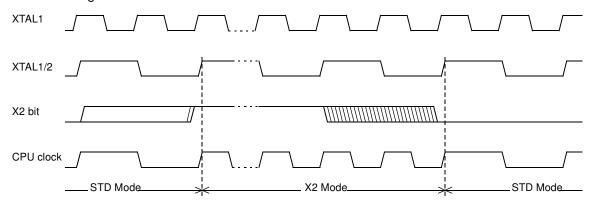

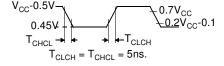

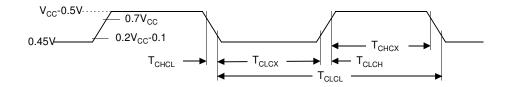

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on the XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 5. shows the clock generation block diagram. The X2 bit is validated on the XTAL1÷2 rising edge to avoid glitches when switching from the X2 to the STD mode. Figure 6 shows the mode switching waveforms.

Figure 5. Clock CPU Generation Diagram

Figure 6. Mode Switching Waveforms

Note: In order to prevent any incorrect operation while operating in the X2 mode, users must be aware that all peripherals using the clock frequency as a time reference (UART, timers...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. A UART with a 4800 baud rate will have a 9600 baud rate.

## Register

Table 12. CKCON Register

CKCON (S:8Fh) Clock Control Register

7 6 5 4 3 2 1 0 - WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                           |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -             | -               | Reserved Do not set this bit.                                                                                                                                                                                         |

| 6             | WDX2            | Watchdog clock <sup>(1)</sup> Clear to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                  |

| 5             | PCAX2           | Programmable Counter Array clock (1) Clear to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                           |

| 4             | SIX2            | Enhanced UART clock (MODE 0 and 2) (1) Clear to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                         |

| 3             | T2X2            | Timer 2 clock <sup>(1)</sup> Clear to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                   |

| 2             | T1X2            | Timer 1 clock <sup>(1)</sup> Clear to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                   |

| 1             | T0X2            | Timer 0 clock <sup>(1)</sup> Clear to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                   |

| 0             | X2              | CPU clock Clear to select 12 clock periods per machine cycle (STD mode) for CPU and all the peripherals. Set to select 6 clock periods per machine cycle (X2 mode) and to enable the individual peripherals "X2"bits. |

Note: 1. This control bit is validated when the CPU clock bit X2 is set; when X2 is low, this bit has no effect.

Reset Value = x000 0000b

## **Power Management**

Two power reduction modes are implemented in the A/T89C51AC2: the Idle mode and the Power-down mode. These modes are detailed in the following sections. In addition to these power reduction modes, the clocks of the core and peripherals can be dynamically divided by 2 using the X2 Mode detailed in Section "Clock".

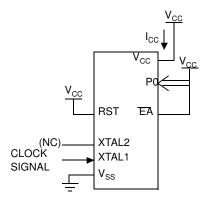

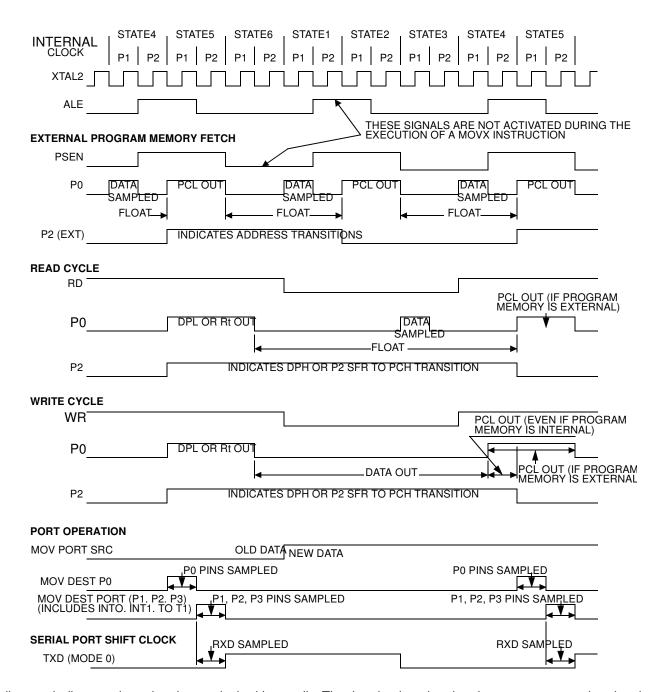

#### **Reset Pin**

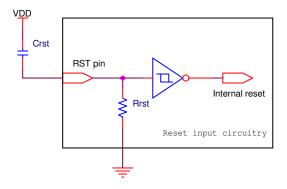

In order to start-up (cold reset) or to restart (warm reset) properly the microcontroller, a high level has to be applied on the RST pin. A bad level leads to a wrong initialisation of the internal registers like SFRs, PC, etc. and to unpredictable behavior of the microcontroller. A warm reset can be applied either directly on the RST pin or indirectly by an internal reset source such as a watchdog, PCA, timer, etc.

## At Power-up (Cold Reset)

Two conditions are required before enabling a CPU start-up:

- VDD must reach the specified VDD range,

- The level on xtal1 input must be outside the specification (VIH, VIL).

If one of these two conditions are not met, the microcontroller does not start correctly and can execute an instruction fetch from anywhere in the program space. An active level applied on the RST pin must be maintained until both of the above conditions are met. A reset is active when the level VIH1 is reached and when the pulse width covers the period of time where VDD and the oscillator are not stabilized. Two parameters have to be taken into account to determine the reset pulse width:

- VDD rise time (vddrst),

- Oscillator startup time (oscrst).

To determine the capacitor the highest value of these two parameters has to be chosen. The reset circuitry is shown in Figure 7.

Figure 7. Reset Circuitry

Table 13 and Table 15 give some typical examples for three values of VDD rise times, two values of oscillator start-up time and two pull-down resistor values.

Table 13. Minimum Reset Capacitor for a 15k Pull-down Resistor

| oscrst/vddrst | 1ms    | 10ms   | 100ms |

|---------------|--------|--------|-------|

| 5 ms          | 2.7 μF | 4.7 μF | 47 μF |

| 20 ms         | 10 μF  | 15 μF  | 47 μF |

Note: These values assume VDD starts from 0v to the nominal value. If the time between two on/off sequences is too fast, the power-supply de coupling capacitors may not be fully discharged, leading to a bad reset sequence.

0

#### **Warm Reset**

To achieve a valid reset, the reset signal must be maintained for at least 2 machine cycles (24 oscillator clock periods) while the oscillator is running. The number of clock periods is mode independent (X2 or X1).

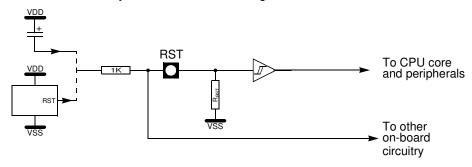

#### **Watchdog Reset**

As detailed in Section "PCA Watchdog Timer", page 80, the WDT generates a 96-clock period pulse on the RST pin. In order to properly propagate this pulse to the rest of the application in case of external capacitor or power-supply supervisor circuit, a  $1K\Omega$  resistor must be added as shown Figure 8.

Figure 8. Reset Circuitry for WDT reset out usage

# Reset Recommendation to Prevent Flash Corruption

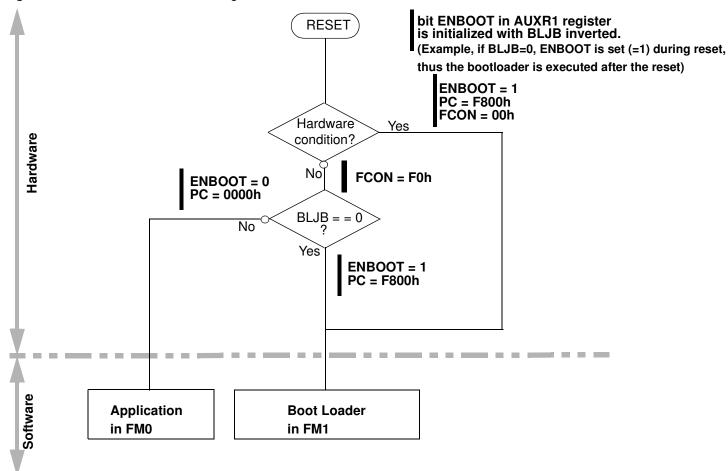

An example of bad initialization situation may occur in an instance where the bit ENBOOT in AUXR1 register is initialized from the hardware bit BLJB upon reset. Since this bit allows mapping of the bootloader in the code area, a reset failure can be critical.

If one wants the ENBOOT cleared in order to unmap the boot from the code area (yet due to a bad reset) the bit ENBOOT in SFRs may be set. If the value of Program Counter is accidently in the range of the boot memory addresses then a flash access (write or erase) may corrupt the Flash on-chip memory.

It is recommended to use an external reset circuitry featuring power supply monitoring to prevent system malfunction during periods of insufficient power supply voltage (power supply failure, power supply switched off).

#### Idle Mode

Idle mode is a power reduction mode that reduces the power consumption. In this mode, program execution halts. Idle mode freezes the clock to the CPU at known states while the peripherals continue to be clocked. The CPU status before entering Idle mode is preserved, i.e., the program counter and program status word register retain their data for the duration of Idle mode. The contents of the SFRs and RAM are also retained. The status of the Port pins during Idle mode is detailed in Table 14.

#### **Entering Idle Mode**

To enter Idle mode, you must set the IDL bit in PCON register (see Table 15). The T89C51CC02 enters Idle mode upon execution of the instruction that sets IDL bit. The instruction that sets IDL bit is the last instruction executed.

Note: If IDL bit and PD bit are set simultaneously, the T89C51CC02 enters Power-down mode. Then it does not go in Idle mode when exiting Power-down mode.

#### **Exiting Idle Mode**

There are two ways to exit Idle mode:

- 1. Generate an enabled interrupt.

- Hardware clears IDL bit in PCON register which restores the clock to the CPU. Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Idle mode.

The general-purpose flags (GF1 and GF0 in PCON register) may be used to indicate whether an interrupt occurred during normal operation or during Idle mode. When Idle mode is exited by an interrupt, the interrupt service routine may examine GF1 and GF0.

#### 2. Generate a reset.

A logic high on the RST pin clears IDL bit in PCON register directly and asynchronously. This restores the clock to the CPU. Program execution momentarily resumes with the instruction immediately following the instruction that activated the Idle mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the T89C51CC02 and vectors the CPU to address C:0000h.

- Notes: 1. During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated Idle mode should not write to a Port pin or to the external RAM.

- 2. If Idle mode is invoked by ADC Idle, the ADC conversion completion will exit Idle.

#### **Power-down Mode**

The Power-down mode places the T89C51CC02 in a very low power state. Power-down mode stops the oscillator and freezes all clocks at known states. The CPU status prior to entering Power-down mode is preserved, i.e., the program counter, program status word register retain their data for the duration of Power-down mode. In addition, the SFRs and RAM contents are preserved. The status of the Port pins during Power-down mode is detailed in Table 14.

#### **Entering Power-down Mode**

To enter Power-down mode, set PD bit in PCON register. The T89C51CC02 enters the Power-down mode upon execution of the instruction that sets PD bit. The instruction that sets PD bit is the last instruction executed.

#### **Exiting Power-down Mode**

If VDD was reduced during the Power-down mode, do not exit Power-down mode until VDD is restored to the normal operating level.

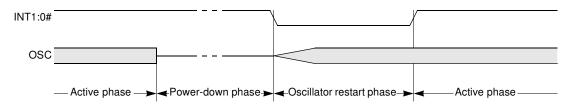

There are two ways to exit the Power-down mode:

- 1. Generate an enabled external interrupt.

- The T89C51CC02 provides capability to exit from Power-down using INT0#,

Hardware clears PD bit in PCON register which starts the oscillator and restores the clocks to the CPU and peripherals. Using INTx# input, execution resumes when the input is released (see Figure 9) while using KINx input, execution resumes after counting 1024 clock ensuring the oscillator is restarted properly (see Figure 8). Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Power-down mode.

#### Note:

- 1. The external interrupt used to exit Power-down mode must be configured as level sensitive (INT0# and INT1#) and must be assigned the highest priority. In addition, the duration of the interrupt must be long enough to allow the oscillator to stabilize. The execution will only resume when the interrupt is deasserted.

- 2. Exit from power-down by external interrupt does not affect the SFRs nor the internal RAM content.

Figure 9. Power-down Exit Waveform Using INT1:0#

#### 2. Generate a reset.

A logic high on the RST pin clears PD bit in PCON register directly and asynchronously. This starts the oscillator and restores the clock to the CPU and peripherals. Program execution momentarily resumes with the instruction immediately following the instruction that activated Power-down mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the T89C51CC02 and vectors the CPU to address 0000h.

- Notes: 1. During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port pins, the instruction immediately following the instruction that activated the Power-down mode should not write to a Port pin or to the external RAM.

- 2. Exit from power-down by reset redefines all the SFRs, but does not affect the internal RAM content.

**Table 14.** Pin Conditions in Special Operating Modes

| Mode                                 | Port 0   | Port 1 | Port 2 | Port 3 | Port 4 | ALE  | PSEN# |

|--------------------------------------|----------|--------|--------|--------|--------|------|-------|

| Reset                                | Floating | High   | High   | High   | High   | High | High  |

| Idle<br>(internal<br>code)           | Data     | Data   | Data   | Data   | Data   | High | High  |

| Idle<br>(external<br>code)           | Floating | Data   | Data   | Data   | Data   | High | High  |

| Power-<br>Down(inter<br>nal code)    | Data     | Data   | Data   | Data   | Data   | Low  | Low   |

| Power-<br>Down<br>(external<br>code) | Floating | Data   | Data   | Data   | Data   | Low  | Low   |

## Registers

## Table 15. PCON Register

PCON (S:87h) – Power configuration Register

7 6 5 4 3 2 1 0 SMOD1 SMOD0 - POF GF1 GF0 PD IDL

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                      |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | SMOD1           | Serial port Mode bit 1                                                                                                                                           |

| /             | SIVIODI         | Set to select double baud rate in mode 1, 2 or 3                                                                                                                 |

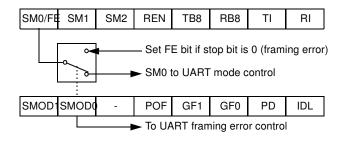

| 6             | SMOD0           | Serial port Mode bit 0 Clear to select SM0 bit in SCON register. Set to select FE bit in SCON register.                                                          |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                                     |

| 4             | POF             | Power-Off Flag Clear to recognize next reset type. Set by hardware when V <sub>cc</sub> rises from 0 to its nominal voltage. Can also be set by software.        |

| 3             | GF1             | General-purpose flag 1 One use is to indicate whether an interrupt occurred during normal operation or during Idle mode.                                         |

| 2             | GF0             | General-purpose flag 0 One use is to indicate whether an interrupt occurred during normal operation or during Idle mode.                                         |

| 1             | PD              | Power-down Mode bit Cleared by hardware when an interrupt or reset occurs. Set to activate the Power-down mode. If IDL and PD are both set, PD takes precedence. |

| 0             | IDL             | Idle Mode bit Cleared by hardware when an interrupt or reset occurs. Set to activate the Idle mode. If IDL and PD are both set, PD takes precedence.             |

Reset Value = 00X1 0000b

## **Data Memory**

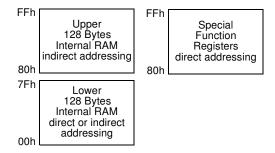

The A/T89C51AC2 provides data memory access in two different spaces:

- 1. The internal space mapped in three separate segments:

- the lower 128 Bytes RAM segment.

- the upper 128 Bytes RAM segment.

- the expanded 1024 Bytes RAM segment (XRAM).

- 2. The external space.

A fourth internal segment is available but dedicated to Special Function Registers, SFRs, (addresses 80h to FFh) accessible by direct addressing mode.

Figure 11 shows the internal and external data memory spaces organization.

Figure 10. Internal Memory - RAM

Figure 11. Internal and External Data Memory Organization XRAM-XRAM

## **Internal Space**

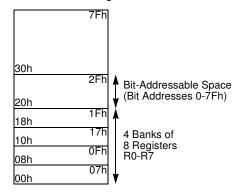

#### **Lower 128 Bytes RAM**

The lower 128 Bytes of RAM (see Figure 11) are accessible from address 00h to 7Fh using direct or indirect addressing modes. The lowest 32 Bytes are grouped into 4 banks of 8 registers (R0 to R7). Two bits RS0 and RS1 in PSW register (see Figure 18) select which bank is in use according to Table 16. This allows more efficient use of code space, since register instructions are shorter than instructions that use direct addressing, and can be used for context switching in interrupt service routines.

Table 16. Register Bank Selection

| RS1 | RS0 | Description                     |

|-----|-----|---------------------------------|

| 0   | 0   | Register bank 0 from 00h to 07h |

| 0   | 1   | Register bank 0 from 08h to 0Fh |

| 1 0 |     | Register bank 0 from 10h to 17h |

| 1   | 1   | Register bank 0 from 18h to 1Fh |

The next 16 Bytes above the register banks form a block of bit-addressable memory space. The C51 instruction set includes a wide selection of single-bit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00h to 7Fh.

Figure 12. Lower 128 Bytes Internal RAM Organization

**Upper 128 Bytes RAM**

The upper 128 Bytes of RAM are accessible from address 80h to FFh using only indirect addressing mode.

**Expanded RAM**

The on-chip 1024 Bytes of expanded RAM (XRAM) are accessible from address 0000h to 03FFh using indirect addressing mode through MOVX instructions. In this address range, the bit EXTRAM in AUXR register is used to select the XRAM (default) or the XRAM. As shown in Figure 11 when EXTRAM = 0, the XRAM is selected and when EXTRAM = 1, the XRAM is selected.

The size of XRAM can be configured by XRS1-0 bit in AUXR register (default size is 1024 Bytes).

Note:

Lower 128 Bytes RAM, Upper 128 Bytes RAM, and expanded RAM are made of volatile memory cells. This means that the RAM content is indeterminate after power-up and must then be initialized properly.

## **External Space**

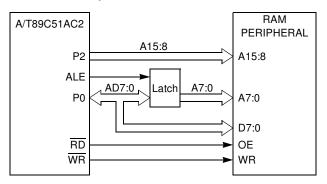

#### **Memory Interface**

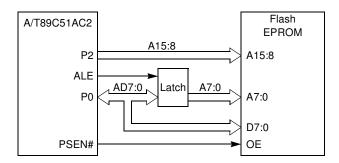

The external memory interface comprises the external bus (port 0 and port 2) as well as the bus control signals ( $\overline{RD}$ ,  $\overline{WR}$ , and ALE).

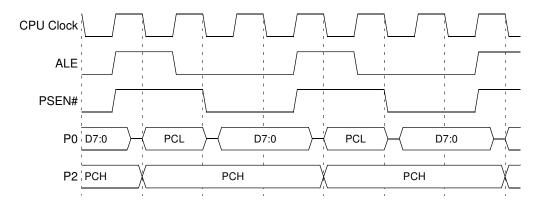

Figure 13 shows the structure of the external address bus. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 17 describes the external memory interface signals.

Figure 13. External Data Memory Interface Structure

Table 17. External Data Memory Interface Signals

| Signal<br>Name | Туре | Description                                                                                             | Alternative<br>Function |

|----------------|------|---------------------------------------------------------------------------------------------------------|-------------------------|

| A15:8          | 0    | Address Lines Upper address lines for the external bus.                                                 | P2.7:0                  |

| AD7:0          | I/O  | Address/Data Lines Multiplexed lower address lines and data for the external memory.                    | P0.7:0                  |

| ALE            | 0    | Address Latch Enable ALE signals indicates that valid address information are available on lines AD7:0. | -                       |

| RD             | 0    | Read Read signal output to external data memory.                                                        | P3.7                    |

| WR             | 0    | Write Write signal output to external memory.                                                           | P3.6                    |

## **External Bus Cycles**

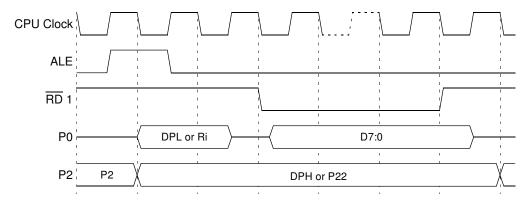

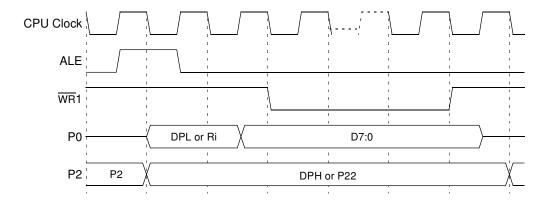

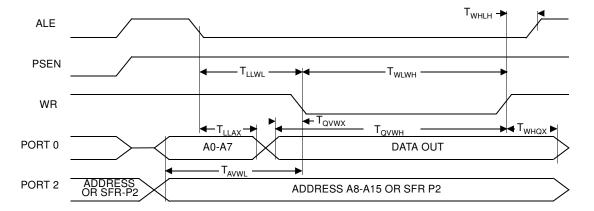

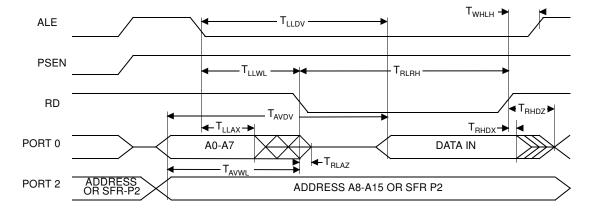

This section describes the bus cycles the A/T89C51AC2 executes to read (see Figure 14), and write data (see Figure 15) in the external data memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator clock period in standard mode or 6 oscillator clock periods in X2 mode. For further information on X2 mode.

Slow peripherals can be accessed by stretching the read and write cycles. This is done using the M0 bit in AUXR register. Setting this bit changes the width of the RD and WR signals from 3 to 15 CPU clock periods.

For simplicity, the accompanying figures depict the bus cycle waveforms in idealized form and do not provide precise timing information. For bus cycle timing parameters refer to the Section "AC Characteristics".

Figure 14. External Data Read Waveforms

Notes: 1.  $\overline{RD}$  signal may be stretched using M0 bit in AUXR register.

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

Figure 15. External Data Write Waveforms

Notes: 1. WR signal may be stretched using M0 bit in AUXR register.

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

#### **Dual Data Pointer**

#### **Description**

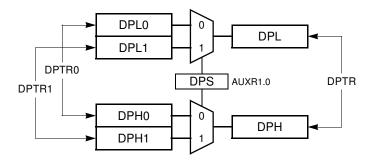

The A/T89C51AC2 implements a second data pointer for speeding up code execution and reducing code size in case of intensive usage of external memory accesses. DPTR 0 and DPTR 1 are seen by the CPU as DPTR and are accessed using the SFR addresses 83h and 84h that are the DPH and DPL addresses. The DPS bit in AUXR1 register (see Figure 20) is used to select whether DPTR is the data pointer 0 or the data pointer 1 (see Figure 16).

Figure 16. Dual Data Pointer Implementation

#### **Application**

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare...) are well served by using one data pointer as a "source" pointer and the other one as a "destination" pointer. Hereafter is an example of block move implementation using the two pointers and coded in assembler. The latest C compiler takes also advantage of this feature by providing enhanced algorithm libraries.

The INC instruction is a short (2 Bytes) and fast (6 machine cycle) way to manipulate the DPS bit in the AUXR1 register. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry.

- ; ASCII block move using dual data pointers

- ; Modifies DPTRO, DPTR1, A and PSW

- ; Ends when encountering NULL character  $% \left( 1\right) =\left( 1\right) \left( 1\right)$

- ; Note: DPS exits opposite to the entry state unless an extra INC AUXR1 is added

#### AUXR1EQU0A2h

move:movDPTR,#SOURCE ; address of SOURCE

incAUXR1 ; switch data pointers

movDPTR,#DEST ; address of DEST

mv\_loop:incAUXR1; switch data pointers

movxA,@DPTR; get a byte from SOURCE

incDPTR; increment SOURCE address

incAUXR1; switch data pointers

movx@DPTR,A; write the byte to DEST

incDPTR; increment DEST address

jnzmv\_loop; check for NULL terminator

end\_move:

## Registers

Table 18. PSW Register

PSW (S:D0h)

Program Status Word Register

| 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |  |

|----|----|----|-----|-----|----|----|---|--|

| CY | AC | F0 | RS1 | RS0 | ٥٧ | F1 | P |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                             |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------|

| 7             | CY              | Carry Flag Carry out from bit 1 of ALU operands.                                                        |

| 6             | AC              | Auxiliary Carry Flag Carry out from bit 1 of addition operands.                                         |

| 5             | F0              | User Definable Flag 0.                                                                                  |

| 4-3           | RS1:0           | Register Bank Select Bits Refer to Table 16 for bits description.                                       |

| 2             | OV              | Overflow Flag Overflow set by arithmetic operations.                                                    |

| 1             | F1              | User Definable Flag 1                                                                                   |

| 0             | Р               | Parity Bit Set when ACC contains an odd number of 1's. Cleared when ACC contains an even number of 1's. |

Reset Value = 0000 0000b

Table 19. AUXR Register

AUXR (S:8Eh) Auxiliary Register

| 7 | 6 | 5  | 4 | 3    | 2    | 1      | 0  |

|---|---|----|---|------|------|--------|----|

| - | - | MO | - | XRS1 | XRS0 | EXTRAM | Α0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                             |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6           | -               | Reserved The value read from these bits are indeterminate. Do not set this bit.                                                                                                                                                         |

| 5             | MO              | Stretch MOVX control: the RD/ and the WR/ pulse length is increased according to the value of M0.  M0 Pulse length in clock period 0 6 1 30                                                                                             |