#### **Features**

- 80C52 Compatible

- 8051 Pin and Instruction Compatible

- Four 8-bit I/O Ports

- Three 16-bit Timer/Counters

- 256 Bytes Scratch Pad RAM

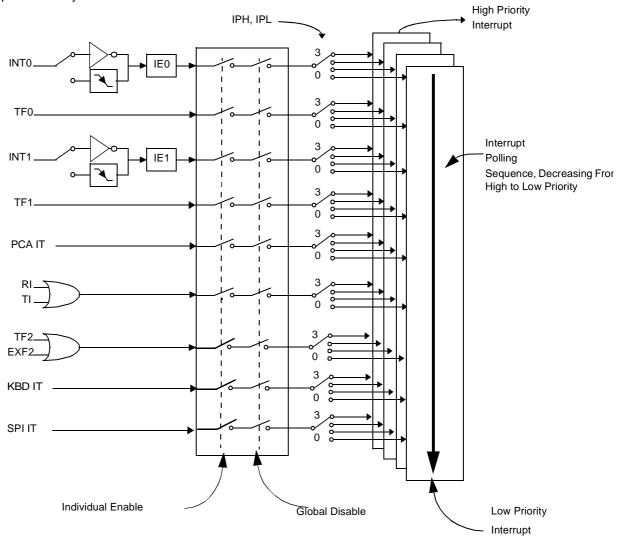

- 9 Interrupt Sources with 4 Priority Levels

- Dual Data Pointer

- Variable Length MOVX for Slow RAM/Peripherals

- ISP (In-system Programming) Using Standard  $V_{CC}$  Power Supply

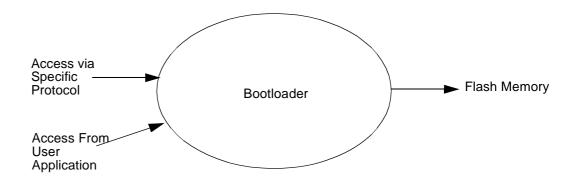

- Boot ROM Contains Low Level Flash Programming Routines and a Default Serial Loader

- High-speed Architecture

- In Standard Mode:

40 MHz (Vcc 2.7V to 5.5V, both Internal and external code execution) 60 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

- In X2 mode (6 Clocks/machine cycle)

20 MHz (Vcc 2.7V to 5.5V, both Internal and external code execution) 30 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

- 16K/32K Bytes On-chip Flash Program/Data Memory

- Byte and Page (128 Bytes) Erase and Write

- 100K Write Cycles

- On-chip 1024 Bytes Expanded RAM (XRAM)

- Software Selectable Size (0, 256, 512, 768, 1024 Bytes)

- 256 Bytes Selected at Reset for TS87C51RB2/RC2 Compatibility

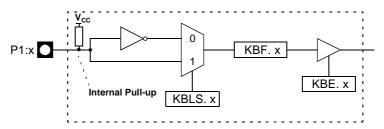

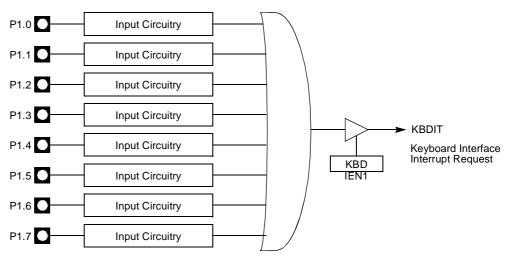

- Keyboard Interrupt Interface on Port P1

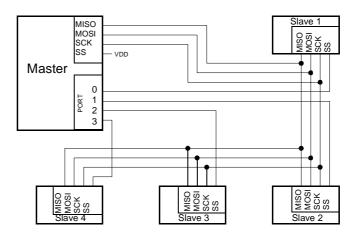

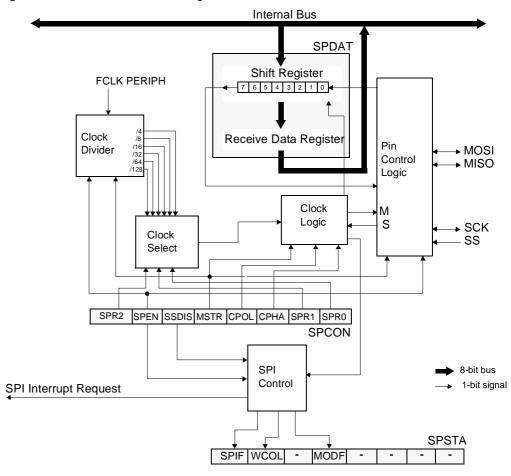

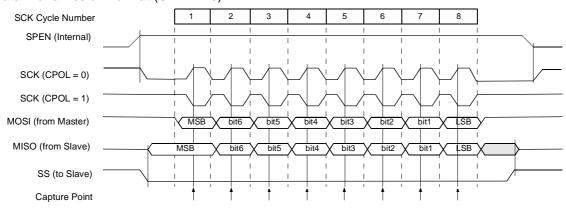

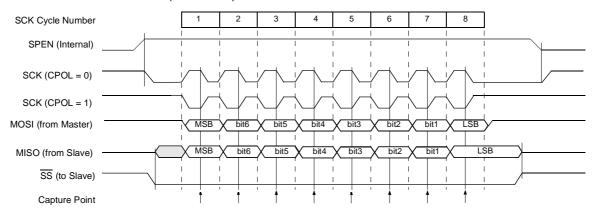

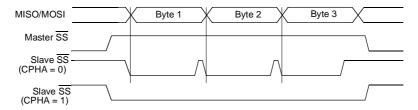

- SPI Interface (Master/Slave Mode)

- 8-bit Clock Prescaler

- Improved X2 Mode with Independent Selection for CPU and Each Peripheral

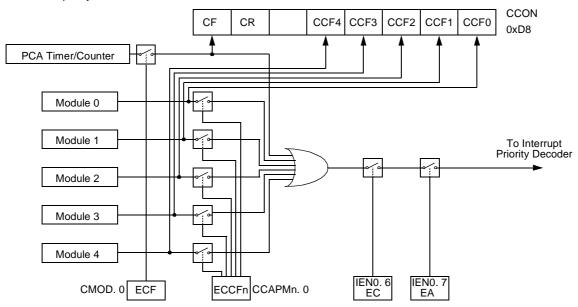

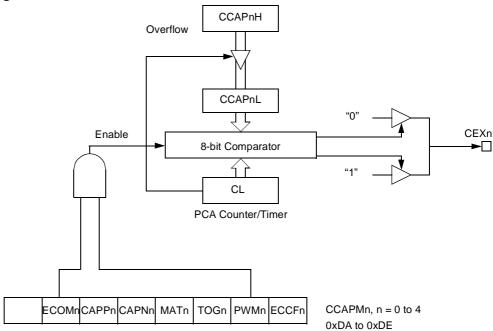

- Programmable Counter Array 5 Channels

- High-speed Output

- Compare/Capture

- Pulse Width Modulator

- Watchdog Timer Capabilities

- Asynchronous Port Reset

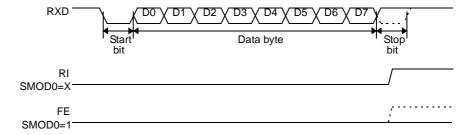

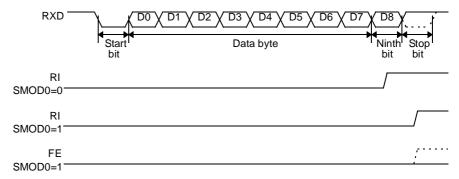

- Full Duplex Enhanced UART

- Dedicated Baud Rate Generator for UART

- Low EMI (Inhibit ALE)

- . Hardware Watchdog Timer (One-time Enabled with Reset-out)

- Power Control Modes

- Idle Mode

- Power-down Mode

- Power-off Flag

- · Power Supply:

- 2.7 to 3.6 (3V Version)

- 2.7 to 5.5V (5V Version)

- Temperature Ranges: Commercial (0 to +70°C) and Industrial (-40°C to +85°C)

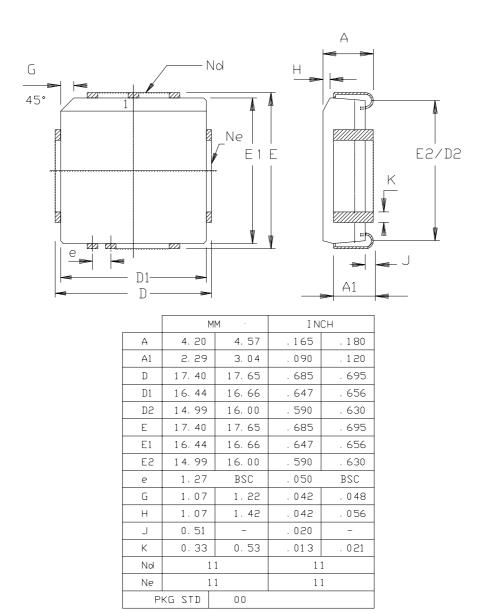

- Packages: PDIL40, PLCC44, VQFP44

## Description

The AT89C51RB2/RC2 is a high-performance Flash version of the 80C51 8-bit microcontrollers. It contains a 16K or 32K Bytes Flash memory block for program and data.

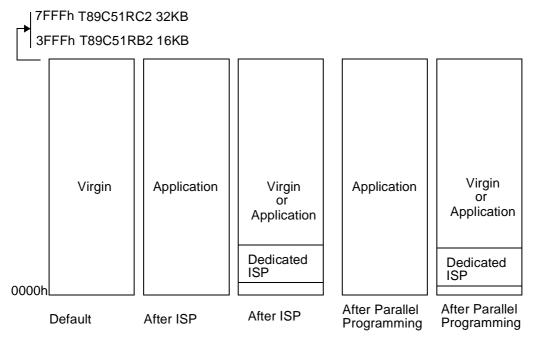

The Flash memory can be programmed either in parallel mode or in serial mode with the ISP capability or with software. The programming voltage is internally generated from the standard VCC pin.

8-bit Microcontroller with 16K/ 32K Bytes Flash

AT89C51RB2 AT89C51RC2

The AT89C51RB2/RC2 retains all features of the 80C52 with 256 Bytes of internal RAM, a 9-source 4-level interrupt controller and three timer/counters.

In addition, the AT89C51RB2/RC2 has a Programmable Counter Array, an XRAM of 1024 Bytes, a Hardware Watchdog Timer, a Keyboard Interface, an SPI Interface, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 mode).

The Pinout is the standard 40/44 pins of the C52.

The fully static design reduces system power consumption of the AT89C51RB2/RC2 by allowing it to bring the clock frequency down to any value, even DC, without loss of data.

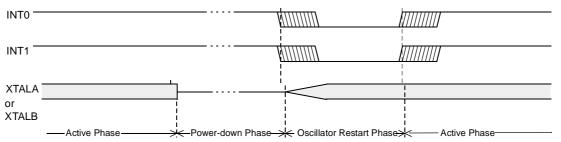

The AT89C51RB2/RC2 has 2 software-selectable modes of reduced activity and 8-bit clock prescaler for further reduction in power consumption. In Idle mode, the CPU is frozen while the peripherals and the interrupt system are still operating. In power-down mode, the RAM is saved and all other functions are inoperative.

The added features of the AT89C51RB2/RC2 make it more powerful for applications that need pulse width modulation, high speed I/O and counting capabilities such as alarms, motor control, corded phones, and smart card readers.

Table 1. Memory Size

| Part Number | Flash (Bytes) | XRAM (Bytes) | TOTAL RAM<br>(Bytes) | I/O |

|-------------|---------------|--------------|----------------------|-----|

| AT89C51RB2  | 16K           | 1024         | 1280                 | 32  |

| AT89C51RC2  | 32K           | 1024         | 1280                 | 32  |

| AT89C51IC2  | 32K           | 1024         | 1280                 | 32  |

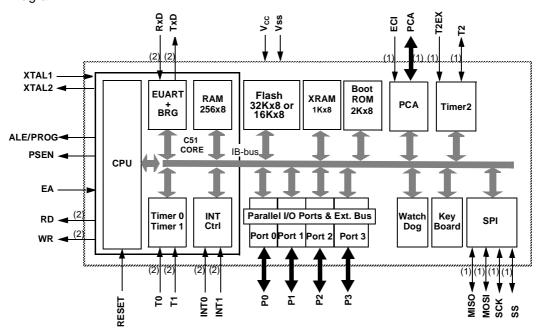

## **Block Diagram**

Figure 1. Block Diagram

Notes: 1. Alternate function of Port 1.

2. Alternate function of Port 3.

## **SFR Mapping**

The Special Function Registers (SFRs) of the AT89C51RB2/RC2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

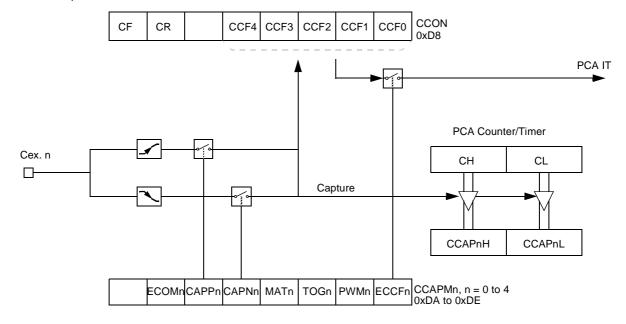

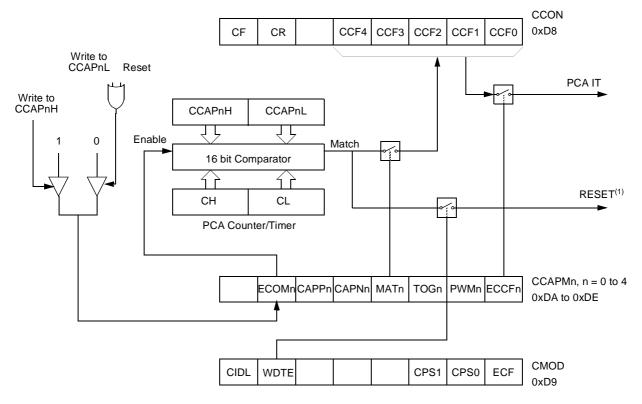

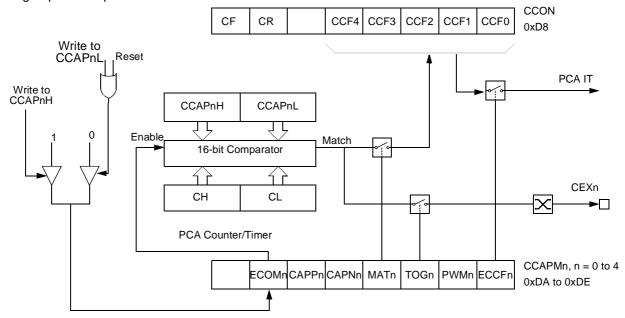

- PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH, CCAPxL (x: 0 to 4)

- · Power and clock control registers: PCON

- Hardware Watchdog Timer registers: WDTRST, WDTPRG

- Interrupt system registers: IEN0, IPL0, IPH0, IEN1, IPL1, IPH1

- Keyboard Interface registers: KBE, KBF, KBLS

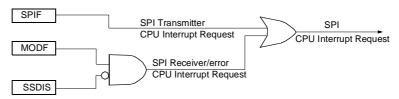

- SPI registers: SPCON, SPSTR, SPDAT

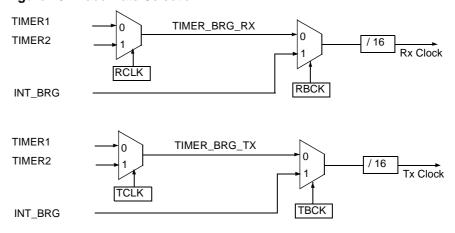

- BRG (Baud Rate Generator) registers: BRL, BDRCON

- Flash register: FCON

- Clock Prescaler register: CKRL

- Others: AUXR, AUXR1, CKCON0, CKCON1

Table 2. C51 Core SFRs

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

Table 3. System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4     | 3     | 2     | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|-------|-------|-------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMOD0 | -      | POF   | GF1   | GF0   | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | DPU   | -     | MO     | XRS2  | XRS1  | XRS0  | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -     | GF3   | 0     | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | CKRL7 | CKRL6 | CKRL5  | CKRL4 | CKRL3 | CKRL2 | CKRL1  | CKRL0 |

| CKCKON0  | 8Fh | Clock Control Register 0 | -     | WDTX2 | PCAX2  | SIX2  | T2X2  | T1X2  | T0X2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -     | -     | -     | -      | SPIX2 |

Table 4. Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3    | 2    | 1     | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|------|------|-------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0   | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | -    | ESPI | EI2C  | KBD  |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PHS | PT1H | PX1H | PT0H  | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PLS | PT1L | PX1L | PT0L  | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | -    | SPIH | IE2CH | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | -    | SPIL | IE2CL | KBDL |

## Table 5. Port SFRs

| Mnemonic | Add | Name         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0 |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1 |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2 |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3 |   |   |   |   |   |   |   |   |

Table 6. Timer SFRs

| Mnemonic | Add | Name                                        | 7     | 6     | 5    | 4    | 3     | 2     | 1     | 0       |

|----------|-----|---------------------------------------------|-------|-------|------|------|-------|-------|-------|---------|

| TCON     | 88h | Timer/Counter 0 and 1 Control               | TF1   | TR1   | TF0  | TR0  | IE1   | IT1   | IE0   | IT0     |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes                 | GATE1 | C/T1# | M11  | M01  | GATE0 | C/T0# | M10   | M00     |

| TL0      | 8Ah | Timer/Counter 0 Low Byte                    |       |       |      |      |       |       |       |         |

| TH0      | 8Ch | Timer/Counter 0 High Byte                   |       |       |      |      |       |       |       |         |

| TL1      | 8Bh | Timer/Counter 1 Low Byte                    |       |       |      |      |       |       |       |         |

| TH1      | 8Dh | Timer/Counter 1 High Byte                   |       |       |      |      |       |       |       |         |

| WDTRST   | A6h | Watchdog Timer Reset                        |       |       |      |      |       |       |       |         |

| WDTPRG   | A7h | Watchdog Timer Program                      | -     | -     | -    | -    | -     | WTO2  | WTO1  | WTO0    |

| T2CON    | C8h | Timer/Counter 2 control                     | TF2   | EXF2  | RCLK | TCLK | EXEN2 | TR2   | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2 Mode                        | -     | -     | -    | -    | -     | -     | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2 Reload/Capture<br>High Byte |       |       |      |      |       |       |       |         |

| RCAP2L   | CAh | Timer/Counter 2 Reload/Capture<br>Low Byte  |       |       |      |      |       |       |       |         |

| TH2      | CDh | Timer/Counter 2 High Byte                   |       |       |      |      |       |       |       |         |

| TL2      | CCh | Timer/Counter 2 Low Byte                    |       |       |      |      |       |       |       |         |

## Table 7. PCA SFRs

| Mnemo-<br>nic | Add | Name                           | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------------|-----|--------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

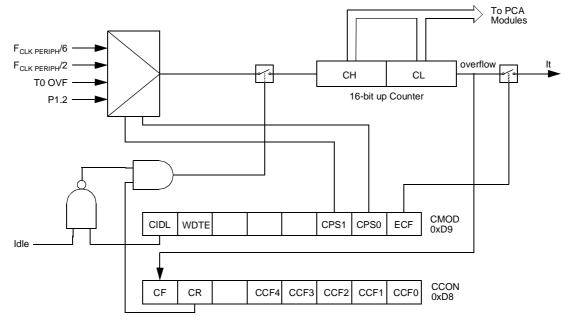

| CCON          | D8h | PCA Timer/Counter Control      | CF      | CR      | -       | CCF4    | CCF3    | CCF2    | CCF1    | CCF0    |

| CMOD          | D9h | PCA Timer/Counter Mode         | CIDL    | WDTE    | -       | -       | -       | CPS1    | CPS0    | ECF     |

| CL            | E9h | PCA Timer/Counter Low Byte     |         |         |         |         |         |         |         |         |

| СН            | F9h | PCA Timer/Counter High Byte    |         |         |         |         |         |         |         |         |

| CCAPM0        | DAh | PCA Timer/Counter Mode 0       |         | ECOM0   | CAPP0   | CAPN0   | MAT0    | TOG0    | PWM0    | ECCF0   |

| CCAPM1        | DBh | PCA Timer/Counter Mode 1       |         | ECOM1   | CAPP1   | CAPN1   | MAT1    | TOG1    | PWM1    | ECCF1   |

| CCAPM2        | DCh | PCA Timer/Counter Mode 2       | -       | ECOM2   | CAPP2   | CAPN2   | MAT2    | TOG2    | PWM2    | ECCF2   |

| ССАРМ3        | DDh | PCA Timer/Counter Mode 3       |         | ECOM3   | CAPP3   | CAPN3   | MAT3    | TOG3    | PWM3    | ECCF3   |

| CCAPM4        | DEh | PCA Timer/Counter Mode 4       |         | ECOM4   | CAPP4   | CAPN4   | MAT4    | TOG4    | PWM4    | ECCF4   |

| CCAP0H        | FAh | PCA Compare Capture Module 0 H | CCAP0H7 | ССАР0Н6 | CCAP0H5 | CCAP0H4 | ССАР0Н3 | CCAP0H2 | CCAP0H1 | ССАР0Н0 |

| CCAP1H        | FBh | PCA Compare Capture Module 1 H | CCAP1H7 | CCAP1H6 | CCAP1H5 | CCAP1H4 | CCAP1H3 | CCAP1H2 | CCAP1H1 | CCAP1H0 |

| CCAP2H        | FCh | PCA Compare Capture Module 2 H | CCAP2H7 | CCAP2H6 | CCAP2H5 | CCAP2H4 | CCAP2H3 | CCAP2H2 | CCAP2H1 | CCAP2H0 |

| CCAP3H        | FDh | PCA Compare Capture Module 3 H | CCAP3H7 | CCAP3H6 | CCAP3H5 | CCAP3H4 | CCAP3H3 | CCAP3H2 | CCAP3H1 | CCAP3H0 |

| CCAP4H        | FEh | PCA Compare Capture Module 4 H | CCAP4H7 | CCAP4H6 | CCAP4H5 | CCAP4H4 | CCAP4H3 | CCAP4H2 | CCAP4H1 | CCAP4H0 |

| CCAP0L        | EAh | PCA Compare Capture Module 0 L | CCAP0L7 | CCAP0L6 | CCAP0L5 | CCAP0L4 | CCAP0L3 | CCAP0L2 | CCAP0L1 | CCAP0L0 |

| CCAP1L        | EBh | PCA Compare Capture Module 1 L | CCAP1L7 | CCAP1L6 | CCAP1L5 | CCAP1L4 | CCAP1L3 | CCAP1L2 | CCAP1L1 | CCAP1L0 |

| CCAP2L        | ECh | PCA Compare Capture Module 2 L | CCAP2L7 | CCAP2L6 | CCAP2L5 | CCAP2L4 | CCAP2L3 | CCAP2L2 | CCAP2L1 | CCAP2L0 |

| CCAP3L        | EDh | PCA Compare Capture Module 3 L | CCAP3L7 | CCAP3L6 | CCAP3L5 | CCAP3L4 | CCAP3L3 | CCAP3L2 | CCAP3L1 | CCAP3L0 |

| CCAP4L        | EEh | PCA Compare Capture Module 4 L | CCAP4L7 | CCAP4L6 | CCAP4L5 | CCAP4L4 | CCAP4L3 | CCAP4L2 | CCAP4L1 | CCAP4L0 |

Table 8. Serial I/O Port SFRs

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|--------------------|--------|-----|-----|-----|------|------|-----|-----|

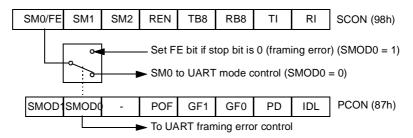

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8  | RB8  | TI  | RI  |

| SBUF     | 99h | Serial Data Buffer |        |     |     |     |      |      |     |     |

| SADEN    | B9h | Slave Address Mask |        |     |     |     |      |      |     |     |

| SADDR    | A9h | Slave Address      |        |     |     |     |      |      |     |     |

| BDRCON   | 9Bh | Baud Rate Control  |        |     |     | BRR | TBCK | RBCK | SPD | SRC |

| BRL      | 9Ah | Baud Rate Reload   |        |     |     |     |      |      |     |     |

## Table 9. SPI Controller SFRs

| Mnemonic | Add | Name        | 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|----------|-----|-------------|------|------|-------|------|------|------|------|------|

| SPCON    | C3h | SPI Control | SPR2 | SPEN | SSDIS | MSTR | CPOL | СРНА | SPR1 | SPR0 |

| SPSTA    | C4h | SPI Status  | SPIF | WCOL | SSERR | MODF | -    | -    | -    | -    |

| SPDAT    | C5h | SPI Data    | SPD7 | SPD6 | SPD5  | SPD4 | SPD3 | SPD2 | SPD1 | SPD0 |

Table 10. Keyboard Interface SFRs

|          | . , |                         |       |       |       |       |       |       |       |       |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

Table 11 shows all SFRs with their address and their reset value.

Table 11. SFR Mapping

|     | Bit addressable    |                       |                     |                     | Non Bit addre        | ssable               |                      |                     |     |

|-----|--------------------|-----------------------|---------------------|---------------------|----------------------|----------------------|----------------------|---------------------|-----|

|     | 0/8                | 1/9                   | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

| F8h |                    | CH<br>0000 0000       | CCAP0H<br>XXXX      | CCAP1H<br>XXXX      | CCAPL2H<br>XXXX      | CCAPL3H<br>XXXX      | CCAPL4H<br>XXXX      |                     | FFh |

| F0h | B<br>0000 0000     |                       |                     |                     |                      |                      |                      |                     | F7h |

| E8h |                    | CL<br>0000 0000       | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAPL2L<br>XXXX XXXX | CCAPL3L<br>XXXX XXXX | CCAPL4L<br>XXXX XXXX |                     | EFh |

| E0h | ACC<br>0000 0000   |                       |                     |                     |                      |                      |                      |                     | E7h |

| D8h | CCON<br>00X0 0000  | CMOD<br>00XX X000     | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000  | CCAPM4<br>X000 0000  |                     | DFh |

| D0h | PSW<br>0000 0000   | FCON (1)<br>XXXX 0000 |                     |                     |                      |                      |                      |                     | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00    | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000     | TH2<br>0000 0000     |                      |                     | CFh |

| C0h |                    |                       |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000   | SPDAT<br>XXXX XXXX   |                      |                     | C7h |

| B8h | IPL0<br>X000 000   | SADEN<br>0000 0000    |                     |                     |                      |                      |                      |                     | BFh |

| B0h | P3<br>1111 1111    | IEN1<br>XXXXX 000     | IPL1<br>XXXXX000    | IPH1<br>XXXX X000   |                      |                      |                      | IPH0<br>X000 0000   | B7h |

| A8h | IEN0<br>0000 0000  | SADDR<br>0000 0000    |                     |                     |                      |                      |                      | CKCON1<br>XXXX XXX0 | AFh |

| A0h | P2<br>1111 1111    |                       | AUXR1<br>XXXXX0X0   |                     |                      |                      | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000 | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>XXXX XXXX     | BRL<br>0000 0000    | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000    | KBE<br>0000 0000     | KBF<br>0000 0000     |                     | 9Fh |

| 90h | P1<br>1111 1111    |                       |                     |                     |                      |                      |                      | CKRL<br>1111 1111   | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000     | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>XX0X 0000    | CKCON0<br>0000 0000 | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111       | DPL<br>0000 0000    | DPH<br>0000 0000    |                      |                      |                      | PCON<br>00X1 0000   | 87h |

|     | 0/8                | 1/9                   | 2/A                 | 3/B                 | 4/C                  | 5/D                  | 6/E                  | 7/F                 |     |

<sup>1.</sup> FCON access is reserved for the Flash API and ISP software.

Reserved

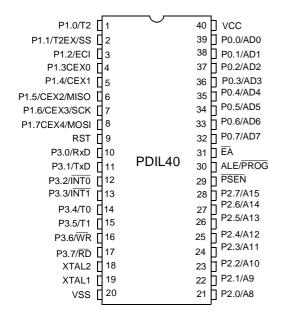

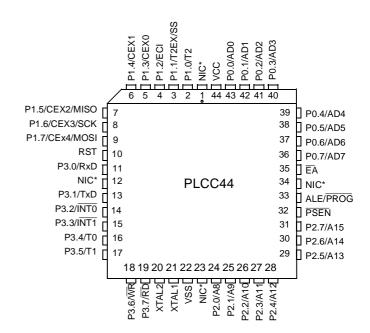

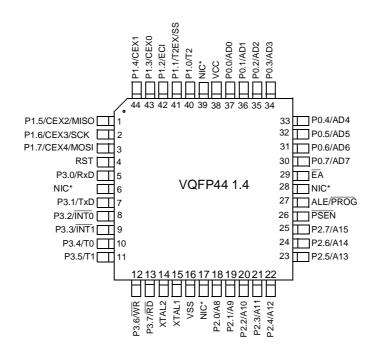

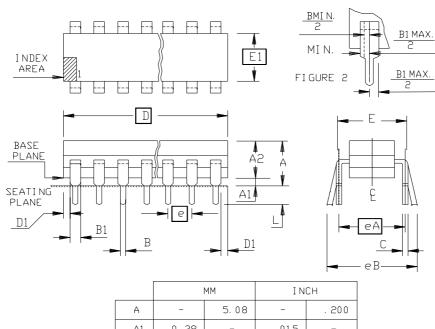

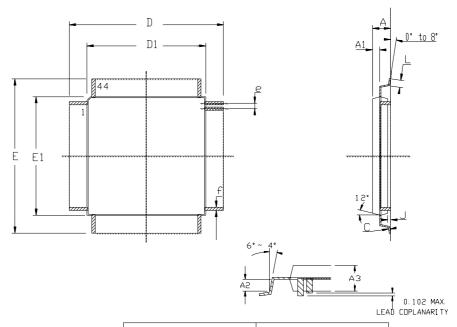

## **Pin Configurations**

Figure 2. Pin Configurations

\*NIC: No Internal Connection

**Table 12.** Pin Description for 40 - 44 Pin Packages

|                 |         | Pin Num | ber              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|---------|---------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic        | DIL     | LCC     | VQFP44 1.4       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> | 20      | 22      | 16               | 1    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>cc</sub> | 40      | 44      | 38               | I    | <b>Power Supply</b> : This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0.0 - P0.7     | 39 - 32 | 43 - 36 | 37 - 30          | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs. Port 0 must be polarized to $V_{CC}$ or $V_{SS}$ in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code Bytes during Flash programming. External pull-ups are required during program verification during which P0 outputs the code Bytes. |

| P1.0 - P1.7     | 1 - 8   | 2 - 9   | 40 - 44<br>1 - 3 | I/O  | Port 1: Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address Byte during memory programming and verification.  Alternate functions for AT89C51RB2/RC2 Port 1 include:                                                                                                                                                                   |

|                 | 1       | 2       | 40               | I/O  | P1.0: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | 2       | 3       | 41               | I/O  | P1.1: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | 1    | T2EX: Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |         |         |                  | 1    | SS: SPI Slave Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | 3       | 4       | 42               | I/O  | P1.2: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | 1    | ECI: External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 | 4       | 5       | 43               | I/O  | P1.3: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX0: Capture/Compare External I/O for PCA Module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 5       | 6       | 44               | I/O  | P1.4: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX1: Capture/Compare External I/O for PCA Module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 | 6       | 7       | 1                | I/O  | P1.5: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX2: Capture/Compare External I/O for PCA Module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |         |         |                  | I/O  | MISO: SPI Master Input Slave Output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |         |         |                  |      | When SPI is in master mode, MISO receives data from the slave peripheral. When SPI is in slave mode, MISO outputs data to the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 | 7       | 8       | 2                | I/O  | P1.6: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |         |         |                  | I/O  | CEX3: Capture/Compare External I/O for PCA Module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |         |         |                  | I/O  | SCK: SPI Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |         |         |                  |      | SCK outputs clock to the slave peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 8       | 9       | 3                | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 12. Pin Description for 40 - 44 Pin Packages (Continued)

|             | Pin Number |                | ber          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------------|------------|----------------|--------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Mnemonic    | DIL        | LCC            | VQFP44 1.4   | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             |            |                |              | I/O   | CEX4: Capture/Compare External I/O for PCA Module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| P1.0 - P1.7 |            |                |              | I/O   | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|             |            |                |              |       | When SPI is in master mode, MOSI outputs data to the slave peripheral. When SPI is in slave mode, MOSI receives data from the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| XTAL1       | 19         | 21             | 15           | I     | Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| XTAL2       | 18         | 20             | 14           | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| P2.0 - P2.7 | 21 - 28    | 24 - 31        | 18 - 25      | I/O   | Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high - order address Byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. Some Port 2 pins receive the high order address bits during EPROM programming and verification:  P2.0 to P2.5 for 16 KB devices  P2.0 to P2.6 for 32KB devices |  |

| P3.0 - P3.7 | 10 - 17    | 11,<br>13 - 19 | 5,<br>7 - 13 | I/O   | <b>Port 3:</b> Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|             | 10         | 11             | 5            | ı     | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|             | 11         | 13             | 7            | 0     | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|             | 12         | 14             | 8            | I     | INTO (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 13         | 15             | 9            | I     | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 14         | 16             | 10           | I     | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 15         | 17             | 11           | I     | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 16         | 18             | 12           | 0     | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|             | 17         | 19             | 13           | 0     | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

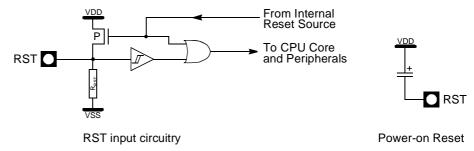

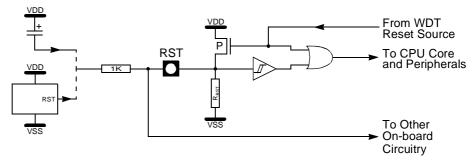

| RST         | 9          | 10             | 4            | I/O   | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . This pin is an output when the hardware watchdog forces a system reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ALE/PROG    | 30         | 33             | 27           | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the low Byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during Flash programming. ALE can be disabled by setting SFR's AUXR. 0 bit. With this bit set, ALE will be inactive during internal fetches.                                                                                                                                                                                                                                                                   |  |

Table 12. Pin Description for 40 - 44 Pin Packages (Continued)

|          | Pin Number |     | Pin Number |      |                                                                                                                                                                                                                                                                                                                                  |  |

|----------|------------|-----|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Mnemonic | DIL        | LCC | VQFP44 1.4 | Туре | Name and Function                                                                                                                                                                                                                                                                                                                |  |

| PSEN     | 29         | 32  | 26         | 0    | Program Strobe Enable: The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory. |  |

| EA       | 31         | 35  | 29         | 1    | <b>External Access Enable:</b> $\overline{EA}$ must be externally held low to enable the device to fetch code from external program memory locations 0000H to FFFFH (RD). If security level 1 is programmed, $\overline{EA}$ will be internally latched on Reset.                                                                |  |

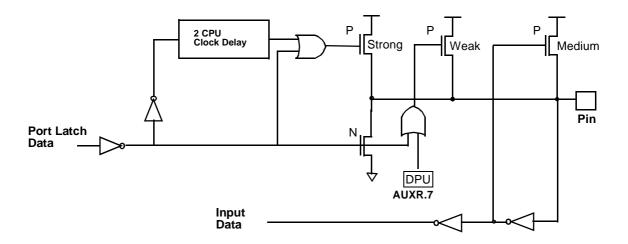

## **Port Types**

AT89C51RB2/RC2 I/O ports (P1, P2, P3) implement the quasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pull-up, called the "medium" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the permanent weak pull up of all ports when latch data is logical 0.

The quasi-bidirectional port configuration is shown in Figure 3.

Figure 3. Quasi-Bidirectional Output

## **Oscillator**

To optimize the power consumption and execution time needed for a specific task, an internal, prescaler feature has been implemented between the oscillator and the CPU and peripherals.

## Registers

Table 13. CKRL Register

CKRL - Clock Reload Register (97h)

| _ | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | CKRL7 | CKRL6 | CKRL5 | CKRL4 | CKRL3 | CKRL2 | CKRL1 | CKRL0 |

| Bit Number | Mnemonic | Description                           |

|------------|----------|---------------------------------------|

| 7:0        | CKRL     | Clock Reload Register Prescaler value |

Reset Value = 1111 1111b

Not bit addressable

Table 14. PCON Register

PCON – Power Control Register (87h)

| 7     | 6     | 5 | 4   | 3   | 2   | 1  | 0   |

|-------|-------|---|-----|-----|-----|----|-----|

| SMOD1 | SMOD0 | - | POF | GF1 | GF0 | PD | IDL |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                 |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | SMOD1        | Serial Port Mode bit 1 Set to select double baud rate in mode 1, 2 or 3.                                                                                    |

| 6          | SMOD0        | Serial Port Mode bit 0 Cleared to select SM0 bit in SCON register. Set to select FE bit in SCON register.                                                   |

| 5          | -            | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                                |

| 4          | POF          | Power-off Flag Cleared to recognize next reset type. Set by hardware when V <sub>CC</sub> rises from 0 to its nominal voltage. Can also be set by software. |

| 3          | GF1          | General-purpose Flag Cleared by software for general-purpose usage. Set by software for general-purpose usage.                                              |

| 2          | GF0          | General-purpose Flag Cleared by software for general-purpose usage. Set by software for general-purpose usage.                                              |

| 1          | PD           | Power-down Mode bit Cleared by hardware when reset occurs. Set to enter power-down mode.                                                                    |

| 0          | IDL          | Idle Mode bit Cleared by hardware when interrupt or reset occurs. Set to enter idle mode.                                                                   |

Reset Value = 00X1 0000b Not bit addressable

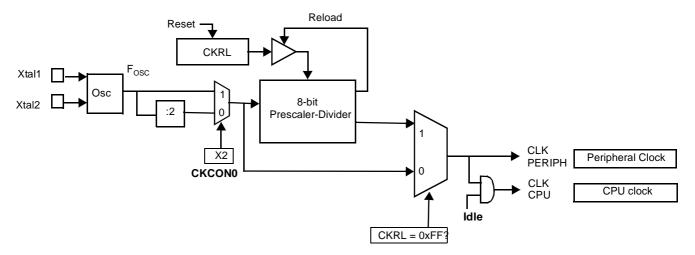

## Functional Block Diagram

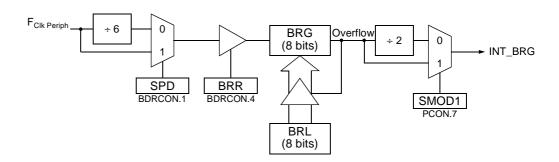

Figure 4. Functional Oscillator Block Diagram

#### **Prescaler Divider**

- A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh: F<sub>CLK CPU</sub> = F<sub>CLK PERIPH</sub> = F<sub>OSC</sub>/2 (Standard C51 feature)

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency  $F_{CLK \ CPU} = F_{CLK \ PERIPH} = F_{OSC}/1020 \ (Standard \ Mode)$   $F_{CLK \ CPU} = F_{CLK \ PERIPH} = F_{OSC}/510 \ (X2 \ Mode)$

- CKRL = FFh: maximum frequency

F<sub>CLK CPU</sub> = F<sub>CLK PERIPH</sub> = F<sub>OSC</sub>/2 (Standard Mode)

F<sub>CLK CPU</sub> = F<sub>CLK PERIPH</sub> = F<sub>OSC</sub> (X2 Mode)

F<sub>CLK CPU</sub> and F<sub>CLK PERIPH</sub>

In X2 Mode, for CKRL<>0xFF:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{2 \times (255 - CKRL)}$$

In X1 Mode, for CKRL<>0xFF then:

$$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{4 \times (255 - CKRL)}$$

#### **Enhanced Features**

In comparison to the original 80C52, the AT89C51RB2/RC2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- power-off flag

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the timer 2

#### X2 Feature

The AT89C51RB2/RC2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

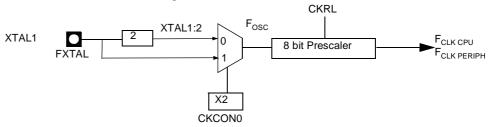

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

#### Description

The clock for the whole circuit and peripherals is first divided by 2 before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

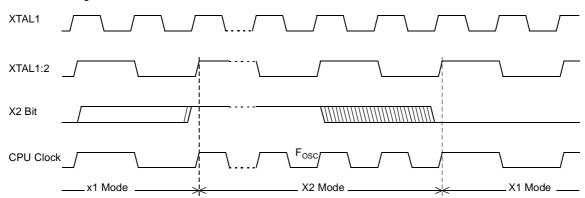

Figure 5 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1÷2 to avoid glitches when switching from X2 to X1 mode. Figure 6 shows the switching mode waveforms.

Figure 5. Clock Generation Diagram

Figure 6. Mode Switching Waveforms

The X2 bit in the CKCON0 register (see Table 15) allows a switch from 12 clock periods per instruction to 6 clock periods and vice versa. At reset, the speed is set according to X2 bit of Hardware Security Byte (HSB). By default, Standard mode is active. Setting the X2 bit activates the X2 feature (X2 mode).

The T0X2, T1X2, T2X2, UARTX2, PCAX2, and WDX2 bits in the CKCON0 register (Table 15) and SPIX2 bit in the CKCON1 register (see Table 16) allow a switch from standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2 mode.

## Table 15. CKCON0 Register

CKCON0 - Clock Control Register (8Fh)

| 7 | 6    | 5     | 4    | 3    | 2    | 1    | 0  |

|---|------|-------|------|------|------|------|----|

| - | WDX2 | PCAX2 | SIX2 | T2X2 | T1X2 | T0X2 | X2 |

|               | WEXE                                                                                 | TORKE OIKE TEKE TOKE KE                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                   |  |  |                  |  |  |  |

|---------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|------------------|--|--|--|

| Bit<br>Number | Bit<br>Mnemonic                                                                      | Description                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                       |  |  |                  |  |  |  |

| 7             | Reserved                                                                             |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   |  |  |                  |  |  |  |

| 6             | WDX2                                                                                 | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                             | Watchdog Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                     |  |  |                  |  |  |  |

| 5             | PCAX2                                                                                | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                             | Programmable Counter Array Clock This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.    |  |  |                  |  |  |  |

| 4             | SIX2                                                                                 | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                             | Enhanced UART Clock (Mode 0 and 2) (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle. |  |  |                  |  |  |  |

| 3             | T2X2                                                                                 | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                             | Timer 2 Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                      |  |  |                  |  |  |  |

| 2             | T1X2                                                                                 | (This control<br>has no effect<br>Cleared to se                                                                                                                                                                                             | Timer 1 Clock  (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).  Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                    |  |  |                  |  |  |  |

| 1             | T0X2                                                                                 | Timer0 Clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect). Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle. |                                                                                                                                                                                                                                                                   |  |  |                  |  |  |  |

| 0             | CPU Clock Cleared to select 12 clock periods per machine cycle (STD, X1 mode) for CP |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                   |  |  | rcle (X2<br>d by |  |  |  |

Reset Value = 0000 000'HSB. X2'b (see Table 65 "Hardware Security Byte") Not bit addressable

## Table 16. CKCON1 Register

CKCON1 - Clock Control Register (AFh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|---|---|---|---|---|---|---|-------|

| - | - | - | - | - | - | • | SPIX2 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                        |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved                                                                                                                                                                                                                           |

| 6             | -               | Reserved                                                                                                                                                                                                                           |

| 5             | -               | Reserved                                                                                                                                                                                                                           |

| 4             | -               | Reserved                                                                                                                                                                                                                           |

| 3             | -               | Reserved                                                                                                                                                                                                                           |

| 2             | -               | Reserved                                                                                                                                                                                                                           |

| 1             | -               | Reserved                                                                                                                                                                                                                           |

| 0             | SPIX2           | SPI (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).  Clear to select 6 clock periods per peripheral clock cycle.  Set to select 12 clock periods per peripheral clock cycle. |

Reset Value = XXXX XXX0b Not bit addressable

## **Dual Data Pointer Register (DPTR)**

The additional data pointer can be used to speed up code execution and reduce code size.

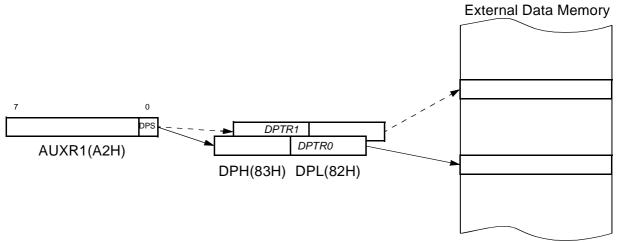

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1.0 (see Table 17) that allows the program code to switch between them (see Figure 7).

Figure 7. Use of Dual Pointer

Table 17. AUXR1 register

AUXR1- Auxiliary Register 1(0A2h)

| 7 | 6 | 5      | 4 | 3   | 2 | 1 | 0   |

|---|---|--------|---|-----|---|---|-----|

| - | - | ENBOOT | - | GF3 | 0 | - | DPS |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                    |

|---------------|-----------------|------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                   |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                   |

| 5             | ENBOOT          | Enable Boot Flash Cleared to disable boot ROM. Set to map the boot ROM between F800h - 0FFFFh. |

| 4             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                   |

| 3             | GF3             | This bit is a general-purpose user flag. <sup>(1)</sup>                                        |

| 2             | 0               | Always Cleared                                                                                 |

| 1             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                   |

| 0             | DPS             | Data Pointer Selection Cleared to select DPTR0. Set to select DPTR1.                           |

Reset Value = XXXX XX0X0b

#### Not bit addressable

Note: 1. Bit 2 stuck at 0; this allows using INC AUXR1 to toggle DPS without changing GF3.

#### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Modifies DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added 00A2 AUXR1 EQU 0A2H 0000 909000MOV DPTR, #SOURCE; address of SOURCE

0003 05A2 INC AUXR1; switch data pointers

0005 90A000 MOV DPTR, #DEST; address of DEST

0008 LOOP:

0008 05A2 INC AUXR1; switch data pointers