#### **Features**

- Utilizes the ARM7TDMI® ARM® Thumb® Processor Core

- High-performance 32-bit RISC Architecture

- High-density 16-bit Instruction Set

- Leader in MIPS/Watt

- Embedded ICE (In-circuit Emulation)

- 8K Bytes Internal SRAM

- Fully Programmable External Bus Interface (EBI)

- Maximum External Address Space of 64M Bytes

- Up to 8 Chip Selects

- Software Programmable 8/16-bit External Data Bus

- 8-channel Peripheral Data Controller

- 8-level Priority, Individually Maskable, Vectored Interrupt Controller

- 5 External Interrupts, Including a High-priority, Low-latency Interrupt Request

- 54 Programmable I/O Lines

- 6-channel 16-bit Timer/Counter

- 6 External Clock Inputs, 2 Multi-purpose I/O Pins per Channel

- 2 USARTs

- 2 Dedicated Peripheral Data Controller (PDC) Channels per USART

- Support for up to 9-bit Data Transfers

- 2 Master/Slave SPI Interfaces

- 2 Dedicated Peripheral Data Controller (PDC) Channels per SPI

- 8- to 16-bit Programmable Data Length

- 4 External Slave Chip Selects per SPI

- 3 System Timers

- Period Interval Timer (PIT); Real-time Timer (RTT); Watchdog Timer (WDT)

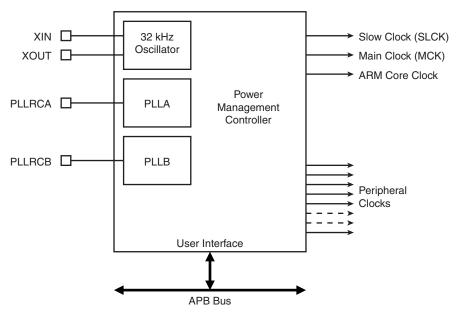

- Power Management Controller (PMC)

- CPU and Peripherals Can be Deactivated Individually

- Clock Generator with 32.768 kHz Low-power Oscillator and PLL

- Support for 38.4 kHz Crystals

- Software Programmable System Clock (up to 33 MHz)

- IEEE® 1149.1 JTAG Boundary Scan on All Active Pins

- Fully Static Operation: 0 Hz to 33 MHz, Internal Frequency Range at V<sub>DDCORE</sub> = 3.0V, 85° C

- 2.7V to 3.6V Core and PLL Operating Voltage Range; 2.7V to 5.5V I/O Operating Voltage Range

- -40° C to +85° C Temperature Range

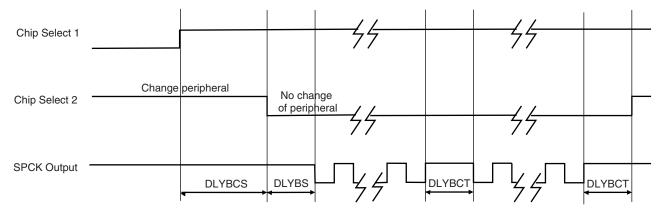

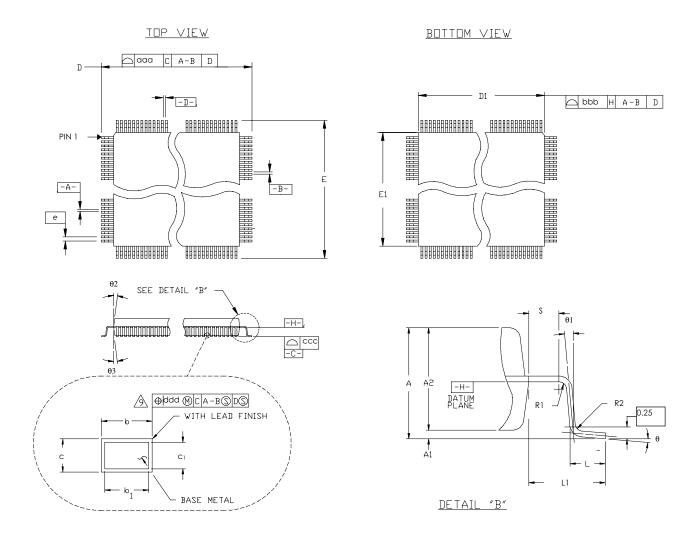

- Available in a 144-lead LQFP Package (Green) and a 144-ball BGA Package (RoHS compliant)

# AT91 ARM Thumb Microcontrollers

AT91M42800A

Rev. 1779D-ATARM-14-Apr-06

# 1. Description

The AT91M42800A is a member of the Atmel AT91 16/32-bit microcontroller family, which is based on the ARM7TDMI processor core. This processor has a high-performance 32-bit RISC architecture with a high-density 16-bit instruction set and very low power consumption. In addition, a large number of internally banked registers result in very fast exception handling, making the device ideal for real-time control applications. The AT91 ARM-based MCU family also features Atmel's high-density, in-system programmable, nonvolatile memory technology. The AT91M42800A has a direct connection to off-chip memory, including Flash, through the External Bus Interface.

The Power Management Controller allows the user to adjust device activity according to system requirements, and, with the 32.768 kHz low-power oscillator, enables the AT91M42800A to reduce power requirements to an absolute minimum. The AT91M42800A is manufactured using Atmel's high-density CMOS technology. By combining the ARM7TDMI processor core with on-chip SRAM and a wide range of peripheral functions including timers, serial communication controllers and a versatile clock generator on a monolithic chip, the AT91M42800A provides a highly flexible and cost-effective solution to many compute-intensive applications.

# 2. Pin Configuration

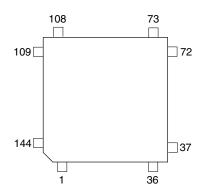

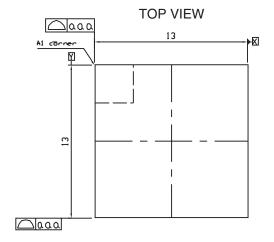

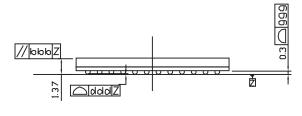

Figure 2-1. Pin Configuration in TQFP144 Package (Top View)

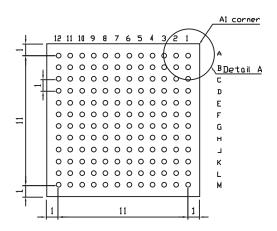

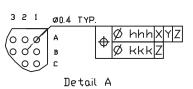

Figure 2-2. Pin Configuration in BGA144 Package (Top View)

|   | 1       | 2       | 3       | 4       | 5       | 6       | 7       | 8       | 9       | 10      | 11      | 12      |

|---|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Α | 0       | $\circ$ | ं       | $\circ$ | $\circ$ | ं       |

| В | $\circ$ |

| С | 0       | $\circ$ | 0       |

| D | 0       | $\circ$ |         |

| E | $\circ$ |

| F | $\circ$ |

| G | $\circ$ |

| Н | $\circ$ |         |

| J | 0       | $\circ$ |

| к | $\circ$ | ं       |

| L | ं       | $\circ$ | ं       |

| М | ं       | ं       | ं       | ं       | ं       | ं       | ं       | ं       | ं       | ं       | ं       | ं       |

Table 1. AT91M42800A Pinout in TQFP 144 Package

| Pin# | Name        |  |

|------|-------------|--|

| 1    | GND         |  |

| 2    | GND         |  |

| 3    | NLB/A0      |  |

| 4    | A1          |  |

| 5    | A2          |  |

| 6    | АЗ          |  |

| 7    | A4          |  |

| 8    | A5          |  |

| 9    | A6          |  |

| 10   | A7          |  |

| 11   | A8          |  |

| 12   | VDDIO       |  |

| 13   | GND         |  |

| 14   | A9          |  |

| 15   | A10         |  |

| 16   | A11         |  |

| 17   | A12         |  |

| 18   | A13         |  |

| 19   | A14         |  |

| 20   | A15         |  |

| 21   | A16         |  |

| 22   | A17         |  |

| 23   | A18         |  |

| 24   | VDDIO       |  |

| 25   | GND         |  |

| 26   | A19         |  |

| 27   | PB2/A20/CS7 |  |

| 28   | PB3/A21/CS6 |  |

| 29   | PB4/A22/CS5 |  |

| 30   | PB5/A23/CS4 |  |

| 31   | D0          |  |

| 32   | D1          |  |

| 33   | D2          |  |

| 34   | D3          |  |

| 35   | VDDCORE     |  |

| 36   | VDDIO       |  |

| ıt in TQ | FP 144 Package |

|----------|----------------|

| Pin#     | Name           |

| 37       | GND            |

| 38       | GND            |

| 39       | D4             |

| 40       | D5             |

| 41       | D6             |

| 42       | D7             |

| 43       | D8             |

| 44       | D9             |

| 45       | D10            |

| 46       | D11            |

| 47       | D12            |

| 48       | VDDIO          |

| 49       | GND            |

| 50       | D13            |

| 51       | D14            |

| 52       | D15            |

| 53       | PB6/TCLK0      |

| 54       | PB7/TIOA0      |

| 55       | PB8/TIOB0      |

| 56       | PB9/TCLK1      |

| 57       | PB10/TIOA1     |

| 58       | PB11/TIOB1     |

| 59       | PB12/TCLK2     |

| 60       | VDDIO          |

| 61       | GND            |

| 62       | PB13/TIOA2     |

| 63       | PB14/TIOB2     |

| 64       | PB15/TCLK3     |

| 65       | PB16/TIOA3     |

| 66       | PB17/TIOB3     |

| 67       | PB18/TCLK4     |

| 68       | PB19/TIOA4     |

| 69       | PB20/TIOB4     |

| 70       | PB21/TCLK5     |

| 71       | VDDCORE        |

| 72       | VDDIO          |

| 73         GND           74         GND           75         PB22/TIOA5           76         PB23/TIOB5           77         PA0/IRQ0           78         PA1/IRQ1           79         PA2/IRQ2           80         PA3/IRQ3           81         PA4/FIQ           82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1                                                      | Pin# | Name             |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|--|--|

| 75         PB22/TIOA5           76         PB23/TIOB5           77         PA0/IRQ0           78         PA1/IRQ1           79         PA2/IRQ2           80         PA3/IRQ3           81         PA4/FIQ           82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3                                    | 73   | GND              |  |  |

| 76 PB23/TIOB5 77 PA0/IRQ0 78 PA1/IRQ1 79 PA2/IRQ2 80 PA3/IRQ3 81 PA4/FIQ 82 PA5/SCK0 83 PA6/TXD0 84 VDDIO 85 GND 86 PA7/RXD0 87 PA8/SCK1 88 PA9/TXD1/NTRI 89 PA10/RXD1 90 PA11/SPCKA 91 PA12/MISOA 92 PA13/MOSIA 93 PA14/NPCSA0/NSSA 94 PA15/NPCSA1 95 PA16/NPCSA2 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 74   | GND              |  |  |

| 77         PA0/IRQ0           78         PA1/IRQ1           79         PA2/IRQ2           80         PA3/IRQ3           81         PA4/FIQ           82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE </td <td>75</td> <td>PB22/TIOA5</td> | 75   | PB22/TIOA5       |  |  |

| 78         PA1/IRQ1           79         PA2/IRQ2           80         PA3/IRQ3           81         PA4/FIQ           82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                    | 76   | PB23/TIOB5       |  |  |

| 79         PA2/IRQ2           80         PA3/IRQ3           81         PA4/FIQ           82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                  | 77   | PA0/IRQ0         |  |  |

| 80         PA3/IRQ3           81         PA4/FIQ           82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                | 78   | PA1/IRQ1         |  |  |

| 81         PA4/FIQ           82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                              | 79   | PA2/IRQ2         |  |  |

| 82         PA5/SCK0           83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                           | 80   | PA3/IRQ3         |  |  |

| 83         PA6/TXD0           84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                         | 81   | PA4/FIQ          |  |  |

| 84         VDDIO           85         GND           86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                       | 82   | PA5/SCK0         |  |  |

| 85 GND  86 PA7/RXD0  87 PA8/SCK1  88 PA9/TXD1/NTRI  89 PA10/RXD1  90 PA11/SPCKA  91 PA12/MISOA  92 PA13/MOSIA  93 PA14/NPCSA0/NSSA  94 PA15/NPCSA1  95 PA16/NPCSA2  96 VDDIO  97 GND  98 PA17/NPCSA3  99 PA18/SPCKB  100 PA19/MISOB  101 PA20/MOSIB  102 PA21/NPCSB0/NSSB  103 PA22/NPCSB1  104 PA23/NPCSB2  105 PA24/NPCSB3  106 PA25/MCKO  107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83   | PA6/TXD0         |  |  |

| 86         PA7/RXD0           87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                                                                           | 84   | VDDIO            |  |  |

| 87         PA8/SCK1           88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                                                                                                         | 85   | GND              |  |  |

| 88         PA9/TXD1/NTRI           89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                                                                                                                                       | 86   | PA7/RXD0         |  |  |

| 89         PA10/RXD1           90         PA11/SPCKA           91         PA12/MISOA           92         PA13/MOSIA           93         PA14/NPCSA0/NSSA           94         PA15/NPCSA1           95         PA16/NPCSA2           96         VDDIO           97         GND           98         PA17/NPCSA3           99         PA18/SPCKB           100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                          | 87   | PA8/SCK1         |  |  |

| 90 PA11/SPCKA 91 PA12/MISOA 92 PA13/MOSIA 93 PA14/NPCSA0/NSSA 94 PA15/NPCSA1 95 PA16/NPCSA2 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88   | PA9/TXD1/NTRI    |  |  |

| 91 PA12/MISOA 92 PA13/MOSIA 93 PA14/NPCSA0/NSSA 94 PA15/NPCSA1 95 PA16/NPCSA2 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 89   | PA10/RXD1        |  |  |

| 92 PA13/MOSIA 93 PA14/NPCSA0/NSSA 94 PA15/NPCSA1 95 PA16/NPCSA2 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90   | PA11/SPCKA       |  |  |

| 93 PA14/NPCSA0/NSSA 94 PA15/NPCSA1 95 PA16/NPCSA2 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91   | PA12/MISOA       |  |  |

| 94 PA15/NPCSA1 95 PA16/NPCSA2 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92   | PA13/MOSIA       |  |  |

| 95 PA16/NPCSA2 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93   | PA14/NPCSA0/NSSA |  |  |

| 96 VDDIO 97 GND 98 PA17/NPCSA3 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94   | PA15/NPCSA1      |  |  |

| 97 GND  98 PA17/NPCSA3  99 PA18/SPCKB  100 PA19/MISOB  101 PA20/MOSIB  102 PA21/NPCSB0/NSSB  103 PA22/NPCSB1  104 PA23/NPCSB2  105 PA24/NPCSB3  106 PA25/MCKO  107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95   | PA16/NPCSA2      |  |  |

| 98 PA17/NPCSA3  99 PA18/SPCKB  100 PA19/MISOB  101 PA20/MOSIB  102 PA21/NPCSB0/NSSB  103 PA22/NPCSB1  104 PA23/NPCSB2  105 PA24/NPCSB3  106 PA25/MCKO  107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96   | VDDIO            |  |  |

| 99 PA18/SPCKB 100 PA19/MISOB 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 97   | GND              |  |  |

| 100         PA19/MISOB           101         PA20/MOSIB           102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98   | PA17/NPCSA3      |  |  |

| 101 PA20/MOSIB 102 PA21/NPCSB0/NSSB 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99   | PA18/SPCKB       |  |  |

| 102         PA21/NPCSB0/NSSB           103         PA22/NPCSB1           104         PA23/NPCSB2           105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100  | PA19/MISOB       |  |  |

| 103 PA22/NPCSB1 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 101  | PA20/MOSIB       |  |  |

| 104 PA23/NPCSB2 105 PA24/NPCSB3 106 PA25/MCKO 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102  | PA21/NPCSB0/NSSB |  |  |

| 105         PA24/NPCSB3           106         PA25/MCKO           107         VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 103  | PA22/NPCSB1      |  |  |

| 106 PA25/MCKO<br>107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 104  | PA23/NPCSB2      |  |  |

| 107 VDDCORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 105  | PA24/NPCSB3      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106  | PA25/MCKO        |  |  |

| 108 VDDIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107  | VDDCORE          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 108  | VDDIO            |  |  |

| Pin# | Name     |

|------|----------|

| 109  | GND      |

| 110  | GND      |

| 111  | PA26     |

| 112  | MODE0    |

| 113  | XIN      |

| 114  | XOUT     |

| 115  | GND      |

| 116  | PLLRCA   |

| 117  | VDDPLL   |

| 118  | PLLRCB   |

| 119  | VDDPLL   |

| 120  | VDDIO    |

| 121  | GND      |

| 122  | NWDOVF   |

| 123  | PA27/BMS |

| 124  | MODE1    |

| 125  | TMS      |

| 126  | TDI      |

| 127  | TDO      |

| 128  | TCK      |

| 129  | NTRST    |

| 130  | NRST     |

| 131  | PA28     |

| 132  | VDDIO    |

| 133  | GND      |

| 134  | PA29/PME |

| 135  | NWAIT    |

| 136  | NOE/NRD  |

| 137  | NWE/NWR0 |

| 138  | NUB/NWR1 |

| 139  | NCS0     |

| 140  | NCS1     |

| 141  | PB0/NCS2 |

| 142  | PB1/NCS3 |

| 143  | VDDCORE  |

| 144  | VDDIO    |

Table 2. AT91M42800A Pinout in BGA 144 Package

| Table 2 | . A 19 110142600A F |  |  |

|---------|---------------------|--|--|

| Pin#    | Name                |  |  |

| A1      | PB1/NCS3            |  |  |

| A2      | NCS0                |  |  |

| А3      | NCS1                |  |  |

| A4      | GND                 |  |  |

| A5      | PLLRCB              |  |  |

| A6      | GND                 |  |  |

| A7      | PLLRCA              |  |  |

| A8      | GND                 |  |  |

| A9      | XOUT                |  |  |

| A10     | XIN                 |  |  |

| A11     | MODE0               |  |  |

| A12     | PA22/NPCSB1         |  |  |

| B1      | NUB/NWR1            |  |  |

| B2      | PB0/NCS2            |  |  |

| В3      | VDDCORE             |  |  |

| B4      | NWE/NWR0            |  |  |

| B5      | VDDPLL              |  |  |

| В6      | TDO                 |  |  |

| В7      | VDDPLL              |  |  |

| B8      | NWDOVF              |  |  |

| В9      | PA26                |  |  |

| B10     | PA19/MISOB          |  |  |

| B11     | PA24/NPCSB3         |  |  |

| B12     | PA23/NPCSB2         |  |  |

| C1      | NLB/A0              |  |  |

| C2      | A1                  |  |  |

| C3      | VDDIO               |  |  |

| C4      | NOE/NRD             |  |  |

| C5      | VDDIO               |  |  |

| C6      | NRST                |  |  |

| C7      | TDI                 |  |  |

| C8      | VDDIO               |  |  |

| C9      | PA27/BMS            |  |  |

| C10     | VDDIO               |  |  |

| C11     | VDDCORE             |  |  |

| C12     | PA20/MOSIB          |  |  |

|         | <u> </u>            |  |  |

| III DGA | 144 Раскаде |  |  |  |

|---------|-------------|--|--|--|

| Pin#    | Name        |  |  |  |

| D1      | A2          |  |  |  |

| D2      | A3          |  |  |  |

| D3      | A4          |  |  |  |

| D4      | NWAIT       |  |  |  |

| D5      | PA29/PME    |  |  |  |

| D6      | PA28        |  |  |  |

| D7      | TCK         |  |  |  |

| D8      | TMS         |  |  |  |

| D9      | MODE1       |  |  |  |

| D10     | PA25/MCKO   |  |  |  |

| D11     | PA21/NPCSB0 |  |  |  |

| D12     | PA18/SPCKB  |  |  |  |

| E1      | A7          |  |  |  |

| E2      | VDDIO       |  |  |  |

| E3      | A6          |  |  |  |

| E4      | A5          |  |  |  |

| E5      | GND         |  |  |  |

| E6      | GND         |  |  |  |

| E7      | GND         |  |  |  |

| E8      | NTRST       |  |  |  |

| E9      | PA13/MOSIA  |  |  |  |

| E10     | PA16/NPCSA2 |  |  |  |

| E11     | VDDIO       |  |  |  |

| E12     | PA17/NPCSA3 |  |  |  |

| F1      | A8          |  |  |  |

| F2      | A12         |  |  |  |

| F3      | A9          |  |  |  |

| F4      | A10         |  |  |  |

| F5      | GND         |  |  |  |

| F6      | GND         |  |  |  |

| F7      | GND         |  |  |  |

| F8      | GND         |  |  |  |

| F9      | PA12/MISOA  |  |  |  |

| F10     | PA15/NPCSA1 |  |  |  |

| F11     | PA11/SPCKA  |  |  |  |

| F12     | PA14/NPCSA0 |  |  |  |

| Pin# | Name          |  |  |  |

|------|---------------|--|--|--|

| G1   | A17           |  |  |  |

| G2   | A16           |  |  |  |

| G3   | A11           |  |  |  |

| G4   | A13           |  |  |  |

| G5   | GND           |  |  |  |

| G6   | GND           |  |  |  |

| G7   | GND           |  |  |  |

| G8   | GND           |  |  |  |

| G9   | PA9/TXD1/NTRI |  |  |  |

| G10  | PA10/RXD1     |  |  |  |

| G11  | PA8/SCK1      |  |  |  |

| G12  | PA7/RXD0      |  |  |  |

| H1   | A18           |  |  |  |

| H2   | VDDIO         |  |  |  |

| НЗ   | A15           |  |  |  |

| H4   | A14           |  |  |  |

| H5   | A19           |  |  |  |

| H6   | GND           |  |  |  |

| H7   | GND           |  |  |  |

| H8   | GND           |  |  |  |

| H9   | PA6/TXD0      |  |  |  |

| H10  | PA4/FIQ       |  |  |  |

| H11  | VDDIO         |  |  |  |

| H12  | PA5/SCK0      |  |  |  |

| J1   | PB5/A23/CS4   |  |  |  |

| J2   | D0            |  |  |  |

| J3   | PB4/A22/CS5   |  |  |  |

| J4   | PB3/A21/CS6   |  |  |  |

| J5   | PB2/A20/CS7   |  |  |  |

| J6   | D15           |  |  |  |

| J7   | PB6/TCLK0     |  |  |  |

| J8   | PB10/TIOA1    |  |  |  |

| J9   | PA3/IRQ3      |  |  |  |

| J10  | PA2/IRQ2      |  |  |  |

| J11  | PA0/IRQ0      |  |  |  |

| J12  | PA1/IRQ1      |  |  |  |

| Pin# | Name       |  |  |  |

|------|------------|--|--|--|

| K1   | D1         |  |  |  |

| K2   | VDDCORE    |  |  |  |

| K3   | VDDIO      |  |  |  |

| K4   | D9         |  |  |  |

| K5   | D10        |  |  |  |

| K6   | D14        |  |  |  |

| K7   | PB9/TCLK1  |  |  |  |

| K8   | PB13/TIOA2 |  |  |  |

| K9   | PB11/TIOB1 |  |  |  |

| K10  | VDDIO      |  |  |  |

| K11  | PB16/TIOA3 |  |  |  |

| K12  | PB23/TIOB5 |  |  |  |

| L1   | D3         |  |  |  |

| L2   | D2         |  |  |  |

| L3   | D5         |  |  |  |

| L4   | D8         |  |  |  |

| L5   | VDDIO      |  |  |  |

| L6   | D13        |  |  |  |

| L7   | PB8/TIOB0  |  |  |  |

| L8   | VDDIO      |  |  |  |

| L9   | PB17/TIOB3 |  |  |  |

| L10  | VDDCORE    |  |  |  |

| L11  | PB20/TIOB4 |  |  |  |

| L12  | PB22/TIOA5 |  |  |  |

| M1   | D4         |  |  |  |

| M2   | D6         |  |  |  |

| М3   | D7         |  |  |  |

| M4   | D11        |  |  |  |

| M5   | D12        |  |  |  |

| M6   | PB7/TIOA0  |  |  |  |

| M7   | PB12/TCLK2 |  |  |  |

| M8   | PB15/TCLK3 |  |  |  |

| M9   | PB14/TIOB2 |  |  |  |

| M10  | PB18/TCLK4 |  |  |  |

| M11  | PB19/TIOA4 |  |  |  |

| M12  | PB21/TCLK5 |  |  |  |

# 3. Pin Description

Table 3. AT91M42800A Pin Description

| Module | Name                               | Function                        | Туре   | Active<br>Level | Comments                   |

|--------|------------------------------------|---------------------------------|--------|-----------------|----------------------------|

|        | A0 - A23                           | Address Bus                     | Output | _               | All valid after reset      |

|        | D0 - D15                           | Data Bus                        | I/O    | _               |                            |

|        | CS4 - CS7                          | Chip Select                     | Output | High            | A23 - A20 after reset      |

|        | NCS0 - NCS3                        | Chip Select                     | Output | Low             |                            |

|        | NWR0                               | Lower Byte 0 Write Signal       | Output | Low             | Used in Byte Write option  |

|        | NWR1                               | Lower Byte 1 Write Signal       | Output | Low             | Used in Byte Write option  |

| EDI    | NRD                                | Read Signal                     | Output | Low             | Used in Byte Write option  |

| EBI    | NWE                                | Write Enable                    | Output | Low             | Used in Byte Select option |

|        | NOE                                | Output Enable                   | Output | Low             | Used in Byte Select option |

|        | NUB                                | Upper Byte Select (16-bit SRAM) | Output | Low             | Used in Byte Select option |

|        | NLB                                | Lower Byte Select (16-bit SRAM) | Output | Low             | Used in Byte Select option |

|        | NWAIT                              | Wait Input                      | Input  | Low             |                            |

|        | BMS                                | Boot Mode Select                | Input  | _               | Sampled during reset       |

|        | PME                                | Protect Mode Enable             | Input  | High            | PIO-controlled after reset |

| A10    | IRQ0 - IRQ3                        | External Interrupt Request      | Input  | _               | PIO-controlled after reset |

| AIC    | FIQ                                | Fast External Interrupt Request | Input  | _               | PIO-controlled after reset |

|        | TCLK0 - TCLK5                      | Timer External Clock            | Input  | _               | PIO-controlled after reset |

| тс     | TIOA0 - TIOA5                      | Multi-purpose Timer I/O Pin A   | I/O    | _               | PIO-controlled after reset |

|        | TIOB0 - TIOB5                      | Multi-purpose Timer I/O Pin B   | I/O    | _               | PIO-controlled after reset |

|        | SCK0 - SCK1                        | External Serial Clock           | I/O    | _               | PIO-controlled after reset |

| USART  | TXD0 - TXD1                        | Transmit Data Output            | Output | _               | PIO-controlled after reset |

|        | RXD0 - RXD1                        | Receive Data Input              | Input  | _               | PIO-controlled after reset |

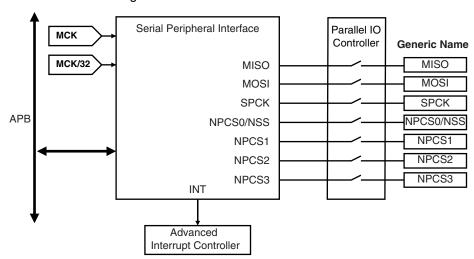

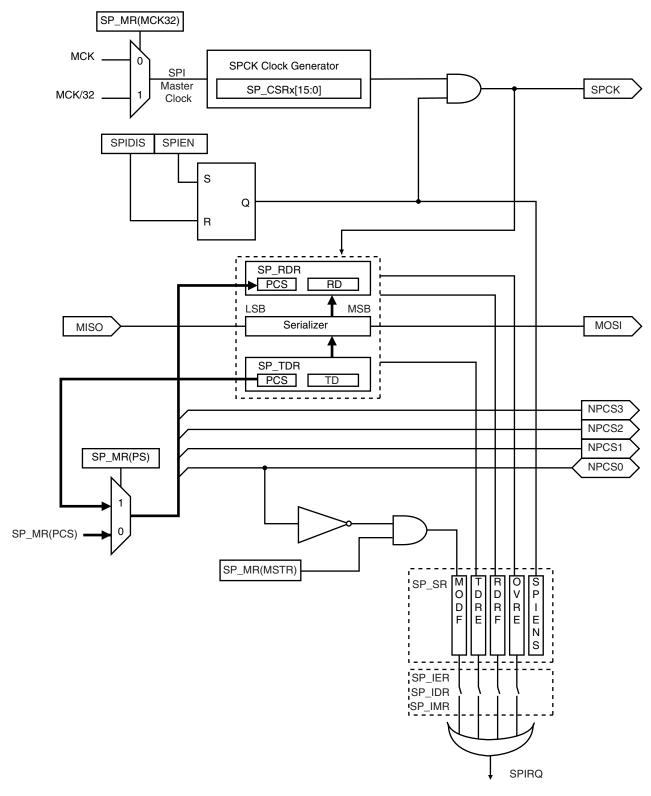

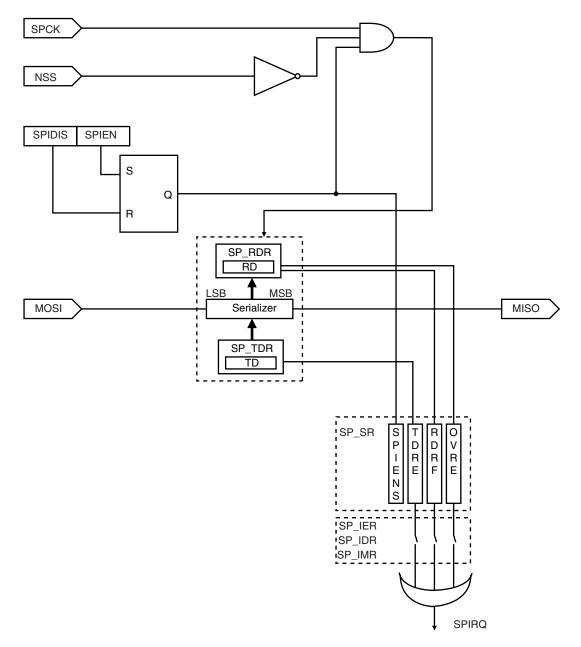

|        | SPCKA/SPCKB                        | Clock                           | I/O    | _               | PIO-controlled after reset |

|        | MISOA/MISOB                        | Master In Slave Out             | I/O    | _               | PIO-controlled after reset |

| SPIA   | MOSIA/MOSIB                        | Master Out Slave In             | I/O    | _               | PIO-controlled after reset |

| SPIB   | NSSA/NSSB                          | Slave Select                    | Input  | Low             | PIO-controlled after reset |

|        | NPCSA0 - NPCSA3<br>NPCSB0 - NPCSB3 | Peripheral Chip Selects         | Output | Low             | PIO-controlled after reset |

| DIO.   | PA0 - PA29                         | Programmable I/O Port A         | I/O    | _               | Input after reset          |

| PIO    | PB0 - PB23                         | Programmable I/O Port B         | I/O    | _               | Input after reset          |

| ST     | NWDOVF                             | Watchdog Timer Overflow         | Output | Low             | Open drain                 |

Table 3. AT91M42800A Pin Description (Continued)

| Module    | Name          | Function                           | Туре   | Active<br>Level | Comments                          |

|-----------|---------------|------------------------------------|--------|-----------------|-----------------------------------|

|           | XIN           | Oscillator Input or External Clock | Input  | _               |                                   |

|           | XOUT          | Oscillator Output                  | Output | _               |                                   |

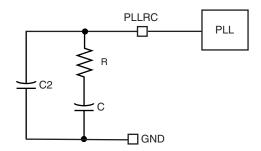

| CLOCK     | PLLRCA        | RC Filter for PLL A                | Input  | _               |                                   |

|           | PLLRCB        | RC Filter for PLL B                | Input  | _               |                                   |

|           | МСКО          | Clock Output                       | Output | _               |                                   |

| Test and  | NRST          | Hardware Reset Input               | Input  | Low             | Schmitt trigger                   |

| Reset     | MODE0 - MODE1 | Mode Selection                     | Input  |                 |                                   |

|           | TMS           | Test Mode Select                   | Input  | _               | Schmitt trigger, internal pull-up |

|           | TDI           | Test Data In                       | Input  | _               | Schmitt trigger, internal pull-up |

| JTAG/ICE  | TDO           | Test Data Out                      | Output | _               |                                   |

|           | TCK           | Test Clock                         | Input  | _               | Schmitt trigger, internal pull-up |

|           | NTRST         | Test Reset Input                   | Input  | Low             | Schmitt trigger, internal pull-up |

| Emulation | NTRI          | Tri-state Mode Enable              | Input  | Low             | Sampled during reset              |

|           | VDDIO         | I/O Power                          | Power  | _               | 3V or 5V nominal supply           |

| Damer     | VDDCORE       | Core Power                         | Power  | _               | 3V nominal supply                 |

| Power     | VDDPLL        | PLL Power                          | Power  | _               | 3V nominal supply                 |

|           | GND           | Ground                             | Ground | _               |                                   |

# 4. Block Diagram

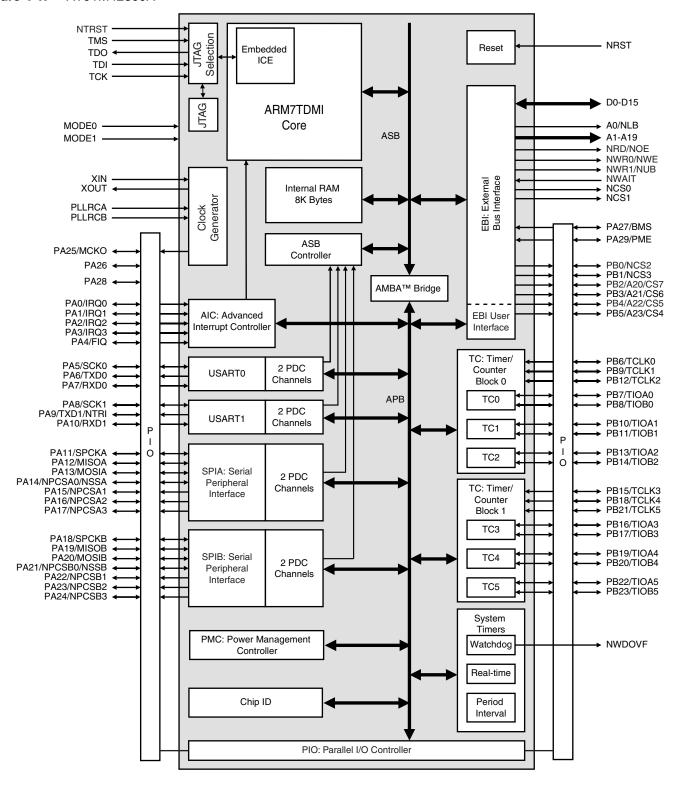

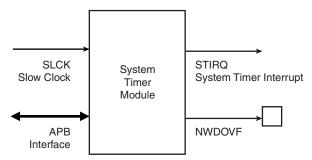

Figure 4-1. AT91M42800A

#### 5. Architectural Overview

The AT91M42800A microcontroller integrates an ARM7TDMI with its embedded ICE interface, memories and peripherals. Its architecture consists of two main buses, the Advanced System Bus (ASB) and the Advanced Peripheral Bus (APB). Designed for maximum performance and controlled by the memory controller, the ASB interfaces the ARM7TDMI processor with the on-chip 32-bit memories, the External Bus Interface (EBI) and the AMBA<sup>™</sup> Bridge. The AMBA Bridge drives the APB, which is designed for accesses to on-chip peripherals and optimized for low power consumption.

The AT91M42800A microcontroller implements the ICE port of the ARM7TDMI processor on dedicated pins, offering a complete, low-cost and easy-to-use debug solution for target debugging.

#### 5.1 Memories

The AT91M42800A microcontroller embeds up to 8K bytes of internal SRAM. The internal memory is directly connected to the 32-bit data bus and is single-cycle accessible. This provides maximum performance of 30 MIPS at 33 MHz by using the ARM instruction set of the processor. The on-chip memory significantly reduces the system power consumption and improves its performance over external memory solutions.

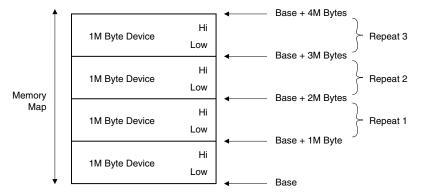

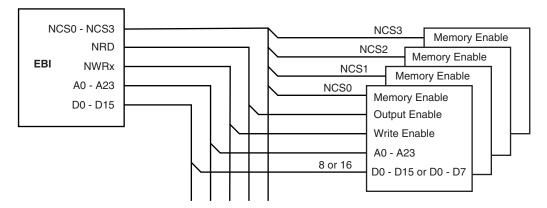

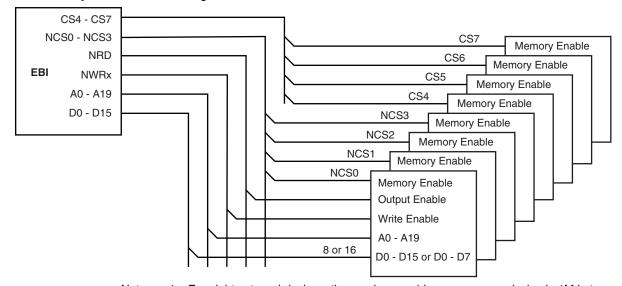

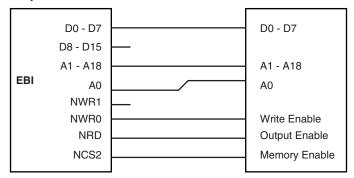

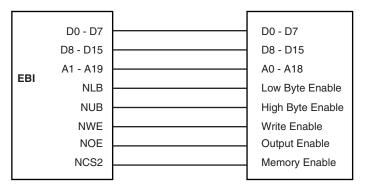

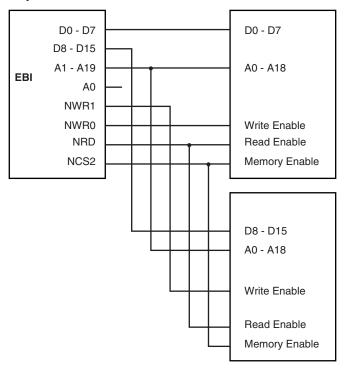

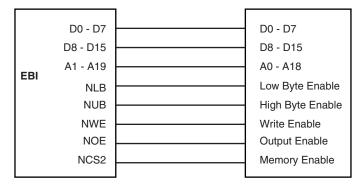

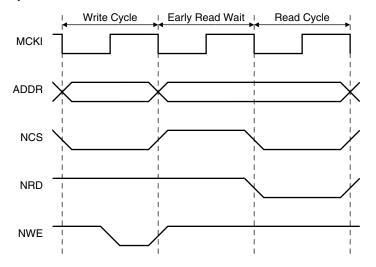

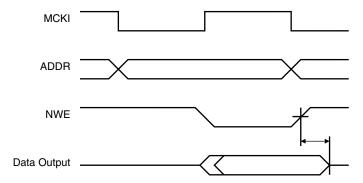

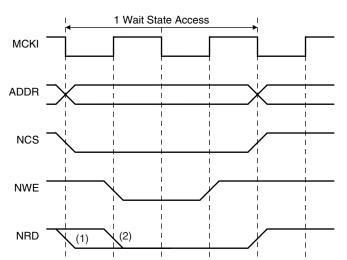

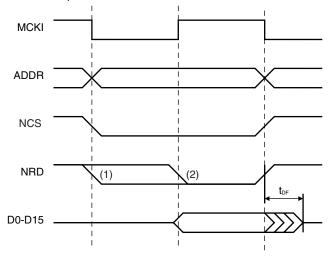

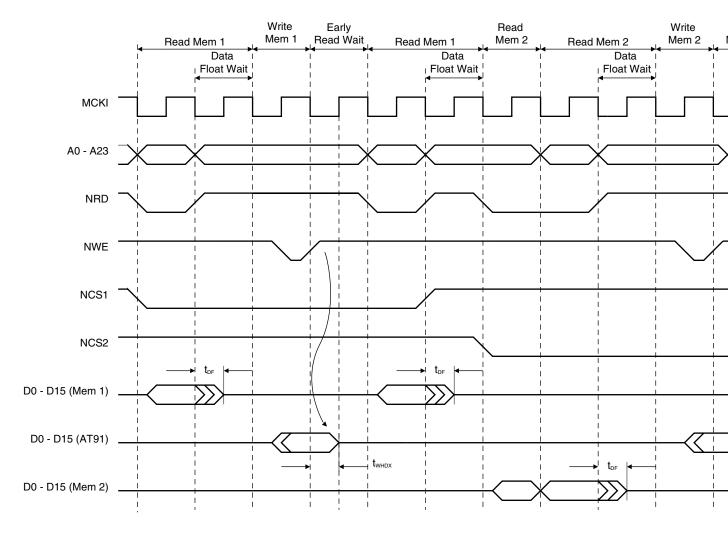

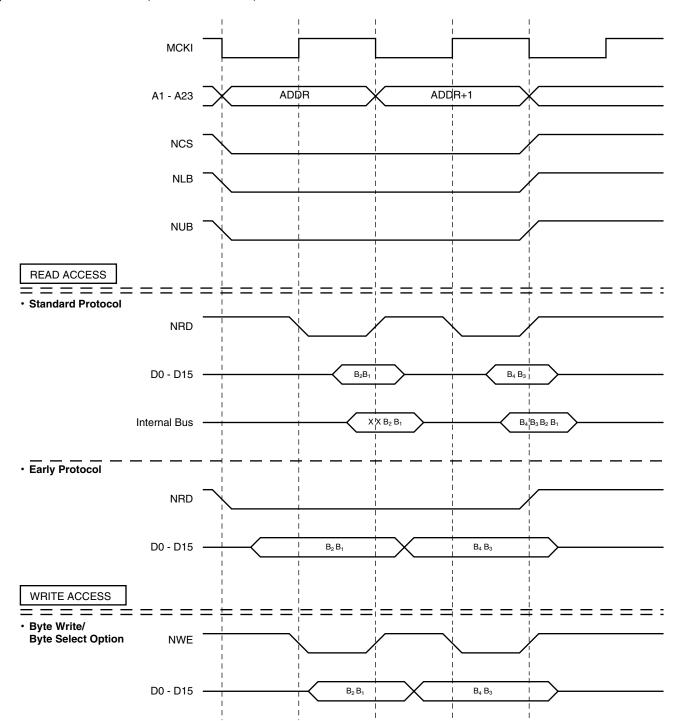

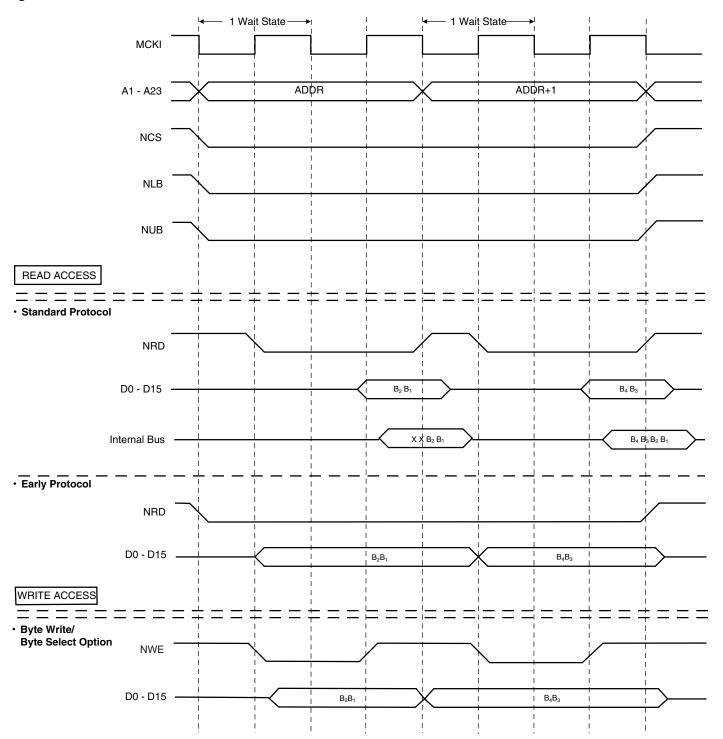

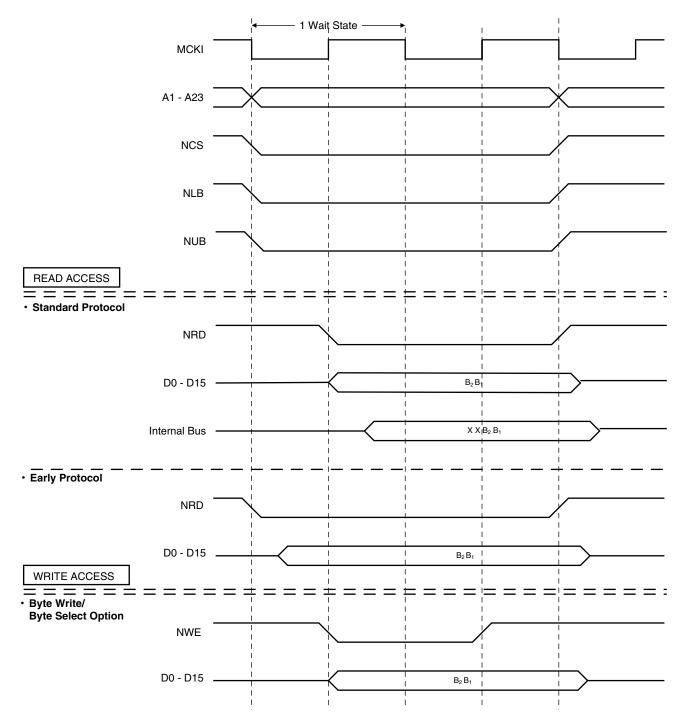

The AT91M42800A microcontroller features an External Bus Interface (EBI), which enables connection of external memories and application-specific peripherals. The EBI supports 8- or 16-bit devices and can use two 8-bit devices to emulate a single 16-bit device. The EBI implements the early read protocol, enabling single clock cycle memory accesses two times faster than standard memory interfaces.

# 5.2 Peripherals

The AT91M42800A microcontroller integrates several peripherals, which are classified as system or user peripherals. All on-chip peripherals are 32-bit accessible by the AMBA Bridge, and can be programmed with a minimum number of instructions. The peripheral register set is composed of control, mode, data, status and enable/disable/status registers.

An on-chip Peripheral Data Controller (PDC) transfers data between the on-chip USARTs/SPIs and the on- and off-chip memories without processor intervention. Most importantly, the PDC removes the processor interrupt handling overhead and significantly reduces the number of clock cycles required for a data transfer. It can transfer up to 64K continuous bytes without reprogramming the start address. As a result, the performance of the microcontroller is increased and the power consumption reduced.

#### 5.2.1 System Peripherals

The External Bus Interface (EBI) controls the external memory and peripheral devices via an 8- or 16-bit data bus and is programmed through the APB. Each chip select line has its own programming register.

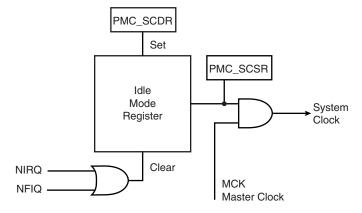

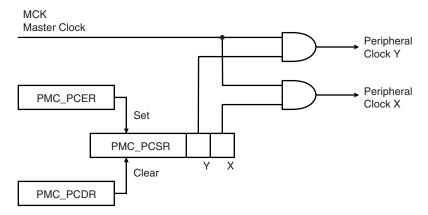

The Power Management Controller (PMC) optimizes power consumption of the product by controlling the clocking elements such as the oscillator and the PLLs, system and user peripheral clocks.

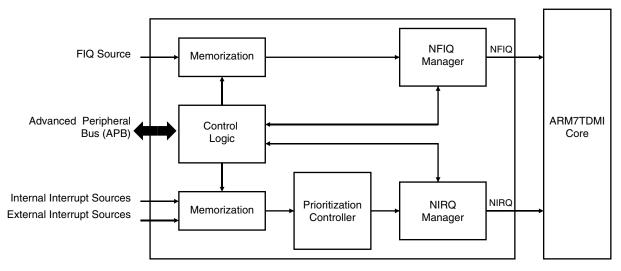

The Advanced Interrupt Controller (AIC) controls the internal sources from the internal peripherals and the five external interrupt lines (including the FIQ) to provide an interrupt and/or fast

interrupt request to the ARM7TDMI. It integrates an 8-level priority controller, and, using the Auto-vectoring feature, reduces the interrupt latency time.

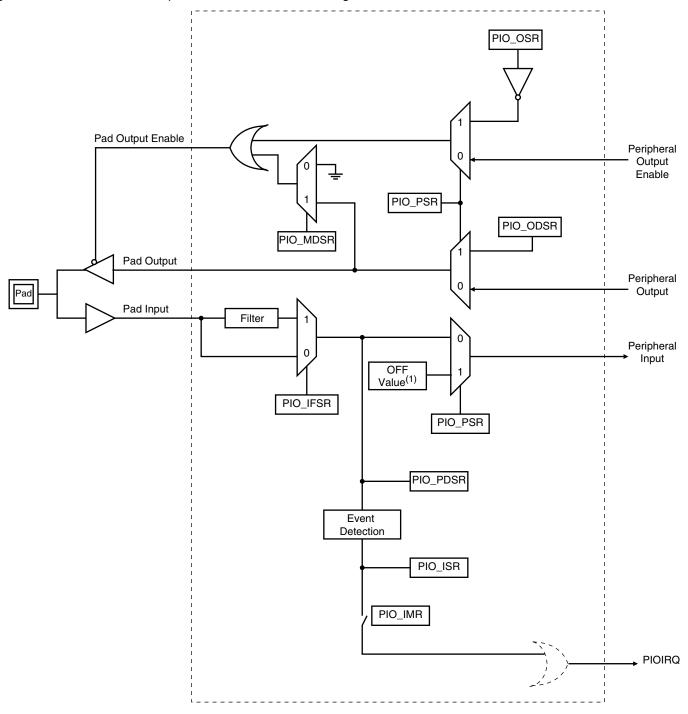

The Parallel Input/Output Controllers (PIOA, PIOB) controls up to 54 I/O lines. It enables the user to select specific pins for on-chip peripheral input/output functions, and general-purpose input/output signal pins. The PIO controllers can be programmed to detect an interrupt on a signal change from each line.

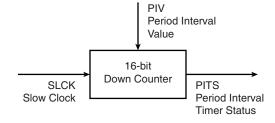

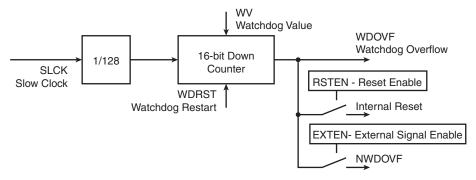

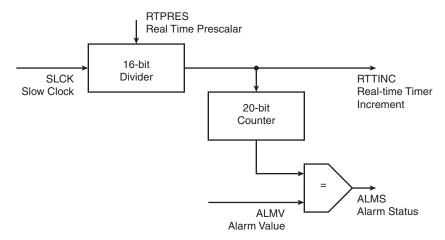

There are three embedded system timers. The Real-time Timer (RTT) counts elapsed seconds and can generate periodic or programmed interrupts. The Period Interval Timer (PIT) can be used as a user-programmable time-base, and can generate periodic ticks. The Watchdog (WD) can be used to prevent system lock-up if the software becomes trapped in a deadlock.

The Special Function (SF) module integrates the Chip ID and the Reset Status registers.

#### 5.2.2 User Peripherals

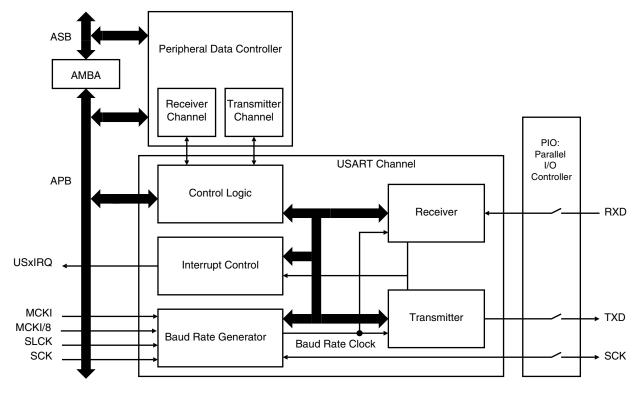

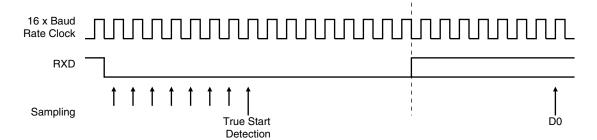

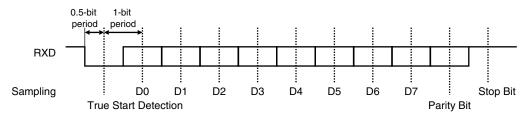

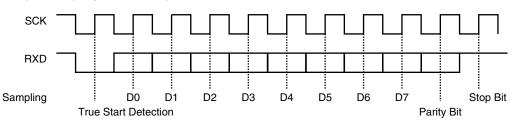

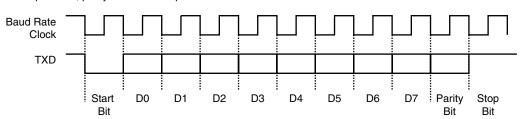

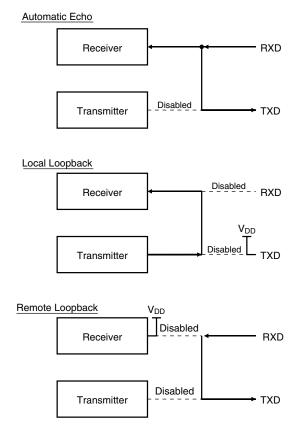

Two USARTs, independently configurable, enable communication at a high baud rate in synchronous or asynchronous mode. The format includes start, stop and parity bits and up to 9 data bits. Each USART also features a Time-out and a Time-guard register, facilitating the use of the two dedicated Peripheral Data Controller (PDC) channels.

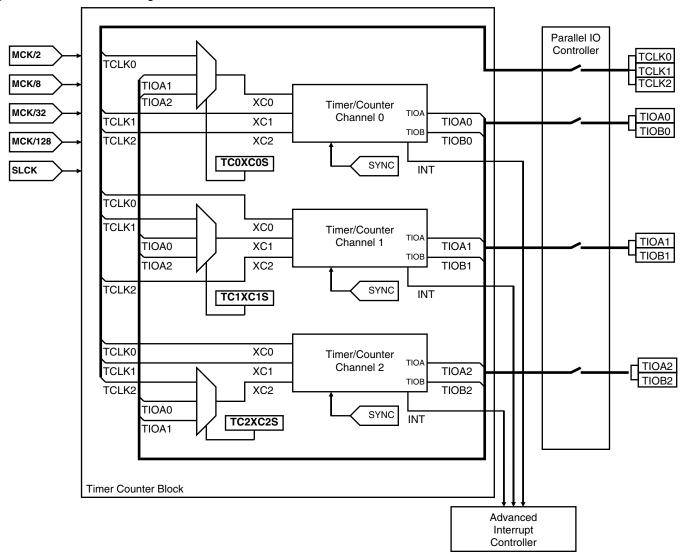

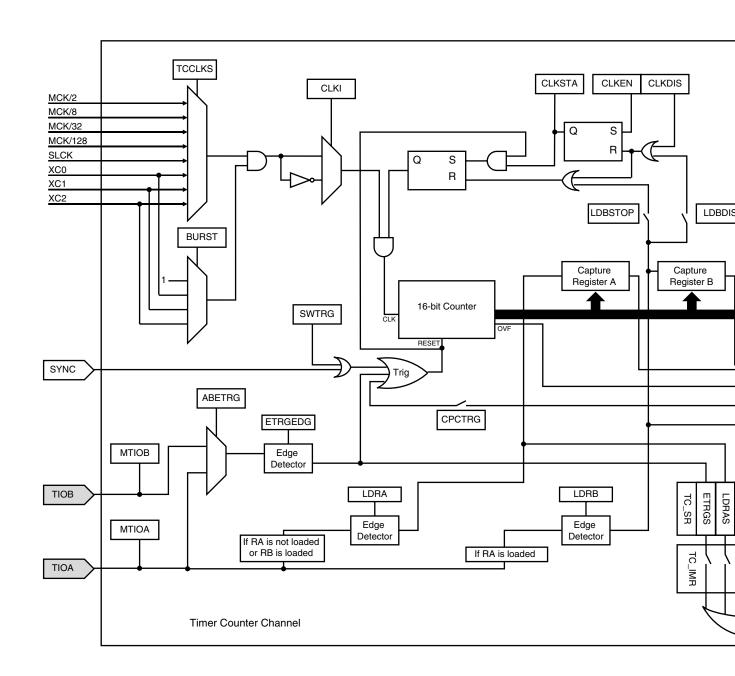

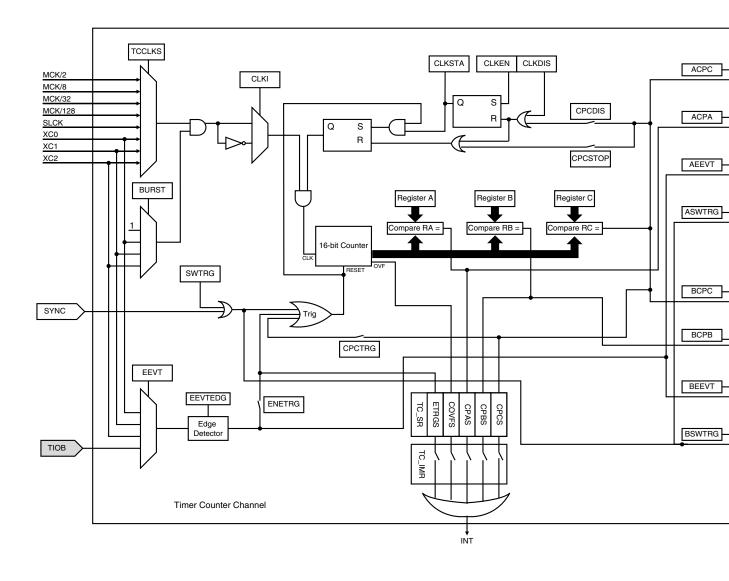

The two 3-channel, 16-bit Timer/Counters (TC) are highly-programmable and support capture or waveform modes. Each TC channel can be programmed to measure or generate different kinds of waves, and can detect and control two input/output signals. Each TC also has three external clock signals.

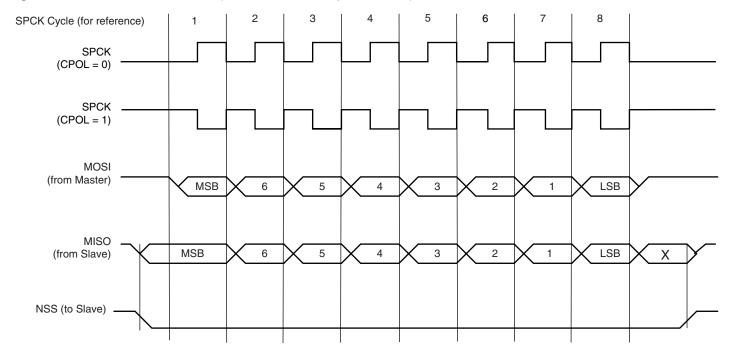

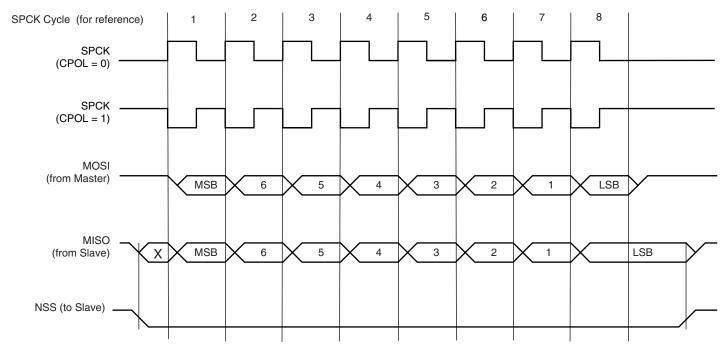

Two independently configurable SPIs provide communication with external devices in master or slave mode. Each has four external chip selects which can be connected to up to 15 devices. The data length is programmable, from 8- to 16-bit.

#### 6. Associated Documentation

**Table 6-1.** Associated Documentation

| Information                                                                                     | Document Title                                   |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Internal architecture of processor ARM/Thumb instruction sets Embedded in-circuit-emulator      | ARM7TDMI (Thumb) Datasheet                       |

| External memory interface mapping Peripheral operations Peripheral user interfaces              | AT91M42800A Datasheet (this document)            |

| DC characteristics Power consumption Thermal and reliability chonsiderations AC characteristics | AT91M42800A Electrical Characteristics Datasheet |

| Product overview Ordering information Packaging information Soldering profile                   | AT91M42800A Summary Datasheet                    |

## 7. Product Overview

# 7.1 Power Supply

The AT91M42800A has three kinds of power supply pins:

- VDDCORE pins that power the chip core

- VDDIO pins that power the I/O lines

- VDDPLL pins that power the oscillator and PLL cells

VDDCORE and VDDIO pins allow core power consumption to be reduced by supplying it with a lower voltage than the I/O lines. The VDDCORE pins must never be powered at a voltage greater than the supply voltage applied to the VDDIO.

The VDDPLL pin is used to supply the oscillator and both PLLs. The voltage applied on these pins is typically 3.3V, and it must not be lower than VDDCORE.

Typical supported voltage combinations are shown in the following table:

Table 1.

| Pins    | Nominal Supply Voltages |              |  |

|---------|-------------------------|--------------|--|

| VDDCORE | 3.3V                    | 3.0V or 3.3V |  |

| VDDIO   | 5.0V                    | 3.0V or 3.3V |  |

| VDDPLL  | 3.3V                    | 3.0V or 3.3V |  |

# 7.2 Input/Output Considerations

After the reset, the peripheral I/Os are initialized as inputs to provide the user with maximum flexibility. It is recommended that in any application phase, the inputs to the AT91M42800A microcontroller be held at valid logic levels to minimize the power consumption.

## 7.3 Operating Modes

The AT91M42800A has two pins dedicated to defining MODE0 and MODE1 operating modes. These pins allow the user to enter the device in Boundary Scan mode. They also allow the user to run the processor from the on-chip oscillator output and from an external clock by bypassing the on-chip oscillator. The last mode is reserved for test purposes. A chip reset must be performed (NRST and NTRST) after MODE0 and/or MODE1 have been changed.

**Table 7-1.**

| MODE0 | MODE1 | Operating Mode                                          |

|-------|-------|---------------------------------------------------------|

| 0     | 0     | Normal operating mode by using the on-chip oscillator   |

| 0     | 1     | Boundary Scan Mode                                      |

| 1     | 0     | Normal operating mode by using an external clock on XIN |

| 1     | 1     | Reserved for test                                       |

**Warning:** The user must take the external oscillator frequency into account so that it is consistent with the minimum access time requested by the memory device used at the boot. Both the default EBI setting (zero wait state) on Chip Select 0 (See "Boot on NCS0" on page 29) and the minimum access time of the boot memory are two parameters that determine this maximum frequency of the external oscillator.

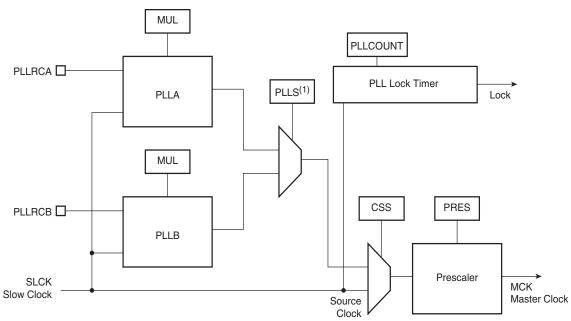

#### 7.4 Clock Generator

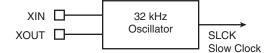

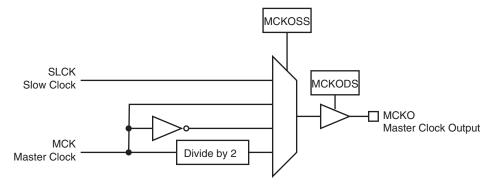

The AT91M42800A microcontroller embeds a 32.768 kHz oscillator that generates the Slow Clock (SLCK). This on-chip oscillator can be bypassed by setting the correct logical level on the MODE0 and MODE1 pins, as shown above. In this case, SLCK equals XIN.

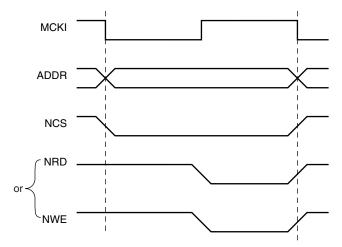

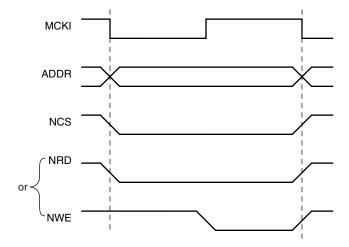

The AT91M42800A microcontroller has a fully static design and works either on the Master Clock (MCK), generated from the Slow Clock by means of the two integrated PLLs, or on the Slow Clock (SLCK).

These clocks are also provided as an output of the device on the pin MCKO, which is multiplexed with a general-purpose I/O line. While NRST is active, and after the reset, the MCKO is valid and outputs an image of the SLCK signal. The PIO Controller must be programmed to use this pin as standard I/O line.

#### 7.5 Reset

Reset initializes the user interface registers to their default states as defined in the peripheral sections of this datasheet and forces the ARM7TDMI to perform the next instruction fetch from address zero. Except for the program counter, the ARM core registers do not have defined reset states. When reset is active, the inputs of the AT91M42800A must be held at valid logic levels. The EBI address lines drive low during reset. All the peripheral clocks are disabled during reset to save power.

#### **7.5.1** NRST Pin

NRST is the active low reset input. It is asserted asynchronously, but exit from reset is synchronized internally to the slow clock (SLCK). At power-up, NRST must be active until the on-chip oscillator is stable. During normal operation, NRST must be active for a minimum of 10 SLCK clock cycles to ensure correct initialization.

The pins BMS and NTRI are sampled during the 10 SLCK clock cycles just prior to the rising edge of NRST.

The NRST pin has no effect on the on-chip Embedded ICE logic.

#### 7.5.2 NTRST Pin

The NTRST control pin initializes the selected TAP controller. The TAP controller involved in this reset is determined according to the initial logical state applied on the JTAGSEL pin after the last valid NRST.

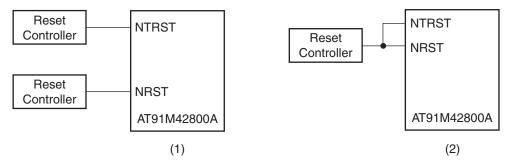

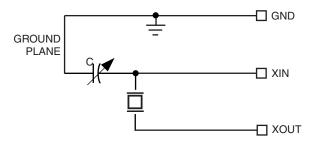

In either Boundary Scan or ICE Mode, a reset can be performed from the same or different circuitry, as shown in Figure 7-1 below. But in all cases, the NTRST like the NRST signal, must be asserted after each power-up. (See the AT91M42800A Electrical Datasheet, Atmel Lit. No. 1776, for the necessary minimum pulse assertion time.)

Figure 7-1. Separate or Common Reset Management

Notes: 1. NRST and NTRST handling in Debug Mode during development.

2. NRST and NTRST handling during production.

In order to benefit from the separation of NRST and NTRST during the debug phase of development, the user must independently manage both signals as shown in example (1) of Figure 7-1 above. However, once debug is completed, both signals are easily managed together during production as shown in example (2) of Figure 7-1 above.

#### 7.5.3 Watchdog Reset

The internally generated watchdog reset has the same effect as the NRST pin, except that the pins BMS and NTRI are not sampled. Boot mode and Tri-state mode are not updated. The NRST pin has priority if both types of reset coincide.

#### 7.6 Emulation Functions

#### 7.6.1 Tri-state Mode

The AT91M42800A provides a Tri-state mode, which is used for debug purposes in order to connect an emulator probe to an application board. In Tri-state mode the AT91M42800A continues to function, but all the output pin drivers are tri-stated.

To enter Tri-state mode, the pin NTRI must be held low during the last 10 SLCK clock cycles before the rising edge of NRST. For normal operation, the pin NTRI must be held high during reset, by a resistor of up to  $400 \text{ k}\Omega$  NTRI must be driven to a valid logic value during reset.

NTRI is multiplexed with Parallel I/O PA9 and USART 1 serial data transmit line TXD1.

Standard RS232 drivers generally contain internal 400 k $\Omega$  pull-up resistors. If TXD1 is connected to one of these drivers, this pull-up will ensure normal operation, without the need for an additional external resistor.

#### 7.6.2 Embedded ICE

ARM standard embedded in-circuit emulation is supported via the JTAG/ICE port. It is connected to a host computer via an embedded ICE Interface.

Embedded ICE mode is selected when MODE1 is low.

It is not possible to switch directly between ICE and JTAG operations. A chip reset must be performed (NRST and NTRST) after MODE0 and/or MODE1 have/has been changed. The reset input to the embedded ICE (NTRST) is provided separately to facilitate debug of boot programs.

#### 7.6.3 IEEE 1149.1 JTAG Boundary Scan

IEEE 1149.1 JTAG Boundary Scan is enabled when MODE0 is low and MODE1 is high. The functions SAMPLE, EXTEST and BYPASS are implemented. In ICE Debug mode, the ARM core responds with a non-JTAG chip ID that identifies the core to the ICE system. This is not IEEE 1149.1 JTAG compliant. It is not possible to switch directly between JTAG and ICE operations. A chip reset must be performed (NRST and NTRST) after MODE0 and/or MODE1 have/has been changed.

### 7.7 Memory Controller

The ARM7TDMI processor address space is 4G bytes. The memory controller decodes the internal 32-bit address bus and defines three address spaces:

- Internal Memories in the four lowest megabytes

- Middle Space reserved for the external devices (memory or peripherals) controlled by the EBI

- Internal Peripherals in the four highest megabytes

In any of these address spaces, the ARM7TDMI operates in little-endian mode only.

#### 7.7.1 Protection Mode

The embedded peripherals can be protected against unwanted access. The PME (Protect Mode Enable) pin must be tied high and validated in its peripheral operation (PIO Disable) to enable the protection mode. When enabled, any peripheral access must be done while the ARM7TDMI is running in Privileged mode (i.e., the accesses in user mode result in an abort). Only the valid peripheral address space is protected and requests to the undefined addresses will lead to a normal operation without abort.

#### 7.7.2 Internal Memories

The AT91M42800A microcontroller integrates an 8-Kbyte primary internal SRAM. All internal memories are 32 bits wide and single-clock cycle accessible. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one cycle. Fetching Thumb or ARM instructions is supported and internal memory can store twice as many Thumb instructions as ARM ones.

The SRAM bank is mapped at address 0x0 (after the remap command), and ARM7TDMI exception vectors between 0x0 and 0x20 that can be modified by the software. The rest of the

bank can be used for stack allocation (to speed up context saving and restoring), or as data and program storage for critical algorithms.

#### 7.7.3 Boot Mode Select

The ARM reset vector is at address 0x0. After the NRST line is released, the ARM7TDMI executes the instruction stored at this address. This means that this address must be mapped in non-volatile memory after the reset.

The input level on the BMS pin during the last 10 SLCK clock cycles before the rising edge of the NRST selects the type of boot memory. The Boot mode depends on BMS (see Table 7-2).

The pin BMS is multiplexed with the I/O line PA27 that can be programmed after reset like any standard PIO line.

**Table 7-2.** Boot Mode Select

| BMS | Boot Memory                    |  |

|-----|--------------------------------|--|

| 1   | External 8-bit memory NCS0     |  |

| 0   | External 16-bit memory on NCS0 |  |

#### 7.7.4 Remap Command

The ARM vectors (Reset, Abort, Data Abort, Prefetch Abort, Undefined Instruction, Interrupt, Fast Interrupt) are mapped from address 0x0 to address 0x20. In order to allow these vectors to be redefined dynamically by the software, the AT91M42800A microcontroller uses a remap command that enables switching between the boot memory and the internal SRAM bank addresses. The remap command is accessible through the EBI User Interface, by writing one in RCB of EBI\_RCR (Remap Control Register). Performing a remap command is mandatory if access to the other external devices (connected to chip selects 1 to 7) is required. The remap operation can only be changed back by an internal reset or an NRST assertion.

Notes: 1. NIRQ de-assertion and automatic interrupt clearing if the source is programmed as level sensitive.

#### 7.7.5 Abort Control

The abort signal providing a Data Abort or a Prefetch Abort exception to the ARM7TDMI is asserted in the following cases:

- When accessing an undefined address in the EBI address space

- When the ARM7TDMI performs a misaligned access

No abort is generated when reading the internal memory or by accessing the internal peripherals, whether the address is defined or not.

When the processor performs a forbidden write access in a mode-protected peripheral register, the write is cancelled but no abort is generated.

The processor can perform word or half-word data access with a misaligned address when a register relative load/store instruction is executed and the register contains a misaligned address. In this case, whether the access is in write or in read, an abort is generated but the access is not cancelled.

The Abort Status Register traces the source that caused the last abort. The address and the type of abort are stored in registers of the External Bus Interface.

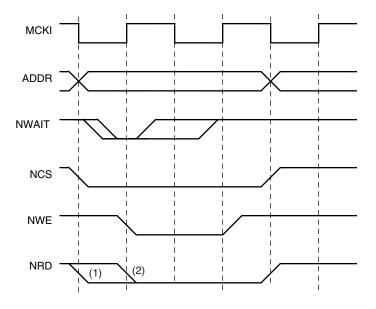

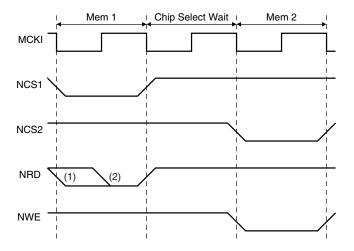

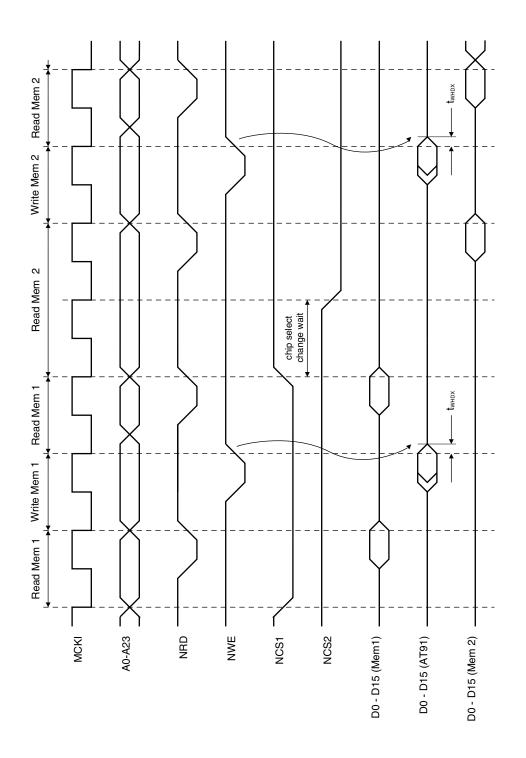

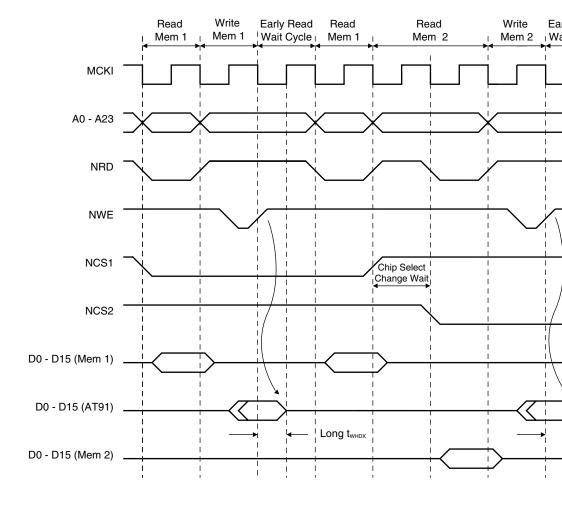

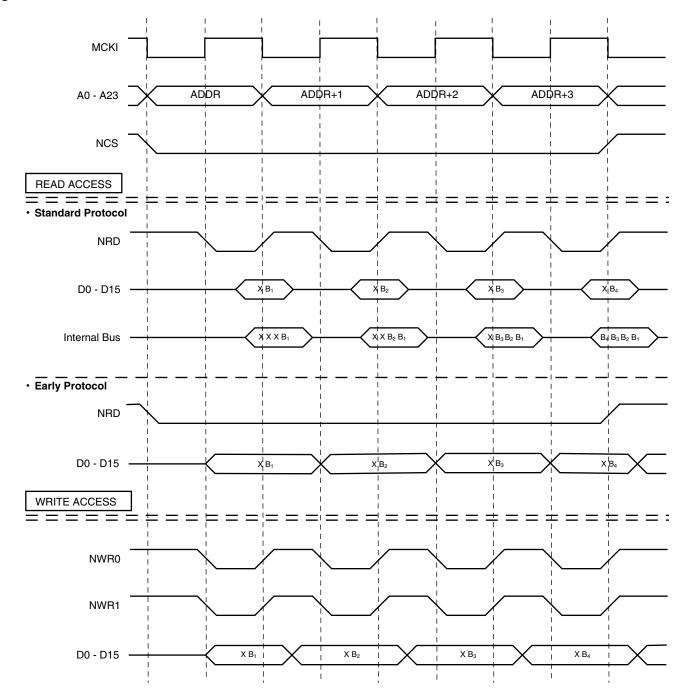

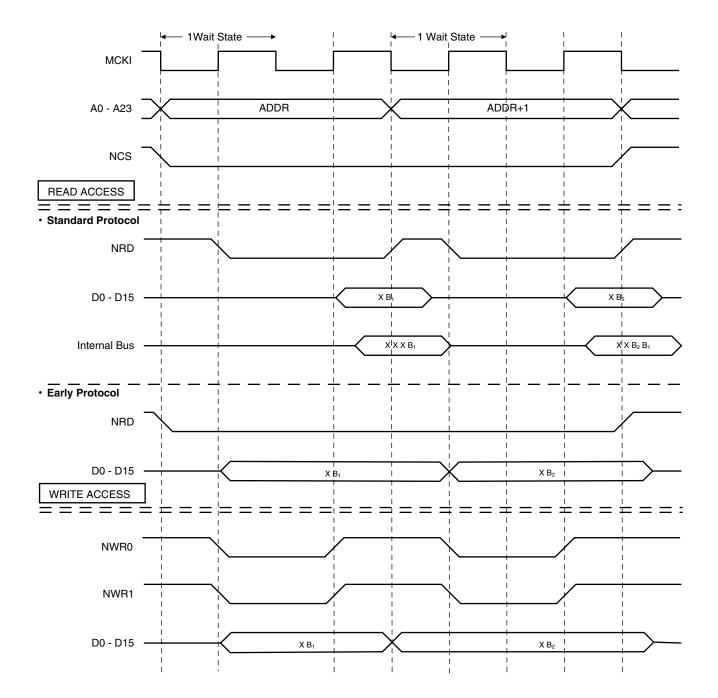

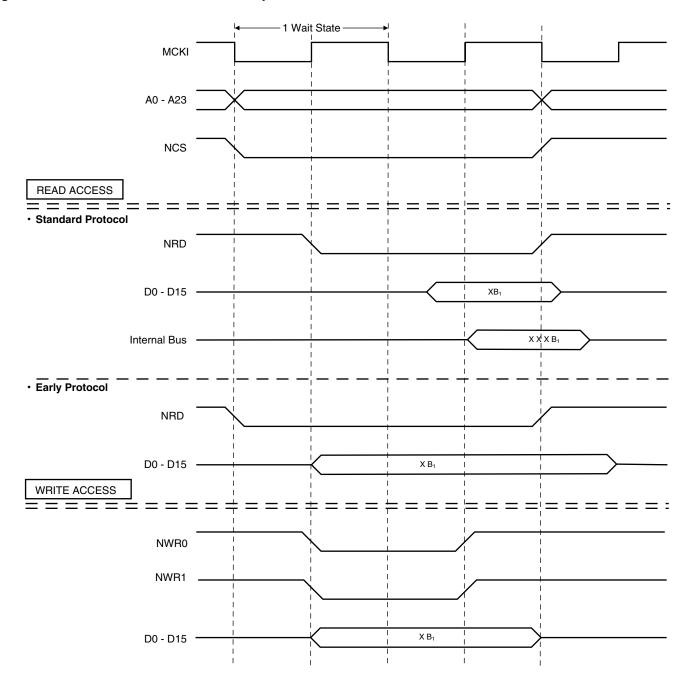

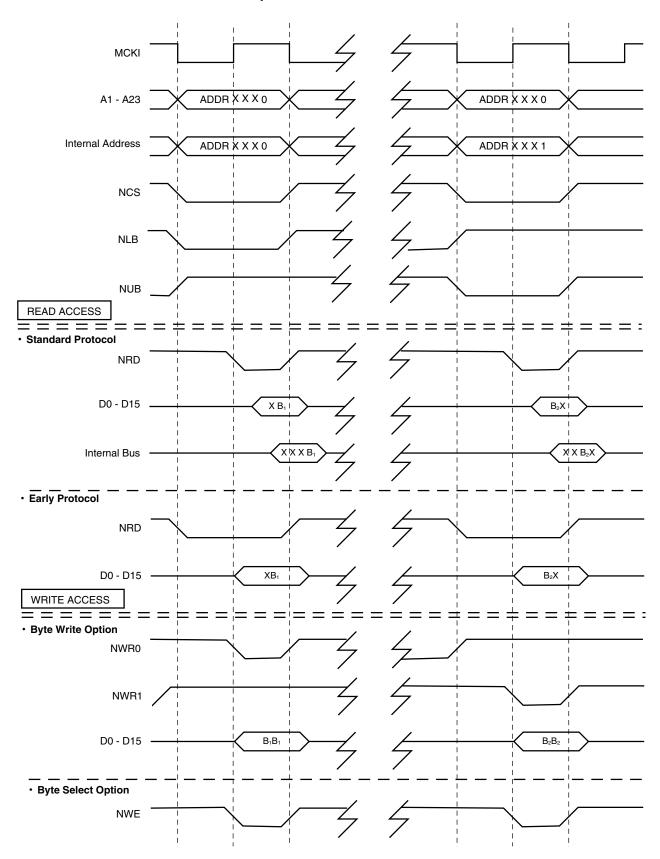

#### 7.8 External Bus Interface