# AT97SC3205

# Atmel

### **Trusted Platform Module – SPI Interface**

### SUMMARY DATASHEET

#### **Features**

- Compliant to the Trusted Computing Group (TCG) Trusted Platform Module (TPM) Version 1.2 Specification

- Compliant with TCG PC Client-Specific TPM Interface Specification (TIS) Version 1.3

- Single-chip, Turnkey Solution

- Hardware Asymmetric Crypto Engine

- Atmel<sup>®</sup> AVR<sup>®</sup> RISC Microprocessor

- Internal EEPROM Storage for RSA Keys

- Serial Peripheral Interface (SPI) Protocol Up to 45MHz\* (\*Typical PC Operating Range is 24MHz to 33MHz)

- Secure Hardware and Firmware Design and Chip Layout

- FIPS-140-2 Module Certified Including the High-quality Random Number Generator (RNG), HMAC, AES, SHA, and RSA Engines

- NV Storage Space for 2066 bytes of User Defined Data

- 3.3V Supply Voltage

- 28-lead Thin TSSOP and 32-pad QFN Package

- Offered in Both Commercial (0°C to 70°C) and Industrial (-40°C to +85°C) Temperature Ranges

#### Description

The Atmel AT97SC3205 is a fully integrated security module designed to be integrated into personal computers and other embedded systems. It implements version 1.2 of the Trusted Computing Group (TCG) specification for Trusted Platform Modules (TPM).

This is a summary document. The complete document is available under NDA. For more information, please contact your local Atmel sales office.

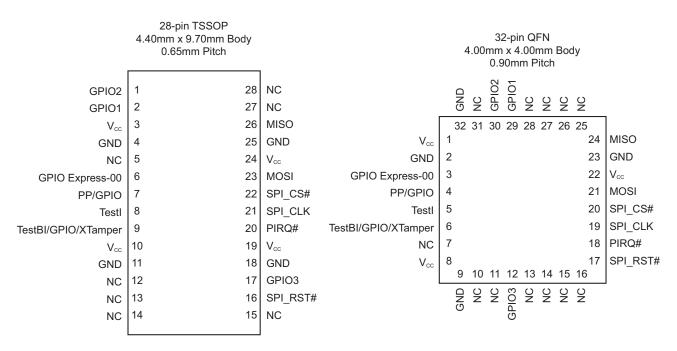

### 1. Pin Configurations and Pinouts

#### Table 1-1. Pin Configurations

| Pin Name        | Function                                   |

|-----------------|--------------------------------------------|

| V <sub>CC</sub> | 3.3V Supply Voltage                        |

| GND             | Ground                                     |

| GPIO Express-00 | GPIO assigned to TPM_NV_INDEX_GPIO_00      |

| PP/GPIO         | Hardware Physical Presence or GPIO pin.    |

| GPIO            | General Purpose Input/Output Pin           |

| MISO            | SPI Slave Data Output                      |

| MOSI            | SPI Slave Data Input                       |

| PIRQ#           | SPI Interrupt Requests                     |

| SPI_CLK         | SPI Clock Input                            |

| SPI_CS#         | SPI Chip Select                            |

| SPI_RST#        | SPI Reset Pin                              |

| Testl           | Testl Manufacturing Test Input (Disabled)  |

| TestBl          | TestBI Manufacturing Test Input (Disabled) |

| XTamper         | Indicate External Tamper Event             |

| NC              | No Connect                                 |

#### Figure 1-1. Pinouts

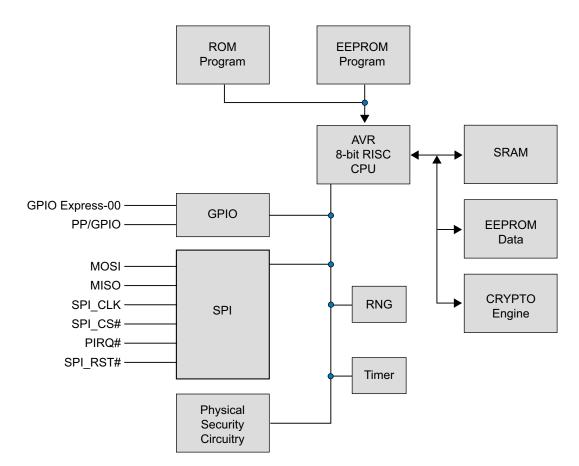

### 2. Block Diagram

The TPM includes hardware Random Number Generator (RNG), including a FIPS certified Pseudo Random Number Generator that is used for key generation and TCG protocol functions. The RNG is also available to the system to generate random numbers that may be needed during normal operation.

The chip uses a dynamic internal memory management scheme to store multiple RSA keys. Other than the standard TCG commands (TPM\_FlushSpecific, TPM\_Loadkey2), no system intervention is required to manage this internal key cache.

The TPM is offered to OEM and ODM manufacturers as a turnkey solution, including the firmware integrated on the chip. In addition, Atmel provides the necessary device driver software for integration into certain operating systems, along with BIOS drivers. Atmel will also provide manufacturing support software for use by OEMs and ODMs during initialization and verification of the TPM during board assembly.

Full documentation for TCG primitives can be found in the TCG TPM Main Specification, Parts 1 to 3, on the TCG web site located at <a href="https://www.trustedcomputinggroup.org">https://www.trustedcomputinggroup.org</a>. TPM features specific to PC client platforms are specified in the TCG PC Client Specific TPM Interface Specification, version 1.3, also available on the TCG web site. Implementation guidance for PC platforms is outlined in the TCG PC Client Specific Implementation Specification for Conventional Bios, version 1.2, also available on the TCG web site.

# 3. Pin Description

### Table 3-1. Pin Descriptions

| Pin                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>cc</sub>         | <b>Power Supply, 3.3V</b> . Care should be taken to prevent excessive noise. Effective decoupling of the $V_{CC}$ inputs to the Atmel TPM is critical to assure consistently reliable operation over the lifetime of the system. The Atmel recommendation is for a decoupling bypass capacitor within the range of 2200pF to 4700pF, to be placed as close as possible, < 5mm, to each of the $V_{CC}$ pins, located between each $V_{CC}$ pin and the immediately adjacent GND pin. A 0.1µF decoupling bypass capacitor should be placed at the node in which these $V_{CC}$ traces join, which should be as close as possible, < 10mm, to the TPM. In all cases, this bypass capacitor should be closer than the next closest component. All capacitors should be of high quality, with dielectric ratings of X5R or X7R. A low-power state is automatically entered when the chip is idle. No further action is required by the system to enter low-power mode. |  |  |

| GND                     | System Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| GPIO Express-00         | General Purpose Input/Output. Internal pull-up resistor. This pin is mapped to NV Index<br>TPM_NV_INDEX_GPIO_00. Default TPM configuration: GPIO Input. GPIO-Express-00 also serves as the XOR<br>chain Output during I/O test mode. Since GPIO-Express-00 has an internal pull-up, it should be left floating if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| PP/GPIO                 | <b>General Purpose Input/Output. Internal pull-down resistor.</b> This pin is an indicator for hardware physical presence; active high. Default TPM configuration: GPIO input. Since PP/GPIO has an internal pull-down, it should be left floating if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| GPIO                    | General Purpose Input/Output. If unused, this pin can be tied to GND or V <sub>CC</sub> at the customers discretion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| MISO                    | Master In Slave Out. SPI Slave Data Output. This pin serves as the SPI Data output from the TPM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| MOSI                    | Master Out Slave In. SPI Slave Data Input. This pin serves as the SPI Data Input to the TPM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PIRQ#                   | <b>SPI Interrupt Pin, Active-low.</b> This pin is used by the TPM to assert interrupts. If unused, this pin should be tied to ground directly or through a $4.7$ K $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| SPI_CLK                 | Clock used to drive the SPI bus. This pin should be asserted high for power savings when the TPM is not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SPI_CS#                 | SPI_CS# Chip Select, Active-low. The TPM chip select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| SPI_RST#                | <b>SPI Reset Pin, Active-low.</b> Pulsing this signal low resets the internal state of the TPM, and is equivalent to removal/restoration of power to the chip. The required minimum reset pulse width is $2\mu$ s. On power-up, it is critical that reset be kept active-low until V <sub>CC</sub> , and SPI_CLK stabilize. To be compliant with TCG requirements, this pin needs to be tied to system reset. TPM_Init is indicated by asserting this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Testl                   | <b>Testi Manufacturing Test Input.</b> Disabled after manufacturing. Tie TestI to ground directly or through a 4.7kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| TestBI/GPIO/<br>XTamper | <b>TestBI Manufacturing Test Input</b> . The Atmel TPM does not support legacy addressing via the optional BADD implementation of this pin. The TestBI pin also serves as the XTamper pin or an additional GPIO pin, active high. (See the application note, "Atmel Specific TPM Commands Reference Guide" for details on XTamper implementation). If unused, this pin should be tied to ground directly or through a 4.7KΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| NC                      | No Connect Pins (TSSOP).<br>The AT97SC3205 TSSOP package has additional pins which are no connects and can be tied to GND, V <sub>CC</sub> , or left<br>floating at the customers discretion:<br>NC – TSSOP Pin 5<br>NC – TSSOP Pin 12<br>NC – TSSOP Pin 13<br>NC – TSSOP Pin 14<br>NC – TSSOP Pin 15<br>NC – TSSOP Pin 27<br>NC – TSSOP Pin 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

#### Table 3-1. Pin Descriptions (Continued)

| Pin | Description                                                                                                                                                                                                                                                                                                                                                          |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin | Description   No Connect Pins (QFN).   The AT97SC3205 QFN package has additional pins which are no connects and can be tied to GND, V <sub>CC</sub> , or left floating at the customers discretion:   NC – QFN Pin 7   NC – QFN Pin 10   NC – QFN Pin 11   NC – QFN Pin 13   NC – QFN Pin 14   NC – QFN Pin 15   NC – QFN Pin 25   NC – QFN Pin 26   NC – QFN Pin 27 |  |

|     |                                                                                                                                                                                                                                                                                                                                                                      |  |

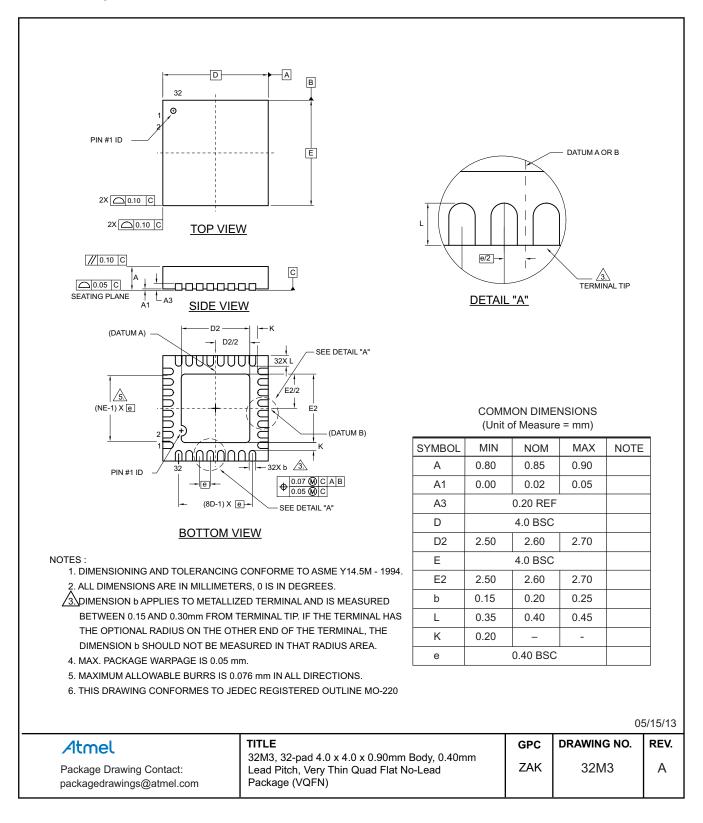

Note: 1. The substrate center pad for the 32-pin QFN is directly tied to GND internally; therefore, this pad can either be left floating or tied to GND.

## 4. Ordering Information

| Atmel Ordering Code       | Package                     |                 | Operating Range                                        |

|---------------------------|-----------------------------|-----------------|--------------------------------------------------------|

| AT97SC3205 <sup>(1)</sup> | 28X1 (28-pin thin TSSOP)    | Lead-free, RoHS | Commercial (0°C to 70°C)<br>Industrial (-40°C to 85°C) |

|                           | 32M3 (32-pin very thin QFN) |                 |                                                        |

Note: 1. Please see the AT97SC3205 datasheet addendum for the complete catalog number ordering code.

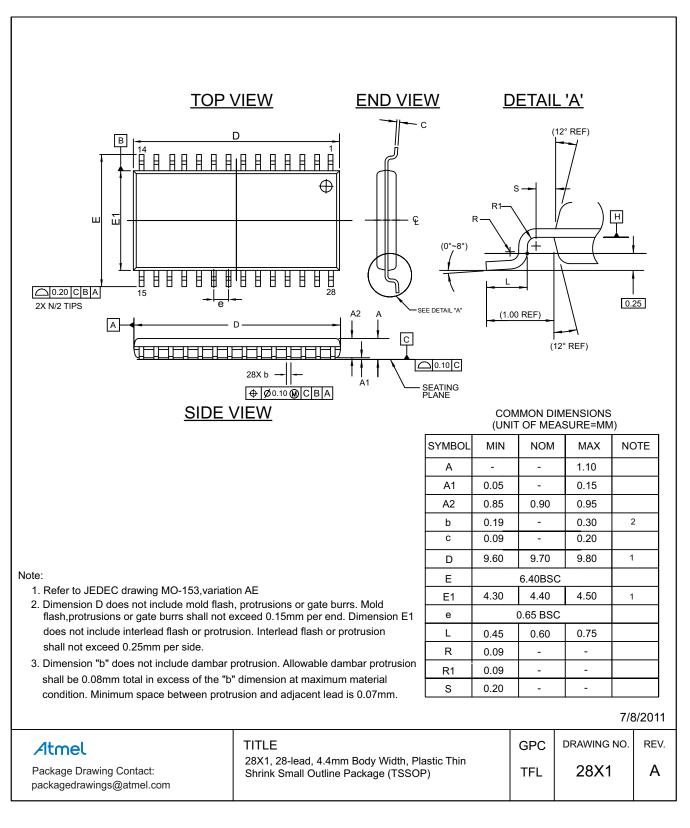

| Package Type |                                                                                     |

|--------------|-------------------------------------------------------------------------------------|

| 28X1         | 28-lead, 4.4mm body width, Plastic Thin Shrink Small Outline (thin TSSOP)           |

| 32M3         | 32-pad, 4.0 x 4.0 x 0.9mm body, 0.4mm lead pitch, Very Thin Quad Flat No-Lead (QFN) |

### 5. Package Drawings

### 5.1 28X1 — 28-lead Thin TSSOP

#### 5.2 32M3 — 32-pad QFN

Atmel

## 6. Revision History

| Doc. Rev. | Date    | Comments                         |

|-----------|---------|----------------------------------|

| 8884AS    | 02/2014 | Initial summary document release |

# Atmel Enabling Unlimited Possibilities

Т

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311

0311 **F:** (+1)(408) 436.4200

www.atmel.com

© 2014 Atmel Corporation. / Rev.: Atmel-8884AS-TPM-AT97SC3205-Datasheet-Summary\_022014.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR ADVISED OF THE VSSIBILISS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completenees of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Security ICs / Authentication ICs category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

RJM8L151F6P6R AT97SC3204T-X2A1B-10 SLS32AIA020A4USON10XTMA2 AT97SC3205T-G3M4C-00 AT97SC3205T-H3M4C-20 AT97SC3204-U4A14-20 AT97SC3205T-H3M4C20B AT97SC3205-X3A12-10 AT97SC3204-U2MA-20 AT97SC3204-X2A1A-10 ATAES132-SH-EQ ATECC508A-MAHDA-S DS2401+ DS1990A-F3+ DS1990A-F5+ DS2401P+T&R DS2401Z+T&R DS2411P+ DS2411P+T&R ATSHA204-TH-CZ-T DS28CM00R-A00+T DS28C22Q+T ATTPM20P-G3MA1-10-B HCS515-IP HCS515P MCS3122-I/ST MIKROE-3047 ATECC508A-SSHDA-T ATSHA204A-SSHDA-B ATAES132A-SHEQ-B ATECC108A-SSHCZ-B ATSHA204A-SSHDA-T W74M32FVSSIQ IPL-CHP1.8V ATSHA204A-STUCZ-T DS2411R+T&R RJM8L151K8Q6Y CW3802 RJGT102WDP8 FM15160 508-03 RJGT102WDT6 RJMU401FH0 ATECC108A-RBHCZ-T IPL-CHP 404726X AT88SC0808CA-Y6H-T AT88SA102S-SH-T MAX66240ESA+