# ATSAMB11-MR210CA/MR510CA

### **Ultra Low Power BLE 4.1 Module**

**DATASHEET**

## **Description**

The Atmel® ATSAMB11-MR210CA is an ultra-low power Bluetooth® SMART (BLE 4.1) module with Integrated MCU, Transceiver, Modem, MAC, PA, TR Switch, and Power Management Unit (PMU). It is a standalone Cortex®-M0 applications processor with embedded Flash memory and BLE connectivity.

The qualified Bluetooth Smart protocol stack is stored in dedicated ROM, the firmware includes L2CAP service layer protocols, Security Manager, Attribute protocol (ATT), Generic Attribute Profile (GATT), and the Generic Access Profile (GAP). Additionally, application profiles such as Proximity, Thermometer, Heart Rate, Blood Pressure, and many others are supported and included in the protocol stack.

The module contains all circuitry required including a ceramic high gain antenna, 26MHz crystal, and PMU circuitry. The customer simply needs to place the module on the customer PCB design, provide power and a 32kHz Real Time Clock or crystal. All References to ATSAMB11-MR210CA, refer to the ATSAMB11-MR510CA as well.

### **Features**

- Complies with Bluetooth V4.1, ETSI EN 300 328 and EN 300 440 Class 2, FCC CFR47 Part 15, and ARIB STD-T66

- Bluetooth Certification

- QD ID Controller (see declaration D028678)

- QD ID Host (see declaration D028679)

- 2.4GHz transceiver and Modem

- 95dBm/-93dBm programmable receiver sensitivity

- -20 to +3.5dBm programmable TX output power

- Integrated T/R switch

- Incorporated antenna

- ARM® Cortex®-M0 32-bit processor

- Single wire Debug (SWD) interface

- Four-channel DMA controller

- Brown-out detector and Power On Reset

- Watch Dog Timer

- Memory

- 128KB embedded RAM (96KB available for application)

- 128KB embedded ROM

- 256KB stacked Flash memory

- Hardware Security Accelerators

- AES-128

- SHA-256

- Peripherals

- $-\,$  23 digital and three wakeup GPIO with 96k $\!\Omega$  Internal Pullup resistors, four Mixed Signal GPIO

- 2x SPI (Master/Slave)

- 2x I<sup>2</sup>C (Master/Slave)

- 2x UART

- 1x SPI Flash

- 3-axis quadrature decoder

- 4x Pulse Width Modulation (PWM), three General Purpose Timers, and one Wake up Timer

- Four channel 11-bit ADC

- Clock

- Integrated 26MHz oscillator

- 26MHz crystal oscillator

- Fully integrated sleep oscillator

- Ultra-low power

- Less than 1.1µA sleep current (8K RAM retention and RTC running)

- 3.2mA peak TX current (0dBm, 3.6V)

- 5.0mA peak RX current (3.6V, -95dBm sensitivity)

- Integrated Power management

- 2.3 4.2V input range for PMU

- 2.3 3.6V input range for I/O (limited by Flash memory)

- Fully integrated Buck DC-DC converter

# **Table of Contents**

| 3  | Blo  | ock Diagram                                   | 5  |

|----|------|-----------------------------------------------|----|

| 4  | Pin  | Out Information                               | 6  |

|    | 4.1  | Pin Assignment                                |    |

|    | 4.2  | Pin Description                               |    |

|    | 4.3  | Module Outline Drawing                        | g  |

| 5  | Ele  | ctrical Specifications                        | 10 |

|    | 5.1  | Absolute Maximum Ratings                      | 10 |

|    | 5.2  | Recommended Operating Conditions              | 10 |

|    | 5.3  | Restrictions for the Power States             | 10 |

|    | 5.4  | Power-up Sequence                             | 11 |

|    | 5.5  | RTC Pins                                      | 11 |

| 6  | Cha  | aracteristics                                 |    |

|    | 6.1  | Device States                                 | 12 |

|    | 6.2  | Receiver Performance                          | 13 |

|    | 6.3  | Transmitter Performance                       | 14 |

| 7  | Арј  | plication Schematic                           | 15 |

|    | 7.1  | Application Schematic                         | 15 |

|    | 7.2  | Applications Schematic with 32.768kHz Crystal | 16 |

|    | 7.3  | Application Schematic BOM                     | 17 |

| 8  | Pla  | cement and Routing Guidelines                 | 18 |

|    | 8.1  | Power and Ground                              | 19 |

|    | 8.2  | Interferers                                   | 19 |

| 9  | Ref  | flow Profile Information                      | 20 |

|    | 9.1  | Storage Conditions                            | 20 |

|    |      | 9.1.1 Moisture Barrier Bag Before Opened      | 20 |

|    |      | 9.1.2 Moisture Barrier Bag Open               | 20 |

|    | 9.2  | Stencil Design                                | 20 |

|    | 9.3  | Baking Conditions                             |    |

|    | 9.4  | Soldering and Reflow Condition                |    |

|    |      | 9.4.1 Reflow Oven                             |    |

|    | 9.5  | Module Assembly Considerations                | 21 |

| 10 | Ref  | ference Documentation and Support             | 22 |

|    | 10.1 | Reference Documents                           | 22 |

| 11 | Cer  | rtifications                                  | 23 |

|    | 11.1 | Agency Compliance                             | 23 |

| 12 | Erra | ata                                           | 24 |

| 13 | Dod  | cument Revision History                       | 25 |

# 1 Ordering Information

| Ordering code      | Package   | Description  |

|--------------------|-----------|--------------|

| ATATSAMB11-MR210CA | 22 x 15mm | Chip Antenna |

| ATATSAMB11-MR510CA | 22 x 15mm | Chip Antenna |

The ATATSAMB11-MR510CA module is identical to ATATSAMB11-MR210CA regarding the module footprint and functionality. The ATATSAMB11-MR510CA also includes the capability of hardware encryption.

# 2 Package Information

Table 2-1. ATATSAMB11-MR210/MR510 Module Information (1)

| Parameter        | Value         | Units | Tolerance |

|------------------|---------------|-------|-----------|

| Package Size     | 22.88 X 15.36 | mm    |           |

| Pad Count        | 40            |       |           |

| Total Thickness  | ~2.1          |       |           |

| Pad Pitch        | 0.9002        |       |           |

| Pad Width        | 0.500         | mm    |           |

| Exposed Pad size | 4.4 x 4.4     |       |           |

Note: 1. For details, see Package Drawing in Section 4.3.

# 3 Block Diagram

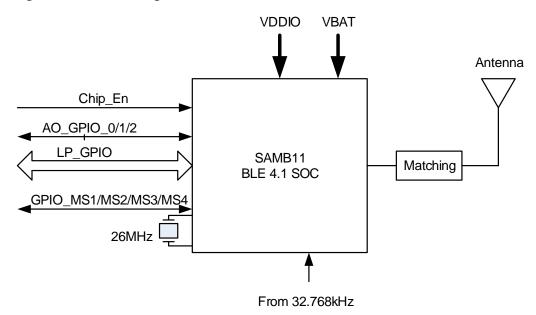

The following image shows the block diagram of the ATSAMB11-MR210CA/MR510 module.

Figure 3-1. Block Diagram

# 4 Pin Out Information

# 4.1 Pin Assignment

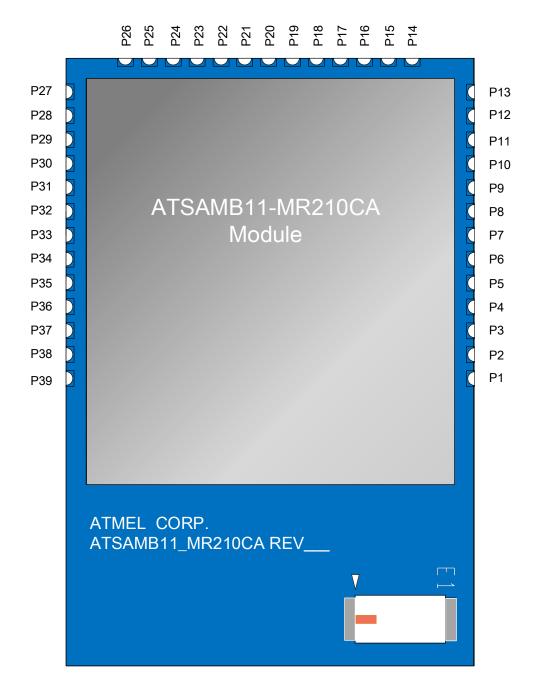

The following image shows the module top view and pin numbering.

Figure 4-1. ATSAMB11-MR210 Pin Assignments

#### **Pin Description** 4.2

Table 4-1. **Pin Description**

| #  | Name       | Туре         | Description                                                                                                                            | Notes                                                         |

|----|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 1  | Ground     | Power        | Ground Pin. Connect to PCB ground                                                                                                      |                                                               |

| 2  | LP_GPIO_0  | I/O          | Used for Single Wire Debug Clock                                                                                                       | Debug interface pin. Connect to a header or test point.       |

| 3  | LP_GPIO_1  | I/O          | Used for Single Wire Debug Data                                                                                                        | Debug interface pin. Connect to a header or test point.       |

| 4  | VBAT       | Power        | Power Supply Pin for the on chip Power Management Unit (PMU). Connect to a 2.35V – 4.3V power supply.                                  |                                                               |

| 5  | LP_GPIO_2  | I/O          | General Purpose I/O                                                                                                                    | Default function is Host UART RXD                             |

| 6  | LP_GPIO_3  | I/O          | General Purpose I/O                                                                                                                    | Default function is Host UART TXD                             |

| 7  | LP_GPIO_4  | I/O          | General Purpose I/O                                                                                                                    | Default function is Host UART CTS                             |

| 8  | LP_GPIO_22 | I/O          | General Purpose I/O                                                                                                                    |                                                               |

| 9  | LP_GPIO_23 | I/O          | General Purpose I/O                                                                                                                    |                                                               |

| 10 | LP_GPIO_5  | I/O          | General Purpose I/O                                                                                                                    | Default function is Host UART RTS                             |

| 11 | LP_GPIO_6  | I/O          | General Purpose I/O                                                                                                                    | Default function is Debug UART RXD                            |

| 12 | LP_GPIO_7  | I/O          | General Purpose I/O                                                                                                                    | Default function is Debug UART TXD                            |

| 13 | LP_GPIO_8  | I/O          | General Purpose I/O                                                                                                                    | Default function is I2C_SDA                                   |

| 14 | Ground     | Power        | Ground Pin. Connect to PCB ground.                                                                                                     |                                                               |

| 15 | LP_GPIO_9  | I/O          | General Purpose I/O                                                                                                                    | Default function is I2C_SCL                                   |

| 16 | LP_GPIO_10 | I/O          | General Purpose I/O                                                                                                                    | Default function is SPI_SCK                                   |

| 17 | LP_GPIO_11 | I/O          | General Purpose I/O                                                                                                                    | Default function is SPI_MOSI                                  |

| 18 | LP_GPIO_12 | I/O          | General Purpose I/O                                                                                                                    | Default function is SPI_SSN                                   |

| 19 | LP_GPIO_13 | I/O          | General Purpose I/O                                                                                                                    | Default function is SPI_MISO                                  |

| 20 | GPIO_MS1   | I/O          | Mixed Signal I/O                                                                                                                       | Configurable to be a GPIO or ADC input                        |

| 21 | GPIO_MS2   | I/O          | Mixed Signal I/O                                                                                                                       | Configurable to be a GPIO or ADC input                        |

| 22 | Chip_En    | Con-<br>trol | Chip Enable. A high level turns on the On Chip PMU and enables operation of the device. Low disables the device and turns off the PMU. | Control this pin with a host GPIO. If not used, tie to VDDIO. |

| 23 | GPIO_MS3   | I/O          | Mixed Signal I/O                                                                                                                       | Configurable to be a GPIO or ADC input                        |

| 24 | GPIO_MS4   | I/O          | Mixed Signal I/O                                                                                                                       | Configurable to be a GPIO or ADC input                        |

| 25 | RTC_CLKP   |              | Positive Pin for Real Time Clock Crystal                                                                                               | Connect to a 32kHz Crystal                                    |

| 26 | Ground     | Power        | Ground Pin. Connect to PCB ground.                                                                                                     |                                                               |

| 27 | RTC_CLKN   |              | Negative Pin for Real Time Clock Crystal                                                                                               | Connect to a 32kHz Crystal                                    |

| 28 | AO_GPIO_0  | 1/0          | Always on GPIO_0. Can be used to wake up the device from sleep. Can also be used as a general purpose I/O.                             |                                                               |

| 29 | AO_GPIO_1  | I/O          | Always on GPIO_0. Can be used to wake up the device from sleep. Can also be used as a general purpose I/O.                             |                                                               |

| #  | Name       | Туре  | Description                                                                                                | Notes                                                   |

|----|------------|-------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 30 | AO_GPIO_2  | I/O   | Always on GPIO_0. Can be used to wake up the device from sleep. Can also be used as a general purpose I/O. |                                                         |

| 31 | LP_GPIO_14 | I/O   | General Purpose I/O                                                                                        | Default function is Debug I2C_SDA                       |

| 32 | VDDIO      | Power | Power Supply Pin for the I/O pins. Connect to a 2.3V – 3.6V power supply.                                  | I/O supply can be less than or equal to VBAT            |

| 33 | LP_GPIO_15 | I/O   | General Purpose I/O                                                                                        | Default function is Debug I2C_SCL                       |

| 34 | LP_GPIO_16 | I/O   | General Purpose I/O                                                                                        |                                                         |

| 35 | LP_GPIO_17 | I/O   | General Purpose I/O                                                                                        |                                                         |

| 36 | LP_GPIO_18 | I/O   | General Purpose I/O                                                                                        |                                                         |

| 37 | LP_GPIO_19 | I/O   | General Purpose I/O                                                                                        |                                                         |

| 38 | LP_GPIO_20 | I/O   | General Purpose I/O                                                                                        |                                                         |

| 39 | Ground     | Power | Ground Pin. Connect to PCB ground.                                                                         |                                                         |

| 40 | Paddle     | Power | Center Ground Paddle                                                                                       | Connect to inner PCB ground plane with an array of vias |

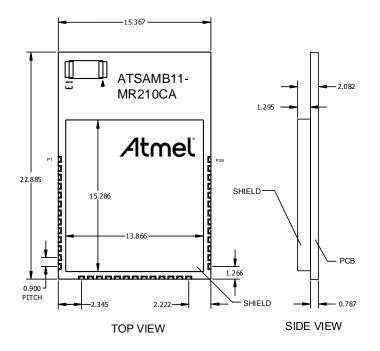

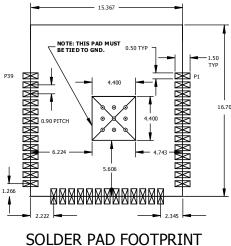

# 4.3 Module Outline Drawing

The following figure shows the bottom view of the module and the module dimensions. All dimensions are in millimeters.

Figure 4-2. ATSAMB11-MR210CA Module Dimensions (millimeters)

BOTTOM VIEW

DIMENSION UNITS: MM DRAWING NOT TO SCALE UNTOLERANCED DIMENSIONS

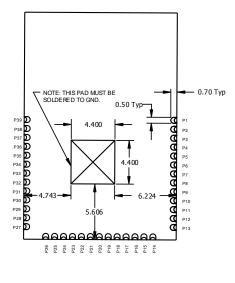

Figure 4-3. ATSAMB11-MR210CA Customer PCB Footprint

DLDER PAD FOOTPRINT TOP VIEW

# 5 Electrical Specifications

### 5.1 Absolute Maximum Ratings

The values listed in this section are ratings that can be peaked by the device, but not sustained without causing irreparable damage to the device.

Table 5-1. ATSAMB11-MR210CA Absolute Maximum Ratings

| Symbol                          | Characteristic         | Min.                          | Max.                          | Unit |

|---------------------------------|------------------------|-------------------------------|-------------------------------|------|

| VDDIO                           | I/O Supply Voltage     | -0.3                          | 4.2                           |      |

| VBAT                            | Battery Supply Voltage | -0.3                          | 5.0                           |      |

| V <sub>IN</sub> <sup>(1)</sup>  | Digital Input Voltage  | -0.3                          | VDDIO                         | V    |

| V <sub>AIN</sub> <sup>(2)</sup> | Analog Input Voltage   | -0.3                          | 1.5                           |      |

| V <sub>ESDHBM</sub> (3)         | ESD Human Body Model   | -1000, -2000(see notes below) | +1000, +2000(see notes below) |      |

| TA                              | Storage Temperature    | -65                           | 150                           | ိုင  |

|                                 | Junction Temperature   |                               | 125                           |      |

Note:

- 1. V<sub>IN</sub> corresponds to all the digital pins.

- 2. V<sub>AIN</sub> corresponds to the following analog pins: RFIO.

- 3. For V<sub>ESDHBM</sub>, each pin is classified as Class 1, or Class 2, or both:

- The Class 1 pins include all the pins (both analog and digital)

- The Class 2 pins include all digital pins only

- V<sub>ESDHBM</sub> is ±1kV for Class1 pins. V<sub>ESDHBM</sub> is ±2kV for Class2 pins

# 5.2 Recommended Operating Conditions

Table 5-2. ATSAMB11-MR210CA Recommended Operating Conditions

| Symbol | Characteristic               | Min. | Тур. | Max. | Units |

|--------|------------------------------|------|------|------|-------|

| VDDIO  | I/O Supply Voltage Low Range | 2.3  | 3.3  | 3.6  | W     |

| VBAT   | Battery Supply Voltage (1)   | 2.3  | 3.6  | 4.3  | V     |

|        | Operating Temperature        | -40  |      | 85   | °C    |

Note: 1. VBAT supply must be greater than or equal to VDDIO.

### 5.3 Restrictions for the Power States

When VDDIO is off (either disconnected or at ground potential), a voltage must not be applied to the device pins. This is because each pin contains an ESD diode from the pin to the VDDIO supply. This diode will turn on when a voltage higher than one diode-drop is supplied to the pin. This, in turn, will try to power up the part through the VDDIO supply.

If a voltage must be applied to the signal pads while the chip is in a low power state, the VDDIO supply must be on.

Similarly, to prevent the pin-to-ground diode from turning on, do not apply a voltage that is more than 0.3V below ground to any pin.

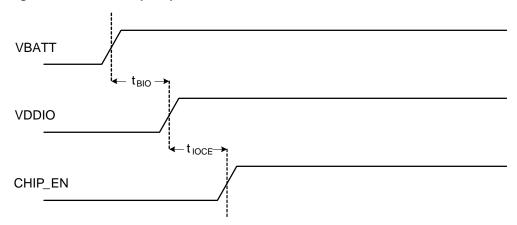

#### 5.4 **Power-up Sequence**

The power-up/down sequence for ATSAMB1-MR210A is shown in Figure 5-1. The timing parameters are provided in Table 5-3.

Figure 5-1. **Power-up Sequence**

**Power-Up Sequence Timing Table 5-3.**

| Parameter        | Min. | Max. | Units | Description                | Notes                                                                                     |

|------------------|------|------|-------|----------------------------|-------------------------------------------------------------------------------------------|

| t <sub>BIO</sub> | 0    |      |       | VBAT rise to VDDIO rise    | VBAT and VDDIO can rise simultaneously or can be tied together                            |

| tioce            | 0    |      | ms    | VDDIO rise to CHIP_EN rise | CHIP_EN must not rise before VDDIO. CHIP_EN must be driven high or low, not left floating |

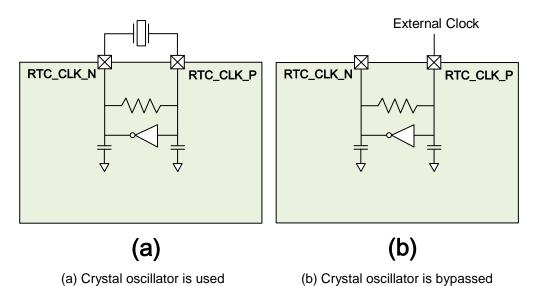

#### 5.5 **RTC Pins**

Module pins 25 and 27 (RTC\_CLKP and RTC\_CLKN, respectively) are used for a 32.768kHz crystal. To be compliant with the BLE specifications for connection events, the frequency accuracy of this clock has to be within ±500ppm. Because of the high accuracy of the 32.768kHz crystal oscillator clock (±25ppm), the power consumption can be minimized by leaving radio circuits in low power sleep mode for as long as possible until they need to wake up for the next connection timed event.

The block diagram in Figure 5-2(a) shows how the internal low-frequency Crystal Oscillator (XO) is connected to the external crystal.

Typically, the crystal should be chosen to have a load capacitance of 7pF to minimize the oscillator current. The ATSAMB11-MR210CA device has switchable on chip capacitance that can be used to adjust the total load the crystal sees to meet its load capacitance specification. Refer to the ATSAMB11-2100A datasheet for more information.

Alternatively, if an external 32.768kHz clock is available, it can be used to drive the RTC\_CLKP pin instead of using a crystal. The XO has 5.625F internal capacitance on the RTC CLKP pin. To bypass the crystal oscillator an external signal capable of driving 5.625pF can be applied to the RTC CLK P terminal as shown in Figure 5-2(b). This signal must be 1.2V maximum. RTC\_CLK\_N must be left unconnected when driving an external source into RTC\_CLK\_P.

Figure 5-2. ATSAMB11-MR210CA XO Connections to Low-Frequency Crystal Oscillator

Table 5-4. ATSAMB11-MR210CA 32.768kHz External Clock Specification

| Parameter               | Min. | Тур.   | Max. | Unit. | Comments                                           |

|-------------------------|------|--------|------|-------|----------------------------------------------------|

| Oscillation frequency   |      | 32.768 |      | kHz   | Must be able to drive 6pF load @ desired frequency |

| VinH                    | 0.7  |        | 1.2  | V     | High level input voltage                           |

| VinL                    | 0    |        | 0.2  | V     | Low level input voltage                            |

| Stability – Temperature | -500 |        | +500 | ppm   |                                                    |

# 6 Characteristics

## 6.1 Device States

Table 6-1. ATSAMB11-MR210CA Device States

| Device State                          | CHIP_EN | VDDIO | VBAT (typical) | IVDDIO (typical) | Remark                                                     |

|---------------------------------------|---------|-------|----------------|------------------|------------------------------------------------------------|

| Power_Down                            | GND     | On    | <0.05µA        | <0.05µA          | Chip Enable Off                                            |

| Ultra Low Power                       | On      | On    | 1.25µA         | 0.1μΑ            | With 8KB retention<br>memory, BLE Timer and<br>RTC enabled |

| BLE_On_Receive@-94dBm                 | On      | On    | 4.5mA          | 12µA             | VBAT = 3.6V                                                |

| BLE_On_Transmit, 0dBm output power    | On      | On    | 3.0mA          | 12µA             | VBAT = 3.6V                                                |

| BLE_On_Transmit, 3.5 dBm output power | On      | On    | 4.0mA          | 12µA             | VBAT = 3.6V                                                |

#### 6.2 **Receiver Performance**

Table 6-2. ATSAMB11-MR210CA Receiver Performance

| Parameter                                                                               | Unit | Min.  | Typ. <sup>(1)</sup> | Max.  |

|-----------------------------------------------------------------------------------------|------|-------|---------------------|-------|

| Frequency                                                                               | MHz  | 2,402 | -                   | 2,480 |

| Sensitivity with on-chip DC/DC                                                          | dBm  | -94.5 | -95                 |       |

| Maximum Receive Signal Level                                                            | dBm  |       | 5                   |       |

| CCI                                                                                     | dB   |       | 13                  |       |

| ACI (N±1)                                                                               | dB   |       | 0                   |       |

| N+2 Blocker (Image)                                                                     | dB   |       | -20                 |       |

| N-2 Blocker                                                                             | dB   |       | -38                 |       |

| N+3 Blocker (Adj. Image)                                                                | dB   |       | -35                 |       |

| N-3 Blocker                                                                             | dB   |       | -43                 |       |

| N±4 or greater                                                                          | dB   |       | -45                 |       |

| Intermod (N+3, N+6)                                                                     | dBm  |       | -33                 |       |

| OOB (2GHz <f<2.399ghz)< td=""><td>dBm</td><td>-15</td><td></td><td></td></f<2.399ghz)<> | dBm  | -15   |                     |       |

| OOB (f<2GHz)                                                                            | dBm  | -10   |                     |       |

| RX peak current draw (2)                                                                |      |       | 4.00 (2)            |       |

Notes: 1. Expected values for production silicon.

2. At -93dBm sensitivity setting. Add 0.2mA at 3.6V for best sensitivity setting.

All measurements performed at 3.6V VBAT and 25°C, with tests following Bluetooth V4.1 standard tests.

### **6.3** Transmitter Performance

Table 6-3. ATSAMB11-MR210CA Transmitter Performance

| Parameter                     | Unit | Min.  | Тур. | Max.  |

|-------------------------------|------|-------|------|-------|

| Frequency                     | MHz  | 2,402 |      | 2,480 |

| Output Power Range            | dBm  | -20   |      | 3.5   |

| In-band Spurious (N±2)        | dBm  |       | -40  |       |

| In-band Spurious (N±3)        | dBm  |       | -50  |       |

| 2 <sup>nd</sup> Harmonic Pout | dBm  | -41   |      |       |

| Frequency Dev                 | kHz  |       | ±250 |       |

All measurements performed at 3.6V VBAT and 25°C, with tests following Bluetooth V4.1 standard tests.

Average advertising current for connectable beacon with a full payload (37-byte packet) is targeted to be 9.7µA. The average advertising current is based on automatic advertising from the ROM with RTC 32kHz, BLE sleep timers, and 8KB memory retention. IDRAM1 and IDRAM2 are OFF. External Peripherals and debug clocks are turned OFF. VBAT is set to 3.6V. This advertising current will be enabled in a future SDK release. For current SDK based advertising current, see errata Chapter 12.

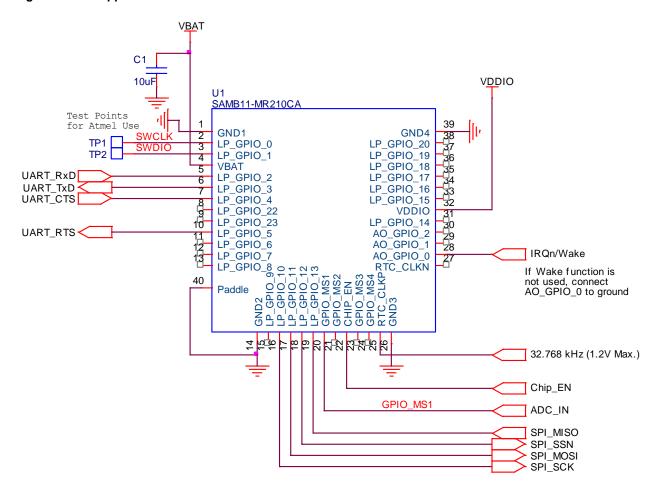

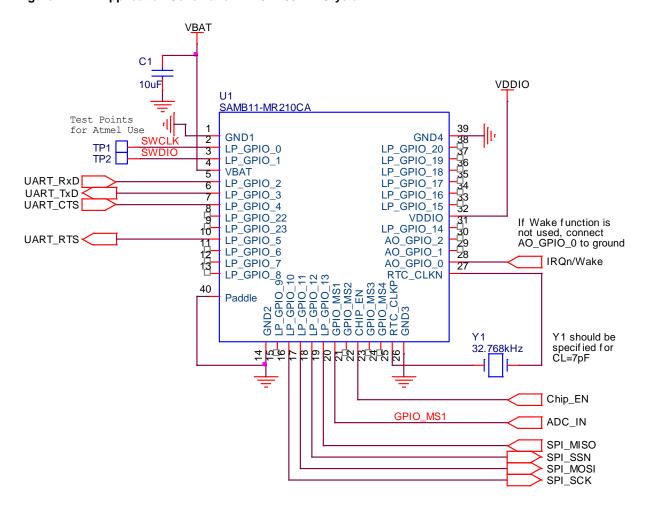

#### 7 **Application Schematic**

The ATSAMB11-MR210/MR510CA modules are fully self-contained. To use the module, just provide VBAT and VDDIO supplies. Figure 7-1 and Figure 7-2 shows a typical design using the ATSAMB11-MR210/MR510CA modules. The schematic shows several host interfaces: UART, I2C, and SPI as well as an input to the ADC on the GPIO MS1 pin. A user can choose the interface(s) required for their application. If a 32.768kHz Real Time Clock is not available in the system, a 32.768kHz crystal can be used. Section 7.2 shows a design using a crystal for the Real Time Clock. The crystal should be specified with a load capacitance, C<sub>L</sub>=7pF and a total frequency error of 200ppm. Table 7-1 shows the BOM for the application schematics.

The UART RTS and UART CTS are used for hardware flow control; they MUST be connected to the host MCU UART and enabled for the UART interface to be functional.

Module design information such as module schematics can be obtained under an NDA from Atmel.

#### 7.1 **Application Schematic**

Figure 7-1. **Application Schematic**

## 7.2 Applications Schematic with 32.768kHz Crystal

Figure 7-2. Application Schematic with 32.768kHz Crystal

### **Application Schematic BOM** 7.3

**Table 7-1. Application Schematic BOM**

| Item | Qty. | Ref.     | Value                | Description                                               | Manufacturer | Part #               |

|------|------|----------|----------------------|-----------------------------------------------------------|--------------|----------------------|

| 1    | 1    | C1       | 10μF                 | CAP,CER,10µF,20%,X5R,0603,6.3V                            | Panasonic    | ECI-1VB0I106M        |

| 2    | 2    | TP1, TP2 |                      | Test point                                                |              |                      |

| 3    | 1    | U1       | ATSAMB11-<br>MR210CA | Module, BLE, ATSAMB11                                     | Atmel        | ATSAMB11-<br>MR210CA |

| 4    | 1    | Y1       | 32.768kHz            | XTAL, 32.768kHz, ±20ppm, -40 to +85°C, CL=7pF, 2 lead, SM | ECS          | ECS327-7-34B-TR      |

## 8 Placement and Routing Guidelines

It is critical to follow the recommendations listed below to achieve the best RF performance:

- 1. The board should have a solid ground plane. The center ground pad of the device must be soldered to the ground plane by using a 3 x 3 grid of vias (see Figure 4-2). Each ground pin of the ATSAMB11-MR210CA should have a ground via placed either in the pad or right next to the pad going down to the ground plane.

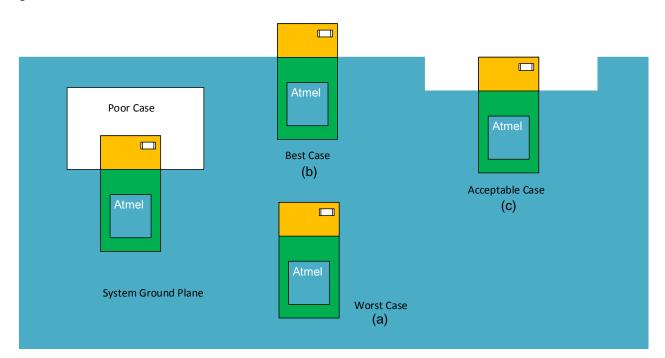

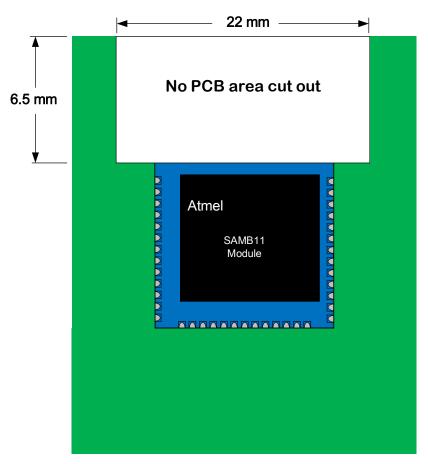

- 2. When the module is placed on the customer PCB design, a provision for the antenna must be made. There should be nothing under the portion of the module, which contains the antenna. This means the antenna should not be placed directly on top of the customer PCB as shown in Figure 8-1(a). This can be accomplished by, for example, placing the module at the edge of the board such that the module edge with the antenna extends beyond the customer PCB edge by 6.5mm as shown in Figure 8-1 (b). Alternatively, a cutout in the customer PCB can be provided under the antenna. The cutout should be at least 22mm x 6.5mm (see Figure 8-1 (c) and Figure 8-2). If the cutout method is used, the SAMB11-MR210CA should be centered in the cutout. The SAMB11-MR210CA must have ground vias spaced 2.5mm apart that should be placed all around the perimeter of the cutout. No large components should be placed near the antenna.

- 3. Keep away from antenna, as far as possible, large metal objects to avoid electromagnetic field blocking

- 4. Do not enclose the antenna within a metal shield

- 5. Keep any components that may radiate noise or signals within the 2.4GHz 2.5GHz frequency band far away from the antenna or better yet, shield the components that are generating the noise. Any noise radiated from the customer PCB in this frequency band will degrade the sensitivity of the SAMB11-MR210CA module.

Figure 8-1. SAMB11-MR210CA Placement Reference

Figure 8-2. No PCB/GND Cut Out Area

#### 8.1 **Power and Ground**

Dedicate one layer as a ground plane. Make sure that this ground plane does not get broken up by routes. Power can route on all layers except the ground layer. Power supply routes should be heavy copper fill planes to ensure the lowest possible inductance. The power pins of the module should have a via directly to the power plane as close to the pin as possible. Decoupling capacitors should have a via right next to the capacitor pin and this via should go directly down to the power plane – that is to say, the capacitor should not route to the power plane through a long trace. The ground side of the decoupling capacitor should have a via right next to the pad which goes directly down to the ground plane. Each decoupling capacitor should have its own via directly to the ground plane and directly to the power plane right next to the pad. The decoupling capacitors should be placed as close to the pin that it is filtering as possible.

#### 8.2 Interferers

One of the biggest problems with RF receivers is poor performance due to interferers on the board radiating noise into the antenna or coupling into the RF traces going to input LNA. Care must be taken to make sure that there is no noisy circuitry placed anywhere near the antenna or the RF traces. All noise generating circuits should also be shielded so they do not radiate noise that is picked up by the antenna. Also, make sure that no traces route underneath the RF portion of the SAMB11-MR210CA. Also, make sure that no traces route underneath any of the RF traces from the antenna to the SAMB11-MR210CA input. This applies to all layers. Even if there is a ground plane on a layer between the RF route and another signal, the ground return current will flow on the ground plane and be coupled into the RF traces.

## 9 Reflow Profile Information

This section provides guidelines for reflow processes in getting the Atmel module soldered to the customer's design.

### 9.1 Storage Conditions

### 9.1.1 Moisture Barrier Bag Before Opened

A moisture barrier bag must be stored in a temperature of less than 30°C with humidity under 85% RH.

The calculated shelf life for the dry-packed product shall be 12 months from the date the bag is sealed.

### 9.1.2 Moisture Barrier Bag Open

Humidity indicator cards must be blue, <30%.

## 9.2 Stencil Design

The recommended stencil is laser-cut, stainless-steel type with a thickness of 100µm to 130µm and approximately a 1:1 ratio of stencil opening to pad dimension. To improve paste release, a positive taper with bottom opening 25µm larger than the top can be utilized. Local manufacturing experience may find other combinations of stencil thickness and aperture size to get good results.

### 9.3 Baking Conditions

This module is rated at MSL level 3. After sealed bag is opened, no baking is required within 168 hours so long as the devices are held at ≤30°C/60% RH or stored at <10% RH.

The module will require baking before mounting if:

- The sealed bag has been open for >168 hours

- Humidity Indicator Card reads >10%

- SIPs need to be baked for 8 hours at 125°C

### 9.4 Soldering and Reflow Condition

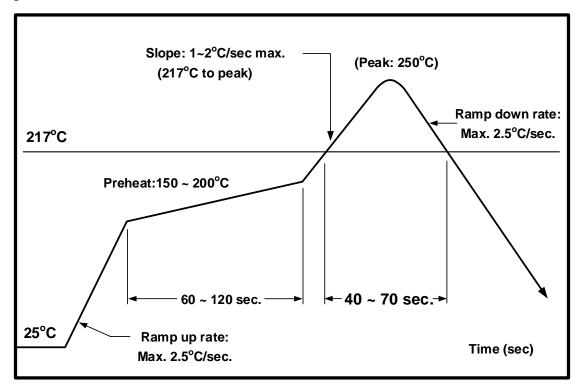

### 9.4.1 Reflow Oven

It is strongly recommended that a reflow oven equipped with more heating zones and Nitrogen atmosphere be used for lead-free assembly. Nitrogen atmosphere has shown to improve the wet-ability and reduce temperature gradient across the board. It can also enhance the appearance of the solder joints by reducing the effects of oxidation.

The following items should also be observed in the reflow process:

- 1. Some recommended pastes include:

- NC-SMQ<sup>®</sup> 230 flux and Indalloy<sup>®</sup> 241 solder paste made up of 95.5 Sn/3.8 Ag/0.7 Cu

- SENJU N705-GRN3360-K2-V Type 3, no clean paste.

- 2. Allowable reflow soldering iterations:

- Three times based on the following reflow soldering profile (as shown in Figure 9-1).

- 3. Temperature profile:

- Reflow soldering shall be done according to the following temperature profile (as shown in Figure 9-1).

- Peak temperature: 250°C.

Figure 9-1. **Solder Reflow Profile**

#### 9.5 **Module Assembly Considerations**

The ATSAMB11-MR210 and ATSAMB11-MR510 modules are assembled with an EMI Shield to ensure compliance with EMI emission and immunity rules. The EMI shield is made of a tin-plated steel (SPTE) and is not hermetically sealed. Solutions like IPA and similar solvents can be used to clean the ATSAMB11-MR210 or ATSAMB11-MR510. However, cleaning solutions, which contain acid, should never be used on the module.

The ATSAMB11-MR210 and ATSAMB11-MR510 modules are manufactured without any conformal coating applied. It is the customer's responsibility if a conformal coating is specified and applied to the ATSAMB11-MR210 or ATSAMB11-MR510 module.

# 10 Reference Documentation and Support

### 10.1 Reference Documents

Atmel offers a set of collateral documentation to ease integration and device ramp. The following table list documents available on Atmel website or integrated into development tools.

Table 10-1. Reference Documents

| Title                                                    | Content                                                                                                                                                                                                          |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet                                                | This document                                                                                                                                                                                                    |

| ATSAMB11 SOC Datasheet                                   | Data sheet for the ATSAMB11 SOC contained on this module.                                                                                                                                                        |

| Ultra Low Power BLE 4.1 SoC - Hardware Design Guidelines | ATSAMB11 hardware design guide with references for placement and routing, external RTC, restrictions on power states, type of information.                                                                       |

| ATBTLC1000 BluSDK Release Package                        | This package contains the software development kit and all the necessary documentation including getting started guides for interacting with different hardware devices, device drivers and API call references. |

For a complete listing of development support tools and documentation, visit <a href="http://www.atmel.com/">http://www.atmel.com/</a>, or contact the nearest Atmel field representative.

#### **Certifications** 11

#### **Agency Compliance** 11.1

The ATATSAMB11-MR210CA has been tested and certified to meet the compliance for the following agencies:

- Bluetooth 4.1 The ATSAMB11-MR210 utilizes the ATBTLC1000 Bluetooth die for Bluetooth operation. Refer to these QD ID reference numbers for Bluetooth certifications.

- QD ID Controller (see declaration D028678)

- QD ID Host: (see declaration D028679)

- FCC

- FCC ID: 2ADHKSAMB11

- CFR47 Part 15

- **ETSI**

- EN 300 328

- EN 300 400 Class 2

- **ARIB**

- STD-T66

### 12 Errata

Issue:

In the ATSAMB11 Datasheet, the measured advertisement current for the cases listed in Table 6-3 will be higher than what is reported.

SDK5.0 does not resemble the same conditions where Table 6-3 has been measured.

### For example:

- The power and timing parameters in the SDK5.0 release have not been fully optimized to their final values

- IDRAM1 and IDRAM2 are always enabled/retained for ROM patches and application development

- SDK5.0 enables clocks to different peripheral blocks to allow easier application development

- Continuous access to the SWD debug interface is needed. Therefore, debug clocks cannot be turned OFF.

A small sample measurement has been performed they show the following results:

### Measurement condition:

- 1-sec advertising interval

- 37 byte advertising payload

- Connectable beacon

- Advertising on 3 channels (37,38,39)

- VBAT and VDDIO are set to 3.3V

Average advertising current: 13.65µA

Average sleep current between beacons: 2.00µA

With VBAT set to 3.6V, the average advertising current under the same conditions is 12.67µA.

### **Document Revision History** 13

| Doc Rev. | Date    | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42498D   | 09/2016 | <ol> <li>Revised Figure 4-1 ATSAMB11-MR210CA Pinouts.</li> <li>Revised Figure 4-2 POD drawing.</li> <li>Updated RTC drawings in Figure 5-2.</li> <li>Corrected KHz to kHz.</li> <li>Updated VDDIO current values in Table 6-1.</li> <li>Revised recommended operating conditions voltage levels in Table 5-2.</li> <li>For consistency, corrected the reference name to be ATSAMB11-MR210CA.</li> <li>Added module placement and keep out drawings in Figure 8-1 and Figure 8-2.</li> <li>Revised Maximum Ratings in Table 5-1.</li> <li>Revised PPM ratings in Table 5-4.</li> <li>Removed TELEC from the certifications.</li> <li>Updated FCCID in section 11.1.</li> <li>Revised Feature numbers.</li> <li>Added text to Absolute Max Ratings in section 5.1 to clarify.</li> <li>Updated the Features, Integrated Power Management section</li> <li>Added section 9.5 for Module Assembly considerations.</li> <li>Revised document reference in section 10.</li> <li>Added clearer reflow profile picture in Figure 9-1.</li> <li>Corrected Footprint drawing in Figure 4-3.</li> <li>Minor edits.</li> </ol> |

| 42498C   | 02/2016 | <ol> <li>Some minor corrections in text and layout.</li> <li>Added text referring to ATSAMB11-MR510CA devices.</li> <li>Updated Module drawing in Figure 4-2.</li> <li>Updated schematic information in Section 7 and added revised Application schematic figures to Figure 7-1 and Figure 7-2.</li> <li>Revised Reflow Profile Section 8.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 42498B   | 02/2016 | <ol> <li>Changed pins in Table 4-1 to add UART flow control.</li> <li>Added UART flow control requirement in Chapter 7.</li> <li>Updated Application Schematics in Chapter 7.</li> <li>Added Agency certifications in Chapter 11.</li> <li>Added full module drawing in Figure 4-2.</li> <li>Revised Table 6-1 to remove footnote that is no longer applicable.</li> <li>Added application Schematic BOM in Table 7-1.</li> <li>Clearer reference schematic for ATSAMB11-MR210 in Figure 7.1.</li> <li>Clearer BOM for ATSAMB11-MR210 in Figure 7-2.</li> <li>Added reference schematic in Figure 7-3.</li> <li>Added BOM for ATSAMB11-MR510 in Figure 7-4.</li> <li>Added comment to Table 6-3.</li> <li>Added Errata (Chapter 12).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                    |

| 42498A   | 09/2015 | Initial document release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2016 Atmel Corporation. / Rev. Atmel-42498D-SAMB11-MR210CA-MR510CA\_Datasheet\_09/2016.

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM®, ARM Connected® logo, Cortex® and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION), DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Bluetooth Modules - 802.15.1 category:

Click to view products by Microchip manufacturer:

Other Similar products are found below:

A2541R24A10GM CYBLE-212023-10 BM78SPP05NC2-0002AA BM78SPP05MC2-0002AA CYW20732S 968EMB0019 E732G4M08S1CX TB-03F-AT\_Mesh TB-04 TB-04--AT\_Mesh BT3L(jibu) BT5S(xoft) BT5S(4k43) BT5S(jcyv) 1327 RN42HID-I/RM ENW89829C3KF BLE113-A-V1 BM70BLE01FC2-0B03AA ACN52832 A2541E24A10GM RN42-I/RM630 MOTG-BLUETOOTH ABBTM2.4GHz-52-T ABBTM-2.4GHz-T ABBTM-2.4GHz-T2 ACN52840 AFERO-BL24-01 BLED112 BM62SPKS1MC2-0001AA

BM78SPPS5MC2-0002AA PX0880/1 DAT12 BM833F BT680F PBA31309V1.00 S LK64 ISP1907-LL-ST ATSAMB11-MR510CA

BM20SPKA1NBC-0001AA BM20SPKS1NBC-0001AA BM23SPKS1NB9-0B02AA BM64SPKS1MC2-0002AA BM70BLE01FC2-0B04AA

BM70BLES1FC2-0B05BA BM70BLE01FC2-0B05BA BM70BLES1FC2-0B04AA BM77SPP03MC2-0007AA BM77SPP03MC2-0008AA

BM78SPP05NC2-0001AA BM78SPPS5NC2-0002AA