# SAM R34/R35 Low Power LoRa® Sub-GHz SiP Datasheet

### Introduction

The SAM R34/R35 is a family of ultra-low power microcontrollers combined with a UHF transceiver communication interface. It uses a 32-bit ARM<sup>®</sup> Cortex<sup>®</sup> -M0+ processor and offers up to 256 KB of Flash and 40 KB of SRAM, including an area of battery backed-up SRAM. The UHF transceiver supports LoRa<sup>®</sup> and FSK modulation. LoRa technology is a spread spectrum protocol optimized for low data-rate, ultra-long range signaling. It is ideal for battery-powered remote sensors and controls.

The SAM R34 includes an integrated microcontroller with USB and the UHF transceiver, making it suitable for USB dongle applications or for software updates via USB. The SAM R35 offers the same microcontroller functions along with the UHF transceiver without the USB interface.

## Features

#### **Operational Features**

- Processor:

- ARM Cortex -M0+ CPU running at up to 48 MHz (2.46CoreMark<sup>®</sup>/MHz)

- Single-Cycle Hardware Multiplier

- Micro Trace Buffer (MTB)

- Memory:

- In-System Self-Programmable Flash Memory, with options for sizes 256 KB, 128 KB or 64 KB

- Static Random Access Memory (SRAM) with options for sizes 32 KB, 16 KB or 8KB

- 8 KB low-power RAM with battery backup retention (with 4 KB option)

- System:

- Power-on Reset (POR) and Brown-out Reset

- Internal and External Clock Options with 48 MHz Digital Frequency Locked Loop (DFLL48M) and 48 MHz to 96 MHz Fractional Digital Phase Locked Loop (FDPLL96M)

- External Interrupt Controller (EIC)

- Up to 15 External Interrupts

- One Non-Maskable Interrupt

- Two Pin Serial Wire Debug (SWD) Programming, Test and Debugging Interfaces

- Operating Voltage: 1.8V- 3.6V

- Low Power Consumption

- Transceiver:

- RX = 16 mA (typical)

- RFO\_HF = 33 mA (typical)

- PA\_BOOST = 95 mA (typical)

- MCU:

- Idle and Standby Sleep Modes

- SleepWalking peripherals

- Temperature Range: -40°C to +85°C (Industrial)

#### **RF/Analog Features**

- Integrated LoRa Technology Transceiver:

- Tri-band Coverage

- 137 MHz to 175 MHz

- 410 MHz to 525 MHz

- 862 MHz to 1020 MHz

- +20 dBm (100 mW) Max Power (VDDANA > 2.4 VDC)

- +17 dBm (50 mW) Max Power (Regulated PA)

- +13 dBm (20 mW) High-efficency PA

- High Sensitivity:

- Down to -136 dBm (LoRaWAN<sup>™</sup> protocol compliant modes)

- Down to -148 dBm (proprietary narrowband modes)

- Up to 168 dB Maximum Link Budget

- Robust Front-End: IIp3 = -11 dBm

- Excellent Blocking Immunity

- Low RX Current of 17 mA (typical)

- Fully Integrated Synthesizer with a Resolution of 61 Hz

- LoRa Technology, (G)FSK, (G)MSK and OOK Modulation

- Preamble Detection

- 127 dB Dynamic Range RSSI

- Automatic RF Sense and CAD with Ultra-Fast Automatic Frequency Control (AFC) Packet Engine up to 256 bytes with Cyclic Redundancy Check (CRC)

#### Peripheral Information

- 12-Channel Direct Memory Access Controller (DMAC)

- 12-Channel Event System

- Three 16-bit Timer/Counters (TC), configurable as either of the following:

- One 8-bit TC with compare/capture channels

- One 16-bit TC with compare/capture channels

- One 32-bit TC with compare/capture channels, by using two TCs

- Three 16-bit Timer/Counters for Control (TCC), with Extended Functions:

- Up to four compare channels with optional complementary output

- Generation of synchronized Pulse Width Modulation (PWM) pattern across port pins

- Deterministic fault protection, fast decay and configurable dead-time between complementary output

- Dithering that increases resolution with up to five bit and reduces quantization error

- 32-bit Real Time Counter (RTC) with Clock/Calendar Function

- Watchdog Timer (WDT)

- CRC-32 Generator

- One Full-Speed (12 Mbps) Universal Serial Bus (USB) 2.0 Interface:

- Embedded host and device function

- Eight endpoints

- Up to Five Serial Communication Interfaces (SERCOM), each configurable to operate as either of the following:

- USART with full-duplex and single-wire half-duplex configuration

- I2C up to 3.4 MHz

- Serial Peripheral Interface (SPI)

- Local Interconnect Network (LIN) Slave

- One 12-bit, 1 Msps Analog-to-Digital Converter (ADC) with up to Eight External Channels:

- Differential and single-ended input

- 1/2x to 16x programmable gain stage

- Automatic offset and gain error compensation

- Oversampling and decimation in hardware to support 13-, 14-, 15-, or 16-bit resolution

- Two Analog Comparators (AC) with Window Compare Function

- Peripheral Touch Controller (PTC):

- 48-channel capacitive touch and proximity sensing

#### Package Information

- 27 Programmable I/O Pins

- 64 Lead Ball Grid Array (BGA)

# **Table of Contents**

| Intr | roduction                                                                  | 1  |  |  |  |  |  |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

| Fea  | atures                                                                     | 1  |  |  |  |  |  |  |  |  |  |  |  |

| 1.   | Description                                                                |    |  |  |  |  |  |  |  |  |  |  |  |

| 2.   | Configuration Summary                                                      | 7  |  |  |  |  |  |  |  |  |  |  |  |

| 3.   | Ordering Information for SAM R34/R35                                       |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 3.1. SAM R34/R35 Ordering Codes                                            |    |  |  |  |  |  |  |  |  |  |  |  |

| 4.   | System Introduction                                                        | 10 |  |  |  |  |  |  |  |  |  |  |  |

|      | 4.1. SAM R34/R35 Pinout Details                                            |    |  |  |  |  |  |  |  |  |  |  |  |

|      | <ul><li>4.2. SiP Block Diagram</li><li>4.3. Peripheral Key Table</li></ul> |    |  |  |  |  |  |  |  |  |  |  |  |

| 5.   | I/O Multiplexing and Considerations                                        | 14 |  |  |  |  |  |  |  |  |  |  |  |

|      | 5.1. Multiplexed Signals                                                   |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 5.2. Internal Multiplexed Signals                                          |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 5.3. Other Functions                                                       | 16 |  |  |  |  |  |  |  |  |  |  |  |

| 6.   | Signal Description                                                         | 18 |  |  |  |  |  |  |  |  |  |  |  |

|      | 6.1. Signal Details                                                        |    |  |  |  |  |  |  |  |  |  |  |  |

| 7.   | Processor and Architecture                                                 | 21 |  |  |  |  |  |  |  |  |  |  |  |

|      | 7.1. Cortex M0+ Processor                                                  |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 7.2. Nested Vector Interrupt Controller                                    |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 7.3. Micro Trace Buffer                                                    |    |  |  |  |  |  |  |  |  |  |  |  |

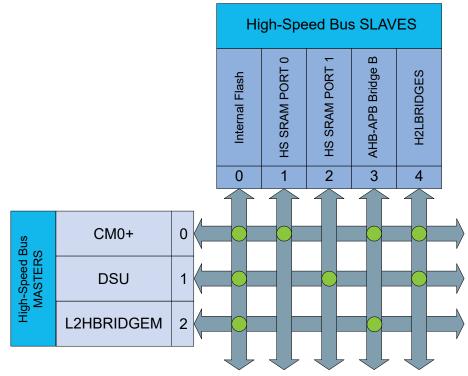

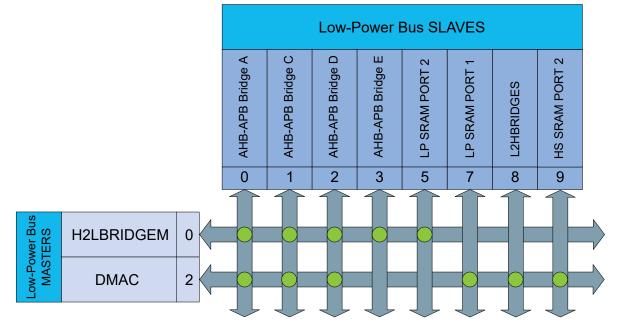

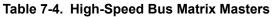

|      | 7.4. High-Speed Bus System                                                 | 25 |  |  |  |  |  |  |  |  |  |  |  |

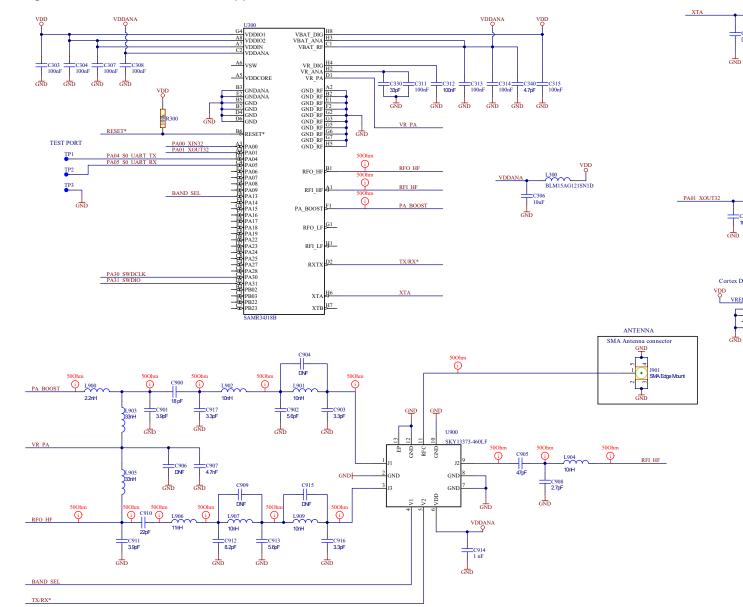

| 8.   | Application Schematic Introduction                                         |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 8.1. SAM R34/R35 Basic Application Schematic                               |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 8.2. SAM R34/R35 Bill of Materials                                         |    |  |  |  |  |  |  |  |  |  |  |  |

| 9.   | Transceiver Circuit Description                                            |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 9.1. Transceiver Pin Description                                           | 34 |  |  |  |  |  |  |  |  |  |  |  |

| 10.  | . Microcontroller Interface                                                |    |  |  |  |  |  |  |  |  |  |  |  |

| 11.  | Electrical Characteristics                                                 |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 11.1. Absolute Maximum Ratings                                             |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 11.2. General Operating Conditions                                         |    |  |  |  |  |  |  |  |  |  |  |  |

|      | 11.3. Performance Characteristics                                          |    |  |  |  |  |  |  |  |  |  |  |  |

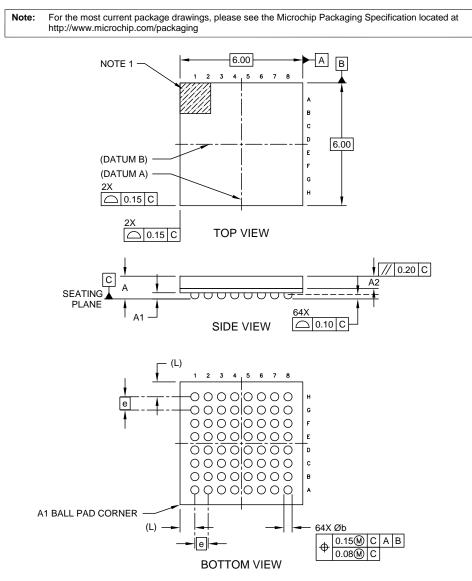

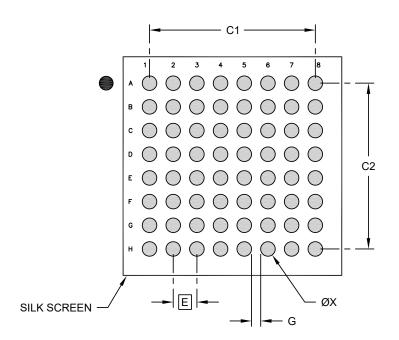

| 12.  | . SAM R34/R35 Package Information                                          | 44 |  |  |  |  |  |  |  |  |  |  |  |

| 12.1.     | Package Drawings                   | 44 |

|-----------|------------------------------------|----|

| 12.2.     | SAM R34/R35 Land Pattern           | 45 |

| 13. Best  | Practices for Designers            |    |

|           | Introduction                       |    |

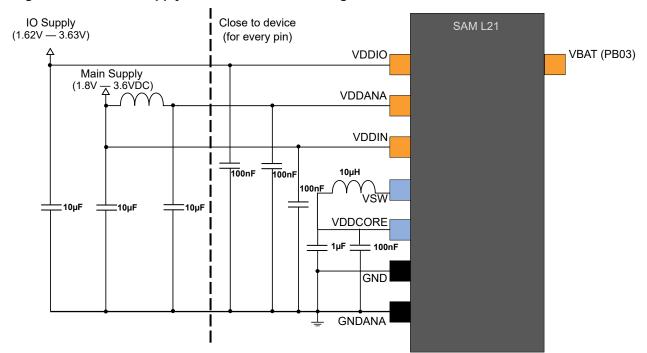

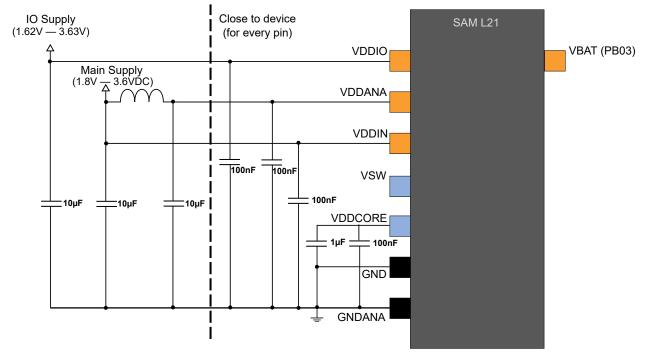

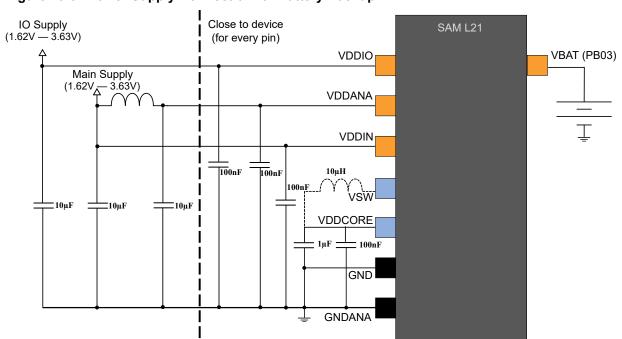

|           | Power Supply                       |    |

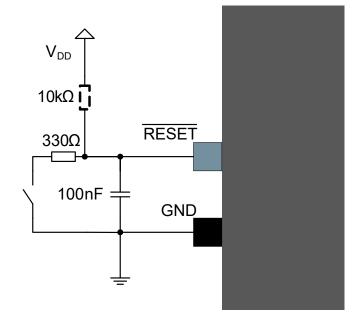

|           | External Reset Circuit             |    |

| 13.4.     | Unused or Unconnected Pins         | 50 |

| 13.5.     | Clocks and Crystal Oscillators     | 50 |

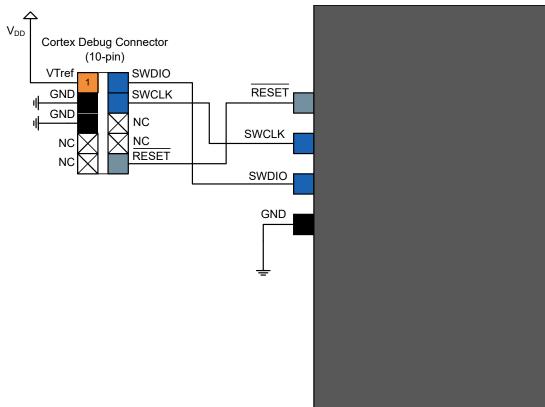

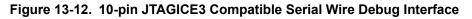

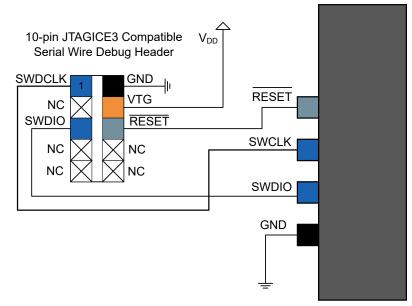

| 13.6.     | Programming and Debug Ports        | 53 |

| 14. Refe  | rence Documentation                | 57 |

| 15. Docu  | ument Revision History             | 58 |

| The Micr  | rochip Web Site                    | 59 |

| Custome   | er Change Notification Service     | 59 |

| Custome   | er Support                         | 59 |

| Microchi  | p Devices Code Protection Feature  |    |

| Legal No  | otice                              | 60 |

| Tradema   | arks                               | 60 |

| Quality N | Management System Certified by DNV | 61 |

| Worldwid  | de Sales and Service               | 62 |

## 1. Description

The SAM R34/R35 devices are a series of ultra-low power microcontrollers equipped with a UHF transceiver. It uses the 32-bit ARM Cortex-M0+ processor at max. 48 MHz (2.46 CoreMark/MHz) and offers 256 KB of Flash and 40 KB of SRAM. Sophisticated power management technologies, such as power domain gating, SleepWalking, ultra-low power peripherals and more, allow for very low line-power consumptions.

The UHF transceiver supports LoRa and FSK modulation schemes. The LoRa technology is optimized for long-range communication with minimal line-power demand. The transceiver can work from frequencies of 137 MHz to 1020 MHz. Maximum transmit power is +20 dBm without an external amplification. Operational frequency bands and power limits are defined by local regulations and the LoRa Alliance. LoRa network stack regional options insure compliance. FSK modulation is also supported for applications including IEEE 802.15.4g, WiSUN, and legacy proprietary networks.

All devices have accurate low power external and internal oscillators. Different clock domains can be independently configured to run at different frequencies, enabling power-saving by running each peripheral at its optimal clock frequency, thus maintaining a high CPU frequency while reducing power consumption.

The SAM R34/R35 devices have four software-selectable sleep modes: Idle, Standby, Backup and Off. In Idle mode, the CPU is stopped while all other functions may be kept running. In Standby mode, all clocks and functions are stopped except those selected to continue running. In this mode all RAMs and logic contents are retained. The device supports SleepWalking, which allows some peripherals to wake-up from sleep based on predefined conditions, thus allowing some internal operations like DMA transfer and/or the CPU to wake-up only when needed; for example, when a threshold is crossed or a result is ready. The event system supports synchronous and asynchronous events, allowing peripherals to receive, react to and send events even in Standby mode. Off mode is not advised, as high impedance on the internal SPI bus results in metastability.

The SAM R34/R35 devices have two software-selectable performance levels (PL0 and PL2) allowing the user to scale the lowest core voltage level that supports the operating frequency. To further minimize current consumption, specifically leakage dissipation, the devices utilize a power domain gating technique with retention to turn off some logic areas while keeping their logic state. This technique is fully handled in hardware.

The Flash program memory can be reprogrammed in-system through the Serial Wire Debug (SWD) interface. The same interface can also be used for non-intrusive on-chip debugging of application code. A boot loader running in the device can use any communication interface to download and upgrade the application program in the Flash memory.

The SAM R34/R35 devices are supported with a full suite of programs and system development tools, including C compilers, macro assemblers, program debugger/simulators, programmers, and evaluation kits.

# 2. Configuration Summary

Table 2-1. Configuration Summary

| Parameter                                               | SAM R34               | SAM R35               |

|---------------------------------------------------------|-----------------------|-----------------------|

| Total Pins                                              | 64                    | 64                    |

| General Purpose I/O pins<br>(GPIOs)                     | 27                    | 27                    |

| Flash                                                   | 256 KB                | 256 KB                |

| Flash RWW Section                                       | 8 KB                  | 8 KB                  |

| System SRAM                                             | 32 KB                 | 32 KB                 |

| Low Power SRAM                                          | 8 KB                  | 8 KB                  |

| Timer Counter (TC)<br>Instances                         | 3                     | 3                     |

| Waveform Output<br>Channels per TC<br>Instance          | 2                     | 2                     |

| Timer Counter for Control (TCC) Instances               | 3                     | 3                     |

| Waveform Output<br>Channels per TCC                     | 4/2/2                 | 4/2/2                 |

| USB Interface                                           | 1                     | 0                     |

| Serial Communication<br>Interface (SERCOM)<br>Instances | 5+1 <sup>(1)</sup>    | 5+1 <sup>(1)</sup>    |

| Analog-to-Digital<br>Converter (ADC)<br>Channels        | 8                     | 8                     |

| Analog Comparators<br>(AC)                              | 2                     | 2                     |

| Real-Time Counter (RTC)                                 | Yes                   | Yes                   |

| RTC Alarms                                              | 1                     | 1                     |

| RTC Compare Values                                      | 1 for 32-bit value or | 1 for 32-bit value or |

|                                                         | 2 for 16-bit values   | 2 for 16-bit values   |

| External Interrupt Lines                                | 15                    | 15                    |

| Maximum CPU<br>Frequency                                | 48 MHz                | 48 MHz                |

| Package                                                 | BGA                   | BGA                   |

| continued                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                  | SAM R34                                                                                                                                                                                                                                                                                                                                                                                                                                        | SAM R35                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 32.768 kHz Crystal<br>Oscillator (XOSC32K) | External                                                                                                                                                                                                                                                                                                                                                                                                                                       | External                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Oscillators                                | <ul> <li>16 MHz crystal oscillator for<br/>TRX (XOSCRF)</li> <li>0.4-32 MHz crystal oscillator<br/>(XOSC)</li> <li>32.768 kHz external oscillator<br/>(OSC32K)</li> <li>32 kHz ultra-low power internal<br/>oscillator (OSCULP32K)</li> <li>8 MHz high-accuracy internal<br/>oscillator (OSC8M)</li> <li>48 MHz Digital Frequency<br/>Locked Loop (DFLL48M)</li> <li>96 MHz Fractional Digital<br/>Phased Locked Loop<br/>(FDPLL96)</li> </ul> | <ul> <li>16 MHz crystal oscillator for<br/>TRX (XOSCRF)</li> <li>0.4-32 MHz crystal oscillator<br/>(XOSC)</li> <li>32.768 kHz external oscillator<br/>(OSC32K)</li> <li>32 kHz ultra-low power internal<br/>oscillator (OSCULP32K)</li> <li>8 MHz high-accuracy internal<br/>oscillator (OSC8M)</li> <li>48 MHz Digital Frequency<br/>Locked Loop (DFLL48M)</li> <li>96 MHz Fractional Digital<br/>Phased Locked Loop<br/>(FDPLL96)</li> </ul> |

| Event System Channels                      | 12                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SW Debug Interface                         | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                            | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Watchdog Timer (WDT)                       | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                            | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                            |

1. SERCOM4 is internally connected to the Transceiver (TRX).

# 3. Ordering Information for SAM R34/R35

Figure 3-1. SAM R34/R35 Ordering Information

|                                                                              | ATSAMR | 34     | J  | 18 | В | T- | 17 | xxx |

|------------------------------------------------------------------------------|--------|--------|----|----|---|----|----|-----|

| Product Family                                                               |        |        |    |    |   |    |    |     |

| SAMR = SoC Microcontroller w                                                 | ith RF | i<br>I |    |    |   |    | i  | i   |

| Product Series<br>34 = Cortex M0+ CPU + DMA +<br>35 = Cortex M0+ CPU + DMA + | -      |        | er |    |   |    |    |     |

| Pin Count                                                                    |        |        |    |    | i |    | ļ  |     |

| J = 64 Pins                                                                  |        |        |    |    |   |    |    |     |

| Flash Memory Density                                                         |        |        |    |    |   |    |    |     |

| 16 = 64 KB<br>17 = 128 KB<br>18 = 256 KB                                     |        |        |    | '  |   |    |    |     |

| Device Variant<br>B = Hardware Revision                                      |        |        |    |    |   |    |    |     |

| Package Carrier                                                              |        |        |    |    |   |    | i  | i   |

| T = Tape and Reel                                                            |        |        |    |    |   |    |    | ļ   |

| Temperature Rating                                                           |        |        |    |    |   |    |    |     |

| I = - 40 to + 85 °C                                                          |        |        |    |    |   |    | !  |     |

| Package Type                                                                 |        |        |    |    |   |    |    |     |

| 7JX = 64 Ball 6x6 mm TFBGA                                                   | ·      |        |    |    |   |    |    |     |

### 3.1 SAM R34/R35 Ordering Codes

### Table 3-1. SAM R34/R35 Ordering Codes

| Ordering Code       | Description                                                       |

|---------------------|-------------------------------------------------------------------|

| ATSAMR34J16BT-I/7JX | LoRa SiP Transceiver USB 64K Flash 8K SRAM, 4KB LP SRAM, T&R      |

| ATSAMR34J17BT-I/7JX | LoRa SiP Transceiver USB 128K Flash 16K SRAM, 8KB LP SRAM, T&R    |

| ATSAMR34J18BT-I/7JX | LoRa SiP Transceiver USB 256K Flash 32K SRAM, 8KB LP SRAM,<br>T&R |

| ATSAMR35J16BT-I/7JX | LoRa SiP Transceiver 64K Flash 8K SRAM, 4KB LP SRAM, T&R          |

| ATSAMR35J17BT-I/7JX | LoRa SiP Transceiver 128K Flash 16K SRAM, 8KB LP SRAM, T&R        |

| ATSAMR35J18BT-I/7JX | LoRa SiP Transceiver 256K Flash 32K SRAM, 8KB LP SRAM, T&R        |

# 4. System Introduction

### 4.1 SAM R34/R35 Pinout Details

#### Figure 4-1. SAM R34/R35 Pin Placement

|   | 1        | 2      | 3        | 4      | 5       | 6      | 7      | 8        |

|---|----------|--------|----------|--------|---------|--------|--------|----------|

| Α | RFI_HF   | GND_RF | PA00     | PA01   | VDDCORE | VSW    | VDDIN  | VDDIO2   |

| В | RFO_HF   | GND_RF | GNDANA   | PB02   | GND     | RESET* | GND    | PA24     |

| С | VBAT_RF  | VDDANA | PB03     | PA05   | PA30    | PA28   | PB23   | PA25     |

| D | VR_PA    | RXTX   | PA04     | GND    | PA31    | GND    | PA23   | PA22     |

| E | GND_RF   | GNDANA | PA06     | PA27   | PB22    | PA17   | PA18   | PA19     |

| F | PA_BOOST | GND_RF | PA07     | PA08   | PA09    | PA13   | PA16   | PA14     |

| G | RFO_LF   | GND_RF | GND_RF   | VDDI01 | GND_RF  | GND_RF | GND_RF | PA15     |

| н | RFI_LF   | VR_ANA | VBAT_ANA | VR_DIG | GND_RF  | ХТА    | ХТВ    | VBAT_DIG |

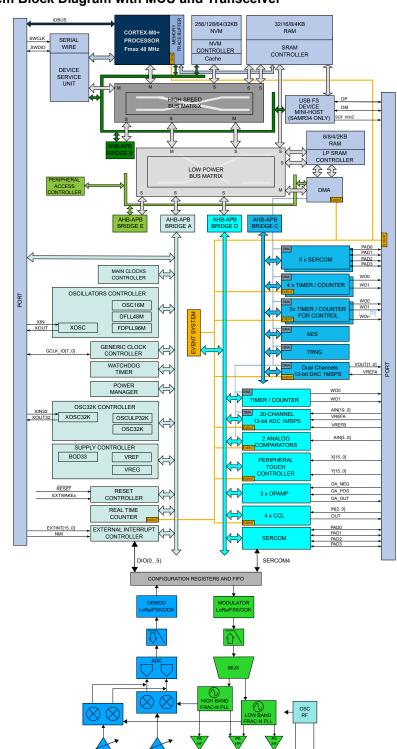

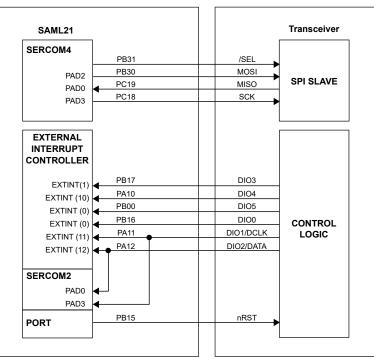

### 4.2 SiP Block Diagram

The following figure illustrates the SAM R34/R35 System-in-Package (SiP) block diagram.

#### Figure 4-2. System Block Diagram with MCU and Transceiver

# 4.3 Peripheral Key Table

# Table 4-1. Peripheral Key Table

| Peripheral | Description                           | Reference<br>Document | Topic # and Keyword                                 | Notes                |

|------------|---------------------------------------|-----------------------|-----------------------------------------------------|----------------------|

| AC         | Analog Comparator                     | 1                     | 43. AC – Analog Comparators                         |                      |

| ADC        | Analog-to-Digital<br>Converter        | 1                     | 42. ADC – Analog-to-Digital<br>Converter            |                      |

| AES        | Advanced Encryption<br>Engine         | 1                     | 38. AES – Advanced<br>Encryption Standard           |                      |

| BOD33      | Brown-out Detector                    | 1                     | 23. SUPC – Supply Controller                        |                      |

| CCL        | Configurable Custom<br>Logic          | 1                     | 40. CCL – Configurable<br>Custom Logic              |                      |

| CRC        | Cyclic Redundancy<br>Check-sum        | 1                     | 15.11.3 32-bit Cyclic<br>Redundancy Check CRC32     |                      |

| DAC        | Digital-to-Analog<br>Converter        | 1                     | 44. DAC – Digital-to-Analog<br>Converter            |                      |

| DMA        | Direct Memory Access<br>Controller    | 1                     | 26. DMAC – Direct Memory<br>Access Controller       |                      |

| EIC        | External Interrupt                    | 1                     | 27. EIC – External Interrupt<br>Controller          |                      |

| EVSYS      | Event System                          | 1                     | 30. EVSYS – Event System                            |                      |

| GCLK       | Generic Clock Control                 | 1                     | 17. GCLK - Generic Clock<br>Controller              |                      |

| 12C        | Inter-integrated Circuit<br>Interface | 1                     | 34. SERCOM I2C – SERCOM<br>Inter-integrated Circuit | SERCOM 4<br>Reserved |

| MCLK       | Main Clock Control                    | 1                     | 18. MCLK – Main Clock                               |                      |

| NVMCTRL    | Nonvolatile Memory<br>Controller      | 1                     | 28. NVMCTRL – Nonvolatile<br>Memory Controller      |                      |

| OPAMP      | Operational Amplifier                 | 1                     | 41. OPAMP – Operational<br>Amplifier Controller     |                      |

| OSC32KCTRL | 32 kHz Clock                          | 1                     | 22. OSC32KCTRL – 32KHz<br>Oscillators Controller    |                      |

| OSCCTRL    | Clock Control                         | 1                     | 21. OSCCTRL – Oscillators<br>Controller             |                      |

| PA_BOOST   | RF Output High-power                  | 5                     | 5.4.2. RF Power Amplifiers                          |                      |

| PM         | Power Management                      | 1                     | 20. PM – Power Manager                              |                      |

© 2018 Microchip Technology Inc.

# **SAM R34/R35**

# System Introduction

| continued  |                                                                   |                       |                                                                                                       |                      |  |  |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|--|--|--|--|

| Peripheral | Description                                                       | Reference<br>Document | Topic # and Keyword                                                                                   | Notes                |  |  |  |  |  |  |  |  |  |

| PORT       | GPIO Port Controller                                              | 1                     | 29. PORT - I/O Pin Controller                                                                         | Limited to 27 Ports  |  |  |  |  |  |  |  |  |  |

| PORT       | Power-On Reset                                                    | 1                     | 23. SUPC – Supply Controller                                                                          |                      |  |  |  |  |  |  |  |  |  |

| PTC        | Peripheral Touch<br>Controller (RC)                               | 1                     | 45. PTC - Peripheral Touch<br>Controller                                                              |                      |  |  |  |  |  |  |  |  |  |

| RFI_HF     | RF Input High<br>Frequency                                        | 5                     | 5.5. Receiver Description                                                                             |                      |  |  |  |  |  |  |  |  |  |

| RFI_LF     | RF Input Low<br>Frequency                                         | 5                     | 5.5. Receiver Description                                                                             |                      |  |  |  |  |  |  |  |  |  |

| RFO_HF     | RF Output High<br>Frequency                                       | 5                     | 5.4.2. RF Power Amplifiers                                                                            |                      |  |  |  |  |  |  |  |  |  |

| RFO_LF     | RF Output Low<br>Frequency                                        | 5                     | 5.4.2. RF Power Amplifiers                                                                            |                      |  |  |  |  |  |  |  |  |  |

| RSTC       | Reset Control                                                     | 1                     | 19. RSTC – Reset Controller                                                                           |                      |  |  |  |  |  |  |  |  |  |

| RTC        | Real-Time Counter                                                 | 1                     | 25. RTC – Real-Time Counter                                                                           |                      |  |  |  |  |  |  |  |  |  |

| SPI        | Serial Peripheral<br>Interface                                    | 1                     | 33. SERCOM SPI – SERCOM<br>Serial Peripheral Interface                                                | SERCOM 4<br>Reserved |  |  |  |  |  |  |  |  |  |

| тс         | Timer Counter                                                     | 1                     | 35. TC – Timer/Counter                                                                                |                      |  |  |  |  |  |  |  |  |  |

| TCC        | Timer Counter for<br>Control                                      | 1                     | 36. TCC – Timer/Counter for<br>Control Applications                                                   |                      |  |  |  |  |  |  |  |  |  |

| TRNG       | Random Number<br>Generator                                        | 1                     | 37. TRNG – True Random<br>Number Generator                                                            |                      |  |  |  |  |  |  |  |  |  |

| USART      | Universal Synchronous<br>and Asynchronous<br>Receiver/Transmitter | 1                     | 32. SERCOM USART –<br>SERCOM Universal<br>Synchronous and<br>Asynchronous Receiver and<br>Transmitter | SERCOM 4<br>Reserved |  |  |  |  |  |  |  |  |  |

| USB        | Full-speed Universal<br>Serial Bus 2.0 interface                  | 1                     | 39. USB – Universal Serial Bus                                                                        | SAMR34<br>Only       |  |  |  |  |  |  |  |  |  |

| VBAT       | External Battery Input                                            | 1                     | 23. SUPC – Supply Controller                                                                          |                      |  |  |  |  |  |  |  |  |  |

| VSW        | Switch Mode Power<br>Output                                       | 1                     | 50.2 Power Supply                                                                                     |                      |  |  |  |  |  |  |  |  |  |

| WDT        | Watchdog Timer                                                    | 1                     | 24. WDT – Watchdog Timer                                                                              |                      |  |  |  |  |  |  |  |  |  |

| XTA/B      | RF Oscillator                                                     | 5                     | 5.3. Frequency Synthesis                                                                              |                      |  |  |  |  |  |  |  |  |  |

# 5. I/O Multiplexing and Considerations

### 5.1 Multiplexed Signals

By default, each pin is controlled by the PORT as a general purpose I/O and alternatively may be assigned to one of the peripheral functions A, B, C, D, E, F, G, H or I. To enable a peripheral function on a pin, the Peripheral Multiplexer Enable bit in the Pin Configuration register corresponding to that pin (PINCFGn.PMUXEN, n = 0..31) in the PORT must be written to '1'. The selection of peripheral functions A to H are done by writing to the Peripheral Multiplexing Odd and Even bits in the Peripheral Multiplexing register (PMUXn.PMUXE/O) in the PORT.

| Pin         | 1/0  | Supply | A          |            | B (1)(2) |         |        |           |           |          | с                  | D                  | E              | F              | G                       | н                | I               |

|-------------|------|--------|------------|------------|----------|---------|--------|-----------|-----------|----------|--------------------|--------------------|----------------|----------------|-------------------------|------------------|-----------------|

| SAM<br>R34/ | Pin  |        | EIC        | RSTC       | REF      | ADC     | AC     | PTC<br>X- | PTC<br>Y- | OPAMP    | SERCOM<br>(1)(2)   | SERCOM-<br>ALT     | тс/тс<br>с     | тсс            | сом                     | AC/GCLK/<br>SUPC | CCL             |

| R35         |      |        |            |            |          |         |        | lines     | lines     |          |                    |                    |                |                |                         |                  |                 |

| A3          | PA00 | VSWOUT | EXTINT[0]  | EXTWAKE[0] | -        | -       | -      | -         | -         | -        | -                  | SERCOM1/<br>PAD[0] | TCC2/<br>WO[0] | -              | -                       | -                | -               |

| A4          | PA01 | VSWOUT | EXTINT[1]  | EXTWAKE[1] | -        | -       | -      | -         | -         | -        | -                  | SERCOM1/<br>PAD[1] | TCC2/<br>WO[1] | -              | -                       | -                | -               |

| D3          | PA04 | VDDANA | EXTINT[4]  | EXTWAKE[4] | VREFB    | AIN[4]  | AIN[0] | -         | -         | OAOUT[2] | -                  | SERCOM0/<br>PAD[0] | TCC0/<br>WO[0] | -              | -                       | -                | CCL0/<br>IN[0]  |

| C4          | PA05 | VDDANA | EXTINT[5]  | EXTWAKE[5] | -        | AIN[5]  | AIN[1] | -         | -         | OAPOS[2] | -                  | SERCOM0/<br>PAD[1] | TCC0/<br>WO[1] | -              | -                       | -                | CCL0/<br>IN[1]  |

| E3          | PA06 | VDDANA | EXTINT[6]  | EXTWAKE[6] | -        | AIN[6]  | AIN[2] | -         | Y[4]      | OAPOS[0] | -                  | SERCOM0/<br>PAD[2] | TCC1/<br>WO[0] | -              | -                       | -                | CCL0/<br>IN[2]  |

| F3          | PA07 | VDDANA | EXTINT[7]  | EXTWAKE[7] | -        | AIN[7]  | AIN[3] | -         | -         | OAOUT[0] | -                  | SERCOM0/<br>PAD[3] | TCC1/<br>WO[1] | -              | -                       | -                | CCL0/<br>OUT[0] |

| F4          | PA08 | VDDIO  | NMI        | -          | -        | AIN[16] | -      | X[0]      | Y[6]      | -        | SERCOM0/<br>PAD[0] | SERCOM2/<br>PAD[0] | TCC0/<br>WO[0] | TCC1/<br>WO[2] | -                       | -                | CCL1/<br>IN[3]  |

| F5          | PA09 | VDDIO  | EXTINT[9]  | -          | -        | AIN[17] |        | X[1]      | Y[7]      | -        | SERCOM0/<br>PAD[1] | SERCOM2/<br>PAD[1] | TCC0/<br>WO[1] | TCC1/<br>WO[3] | -                       | -                | CCL1/<br>IN[1]  |

| F6          | PA13 | VDDIO  | EXTINT[13] | -          | -        | -       | -      | -         | -         | -        | SERCOM2/<br>PAD[1] | SERCOM4/<br>PAD[1] | TCC2/<br>WO[1] | TCC0/<br>WO[7] | -                       | AC/CMP[1]        | -               |

| F8          | PA14 | VDDIO  | EXTINT[14] | -          | -        | -       | -      | -         | -         | -        | SERCOM2/<br>PAD[2] | SERCOM4/<br>PAD[2] | TC4/<br>WO[0]  | TCC0/<br>WO[4] | -                       | GCLK_IO[0]       | -               |

| G8          | PA15 | VDDIO  | EXTINT[15] | -          | -        | -       | -      | -         | -         | -        | SERCOM2/<br>PAD[3] | SERCOM4/<br>PAD[3] | TC4/<br>WO[1]  | TCC0/<br>WO[5] | -                       | GCLK_IO[1]       | -               |

| F7          | PA16 | VDDIO  | EXTINT[0]  | -          | -        | -       | -      | X[4]      | -         | -        | SERCOM1/<br>PAD[0] | SERCOM3/<br>PAD[0] | TCC2/<br>WO[0] | TCC0/<br>WO[6] | -                       | GCLK_IO[2]       | CCL0/<br>IN[0]  |

| E6          | PA17 | VDDIO  | EXTINT[1]  | -          | -        | -       | -      | X[5]      | -         | -        | SERCOM1/<br>PAD[1] | SERCOM3/<br>PAD[1] | TCC2/<br>WO[1] | TCC0/<br>WO[1] | -                       | GCLK_IO[3]       | CCL0/<br>IN[1]  |

| E7          | PA18 | VDDIO  | EXTINT[2]  | -          | -        | -       | -      | X[6]      | -         | -        | SERCOM1/<br>PAD[2] | SERCOM3/<br>PAD[2] | TC4/<br>WO[0]  | TCC0/<br>WO[2] | -                       | AC/CMP[0]        | CCL0/<br>IN[2]  |

| E8          | PA19 | VDDIO  | EXTINT[3]  | -          | -        | -       | -      | X[7]      | -         | -        | SERCOM1/<br>PAD[3] | SERCOM3/<br>PAD[3] | TC4/<br>WO[1]  | TCC0/<br>WO[3] | -                       | AC/CMP[1]        | CCL0/<br>OUT[0] |

| D8          | PA22 | VDDIO  | EXTINT[6]  | -          | -        | -       | -      | X[10]     | -         | -        | SERCOM3/<br>PAD[0] | SERCOM5/<br>PAD[0] | TC0/<br>WO[0]  | TCC0/<br>WO[4] | -                       | GCLK_IO[6]       | CCL2/<br>IN[0]  |

| D7          | PA23 | VDDIO  | EXTINT[7]  | -          | -        | -       | -      | X[11]     | -         | -        | SERCOM3/<br>PAD[1] | SERCOM5/<br>PAD[1] | TC0/<br>WO[1]  | TCC0/<br>WO[5] | USB/SO<br>F 1<br>kHz[6] | GCLK_IO[7]       | CCL2/<br>IN[1]  |

| B8          | PA24 | VDDIO  | EXTINT[12] | -          | -        | -       | -      | -         | -         | -        | SERCOM3/<br>PAD[2] | SERCOM5/<br>PAD[2] | TC1/<br>WO[0]  | TCC1/<br>WO[2] | USB/<br>DM[6]           | -                | CCL2/<br>IN[2]  |

| C8          | PA25 | VDDIO  | EXTINT[13] | -          | -        | -       | -      | -         | -         | -        | SERCOM3/<br>PAD[3] | SERCOM5/<br>PAD[3] | TC1/<br>WO[1]  | TCC1/<br>WO[3] | USB/<br>DP[6]           | -                | CCL2/<br>OUT[2] |

| E5          | PB22 | VDDIN  | EXTINT[6]  | -          | -        | -       | -      | -         | -         | -        | -                  | SERCOM5/<br>PAD[2] | TC3/<br>WO[0]  | -              | -                       | GCLK_IO[0]       | CCL0/<br>IN[0]  |

| C7          | PB23 | VDDIN  | EXTINT[7]  | -          | -        | -       | -      | -         | -         | -        | -                  | SERCOM5/<br>PAD[3] | TC3/<br>WO[1]  | -              | -                       | GCLK_IO[1]       | CCL0/<br>OUT[0] |

| E4          | PA27 | VDDIN  | EXTINT[15] | -          | -        | -       | -      | -         | -         | -        | -                  | -                  | -              | -              | -                       | GCLK_IO[0]       | -               |

#### Table 5-1. Port Function Multiplexing

| c                  | continued  |        |            |      |          |         |    |                    |                    |       |                  |                    |                |     |              |                  |                 |

|--------------------|------------|--------|------------|------|----------|---------|----|--------------------|--------------------|-------|------------------|--------------------|----------------|-----|--------------|------------------|-----------------|

| Pin                | I/O<br>Pin | Supply | A          |      | B (1)(2) |         |    |                    |                    |       | с                | D                  | E              | F   | G            | н                | 1               |

| SAM<br>R34/<br>R35 |            |        | EIC        | RSTC | REF      | ADC     | AC | PTC<br>X-<br>lines | PTC<br>Y-<br>lines | OPAMP | SERCOM<br>(1)(2) | SERCOM-<br>ALT     | тс/тс<br>с     | тсс | сом          | AC/GCLK/<br>SUPC | CCL             |

| C6                 | PA28       | VDDIN  | EXTINT[8]  | -    | -        | -       | -  | -                  | -                  | -     | -                | -                  | -              | -   | -            | GCLK_IO[0]       | -               |

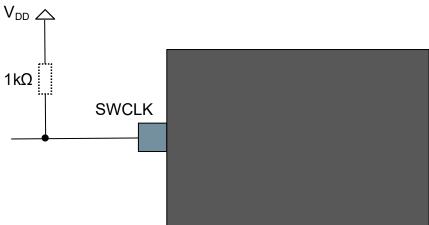

| C5                 | PA30       | VDDIN  | EXTINT[10] | -    | -        | -       | -  | -                  | -                  | -     | -                | SERCOM1/<br>PAD[2] | TCC1/<br>WO[0] | -   | SWCLK        | GCLK_IO[0]       | CCL1/<br>IN[0]  |

| D5                 | PA31       | VDDIN  | EXTINT[11] | -    | -        | -       | -  | -                  | -                  | -     | -                | SERCOM1/<br>PAD[3] | TCC1/<br>WO[1] | -   | SWDIO(<br>3) | -                | CCL1/<br>OUT[1] |

| B4                 | PB02       | VSWOUT | EXTINT[2]  | -    | -        | AIN[10] | -  | -                  | -                  | -     | -                | SERCOM5/<br>PAD[0] | TC2/<br>WO[0]  | -   | -            | SUPC/<br>OUT[1]  | CCL0/<br>OUT[0] |

| C3                 | PB03       | VSWOUT | EXTINT[3]  | -    | -        | AIN[11] | -  | -                  | -                  | -     | -                | SERCOM5/<br>PAD[1] | TC2/<br>WO[1]  | -   | -            | SUPC/VBAT        |                 |

- 1. All analog pin functions are on peripheral function B. Peripheral function B must be selected to disable the digital control of the pin.

- 2. Only some pins can be used in SERCOM I2Cmode. See 5.3.3 SERCOM I2C Pins .

- 3. This function is only activated in the presence of a debugger.

- 4. When an analog peripheral is enabled, the analog output of the peripheral interferes with the alternative functions of this pin. This is also true even when the peripheral is used for internal purposes.

- 5. Clusters of multiple GPIO pins are sharing the same supply pin. See 5.3.4 GPIO Cluster.

- 6. USB is not available on the SAM R35 devices.

### 5.2 Internal Multiplexed Signals

By default, each pin is controlled by the PORT as a general purpose I/O and alternatively may be assigned to one of the peripheral functions A, B, C, D, E, F, G, H or I. To enable a peripheral function on a pin, the Peripheral Multiplexer Enable bit in the Pin Configuration register corresponding to that pin (PINCFGn.PMUXEN, n = 0-31) in the PORT must be written to '1'. The selection of peripheral functions A to H are done by writing to the Peripheral Multiplexing Odd and Even bits in the Peripheral Multiplexing register (PMUXn.PMUXE/O) in the PORT.

| Internal      |      |        |     |            | в    |     |         |    |                    |                    | с     | D                  | E                  | F              | G                         | н   | I                |                 |

|---------------|------|--------|-----|------------|------|-----|---------|----|--------------------|--------------------|-------|--------------------|--------------------|----------------|---------------------------|-----|------------------|-----------------|

| Signal        | Pin  |        |     | EIC        | RSTC | REF | ADC     | AC | PTC<br>X-<br>lines | PTC<br>Y-<br>lines | OPAMP | SERCOM             | SERCOM-<br>ALT     | тс/тс<br>с     | FECTRL/<br>TCC/<br>SERCOM | сом | AC/GCLK/<br>SUPC | CCL             |

| DIO0          | PB16 | VDDIO  | I/O | EXTINT[0]  | -    | -   | -       | -  | -                  | -                  | -     | SERCOM5/<br>PAD[0] | -                  | TCC2/<br>WO[0] | TCC0/<br>WO[4]            | -   | GCLK_IO[2]       | CCL3/<br>IN[11] |

| DIO1/<br>DCLK | PA11 | VDDIO  | I/O | EXTINT[11] | -    | -   | AIN[19] | -  | X[3]               | Y[9]               | -     | SERCOM0/<br>PAD[3] | SERCOM2/<br>PAD[3] | TCC1/<br>WO[1] | TCC0/<br>WO[3]            | -   | GCLK_IO[5]       | CCL1/<br>OUT[1] |

| DIO2/<br>DATA | PA12 | VDDIO  | I/O | EXTINT[12] | -    | -   | -       | -  | -                  | -                  | -     | SERCOM2/<br>PAD[0] | SERCOM4/<br>PAD[0] | TCC2/<br>WO[0] | TCC0/<br>WO[6]            | -   | AC/CMP[0]        | -               |

| DIO3          | PB17 | VDDIO  | I/O | EXTINT[1]  | -    | -   | -       | -  | -                  | -                  | -     | SERCOM5/<br>PAD[1] | -                  | TCC2/<br>WO[1] | TCC0/<br>WO[5]            | -   | GCLK_IO[3]       | CCL3/<br>OUT[3] |

| DIO4          | PA10 | VDDIO  | I/O | EXTINT[10] | -    | -   | AIN[18] | -  | X[2]               | Y[8]               | -     | SERCOM0/<br>PAD[2] | SERCOM2/<br>PAD[2] | TCC1/<br>WO[0] | TCC0/<br>WO[2]            | -   | GCLK_IO[4]       | CCL1/<br>IN[5]  |

| DIO5          | PB00 | VDDANA | I/O | EXTINT[0]  | -    | -   | AIN[8]  | -  | -                  | -                  | -     | -                  | SERCOM5/<br>PAD[2] | TCC3/<br>WO[0] | -                         | -   | SUPC_PSOK        | CCL0/<br>IN[1]  |

| RF_RST        | PB15 | VDDIO  | I/O | EXTINT[15] | -    | -   | -       | -  | X[15]              | -                  | -     | SERCOM4/<br>PAD[3] | -                  | TCC0/<br>WO[1] | -                         | -   | GCLK_IO[1]       | CCL3/<br>IN[10] |

| MOSI          | PB30 | VDDIO  | I/O | EXTINT[14] | -    | -   | -       | -  | -                  | -                  | -     | -                  | SERCOM5/<br>PAD[0] | TCC0/<br>WO[0] | SERCOM4/<br>PAD[2]        | -   | -                | -               |

| SEL           | PB31 | VDDIO  | I/O | EXTINT[15] | -    | -   | -       | -  | -                  | -                  | -     | -                  | SERCOM5/<br>PAD[1] | TCC0/<br>WO[1] | SERCOM4/<br>PAD[1]        | -   | -                | -               |

# SAM R34/R35 I/O Multiplexing and Considerations

| cont     | tinued |       |     |     |      |     |     |    |                    |                    |       |        |                |            |                           |     |                  |     |

|----------|--------|-------|-----|-----|------|-----|-----|----|--------------------|--------------------|-------|--------|----------------|------------|---------------------------|-----|------------------|-----|

| Internal |        |       | A   |     | В    |     |     |    |                    | с                  | D     | E      | F              | G          | н                         | 1   |                  |     |

| Signal   | Pin    |       |     | EIC | RSTC | REF | ADC | AC | PTC<br>X-<br>lines | PTC<br>Y-<br>lines | OPAMP | SERCOM | SERCOM-<br>ALT | тс/тс<br>с | FECTRL/<br>TCC/<br>SERCOM | СОМ | AC/GCLK/<br>SUPC | CCL |

| SCLK     | PC18   | VDDIO | I/O | -   | -    | -   | -   | -  | -                  | -                  | -     | -      | -              | -          | SERCOM4/<br>PAD[3]        | -   | -                | -   |

| MISO     | PC19   | VDDIO | I/O | -   | -    | -   | -   | -  | -                  | -                  | -     | -      | -              | -          | SERCOM4/<br>PAD[0]        | -   | -                | -   |

### 5.3 Other Functions

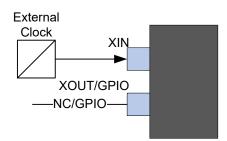

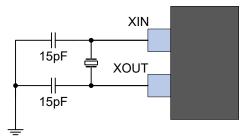

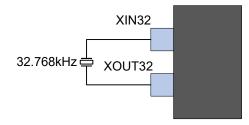

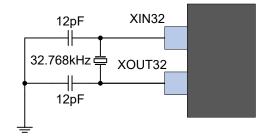

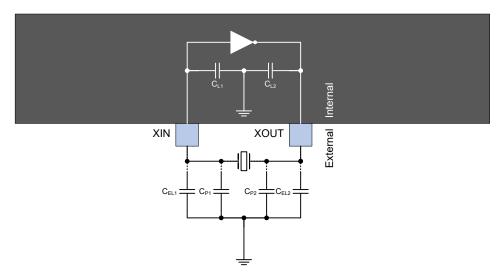

#### 5.3.1 Oscillator Pinout

The oscillators are not mapped to the normal PORT functions, and their multiplexing is controlled by registers in the Oscillator Controller (OSCCTROL) and in the 32kHz Oscillators Controller (OSC32KCTRL).

#### Table 5-3. Oscillator Pinout

| Oscillator | Supply | Signal | I/O Port |

|------------|--------|--------|----------|

| XOSC       | VDDIO  | XIN    | PA14     |

|            |        | XOUT   | PA15     |

| XOSC32K    | VSWOUT | XIN32  | PA00     |

|            |        | XOUT32 | PA01     |

#### 5.3.2 Serial Wire Debug Interface Pins

Only the SWCLK pin is mapped to the normal PORT functions. A debugger cold-plugging or hot-plugging detection will automatically switch the SWDIO port to the SWDIO function.

#### Table 5-4. Serial Wire Debug Interface Pinout

| Signal | Supply | I/O Pin |

|--------|--------|---------|

| SWCLK  | VDDIN  | PA30    |

| SWDIO  | VDDIN  | PA31    |

### 5.3.3 SERCOM I<sup>2</sup>C Pins

#### Table 5-5. SERCOM Pins Supporting I<sup>2</sup>C

| Device      | Pins Supporting I <sup>2</sup> C HS Mode |

|-------------|------------------------------------------|

| SAM R34/R35 | PA08, PA09, PA13, PA16, PA17, PA22, PA23 |

#### 5.3.4 GPIO Cluster

Table 5-6. GPIO Clusters

| Package | Cluster | GPIO | GPIO |      |      |      |      |      |      |      |      |      | Supply Pins Connected to the Cluster |      |                                        |

|---------|---------|------|------|------|------|------|------|------|------|------|------|------|--------------------------------------|------|----------------------------------------|

| 64 Pins | 1       | PA31 | PA30 | -    | -    | -    | -    | -    | -    | -    | -    | -    | -                                    | -    | VDDIN C4/GND D4                        |

|         | 2       | PA28 | PA27 | PB23 | PB22 | -    | -    | -    | -    | -    | -    | -    | -                                    | -    | VDDIN C4/GND D4 and<br>VDDIO C6/GND C5 |

|         | 3       | PA25 | PA24 | PA23 | PA22 | -    | -    | PA19 | PA18 | PA17 | PA16 | PA15 | PA14                                 | PA13 | VDDIO C6/GND C5 and<br>VDDIO F3/GND F4 |

|         | 4       | -    | -    | PA09 | PA08 | -    | -    | -    | -    | -    | -    | -    | -                                    | -    | VDDIO F3/GND F4                        |

|         | 5       | PA07 | PA06 | PA05 | PA04 | -    | -    | -    | -    | -    | -    | -    | -                                    | -    | VDDANA C1/GNDANA C3                    |

|         | 6       | -    | -    | PA01 | PA00 | PB03 | PB02 | -    | -    | -    | -    | -    | -                                    | -    | VDDANA C1/GNDANA C3                    |

#### 5.3.5 TCC Configurations

The SAML21 has three instances of the Timer/Counter for Control applications (TCC) peripheral, TCC<2:0>.

#### Table 5-7. TCC Configuration Summary

| TCC<br>No. |   |   | Counter<br>Size | Fault | Dithering | -   | Dead<br>Time<br>Insertion<br>(DTI) | SWAP | Pattern<br>Generation |

|------------|---|---|-----------------|-------|-----------|-----|------------------------------------|------|-----------------------|

| 0          | 4 | 8 | 24-bit          | Yes   | Yes       | Yes | Yes                                | Yes  | Yes                   |

| 1          | 2 | 4 | 24-bit          | Yes   | Yes       |     | —                                  | _    | Yes                   |

| 2          | 2 | 2 | 16-bit          | Yes   |           |     |                                    |      |                       |

**Note:** The number of CC register (CC\_NUM)\_ for each TCC corresponds to the number of compare/ capture channels to ensure that a TCC can have more Waveform Outputs (WO\_NUM) than CC registers.

# 6. Signal Description

This section provides the required information to understand the origin and the function of each such signal. The nature of a SIP results in the situation where the package pins may be bonded to the microcontroller die or the transceiver die. There are also signals bonded in-between the two dies.

### 6.1 Signal Details

This section provides the naming and functional description of the internal and external signals. 5. I/O Multiplexing and Considerations describes the routing of these signals between the MCU core and transceiver subsystem and to the external package pins.

| Signal Name                    | Function                                                              | Туре    |  |  |  |  |  |  |

|--------------------------------|-----------------------------------------------------------------------|---------|--|--|--|--|--|--|

| Analog Compara                 | itors (AC)                                                            |         |  |  |  |  |  |  |

| AIN<3:0>                       | AC analog inputs                                                      | Analog  |  |  |  |  |  |  |

| CMP<1:0>                       | AC comparator outputs                                                 | Digital |  |  |  |  |  |  |

| Analog Digital Converter (ADC) |                                                                       |         |  |  |  |  |  |  |

| AIN<19:0>                      | ADC analog inputs                                                     | Analog  |  |  |  |  |  |  |

| VREFB                          | ADC voltage external reference B                                      | Analog  |  |  |  |  |  |  |

| Operational Amp                | olifier (OPAMP)                                                       |         |  |  |  |  |  |  |

| OANEG<2:0>                     | OPAMP analog negative inputs                                          | Analog  |  |  |  |  |  |  |

| OAPOS<2:0>                     | OPAMP analog positive inputs                                          | Analog  |  |  |  |  |  |  |

| OAOUT<2:0>                     | OPAMP analog outputs                                                  | Analog  |  |  |  |  |  |  |

| External Interrup              | ot Controller (EIC)                                                   |         |  |  |  |  |  |  |

| EXTINT<15:0>                   | External interrupts inputs                                            | Digital |  |  |  |  |  |  |

| NMI                            | External non-maskable interrupt input                                 | Digital |  |  |  |  |  |  |

| Reset Controller               | (RSTC)                                                                |         |  |  |  |  |  |  |

| EXTWAKE<7:0>                   | External wake-up inputs                                               | Digital |  |  |  |  |  |  |

| Generic Clock G                | enerator (GCLK)                                                       |         |  |  |  |  |  |  |

| GCLK_IO<7:0>                   | Generic clock (source clock inputs or generic clock generator output) | Digital |  |  |  |  |  |  |

| Custom Control                 | Logic (CCL)                                                           |         |  |  |  |  |  |  |

| IN<11:0>                       | Logic inputs                                                          | Digital |  |  |  |  |  |  |

| OUT<3:0>                       | Logic outputs                                                         | Digital |  |  |  |  |  |  |

| Supply Controlle               | er (SUPC)                                                             |         |  |  |  |  |  |  |

| VBAT                           | External battery supply inputs                                        | Analog  |  |  |  |  |  |  |

| PSOK                           | Main power supply OK input                                            | Digital |  |  |  |  |  |  |

Table 6-1. Signal Descriptions List

# **SAM R34/R35**

# Signal Description

| continued                                |                                               |                |  |  |  |  |  |  |

|------------------------------------------|-----------------------------------------------|----------------|--|--|--|--|--|--|

| Signal Name                              | Function                                      | Туре           |  |  |  |  |  |  |

| OUT<1:0>                                 | Logic outputs                                 | Digital        |  |  |  |  |  |  |

| Power Manager (PM)                       |                                               |                |  |  |  |  |  |  |

| RESETN                                   | Active low Reset input                        | Digital        |  |  |  |  |  |  |

| Serial Communication Interface (SERCOMx) |                                               |                |  |  |  |  |  |  |

| PAD<3:0>                                 | SERCOM Input/Output pads                      | Digital        |  |  |  |  |  |  |

| <b>Oscillators Cont</b>                  | rol (OSCCTRL)                                 |                |  |  |  |  |  |  |

| XIN                                      | Crystal or external clock input               | Analog/Digital |  |  |  |  |  |  |

| XOUT                                     | Crystal output                                | Analog         |  |  |  |  |  |  |

| 32KHz Oscillator                         | rs Control (OSC32KCTRL)                       |                |  |  |  |  |  |  |

| XIN32                                    | 32KHz crystal or external clock input         | Analog/Digital |  |  |  |  |  |  |

| XOUT32                                   | 32KHz crystal output                          | Analog         |  |  |  |  |  |  |

| Timer Counter (1                         | ГСх)                                          |                |  |  |  |  |  |  |

| WO<1:0>                                  | Waveform outputs                              | Digital        |  |  |  |  |  |  |

| Timer Counter (1                         | rccx)                                         |                |  |  |  |  |  |  |

| WO<7:0>                                  | Waveform outputs                              | Digital        |  |  |  |  |  |  |

| General Purpose                          | e I/O (PORT)                                  |                |  |  |  |  |  |  |

| PA01-PA00                                | Parallel I/O controller I/O Port A            | Digital        |  |  |  |  |  |  |

| PA09-PA04                                | Parallel I/O controller I/O Port A            | Digital        |  |  |  |  |  |  |

| PA25-PA22                                | Parallel I/O controller I/O Port A            | Digital        |  |  |  |  |  |  |

| PA28-PA27                                | Parallel I/O controller I/O Port A            | Digital        |  |  |  |  |  |  |

| PA03-PB02                                | Parallel I/O controller I/O Port B            | Digital        |  |  |  |  |  |  |

| PA23-PB22                                | Parallel I/O controller I/O Port B            | Digital        |  |  |  |  |  |  |

| Universal Serial                         | Bus (USB)                                     |                |  |  |  |  |  |  |

| DP                                       | DP for USB (SAM R34 only)                     | Digital        |  |  |  |  |  |  |

| DM                                       | DM for USB (SAM R34 only)                     | Digital        |  |  |  |  |  |  |

| External RF Sigr                         | nals                                          |                |  |  |  |  |  |  |

| RF_XTB                                   | XTAL connection                               | OSC            |  |  |  |  |  |  |

| RF_XTA                                   | XTAL connection or TCXO input                 | OSC            |  |  |  |  |  |  |

| VR_DIG                                   | Regulated supply voltage for digital blocks   | Reg Output     |  |  |  |  |  |  |

| VBAT_ANA                                 | Supply voltage for analog circuitry           | Analog Power   |  |  |  |  |  |  |

| VR_ANA                                   | Regulated supply voltage for analog circuitry | Reg Output     |  |  |  |  |  |  |

# SAM R34/R35

# Signal Description

| continued                     |                                                    |               |  |  |  |  |  |

|-------------------------------|----------------------------------------------------|---------------|--|--|--|--|--|

| Signal Name                   | Function                                           | Туре          |  |  |  |  |  |

| RFI_LF                        | RF input for bands 2 and 3                         | RF Input      |  |  |  |  |  |

| RFO_LF                        | RF output for bands 2 and 3                        | RF Output     |  |  |  |  |  |

| PA_BOOST                      | Optional high-power PA output, all frequency bands | RF Output     |  |  |  |  |  |

| VR_PA                         | Regulated supply voltage for the PA                | Reg Output    |  |  |  |  |  |

| VBAT_RF                       | Supply voltage for RF blocks                       | RF Power      |  |  |  |  |  |

| RFO_HF                        | RF output for band 1                               | RF Output     |  |  |  |  |  |

| VBAT_DIG                      | Supply voltage for digital blocks                  | Digital Power |  |  |  |  |  |

| RXTX                          | RX/TX switch control: High in TX                   | Digital I/O   |  |  |  |  |  |

| RFI_HF                        | RF input for band 1                                | RF Input      |  |  |  |  |  |

| Internal Interconnect Signals |                                                    |               |  |  |  |  |  |

| DIO0                          | Digital I/O, software configured                   | I/O           |  |  |  |  |  |

| DIO1/DCLK                     | Digital I/O, software configured                   | I/O           |  |  |  |  |  |

| DIO2/DATA                     | Digital I/O, software configured                   | I/O           |  |  |  |  |  |

| DIO3                          | Digital I/O, software configured                   | I/O           |  |  |  |  |  |

| DIO4                          | Digital I/O, software configured                   | I/O           |  |  |  |  |  |

| DIO5                          | Digital I/O, software configured                   | I/O           |  |  |  |  |  |

| SCLK                          | SPI clock input                                    | Input         |  |  |  |  |  |

| MISO                          | SPI data output                                    | Output        |  |  |  |  |  |

| MOSI                          | SPI data input                                     | Input         |  |  |  |  |  |

| SEL                           | SPI chip select input                              | Input         |  |  |  |  |  |

| RF_RST                        | Reset trigger input                                | I/O           |  |  |  |  |  |

## 7. Processor and Architecture

### 7.1 Cortex M0+ Processor

The SAM R34/R35 contains an ATSAML21J18B ARM Cortex-M0+ processor, based on the ARMv6 Architecture and Thumb<sup>®</sup>-2 ISA. The Cortex-M0+ is 100% instruction set compatible with its predecessor, the Cortex-M0 core, and upward compatible to Cortex-M3 and M4 cores. The implemented ARM Cortex-M0+ is revision r0p1. For more information refer to http://www.arm.com.

#### 7.1.1 Cortex M0+ Configuration

| Features                         | Cortex M0+ options           | SAM R34/R35 configuration                            |

|----------------------------------|------------------------------|------------------------------------------------------|

| Interrupts                       | External interrupts 0-32     | 29                                                   |

| Data endianness                  | Little-endian or big-endian  | Little-endian                                        |

| SysTick timer                    | Present or absent            | Present                                              |

| Number of watchpoint comparators | 0, 1, 2                      | 2                                                    |

| Number of breakpoint comparators | 0, 1, 2, 3, 4                | 4                                                    |

| Halting debug support            | Present or absent            | Present                                              |

| Multiplier                       | Fast or small                | Fast (single cycle)                                  |

| Single-cycle I/O port            | Present or absent            | Present                                              |

| Wake-up interrupt controller     | Supported or not supported   | Not supported                                        |

| Vector Table Offset Register     | Present or absent            | Present                                              |

| Unprivileged/Privileged support  | Present or absent            | Absent - All software run in<br>privileged mode only |

| Memory Protection Unit           | Not present or 8-region      | Not present                                          |

| Reset all registers              | Present or absent            | Absent                                               |

| Instruction fetch width          | 16-bit only or mostly 32-bit | 32-bit                                               |

#### Table 7-1. Cortex M0+ Configuration in SAM R34/R35

The ARM Cortex-M0+ core has two bus interfaces:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides connections to peripherals and all system memory including Flash memory and RAM

- Single 32-bit I/O port bus interfacing to the PORT with 1-cycle loads and stores

#### 7.1.1.1 Cortex M0+ Peripherals

- System Control Space (SCS)

- The processor provides debug through registers in the SCS. Refer to the Cortex-M0+ Technical Reference Manual for details (http://www.arm.com)

- Nested Vectored Interrupt Controller (NVIC)

External interrupt signals connect to the NVIC, and the NVIC prioritizes the interrupts. Software can set the priority of each interrupt. The NVIC and the Cortex-M0+ processor core are closely coupled, providing low latency interrupt processing and efficient processing of late arriving interrupts. Refer to the Cortex-M0+ Technical Reference Manual for details (http:// www.arm.com).

**Note:** When the CPU frequency is much higher than the APB frequency it is recommended to insert a memory read barrier after each CPU write to registers mapped on the APB. Failing to do so in such conditions may lead to unexpected behavior such as re-entering a peripheral interrupt handler just after leaving it.

- System Timer (SysTick)

- The System Timer is a 24-bit timer clocked by CLK\_CPU that extends the functionality of both the processor and the NVIC. Refer to the Cortex-M0+ Technical Reference Manual for details (http://www.arm.com).

- System Control Block (SCB)

- The System Control Block provides system implementation information, and system control. This includes configuration, control, and reporting of the system exceptions. Refer to the Cortex-M0+ Devices Generic User Guide for details (http://www.arm.com)

- Micro Trace Buffer (MTB)

- The CoreSight MTB-M0+ (MTB) provides a simple execution trace capability to the Cortex-M0+ processor. Refer to section MTB-Micro Trace Buffer and the CoreSight MTB-M0+ Technical Reference Manual for details (http://www.arm.com).

#### **Related Links**

7.2 Nested Vector Interrupt Controller

#### 7.1.1.2 Cortex M0+ Address Map

#### Table 7-2. Cortex-M0+ Address Map

| Address    | Peripheral                                  |

|------------|---------------------------------------------|

| 0xE000E000 | System Control Space (SCS)                  |

| 0xE000E010 | System Timer (SysTick)                      |

| 0xE000E100 | Nested Vectored Interrupt Controller (NVIC) |

| 0xE000ED00 | System Control Block (SCB)                  |

| 0x41006000 | Micro Trace Buffer (MTB)                    |

#### 7.1.1.3 I/O Interface

The device allows direct access to PORT registers. Accesses to the AMBA<sup>®</sup> AHB-Lite<sup>™</sup> and the single cycle I/O interface can be made concurrently, so the Cortex M0+ processor can fetch the next instructions while accessing the I/Os. This enables single cycle I/O access to be sustained for as long as necessary.

### 7.2 Nested Vector Interrupt Controller

#### 7.2.1 Overview

The Nested Vectored Interrupt Controller (NVIC) in the SAM R34/R35 supports 32 interrupt lines with four different priority levels. For more details, refer to the Cortex-M0+ Technical Reference Manual (http://www.arm.com).

#### 7.2.2 Interrupt Line Mapping

Each of the 23 interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can have one or more interrupt flags, located in the peripheral's Interrupt Flag Status and Clear (INTFLAG) register.

An interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by writing a 1 to the corresponding bit in the peripheral's Interrupt Enable Set (INTENSET) register, and disabled by writing 1 to the corresponding bit in the peripheral's Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated from the peripheral when the interrupt flag is set and the corresponding interrupt is enabled.

The interrupt requests for one peripheral are ORed together on system level, generating one interrupt request for each peripheral. An interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt pending registers (SETPEND/CLRPEND bits in ISPR/ICPR).

For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt enable register (SETENA/ CLRENA bits in ISER/ICER). The NVIC interrupt priority registers IPR0-IPR7 provide a priority field for each interrupt.

| Peripheral Source                          | NVIC Line |

|--------------------------------------------|-----------|

| EIC NMI – External Interrupt Controller    | NMI       |

| PM – Power Manager                         | 0         |

| MCLK - Main Clock                          |           |

| OSCCTRL - Oscillators Controller           |           |

| OSC32KCTRL - 32KHz Oscillators Controller  |           |

| SUPC - Supply Controller                   |           |

| PAC - Protecion Access Controller          |           |

| WDT – Watchdog Timer                       | 1         |

| RTC – Real Time Counter                    | 2         |

| EIC – External Interrupt Controller        | 3         |

| NVMCTRL – Non-Volatile Memory Controller   | 4         |

| DMAC - Direct Memory Access Controller     | 5         |

| USB - Universal Serial Bus                 | 6         |

| EVSYS – Event System                       | 7         |

| SERCOM0 – Serial Communication Interface 0 | 8         |

| SERCOM1 – Serial Communication Interface 1 | 9         |

| SERCOM2 – Serial Communication Interface 2 | 10        |

| SERCOM3 – Serial Communication Interface 3 | 11        |

| SERCOM4 – Serial Communication Interface 4 | 12        |

#### Table 7-3. Interrupt Line Mapping

| continued                                  |           |

|--------------------------------------------|-----------|

| Peripheral Source                          | NVIC Line |

| SERCOM5 – Serial Communication Interface 5 | 13        |

| TCC0 – Timer Counter for Control 0         | 14        |

| TCC1 – Timer Counter for Control 1         | 15        |

| TCC2 – Timer Counter for Control 2         | 16        |

| TC0 – Timer Counter 0                      | 17        |

| TC1 – Timer Counter 1                      | 18        |

| TC4 – Timer Counter 4                      | 19        |

| ADC – Analog-to-Digital Converter          | 20        |

| AC – Analog Comparator                     | 21        |

### 7.3 Micro Trace Buffer

#### 7.3.1 Features

- Program flow tracing for the Cortex-M0+ processor

- MTB SRAM can be used for both trace and general purpose storage by the processor

- The position and size of the trace buffer in SRAM is configurable by software

- CoreSight compliant

#### 7.3.2 Overview

When enabled, the MTB records the changes in program flow that are reported by the Cortex-M0+ processor over the execution trace interface. This interface is shared between the Cortex-M0+ processor and the CoreSight MTB-M0+. The information is stored by the MTB in the SRAM as trace packets. An off-chip debugger can extract the trace information using the Debug Access Port to read the trace information from the SRAM. The debugger can then reconstruct the program flow from this information.

The MTB stores trace information into the SRAM and gives the processor access to the SRAM simultaneously. The MTB ensures that trace write accesses have priority over processor accesses.