# **ECE1088**

## **GPIO Expansion via SMBus or BC-Link Bus**

### Highlights

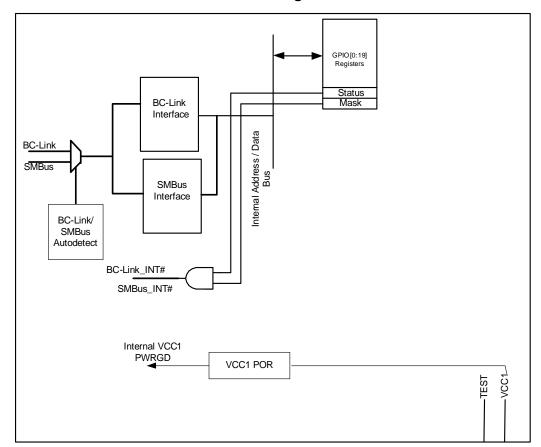

The ECE1088 is a 28-Pin 3.3V GPIO Expansion device. The device is connected to a Master via the BC-Link interface or via the SMBus.

### Features

- 20 Multiplexed General Purpose I/O pins

All are MCU addressable I/O Pins

- BC-Link Interconnect Bus

- Link to embedded controller

- SMBus Interconnect

- One of two address selection

- 3.3V Operation

- 28-Pin, QFN RoHS Compliant package

- 0.5mm Pitch

- 5x5mm Body size

#### **Block Diagram**

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

- To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Table of Contents**

| 1.0 Pin Functions                       | 4  |

|-----------------------------------------|----|

| 2.0 Product Description                 | 10 |

| 3.0 Operational Description             | 22 |

| 4.0 Timing Diagrams                     |    |

| 5.0 Package Outline                     |    |

| Appendix A: Data sheet Revision History | 27 |

| The Microchip Web Site                  |    |

| Customer Change Notification Service    | 28 |

| Customer Support                        | 28 |

| Product Identification System           | 29 |

|                                         |    |

## 1.0 PIN FUNCTIONS

## TABLE 1-1: ECE1088 PIN TABLE

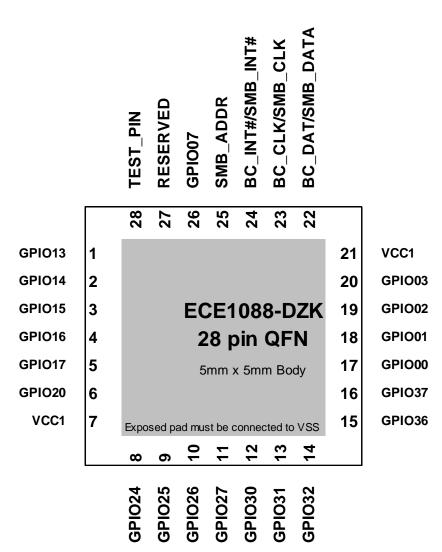

| Pin # | Name   | Pin # | Name             |

|-------|--------|-------|------------------|

| 1     | GPIO13 | 15    | GPIO36           |

| 2     | GPIO14 | 16    | GPIO37           |

| 3     | GPIO15 | 17    | GPIO00           |

| 4     | GPIO16 | 18    | GPIO01           |

| 5     | GPIO17 | 19    | GPIO02           |

| 6     | GPIO20 | 20    | GPIO03           |

| 7     | VCC1   | 21    | VCC1             |

| 8     | GPIO24 | 22    | BC_DAT/SMB_DATA  |

| 9     | GPIO25 | 23    | BC_CLK/SMB_CLK   |

| 10    | GPIO26 | 24    | BC_INT#/SMB_INT# |

| 11    | GPIO27 | 25    | SMB_ADDR         |

| 12    | GPIO30 | 26    | GPIO07           |

| 13    | GPIO31 | 27    | RESERVED         |

| 14    | GPIO32 | 28    | TEST_PIN         |

FIGURE 1-1: ECE1088 PIN DIAGRAM (TOP VIEW, EXPOSED PAD IS ON THE BOTTOM)

## TABLE 1-2: ECE1088 PIN DESCRIPTIONS

| Pin # | Name   | Description         | Buffer | Notes |

|-------|--------|---------------------|--------|-------|

| 1     | GPIO13 | General Purpose IO. | ISP/O8 | 3     |

| 2     | GPIO14 | General Purpose IO. | ISP/O8 | 3     |

| 3     | GPIO15 | General Purpose IO. | ISP/O8 | 3     |

| 4     | GPIO16 | General Purpose IO. | ISP/O8 | 3     |

| 5     | GPIO17 | General Purpose IO. | ISP/O8 | 3     |

| 6     | GPIO20 | General Purpose IO. | IP/O8  | 3     |

| 7     | VCC1   | PWR                 | PWR    |       |

| 8     | GPIO24 | General Purpose IO. | IP/O8  | 3     |

| 9     | GPIO25 | General Purpose IO. | IP/08  | 3     |

| 10    | GPIO26 | General Purpose IO. | IP/O8  | 3     |

| 11    | GPIO27 | General Purpose IO. | IP/O8  | 3     |

| 12    | GPIO30 | General Purpose IO. | IP/O8  | 3     |

| 13    | GPIO31 | General Purpose IO. | IP/O8  | 3     |

| 14    | GPIO32 | General Purpose IO. | IP/08  | 3     |

| 15    | GPIO36 | General Purpose IO. | IP/O8  | 3     |

| 16    | GPIO37 | General Purpose IO. | IP/08  | 3     |

| 17    | GPIO00 | General Purpose IO. | IP/O8  | 3     |

| 18    | GPIO01 | General Purpose IO. | IP/O8  | 3     |

| 19    | GPIO02 | General Purpose IO. | IP/O8  | 3     |

| Pin # | Name             | Description                                                                     | Buffer | Notes |

|-------|------------------|---------------------------------------------------------------------------------|--------|-------|

| 20    | GPIO03           | General Purpose IO.                                                             | IP/O8  | 3     |

| 21    | VCC1             | PWR                                                                             | PWR    |       |

| 22    | BC_DAT/SMB_DATA  | BC_DAT IO. SMBus Data IO                                                        | I/O8   |       |

| 23    | BC_CLK/SMB_CLK   | BC_CLK. SMBus Slave Clock I                                                     | I      |       |

| 24    | BC_INT#/SMB_INT# | BCINT#t Output Active Low . SMBus Interrupt<br>Output Active Low                | O8     | 4     |

| 25    | SMB_ADDR         | SMBus Address Select Strap. Selects between one<br>of two SMBus Slave Addresses | Ι      |       |

| 26    | GPIO07           | General Purpose IO.                                                             | IP/O8  | 3     |

| 27    | RESERVED         | Reserved                                                                        | NC     | 2     |

| 28    | TEST_PIN         | Test Pin Input                                                                  | I      | 1     |

|       |                  | Exposed pad must be connected to VSS                                            |        |       |

Note 1: This pin requires an external pull-down resister to ensure that the pin remains de-asserted.

- 2: NC Not Connected.

- 3: Full Function GPIO Refer to Table 2-4, "GPIO Configuration Register".

- 4: SMB\_INT# is Open Drain / BC\_INT# is Push-pull. SMBus is default.

## TABLE 1-3: ALTERNATE PIN FUNCTIONS

| Pin # | Primary  | Alternate |

|-------|----------|-----------|

| 1     | GPIO13   |           |

| 2     | GPIO14   |           |

| 3     | GPIO15   |           |

| 4     | GPIO16   |           |

| 5     | GPIO17   |           |

| 6     | GPIO20   |           |

| 7     | VCC1     |           |

| 8     | GPIO24   |           |

| 9     | GPIO25   |           |

| 10    | GPIO26   |           |

| 11    | GPIO27   |           |

| 12    | GPIO30   |           |

| 13    | GPIO31   |           |

| 14    | GPIO32   |           |

| 15    | GPIO36   |           |

| 16    | GPIO37   |           |

| 17    | GPIO00   |           |

| 18    | GPIO01   |           |

| 19    | GPIO02   |           |

| 20    | GPIO03   |           |

| 21    | VCC1     |           |

| 22    | BC_DAT   | SMB_DATA  |

| 23    | BC_CLK   | SMB_CLK   |

| 24    | BC_INT#  | SMB_INT#  |

| 25    | SMB_ADDR |           |

| 26    | GPIO07   |           |

| 27    | RESERVED |           |

| 28    | TEST_PIN |           |

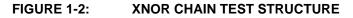

## 1.1 XNOR Chain Test Mode

An XNOR Chain test structure is in to the ECE1088 to allow users to confirm that all pins are in contact with the motherboard during assembly and test operations (Figure 1-2, "XNOR Chain Test Structure").

The XNOR Chain test structure must be activated to perform these tests. When the XNOR Chain is activated, the ECE1088 pin functions are disconnected from the device pins, which all become input pins except for one output pin at the end of XNOR Chain.

The tests that are performed when the XNOR Chain test structure is activated require the board-level test hardware to control the device pins and observe the results at the XNOR Chain output pin.

#### 1.2 Pins in XNOR Chain Structure

All pins are inputs into the XNOR Chain with the exception of the following pins:

- TEST\_PIN (this is the XNOR Chain enable input)

- RESERVED

- SMB\_ADDR

- BC\_INT#/SMB\_INT#

## 1.3 Entering and Exiting the XNOR Chain

The XNOR Chain test is entered by setting TEST\_PIN to 1 while SMB\_ADDR is 0.

When activated, the test mode allows one single input pin, when switched, to toggle the BC\_INT#/SMB\_INT# output. The XNOR Chain is exited by setting TEST\_PIN to 0, independent of the value of SMB\_ADDR.

## 2.0 PRODUCT DESCRIPTION

## 2.1 Summary

The ECE1088 is a 28-pin 3.3V GPIO Expansion device. The device is connected to a Master via the BC-Link interface or via the SMBus.

## 2.2 Interrupt Generation

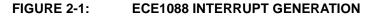

Interrupts can be generated by an edge detection on a GPIO pin or an edge detection on one of the bus interface pins. The bus interrupt pin (BC\_INT# or SMBUS\_INT#) is asserted if any bit in one of the Interrupt Status registers is 1 and the corresponding Interrupt Mask bit is also 1. Interrupt generation is illustrated in Figure 2-1, "ECE1088 Interrupt Generation".

In order for software to determine which device is the source of an interrupt, it should first read the Group Interrupt Status Register to determine which Status register group is a source for the interrupt. Software should read both the Status register and the associated Mask register, then AND the two values together. Bits that are 1 in the result of the AND are active interrupts.

Software clears an interrupt by writing a 1 to the corresponding bit in the Status register.

**Note:** Although the ECE1088 can generate the SMBus interrupt signal SMBUS\_INT# as described above, it will not respond to the SMBus Alert Response Address transaction unless Bit4 ARA in the Clock Control Register (Register FAh) is set to 1.

#### 2.3 Integrated VCC1 Reset Generator

When VCC1 power is applied to the ECE1088, a VCC1 POR will be generated. This VCC1 POR will reset the device.

#### 2.4 Register Address Table

| TABLE 2-1: | REGISTER SUMMARY |

|------------|------------------|

|------------|------------------|

| Address (HEX) | Register                 | VCC1 POR Default |  |  |

|---------------|--------------------------|------------------|--|--|

| 00h           | GPIO[7, 3:0] Input       | 00h              |  |  |

| 01h           | GPIO[17:13] Input        | 00h              |  |  |

| 02h           | GPIO[27,24:20] Input     | 00h              |  |  |

| 03h           | GPIO[37:36,32:30] Input  | 00h              |  |  |

| 04h           | Reserved                 | 00h              |  |  |

| 05h           | GPIO[7,3:0] Output       | 00h              |  |  |

| 06h           | GPIO[17:10] Output       | 00h              |  |  |

| 07h           | GPIO[27:24,20] Output    | 00h              |  |  |

| 08h           | GPIO[37:36,32:30] Output | 00h              |  |  |

| 09h           | Reserved                 | 00h              |  |  |

| 0Ah           | GPIO00 Configuration     | 00h              |  |  |

| 0Bh           | GPIO01 Configuration     | 00h              |  |  |

| 0Ch           | GPIO02 Configuration     | 00h              |  |  |

| 0Dh           | GPIO03 Configuration     | 00h              |  |  |

| 0E-10h        | Reserved                 | 00h              |  |  |

| 11h           | GPIO07 Configuration     | 00h              |  |  |

| 12-14h        | Reserved                 | 00h              |  |  |

| 15h           | GPIO13 Configuration     | 00h              |  |  |

| 16h           | GPIO14 Configuration     | 00h              |  |  |

| 17h           | GPIO15 Configuration     | 00h              |  |  |

| 18h           | GPIO16 Configuration     | 00h              |  |  |

| 19h           | GPIO17 Configuration     | 00h              |  |  |

| 1Ah           | GPIO20 Configuration     | 00h              |  |  |

| 1B-1Dh        | Reserved                 | 00h              |  |  |

| 1Eh           | GPIO24 Configuration     | 00h              |  |  |

| 1Fh           | GPIO25 Configuration     | 00h              |  |  |

| 20h           | GPIO26 Configuration 00  |                  |  |  |

| 21h           | GPIO27 Configuration     | 00h              |  |  |

| 22h           | GPIO30 Configuration     | 00h              |  |  |

| 23h           | GPIO31 Configuration     | 00h              |  |  |

| Address (HEX) | Register                          | VCC1 POR Default |

|---------------|-----------------------------------|------------------|

| 24h           | GPIO32 Configuration              | 00h              |

| 25-27h        | Reserved                          | 00h              |

| 28h           | GPIO36 Configuration              | 00h              |

| 29h           | GPIO37 Configuration              | 00h              |

| 2A-31h        | Reserved                          | 00h              |

| 32h           | GPIO[7,3:0] Interrupt Status      | 00h              |

| 33h           | GPIO[17:13] Interrupt Status      | 00h              |

| 34h           | GPIO[27:24.20] Interrupt Status   | 00h              |

| 35h           | GPIO[37:36,32:30]Interrupt Status | 00h              |

| 36h           | Reserved                          | 00h              |

| 37h           | GPIO[7,3:0] Interrupt Mask        | 00h              |

| 38h           | GPIO[17:13] Interrupt Mask        | 00h              |

| 39h           | GPIO[27:24,20] Interrupt Mask     | 00h              |

| 3Ah           | GPIO[37:36,32:30] Interrupt Mask  | 00h              |

| 3B-F4h        | Reserved                          | 00h              |

| F5h           | Reset                             | 00h              |

| F6h           | MCHP test                         | 00h              |

| F7h-F8h       | Reserved                          | 00h              |

| F9h           | Group Interrupt                   | 00h              |

| FAh           | Clock Control                     | 00h              |

| FBh           | Wakeup Control                    | 00h              |

| FCH           | Device ID                         | 40h              |

| FDh           | Device Version Number             | Current version  |

| FEh           | Vendor ID (LSB)                   | 55h              |

| FFh           | Vendor ID (MSB)                   | 10h              |

#### TABLE 2-1: REGISTER SUMMARY (CONTINUED)

## 2.5 Detailed Register Descriptions

2.5.1 GPIO REGISTERS

#### 2.5.2 GPIO INPUT REGISTER

#### TABLE 2-2:GPIO INPUT REGISTER

| ADDRESS      | REFER TO Table 2-1, "Register Summary" |        |        | 8-bit SIZE |        |        |                     |        |

|--------------|----------------------------------------|--------|--------|------------|--------|--------|---------------------|--------|

| POWER        | VCC1                                   |        |        |            |        | N/A    | VCC1 POF<br>DEFAULT | R      |

|              |                                        |        |        |            |        |        |                     |        |

| BIT          | D7                                     | D6     | D5     | D4         | D3     | D2     | D1                  | D0     |

| BC-LINK TYPE | R                                      | R      | R      | R          | R      | R      | R                   | R      |

| BIT NAME     | GPIOx7                                 | GPIOx6 | GPIOx5 | GPIOx4     | GPIOx3 | GPIOx2 | GPIOx1              | GPIOx0 |

## ECE1088

#### 2.5.3 GPIO OUTPUT REGISTER

#### TABLE 2-3: GPIO OUTPUT REGISTER

| ADDRESS      | REFER TO Table 2-1, "Register Summary" |        |        | 8-bit  |        |        | SIZE                |        |

|--------------|----------------------------------------|--------|--------|--------|--------|--------|---------------------|--------|

| POWER        | VCC1                                   |        |        |        |        | 00h    | VCC1 POF<br>DEFAULT | R      |

|              |                                        |        |        |        |        |        |                     |        |

| BIT          | D7                                     | D6     | D5     | D4     | D3     | D2     | D1                  | D0     |

| BC-LINK TYPE | R/W                                    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W                 | R/W    |

| BIT NAME     | GPIOx7                                 | GPIOx6 | GPIOx5 | GPIOx4 | GPIOx3 | GPIOx2 | GPIOx1              | GPIOx0 |

#### 2.5.4 GPIO CONFIGURATION REGISTER

#### TABLE 2-4:GPIO CONFIGURATION REGISTER

| ADDRESS      | REFER TO<br>Summary" | Table 2-1, | "Register | 8-bit SIZE |     |     |                     |     |

|--------------|----------------------|------------|-----------|------------|-----|-----|---------------------|-----|

| POWER        | VCC1                 |            |           |            |     | 00h | VCC1 POR<br>DEFAULT |     |

|              |                      |            |           |            |     |     |                     |     |

| BIT          | D7                   | D6         | D5        | D4         | D3  | D2  | D1                  | D0  |

| BC-LINK TYPE | R                    | R/W        | R/W       | R/W        | R/W | R/W | R                   | R/W |

| BIT NAME     | RES ALT DIR          |            |           | TY         | PE  | POL | RES                 | PU  |

#### 2.5.4.1 ALT

ALT Function select bit should always be set as 0.

#### 2.5.4.2 DIR, TYPE

The level/edge and output type are controlled by these fields. The effects are defined in Table 2-5, "Direction, Level/Edge, Output Type Bit Definition".

#### TABLE 2-5: DIRECTION, LEVEL/EDGE, OUTPUT TYPE BIT DEFINITION

| Direction<br>Bit 5 | Type<br>Bit 4 | Type<br>Bit 3 | Selected Function             |

|--------------------|---------------|---------------|-------------------------------|

| 0                  | 0             | 0             | Input, Level Sensitive Low    |

| 0                  | 0             | 1             | Input, Rising Edge Triggered  |

| 0                  | 1             | 0             | Input, Falling Edge Triggered |

| 0                  | 1             | 1             | Input, Both Edge Triggered    |

| 1                  | 0             | х             | Output, Push-Pull             |

| 1                  | 1             | х             | Output, Open Drain            |

In order to enable oscillator wakeup from Low Power Mode for any GPIO pin, the GPIO Configuration Register for that GPIO must be configured for Input in Bit 5). See Section 2.6.2, "Clock Control".

#### 2.5.4.3 POL

When the **POL** bit is set to '1" the signal output is inverted when routed to its pin and the interrupt level sense is inverted when a level-sensitive interrupt is selected by the **DIR**, **TYPE** fields. The state of the pin is always reported without inversion in the GPIO Input Register.

### 2.5.4.4 PU

When this bit is 1, an internal pull-up resistor is connected to the pin. When this bit is 0, the pullup is disabled.

#### 2.5.5 GPIO INTERRUPT STATUS REGISTER

#### TABLE 2-6: GPIO INTERRUPT STATUS REGISTER

| ADDRESS      | REFER TO<br>Summary" | Table 2-1, | "Register | 8-bit  |        |        | SIZE                |        |

|--------------|----------------------|------------|-----------|--------|--------|--------|---------------------|--------|

| POWER        | VCC1                 |            |           | 00h    |        |        | VCC1 POR<br>DEFAULT |        |

|              |                      |            |           |        |        |        |                     |        |

| BIT          | D7                   | D6         | D5        | D4     | D3     | D2     | D1                  | D0     |

| BC-LINK TYPE | R/WC                 | R/WC       | R/WC      | R/WC   | R/WC   | R/WC   | R/WC                | R/WC   |

| BIT NAME     | GPIOX7               | GPIOX6     | GPIOX5    | GPIOX4 | GPIOX3 | GPIOX2 | GPIOX1              | GPIOX0 |

A bit in a GPIOX Interrupt Status Register is set to 1 when the DIRECTION field for that bit in the corresponding GPIOX n Configuration Register is set for Input and the bit in the corresponding GPIOX Input Register matches the conditions defined by the TYPE field in the GPIOX Configuration Register. For example, if the TYPE field for GPIO Xn is set for Level Sensitive Low, then bit n in the GPIOX Interrupt Status Register is set to 1 when bit n in the GPIOX Input Register is 0. If the TYPE field specifies edge triggering, then the Status Register bit is set when the Input Register bit transitions with the specified edge.

Writing a bit in a GPIOX Interrupt Status Register clears that bit. Writing a bit with a 0 has no effect.

#### 2.5.6 GPIO INTERRUPT MASK REGISTER

#### TABLE 2-7:GPIO INTERRUPT MASK REGISTER

| ADDRESS      | REFER TO<br>Summary"        | Table 2-1,                  | "Register                   | 8-bit                       |                             |                             | SIZE                        |                             |

|--------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| POWER        | VCC1                        |                             |                             | 00h VCC1 POR<br>DEFAULT     |                             |                             | 2                           |                             |

|              |                             |                             |                             |                             |                             |                             |                             |                             |

| BIT          | D7                          | D6                          | D5                          | D4                          | D3                          | D2                          | D1                          | D0                          |

| BC-LINK TYPE | R/W                         |

| BIT NAME     | GPIOX7<br>0 No Int<br>1 Int | GPIOX6<br>0 No Int<br>1 Int | GPIOX5<br>0 No Int<br>1 Int | GPIOX4<br>0 No Int<br>1 Int | GPIOX3<br>0 No Int<br>1 Int | GPIOX2<br>0 No Int<br>1 Int | GPIOX1<br>0 No Int<br>1 Int | GPIOX0<br>0 No Int<br>1 Int |

An interrupt is signaled on either BC\_INT# or SMBus\_INT# when a GPIOX bit in a GPIO Interrupt Status Register is 1 and the corresponding GPIOX bit in the GPIO Interrupt Mask Register is also 1.

# ECE1088

#### 2.6 Other Control Registers

#### 2.6.1 GROUP INTERRUPT STATUS

#### TABLE 2-8: GROUP INTERRUPT STATUS REGISTER

| ADDRESS      | F9h      |          |          | 8-bit SIZE              |      |      |      |      |

|--------------|----------|----------|----------|-------------------------|------|------|------|------|

| POWER        | VCC1     |          |          | 00h VCC1 POR<br>DEFAULT |      |      |      | 2    |

|              |          |          |          |                         |      |      |      |      |

| BIT          | D7       | D6       | D5       | D4                      | D3   | D2   | D1   | D0   |

| BC-LINK TYPE | R        | R        | R        | R                       | R    | R    | R    | R    |

| BIT NAME     | Reserved | Reserved | Reserved | Reserved                | Grp3 | Grp2 | Grp1 | Grp0 |

### 2.6.1.1 Bit3 Grp3

0 No interrupts in GPIO Group 3

1 Interrupt in at least one of GPIO37-GPIO30

#### 2.6.1.2 Bit2 Grp2

0 No interrupts in GPIO Group21 Interrupt in at least one of GPIO27-GPIO20

#### 2.6.1.3 Bit1 Grp1

0 No interrupts in GPIO Group1

1 Interrupt in at least one of GPIO17-GPIO10

#### 2.6.1.4 Bit0 Grp0

0 No interrupts in GPIO Group0

1 Interrupt in at least one of GPIO07-GPIO00

#### 2.6.2 CLOCK CONTROL

#### TABLE 2-9:CLOCK CONTROL REGISTER

| ADDRESS      | FAh      |    |    | 8-bit SIZE              |          |                |           |           |

|--------------|----------|----|----|-------------------------|----------|----------------|-----------|-----------|

| POWER        | VCC1     |    |    | 00h VCC1 POR<br>DEFAULT |          |                |           | ł         |

|              |          |    |    |                         |          |                |           |           |

| BIT          | D7       | D6 | D5 | D4                      | D3       | D2             | D1        | D0        |

| BC-LINK TYPE | R        | R  | R  | R/W                     | R/W      | R/W            | R/W       | R/W       |

| BIT NAME     | Reserved |    |    | ARA                     | Reserved | OSC<br>Control | Interface | Selection |

#### 2.6.2.1 Bit4 ARA

If this bit is 1b and the SMBus interface is enabled (either by setting the Interface Selection field to 11b or by setting the Interface Selection field to 0xb and an SMBus transaction is detected), the ECE1088 will respond to an SMBus Alert Response Address Read Byte command as defined in the SMBus specification. If this bit is 0b, the ECE1088 will ignore the Alert Response Address at all times.

APPLICATION NOTE: Software must insure that the field Interface Selection in this register is '11b' (SMBus Interface enabled) before setting ARA to '1b'.

#### 2.6.2.2 Bit2 OSC Control

**Ob Oscillator Enabled (Default)**

1b Oscillator Low Power Enable.

The Oscillator may be stopped and once stopped may be restarted by activity on either the bus interface pins or on inputs that are enabled for interrupts. See Section 2.6.3, "Wakeup Control" for conditions that restart the Oscillator

When OSC Control is set to Low Power Enable (1b) the Oscillator will stop only when the SMBus or BC-Link are idle. This means:

No Interrupts are pending

No traffic is on the bus

Transactions on the bus have completed

APPLICATION NOTE: When OSC Control is set to '1b', the ring oscillator will be shut down after every BC-Link or SMBus transaction completes and no interrupts are pending. The oscillator will restart when a wakeup enabled by the Wakeup Control registers occurs. The Wakeup Control register must be configured properly before setting OSC Control to '1b'.

2.6.2.3 Bit[1:0] Interface Selection

0Xb Autodetect Mode (default)

10b BC-Link interface enabled.

11b SMBus interface enabled

**APPLICATION NOTE:** The first access to the ECE1088 must be a write to the Clock Control register to configure the Interface Selection field to the desired interface type (10b or 11b). This is required so that Oscillator control works properly and so that the bus type does not inadvertently switch during use.

#### 2.6.3 WAKEUP CONTROL

The Wakeup Control Register determines which events restart the Oscillator when the Oscillator is in Low Power Mode.

| ADDRESS         | FBh      |          |          |          |          | 8-bit | SIZE                  |         |  |

|-----------------|----------|----------|----------|----------|----------|-------|-----------------------|---------|--|

| POWER           | VCC1     |          |          |          |          | 00h   | h VCC1 POR<br>DEFAULT |         |  |

|                 |          |          |          |          |          |       |                       |         |  |

| BIT             | D7       | D6       | D5       | D4       | D3       | D2    | D1                    | D0      |  |

| BC-LINK<br>TYPE | R R R    |          | R        | R        | R/W      | R/W   | R/W                   |         |  |

| BIT NAME        | Reserved | Reserved | Reserved | Reserved | Reserved | GPIO  | BUS_DAT               | BUS_CLK |  |

#### TABLE 2-10: WAKEUP CONTROL REGISTER

#### 2.6.3.1 Bit2 GPIO

0 GPIO Interrupts do not affect the Oscillator

1 A GPIO interrupt that is requested on any GPIO pin for which GPIO function is selected and a GPIO interrupt is enabled will restart the Oscillator when the Oscillator is stopped in Low Power mode.

In order for edge detection to work on any GPIO pin the pin must be selected for input and the desired edges configured, as described in Table 2-5, "Direction, Level/Edge, Output Type Bit Definition", in the GPIO configuration register.

# ECE1088

#### 2.6.3.2 Bit1 BUS\_DAT

0 The BUS\_DAT signal (BC\_DAT or SMB\_DAT) does not affect the Oscillator

1 Either a rising edge or a falling edge on the BUS\_DAT signal will restart the Oscillator when the Oscillator is stopped in Low Power mode.

#### 2.6.3.3 Bit0 BUS\_CLK

0 The BUS\_Clk signal (BC\_CLK or SMB\_CLK) does not affect the Oscillator

1 Either a rising edge or a falling edge on the BUS\_Clk signal will restart the Oscillator when the Oscillator is stopped in Low Power mode.

#### 2.6.4 DEVICE ID REGISTER

### TABLE 2-11: DEVICE ID REGISTER

| ADDRESS      | FCH  |    |    |                         |    | 8-bit | SIZE |    |

|--------------|------|----|----|-------------------------|----|-------|------|----|

| POWER        | VCC1 |    |    | 40h VCC1 POR<br>DEFAULT |    |       |      | ł  |

|              |      |    |    | •                       |    |       |      |    |

| BIT          | D7   | D6 | D5 | D4                      | D3 | D2    | D1   | D0 |

| BC-LINK TYPE | R    | R  | R  | R                       | R  | R     | R    | R  |

| ECE1088      | 40h  |    |    |                         |    |       |      |    |

#### TABLE 2-12: DEVICE REVISION REGISTER

| ADDRESS      | FDh  |                         |    |    |    | 8-bit | SIZE                |    |

|--------------|------|-------------------------|----|----|----|-------|---------------------|----|

| POWER        | VCC1 |                         |    |    |    | 00h   | VCC1 POF<br>DEFAULT | 2  |

|              |      |                         |    |    |    |       |                     |    |

| BIT          | D7   | D6                      | D5 | D4 | D3 | D2    | D1                  | D0 |

| BC-LINK TYPE | R    | R                       | R  | R  | R  | R     | R                   | R  |

| BIT NAME     |      | Current Revision Number |    |    |    |       |                     |    |

#### TABLE 2-13: VENDOR ID (LSB) REGISTER

| ADDRESS      | FEh  |    |    |    |    | 8-bit | SIZE                |    |

|--------------|------|----|----|----|----|-------|---------------------|----|

| POWER        | VCC1 |    |    |    |    | 55h   | VCC1 POF<br>DEFAULT | ł  |

|              |      |    |    |    |    |       |                     |    |

| BIT          | D7   | D6 | D5 | D4 | D3 | D2    | D1                  | D0 |

| BC-LINK TYPE | R    | R  | R  | R  | R  | R     | R                   | R  |

| BIT NAME     |      |    |    | 55 | ōh |       |                     |    |

#### TABLE 2-14: VENDOR ID (MSB) REGISTER

| ADDRESS      | FFh  |    |    |                         |    | 8-bit | SIZE |    |

|--------------|------|----|----|-------------------------|----|-------|------|----|

| POWER        | VCC1 |    |    | 10h VCC1 POR<br>DEFAULT |    |       |      | 2  |

|              |      |    |    |                         |    |       |      |    |

| BIT          | D7   | D6 | D5 | D4                      | D3 | D2    | D1   | D0 |

| BC-LINK TYPE | R    | R  | R  | R                       | R  | R     | R    | R  |

| BIT NAME     |      |    |    | 1(                      | Dh |       |      |    |

#### 2.6.5 RESET REGISTER

#### TABLE 2-15: RESET REGISTER

| ADDRESS      | F5H  |    |    | 8-bit SIZE |    |    |    |               |

|--------------|------|----|----|------------|----|----|----|---------------|

| POWER        | VCC1 |    |    |            | R  |    |    |               |

|              |      |    |    |            |    |    |    |               |

| BIT          | D7   | D6 | D5 | D4         | D3 | D2 | D1 | D0            |

| BC-LINK TYPE | R    | R  | R  | R          | R  | R  | R  | W             |

| BIT NAME     |      |    |    | Reserved   |    |    |    | Force_<br>POR |

#### 2.6.5.1 Force\_POR

Writing this bit with a 1 will force a VCC1 POR. All registers and state machines in the device will be reset to their default power-on values. Writing a 0 to this bit has no effect. This is a self clearing bit.

**Note:** The Force\_POR bit does not affect the **Interface Selection** setting of the Clock Control register. Whichever bus interface is in effect at the time Force\_POR is set (BC-Link or SMBus) will remain in effect after the POR.

#### 2.6.6 MCHP TEST REGISTER

#### TABLE 2-16: MCHP TEST REGISTER

| ADDRESS      | F6H      |          |          | 8-bit SIZE |          |          |                     |          |

|--------------|----------|----------|----------|------------|----------|----------|---------------------|----------|

| POWER        | VCC1     |          |          | 00h        |          |          | VCC1 POR<br>DEFAULT |          |

|              |          |          |          |            |          |          |                     |          |

| BIT          | D7       | D6       | D5       | D4         | D3       | D2       | D1                  | D0       |

| BC-LINK TYPE | R        | R        | R        | R          | R        | R        | R                   | R        |

| BIT NAME     | Reserved | Reserved | Reserved | Reserved   | Reserved | Reserved | Reserved            | Reserved |

#### 2.6.6.1 RESERVED

Reserved for Microchip test purposes. Should not be written.

## 2.7 SMBus / BC-Link Autodetect Circuit

#### 2.7.1 OVERVIEW

For either the SMBus or the BC-Link, by detecting difference in start conditions, the Bus type is indicated. From an idle condition, the device will sample the data line on the first falling edge of the clock. If it is low, a SMBus interface is selected; if it is high, a BC-Link interface is selected. The idle condition is defined as a POR or no activity for 75 ms. To safeguard against glitches selecting the wrong bus and locking the system, the device use time-outs that reload on a start from the respective bus interface. For SMBus, the timeout is 75 ms. For BC-Link, the timeout is 75 µs.

#### 2.8 SMBus Slave Interface

The host processor communicates with the ECE1088 device through a series of read/write registers via the SMBus interface. SMBus is a serial communication protocol between a computer host and its peripheral devices.

The SMBus data rate is 10KHz minimum to 400 KHz maximum.

#### 2.8.1 CLOCKING

The SMBus Slave interface is driven by an internal Ring Oscillator. This oscillator runs at a nominal frequency of 32MHz.

The Ring Oscillator may be started and stopped through firmware interactions. The that controls the operation of the Oscillator is described in Section 2.6.2, "Clock Control" and Section 2.6.3, "Wakeup Control".

#### 2.8.2 SLAVE ADDRESS

Upon power up, the ECE1088 device will be placed into Address Select mode and assign itself an SMBus address according to the Address Select input. The device will latch the address during the first valid SMBus transaction in which the first five bits of the targeted address match those of the ECE1088 address. This feature eliminates the possibility of a glitch on the SMBus interfering with address selection.

#### TABLE 2-17:SMBUS SLAVE ADDRESS OPTIONS

| Address Select | Board Implementation                                           | SMBus Address [7:1] |

|----------------|----------------------------------------------------------------|---------------------|

| 0              | Address Select Pulled to ground through a $10k\Omega$ resistor | 0111 000b           |

| 1              | Address Select pulled to VCC1 through a $10k\Omega$ resistor   | 0111 001b           |

#### 2.8.3 SLAVE BUS INTERFACE

The ECE1088 device SMBus implementation is a subset of the SMBus interface to the host. The device is a *slave-only* SMBus device. The implementation in the device is a subset of SMBus since it only supports four protocols.

The Write Byte, Read Byte, Send Byte, and Receive Byte protocols are the only valid SMBus protocols for the device. This part responds to other protocols as described in the Invalid Protocol Section. Reference the System Management Bus Specification, Rev 2.0.

The SMBus interface is used to read and write the registers in the device. The register set is shown in Table 2-1, "Register Summary".

#### 2.8.4 WRITE BYTE

The Write Byte protocol is used to write data to the registers. The data will only be written if the protocol shown in Table 2-18, "SMBus Write Byte Protocol" is performed correctly. Only one byte is transferred at time for a Write Byte protocol.

#### TABLE 2-18: SMBUS WRITE BYTE PROTOCOL

| Field | Start | Slave Addr | Wr | Ack | Reg. Addr | Ack | Reg. Data | Ack | Stop |

|-------|-------|------------|----|-----|-----------|-----|-----------|-----|------|

| Bits  | 1     | 7          | 1  | 1   | 8         | 1   | 8         | 1   | 1    |

#### 2.8.5 READ BYTE

The Read Byte protocol is used to read data from the registers. The data will only be read if the protocol shown in Table 2-19, "SMBus Read Byte Protocol" is performed correctly. Only one byte is transferred at time for a Read Byte protocol.

#### TABLE 2-19:SMBUS READ BYTE PROTOCOL

| Field: | Start | Slave<br>Addr | Wr | Ack | Reg.<br>Addr | Ack | Start | Slave<br>Addr | Rd | Ack | Reg. Data | Nack | Stop |

|--------|-------|---------------|----|-----|--------------|-----|-------|---------------|----|-----|-----------|------|------|

| Bits:  | 1     | 7             | 1  | 1   | 8            | 1   | 1     | 7             | 1  | 1   | 8         | 1    | 1    |

#### 2.8.6 SEND BYTE

The Send Byte protocol is used to set the Internal Address Register to the correct register in the ECE1088. No data is transferred for a Send Byte protocol. The send byte protocol is shown in Table 2-20, "SMBus Send Byte Protocol".

#### TABLE 2-20: SMBUS SEND BYTE PROTOCOL

| Field: | Start | Slave Addr | Wr | Ack | Reg. Addr | Ack | Stop |

|--------|-------|------------|----|-----|-----------|-----|------|

| Bits:  | 1     | 7          | 1  | 1   | 8         | 1   | 1    |

#### 2.8.7 RECEIVE BYTE

The Receive Byte protocol is used to read data from the registers when the register address is known to be at the desired address (using the Internal Address Register). Only one byte is transferred at time for a Receive Byte protocol.

#### TABLE 2-21: SMBUS RECEIVE BYTE PROTOCOL

| Field: | Start | Slave Addr | Rd | Ack | Reg. Data | Nack | Stop |

|--------|-------|------------|----|-----|-----------|------|------|

| Bits:  | 1     | 7          | 1  | 1   | 8         | 1    | 1    |

**Note:** Some simple devices do not contain a clock low drive circuit; this simple kind of device typically may reset its communications port after a start or stop condition.

#### 2.8.8 STRETCHING THE SCLK SIGNAL

The ECE1088 supports stretching of the SCLK by other devices on the SMBus.

#### 2.8.9 SMBUS TIMING

The SMBus Slave Interface complies with the SMBus AC Timing Specification. See the SMBus timing diagram shown in Section 4.2, "SMBus Timing".

#### 2.8.10 SMBUS ALERT RESPONSE ADDRESS

This device responds to protocols with the SMBus Alert Response Address of 0001\_100 if the ARA bit in the Clock Control register is set.

#### 2.8.11 SMBUS TIME-OUT

The ECE1088 includes an SMBus time-out feature. Following a 30 ms period of inactivity on the SMBus, the device time-out and reset the SMBus interface.

#### 2.9 BC-Link Interface

The BC-Link is a proprietary bus that allows communication between a Master device and a Companion device. The Master device uses this serial bus to read and write registers located on the Companion device.

The bus comprises three signals, BC\_CLK, BC\_DAT and BC\_INT#. The Master device always provides the clock, BC\_-CLK, and the Companion device is the source for an independent asynchronous interrupt signal, BC\_INT#.

The ECE1088 supports BC-Link speeds up to 24MHz.

## 3.0 OPERATIONAL DESCRIPTION

## 3.1 Maximum Ratings

| Maximum V <sub>cc1</sub>                            | +5V           |

|-----------------------------------------------------|---------------|

| Negative Voltage on any pin, with respect to Ground | -0.3V         |

| Operating Temperature Range                         | 0°C to +70°C  |

| Storage Temperature Range                           | 55° to +150°C |

| Lead Temperature Range                              |               |

**Note:** Stresses above those listed above and below could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied. When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists, it is suggested that a clamp circuit be used.

## 3.2 DC Electrical Characteristics

#### DC ELECTRICAL CHARACTERISTICS $T_A = 0^{O}C - 70^{O}C$ , $V_{CC1} = +3.3 V \pm 10\%$ **TABLE 3-1:** Symbol MIN TYP MAX Units Parameter Comments I Type Input Buffer Low Input Level VIII 0.8 V **TTL Levels** 5.5 High Input Level VIHI V 2.0 ISP Type Input Buffer with Note 3-1 90µA Pull-up Schmitt Trigger 0.8 V Low Input Level VILIS Schmitt Trigger High Input Level V<sub>IHIS</sub> 2.2 5.5 V Schmitt Trigger Hysteresis 100 m٧ V<sub>HYS</sub> IP/O8 Type Buffer with 90µA Note 3-1 **TTL Levels** Pull-up 0.8 V Low Input Level Vii i 5.5 V VIHI $I_{OL} = 8mA$ High Input Level 2.0 V<sub>OL</sub> $I_{OH} = -4mA$ Low Output Level 0.4 V High Output Level V<sub>он</sub> 2.4 $V_{cc1} + 0.3$ V I/O8 Type Buffer TTL Levels Low Input Level 0.8 VILI V 5.5 High Input Level VIHI V 2.0 Low Output Level V<sub>OL</sub> 0.4 V $I_{OL} = 8mA$ High Output Level VOH 2.4 $V_{cc1} + 0.3$ V $I_{OH} = -4mA$ **O8** Type Buffer V<sub>OL</sub> Low Output Level 0.4 V $I_{OL} = 8mA$

$V_{cc1} + 0.3$

V

2.4

V<sub>он</sub>

High Output Level

$I_{OH} = -4mA$

| Parameter                                                          | Symbol              | MIN | TYP | MAX | Units | Comments                                                                                                |

|--------------------------------------------------------------------|---------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------------------------------|

| Leakage Current (ALL –<br>except Buffers)                          |                     |     |     |     |       | Note 3-2                                                                                                |

| Input High Current                                                 | ILEAK <sub>IH</sub> |     |     | 10  | μA    | $V_{IN} = V_{cc1}$                                                                                      |

| Input Low Current                                                  | ILEAK <sub>IL</sub> |     |     | -10 | μA    | $V_{IN} = 0V$                                                                                           |

| 5V Tolerant Pins                                                   |                     |     |     |     |       | V <sub>cc1</sub> = 3.3V                                                                                 |

| Input High Current                                                 | ILEAK <sub>IH</sub> |     |     | 100 | μA    | V <sub>IN</sub> =5.5V Max                                                                               |

| Input High Current                                                 | ILEAK <sub>IH</sub> |     |     | 10  | μA    | $V_{IN} \le V_{cc1}$                                                                                    |

| Input Low Current                                                  | ILEAK <sub>IL</sub> |     |     | -10 | μA    | $V_{IN} = 0V$                                                                                           |

| V <sub>CC1</sub> Supply Current Active                             | I <sub>CC</sub>     |     | 3   | 8   | mA    | measured with<br>SMBus/BC-Link traffic                                                                  |

| V <sub>CC1</sub> Supply Current Active<br>with Ring Oscillator Off | I <sub>CC</sub>     |     |     | 500 | μA    | measured with Ring<br>Oscillator off (OCS<br>Control bit set to<br>Oscillator Low Power<br>Enable mode) |

| Reset Voltage                                                      | V <sub>RST</sub>    | 1.6 | 1.8 | 2.1 | V     | Device is in internal reset state when $V_{cc1}$ is below min $V_{RST}$                                 |

## TABLE 3-1: DC ELECTRICAL CHARACTERISTICS $T_A = 0^{O}C - 70^{O}C$ , $V_{CC1} = +3.3 V \pm 10\%$

• Voltages are measured from the local ground potential, unless otherwise specified.

• Typicals are at TA=25°C and represent most likely parametric norm.

• The maximum allowable power dissipation at any temperature is PD = (TJmax - TA) / QJA.

• Timing specifications are tested at the TTL logic levels, VIL=0.4V for a falling edge and VIH=2.4V for a rising edge. TRI-STATE output voltage is forced to 1.4V.

• All pins except power and ground are 5V tolerant.

**Note 3-1** 90µA Pull-up with +/- 40% variation

**Note 3-2** leakage currents are measured with all pins in high impedance.

#### 3.3 AC Timing Specifications

Refer to the LSBC Bus Specification.

#### 3.4 Capacitance Values for Pins

CAPACITANCE  $T_A = 25^{\circ}C$ ; fc = 1MHz;  $V_{CC1} = 3.3V \pm 10\%$

#### TABLE 3-2: CAPACITANCE VALUES FOR PINS

| Parameter               | Symbol           |     | Limits |     | Unit | Test Condition                                         |

|-------------------------|------------------|-----|--------|-----|------|--------------------------------------------------------|

| Farameter               | Symbol           | MIN | TYP    | MAX | Unit | Test Condition                                         |

| Clock Input Capacitance | C <sub>IN</sub>  |     |        | 20  | pF   | All pins except pin<br>under test tied to AC<br>ground |

| Input Capacitance       | C <sub>IN</sub>  |     |        | 10  | pF   |                                                        |

| Output Capacitance      | C <sub>OUT</sub> |     |        | 20  | pF   |                                                        |

**Note 3-3** The input capacitance of a port is measured at the connector pins.

# ECE1088

## 4.0 TIMING DIAGRAMS

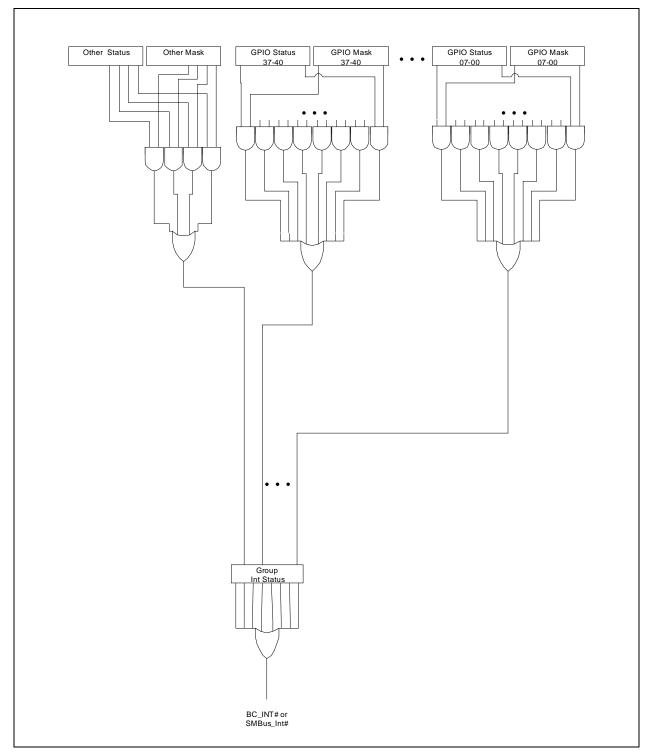

## 4.1 V<sub>CC1</sub> Power

## FIGURE 4-1: V<sub>CC1</sub> POWER

## TABLE 4-1: V<sub>CC1</sub> POWER PARAMETERS

| Symbol Parameter |                                        | Limit | S   | Units | Comments |

|------------------|----------------------------------------|-------|-----|-------|----------|

| Symbol           | Faiametei                              | Min   | Max | Units | Comments |

| t <sub>R</sub>   | V <sub>CC1</sub> Rise time, 10% to 90% | 0.150 | 30  | msec  |          |

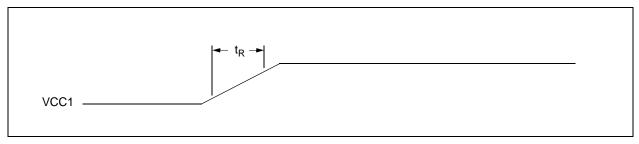

## 4.2 SMBus Timing

## FIGURE 4-2: SMBUS TIMING

| Symbol  | Parameter                                                                                    | Limit                | S   | Units | Comments |

|---------|----------------------------------------------------------------------------------------------|----------------------|-----|-------|----------|

| Symbol  | Farameter                                                                                    | Min                  | Max | Units | Comments |

| Fsmb    | SMB Operating Frequency                                                                      | 10                   | 400 | KHz   | Note 4-1 |

| Tsp     | Spike Suppression                                                                            |                      | 50  | ns    | Note 4-2 |

| Tbuf    | Bus free time between Stop and Start Condition                                               | 1.3                  |     | μS    |          |

| Thd:sta | Hold time after (Repeated) Start Condition. After this period, the first clock is generated. | 0.6                  |     | μS    |          |

| Tsu:sta | Repeated Start Condition setup time                                                          | 0.6                  |     | μS    |          |

| Tsu:sto | Stop Condition setup time                                                                    | 0.6                  |     | μS    |          |

| Thd:dat | Data hold time                                                                               | 0.3                  | 0.9 | μS    |          |

| Tsu:dat | Data setup time                                                                              | 100                  |     | ns    | Note 4-3 |

| Tlow    | Clock low period                                                                             | 1.3                  |     | μS    |          |

| Thigh   | Clock high period                                                                            | 0.6                  |     | μS    |          |

| Tf      | Clock/Data Fall Time                                                                         | 20+0.1C <sub>b</sub> | 300 | ns    |          |

| Tr      | Clock/Data Rise Time                                                                         | 20+0.1C <sub>b</sub> | 300 | ns    |          |

| Cb      | Capacitive load for each bus line                                                            |                      | 400 | pF    |          |

#### TABLE 4-2: SMBUS TIMING PARAMETERS

**Note 4-1** The max SMBus timing operating frequency exceeds that specified in the System Management Bus Specification, Rev 1.1, but corresponds to the maximum clock frequency for fast mode devices on the I<sup>2</sup>C bus (see the I<sup>2</sup>C Bus Specification).

Note 4-2 At 400kHz, the input filter suppresses spikes of a maximum pulse width of 50ns.

Note 4-3 if using 100 KHz clock frequency, the next data bit output to the SDA line will be 1250 ns (1000 ns (TR max) + 250 ns (Tsu:DAT min) @ 100 kHz) before the SCLK line is released.

# ECE1088

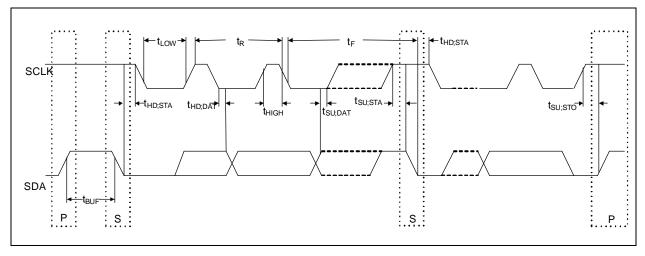

## 5.0 PACKAGE OUTLINE

#### S.K.ILEV S.K.ILEV S.K.ILEV S.K.ILEV S.K.ILEV 0.5mm PITCH REL. BY S.K.ILEV Ċ SK ALL DIMENSIONS ARE IN MILLIMETER. ALL DIMENSIONS "b" APPLIES TO PLATED TERMINALS AND IT IS MEASURED BETWEEN 0.15 AND 0.30 mm FROM THE TERMINAL. TIP. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL BUT MUST BE LOCATED WITHIN THE AREA INDICATED. ROUNDED INNER TIPS ON TERMINALS ARE OPTIONAL. 1 OF see the Microchip Packaging Specification at http://www.microchip.com/packaging Note: For the most current package drawings SHEET OVERALL PACKAGE HEIGHT LEADFRAME THICKNESS 10/7/03 12/1/03 12/14/04 12/20/04 X/Y EXPOSED PAD SIZE MOLD CAP THICKNESS 6/21/05 4/12/2011 4/20/06 DATE X/Y MOLD CAP SIZE **TERMINAL LENGTH** TERMINAL WIDTH TERMINAL PITCH X/Y BODY SIZE 28 TERMINAL QFN, 5x5mm BODY, ( 3106 PCB FEATURES POD-28QFN-5x5B-05P-3106 STANDOFF REMARK PACKAGE DATA ADDED PARALLELISM TOL, DZ'RZ' MAX, Y(nom) and X(nom), POSITION TOL MOVED TO TOP VIEW. SIDE ANGLE (max) FROM 12 TO 14° DIE and DZ/RZ TOL ROM 40.15 TO 4.10, GD/ED FROM 3.53 TO 3.65 Y(max) NOT SPECIFED NOW JEDEC: MO-220 NEW DRAWING FORMAT AND 3-D VIEW ADDED D2/E2(MIN) FROM 1.25 TO 2.95 & (NOM) ADDED **REVISION HISTORY** RECOMMENDED PCB LAND PATTERN ADDED COMMON DIMENSIONS STD COMPLIANCE REMOVE THE "PRELIMINARY" NOTE DESCRIPTION ADDING "PRELIMINARY" NOTE NOTE 4 ÷ . 1 2 $\sim$ 1 INITIAL RELEASE Ξ CALE MAX 1.00 0.05 0.80 5.10 4.95 3.20 0.75 0.30 10/7/03 10/7/03 10/7/03 DATE 0.20 (REF MON 0.50 BSC 5.00 4.75 3.10 0.60 0.25 0.85 0.02 0.65 $\square$ REV < m ۵ o ш U RAWN S.K.ILIEV S.K.ILEV S.K.ILEV $\oplus$ NAME NΝ 4.55 3.00 0.50 0.18 PROVED 0.80 0.60 4.90 0 HIRD SYMBOL D2/E2 D1/E1 ANGULAR ±1° D/E Ł A2 A3 p Ф ∢ \_ NOTES: UNLESS OTHERWISE SPECIFIED DIMENSIONS ARE IN MILLIMETERS AND TOLERANCES ARE: INTERPRET DIM AND TOL PER ASME Y14.5M - 1994 PRINT WITH "SCALE TO FIT DO NOT SCALE DRAWING . DECIMAL XX ±0.1 XXX ±0.05 XXXX±0.025 -TERMINAL #1 IDENTIFIER AREA (D/2 X E/2) EXPOSED PAD (ePAD) 28X L 🔬 $\leq$ BOTTOM VIEW **3-D VIEWS** πυπόλητα MAX 0.28 0.10 0.05 **NAAAA** 0.1000 C A B LAND PATTERN DIMENSIONS $\triangleleft$ MON -D2 3 10 0 24 0 89 0 50 UUUUU MIM 65 28X k (DATUM B) SYMBOL ⊕ 0.10 m C A B (DATUM A) // 0.10 C PCB LAND PATTERN MAXIMUM THERMAL AND ELECTRICAL PACKAGE PEFFORMANCE IS ACHIEVED WHEN AN ARRAY OF SOLD VIAS IS INCORPORATED IN THE CENTER LAND PATTERN THE USER MAY MODIFY THE PCB LAND PATTERN TERMINAL #1 IDENTIFIER AREA A3. -ON THEIR EXPERIENCE 4X 45°X0.6MAX (OPTIONAL) SIDE VIEW TOP VIEW שששששם 4X 0°-14° DIMENSIONS BASED ON THEIR AND/OR PROCESS CAPABILITY ġ - D2'ì 0

### FIGURE 5-1: PACKAGE OUTLINE: 28-PIN QFN BODY 5X5 MM BODY

## APPENDIX A: DATA SHEET REVISION HISTORY

| <b>Revision Level &amp; Date</b> | Section/Figure/Entry                                                | Correction |  |  |  |  |

|----------------------------------|---------------------------------------------------------------------|------------|--|--|--|--|

| DS00002623A (01-15-18)           | Public Release, REV A replaces previous SMSC version Rev. 1.6 (02-2 |            |  |  |  |  |

#### TABLE A-1: REVISION HISTORY

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. <sup>(1)</sup><br>Device | - <u>XXX</u> <sup>(2)</sup> - <u>[X]</u> <sup>(3)</sup><br>Package Tape and Reel<br>Option | Exam<br>a) E | <b>ple:</b><br>CE1088-DZK = 28-pin QFN                                                                                                                                                                                                                                    |

|-----------------------------------|--------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                           | ECE1088 <sup>(1)</sup>                                                                     | Note 1:      | These products meet the halogen maximum concentration values per IEC61249-2-21.                                                                                                                                                                                           |

| Package:                          | DZK = 28 pin QFN <sup>(2)</sup><br>Blank = Tray packaging                                  | Note 2:      | All package options are RoHS compliant.<br>For RoHS compliance and environmental<br>information, please visit <u>http://www.micro-<br/>chip.com/pagehandler/en-us/aboutus/</u><br>ehs.html.                                                                               |

| Option:                           | TR = Tape and Reel <sup>(3)</sup>                                                          | Note 3:      | Tape and Reel identifier only appears in the catalog part number description. This identi-<br>fier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. |

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2008-2018, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 9781522425663

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

## Worldwide Sales and Service

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 **Technical Support:** http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880- 3770

Tel: 82-53-744-4301

Tel: 82-2-554-7200

Tel: 63-2-634-9065

Taiwan - Hsin Chu

Tel: 886-3-577-8366 Taiwan - Kaohsiung

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

Fax: 31-416-690340

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4450-2828

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

**Germany - Garching**

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Italy - Milan

Italy - Padova

Tel: 972-9-744-7705

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

Tel: 49-7131-67-3636

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

Korea - Daegu

Korea - Seoul

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila

Singapore Tel: 65-6334-8870

Taiwan - Taipei

Thailand - Bangkok Tel: 66-2-694-1351

Tel: 886-7-213-7830

Tel: 886-2-2508-8600

**Netherlands - Drunen** Tel: 31-416-690399

> Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

**Romania - Bucharest** Tel: 40-21-407-87-50

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Interface - I/O Expanders category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

PCA9654EDR2G LC709006V-E LC709006V-TLM-E PM8004C-F3EI PM8005C-F3EI PI4IOE5V9554LEX PI4IOE5V9555LEX PI4IOE5V6534Q2ZLWEX PI4IOE5V6416Q2LEX 41700-100 MCP25050-E/P PCA9554PW.112 PCF8575TS/1.112 PCA9555PW.112 MIC74YQS ADP5585ACBZ-00-R7 ADP5585ACBZ-04-R7 EM4095HMSO16A HTRC11001T/02EE ADP5587ACPZ-1-R7 ADP5587ACPZ-R7 ADP5585ACPZ-01-R7 ADP5586ACBZ-00-R7 PCF8574P XD8574AP XD8574P XD8255-2 XD82C55-5 EM4095HMSO16B KTS1620EWA-TR MAX7311AWG+ MCP25025-ISL MCP25020-I/SL MAX7300ATL+ MAX7301ATL+T MCP23009T-E/SS MCP23008-E/SS MCP23009-E/SS MAX7325ATG+T MCP23016-I/SO MCP23S17-E/SO MAX7300AAI+ MAX7301AAI+ MAX7312AUG+ MAX7315AEE+ MAX7317AEE+ MAX7321AEE+ MCP25020-I/P PCA9554APW,118 MAX7310AUE+