# HV53011

### 16-Channel ±135V Push-Pull Driver with RTZ

#### Features

- 16-Channel Push-Pull Output

- Return-To-Zero (RTZ) and High Impedance (Hi-Z) Function

- Up to ±135V Output Voltage

- 24 mA Minimum Source Sink Output Current

- 250 pF Maximum Output Load

- · Current Sensor Output

- SPI Interface with Quad-Latched 2-Bit per Channel Architecture

- Power-On Reset Function

- Shutdown Function

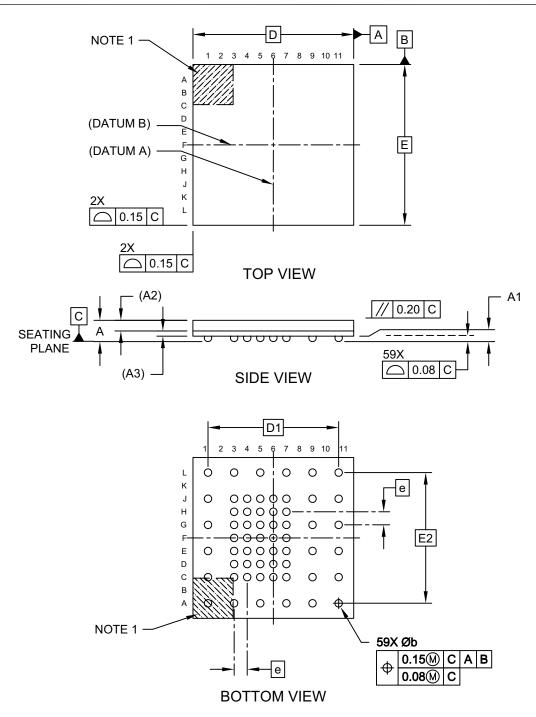

- 59-Ball 8 x 8 mm TFBGA Package

#### Application

- Surface Haptic Application

- MEMS Driver

- Piezo Driver

#### **General Description**

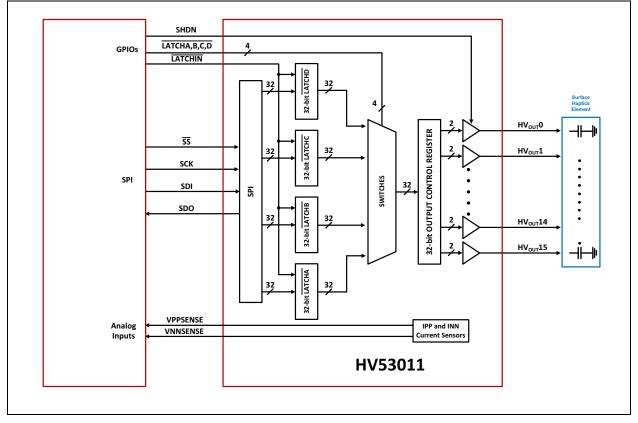

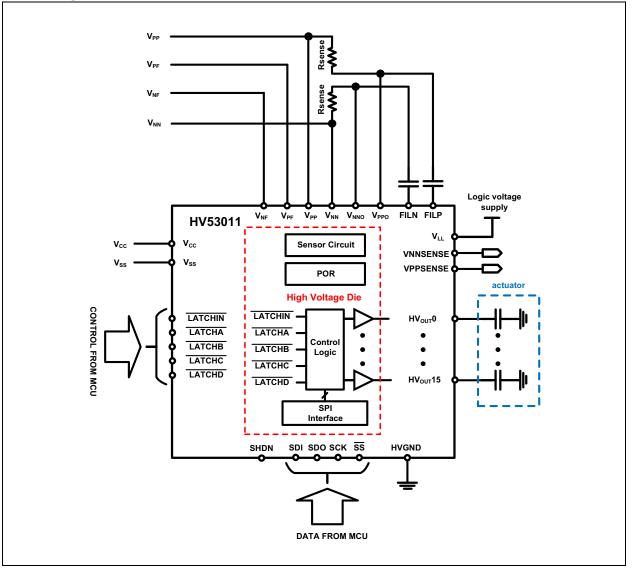

HV53011 is a high-voltage driver solution for surface haptic applications. It consists of 16 push-pull drivers capable of ±135V output swing with Return-To-Zero (RTZ) function. Each output driver is capable of sourcing and sinking at least 24 mA. Each high-voltage output is capable of driving up to 250 pF capacitive load. A global current sensor function is also integrated into this device to monitor the charge and discharge currents. The measured current is mapped to a low voltage analog output with a scale factor of 3.1 V/V via a current-sensing resistor.

An SPI interface is used to communicate between the microcontroller/processor and the high-voltage drivers. This interface accepts 3.3V logic I/O signals up to clock speeds of 32 MHz. Five digital LATCH control signals manage the data flow and the firing pattern. It establishes the output to one of four possible states:  $V_{PP}$ ,  $V_{NN}$ , 0V or high impedance.

A proper power on and off sequence is critical to ensure the operation of the high-voltage driver. This driver requires four high-voltage power rails, V<sub>PP</sub>, V<sub>PF</sub>, V<sub>NN</sub>, V<sub>NF</sub>, and three low-voltage power rails, V<sub>CC</sub>, V<sub>SS</sub> and V<sub>LL</sub>. A companion integrated driver IC, HV53001, has a built-in power on/off sequence control circuits to maintain the proper orders.

A shutdown function is available to disable the driver and set it to consume minimum power when the driver is not used.

The HV53011 device is packaged in a 8 x 8 mm 59-ball TFBGA package. All high-voltage I/Os are assigned to have sufficient clearance for safety purposes.

#### **Typical Application Diagram**

### HV53011

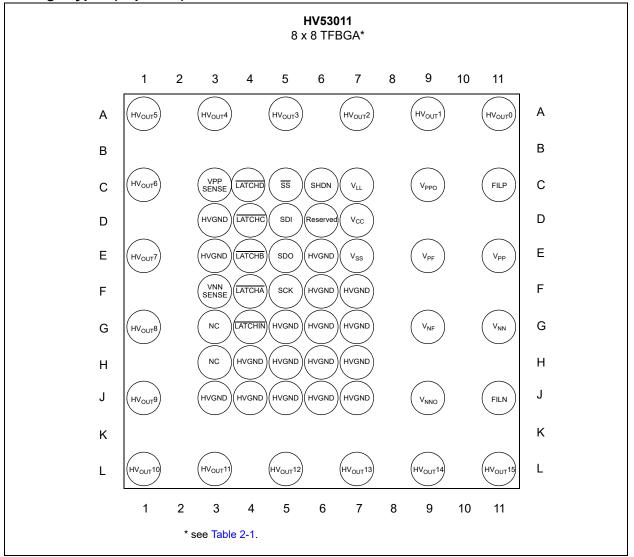

Package Types (Top View)

# HV53011

#### **Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| High Positive Supply Voltage ( $V_{PP}$ )<br>High Negative Supply Voltage ( $V_{NN}$ )<br>High Positive Floating Supply Voltage ( $V_{PF}$ )<br>High Negative Floating Supply Voltage ( $V_{NF}$ )<br>Analog Low Positive Voltage Supply ( $V_{CC}$ )<br>Analog Low Negative Voltage Supply ( $V_{SS}$ )<br>Logic Voltage Supply ( $V_{LL}$ )<br>Logic Input Levels (Hi-V Driver, SPI interface, LATCHx and SHDN)<br>Maximum Junction Temperature ( $T_{J(MAX)}$ )<br>Storage Temperature<br>ESD Rating on Low Voltage Pins (Human Body Model)<br>ESD Rating on High Voltage Pins (Human Body Model) | $\begin{array}{c} -140 \mbox{V to } +0.3 \mbox{V}_{PP} - 14 \mbox{V to } \mbox{V}_{PP} \\ & \ & \ & \ & \ & \ & \ & \ & \ & \ &$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| ESD Rating on High Voltage Pins (Charged Device Model)<br>ESD Rating on High Voltage Pins (Charged Device Model)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 500 V                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 1-1: OPERATING SUPPLY VOLTAGES

**Electrical Specifications:** Unless otherwise specified:  $T_A = T_J = +25^{\circ}C$ . **Boldface** specifications apply over the  $T_A = T_J = range$  of -40°C to +125°C.

| Parameter                                            | Sym.            | Min.                   | Тур. | Max.                   | Units | Conditions |

|------------------------------------------------------|-----------------|------------------------|------|------------------------|-------|------------|

| High Positive Supply Voltage                         | V <sub>PP</sub> | 48                     |      | 135                    | V     | Note 1     |

| High Negative Supply Voltage                         | V <sub>NN</sub> | -135                   |      | -48                    | V     |            |

| Low Positive Supply Voltage<br>(High Voltage Driver) | V <sub>CC</sub> | 6.0                    | 6.5  | 7.0                    | V     |            |

| Low Negative Supply Voltage<br>(High Voltage Driver) | V <sub>SS</sub> | -6.5                   | -6.0 | -5.5                   | V     |            |

| Logic Input Supply Voltage<br>(SPI Interface)        | $V_{LL}$        | 3.0                    | 3.3  | 3.6                    | V     |            |

| Negative Floating Supply Voltage                     | V <sub>NF</sub> | V <sub>NN</sub> + 9V   | -    | V <sub>NN</sub> +13.2V | V     |            |

| Positive Floating Supply Voltage                     | V <sub>PF</sub> | V <sub>PP</sub> -13.2V | -    | V <sub>PP</sub> - 9V   | V     |            |

| High-Level Input Logic Voltage                       | V <sub>IH</sub> | 0.8 V <sub>LL</sub>    |      |                        | V     |            |

| Low-Level Input Logic Voltage                        | V <sub>IL</sub> | 0                      |      | 0.2 V <sub>LL</sub>    | V     |            |

**Note 1:** Specification is obtained by characterization and is not 100% tested.

#### TABLE 1-2: ELECTRICAL CHARACTERISTICS

**Electrical Specifications:** Unless otherwise specified, all limits apply for  $T_A = T_J = 25^{\circ}C$ ; **Boldface** specifications apply over the full operating temperature range of  $T_A = T_J = -40^{\circ}C$  to  $125^{\circ}C$ . Typical values are at  $+25^{\circ}C$ .  $V_{PP} = +135V$ ,  $V_{PF} = +123V$ ,  $V_{NF} = -123V$ ,  $V_{CC} = +6.5V$ ,  $V_{SS} = -6.0V$ ,  $V_{LL} = +3.3V$  unless otherwise specified.

| specified.                                                                                                   |                    |      |      | P    |       | 1                                                                                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------|--------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                                                                    | Sym.               | Min. | Тур. | Max. | Units | Conditions                                                                                                                                                      |  |

| High Voltage Driver                                                                                          |                    |      |      |      |       |                                                                                                                                                                 |  |

| Quiescent $V_{PP}$ Supply Current (Sum of Current at $V_{PP}$ and $V_{PPO}$ pins)                            | I <sub>PP</sub> Q  |      | 3.7  | 5.6  | mA    |                                                                                                                                                                 |  |

| Quiescent V <sub>NN</sub> Supply Current<br>(Sum of Current at V <sub>NN</sub> and<br>V <sub>NNO</sub> pins) | I <sub>NN</sub> Q  | -5.8 | -3.8 |      | mA    |                                                                                                                                                                 |  |

| Quiescent V <sub>PF</sub> Supply Current<br>(Source)                                                         | I <sub>PF</sub> Q  | -5.2 | -3.6 |      | mA    |                                                                                                                                                                 |  |

| Quiescent V <sub>NF</sub> Supply Current<br>(Source)                                                         | I <sub>NF</sub> Q  |      | 3.7  | 5.4  | mA    |                                                                                                                                                                 |  |

| Quiescent High Voltage Positive<br>Supply Resultant Current,<br>I <sub>PP</sub> Q+ I <sub>PF</sub> Q         | I <sub>PPR</sub> Q |      |      | 0.4  | mA    |                                                                                                                                                                 |  |

| Quiescent High Voltage<br>Negative Supply Resultant<br>Current, I <sub>NN</sub> Q+ I <sub>NF</sub> Q         | I <sub>NNR</sub> Q | -0.4 |      |      | mA    |                                                                                                                                                                 |  |

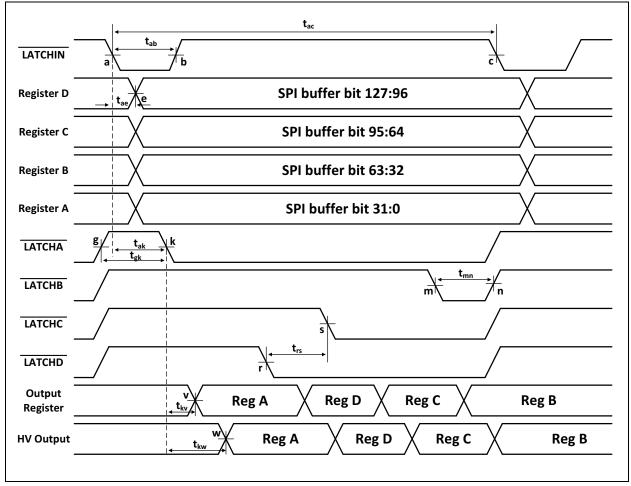

| V <sub>PP</sub> Supply Current<br>(Sum of current at V <sub>PP</sub> and<br>V <sub>PPO</sub> pins)           | Ipp                |      |      | 7.5  | mA    | V <sub>PP</sub> =+90V, V <sub>NN</sub> =-90V,<br>V <sub>PF</sub> =+78V, V <sub>NF</sub> =-78V,<br>f <sub>HVOUT</sub> = 20 kHz,CL=                               |  |

| V <sub>NN</sub> Supply Current<br>(Sum of current at V <sub>NN</sub> and<br>V <sub>NNO</sub> pins)           | I <sub>NN</sub>    | -7.5 |      |      | mA    | 250 pF, Running two<br>channels. Test pattern =<br>Figure 1-3 with 12.5 μs<br>pulse width                                                                       |  |

| High Voltage Positive Supply<br>Resultant Current, I <sub>PP</sub> + I <sub>PF</sub>                         | I <sub>PPR</sub>   |      |      | 2    | mA    | V <sub>PP</sub> =+90V, V <sub>NN</sub> =-90V,<br>V <sub>PF</sub> =+78V, V <sub>NF</sub> =-78V,<br>f <sub>HVOUT</sub> = 20 kHz,CL=<br>250 pF Bunning two         |  |

| High Voltage Negative Supply<br>Resultant Current, I <sub>NN</sub> + I <sub>NF</sub>                         | I <sub>NNR</sub>   | -2   |      |      | mA    | 250 pF, Running two<br>channels. Test pattern =<br>Figure 1-3 with 12.5 μs<br>pulse width                                                                       |  |

| V <sub>PF</sub> Operating Supply Current                                                                     | I <sub>PF</sub>    | -5.5 |      |      | mA    | V <sub>PP</sub> = +90V, V <sub>NN</sub> = -90V,<br>V <sub>PF</sub> = + 78V, V <sub>NF</sub> = -78V,<br>f <sub>HVOUT</sub> = 20 kHz,<br>C <sub>L</sub> = 250 pF, |  |

| V <sub>NF</sub> Operating Supply Current                                                                     | I <sub>NF</sub>    |      |      | 5.5  | mA    | C <sub>L</sub> = 250 pF,<br>Running two channels.<br>Test pattern =<br>Figure 1-3 with 12.5 μs<br>pulse width                                                   |  |

Note 1: Recommended operating conditions:  $V_{LL} = +3.3V$ ,  $V_{CC} = +6.5V$ ,  $V_{SS} = -6.0V$ ,  $V_{PP} = +135V$ ,  $V_{NN} = -135V$  all input pins = 0V unless noted.  $T_J = 25^{\circ}.C$

**2:** Design guidance only.

**3:** Specification is obtained by characterization and is not 100% tested.

#### TABLE 1-2: ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all limits apply for  $T_A = T_J = 25^{\circ}C$ ; **Boldface** specifications apply over the full operating temperature range of  $T_A = T_J = -40^{\circ}C$  to  $125^{\circ}C$ . Typical values are at  $+25^{\circ}C$ .  $V_{PP} = +135V$ ,  $V_{PF} = +123V$ ,  $V_{NF} = -123V$ ,  $V_{CC} = +6.5V$ ,  $V_{SS} = -6.0V$ ,  $V_{LL} = +3.3V$  unless otherwise specified.

| Parameter                                                                                                   | Sym.                   | Min.                   | Тур. | Max.                   | Units | Conditions                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------|------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> Operating Supply Current                                                                    | I <sub>CC</sub>        |                        |      | 0.2                    | mA    | V <sub>PP</sub> =+90V, V <sub>NN</sub> =-90V,<br>V <sub>PF</sub> =+78V, V <sub>NF</sub> =-78V,<br>Test pattern =                              |

| V <sub>SS</sub> Operating Supply Current                                                                    | I <sub>SS</sub>        | -0.2                   |      |                        | mA    | Figure 1-3 with 12.5 $\mu$ s pulse width                                                                                                      |

| V <sub>LL</sub> Operating Supply Current                                                                    | ارر                    |                        |      | 25                     | mA    | $V_{LL}$ = +3.3V<br>SCK = 32 MHz,<br>SDI = 16 MHz pulse<br>train                                                                              |

| V <sub>NF</sub> Negative Floating Supply<br>Voltage                                                         | V <sub>NF</sub>        | V <sub>NN</sub> +9V    | -    | V <sub>NN</sub> +13.2V | V     |                                                                                                                                               |

| V <sub>PF</sub> Positive Floating Supply<br>Voltage                                                         | V <sub>PF</sub>        | V <sub>PP</sub> -13.2V | -    | V <sub>PP</sub> -9V    | V     |                                                                                                                                               |

| HV <sub>OUT</sub> Switching Frequency                                                                       | <sup>f</sup> нvouт     | 0                      |      | 25                     | kHz   | $V_{PP} = +90V, V_{NN} = -90V, V_{PF} = +78V, V_{NF} = -78V, C_L = 250 \text{ pF}, Test pattern = Figure 1-3 with 12.5 \ \mu s \ pulse width$ |

| HV <sub>OUT</sub> Output Source and Sink<br>Current                                                         | I <sub>HVOUT</sub>     | 24                     |      |                        | mA    | V <sub>PP</sub> = +90V,<br>V <sub>NN</sub> = -90V,<br>V <sub>PF</sub> = +78V,<br>V <sub>NF</sub> = -78V                                       |

| Return-To-Zero Slew Rate<br>90% to 10%<br>(i) from V <sub>PP</sub> to 0V<br>(ii) from V <sub>NN</sub> to 0V | SR                     | 40                     | 100  | 200                    | V/µs  | $V_{PP} = +90V, V_{NN} = -90V, V_{PF} = +78V, V_{NF} = -78V, V_{CC} = +6.5V, V_{SS} = -6.0V C_L = 250 \text{ pF}$                             |

| Delay Time for Output to Start<br>Rise/Fall<br>(from LATCHA, B, C, D to<br>1V HV <sub>OUT</sub> )           | t <sub>d(ON/OFF)</sub> |                        |      | 100                    | ns    | $V_{PP}$ = +135 V,<br>$V_{NN}$ = -135 V,<br>$V_{CC}$ = 6.5V, $V_{SS}$ = -6.0V<br>No load (Note 3)                                             |

| Variation of Delay Time<br>(Channel to Channel)                                                             | $\Delta t_{d}$         |                        |      | 40                     | ns    | Note 3                                                                                                                                        |

| Shutdown Pin Input Enable<br>Voltage                                                                        | V <sub>IH(SHDN)</sub>  | 2.5                    |      |                        | V     |                                                                                                                                               |

VPPSENSE and VNNSENSE Current Sensor

Note 1: Recommended operating conditions:  $V_{LL} = +3.3V$ ,  $V_{CC} = +6.5V$ ,  $V_{SS} = -6.0V$ ,  $V_{PP} = +135V$ ,  $V_{NN} = -135V$  all input pins = 0V unless noted.  $T_J = 25^{\circ}$ .C

- **2:** Design guidance only.

- **3:** Specification is obtained by characterization and is not 100% tested.

#### TABLE 1-2: ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all limits apply for  $T_A = T_J = 25^{\circ}C$ ; **Boldface** specifications apply over the full operating temperature range of  $T_A = T_J = -40^{\circ}C$  to  $125^{\circ}C$ . Typical values are at  $+25^{\circ}C$ .  $V_{PP} = +135V$ ,  $V_{PF} = +123V$ ,  $V_{NF} = -123V$ ,  $V_{CC} = +6.5V$ ,  $V_{SS} = -6.0V$ ,  $V_{LL} = +3.3V$  unless otherwise specified.

| Parameter                                                             | Sym.                                        | Min.               | Тур. | Max.               | Units | Conditions                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------|---------------------------------------------|--------------------|------|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Farameter                                                             | Sym.                                        | IVIIII.            | тур. | IVIAA.             | Units |                                                                                                                                                                                                                                                      |

| VPPSENSE/VNNSENSE<br>Output Voltage                                   | V <sub>out</sub><br>(VPPSENSE/<br>VNNSENSE) | 0                  |      | 3.6                | v     | $V_{PP} = +135V, \\ V_{NN} = -135V, \\ V_{CC} = +6.5V, \\ V_{SS} = -6.0V, \\ V_{PP} - V_{PPO} = 1.0V, \\ V_{NNO} - V_{NN} = 1.0V$                                                                                                                    |

| Voltage Gain of Current Sensor                                        | AV <sub>SENSE</sub>                         | -14%               | 3.1  | +14%               | V/V   | $V_{PP} = +135V,$<br>$V_{NN} = -135V,$<br>$V_{CC} = +6.5V,$<br>$V_{SS} = -6.0V,$<br>$V_{PP}-V_{PPO}$ and<br>$V_{NNO}-V_{NN}$ : from 0.1 to<br>1.0V                                                                                                   |

| Sensing Amplifier Output Offset                                       | V <sub>OS</sub>                             | -280               |      | +280               | mV    | $V_{PP} = +135V, \\ V_{NN} = -135V, \\ V_{CC} = +6.5V, \\ V_{SS} = -6.0V, \\ V_{PP}-V_{PPO} \text{ and } \\ V_{NNO}-V_{NN}: \text{ from } 0.1 \text{ to } \\ 1.0V$                                                                                   |

| Rise Time                                                             |                                             |                    |      | 300                | ns    | (Note 3)<br>$V_{PP} = +90V,$<br>$V_{NN} = -90V,$<br>$V_{CC} = +6.5V,$<br>$V_{SS} = -6.0V, C_{L} = 3 pF,$<br>Test pulse: 1V, 1 µs<br>pulse width<br>1. $V_{PP}$ and $V_{PPO}$<br>2. $V_{NN}$ and $V_{NNO}$                                            |

| (Time from 10% to 90% of targeted value)                              | t <sub>R</sub>                              |                    |      | 740                | ns    | $V_{PP} = +90V, \\ V_{NN} = -90V, \\ V_{CC} = +6.5V, \\ V_{SS} = -6.0V, C_{L} = 20 \text{ pF}, \\ \text{Test pulse: } 1V, 1  \mu\text{s} \\ \text{pulse width} \\ 1.  V_{PP} \text{ and } V_{PPO} \\ 2.  V_{NN} \text{ and } V_{NNO} \\ \end{array}$ |

| VPPSENSE/VNNSENSE                                                     | R <sub>LOAD</sub>                           | 10                 |      |                    | MΩ    | Note 2                                                                                                                                                                                                                                               |

| Output Load                                                           | C <sub>LOAD</sub>                           |                    |      | 3                  | pF    | Note 2                                                                                                                                                                                                                                               |

| SPI Interface                                                         | · · · · · ·                                 |                    | 1    | 1                  | T     | 1                                                                                                                                                                                                                                                    |

| Digital Input Clock Frequency                                         | f <sub>CLK</sub>                            |                    |      | 32                 | MHz   | 3.3V logic input                                                                                                                                                                                                                                     |

| High-Level Input Logic Voltage                                        | V <sub>IH</sub>                             | 0.8V <sub>LL</sub> |      |                    | V     |                                                                                                                                                                                                                                                      |

| Low-Level Input Logic Voltage                                         | V <sub>IL</sub>                             | 0                  |      | 0.2V <sub>LL</sub> | V     |                                                                                                                                                                                                                                                      |

| Logic I/O Pin Rise and Fall Time <b>Note 1:</b> Recommended operation | t <sub>R</sub> , t <sub>F</sub>             |                    |      | 5                  | ns    | C <sub>L</sub> = 15 pF ( <b>Note 3</b> )                                                                                                                                                                                                             |

Note 1: Recommended operating conditions:  $V_{LL}$  = +3.3V,  $V_{CC}$  = +6.5V,  $V_{SS}$  = -6.0V,  $V_{PP}$  = +135V,  $V_{NN}$  = -135V all input pins = 0V unless noted.  $T_J$  = 25°.C

**2:** Design guidance only.

**3:** Specification is obtained by characterization and is not 100% tested.

#### TABLE 1-2: ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise specified, all limits apply for  $T_A = T_J = 25^{\circ}C$ ; **Boldface** specifications apply over the full operating temperature range of  $T_A = T_J = -40^{\circ}C$  to  $125^{\circ}C$ . Typical values are at  $+25^{\circ}C$ .  $V_{PP} = +135V$ ,  $V_{PF} = +123V$ ,  $V_{NF} = -123V$ ,  $V_{CC} = +6.5V$ ,  $V_{SS} = -6.0V$ ,  $V_{LL} = +3.3V$  unless otherwise specified.

| Parameter                                                                    | Sym.                | Min. | Тур.                            | Max.                          | Units | Conditions                                                          |  |

|------------------------------------------------------------------------------|---------------------|------|---------------------------------|-------------------------------|-------|---------------------------------------------------------------------|--|

| Sourced by any standard I/O pin                                              | Isource             | 10   |                                 |                               | mA    | Note 2                                                              |  |

| Sunk by any standard I/O pin                                                 | lsink               | 10   |                                 |                               | mA    | Note 2                                                              |  |

| SPI Quiescent Current of Low<br>Voltage Supplies with Shut-<br>down asserted | I <sub>LL</sub> Q   |      |                                 | 100                           | μA    | In shutdown mode.<br>All logic input = 0V.<br>$V_{(SHDN)} = V_{LL}$ |  |

| Time to Enter and Exit<br>Shutdown                                           | t <sub>SHDN</sub>   |      |                                 | 1                             | ms    | SCK = 32 MHz and<br>SDI = 16 MHz pulse<br>train.                    |  |

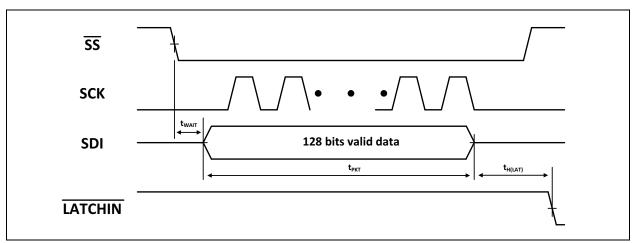

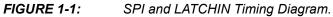

| Time from Chip Select and SPI data                                           | t <sub>WAIT</sub>   | 20   | 50                              | -                             | ns    | Refer to Figure 1-1<br>(Note 2)                                     |  |

| Time to Transfer 128 Bits of<br>Data                                         | t <sub>PKT</sub>    | 4    | -                               | -                             | μs    | Refer to Figure 1-1<br>(Note 2)                                     |  |

| Time from Last Clock Pulse to<br>LATCHIN                                     | t <sub>H(LAT)</sub> | 20   | 50                              | -                             | ns    | Refer to Figure 1-1<br>(Note 2)                                     |  |

| Digital Interface                                                            |                     |      |                                 |                               |       |                                                                     |  |

| Time SPI Latch Held Low                                                      | t <sub>ab</sub>     | 20   | 50                              | -                             | ns    | Refer to Figure 1-2<br>(Note 2)                                     |  |

| Time Between SPI Latches                                                     | t <sub>ac</sub>     | 10   | 12                              | -                             | μs    | Refer to Figure 1-2<br>(Note 2)                                     |  |

| Time from SPI Latch Assert to<br>Data Valid                                  | t <sub>ae</sub>     | -    | 10                              | 20                            | ns    | Refer to Figure 1-2<br>(Note 2)                                     |  |

| Time from SPI Latch to Data<br>Latch                                         | t <sub>ak</sub>     | 20   | 50                              | -                             | ns    | Refer to Figure 1-2<br>(Note 2)                                     |  |

| Time Latch Signal Held High t <sub>gk</sub> 20 50 - ns                       |                     | ns   | Refer to Figure 1-2<br>(Note 2) |                               |       |                                                                     |  |

| Time Latch Signal Held Low                                                   | t <sub>mn</sub>     | 20   | 50                              | - ns Refer to Figure (Note 2) |       | Refer to Figure 1-2<br>(Note 2)                                     |  |

| Time Between Two Data Latch<br>Events                                        | t <sub>rs</sub>     | 80   | 100                             | -                             | ns    | Refer to Figure 1-2<br>(Note 2)                                     |  |

| Propagation Delay from Data<br>Register to Output Register                   | t <sub>kv</sub>     | -    | 10                              | 20                            | ns    | Refer to Figure 1-2<br>(Note 2)                                     |  |

Note 1: Recommended operating conditions:  $V_{LL}$  = +3.3V,  $V_{CC}$  = +6.5V,  $V_{SS}$  = -6.0V,  $V_{PP}$  = +135V,  $V_{NN}$  = -135V all input pins = 0V unless noted.  $T_J$  = 25°.C

2: Design guidance only.

**3:** Specification is obtained by characterization and is not 100% tested.

#### **TEMPERATURE SPECIFICATIONS**

| Electrical Specifications: $V_{PP}$ = +135V, $V_{NN}$ = -135V, $V_{PF}$ = +123V, $V_{NF}$ = -123V, $V_{CC}$ = +6.5V, $V_{SS}$ = -6.0V, $V_{LL}$ = +3.3V unless otherwise specified. |                |      |      |      |       |            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|------------|--|

| Parameters                                                                                                                                                                          | Sym.           | Min. | Тур. | Max. | Units | Conditions |  |

| Temperature Ranges                                                                                                                                                                  |                |      |      |      |       |            |  |

| Operating Junction Temperature Range                                                                                                                                                | Τ <sub>J</sub> | -40  | _    | +125 | °C    |            |  |

| Storage Temperature Range                                                                                                                                                           | T <sub>A</sub> | -65  | —    | +150 | °C    |            |  |

| Package Thermal Resistance                                                                                                                                                          |                |      |      |      |       |            |  |

| Thermal Resistance, 59B 8x8 TFBGA                                                                                                                                                   | $\theta_{JA}$  | _    | 33.7 | _    | °C/W  |            |  |

#### 1.1 Timing Diagrams

FIGURE 1-2: LATCHA, B, C, D and High Voltage Output Timing Diagram.

FIGURE 1-3: High Voltage Output Test Pattern.

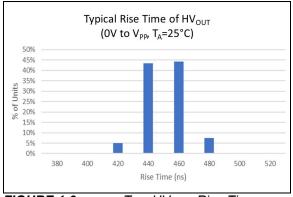

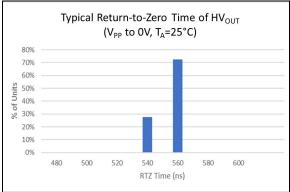

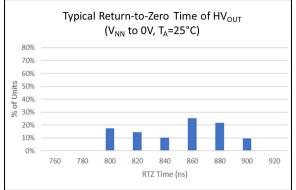

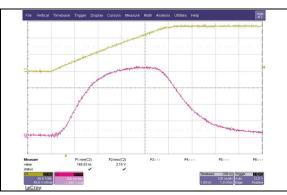

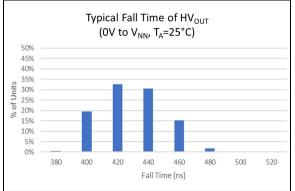

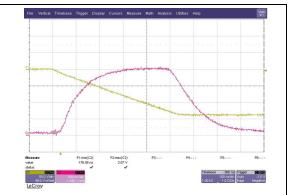

#### 1.2 Typical Performance Curves

**Note:** The graphs and tables provided below are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g. outside specified power supply range) and therefore outside the warranted range.

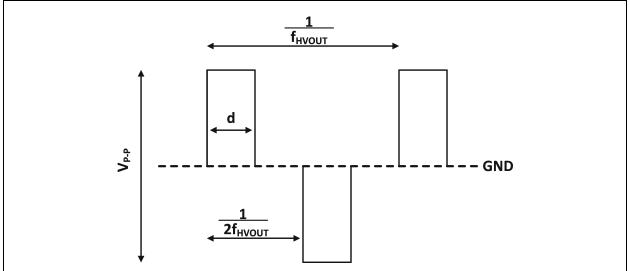

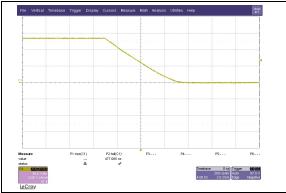

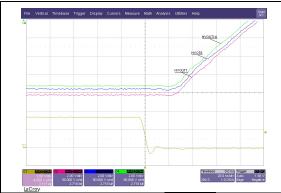

**FIGURE 1-4:** Typical  $HV_{OUT}$  Output Waveform  $V_{PP}$ =135V,  $V_{NN}$ =-135V, Load = 100 pF.

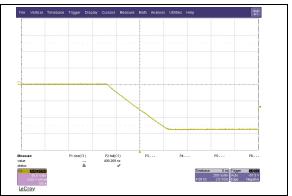

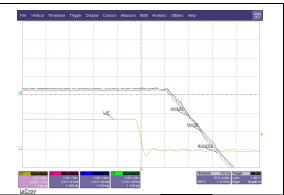

**FIGURE 1-6:** Typical  $HV_{OUT}$  from 135V to 0V, Load = 100 pF.

**FIGURE 1-8:** Typical  $HV_{OUT}$  from -135V to 0V, Load = 100 pF.

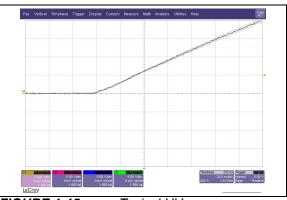

**FIGURE 1-5:** Typical  $HV_{OUT}$  from 0V to 135V, Load = 100 pF

**FIGURE 1-7:** Typical HV<sub>OUT</sub> from 0V to -135V, Load = 100 pF.

**FIGURE 1-9:** Typ. HV<sub>OUT</sub> Rise Time Distribution, from 0V to 90V, Load = 250 pF.

**Note:** The graphs and tables provided below are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g. outside specified power supply range) and therefore outside the warranted range.

**FIGURE 1-10:** Typ. HV<sub>OUT</sub> Fall Time Distribution, from 90V to 0V, Load = 250 pF.

**FIGURE 1-12:** Typ. HV<sub>OUT</sub> Rise Time Distribution, from -90V to 0V, Load = 250 pF.

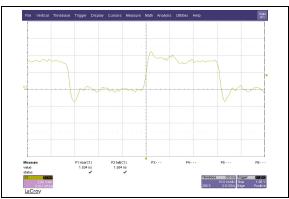

**FIGURE 1-14:** Typical VPPSENSE buffered output,  $V_{PP} = 135V$ ,  $V_{NN} = -135V$ , Load=100 pF, 6.04 ohm sense resistor, four channels active.

**FIGURE 1-11:** Typ. HV<sub>OUT</sub> Fall Time Distribution, from 0V to -90V, Load = 250 pF.

*FIGURE 1-13:* Typical VNNSENSE Buffered Output, V<sub>PP</sub>=135V, V<sub>NN</sub>=-135V, Load=100pF, 6.04 ohm sense resistor, four channels active.

FIGURE 1-15: Typical HV<sub>OUT</sub> Channel-to-Channel Delay.

**Note:** The graphs and tables provided below are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g. outside specified power supply range) and therefore outside the warranted range.

**FIGURE 1-16:** Typical LATCHA to HV<sub>OUT</sub> Propagation Delay

**FIGURE 1-18:** Typical LATCHC to HV<sub>OUT</sub> Propagation Delay

FIGURE 1-20: Typical SDO output Rise Time and Fall Time

**FIGURE 1-17:** Typical LATCHB to HV<sub>OUT</sub> Propagation Delay

**FIGURE 1-19:** Typical LATCHD to HV<sub>OUT</sub> Propagation Delay

#### 2.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 2-1.

#### TABLE 2-1:PIN FUNCTION TABLE

| Pin                                  | Symbol               | Description                                                         |

|--------------------------------------|----------------------|---------------------------------------------------------------------|

| E11                                  | V <sub>PP</sub>      | Positive High-Voltage Supply                                        |

| C9                                   | V <sub>PPO</sub>     | Positive High-Voltage Current Sense                                 |

| G11                                  | V <sub>NN</sub>      | Negative High-Voltage Supply                                        |

| J9                                   | V <sub>NNO</sub>     | Negative High-Voltage Current Sense                                 |

| D7                                   | V <sub>CC</sub>      | Positive Low-Voltage Supply                                         |

| E7                                   | V <sub>SS</sub>      | Negative Low-Voltage Supply                                         |

| C7                                   | V <sub>LL</sub>      | VLL Logic Voltage                                                   |

| J3-7, H4-7,G5-7,<br>F6-7, E6, D3, E3 | HVGND                | High-Voltage Ground                                                 |

| E9                                   | V <sub>PF</sub>      | Positive floating voltage supply reference to V <sub>PP</sub> level |

| G9                                   | V <sub>NF</sub>      | Negative floating voltage supply reference to V <sub>NN</sub> level |

| J11                                  | FILN                 | 0.1 µF Capacitor across FILN and VNNO                               |

| C11                                  | FILP                 | 0.1 µF Capacitor across FILP and VPPO                               |

| C3                                   | VPPSENSE             | Positive High-Voltage Sense Analog Output                           |

| F3                                   | VNNSENSE             | Negative High-Voltage Sense Analog Output                           |

| G3                                   | NC                   | No connection (Do not connect. Keep the pin floating.)              |

| H3                                   | NC                   | No connection (Do not connect. Keep the pin floating.)              |

| A11                                  | HV <sub>OUT</sub> 0  | High-Voltage Output 0                                               |

| A9                                   | HV <sub>OUT</sub> 1  | High-Voltage Output 1                                               |

| A7                                   | HV <sub>OUT</sub> 2  | High-Voltage Output 2                                               |

| A5                                   | HV <sub>OUT</sub> 3  | High-Voltage Output 3                                               |

| A3                                   | HV <sub>OUT</sub> 4  | High-Voltage Output 4                                               |

| A1                                   | HV <sub>OUT</sub> 5  | High-Voltage Output 5                                               |

| C1                                   | HV <sub>OUT</sub> 6  | High-Voltage Output 6                                               |

| E1                                   | HV <sub>OUT</sub> 7  | High-Voltage Output 7                                               |

| G1                                   | HV <sub>OUT</sub> 8  | High-Voltage Output 8                                               |

| J1                                   | HV <sub>OUT</sub> 9  | High-Voltage Output 9                                               |

| L1                                   | HV <sub>OUT</sub> 10 | High-Voltage Output 10                                              |

| L3                                   | HV <sub>OUT</sub> 11 | High-Voltage Output 11                                              |

| L5                                   | HV <sub>OUT</sub> 12 | High-Voltage Output 12                                              |

| L7                                   | HV <sub>OUT</sub> 13 | High-Voltage Output 13                                              |

| L9                                   | HV <sub>OUT</sub> 14 | High-Voltage Output 14                                              |

| L11                                  | HV <sub>OUT</sub> 15 | High-Voltage Output 15                                              |

| C5                                   | SS                   | SPI Chip Select                                                     |

| D5                                   | SDI                  | SPI Data In                                                         |

| E5                                   | SDO                  | SPI Data Out (for daisy chain)                                      |

| F5                                   | SCK                  | SPI Clock                                                           |

| G4                                   | LATCHIN              | Latch SPI Data (SPI -> Latch A, B, C, D)                            |

| F4                                   | LATCHA               | Latch A -> Output Register                                          |

| E4                                   | LATCHB               | Latch B -> Output Register                                          |

| D4                                   | LATCHC               | Latch C -> Output Register                                          |

| C4                                   | LATCHD               | Latch D -> Output Register                                          |

TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

| Pin | Symbol   | Description                      |  |  |  |

|-----|----------|----------------------------------|--|--|--|

| C6  | SHDN     | Shutdown Mode                    |  |  |  |

| D6  | Reserved | Reserved Pin. Connect to Ground. |  |  |  |

#### 3.0 DEVICE DESCRIPTION

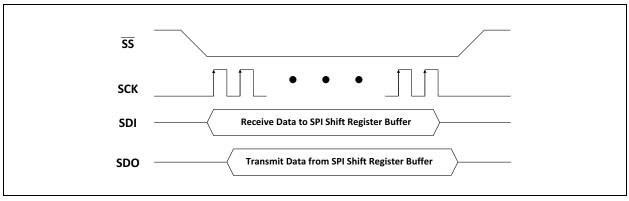

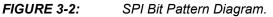

#### 3.1 Serial Peripheral Interface

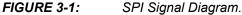

The SPI interface is used to transfer data of the channel settings from the microcontroller to the high-voltage driver. The HV53011 operates as an SPI slave device and receives 128 bits of data from the master device (microcontroller). The HV53011 SPI interface is designed to be compatible with all Microchip 8-bit, 16-bit and 32-bit SPI data transmission formats. This SPI interface has a 128-bit shift register buffer to store 128 bits of data.

The  $\overline{SS}$  pin is a chip select function which is similar to the enable function to guard the clock and data input signal. The SCK contains the bus clock signal from the

microcontroller or host processor. The SDI and SDO are the data input and data output pins of the SPI shift register buffer.

The SDI and SDO can be used to cascade multiple HV53011 or HV53011 drivers together if only a single SPI port is available. This SPI interface is compatible with 3.3V logic input voltage with a maximum clock frequency of 32 MHz.

The SPI shift register captures the data at the SDI input in the rising edge of the SCK clock and pushes out the data from the buffer to the SDO output in the falling edge of the SCK clock. When the SPI bus is at idle status, the  $\overline{SS}$  pin stays in logic "1" and the SCK clock is expected to stay at "0".

The bit order of the SDI data input is defined as follows. The first and second data bits represent bit 1 and bit 0 of channel 15 in register D, respectively. The third and fourth bits represent bit 1 and bit 0 of channel 14 in register D. The similar pattern is extended all the way to channel 0. Hence, there are 32 data bits to control register D to cover all sixteen channels. The next 32 data bits are arranged in the same fashion for register C. Similarly, the exact pattern repeats itself for register B and A. Since each register (A, B, C and D) contains 32 bits of data, the SPI shift register buffer is 128 bits long.

Bit 1 of channel 15 in register D is defined as the MSb (Most Significant bit) and bit 0 of channel 0 in register A as the LSb (Least Significant bit) in this SPI shift register buffer definition.

The following table shows the summary of the SPI shift register buffer.

#### TABLE 3-1: REGISTER LEGEND

| Sym | Description                    |    | Description              |

|-----|--------------------------------|----|--------------------------|

| R   | Readable bit                   | HC | Cleared by Hardware only |

| W   | Writable bit                   | HS | Set by Hardware only     |

| U   | Unimplemented bit, read as '0' | 1  | Bit is set at Reset      |

| Р   | Programmable bit               | 0  | Bit is cleared at Reset  |

| S   | Settable bit                   | х  | Bit is unknown at Reset  |

| С   | Clearable bit                  |    |                          |

**Example:** R/W - 0 indicates the bit is both readable or writable, and reads '0' after a Reset.

#### TABLE 3-2: SPI\_SR 128-BIT BUFFER SUMMARY

|                  |           | -                          |                            |                            |                            |                           |                           |                           |                           |  |

|------------------|-----------|----------------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|

| Register<br>Name | Bit Range | Bit<br>127/119/111/<br>103 | Bit<br>126/118/110/<br>102 | Bit<br>125/117/109/<br>101 | Bit<br>124/116/108/<br>100 | Bit<br>123/115/107/<br>99 | Bit<br>122/114/106/<br>98 | Bit<br>121/113/105/<br>97 | Bit<br>120/112/104/<br>96 |  |

| LATCHD           | <127:120> | CH15                       | <1:0>                      | CH14                       | <1:0>                      | CH13                      | <1:0>                     | CH12                      | <1:0>                     |  |

|                  | <119:112> | CH11                       | <1:0>                      | CH10                       | <1:0>                      | CH9<                      | <1:0>                     | CH8<1:0>                  |                           |  |

|                  | <111:104> | CH7·                       | <1:0>                      | CH64                       | <1:0>                      | CH5•                      | <1:0>                     | CH4                       | <1:0>                     |  |

|                  | <103:96>  | CH3-                       | <1:0>                      | CH2•                       | <1:0>                      | CH1•                      | <1:0>                     | CH04                      | <1:0>                     |  |

| Register<br>Name | Bit Range | Bit<br>95/87/79/71         | Bit<br>94/86/78/70         | Bit<br>93/85/77/69         | Bit<br>92/84/76/68         | Bit<br>91/83/75/67        | Bit<br>90/82/74/66        | Bit<br>89/81/73/65        | Bit<br>88/80/72/64        |  |

| LATCHC           | <95:88>   | CH15                       | <1:0>                      | CH14                       | <1:0>                      | CH13                      | <1:0>                     | CH12                      | <1:0>                     |  |

|                  | <87:80>   | CH11                       | <1:0>                      | CH10<1:0>                  |                            | CH9<1:0>                  |                           | CH8<1:0>                  |                           |  |

|                  | <79:72>   | CH7·                       | <1:0>                      | CH6<1:0>                   |                            | CH5<1:0>                  |                           | CH4<1:0>                  |                           |  |

|                  | <71:64>   | CH3-                       | <1:0>                      | CH2<1:0>                   |                            | CH1<1:0>                  |                           | CH0<1:0>                  |                           |  |

| Register<br>Name | Bit Range | Bit<br>63/55/47/39         | Bit<br>62/54/46/38         | Bit<br>61/53/45/37         | Bit<br>60/52/44/36         | Bit<br>59/51/43/35        | Bit<br>58/50/42/34        | Bit<br>57/49/41/33        | Bit<br>56/48/40/32        |  |

| LATCHB           | <63:56>   | CH15                       | <1:0>                      | CH14<1:0>                  |                            | CH13<1:0>                 |                           | CH12<1:0>                 |                           |  |

|                  | <55:48>   | CH11                       | <1:0>                      | CH10<1:0>                  |                            | CH9<1:0>                  |                           | CH8<1:0>                  |                           |  |

|                  | <47:40>   | CH7·                       | <1:0>                      | CH6<1:0>                   |                            | CH5<1:0>                  |                           | CH4                       | <1:0>                     |  |

|                  | <39:32>   | CH3·                       | <1:0>                      | CH2•                       | CH2<1:0>                   |                           | CH1<1:0>                  |                           | <1:0>                     |  |

| Register<br>Name | Bit Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6          | Bit<br>29/21/13/5          | Bit<br>28/20/12/4          | Bit<br>27/19/11/3         | Bit<br>26/18/10/2         | Bit<br>25/17/9/1          | Bit<br>24/16/8/0          |  |

| LATCHA           | <31:24>   | CH15                       | CH15<1:0>                  |                            | CH14<1:0>                  |                           | CH13<1:0>                 |                           | CH12<1:0>                 |  |

|                  | <23:16>   | CH11<1:0>                  |                            | CH10                       | CH10<1:0>                  |                           | CH9<1:0>                  |                           | CH8<1:0>                  |  |

|                  | <15:8>    | CH7·                       | <1:0>                      | CH6                        | <1:0>                      | CH5<1:0>                  |                           | CH4<1:0>                  |                           |  |

|                  | <7:0>     | CH3-                       | <1:0>                      | CH2•                       | <1:0>                      | CH1•                      | <1:0>                     | CH0<1:0>                  |                           |  |

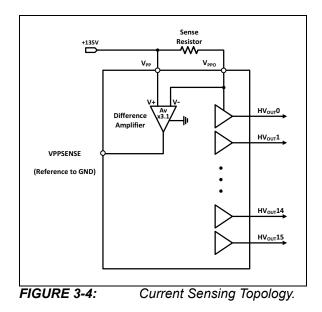

#### 3.2 Quad-Latched Two-Bit per Channel Architecture

In the Quad-Latched 2-bit per channel architecture, each channel is controlled by a 2-bit encoding for each of the four possible states: "00" = (Hi-Z) high impedance, "01" = Pull-down to  $V_{NN}$ , "10" = Pull-up to  $V_{PP}$ ,

"11" = Driven to Ground. Since there are 16 channels on each HV53011 device, a 32-bit output control register is required.

Four separate latched arrays (A, B, C, & D) hold four possible 32-bit output configurations. The data is loaded from the arrays into the output control register by four separate external control signals (LATCHA,  $\overline{B}$ ,  $\overline{C}$ ,  $\overline{D}$ ). When the output control register is being

updated using one of the latch signals, the output will go to a not driven state temporarily to avoid shoot-through.

The data in these four latched arrays can be updated using the SPI shift register buffer. The 128 bits of data is first transmitted from the host processor to this device via the SPI interface. The data format has been discussed in the previous section. After this 128 bits transaction has completed, the data will stay in the SPI shift register <u>buffer</u>. Then the user sends an activation signal at the LATCHIN pin to initiate the transfer of the data from the SPI shift register to the four 32-bit registers (A, B, C and D).

When the application requires more output channels, the user can cascade more driver devices in a daisy chain configuration. The SDO pin is used to pass the data from the SPI shift register buffer to the cascaded driver IC.

The SPI signal pins (SCK, SS, SDI and SDO) are used to control the data flow of the SPI shift register buffer. The five latch control signals (LATCHIN, LATCHA,

LATCHB, LATCHC and LATCHD) are used to control the data selection of the high-voltage output from the four 32-bit registers. The SPI interface and latch functions are two independent operation blocks.

To achieve some power savings when idling for a period of time, a shutdown pin is available to reduce the quiescent current draw as much as possible.

#### TABLE 3-3: 2-BIT CONTROL AND OUTPUT VOLTAGE LOGIC TABLE

| CONTR | OL BITS | HVOUT OUTPUT                   |  |  |  |  |

|-------|---------|--------------------------------|--|--|--|--|

| Bit 1 | Bit 0   |                                |  |  |  |  |

| 0     | 0       | High Impedance (Hi-Z)          |  |  |  |  |

| 0     | 1       | Driven Low (V <sub>NN</sub> )  |  |  |  |  |

| 1     | 0       | Driven High (V <sub>PP</sub> ) |  |  |  |  |

| 1     | 1       | Driven to Ground (0V)          |  |  |  |  |

FIGURE 3-3: Quad-Latched Two Bits per Channel Architecture.

| LATCHIN | LATCHA       | LATCHB       | LATCHC       | LATCHD       | Description                                                                                                                                                  |

|---------|--------------|--------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ļ       | Х            | Х            | Х            | Х            | SPI bit[127:96] into Latch Register D<br>SPI bit[95:64] into Latch Register C<br>SPI bit[63:32] into Latch Register B<br>SPI bit[31:0] into Latch Register A |

| X*      | $\downarrow$ | Х            | Х            | Х            | Register A to output                                                                                                                                         |

| X*      | Х            | $\downarrow$ | Х            | Х            | Register B to output                                                                                                                                         |

| X*      | Х            | Х            | $\downarrow$ | Х            | Register C to output                                                                                                                                         |

| X*      | Х            | Х            | Х            | $\downarrow$ | Register D to output                                                                                                                                         |

TABLE 3-4: QUAD-LATCHED TWO-BIT LOGIC STATE TABLE

Note: \* = Delay LATCHX appropriately if a register update from LATCHIN is still in progress.

$\downarrow$  = Negative edge-triggered.

X = Don't care.

#### 3.3 Driver Shutdown Mode

When the shutdown (SHDN) pin is at logic "1", any unnecessary circuit in the line driver will be disabled to minimize power consumption. It includes the level translator, bias current, voltage reference, driver output, SPI interface, and combinational logic. During shutdown, the quiescent current will be less than 100  $\mu$ A. The system response time is less than 1 ms to switch between shutdown and active modes when a new signal is asserted at the shutdown pin.

#### 3.4 Driver Power On Reset

The Power-on Reset function resets all high-voltage HV<sub>OUT</sub> output to high impedance when the device is initially powered on. It also resets and clears the SPI buffer registers, registers A, B, C and D to logic "0".

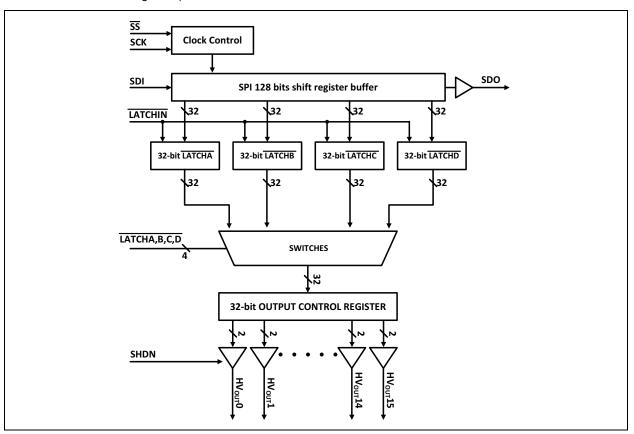

#### 3.5 Driver Output Current Sensing

Some system designs require a load sensing function to determine the size or any change of the capacitive load. One simple scheme is to place a series current sensing resistor on the power supply rail and measure the voltage drop across this resistor. This solution is very effective as long as the voltage drop is small enough not to affect the operation of the system.

The HV53011 driver IC provides this function by which users can monitor the supply current flowing through both high-voltage positive and negative supplies. Two external current sensing resistors are connected to  $V_{PP}$  and  $V_{NN}$  supply rails, respectively, as high side current sensing. The voltage drop across these resistors are fed to two pin pairs,  $V_{PP}$ - $V_{PPO}$  and  $V_{NN}$ - $V_{NNO}$ . Since this voltage drop is referenced to the  $V_{PP}$  and  $V_{NN}$  supply rails, it is not practical for any low-voltage ADC to measure this voltage. Hence, two internal difference amplifiers in the driver IC convert these voltage drops to ground reference.

The difference amplifier accepts maximum input voltage of 1V. The amplifier gain of 3.1 amplifies this input and send the output to the VPPSENSE and VNN-SENSE pins. These amplifiers are designed using high-voltage and high value resistors to minimize its power consumption. These amplifier outputs are high impedance in nature, so an external high bandwidth (200 MHz) unity gain buffer is recommended. The high bandwidth is needed to capture the fast current pulse during the transition.

The user selects the value of the sensing resistor to fit the system requirement. The speed of the difference amplifier is its highest priority because the charge or discharge current appear in a short period of time. The amplifier output accuracy is less important. Both VPPSENSE and VNNSENSE outputs have a tolerance of  $\pm 14\%$ .

#### TABLE 3-5: ACCEPTABLE POWER-ON SEQUENCES

| Steps | Description                                                                                                                                                            |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | Connect ground.                                                                                                                                                        |  |  |

| 2     | Keep shutdown pin to low.                                                                                                                                              |  |  |

| 3     | Set all driver inputs to low.                                                                                                                                          |  |  |

| 4     | Power-on supplies in this sequence: V <sub>LL</sub> , V <sub>NN</sub> , V <sub>NF</sub> , V <sub>SS</sub> , V <sub>CC</sub> , V <sub>PF</sub> and then V <sub>PP</sub> |  |  |

| 5     | Set all inputs to a known state.                                                                                                                                       |  |  |

#### TABLE 3-6: ACCEPTABLE POWER-OFF SEQUENCES

| Steps | Description                                                                                               |  |  |

|-------|-----------------------------------------------------------------------------------------------------------|--|--|

| 1     | Set all inputs and shutdown pin to low.                                                                   |  |  |

| 2     | Power-off supplies in this sequence: $V_{PP,} V_{PF}, V_{CC}, V_{SS}, V_{NF}, V_{NN}$ and then $V_{LL}$ . |  |  |

| 3     | Disconnect ground                                                                                         |  |  |

#### 4.0 PACKAGING INFORMATION

#### 4.1 Package Marking Information

59-Ball TFBGA (8x8x1.2 mm)

• **&** HV53011 2008256

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>e8<br>*                                                                                                                                                                                                                            | Product Code or Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e8)<br>can be found on the outer packaging for this package. |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. Package may or may not include<br>the corporate logo. |                                                                                                                                                                                                                                                                                                                                                                                              |  |

#### 59-Ball Thin Fine Pitch Ball Grid Array (KVX) - 8x8 mm Body [TFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### 59-Ball Thin Fine Pitch Ball Grid Array (KVX) - 8x8 mm Body [TFBGA]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |

|--------------------------|-------------|----------|----------|------|

| Dimension                | Limits      | MIN      | NOM      | MAX  |

| Number of Terminals      | Ν           | 59       |          |      |

| Pitch                    | е           | 0.65 BSC |          |      |

| Overall Height           | Α           | -        | -        | 1.20 |

| Standoff                 | A1          | 0.22     | 0.27     | 0.32 |

| Mold Thickness           | A2          | 0.53 REF |          |      |

| Substrate Thickness      | A3          | 0.26 REF |          |      |

| Overall Length           | D           |          | 8.00 BSC |      |

| Overall Terminal Spacing | D1          | 6.50 BSC |          |      |

| Overall Width            | E           | 8.00 BSC |          |      |

| Overall Terminal Spacing | E1          | 6.50 BSC |          |      |

| Terminal Diameter        | b           | 0.32     | 0.37     | 0.42 |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

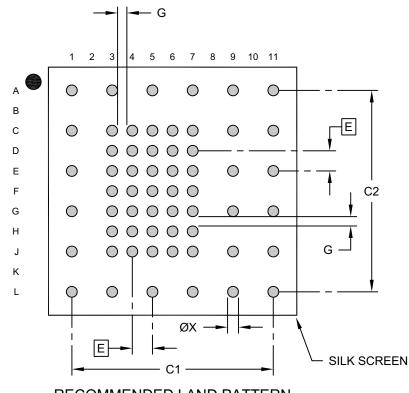

#### 59-Ball Thin Fine Pitch Ball Grid Array (KVX) - 8x8 mm Body [TFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                             | MILLIMETERS |          |      |      |

|-----------------------------|-------------|----------|------|------|

| Dimension Limits            |             | MIN      | NOM  | MAX  |

| Contact Pitch               |             | 0.65 BSC |      |      |

| Overall Contact Pad Spacing | C1          |          | 6.50 |      |

| Overall Contact Pad Spacing | C2          |          | 6.50 |      |

| Contact Pad Width (X59)     | Х           |          |      | 0.35 |

| Contact Pad to Contact Pad  | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

#### APPENDIX A: REVISION HISTORY

#### Revision A (March 2021)

• Original Release of this Document.

# HV53011

NOTES:

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO               |                                                                         | Examples:                                                                                                                                                                                                                                                                            |

|-----------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Media Type Temperature Package<br>Tape and Reel Range                   | a) HV53011-E/KVX: 16-Channel, ±135V Push-Pull<br>Driver with RTZ. Thin Fine Pitch<br>Ball Grid Array, 59-Ball TFBGA (8<br>× 8 x 1.2mm) Package, 260/Tray                                                                                                                             |

| Device:               | HV53011: 16-Channel, ±135V Push-Pull Driver with RTZ                    | b) HV53011T-E/KVX:16-Channel, ±135V Push-Pull<br>Driver with RTZ. Thin Fine Pitch<br>Ball Grid Array, 59-Ball TTBGA (8x<br>8 x 1.2mm) Package, 1000/Reel                                                                                                                             |

| Media Type:           | blank = 260/Tray for KVX Package<br>T = 1000/Reel for KVX Package       |                                                                                                                                                                                                                                                                                      |

| Temperature<br>Range: | E =-40°C to +125°C (Extended) RoHS Compliant                            |                                                                                                                                                                                                                                                                                      |

| Package:              | KVX = Thin Fine Pitch Ball Grid Array<br>59-Ball TFBGA (8 x 8 x 1.2 mm) | Note 1:         Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. |

# HV53011

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are

committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection

feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or

other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-7930-7

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

### Worldwide Sales and Service

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138 China - Zhuhai

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200 Malaysia - Kuala Lumpur

Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Tel: 84-28-5448-2100

**Netherlands - Drunen** Tel: 31-416-690399

Italy - Padova

Italy - Milan

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4485-5910

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Tel: 972-9-744-7705

Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654