# HV56020

### Dual High Voltage Op Amp with Step-Up Converter and Power MOSFET

#### Features

- Dual High Voltage Operational Amplifiers

- Up to +225V

- 40 mA Minimum Peak Output Sink/Source Current

- Output Voltage Comparators for Short Circuit Detection

- 124 Hz, -3 dB Bandwidth with 0.22 µF Load

- DC-to-DC Step-Up Converter

- Single Input Voltage Supply VIN: 2.7V to 5.5V

- Overvoltage Protection

- Undervoltage Protection

- Short Circuit Protection

- Low Current Standby Mode

- Temperature Sensor

- Power-ON Reset

- 24 MHz SPI Interface

- Power MOSFET

- 60V BV<sub>DSS</sub>

- 10 m  $\Omega$  On Resistance

#### Applications

- Haptic Drivers

- · Power Amplifiers

#### **Related Devices**

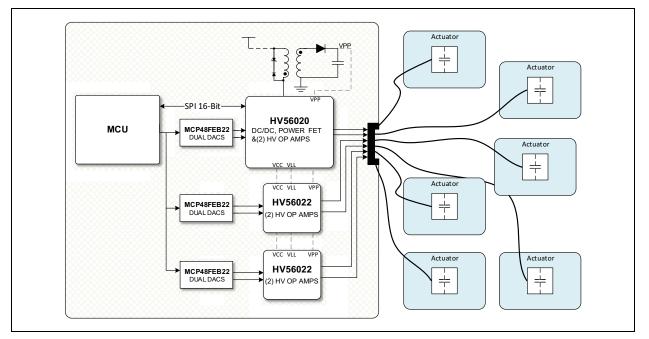

HV56022 Dual High Voltage Operational Amplifiers

#### Description

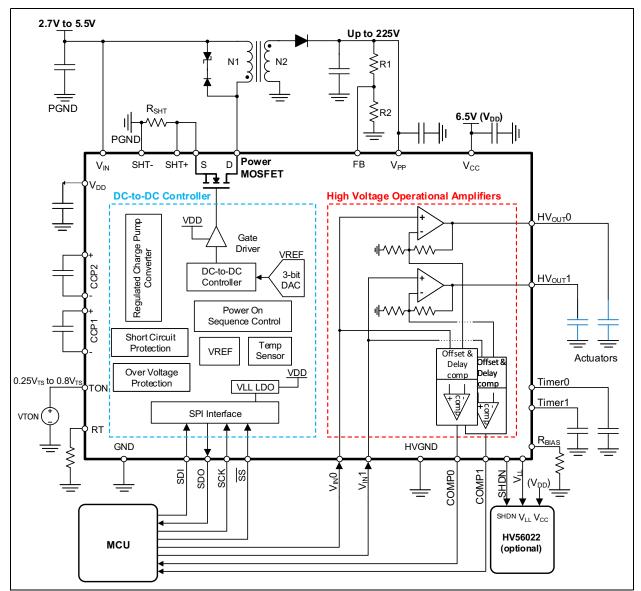

The HV56020 is a Multi-Chip Module (MCM) driver solution designed for Haptic Applications. The IC consists of three devices: (1) Dual High Voltage Operational Amplifiers, (2) a DC-to-DC Controller, and (3) a Power MOSFET. The Op Amps are designed to drive haptic (piezo) actuators at 225V with 40 mA minimum source/sink current. The DC-to-DC Controller and the power MOSFET along with an external transformer generate the voltage supply for the High Voltage Op Amps using a Non-Isolated Flyback configuration.

The HV56020 includes ample protection circuitry: Over/Undervoltage Protection, Output Short Circuit Protection (DC-to-DC), Temperature Sensor and Output Voltage Comparators for load Short Circuit Detection.

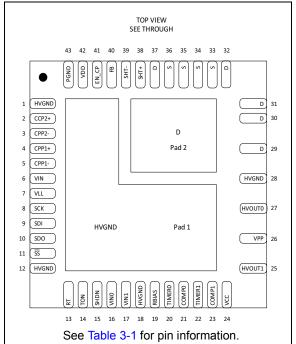

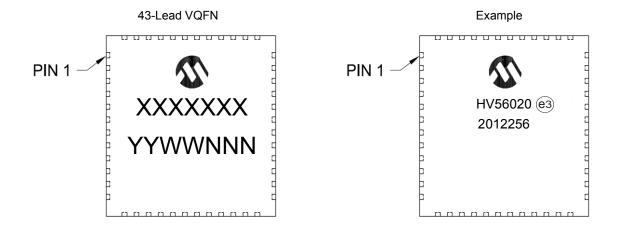

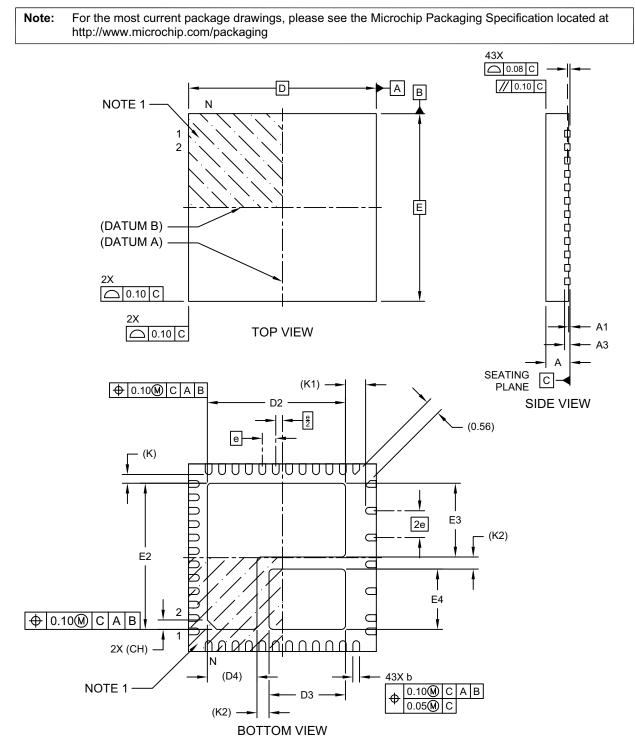

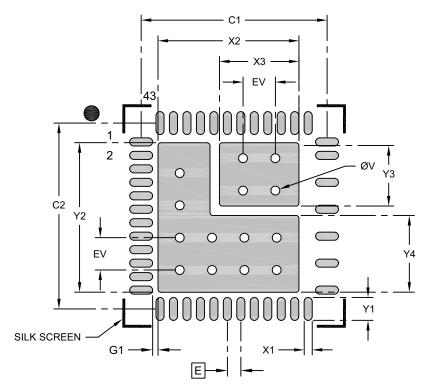

#### Package Type

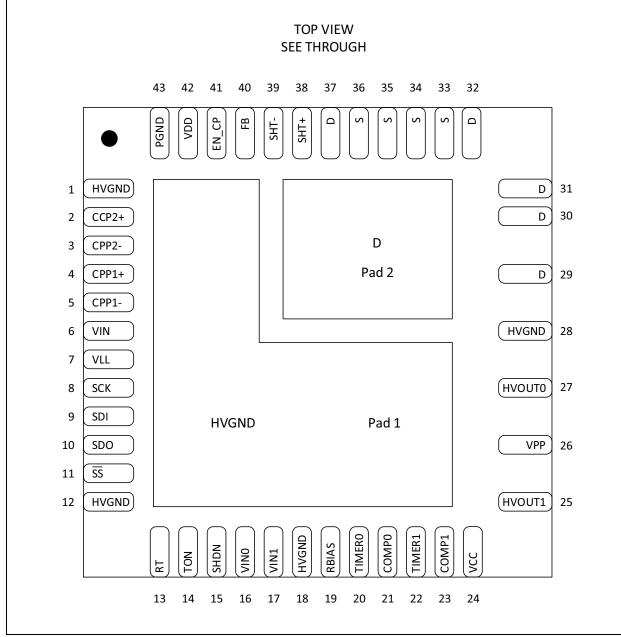

7 mm x 7 mm 43-Lead VQFN

### HV56020

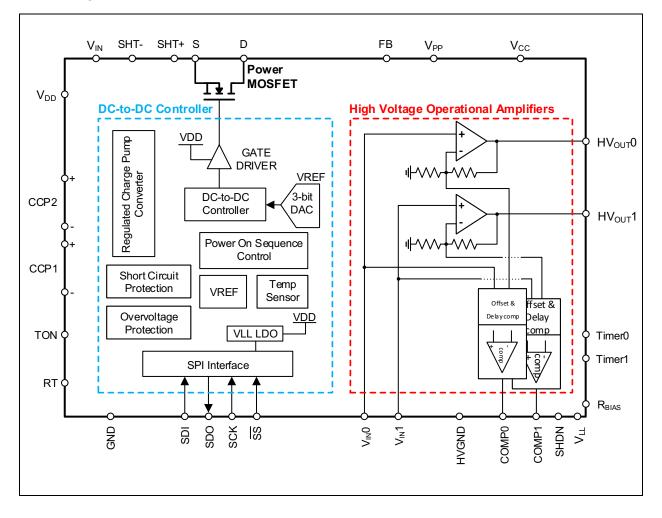

#### **Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings †

| V <sub>LL</sub> , Low Voltage Logic Supply                    | 0.3V to 5.5V   |

|---------------------------------------------------------------|----------------|

| V <sub>IN</sub> 0,1, High Voltage Op Amps Inputs              | -0.3V to 5.5V  |

| V <sub>IN</sub> , Converter Input Voltage Supply              | -0.3V to 6.0V  |

| EN_CP, Enable Charge Pump Input Voltage                       | -0.3V to 6.0V  |

| V <sub>DD</sub> , Low Output Voltage Supply                   | -0.3V to 8.0V  |

| V <sub>CC</sub> , Low Voltage Supply for High Voltage Op Amps | -0.3V to 8.0V  |

| V <sub>PP</sub> , High Voltage Supply for Op Amps             | -0.3V to 250V  |

| Storage Temperature                                           | 55°C to +150°C |

| Operating Junction Temperature                                | 0°C to +125°C  |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameters                      | Symbol                              | Min. | Тур. | Max.            | Units | Conditions   |  |  |

|---------------------------------|-------------------------------------|------|------|-----------------|-------|--------------|--|--|

| DC-TO-DC CONTROLLER             |                                     |      |      |                 |       |              |  |  |

| Charge Pump Supply Voltage      | V <sub>IN</sub>                     | 2.7  | 3.3  | 5.5             | V     |              |  |  |

| Logic Supply Voltage            | V <sub>LL</sub>                     | 3.0  | 3.3  | 3.6             | V     | Internal LDO |  |  |

| High-Level Input Logic Voltage  | V <sub>IH</sub>                     | 2.0  | _    | V <sub>LL</sub> | V     |              |  |  |

| Low-Level Input Logic Voltage   | V <sub>LL</sub>                     | 0    | _    | 0.8             | V     |              |  |  |

| HIGH VOLTAGE OPERATIONAL AI     | HIGH VOLTAGE OPERATIONAL AMPLIFIERS |      |      |                 |       |              |  |  |

| High Voltage Supply             | V <sub>PP</sub>                     | 50   | _    | 225             | V     |              |  |  |

| Low Voltage Supply              | V <sub>CC</sub>                     | 6.0  | 6.5  | 7.0             | V     |              |  |  |

| Inputs for High Voltage Op Amps | V <sub>IN</sub> 0,1                 | 0    | _    | 2.98            | V     |              |  |  |

#### **POWER SEQUENCE**

#### **Power-Up Sequence:**

- 1. Connect ground

- 2. Set all driver inputs to low

- 3. Apply V<sub>IN</sub>

- 4. Enable  $V_{DD}(V_{CC})$

- 5. Set all converter inputs to a known state

- 6. Enable V<sub>PP</sub>

#### **Power-Down Sequence:**

- 1. Disable  $V_{IN}$ 0 and  $V_{IN}$ 1 (set to 0V)

- 2. Disable  $V_{PP}$

- 3. Disable  $V_{DD}$  ( $V_{CC}$ )

- 4. Power down V<sub>IN</sub>

- 5. Disconnect ground

#### DC-TO-DC CONTROLLER: AC/DC CHARACTERISTICS

Unless otherwise specified,  $T_A = T_J = +25^{\circ}$ C. **Boldface** specifications apply over the full operating temperature range of  $T_A = T_J = 0^{\circ}$ C to +125°C. Typical values are at +25°C. EN\_CP = "1", V<sub>LL</sub>=3.3V, V<sub>CC</sub> = 6.5V unless otherwise specified.

| Parameters                                         | Symbol                  | Min.     | Тур.        | Max.            | Units | Conditions                                                                   |

|----------------------------------------------------|-------------------------|----------|-------------|-----------------|-------|------------------------------------------------------------------------------|

| Charge Pump Regulator                              |                         |          |             |                 |       |                                                                              |

| Charge Pump Input Voltage                          | V <sub>IN</sub>         | 2.7      | 3.3         | 5.5             | V     |                                                                              |

| Charge Pump Output Voltage                         | V <sub>DD</sub>         | 6        | 6.5         | 7               | V     | 2.7V ≤ V <sub>IN</sub> ≤ 5.5V, I <sub>DD</sub> =15 mA                        |

| Charge Pump Output Load Current                    |                         | 15       | _           | _               | mA    | Depends on IC loading and external capacitor selection                       |

| Output Ripple Voltage                              | V <sub>RIPPLE</sub>     | —        | _           | 80              | mV    | $V_{IN}$ = 3.3V, $I_{DD}$ = 15 mA,<br>Output Capacitance = 10 µF<br>(Note 1) |

| V <sub>DD</sub> Undervoltage Lockout               | VDD <sub>UVLO</sub>     | 4.25     | _           | 4.75            | V     | Rising Edge                                                                  |

| V <sub>DD</sub> Undervoltage Lockout<br>Hysteresis | VDD <sub>HYST</sub>     |          | 0.25        |                 | V     | Falling                                                                      |

| Enable Charge Pump Input Pin                       | EN_CP                   | 0        | —           | V <sub>IN</sub> | V     |                                                                              |

| Low Threshold for EN_CP Pin                        | V <sub>IL</sub> (EN_CP) | 0        | _           | 0.8             | V     |                                                                              |

| High Threshold for EN_CP Pin                       | V <sub>IH</sub> (EN_CP) | 2.0      | _           | V <sub>IN</sub> | V     |                                                                              |

| Pull Down Resistor at EN_CP Pin                    | EN_CP <sub>PD</sub>     | _        | 500         | _               | kΩ    | EN_CP = 3.3V                                                                 |

| Power-Down Input Current                           | I <sub>DDPD</sub>       |          |             | 5               | μA    | EN_CP = 0V                                                                   |

| Clock Generation                                   |                         |          |             |                 |       |                                                                              |

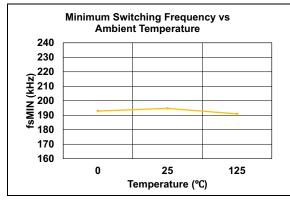

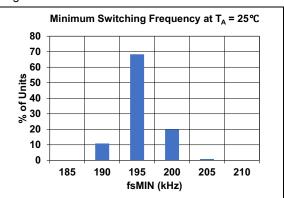

| Minimum Switching Frequency                        | f <sub>s,MIN</sub>      | 160      | 200         | 240             | kHz   | RT = 400 kΩ                                                                  |

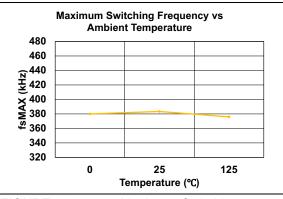

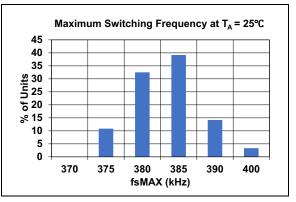

| Maximum Switching Frequency                        | f <sub>s,MAX</sub>      | 320      | 400         | 480             | kHz   | RT = 200 kΩ                                                                  |

| Clock Ramp Maximum                                 | V <sub>TS</sub>         | _        | 3.5         | _               | V     | Note 2                                                                       |

| Clock Ramp Minimum                                 | V <sub>RST</sub>        | _        | 0.2         | _               | V     | Note 2                                                                       |

| TON Generation                                     | <u> </u>                |          |             |                 |       | -                                                                            |

| Maximum Voltage at TON                             | VTON <sub>MAX</sub>     | _        | _           | 2.8             | V     | 2.8V = 0.8V <sub>TS</sub> = 80% PWM<br>Max (Note 2)                          |

| Minimum Voltage at TON                             | VTON <sub>MIN</sub>     | 0        | —           | —               | V     | 0.25V <sub>TS</sub> = 25% PWM Min<br>( <b>Note 2</b> )                       |

| TON Generation Internal Gain                       | K <sub>TON</sub>        | _        | 40          | —               | V/V   | Note 2                                                                       |

| Output Voltage Feedback                            |                         |          |             |                 |       | ·                                                                            |

| Comparator Delay                                   | T <sub>DLYCOMP</sub>    | —        | _           | 50              | ns    | 10 mV Overdrive (Note 2)                                                     |

| Overvoltage Protection                             |                         |          |             |                 |       |                                                                              |

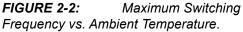

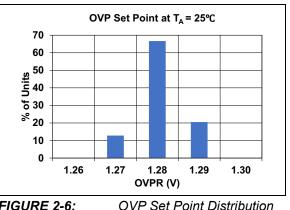

| OVP Set Point                                      | OVP <sub>R</sub>        | -3%      | 1.278       | +3%             | V     |                                                                              |

| OVP Hysteresis                                     | OVP <sub>HYST</sub>     | —        | 0.36        | —               | V     |                                                                              |

| OVP Delay Time                                     | OVP <sub>DLY</sub>      | _        | 50          | _               | ns    | 100 mV Overdrive (Note 2)                                                    |

| Short Circuit Protection                           |                         |          |             |                 |       | •                                                                            |

| Short Circuit Comparator Offset                    | SH <sub>OFF</sub>       | 34       | 50          | 68              | mV    | SHT_EN = 1<br>(SHT+ and SHT- pins)                                           |

| Temperature Sensor                                 |                         |          |             |                 |       | · · · · · ·                                                                  |

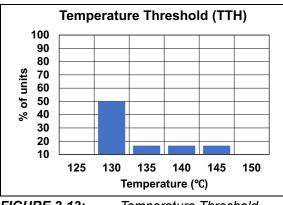

| Temperature Threshold                              | T <sub>TH</sub>         | 125      |             | 150             | °C    | Note 2                                                                       |

| Temperature Threshold Hysteresis                   | T <sub>THHYST</sub>     | _        | 25          | —               | °C    | Note 2                                                                       |

| Voltage Reference 3-Bit DAC                        |                         |          |             |                 |       | ·                                                                            |

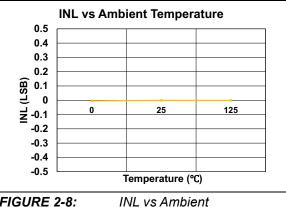

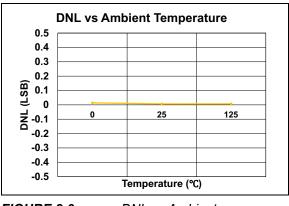

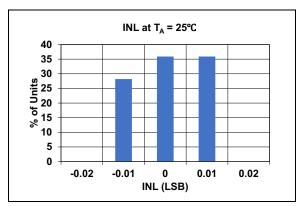

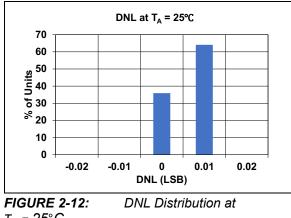

| Integral Nonlinearity                              | INL                     | _        | _           | ±0.5            | LSB   | Note 1                                                                       |

| Differential Nonlinearity                          | DNL                     |          | _           | ±0.5            | LSB   | Note 1                                                                       |

| Note 1: Specification is obtained                  |                         | ation on | lia not 100 |                 |       |                                                                              |

**Note 1:** Specification is obtained by characterization and is not 100% tested.

**2:** Design guidance only.

#### DC-TO-DC CONTROLLER: AC/DC CHARACTERISTICS (CONTINUED)

Unless otherwise specified,  $T_A = T_J = +25^{\circ}$ C. **Boldface** specifications apply over the full operating temperature range of  $T_A = T_J = 0^{\circ}$ C to +125°C. Typical values are at +25°C. EN\_CP = "1", V<sub>LL</sub>=3.3V, V<sub>CC</sub> = 6.5V unless otherwise specified.

| Parameters                                     | Symbol                          | Min. | Тур.                 | Max.     | Units | Conditions       |

|------------------------------------------------|---------------------------------|------|----------------------|----------|-------|------------------|

| Code Word                                      |                                 |      |                      |          |       |                  |

| Code 000                                       |                                 |      | 0.3 V <sub>REF</sub> |          | V     | VPP READY =1     |

| Code 001                                       |                                 |      | 0.4 VREF             | _        | V     |                  |

| Code 010                                       |                                 |      | $0.5  V_{REF}$       |          | V     |                  |

| Code 011                                       |                                 | _    | 0.6 V <sub>REF</sub> |          | V     |                  |

| Code 100                                       |                                 | _    | $0.7 V_{REF}$        |          | V     | Note 1           |

| Code 101                                       |                                 | _    | 0.8 V <sub>REF</sub> |          | V     |                  |

| Code 110                                       |                                 |      | 0.9 V <sub>REF</sub> | _        | V     |                  |

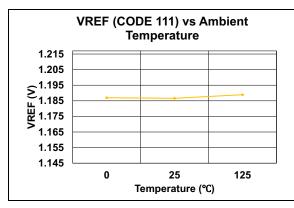

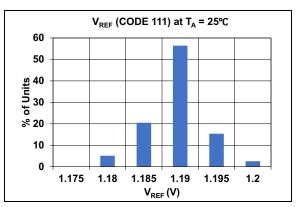

| Code 111                                       | V <sub>REF</sub>                | -3%  | 1.188                | +3%      | V     | VPP READY = 1    |

| Logic Voltage Supply (Internal LD              | O for SPI)                      |      |                      |          |       |                  |

| Logic Voltage Supply                           | $V_{LL}$                        | 3.0  | 3.3                  | 3.6      | V     |                  |

| High-Level Input Logic Voltage                 | V <sub>IH</sub>                 | 2.0  | _                    | $V_{LL}$ | V     |                  |

| Low-Level Input Logic Voltage                  | V <sub>IL</sub>                 | 0    | —                    | 0.8      | V     |                  |

| VLL Undervoltage Lockout                       | VLDO <sub>UVLO</sub>            | 2.25 | 2.5                  | 2.75     | V     |                  |

| VLL Undervoltage Lockout<br>Hysteresis         | VLDO <sub>HYST</sub>            | _    | 0.25                 |          | V     |                  |

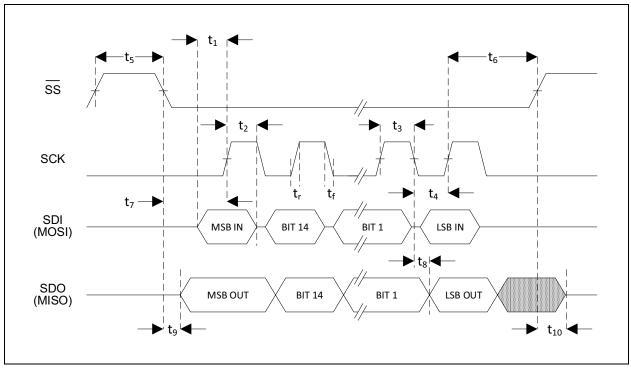

| SPI Interface                                  |                                 |      |                      |          |       | L                |

| Maximum SPI Clock Frequency                    | SCK                             | 24   | —                    |          | MHz   | 3.3V Input Logic |

| Logic Input Rise and Fall Time                 | t <sub>r</sub> , t <sub>f</sub> |      | 5                    | _        | ns    | Note 1           |

| Source Current by Standard I/O Pin             | Isource                         | 10   | —                    | _        | mA    |                  |

| Sink Current by Standard I/O Pin               | lsink                           | 10   | —                    | _        | mA    | Note 2           |

| SDI Valid to SCK Setup Time                    | t <sub>1</sub>                  | 10   | _                    | —        | ns    |                  |

| SDI Valid to SCK Hold Time                     | t <sub>2</sub>                  | 20   | —                    | —        | ns    |                  |

| SCK High Time % of 1/f <sub>clk</sub>          | t <sub>3</sub>                  | 45   | —                    | 55       | %     |                  |

| SCK Low Time % of 1/f <sub>clk</sub>           | t <sub>4</sub>                  | 45   | —                    | 55       | %     |                  |

| SS Pulse Width                                 | t <sub>5</sub>                  | 300  | —                    | _        | ns    | Note 1           |

| LSB SCK High to SS High                        | t <sub>6</sub>                  | 10   | —                    | _        | ns    |                  |

| SS Low to SCK High                             | t <sub>7</sub>                  | 20   | —                    | _        | ns    |                  |

| SDO Propagation Delay from SCK<br>Falling Edge | t <sub>8</sub>                  | 10   | _                    | _        | ns    |                  |

| SDO Output Valid after SS Low                  | t <sub>9</sub>                  | 20   | —                    | _        | ns    |                  |

| SS Inactive to SDO High<br>Impedance           | t <sub>10</sub>                 | 40   | _                    | _        | ns    | Note 2           |

Note 1: Specification is obtained by characterization and is not 100% tested.

2: Design guidance only.

FIGURE 1-1: SPI Timing Diagram.

#### **HV OPERATIONAL AMPLIFIERS: AC/DC CHARACTERISTICS**

Unless otherwise specified,  $T_A = T_J = +25^{\circ}$ C. **Boldface** specifications apply over the full operating temperature range  $T_A = T_J = 0^{\circ}$ C to +125°C. Typical values are at +25°C,  $V_{CC} = 6.5$ V unless otherwise specified.

| Parameter                                | Symbol                         | Min. | Тур. | Max. | Units | Conditions                                                                                                                                                                     |

|------------------------------------------|--------------------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HV Op Amps Low Voltage Supply            | V <sub>CC</sub>                | 6    | 6.5  | 7    | V     |                                                                                                                                                                                |

| HV Op Amps Low Voltage<br>Supply Current | I <sub>CC</sub>                | _    | 0.2  |      | mA    | $V_{CC}$ = 6.5V, $V_{PP}$ = 225V,<br>f <sub>HVOUT</sub> = 124 Hz,<br>sine wave $V_{IN}$ 0,1= 0 to 2.98V,<br>$C_L$ = 0.22 µF (Note 1)                                           |

| HV Op Amps Input Analog Voltage          | V <sub>IN</sub> 0,1            | 0    |      | 2.98 | V     | V <sub>PP</sub> = 225V, V <sub>CC</sub> = 6.5V                                                                                                                                 |

| High Voltage Supply                      | V <sub>PP</sub>                | 50   | _    | 225  | V     |                                                                                                                                                                                |

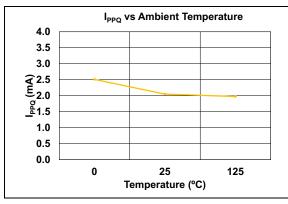

| V <sub>PP</sub> Quiescent Supply Current | I <sub>PPQ</sub>               |      | _    | 4.5  | mA    | V <sub>IN</sub> 0,1= 0V, SHDN = 0                                                                                                                                              |

| V <sub>PP</sub> Supply Current           | I <sub>PP</sub>                | _    | 16.5 | _    | mA    | $\begin{split} V_{CC} &= 6.5V, \ V_{PP} = 225V, \\ f_{HVOUT} &= 124 \ Hz, \\ sine \ wave \ V_{IN} 0, 1 = 0 \ to \ 2.98V, \\ C_L &= 0.22 \ \mu F \ (\text{Note 1}) \end{split}$ |

| V <sub>PP</sub> Shutdown Supply Current  | I <sub>PPDN</sub>              | —    | _    | 2    | μA    | SHDN = 1                                                                                                                                                                       |

| HV <sub>OUT</sub> High Level Output      | V <sub>OH</sub>                | 214  | _    | _    | V     | V <sub>CC</sub> = 6.5V, V <sub>PP</sub> = 225V,<br>Ι <sub>HVOUT</sub> = 100 μΑ                                                                                                 |

| HV <sub>OUT</sub> Low Level Output       | V <sub>OL</sub>                | —    | —    | 1    | V     | V <sub>CC</sub> = 6.5V, V <sub>PP</sub> = 225V,<br>Ι <sub>HVOUT</sub> = -100 μΑ                                                                                                |

| HV Op Amps Output Offset Voltage         | HV <sub>OFFSET</sub>           | -1.1 |      | +1.1 | V     |                                                                                                                                                                                |

| HV <sub>OUT</sub> Output Source Current  | I <sub>HVOUT</sub><br>(SOURCE) | 40   |      | _    | mA    | $100V \le V_{PP} \le 225V, V_{CC} = 6.5V$                                                                                                                                      |

| HV <sub>OUT</sub> Output Sink Current    | I <sub>HVOUT</sub><br>(SINK)   | 40   |      | _    | mA    | $100V \le V_{PP} \le 225V, V_{CC} = 6.5V$                                                                                                                                      |

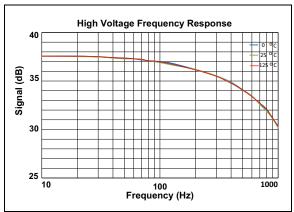

| HV <sub>OUT</sub> -3 dB Bandwidth        | BW <sub>124Hz</sub>            | _    | 124  |      | Hz    | $V_{PP}$ = 225V, $V_{CC}$ = 6.5V,<br>$C_L$ = 0 to 0.22 μF,<br>$HV_{OUT}$ = Full scale output,<br>25°C ≤ T <sub>J</sub> ≤ 60°C,<br>$R_{BIAS}$ = 150 kΩ (Note 1)                 |

| HV <sub>OUT</sub> Slew Rate              | SR <sub>HV</sub>               | 0.09 | _    |      | V/µs  | $V_{PP}$ = 225V, $V_{CC}$ = 6.5V, $C_{L}$ = 0.22 µF                                                                                                                            |

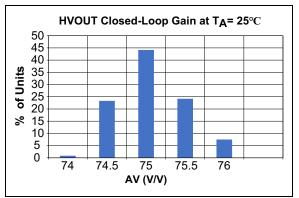

| Closed Loop Gain                         | A <sub>V</sub>                 | 72   | 75   | 78   | V/V   | V <sub>PP</sub> = 225V, V <sub>CC</sub> = 6.5V, No Load                                                                                                                        |

| Shut Down Input Pin                      | SHDN                           | 0.3  |      | 3.3  | V     |                                                                                                                                                                                |

| HV Op Amps Shutdown Time                 | t <sub>SHDN</sub>              | _    | 300  | _    | ns    | V <sub>PP</sub> = 225V, V <sub>CC</sub> = 6.5V,<br>SHDN = 0 to 1, V <sub>IN</sub> 0,1 = 0 ( <b>Note 2</b> )                                                                    |

| HV Op Amps Wake-Up Time<br>from Shutdown | t <sub>WKUP</sub>              | _    | 2    | _    | ms    | V <sub>PP</sub> = 225V, V <sub>CC</sub> = 6.5V,<br>SHDN = 1 to 0, V <sub>IN</sub> 0,1 = 0 ( <b>Note 2</b> )                                                                    |

| HV Op Amp Output<br>Preload Capacitor    | C <sub>PRE</sub>               | _    | 10   | _    | nF    | Note 2                                                                                                                                                                         |

| Output Voltage Comparators               |                                |      |      |      |       |                                                                                                                                                                                |

| Comparator Output High Logic (VOH)       | COMP0,                         | 2    |      | 3.3  | v     |                                                                                                                                                                                |

| Comparator Output Low Logic (VOL)        | COMP1                          | 0    |      | 0.8  | v     |                                                                                                                                                                                |

| Comparator Output Sink Current           | C <sub>ISINK</sub>             |      | -2   |      | mA    | Note 1                                                                                                                                                                         |

| Comparator Output Source Current         | CISOURCE                       | —    | 2    | _    | mA    | Note 1                                                                                                                                                                         |

| Comparator Input Offset                  | V <sub>OFFSET</sub>            |      | 110  | _    | mV    | Note 1                                                                                                                                                                         |

| Comparator Delay                         | t <sub>DELAY</sub>             | 0.6  | 1.6  | 2.6  | ms    | 1.5 nF at Timer 0, 1 pin, $R_{BIAS}$ = 150 k $\Omega$                                                                                                                          |

Note 1: Specification is obtained by characterization and is not 100% tested.

**2:** Design guidance only.

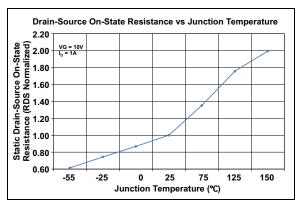

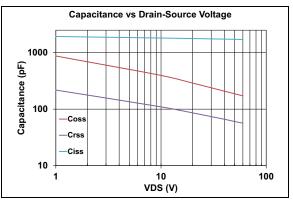

#### POWER MOSFET: AC/DC CHARACTERISTICS

Unless otherwise specified  $T_A = T_J = +25^{\circ}$ C. **Boldface** specifications apply over the full operating temperature range  $T_A = T_J = 0^{\circ}$ C to +125°C. Typical values are at +25°C, EN\_CP = 1,  $V_{IN} = 3.3$ V,  $V_{CC} = 6.5$ V unless otherwise specified.

| Parameters                        | Symbol               | Min. | Тур. | Max. | Units | Conditions                                      |

|-----------------------------------|----------------------|------|------|------|-------|-------------------------------------------------|

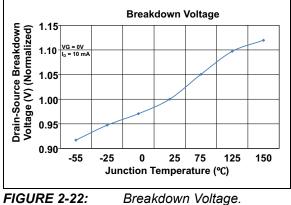

| Drain to Source Breakdown Voltage | BVDSS                | 60   | _    | _    | V     | V <sub>GS</sub> = 0V                            |

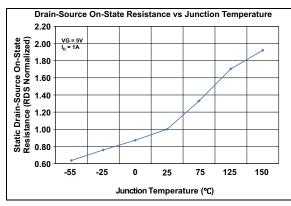

| Drain to Source ON Resistance     | R <sub>DS</sub> (ON) | —    |      | 10   | mΩ    | V <sub>GS</sub> = 5V, ID = 1A ( <b>Note 1</b> ) |

| Diode Forward Voltage             | V <sub>SD</sub>      |      |      | 1.2  | V     | $I_{\rm S}$ = 60A, $V_{\rm GS}$ = 0V            |

**Note 1:** Design guidance only.

#### **TEMPERATURE SPECIFICATIONS**

| Parameter                      | Symbol          | Min. | Тур. | Max. | Units | Conditions |  |

|--------------------------------|-----------------|------|------|------|-------|------------|--|

| Temperatures Ranges            |                 |      |      |      |       |            |  |

| Operating Junction Temperature | TJ              | 0    | —    | +125 | °C    |            |  |

| Storage Temperature            | T <sub>A</sub>  | -55  | —    | +150 | °C    |            |  |

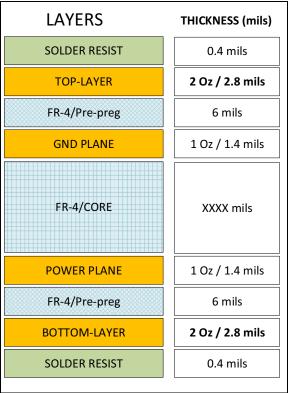

| Package Thermal Resistances    |                 |      |      |      |       |            |  |

| Thermal Resistance             | θ <sub>JC</sub> | _    | 1.66 | _    | °C/W  | Note 1     |  |

| (43-Lead VQFN)                 | θ <sub>JA</sub> |      | 27   | _    | °C/W  | Note 1     |  |

Note 1: 4 Layers FR4 4"X4" PCB.

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

#### 2.1 DC-to-DC Controller

FIGURE 2-3:OVP Set Point vs AmbientTemperature.

**FIGURE 2-4:** Minimum Switching Frequency Distribution at  $T_A = 25^{\circ}C$ .

**FIGURE 2-5:** Maximum Switching Frequency Distribution at  $T_A = 25^{\circ}$ C.

**FIGURE 2-6:** OVP Set Point Distribution at  $T_A = 25^{\circ}$ C.

FIGURE 2-7: VREF (Code 111) vs Ambient Temperature.

FIGURE 2-8: Temperature.

FIGURE 2-9: Temperature.

DNL vs Ambient

**FIGURE 2-10:** VREF (Code 111) Distribution at  $T_A = 25^{\circ}$ C.

**FIGURE 2-11:** INL Distribution at  $T_A = 25^{\circ}$ C.

$T_A = 25^{\circ}C.$

FIGURE 2-13:Temperature ThresholdDistribution.

#### 2.2 HV Amplifiers

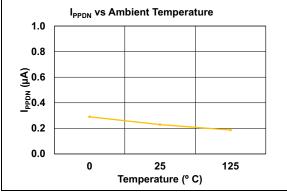

**FIGURE 2-15:** I<sub>PPDN</sub> vs Ambient Temperature.

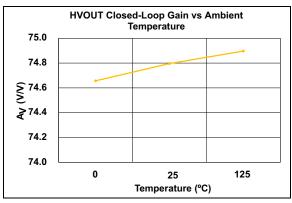

**FIGURE 2-16:** HVOUT Closed-Loop Gain vs Ambient Temperature.

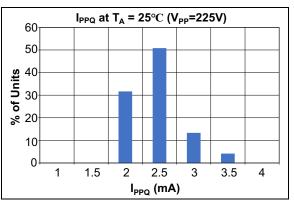

**FIGURE 2-17:**  $I_{PPQ}$  Distribution at  $T_A = 25^{\circ}$ C.

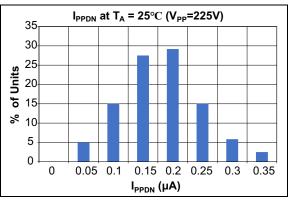

**FIGURE 2-18:**  $I_{PPDN}$  Distribution at  $T_A = 25^{\circ}C$ .

**FIGURE 2-19:** HVOUT Closed-Loop Gain Distribution at  $T_A = 25^{\circ}$ C.

FIGURE 2-20:High Voltage FrequencyResponse: Signal vs Frequency ( $V_{PP} = 225V$ , $V_{CC} = 6.5V$ ,  $V_{LL} = 3.3V$ ,  $R_{BIAS} = 150 \ k\Omega$ ,  $V_{IN} = 0$ to 2.98V, Load = 0.22  $\mu$ F).

#### 2.3 **Power MOSFET**

FIGURE 2-21: Drain-Source On-State Resistance vs Junction Temperature (VG = 5V).

**FIGURE 2-22:**

**FIGURE 2-23:** Drain-Source On-State Resistance vs Junction Temperature (VG = 10V).

FIGURE 2-24: Capacitance vs Drain-Source Voltage.

### HV56020

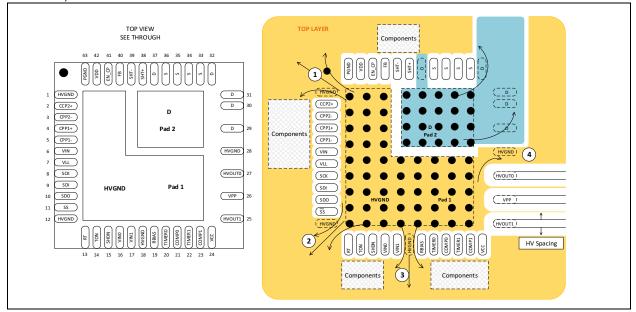

FIGURE 3-1:

VQFN 43-Lead 7 x 7 mm.

#### 3.1 Pin Description

The descriptions of the pins are listed in Table 3-1.

| TABLE 3-1: | PIN FUNCTION TABLE |

|------------|--------------------|

|------------|--------------------|

| PIN                   | Symbol              | Description                                      |

|-----------------------|---------------------|--------------------------------------------------|

| 1                     | HVGND               | High Voltage Ground                              |

| 2                     | CCP2+               | Charge Pump Storage Capacitor #2 Plus Terminal   |

| 3                     | CCP2-               | Charge Pump Storage Capacitor #2 Minus Terminal  |

| 4                     | CCP1+               | Charge Pump Storage Capacitor #1 Plus Terminal   |

| 5                     | CCP1-               | Charge Pump Storage Capacitor #1 Minus Terminal  |

| 6                     | V <sub>IN</sub>     | Input Voltage Supply                             |

| 7                     | V <sub>LL</sub>     | Logic Output Voltage Supply                      |

| 8                     | SCK                 | SPI Clock                                        |

| 9                     | SDI                 | SPI Data Input                                   |

| 10                    | SDO                 | SPI Data Output                                  |

| 11                    | SS                  | SPI Chip Select                                  |

| 12                    | HVGND               | High Voltage Ground                              |

| 13                    | RT                  | Frequency Adjustment Pin for DC-to-DC Controller |

| 14                    | TON                 | TON Timer for Pulse Width Modulation             |

| 15                    | SHDN                | Shutdown Output Pin                              |

| 16                    | V <sub>IN</sub> 0   | CH0 Amplifier Input                              |

| 17                    | V <sub>IN</sub> 1   | CH1 Amplifier Input                              |

| 18                    | HVGND               | High Voltage Ground                              |

| 19                    | R <sub>BIAS</sub>   | Bias Reference for High Voltage Amplifiers       |

| 20                    | Timer0              | Delay Timer 0                                    |

| 21                    | Comp0               | Comparator Output 0                              |

| 22                    | Timer1              | Delay Timer 1                                    |

| 23                    | Comp1               | Comparator Output 1                              |

| 24                    | V <sub>CC</sub>     | Low Voltage Amplifier Supply                     |

| 25                    | HV <sub>OUT</sub> 1 | CH1 High Voltage Amplifier Output                |

| 26                    | V <sub>PP</sub>     | High Voltage Amplifier Supply                    |

| 27                    | HV <sub>OUT</sub> 0 | CH0 High Voltage Amplifier Output                |

| 28                    | HVGND               | High Voltage Ground                              |

| 29,30,31,32,37, Pad 2 | D                   | Power MOSFET Drain                               |

| 33,34,35,36           | S                   | Power MOSFET Source                              |

| 38                    | SHT+                | Current Sense + Terminal                         |

| 39                    | SHT-                | Current Sense - Terminal                         |

| 40                    | FB                  | Power Supply Feedback Input                      |

| 41                    | EN_CP               | Charge Pump Enable Input Pin                     |

| 42                    | V <sub>DD</sub>     | Charge Pump Output Voltage                       |

| 43                    | PGND                | Power Ground                                     |

#### 3.2 Charge Pump Storage Capacitors (CPP2+, CPP2-, CPP1+, CPP1-)

The storage capacitors input pins are used for the internal charge pump to generate  $V_{DD}$ .  $V_{DD}$  is the required voltage source to operate all the circuitry in the DC-to-DC Controller and the HV Op Amps bias currents,  $V_{CC}$ . 2 µF capacitors are recommended for both storage capacitors, CPP1 and CPP2.

#### 3.3 Input Voltage Supply (VIN)

Input Voltage Supply pin for internal circuitry of the device and for the non-isolated flyback configuration. The device is intended for battery operated applications with a voltage range of 2.7V to 5.5V.

#### 3.4 Logic Voltage Supply Output Pin (V<sub>LL</sub>)

$V_{LL}$  is an internally generated 3.3V voltage source for the SPI interface.  $V_{LL}$  is an output pin and can be used to power the other family device, HV56022, that requires a 3.3V voltage source. A 1  $\mu F$  bypass capacitor is recommended to be connected at the  $V_{LL}$  output pin.

#### 3.5 SPI- Serial Clock (SCK)

Serial clock pin for the SPI interface.

#### 3.6 SPI- Serial Data Input (SDI)

Serial data input pin for the SPI interface.

#### 3.7 SPI- Serial Data Output (SDO)

Serial data output pin for the SPI interface.

#### 3.8 SPI- Serial Chip Select (SS)

Serial data chip select pin for the SPI interface.

#### 3.9 High Voltage Ground (HVGND)

Ground reference pins for the High Voltage Amplifiers.

#### 3.10 Power Ground (PGND)

Ground reference pin for the DC-to-DC converter, the internal Power MOSFET, and the short circuit sense resistor,  $R_{SHT}$ . The power ground separates the

DC-to-DC converter switching noise from the rest of the circuitry.

#### 3.11 Frequency Adjustment (RT)

Adjustment input pin for the DC-to-DC converter PWM switching frequency, fs. A 200 k $\Omega$  resistor will set the switching frequency to 400 kHz (typical).

fs = 1/((RT\*12 pF)+100 ns)

#### 3.12 Duty Cycle On Time (TON)

The On-Time input pin takes a voltage reference, VTON, to set the PWM (Pulse Width Modulation) duty cycle. TON voltage range is from  $0.25V_{TS}$  to  $0.8V_{TS}$  to generate a 25% to 80% duty cycle, respectively.

#### 3.13 Shutdown Output Pin (SHDN)

The Shutdown output pin is used to deactivate the other family device, HV56022 Dual High Voltage Amplifiers, when both devices are used in the same application. The HV Op Amps shutdown option is available at the RXB Register over the SPI interface; see Section 4.2.13 "SPI Control Registers" for more details.

# 3.14 High Voltage Amplifiers Inputs (V<sub>IN</sub>0, V<sub>IN</sub>1)

Input data signals for the High Voltage Operational Amplifiers.

#### 3.15 Amplifiers Bias Reference Pin (R<sub>BIAS</sub>)

High Voltage Amplifiers bias reference input pin. A 150 k $\Omega$  resistor will set the bias currents for a 124 Hz, –3 dB bandwidth for 225V sinusoidal waveforms driving 0.22  $\mu$ F capacitive loads.

#### 3.16 Output Voltage Comparator Output Pins (COMP0, COMP1)

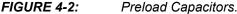

The internal voltage comparators monitor the input data signals,  $V_{IN}0, V_{IN}1$ , and the High Voltage Amplifiers' feedback signals for a short at the amplifiers' outputs. The comparators monitor for a 20% or greater voltage drop in the output against the input signal before reporting a short flag, COMP0,1 = 1 or 3.3V.

#### 3.17 Output Voltage Comparators Delay Timer Pins (Timer0, Timer1)

The output voltage comparators monitor the input data signals,  $V_{IN}0$ ,  $V_{IN}1$ , against the HV Op Amp feedback signals: if there is a heavy capacitive load, the HVOUT signals will slowly increase, causing the comparators to detect a false short. False triggering is avoided by adding a delay to the input signals of the comparators. A 1.5 nF capacitor will add a 1.6 ms delay time when  $R_{BIAS}$  is set to 150 k $\Omega$ .

**Time Delay** = 7.55\*R<sub>BIAS</sub>\*C (Timer)

#### 3.18 Low Voltage Supply Input Pin for High Voltage Amplifiers (V<sub>cc</sub>)

$V_{CC}$  is the low voltage supply input pin for the High Voltage Op Amps and has an operational voltage range of 6V to 7V.  $V_{CC}$  is intended to be biased from the internal charge pump converter output voltage,  $V_{DD}$ . A 2  $\mu F$  bypass capacitor is recommended to be added close to the  $V_{CC}$  pin.

# 3.19 High Voltage Amplifiers Outputs (HV<sub>OUT</sub>0, HV<sub>OUT</sub>1)

High Voltage Amplifiers Output channels.

#### 3.20 High Voltage Amplifiers Supply Input Pin (V<sub>PP</sub>)

Input power supply pin for the High Voltage Op Amps. V<sub>PP</sub> is generated by the flyback configuration formed by the internal power MOSFET, the DC-to-DC Controller, and the external transformer. The maximum operating voltage is 225V. A 0.1  $\mu$ F or higher bypass capacitor is recommended to be added close to the V<sub>PP</sub> pin.

#### 3.21 Power MOSFET Drain (D)

Drain pin connections for the internal Power MOSFET.

#### 3.22 **Power MOSFET Source (S)**

Source pin connections for the internal Power MOSFET.

#### 3.23 Current Sense Resistor Input Pins (SHT-, SHT+)

Current sense resistor input pins for the Short Circuit Protection circuitry in the DC-to-DC Controller.

#### 3.24 Power Supply Feedback Input Pin (FB)

Feedback input pin for the DC-to-DC Controller.

#### 3.25 Charge Pump Enable Input Pin (EN\_CP)

Internal Charge Pump enable control pin.

EN\_CP = '1' or 3.3V enables  $V_{DD}$ ; EN\_CP = '0' or 0.V disables  $V_{DD}$ .

#### 3.26 Charge Pump Output Voltage (V<sub>DD</sub>)

Charge pump output voltage source for the DC-to-DC internal circuitry and V<sub>CC</sub>. V<sub>DD</sub> is designed to supply voltage source for the HV56020 as well as for the HV56022, which is part of the same device family. A 10  $\mu$ F or greater capacitor is recommended for decoupling.

#### 4.0 FUNCTIONAL DESCRIPTION

The HV56020 is a Multi-Chip Module (MCM) driver solution designed for Haptic Applications. The IC consists of three devices: (1) Dual High Voltage Operational Amplifiers, (2) a DC-to-DC Converter Controller, and (3) a Power MOSFET.

The High Voltage Operational Amplifiers operate up to 225V and can source/sink 40 mA minimum peak currents. The amplifiers are designed for a –3 dB bandwidth of 124 Hz for 225V sinusoidal waveforms driving 0.22  $\mu F$  capacitive loads. In addition, the amplifiers are paired with output voltage comparators to monitor and report short circuit conditions.

The DC-to-DC Controller and the power MOSFET along with an external transformer generate the required voltage supply for the High Voltage Op Amps using a Non-Isolated Flyback configuration. The DC-to-DC Controller also includes many protection circuitries: Over and Undervoltage Protection, Short Circuit Protection (DC-to-DC), Power ON Reset, and a Temperature Sensor.

The power MOSFET is a 60V device with a 10 m $\Omega$  On resistance and a 14 nC gate charge. The MOSFET allows the flyback configuration to sustain a 400 kHz switching frequency.

FIGURE 4-1: Functional Block Diagram.

#### 4.1 High Voltage Operation Amplifiers

The High Voltage Operational Amplifiers operate up to 225V (unipolar) with 40 mA minimum source/sink peak current capabilities and are designed with a fixed 75V/V gain.

#### 4.1.1 BANDWIDTH

The amplifiers' bandwidth is controlled in part by the internal bias currents set by an external resistor, **R**<sub>BIAS</sub>. The internal bias currents can be increased by reducing R<sub>BIAS</sub> to achieve higher Bandwidth. Increasing the Bandwidth will lead to higher power consumption. A 150 k $\Omega$  R<sub>BIAS</sub> will set the bias currents for a 124 Hz,

-3~dB,~Bandwidth for 225V sinusoidal waveforms driving 0.22  $\mu\text{F}$  capacitive loads.

#### 4.1.2 STABILITY

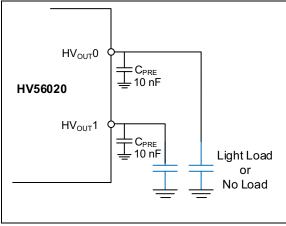

Amplifiers are designed to operate for a wide range of capacitive loads and to maintain stability when light or no loads are present. 10 nF preload capacitors,  $C_{PRE}$ , are recommended to be added in parallel with the outputs  $HV_{OUT}0$  and  $HV_{OUT}1$ . Figure 4-2 illustrates the application diagram using 10 nF preload capacitors.

#### 4.1.3 SHORT CIRCUIT DETECTION

Amplifiers are paired with voltage comparators for output short circuit detection. The Output Voltage Comparators, **COMP0** and **COMP1**, are a safety feature designed to check the voltage across the load (haptic actuator) during operation. Comparators monitor the Amplifiers' feedback signals against 80% of the input signals,  $V_{IN}0$  and  $V_{IN}1$ . If there is a short or failing load (drooping voltage) at the output, a flag ('1' or 3.3V) will be raised by the comparators for the MCU (controlling host).

Comparators are designed with internal voltage offset,  $V_{OFFSET}$  (~110 mV) and delay timer pins, Timer0 and Timer1, to prevent false triggering.

The internal voltage offsets are designed to avoid false triggering due to ground noise when input signals swing close to zero level.

Timer pins add delay compensation to the comparators' inputs,  $V_{IN}0$  and  $V_{IN}1$ , by using capacitors at the Timer0 and Timer1 pins. When input signals are step functions (for example square waves), the amplifiers' outputs will slowly charge, producing trapezoidal waveforms. If input signals are not delayed, amplifiers' feedback signals will appear as short when compared to the input signals. A 150 k $\Omega$  R<sub>BIAS</sub> and timer pins with 1.5 nF capacitors will provide a 1.6 ms delay. Figure 4-3 illustrates a false detection event when timer capacitors are not being used.

FIGURE 4-3: False Detection.

#### 4.1.4 SHUTDOWN MODE

The shutdown mode, **SHDN**, disables the internal bias current, allowing for power saving when the amplifiers are not operating. The shutdown mode is available in the RXB Register Bit 1, **SHDN**; see Section 4.2.13 "SPI Control Registers" for more details.

#### 4.2 DC-to-DC Controller

A Hysteretic Step-up DC-to-DC Controller is integrated in this driver IC to generate the high voltage rail,  $V_{PP}$ , required to power the High Voltage Amplifiers. The feedback input is a typical DC-to-DC feedback which monitors the feedback voltage from a resistor divider referenced to ground. When the sensing voltage is higher than the internal reference voltage,  $V_{REF}$ , it deactivates the pulse in the next cycle. When the sensing voltage is lower, it activates the pulse.

The DC-to-DC controller consists of a Charge Pump Regulator, PWM Controller, Oscillator Circuit, 3-Bit DAC for Voltage Reference, Overvoltage Protection, Short Circuit Protection, Temperature Sensor, Power-On Reset and a 16-bit Serial Peripheral Interface (SPI).

#### 4.2.1 CHARGE PUMP REGULATOR

The internal charge pump regulator runs at a fixed switching frequency to generate  $V_{DD}$ , a 6.5V voltage source with 15 mA supply current.  $V_{DD}$  is the voltage source required to drive the gate of the internal power MOSFET, the DC-to-DC circuitry, and the High Voltage Amplifiers bias currents,  $V_{CC}$ . The enable charge pump input pin, **EN\_CP**, turns ON the charge pump when it is High, and OFF when it is pulled Low or Open.  $V_{DD}$  is also designed to provide power for additional HV56022 devices ( $V_{CC}$ ).

#### 4.2.2 POWER-ON-RESET

The Power-on-Reset circuit ensures  $V_{DD}$  voltage has reached the operational mode, **VDD<sub>UVLO</sub>**, (4.5V typical) before the internal circuitry is turned ON. The Power-on-Reset circuit also prevents the internal circuitry from running in case  $V_{DD}$  voltage drops below the non-operational mode, VDD<sub>UVLO</sub> - **VDD<sub>HYST</sub>**.

#### 4.2.3 CLOCK GENERATION

The internal clock source is generated by an internal bias current set by an external resistor, **RT**. The frequency adjustment pin, RT, recommended range is from 200 k $\Omega$  to 400 k $\Omega$  to generate a 400 kHz to 200 kHz clock source respectively.

#### fs = 1/((RT\*12pF)+100ns)

#### 4.2.4 GATE DRIVER

The gate driver is designed to drive the internal power MOSFET transistor to the maximum switching frequency  $\mathbf{f}_{s,MAX}$ . The gate driver swings between  $V_{DD}$  and ground to drive the power MOSFET with fast rise and fall transition times.

#### 4.2.5 VOLTAGE REFERENCE

The voltage reference sets the DC-to-DC output voltage,  $V_{PP}$ , when the IC is configured in a flyback configuration (suggested topology). The voltage

reference,  $V_{REF}$ , is specified by a 3-Bit code word and is set over the 16-Bit SPI interface (see Section 4.2.12 "SPI Serial Interface Mode 0" for more details). The 3-Bit code word allows for 8 different voltage levels starting with 000 equivalent to 67.5V, and 111 equivalent to 225V. Table 4-1 shows the complete operational values. The code word setting corresponds to a percentage of the V<sub>REF</sub> that is set to be 1.188V. The minimum setting is 000, which corresponds to 30% of V<sub>REF</sub>, and 111 to 100%. The maximum recommended operating V<sub>PP</sub> voltage is 225V. To set V<sub>PP</sub> to zero, the device needs to be disabled by the EN Bit (EN = '0') or set in a standby mode by STD\_BY Bit (STD\_BY = '1', EN = '1').

### TABLE 4-1:3-BIT DAC TO OUTPUT<br/>VOLTAGE

| DAC <7:5> | V <sub>REF</sub> (%) | V <sub>PP</sub> (V) |

|-----------|----------------------|---------------------|

| 000       | 30                   | 67.5                |

| 001       | 40                   | 90                  |

| 010       | 50                   | 112.5               |

| 011       | 60                   | 135                 |

| 100       | 70                   | 157.5               |

| 101       | 80                   | 180                 |

| 110       | 90                   | 202.5               |

| 111       | 100                  | 225                 |

#### 4.2.6 OVERVOLTAGE PROTECTION

The Overvoltage Protection ( $OVP_R$ ) circuitry monitors the DC-to-DC Controller output voltage,  $V_{PP}$ , for an overvoltage condition by checking the feedback voltage, VFB. If the output voltage surpasses 8% of maximum  $V_{PP}$  (225V), the Overvoltage protection circuitry will shut down the DC-to-DC Controller to prevent damage to the IC. In case of an Overvoltage condition there will also be an Overvoltage flag, OVER, reported in the TXB Register.

#### 4.2.7 SHORT CIRCUIT PROTECTION

A short circuit at the output of the flyback transformer may cause damage to the power supply circuit and to the application system. A short circuit protection scheme is implemented in the DC-to-DC controller by monitoring the power MOSFET Source-to-Ground current with a sense resistor,  $\mathbf{R}_{SHT}$ . Short circuit is indirectly detected by sensing the inductor's saturation.

The presence of a higher than designed current through  $R_{SHT}$  will cause the voltage drop across the sense resistor to be greater than the 50 mV threshold offset voltage, **SH<sub>OFF</sub>**, causing the short circuit condition, suspending DC-to-DC operation, and raising a **SHORT** flag in the TXB Register. The short circuit protection circuit can be enabled or disabled by the **SHT\_EN** Bit in the RXB Register.

#### 4.2.8 STANDBY MODE (STD\_BY)

The standby mode sets the HV56020 into power saving mode when there are no actuations required at the High Voltage Outputs (HVOUTs), by disabling the DC-to-DC converter output,  $V_{PP}$ . The standby bit, **STD\_BY**, is available at the RXB Register Bit 3. The standby mode stops PWM pulses for power MOSFET and keeps the rest of the device running until the full operational mode is enabled, EN = '1' and STD\_BY = '0'.

#### 4.2.9 ENABLE CONTROL (EN)

Enable control input bit, **EN**, for the DC-to-DC Controller is available in the RXB Register Bit 2. In disabled mode, EN = '0', all internal circuitry except the wake-up circuit is turned off. The wake-up circuit restores the internal circuitry to normal operation when the enable bit is set high, EN = '1'.

#### 4.2.10 TEMPERATURE SENSOR

The Temperature Sensor helps to ensure that the maximum operational temperature of the IC, +150°C, is not exceeded. If the temperature of the device reaches the threshold temperature range,  $T_{TH}$ , the **TEMP** flag Bit will be set to '1' in the TXB Register. The Temperature Sensor has a +25°C hysteresis that

resets the TEMP Bit flags to '0' once temperature drops below the hysteresis threshold temperature, T<sub>THHYST</sub>. The Temperature Sensor is only an indicator and will NOT perform any further action to the DC-to-DC or HV Op Amps.

#### 4.2.11 TON GENERATION

TON input pin takes a voltage reference to set the duty cycle, **TON**, of the Pulse Width Modulation (PWM) cycles for the internal gate driver. The voltage range is  $0.25V_{TS}$  to  $0.8V_{TS}$  to generate 25% to 80% duty cycle respectively, where **V**<sub>TS</sub> is typically 3.5V.

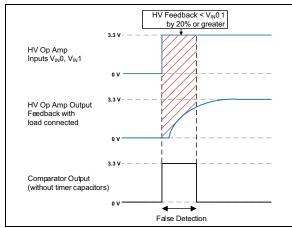

To have a soft start-up, low input peak currents, in the flyback topology it is recommended to start increasing the PWM duty cycle slowly until the topology has reached the designed PWM duty cycle, TON. The slow increase in the TON is achieved by slowly increasing the **VTON** voltage reference. The diagram in Figure 4-4 shows two cases: when no soft start-up and when soft start-up is implemented using VTON. A 10 ms time constant is recommended for soft start-up.

Toggling EN or STBY Bit will reset the internal, VTON, voltage reference for PWM duty cycle. A TON reset ensures a soft start-up mode when EN or STBY are used multiple times during operation.

FIGURE 4-4:

TON Soft Start-Up Implementation.

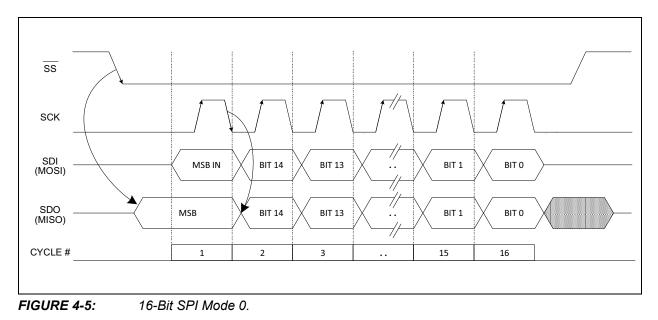

#### 4.2.12 SPI SERIAL INTERFACE MODE 0

The HV56020 uses a 16-bit Serial Peripheral Interface (SPI) module to communicate with the host controller. The serial synchronous interface is used to control and monitor the DC-to-DC Step-Up converter. The SPI module is designed to be compatible with operation Mode 0.

In Mode 0, data transmission starts when  $\overline{SS}$  goes Low, causing the Slave to output the Most Significant Bit (MSB) data in to the SDO (MISO) pin. Data transfer between Master and Slave takes place during the rising edge of the clock (SCK), which is considered to be idle when it is Low. This mode of operation requires data for Master and Slave to be present in the line (MISO/MOSI) before the rising edge of the clock (defining SDI to SCK setup time). Data are pushed out of the SDO (MISO) pin during the falling edge of the clock. After the first transaction, 16-Bit data exchange, Master writes the latest data (Dn) to Slave, while Slave passes its previous (Dn-1) stored data to the Master. Figure 4-5 illustrates the 16-bit operation mode.

#### 4.2.13 SPI CONTROL REGISTERS

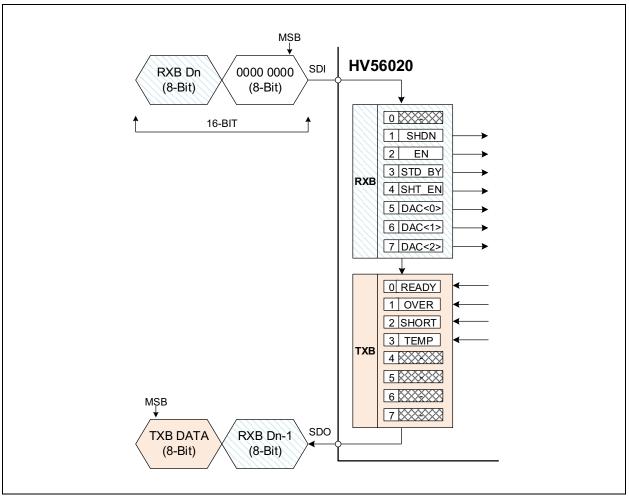

The 16-Bit SPI Interface module consists of two 8-Bit registers, a Receive Register, RXB, and a Transmit Register, TXB.

The Receive Register (**RXB**) is where the control settings for the DC-to-DC Controller are specified, for example, the Step-Up voltage level (V<sub>PP</sub>), Short Circuit Detection Enable (SHT\_EN), Standby (STD\_BY), Enable (EN) and Shutdown (SHDN) modes of operation.

The Transmit Register (**TXB**) is used by the DC-to-DC converter to report the current operation state by using various status flags like Overtemperature (TEMP),

Short Circuit (SHORT), Overvoltage Detection (OVER) at  $V_{PP}$ , and whether the Step-Up voltage ( $V_{PP}$ ) is ready for operation (READY).

To operate the DC-to-DC controller, only 8 bits of data are required, and correspond to the lower byte. The upper byte is a place holder used by the TXB register to report the status of the DC-to-DC controller, see Figure 4-6. The Most Significant Bit (MSB) of data is written (to SDI/MOSI pin) and read (pushed out of SDO/MISO pin) first.

FIGURE 4-6:

SPI Registers: RXB, TXB.

#### 4.2.13.1 RECEIVE REGISTER (RXB)

|                | R-0                                                                                                                                                                | R-0                                                                                                                                                     | R-0                                                     | R-0                        | R-0                | R-0               | U-0          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------|--------------------|-------------------|--------------|

| R-0            | DAC<2:0>                                                                                                                                                           | 14-0                                                                                                                                                    | SHT EN                                                  | STD BY                     | EN                 | SHDN              |              |

| bit 7          | DA0 - 2.02                                                                                                                                                         |                                                                                                                                                         |                                                         | 010_01                     |                    | OTDIN             | bit (        |

|                |                                                                                                                                                                    |                                                                                                                                                         |                                                         |                            |                    |                   | bit (        |

| Legend:        |                                                                                                                                                                    |                                                                                                                                                         |                                                         |                            |                    |                   |              |

| R = Readabl    | le bit                                                                                                                                                             | W = Writable                                                                                                                                            | bit                                                     | U = Unimplen               | nented bit, read   | as '0'            |              |

| -n = Value at  | t POR                                                                                                                                                              | '1' = Bit is set                                                                                                                                        |                                                         | '0' = Bit is clea          | ared               | x = Bit is unkn   | own          |

|                |                                                                                                                                                                    |                                                                                                                                                         |                                                         |                            |                    |                   |              |

| bit 7-5        | DAC[2:0]: VF                                                                                                                                                       | REF 3-Bit Code                                                                                                                                          | Word                                                    |                            |                    |                   |              |

|                | Bits DAC[7:5                                                                                                                                                       | i] set the DC-t                                                                                                                                         | o-DC output                                             | voltage, V <sub>PP</sub> . | Table 4-3 prese    | nts the corresp   | onding cod   |

|                | word values f                                                                                                                                                      | or the desired                                                                                                                                          | V <sub>PP</sub> voltage.                                |                            |                    |                   |              |

| bit 4          | SHT_EN: She                                                                                                                                                        | ort Circuit Prote                                                                                                                                       | ection Enable                                           |                            |                    |                   |              |

|                |                                                                                                                                                                    |                                                                                                                                                         |                                                         |                            | to-DC is operat    |                   |              |

|                |                                                                                                                                                                    |                                                                                                                                                         |                                                         | ,                          | T Flag will be rai | sed and reporte   | ed on the TX |

|                | •                                                                                                                                                                  | and DC-to-DC                                                                                                                                            |                                                         |                            | SHORT Flag is      | roported in the - | TVP Dogiato  |

|                |                                                                                                                                                                    |                                                                                                                                                         |                                                         |                            | the Step-Up cor    |                   |              |

|                | be operating                                                                                                                                                       | in a CCM mod                                                                                                                                            |                                                         |                            | on SHT+ and S      |                   |              |

|                | on TXB Regis                                                                                                                                                       | ster Bit 2.                                                                                                                                             |                                                         |                            |                    |                   | Ų            |

|                | Note: if SHT_EN = 0, state of SHORT = 0.                                                                                                                           |                                                                                                                                                         |                                                         |                            |                    |                   |              |

|                | _                                                                                                                                                                  | EN = 0, state                                                                                                                                           | of SHORT = 0                                            |                            |                    |                   | J            |

| bit 3          | STD_BY: Sta                                                                                                                                                        | -                                                                                                                                                       | of SHORT = 0                                            |                            |                    |                   | J            |

| bit 3          | <b>STD_BY:</b> Sta<br>1 = Disables                                                                                                                                 | ndby Mode                                                                                                                                               | converter outp                                          |                            | rest of the circu  | itry keeps runn   | -            |

| bit 3<br>bit 2 | STD_BY: Sta<br>1 = Disables<br>0 = Standby r                                                                                                                       | andby Mode<br>the DC-to-DC of                                                                                                                           | converter outp                                          |                            | rest of the circu  | iitry keeps runn  | -            |

|                | <b>STD_BY:</b> Sta<br>1 = Disables<br>0 = Standby (<br><b>EN:</b> DC-to-D(<br>1 = DC-to-D(                                                                         | indby Mode<br>the DC-to-DC (<br>mode disabled.<br>C Step-Up Con<br>C enabled.                                                                           | converter outp                                          |                            | rest of the circu  | iitry keeps runn  | -            |

| bit 2          | <b>STD_BY:</b> Sta<br>1 = Disables<br>0 = Standby r<br><b>EN:</b> DC-to-D(<br>1 = DC-to-D(<br>0 = DC-to-D(                                                         | indby Mode<br>the DC-to-DC (<br>mode disabled.<br>C Step-Up Con<br>C enabled.<br>C disabled.                                                            | converter outp<br>verter Enable                         | ut voltage, the            | rest of the circu  | iitry keeps runn  | -            |

| bit 2          | <b>STD_BY:</b> Sta<br>1 = Disables<br>0 = Standby n<br><b>EN:</b> DC-to-D(<br>1 = DC-to-D(<br>0 = DC-to-D(<br><b>SHDN:</b> High <sup>2</sup>                       | indby Mode<br>the DC-to-DC (<br>mode disabled.<br>C Step-Up Con<br>C enabled.<br>C disabled.<br>Voltage Amplifi                                         | converter outp<br>verter Enable<br>ers Shut Dow         | ut voltage, the            | rest of the circu  | iitry keeps runn  | -            |

| bit 2          | <b>STD_BY:</b> Sta<br>1 = Disables<br>0 = Standby (<br><b>EN:</b> DC-to-D(<br>1 = DC-to-D(<br>0 = DC-to-D(<br><b>SHDN:</b> High (<br>1 = Disables                  | indby Mode<br>the DC-to-DC (<br>mode disabled.<br>C Step-Up Con<br>C enabled.<br>C disabled.<br>Voltage Amplifi<br>the HV Op amp                        | converter outp<br>verter Enable<br>ers Shut Down        | ut voltage, the            | rest of the circu  | iitry keeps runn  | -            |

| bit 2<br>bit 1 | <b>STD_BY:</b> Sta<br>1 = Disables<br>0 = Standby r<br><b>EN:</b> DC-to-D0<br>1 = DC-to-D0<br>0 = DC-to-D0<br><b>SHDN:</b> High 1<br>1 = Disables<br>0 = Enables t | indby Mode<br>the DC-to-DC of<br>mode disabled.<br>C Step-Up Con<br>C enabled.<br>C disabled.<br>Voltage Amplifi<br>the HV Op amp<br>he HV Op amp       | converter outp<br>verter Enable<br>ers Shut Down<br>os. | ut voltage, the            | rest of the circu  | iitry keeps runn  | -            |

|                | <b>STD_BY:</b> Sta<br>1 = Disables<br>0 = Standby r<br><b>EN:</b> DC-to-D0<br>1 = DC-to-D0<br>0 = DC-to-D0<br><b>SHDN:</b> High 1<br>1 = Disables<br>0 = Enables t | the DC-to-DC of<br>mode disabled.<br>C Step-Up Con<br>C enabled.<br>C disabled.<br>Voltage Amplifit<br>the HV Op amp<br>he HV Op amp<br>ted: Read as of | converter outp<br>verter Enable<br>ers Shut Down<br>os. | ut voltage, the            | rest of the circu  | iitry keeps runn  |              |

| V <sub>REF</sub>      | V <sub>PP</sub> (V)                                                                                                                                                        |  |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0.30 V <sub>REF</sub> | 67.5                                                                                                                                                                       |  |  |  |  |  |

| 0.40 V <sub>REF</sub> | 90                                                                                                                                                                         |  |  |  |  |  |

| 0.50 V <sub>REF</sub> | 112.5                                                                                                                                                                      |  |  |  |  |  |

| 0.60 V <sub>REF</sub> | 135                                                                                                                                                                        |  |  |  |  |  |

| 0.70 V <sub>REF</sub> | 157.5                                                                                                                                                                      |  |  |  |  |  |

| 0.80 V <sub>REF</sub> | 180                                                                                                                                                                        |  |  |  |  |  |

| 0.90 V <sub>REF</sub> | 202.5                                                                                                                                                                      |  |  |  |  |  |

| 1.00 V <sub>REF</sub> | 225                                                                                                                                                                        |  |  |  |  |  |

|                       | V <sub>REF</sub> 0.30 V <sub>REF</sub> 0.40 V <sub>REF</sub> 0.50 V <sub>REF</sub> 0.60 V <sub>REF</sub> 0.70 V <sub>REF</sub> 0.80 V <sub>REF</sub> 0.90 V <sub>REF</sub> |  |  |  |  |  |

#### TABLE 4-3:CODE WORD LEVELS

### HV56020

#### 4.2.13.2 TRANSMIT REGISTER (TXB)

| TABLE 4-4    | : TRANS                                                                                                                              | MIT REGISTER                                                                                    | R (TXB) |                  |                  |                    |       |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------|------------------|------------------|--------------------|-------|--|--|--|--|--|

| R-0          | R-0                                                                                                                                  | R-0                                                                                             | R-0     | W-0              | W-0              | W-0                | W-0   |  |  |  |  |  |

|              |                                                                                                                                      | —                                                                                               |         | TEMP             | SHORT            | OVER               | READY |  |  |  |  |  |

| bit 7        |                                                                                                                                      |                                                                                                 |         |                  |                  |                    | bit ( |  |  |  |  |  |

| Legend:      |                                                                                                                                      |                                                                                                 |         |                  |                  |                    |       |  |  |  |  |  |

| R = Readal   | ole bit                                                                                                                              | W = Writable                                                                                    | e bit   | U = Unimpler     | mented bit, read | d as '0'           |       |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                               | '1' = Bit is se                                                                                 | t       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |  |  |  |

| bit 7-4      | Unimplem                                                                                                                             | nented: Read as                                                                                 | 0       |                  |                  |                    |       |  |  |  |  |  |

| bit 3        |                                                                                                                                      | for future use.<br>mperature Senso                                                              | or Flag |                  |                  |                    |       |  |  |  |  |  |

|              | 1 = Junction temperature in the device has reached +125 °C to +150 °C.                                                               |                                                                                                 |         |                  |                  |                    |       |  |  |  |  |  |

|              |                                                                                                                                      | 0 = Junction temperature in the device is within the recommended operating range.               |         |                  |                  |                    |       |  |  |  |  |  |

|              |                                                                                                                                      | Note: The temperature sensor has a +25°C hysteresis. This is only an indicator flag and will no |         |                  |                  |                    |       |  |  |  |  |  |

|              | perform ar                                                                                                                           | perform any actions to the DC-to-DC Controller or HV Amplifiers.                                |         |                  |                  |                    |       |  |  |  |  |  |

| bit 2        | SHORT: S                                                                                                                             | SHORT: Short Circuit Flag                                                                       |         |                  |                  |                    |       |  |  |  |  |  |

|              | <ul> <li>1 = Short Circuit detected, the DC-to-DC Controller suspends operation.</li> <li>0 = Short Circuit NOT detected.</li> </ul> |                                                                                                 |         |                  |                  |                    |       |  |  |  |  |  |

|              | Short Circuit Case:                                                                                                                  |                                                                                                 |         |                  |                  |                    |       |  |  |  |  |  |