# HV9912

# Switch-Mode LED Driver IC with High Current Accuracy and Hiccup Mode Protection

#### **Features**

- · Switch-mode Controller for Single-switch Drivers:

- Buck

- Boost

- Buck-boost

- SEPIC

- · Works with High-side Current Sensors

- · Closed-loop Control of Output Current

- High Pulse-Width Modulation (PWM) Dimming Ratio

- Internal 90V Linear Regulator (can be extended using external Zener Diodes)

- Internal 2% Voltage Reference (0°C < T<sub>A</sub> < 85°C)</li>

- Constant Frequency or Constant Off-time Operation

- · Programmable Slope Compensation

- · Linear and PWM Dimming

- +0.2A/–0.4A Gate Driver

- Hiccup Mode Protection for both Short-circuit and Open-circuit Conditions

- · Output Overvoltage Protection

- · Synchronization Capability

- · Pin Compatible with HV9911

#### **Applications**

- · RGB Backlight Applications

- · General LED Lighting Applications

- Battery-powered LED Lamps

#### **General Description**

HV9912 is an LED driver IC designed to control single-switch PWM converters (buck, buck-boost and SEPIC) in a Constant Frequency or Constant Off-time mode. The controller uses a peak Current Mode control scheme with programmable slope compensation and includes an internal transconductance amplifier to control the output current in closed loop, enabling high output current accuracy. In the case of buck and buck-boost converters, the output current can be sensed using a high-side current sensor like the HV7800. In the Constant Frequency mode, multiple HV9912 ICs can be synchronized with each other or with an external clock, using the SYNC pin. Programmable MOSFET current limit enables current limiting during Input Undervoltage and Output Overload conditions. The IC also includes a 0.2A source and 0.4A sink gate driver that makes the HV9912 suitable for high-power applications. An internal 90V linear regulator powers the IC, eliminating the need for a separate power supply for the IC. The IC also provides a FAULT output, which can be used to disconnect the LEDs in case of a Fault condition using an external disconnect FET. HV9912 also provides a TTL-compatible, low-frequency PWM dimming input that can accept an external control signal with a duty ratio of 0-100% and a frequency of up to a few kilohertz. The HV9912 includes hiccup protection from both short and open circuits, with automatic recovery after the Fault condition is cleared.

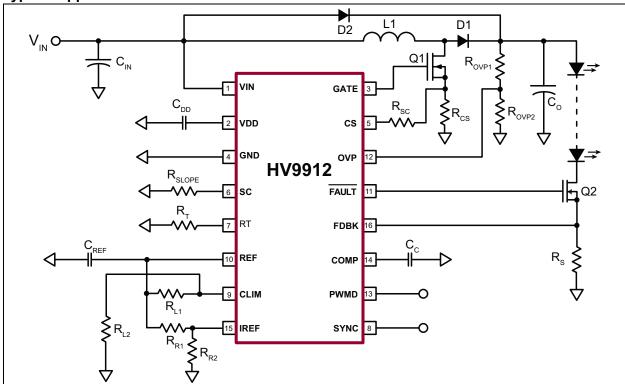

The HV9912 is a pin-compatible replacement for HV9911. It can be used with existing HV9911 designs, which have input voltages of less than 90V, by changing  $R_{OVP1}$ ,  $R_{OVP}$  and  $R_{T}$ .

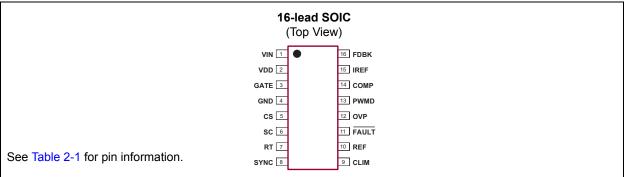

#### Package Type

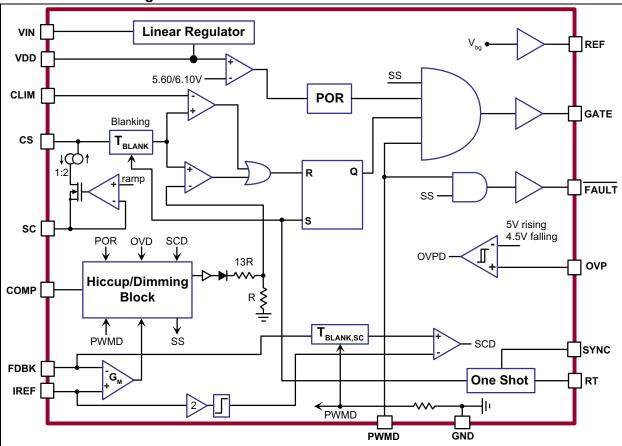

# **Functional Block Diagram**

# **Typical Application Circuit**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| –0.5 to +100V                  |

|--------------------------------|

| –0.3V to +13.5V                |

| –0.3V to V <sub>DD</sub> +0.3V |

| 1200 mW                        |

| –40°C to +125°C                |

| –65°C to +150°C                |

|                                |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

| <b>Electrical Specifications</b> : $T_A = 25^{\circ}C$ and $V_{IN} = 12V$ unless otherwise specified. |                      |        |      |       |          |                                                                                                                                         |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------------|--------|------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameters                                                                                            | Sym.                 | Min.   | Тур. | Max.  | Units    | Conditions                                                                                                                              |  |  |  |  |

| INPUT                                                                                                 |                      |        |      |       |          |                                                                                                                                         |  |  |  |  |

| Input DC Supply Voltage Range                                                                         | V <sub>INDC</sub>    | Note 1 | 1    | 90    | <b>V</b> | DC input voltage (Note 2)                                                                                                               |  |  |  |  |

| Shutdown Mode Supply Current                                                                          | I <sub>INSD</sub>    | _      |      | 1.5   | mA       | PWMD connected to GND (Note 2)                                                                                                          |  |  |  |  |

| INTERNAL REGULATOR                                                                                    |                      |        |      |       |          |                                                                                                                                         |  |  |  |  |

| Internally Regulated Voltage                                                                          | V <sub>DD</sub>      | 7.25   | 7.75 | 8.25  | <b>V</b> | V <sub>IN</sub> = 9V–90V; PWMD connected to GND ( <b>Note 2</b> )                                                                       |  |  |  |  |

| V <sub>DD</sub> Undervoltage Lockout<br>Threshold                                                     | UVLO <sub>RISE</sub> | 6.5    |      | 7     | >        | V <sub>DD</sub> rising                                                                                                                  |  |  |  |  |

| V <sub>DD</sub> Undervoltage Lockout<br>Hysteresis                                                    | UVLO <sub>HYST</sub> | _      | 500  | _     | mV       | V <sub>DD</sub> falling                                                                                                                 |  |  |  |  |

| REFERENCE                                                                                             |                      |        |      |       |          |                                                                                                                                         |  |  |  |  |

| REF Pin Voltage                                                                                       | $V_REF$              | 1.225  | 1.25 | 1.285 | ٧        | REF bypassed with a 0.1 $\mu$ F capacitor to GND; I <sub>REF</sub> = 0; PWMD = GND; 0°C < T <sub>A</sub> < +85°C                        |  |  |  |  |

|                                                                                                       |                      | 1.225  | 1.25 | 1.29  |          | REF bypassed with a 0.1 $\mu$ F capacitor to GND; I <sub>REF</sub> = 0; PWMD = GND; $-40^{\circ}$ C < T <sub>A</sub> < 125 $^{\circ}$ C |  |  |  |  |

| Line Regulation of Reference Voltage                                                                  | V <sub>REFLINE</sub> | 0      | _    | 20    | mV       | REF bypassed with a 0.1 $\mu$ F capacitor to GND; I <sub>REF</sub> = 0; V <sub>DD</sub> = 7.25V–12V; PWMD = GND                         |  |  |  |  |

- Note 1: See Section 3.3 "Minimum Input Voltage at VIN Pin" for the minimum input voltage.

- 2: The specifications which apply over the full operating temperature range at  $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$  are guaranteed by design and characterization.

- 3: For design guidance only

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| Electrical Specifications: T <sub>A</sub> = 25°C and V <sub>IN</sub> = 12V unless otherwise specified. |                         |            |      |      |          |                                                                                                                                                                                                  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-------------------------|------------|------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameters                                                                                             | Sym.                    | Min.       | Тур. | Max. | Units    | Conditions                                                                                                                                                                                       |  |  |  |  |

| Load Regulation of Reference<br>Voltage                                                                | V <sub>REFLOAD</sub>    | 0          | _    | 10   | mV       | REF bypassed with a 0.1 $\mu$ F capacitor to GND;<br>$I_{REF} = 0 \ \mu$ A-500 $\mu$ A;<br>PWMD = GND                                                                                            |  |  |  |  |

| PWM DIMMING                                                                                            |                         |            |      |      |          |                                                                                                                                                                                                  |  |  |  |  |

| PWMD Input Low Voltage                                                                                 | V <sub>PWMD(LO)</sub>   | _          | _    | 0.8  | V        | Note 2                                                                                                                                                                                           |  |  |  |  |

| PWMD Input High Voltage                                                                                | V <sub>PWMD(HI)</sub>   | 2          | _    | _    | V        | Note 2                                                                                                                                                                                           |  |  |  |  |

| PWMD Pull-down Resistance                                                                              | R <sub>PWMD</sub>       | 50         | 100  | 150  | kΩ       | V <sub>PWMD</sub> = 5V                                                                                                                                                                           |  |  |  |  |

| GATE                                                                                                   |                         |            |      |      |          |                                                                                                                                                                                                  |  |  |  |  |

| GATE Short-circuit Current                                                                             | I <sub>SOURCE</sub>     | 0.2        |      |      | Α        | V <sub>GATE</sub> = 0V                                                                                                                                                                           |  |  |  |  |

| GATE Sinking Current                                                                                   | I <sub>SINK</sub>       | 0.4        |      |      | Α        | $V_{GATE} = V_{DD}$                                                                                                                                                                              |  |  |  |  |

| GATE Output Rise Time                                                                                  | T <sub>RISE</sub>       | _          | 50   | 85   | ns       | C <sub>GATE</sub> = 1 nF                                                                                                                                                                         |  |  |  |  |

| GATE Output Fall Time                                                                                  | T <sub>FALL</sub>       | _          | 25   | 45   | ns       | C <sub>GATE</sub> = 1 nF                                                                                                                                                                         |  |  |  |  |

| OVERVOLTAGE PROTECTION                                                                                 |                         |            |      |      |          |                                                                                                                                                                                                  |  |  |  |  |

| Overvoltage Rising Trip Point                                                                          | V <sub>OVP,RISING</sub> | 4.75       | 5    | 5.25 | V        | OVP rising                                                                                                                                                                                       |  |  |  |  |

| Overvoltage Hysteresis                                                                                 | V <sub>OVP,HYST</sub>   | _          | 0.5  | _    | V        | OVP falling                                                                                                                                                                                      |  |  |  |  |

| CURRENT SENSE                                                                                          | ,                       |            |      |      |          |                                                                                                                                                                                                  |  |  |  |  |

| Landing Edge Disabing                                                                                  | T <sub>BLANK</sub>      | 100        |      | 280  | ns       | 0°C < T <sub>A</sub> < +85°C                                                                                                                                                                     |  |  |  |  |

| Leading Edge Blanking                                                                                  |                         | 100        | _    | 330  |          | -40°C < T <sub>A</sub> < +125°C                                                                                                                                                                  |  |  |  |  |

| Delay to Output of C <sub>OMP</sub> Comparator                                                         | T <sub>DELAY1</sub>     | _          | _    | 200  | ns       | $\begin{aligned} &COMP = V_{DD};  C_{LIM} = REF; \\ &C_{SENSE} = 0 \; mV \; to \; 600 \; mV \\ &(step \; up) \end{aligned}$                                                                      |  |  |  |  |

| Delay to Output of C <sub>LIMIT</sub> Comparator                                                       | T <sub>DELAY2</sub>     | _          | _    | 200  | ns       | $\begin{aligned} &\text{COMP} = \text{V}_{\text{DD}}; \text{ C}_{\text{LIM}} = 300 \text{ mV}; \\ &\text{C}_{\text{SENSE}} = 0 \text{ mV to } 400 \text{ mV} \\ &\text{(step up)} \end{aligned}$ |  |  |  |  |

| Comparator Offset Voltage                                                                              | V <sub>OFFSET</sub>     | -10        |      | 10   | mV       |                                                                                                                                                                                                  |  |  |  |  |

| INTERNAL TRANSCONDUCTANCE                                                                              |                         |            |      |      |          |                                                                                                                                                                                                  |  |  |  |  |

| Gain Bandwidth Product                                                                                 | GBW                     | _          | 1    | _    | MHz      | 75 pF capacitance at OP pin (Note 3)                                                                                                                                                             |  |  |  |  |

| Open-loop DC Gain                                                                                      | $A_{V}$                 | 60         |      |      | dB       | Output open                                                                                                                                                                                      |  |  |  |  |

| Input Common Mode Range                                                                                | V <sub>CM</sub>         | -0.3       | _    | 3    | <b>V</b> | Note 3                                                                                                                                                                                           |  |  |  |  |

| Output Voltage Range                                                                                   | V <sub>O</sub>          | 0.7        | _    | 6.75 | V        | Note 3                                                                                                                                                                                           |  |  |  |  |

| Transconductance                                                                                       | 9 <sub>M</sub>          | 450        | 550  | 650  | μΑ/V     |                                                                                                                                                                                                  |  |  |  |  |

| Input Offset Voltage                                                                                   | V <sub>OFFSET</sub>     | <b>-</b> 5 | _    | 5    | mV       |                                                                                                                                                                                                  |  |  |  |  |

| Input Bias Current                                                                                     | I <sub>BIAS</sub>       | _          | 0.5  | 1    | nA       | Note 3                                                                                                                                                                                           |  |  |  |  |

| OSCILLATOR                                                                                             |                         |            |      |      |          |                                                                                                                                                                                                  |  |  |  |  |

| Ossillator Fraguencii                                                                                  | f <sub>OSC1</sub>       | 99         | 106  | 118  | kHz      | $R_T = 500 \text{ k}\Omega \text{ (Note 2)}$                                                                                                                                                     |  |  |  |  |

| Oscillator Frequency                                                                                   | f <sub>OSC2</sub>       | 510        | 580  | 650  | kHz      | $R_T = 96 \text{ k}\Omega \text{ (Note 2)}$                                                                                                                                                      |  |  |  |  |

| Maximum Duty Cycle                                                                                     | D <sub>MAX</sub>        | 87         | _    | 93   | %        |                                                                                                                                                                                                  |  |  |  |  |

Note 1: See Section 3.3 "Minimum Input Voltage at VIN Pin" for the minimum input voltage.

3: For design guidance only

<sup>2:</sup> The specifications which apply over the full operating temperature range at  $-40^{\circ}$ C <  $T_A$  < +85°C are guaranteed by design and characterization.

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| <b>Electrical Specifications</b> : $T_A = 25$ °C and $V_{IN} = 12$ V unless otherwise specified. |                         |       |      |      |       |                                                                                                                         |  |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------|-------|------|------|-------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameters                                                                                       | Sym.                    | Min.  | Тур. | Max. | Units | Conditions                                                                                                              |  |  |  |

| SYNC Input High                                                                                  | V <sub>SYNCH</sub>      | 2     | _    | _    | V     |                                                                                                                         |  |  |  |

| SYNC Input Low                                                                                   | V <sub>SYNCL</sub>      | _     | _    | 0.8  | V     |                                                                                                                         |  |  |  |

| SYNC Output Current                                                                              | I <sub>OUTSYNC</sub>    | _     | 18   | _    | μΑ    |                                                                                                                         |  |  |  |

| OUTPUT SHORT-CIRCUIT                                                                             |                         |       |      |      |       |                                                                                                                         |  |  |  |

| Gain for Short-circuit Comparator                                                                | G <sub>SC</sub>         | 1.9   | 2    | 2.1  | V     |                                                                                                                         |  |  |  |

| Minimum Output Voltage of the Gain                                                               | V <sub>OMIN</sub>       | 0.125 | _    | 0.25 | V     | 0°C < T <sub>A</sub> < +85°C;<br>I <sub>REF</sub> = GND                                                                 |  |  |  |

| Stage                                                                                            |                         | 0.125 | _    | 0.26 | V     | -40°C < T <sub>A</sub> < +125°C;<br>I <sub>REF</sub> = GND                                                              |  |  |  |

| Propagation Time for Short-circuit Detection                                                     | T <sub>OFF</sub>        | _     | _    | 250  | ns    | PWMD = V <sub>DD</sub> ; I <sub>REF</sub> = 400 mA;<br>FDBK step from<br>0 mV to 900 mV; FAULT goes<br>from high to low |  |  |  |

| Fault Output Rise Time                                                                           | T <sub>RISE,FAULT</sub> |       | _    | 300  | ns    | 330 pF capacitor at FAULT pin                                                                                           |  |  |  |

| Fault Output Fall Time                                                                           | T <sub>FALL,FAULT</sub> |       | _    | 300  | ns    | 330 pF capacitor at FAULT pin                                                                                           |  |  |  |

| Blanking Time                                                                                    | T <sub>BLANK,SC</sub>   | 480   | _    | 900  | ns    |                                                                                                                         |  |  |  |

| Current Source at COMP Pin used for Hiccup Mode Protection                                       | I <sub>HICCUP</sub>     |       | 5    | _    | μA    |                                                                                                                         |  |  |  |

| SLOPE COMPENSATION                                                                               |                         |       |      |      |       |                                                                                                                         |  |  |  |

| Current Sourced Out of SC Pin                                                                    | I <sub>SLOPE</sub>      | 0     |      | 100  | μA    | Note 2                                                                                                                  |  |  |  |

| Internal Current Mirror Ratio                                                                    | G <sub>SLOPE</sub>      | 1.8   | 2    | 2.26 |       | $I_{SLOPE}$ = 50 μA;<br>R <sub>SC</sub> = 1 kΩ                                                                          |  |  |  |

- Note 1: See Section 3.3 "Minimum Input Voltage at VIN Pin" for the minimum input voltage.

- 2: The specifications which apply over the full operating temperature range at  $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$  are guaranteed by design and characterization.

- 3: For design guidance only

## **TEMPERATURE SPECIFICATIONS**

| Parameters                     | Sym.          | Min.            | Тур. | Max. | Units | Conditions |

|--------------------------------|---------------|-----------------|------|------|-------|------------|

| TEMPERATURE RANGES             |               |                 |      |      |       |            |

| Operating Junction Temperature | $T_J$         | <del>-4</del> 0 | _    | +125 | °C    |            |

| Storage Temperature            | Ts            | -65             | _    | +150 | °C    |            |

| PACKAGE THERMAL RESISTANCE     |               |                 |      |      |       |            |

| 16-lead SOIC                   | $\theta_{JA}$ | _               | 83   | _    | °C/W  |            |

## 2.0 PIN DESCRIPTION

Table 2-1 shows the pin description details of HV9912.

TABLE 2-1: PIN DESCRIPTION TABLE

| IABLL 2-1. |       | FIION IABLE                                                                                                                                                                                                                                    |

|------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Name  | Description                                                                                                                                                                                                                                    |

| 1          | VIN   | This pin is the input of a 90V high-voltage regulator.                                                                                                                                                                                         |

| 2          | VDD   | This is a power supply pin for all internal circuits. It must be bypassed with a low-ESR capacitor to GND (at least 0.1 µF).                                                                                                                   |

| 3          | GATE  | This pin is the output gate driver for an external N-channel power MOSFET.                                                                                                                                                                     |

| 4          | GND   | This is the ground return for all the low-power analog internal circuitry. This pin must be connected to the return path from the input.                                                                                                       |

| 5          | CS    | This pin is used to sense the source current of the external power FET. It includes a built-in 100 ns (minimum) blanking time.                                                                                                                 |

| 6          | SC    | This pin is used to set the slope compensation.                                                                                                                                                                                                |

| 7          | RT    | This pin sets the frequency of the power circuit. A resistor between RT and GND will program the circuit in Constant Frequency mode.                                                                                                           |

| 8          | SYNC  | This I/O pin may be connected to the SYNC pin of other HV9912 circuits and will cause the oscillators to lock to the highest frequency oscillator.                                                                                             |

| 9          | CLIM  | This pin provides a programmable input current limit for the converter. The current limit can be set using a resistor divider from the REF pin.                                                                                                |

| 10         | REF   | This pin provides 2% accurate reference voltage. It must be bypassed with a 0.01 $\mu$ F=0.1 $\mu$ F capacitor to GND.                                                                                                                         |

| 11         | FAULT | This pin is pulled to ground when there is an Output Short-circuit condition or Output Overvoltage condition. This pin can be used to drive an external MOSFET (in the case of boost converters) to disconnect the load from the source.       |

| 12         | OVP   | This pin provides the overvoltage protection for the converter. When the voltage at this pin exceeds 5V, the GATE output of the HV9912 is turned off, and the FAULT goes low. The IC will turn on when the voltage at the pin goes below 4.5V. |

| 13         | PWMD  | When this pin is pulled to GND (or left open), switching of the HV9912 is disabled. When an external TTL high level is applied to it, switching will resume.                                                                                   |

| 14         | COMP  | Stable Closed-loop control can be accomplished by connecting a compensation network between COMP and GND. This capacitor also controls the hiccup time.                                                                                        |

| 15         | IREF  | The voltage at this pin sets the output current level. The current reference can be set using a resistor divider from the REF pin.                                                                                                             |

| 16         | FDBK  | This pin provides output current feedback to the HV9912 by using a current sense resistor.                                                                                                                                                     |

#### 3.0 DETAILED DESCRIPTION

#### 3.1 Power Topology

The HV9912 is a Switch-mode converter LED driver designed to control a Continuous Conduction mode buck or boost in a Constant Frequency or Constant Off-time mode. The IC includes an internal linear regulator, which operates from input voltages up to 90V, eliminating the need for an external power supply for the IC. The IC includes features typically required in LED drivers, such as open LED protection, output short-circuit protection, linear and PWM dimming, programmable input current limiting and accurate control of the LED current. A high-current gate drive output enables the controller to be used in high-power converters.

The HV9912 is an enhanced version of the HV9911 with hysteretic overvoltage protection and Hiccup mode short-circuit protection. The IC includes a blanking network controlled by the PWMD input to prevent the short-circuit protection from triggering prematurely during PWM dimming due to the parasitic capacitance of the LED string. It also allows the  $I_{\rm REF}$  pin to be pulled all the way down to GND without triggering the short-circuit protection. It is a pin-compatible replacement for the HV9911.

#### 3.2 Linear Regulator

The HV9912 can be powered directly from its  $V_{IN}$  pin that withstands a voltage of up to 90V. When a voltage is applied to the  $V_{IN}$  pin, the HV9912 tries to maintain a constant 7.75V (typical) at the  $V_{DD}$  pin. The regulator also has a built-in undervoltage lockout which shuts off the IC if the voltage at the  $V_{DD}$  pin falls below the UVLO threshold.

The  $V_{DD}$  pin must be bypassed by a low-ESR capacitor ( $\geq$ 0.1  $\mu$ F) to provide a low-impedance path for the high-frequency current of the output gate driver.

The input current drawn from the  $V_{\text{IN}}$  pin is the sum of the 1.5 mA current drawn by the internal circuit and the current drawn by the gate driver, which in turn depends on the switching frequency and the gate charge of the external FET. See Equation 3-1.

#### **EQUATION 3-1:**

$$I_{IN} = 1.5mA + (Q_G \bullet f_S)$$

In the above equation,  $f_S$  is the switching frequency, and  $Q_G$  is the external FET's gate charge, which can be obtained from the data sheet of the FET.

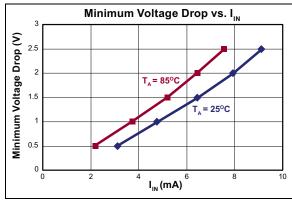

#### 3.3 Minimum Input Voltage at V<sub>IN</sub> Pin

The minimum input voltage at which the converter will start and stop depends on the minimum voltage drop required for the linear regulator. The internal linear regulator will control the voltage at the  $V_{DD}$  pin when  $V_{IN}$  is between 9V and 90V. However, when  $V_{IN}$  is less than 9V, the converter will still function as long as  $V_{DD}$  is greater than the undervoltage lockout. Thus, the converter might be able to start at input voltages lower than 9V. The start/stop voltages at the  $V_{IN}$  pin can be determined using the minimum voltage drop across the linear regulator as a function of the current drawn. This data is shown in Figure 3-1 for ambient temperatures of  $25^{\circ}\mathrm{C}$  and  $85^{\circ}\mathrm{C}$ .

Assume an ambient temperature of 85°C. Provided that the IC is driving a 15 nC gate charge FET at 200 kHz, the total input current is estimated to be 4.5 mA when Equation 3-1 is used. At this input current, the minimum voltage drop from Figure 3-1 would be around  $V_{DROP} = 1.25V$ . However, before the IC starts switching, the current drawn would have been 1.5 mA. At this current level, the voltage drop would be approximately  $V_{DROP1} = 0.3V$ . Thus, the start/stop  $V_{IN}$  voltages could be computed as demonstrated in Equation 3-2 and Equation 3-3 below:

#### **EQUATION 3-2:**

$$\begin{array}{ll} V_{IN(START)} &=& UVLO_{MAX} + V_{DROP1} \\ &=& 7V + 0.3\,V \\ &=& 7.3\,V \end{array}$$

#### **EQUATION 3-3:**

$$\begin{split} V_{IN(STOP)} &= UVLO_{MAX} - \Delta UVLO + V_{DROP} \\ &= 7V - 0.5V + 1.25V \\ &= 7.75V \end{split}$$

FIGURE 3-1: Headroom vs. Input Current.

In this case, the gate driver draws too much current and  $V_{INSTART}$  is less than  $V_{INSTOP}$ . When this happens, the IC will oscillate between ON and OFF if the input

voltage is between the start and stop voltages. Therefore, it is recommended that the input voltage be kept higher than V<sub>INSTOP</sub>.

#### 3.4 Reference

HV9912 includes a 2% accurate 1.25V reference, which can be used as the reference for the output current as well as to set the switch current limit. The reference is buffered so that it can deliver a maximum of  $500~\mu A$  external current to drive the external circuitry. The reference should be bypassed with at least a 10 nF low-ESR capacitor.

Note:

To avoid abnormal Startup conditions, the bypass capacitor at the REF pin should not exceed 0.1 µF.

#### 3.5 Oscillator

Connecting the resistor between  $R_{T}$  and GND will program the time period.

In both cases, resistor  $R_T$  sets the current, which charges an internal oscillator capacitor. The capacitor voltage ramps up linearly. When the voltage increases beyond the internal set voltage, a comparator triggers the set input of the internal SR flip-flop. This starts the next switching cycle. The time period of the oscillator can be computed as shown in Equation 3-4.

#### **EQUATION 3-4:**

$$T_S \approx R_T \bullet 18pF$$

#### 3.6 Synchronization

The SYNC pin is an input/output (I/O) port to a fault-tolerant peer-to-peer and/or master clock synchronization circuit. For synchronization, the SYNC pins of multiple HV9912-based converters can be connected together and may also be connected to the open drain output of a master clock. When connected in this manner, the oscillators will lock to the device with the highest operating frequency. When synchronizing multiple ICs, it is recommended that the same timing resistor (corresponding to the switching frequency) be used in all the HV9912 circuits.

On rare occasions, given the length of the connecting lines for the SYNC pins, a resistor between SYNC and GND may be required to damp any ringing due to parasitic capacitances. It is recommended that the resistor chosen be greater than 300  $k\Omega.$

When synchronized in this manner, a permanent High or Low condition on the SYNC pin will result in a loss of synchronization, but the HV9912-based converters will continue to operate at their individually set operating frequencies. Since loss of synchronization will not result in total system failure, the SYNC pin is considered fault tolerant.

#### 3.7 Slope Compensation

For Continuous Conduction mode converters operating in the Constant Frequency mode, slope compensation becomes necessary to ensure stability of the Peak Current mode controller if the operating duty cycle is greater than 50%. Choosing a slope compensation which is one half of the down slope of the inductor current ensures that the converter will be stable for all duty cycles.

Slope compensation can be programmed by two resistors  $R_{SLOPE}$  and  $R_{SC}$ . Assuming a down slope of DS (A/ $\mu$ s) for the inductor current, the slope compensation resistors can be computed as illustrated in Equation 3-5.

#### **EQUATION 3-5:**

$$R_{SC} = \frac{R_{SLOPE} \bullet DS \bullet 10^6 \bullet T_S \bullet R_{CS}}{10}$$

Where  $R_{CS}$  is the current sense resistor which senses the switching FET current

Note:

The maximum current that can be sourced out of the SC pin is 100  $\mu$ A. This limits the minimum value of the R<sub>SLOPE</sub> resistor to 25 k $\Omega$ . If the equation for slope compensation produces a R<sub>SLOPE</sub> less than this value, then R<sub>SC</sub> would have to be reduced accordingly. It is recommended that R<sub>SLOPE</sub> be chosen within the range of 25 k $\Omega$  to 50 k $\Omega$ .

#### 3.8 Current Sense

The current sense input of the HV9912 includes a built-in 100 ns (minimum) blanking time to prevent spurious turn-off due to the initial current spike when the FET turns on.

The HV9912 includes two high-speed comparators—one is used during normal operation and the other is used to limit the maximum input current during Input Undervoltage or Overload conditions.

The IC includes an internal resistor divider network, which steps down the voltage at the COMP pin by a factor of 15. This stepped-down voltage is given to one of the comparators as the current reference. The reference to the other comparator, which acts to limit the maximum inductor current, is given externally.

It is recommended that the sense resistor  $R_{CS}$  be chosen so as to provide about 250 mV current sense signal.

#### 3.9 Current Limit

Current limit has to be set by a resistor divider from the 1.25V reference available on the IC. Assuming a maximum operating inductor current  $I_{pk}$  (including ripple current), the maximum voltage at the  $C_{LIM}$  pin can be set as shown in Equation 3-6.

#### **EQUATION 3-6:**

$$V_{CLIM} \ge 1.2 \bullet I_{PK} \bullet R_{CS} + (5 \bullet R_{CS} / R_{SLOPE}) \bullet 0.9$$

Note that this equation assumes a current limit at 120% of the maximum input current. Also, if  $V_{CLIM}$  is greater than 450 mV, the saturation of the internal opamp will determine the limit on the input current rather than the  $C_{LIM}$  pin. In such a case, the sense resistor  $R_{CS}$  should be reduced until  $V_{CLIM}$  reduces below 550 mV.

It is recommended that no capacitor be connected between  $\mathsf{C}_{\mathsf{LIM}}$  and  $\mathsf{GND}.$

## 3.10 Internal 1 MHz Transconductance Amplifier

HV9912 includes a built-in 1 MHz transconductance amplifier with tri-state output, which can be used to close the feedback loop. The output current sense signal is connected to the FDBK pin and the current reference is connected to the  $I_{\rm RFF}$  pin.

The output of the opamp is controlled by the signal applied to the PWMD pin. When PWMD is high, the output of the opamp is connected to the COMP pin. When PWMD is low, the output is left open. This enables the integrating capacitor to hold the charge when the PWMD signal has turned off the gate drive. When the IC is enabled, the voltage on the integrating capacitor will force the converter into Steady state almost instantaneously.

The output of the opamp is buffered and connected to the current sense comparator using a 15:1 divider. The buffer helps to prevent the integrator capacitor from discharging during the PWM Dimming state.

#### 3.11 PWM Dimming

PWM dimming can be achieved by driving the PWMD pin with a TTL-compatible square wave source. The PWM signal is connected internally to three different nodes—the transconductance amplifier, the FAULT output and the GATE output.

When the PWMD signal is high, the GATE and FAULT pins are enabled and the transconductance opamp's output is connected to the external compensation network. Thus, the internal amplifier controls the output current. When the PWMD signal goes low, the output of the transconductance amplifier is disconnected from the compensation network. Therefore the integrating

capacitor maintains the voltage across it. The GATE is disabled, so the converter stops switching and the FAULT pin goes low, turning off the disconnect switch.

The output capacitor of the converter determines the converter's PWM dimming response because the capacitor has to get charged and discharged whenever the PWMD signal goes high or low. In the case of a buck converter, since the inductor current is continuous, a very small capacitor is used across the LEDs. This minimizes the effect of the capacitor on the converter's PWM dimming response. However, in the case of a boost converter, the output current is discontinuous, and a very large output capacitor is required to reduce the ripple in the LED current. Thus. this capacitor will have a significant impact on the PWM dimming response. By turning off the disconnect switch when PWMD goes low, the output capacitor is prevented from being discharged. This dramatically improves the boost converter's PWM dimming response.

Note:

In case of Continuous Conduction mode boost converters, disconnecting the capacitor might cause a sudden spike in the capacitor voltage as the energy in the inductor is dumped into the capacitor. This increase in the capacitor voltage might cause the OVP comparator to trip if the OVP point is set too close to the maximum operating voltage. Thus, either the capacitor has to be larger to absorb this energy without increasing the capacitor voltage significantly or the OVP set point has to be increased.

# 3.12 False Triggering of the Short-Circuit Comparator During PWM Dimming

During PWM dimming, the parasitic capacitance of the LED string causes a spike in the output current when the disconnect FET is turned on. With the HV9911, this parasitic spike in the output current makes the IC falsely detect an Overcurrent condition and shut down. To prevent this false shutdown, an R-C filter is used at the FDBK pin to filter this spike.

To prevent false triggering in the HV9912, there is a built-in 500 ns blanking network for the short-circuit comparator, which eliminates the need for the external R-C low-pass filter. This blanking network is activated when the PWMD input goes high. Thus, the short-circuit comparator will not see the spike in the LED current during the PWM Dimming turn-on transition. Once the blanking timer is completed, the short-circuit comparator will start monitoring the output current. Thus, the total delay time for detecting a short-circuit will depend on the condition of the PWMD input.

If the output short-circuit exists before the PWMD signal goes high, the total detection can be computed as shown in Equation 3-7:

#### **EQUATION 3-7:**

$$t_{detect} = t_{blank, SC(max)} + t_{delay(max)} \approx 900 + 250$$

$\approx 1150 ns(max)$

If the short-circuit occurs when the PWMD signal is already high, the time to detect is determined through Equation 3-8:

#### **EQUATION 3-8:**

$$t_{detect1} = t_{delay(max)} \approx 250 ns(max)$$

#### 3.13 Hiccup Timer

HV9912 reuses the compensation network on the COMP pin to create a timer which is activated upon startup or when a detected Fault has been cleared. When a Fault is detected (either open-circuit or short-circuit) or upon startup, the COMP pin is  $\underline{\text{discon}}_{\text{nected}}$  from the  $g_{\text{M}}$  amplifier and the GATE and FAULT pins are pulled low, disabling the LED driver. When the Fault has cleared, a 5 µA current source is activated which pulls the COMP network up to 5V. Once the voltage at the COMP network reaches 5V, the 5 µA sourcing current is disconnected and a 5 µA sinking current is activated which pulls the COMP pin low. When the voltage at the COMP pin reaches 1V, the sinking current is disconnected and the  $g_M$  amplifier is reconnected to the COMP pin. The FAULT pin goes high and the GATE pin would be allowed to switch. The closed-loop control then takes over the control of the LED current.

#### 3.14 Startup Condition

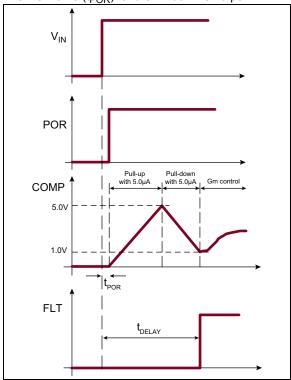

The startup waveforms are shown in Figure 3-2.

Assuming a pole-zero R-C network at the COMP pin (series combination of  $R_Z$  and  $C_Z$  in parallel with  $C_C$ ), the start-up delay time can be approximately computed as shown in Equation 3-9.

#### **EQUATION 3-9:**

$$t_{delay} \approx t_{POR} + (C_C + C_Z) \bullet \frac{9V}{5\mu A}$$

This equation assumes that the voltage drop across  $R_Z$  can be neglected compared to the voltage swing at the COMP pin, which is true in most cases ( $R_Z$  < 100 k $\Omega$ ). The POR time ( $t_{POR}$ ) for the HV9912 is 10  $\mu$ s.

FIGURE 3-2: Waveforms during Startup.

#### 3.15 Fault Condition

In the case of a Fault condition (either open-circuit or short-circuit), the same sequence is repeated, and the only difference is that the COMP pin voltage does not start from zero but from its Steady-state condition.

#### 3.16 Short-Circuit Protection

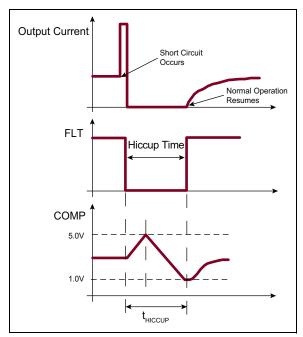

When a Short-circuit condition is detected (output current becomes higher than twice the Steady-state current), the GATE and FAULT outputs are pulled low. As soon as the disconnect FET is turned off, the output current goes to zero and the Short-circuit condition disappears. At this time, the hiccup timer is started. (See Figure 3-3.) Once the timing is complete, the converter attempts to restart. If the Fault condition still persists, the converter shuts down and goes through the cycle again. If the Fault condition is cleared due to a momentary output short, the converter will start regulating the output current normally. This allows the LED driver to recover from accidental shorts without having to reset the IC.

The hiccup time will depend on the Steady-state voltage of the COMP pin ( $V_{COMP}$ ). This is typically in the range of 3V–4V. The hiccup time can be approximately computed with Equation 3-10.

#### **EQUATION 3-10:**

$$t_{HICCUP} \approx (C_C + C_Z) \bullet \frac{9V - V_{COMP}}{5\mu A}$$

FIGURE 3-3: Short-circuit Protection.

#### 3.17 Overvoltage Protection

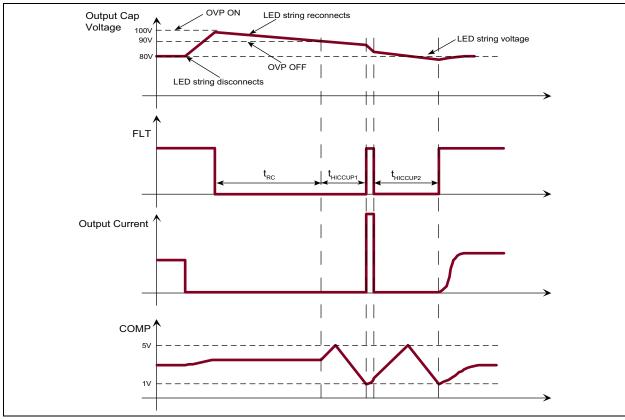

The HV9912 provides hysteretic overvoltage protection, allowing the IC to recover in case the LED load is disconnected momentarily.

When the load is disconnected in a boost converter, the output voltage rises as the output capacitor starts charging. When the output voltage reaches the OVP rising threshold, the HV9912 detects an Overvoltage condition and turns off the converter. The converter is turned back on only when the output voltage falls below the falling OVP threshold, which is 10% lower than the rising threshold. This time is mostly dictated by the R-C time constant of the output capacitor  $C_{\rm O}$  and the resistor network used to sense overvoltage ( $R_{\rm OVP1}+R_{\rm OVP2}$ ). In case of a persistent Open-circuit condition, this cycle keeps repeating, maintaining the output voltage within a 10% band.

In most designs, the lower threshold voltage of the overvoltage protection is more than the LED string voltage when the converter is turned on. Thus, when the LED load is reconnected to the output of the converter, the voltage differential between the actual output voltage and the LED string voltage will cause a spike in the output current when the FAULT signal goes high. This causes a short-circuit to be detected and the HV9912 will go into short-circuit protection. This continues until the output voltage becomes lower than

the LED string voltage, at which point no Fault will be detected and the normal operation of the circuit will commence. (See Figure 3-4.)

The various delay times can be determined as shown in Equation 3-11, Equation 3-12 and Equation 3-13:

#### **EQUATION 3-11:**

$$t_{RC} \approx 0.1 \bullet (R_{OVP1} + R_{OVP2}) \bullet C_O$$

#### **EQUATION 3-12:**

$$t_{HICCUP1} \approx (C_C + C_Z) \bullet \frac{9V - V_{COMP}}{5\mu A}$$

#### **EQUATION 3-13:**

$$t_{HICCUP2-n} \approx (C_C + C_Z) \bullet \frac{9V}{5\mu A}$$

**Note:** The number of hiccup cycles might be more than two.

#### 3.18 Linear Dimming

Linear dimming can be achieved by varying the voltage at the I<sub>REF</sub> pin because the output current is proportional to the voltage at the pin. This can be done either by using a potentiometer from the I<sub>REF</sub> pin or applying an external voltage source to the pin.

In the HV9911, due to the offset voltage of the short-circuit comparator as well as the non-linearity of the X2 gain stage, pulling the  $I_{REF}$  pin very close to GND will cause the internal short-circuit comparator to trigger and shut down the IC.

To overcome this in the HV9912, the minimum output of the gain stage is limited to 125 ~ 250mV, allowing the  $I_{REF}$  pin to be pulled all the way to 0V without triggering the short-circuit comparator.

Note:

Since this control IC is a Peak Current mode controller, pulling the I<sub>REF</sub> pin to zero will not cause the LED current to become zero. The converter will still be operating at its minimum on time, causing a very small current to flow through the LEDs. To get zero LED current, the PWMD input has to be pulled to GND.

FIGURE 3-4: Open-circuit Protection.

#### 4.0 PACKAGING INFORMATION

#### 4.1 **Package Marking Information**

Product Code or Customer-specific information Legend: XX...X

Year code (last digit of calendar year) ΥY Year code (last 2 digits of calendar year) Week code (week of January 1 is week '01') WW

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for product code or customer-specific information. Package may or not include the corporate logo.

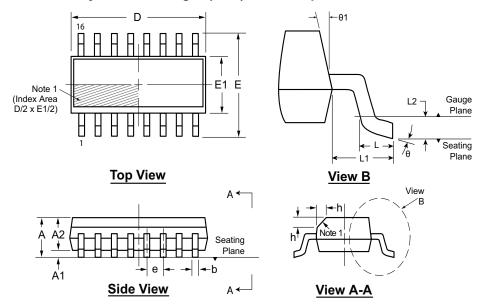

# 16-Lead SOIC (Narrow Body) Package Outline (NG)

9.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

#### Note:

This chamfer feature is optional. If it is not present, then a Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo             | ol  | Α     | A1   | A2    | b    | D      | Е     | E1    | е           | h    | L    | L1          | L2          | θ          | θ1  |

|-------------------|-----|-------|------|-------|------|--------|-------|-------|-------------|------|------|-------------|-------------|------------|-----|

|                   | MIN | 1.35* | 0.10 | 1.25  | 0.31 | 9.80*  | 5.80* | 3.80* |             | 0.25 | 0.40 |             |             | <b>0</b> ° | 5°  |

| Dimension<br>(mm) | NOM | -     | -    | -     | -    | 9.90   | 6.00  | 3.90  | 1.27<br>BSC | -    | -    | 1.04<br>REF | 0.25<br>BSC | -          | -   |

| ()                | MAX | 1.75  | 0.25 | 1.65* | 0.51 | 10.00* | 6.20* | 4.00* |             | 0.50 | 1.27 |             | 200         | <b>8</b> ° | 15° |

JEDEC Registration MS-012, Variation AC, Issue E, Sept. 2005.

\* This dimension is not specified in the JEDEC drawing.

Drawings are not to scale.

NOTES:

# HV9912

# APPENDIX A: REVISION HISTORY

# Revision A (July 2016)

- Converted Supertex Doc# DSFP-HV9912 to Microchip DS20005583A.

- Made minor text changes throughout the document.

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| PART NO        | ) XX         |       | - Y - Y                                                                                         | E        | amples:          |                                                                                                                                                             |

|----------------|--------------|-------|-------------------------------------------------------------------------------------------------|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device         | Pack<br>Opti | age   | Environmental Media Type                                                                        | a)<br>b) |                  | Switch-Mode LED Driver IC with<br>High Current Accuracy and Hic-<br>cup Mode Protection, 16-lead<br>SOIC Package, 45/Tube<br>Switch-Mode LED Driver IC with |

| Device:        | HV9912       | =     | Switch-Mode LED Driver IC with High<br>Current Accuracy and Hiccup Mode<br>Protection           | c)       | HV9912NG-G-M934: | High Current Accuracy and Hic-<br>cup Mode Protection, 16-lead<br>SOIC Package, 2600/Reel                                                                   |

| Package:       | NG           | =     | 16-lead SOIC                                                                                    |          |                  | SOIC Package, 2600/Reel                                                                                                                                     |

| Environmental: | G            | =     | Lead (Pb)-free/RoHS-compliant Package                                                           |          |                  |                                                                                                                                                             |

| Media Types:   | (blank)      | =     | 45/Tube for an NG Package                                                                       |          |                  |                                                                                                                                                             |

|                | M901         | =     | 2600/Reel for an NG Package                                                                     |          |                  |                                                                                                                                                             |

|                | M934         | =     | 2600/Reel for an NG Package                                                                     |          |                  |                                                                                                                                                             |

| was stand      |              | 2600/ | d M934, the base quantity for tape and reel reel. Both options will result in delivery of the . |          |                  |                                                                                                                                                             |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0798-0

# **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA

Tel: 408-735-9110 Canada - Toronto

Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511

Fax: 86-28-8665-7889 China - Chongging

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou

Tel: 86-20-8755-8029 China - Hangzhou

Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470

China - Qingdao

Tol: 86 532 8502 7355

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444

Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631

Fax: 91-11-4160-8631

India - Pune

Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770

Fax: 81-3-6880-3770

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870

Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0

Fax: 49-89-627-144-44 Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

06/23/16

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LED Lighting Drivers category:

Click to view products by Microchip manufacturer:

Other Similar products are found below:

LV5235V-MPB-H MB39C602PNF-G-JNEFE1 MIC2871YMK-T5 AL1676-10BS7-13 AL1676-20AS7-13 AP5726WUG-7 MX877RTR

ICL8201 IS31BL3228B-UTLS2-TR IS31BL3506B-TTLS2-TR AL3157F-7 AP5725FDCG-7 AP5726FDCG-7 LV52204MTTBG

AP5725WUG-7 STP4CMPQTR NCL30086BDR2G CAT4004BHU2-GT3 LV52207AXA-VH AP1694AS-13 TLE4242EJ AS3688

IS31LT3172-GRLS4-TR TLD2311EL KTD2694EDQ-TR KTZ8864EJAA-TR IS32LT3174-GRLA3-TR ZXLD1374QESTTC MP2488DN-LF-Z NLM0010XTSA1 AL1676-20BS7-13 MPQ7220GF-AEC1-P MPQ4425BGJ-AEC1-P MPQ7220GF-AEC1-Z MPQ4425BGJ-AEC1-Z IS31FL3737B-QFLS4-TR IS31FL3239-QFLS4-TR KTD2058EUAC-TR KTD2037EWE-TR DIO5662ST6 IS31BL3508A-TTLS2-TR

MAX20052CATC/V+ MAX25606AUP/V+ BD6586MUV-E2 BD9206EFV-E2 BD9416FS-E2 LYT4227E LYT6079C-TL MP3394SGF-P MP4689AGN-P