# KS8995MA/FQ

Integrated 5-Port 10/100 Managed Switch

Rev. 3.0

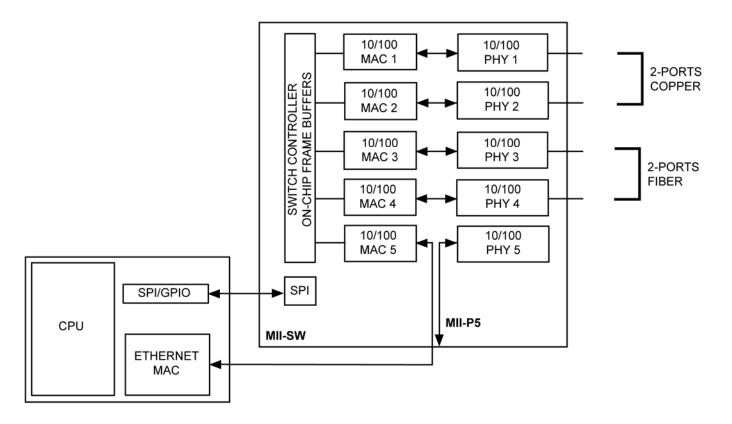

### **General Description**

The KS8995MA/FQ is a highly-integrated Layer 2 managed switch with optimized bill of materials (BOM) cost for low port count, cost-sensitive 10/100Mbps switch systems with both copper and optic fiber media. It also provides an extensive feature set such as tag/port-based VLAN, quality of service (QoS) priority, management, MIB counters, dual MII interfaces and CPU control/data interfaces to effectively address both current and emerging fast Ethernet applications.

The KS8995MA/FQ contains five 10/100 transceivers with patented mixed-signal low-power technology, five media access control (MAC) units, a high-speed non-blocking switch fabric, a dedicated address lookup engine, and an on-chip frame buffer memory.

All PHY units support 10BASE-T and 100BASE-TX. In addition, two of the PHY units support 100BASE-FX on ports 4 and 5 for KSZ8995MA, two of the PHY units support 100BASE-FX on ports 3 and 4 for KSZ8995FQ. Datasheets and support documentation can be found on Micrel's web site at: www.micrel.com.

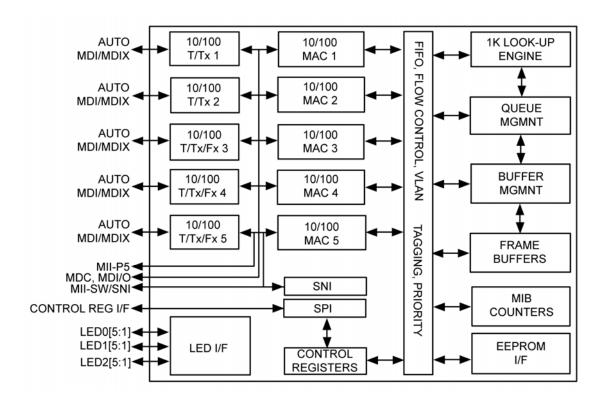

### **Functional Diagram**

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## Features

- Integrated switch with five MACs and five fast Ethernet transceivers fully-compliant to IEEE 802.3u standard

- Shared memory based switch fabric with fully nonblocking configuration

- 1.4Gbps high-performance memory bandwidth

- 10BASE-T, 100BASE-TX, and 100BASE-FX modes

- Dual MII configuration: MII-Switch (MAC or PHY mode MII) and MII-P5 (PHY mode MII).

- IEEE 802.1q tag-based VLAN (16 VLANs, full-range VID) for DMZ port, WAN/LAN separation or inter-VLAN switch links

- VLAN ID tag/untag options, per-port basis

- Programmable rate limiting 0Mbps to 100Mbps, ingress and egress port, rate options for high and low priority, per-port basis in 32Kbps increments

- Flow control or drop packet rate limiting (ingress port)

- Integrated MIB counters for fully-compliant statistics gathering, 34 MIB counters per port

- Enable/Disable option for huge frame size up to 1916 bytes per frame

- IGMP v1/v2 snooping for multicast packet filtering

- Special tagging mode to send CPU info on ingress packet's port value

- SPI slave (complete) and MDIO (MII PHY only) serial management interface for control of register configuration

- MAC-id based security lock option

- Control registers configurable on-the-fly (portpriority, 802.1p/d/q, AN...)

- CPU read access to MAC forwarding table entries

- 802.1d spanning tree protocol

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic to any port or MII

- Broadcast storm protection with % control global and per-port basis

- Optimization for fiber-to-copper media conversion

- Full-chip hardware power-down support (register configuration not saved)

- Per-port based software power-save on PHY (idle link detection, register configuration preserved)

- QoS/CoS packets prioritization supports:

- Per port, 802.1p and DiffServ based

- 802.1p/q tag insertion or removal on a per-port basis (egress)

- MDC and MDI/O interface support to access the MII PHY control registers (not all control registers)

- MII local loopback support

- On-chip 64Kbyte memory for frame buffering (not shared with 1K unicast address table)

- Wire-speed reception and transmission

- Integrated look-up engine with dedicated 1K MAC addresses

- Full duplex IEEE 802.3x and half-duplex back pressure flow control

- Comprehensive LED support

- 7-wire SNI support for legacy MAC interface

- Automatic MDI/MDI-X crossover for plug-and-play

- Disable automatic MDI/MDI-X option

- Low power:

- Core: 1.8V

- Digital I/O: 3.3V

- Analog I/O: 3.3V

- 0.18µm CMOS technology

- Temperature ranges:

- Commercial: 0°C to +70°C

- Industrial: –40°C to +85°C

- Available in 128-pin PQFP package

## Applications

- Broadband gateway/firewall/VPN

- Integrated DSL or cable modem multi-port router

- Wireless LAN access point plus gateway

- Home networking expansion

- Standalone 10/100 switch

- Hotel/campus/MxU gateway

- Enterprise VoIP gateway/phone

- FTTx customer premise equipment

- Managed media converter

# **Ordering Information**

| Part      | Number         | Temperature Range | Package      |  |

|-----------|----------------|-------------------|--------------|--|

| Standard  | Pb (lead)-Free | Temperature Range | i uchuge     |  |

| KS8995MA  | KSZ8995MA      | 0°C to +70°C      | 128-Pin PQFP |  |

| KS8995FQ  | KSZ8995FQ      | 0°C to +70°C      | 128-Pin PQFP |  |

| KS8995MAI | KSZ8995MAI     | -40°C to +85°C    | 128-Pin PQFP |  |

| KS8995FQI | KSZ8995FQI     | –40°C to +85°C    | 128-Pin PQFP |  |

# **Revision History**

| Revision | Date     | Summary of Changes                                                                                                                                                                                |  |  |  |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2.0      | 10/10/03 | Created.                                                                                                                                                                                          |  |  |  |

| 2.1      | 10/30/03 | Editorial changes on electrical characteristics.                                                                                                                                                  |  |  |  |

| 2.2      | 04/01/04 | Editorial changes on the TTL input and output electrical characteristics.                                                                                                                         |  |  |  |

| 2.3      | 01/19/05 | Insert recommended reset circuit, pg. 70. Editorial, Pg. 36.                                                                                                                                      |  |  |  |

| 2.4      | 04/13/05 | Changed VDDIO to 3.3V.<br>Changed Jitter to 16 ns Max.                                                                                                                                            |  |  |  |

| 2.5      | 02/06/06 | Added Pb-Free option for Industrial version.                                                                                                                                                      |  |  |  |

| 2.6      | 07/12/06 | Add a note for VLAN table write, improve the timing diagram for MII interface, update pin description for PCRS, PCOL, etc. And update the description of the register bits for the loopback, etc. |  |  |  |

| 2.7      | 06/01/07 | Add the package thermal information in the operating rating and the transformer power consumption information in the electrical characteristics note.                                             |  |  |  |

| 2.8      | 03/20/08 | Add KSZ8995FQ information and pin description.                                                                                                                                                    |  |  |  |

| 2.9      | 09/15/08 | Add KSZ8995FQ block diagram and descriptions for revision ID and LED mode.                                                                                                                        |  |  |  |

|          | 10/26/11 | Update some descriptions for VDDAT voltage, MDI/MDIX bits of the registers. Update the equation of the broadcast storm protection, correct typo.                                                  |  |  |  |

| 3.0      | 12/09/11 | Update the description of MDI/MDIX in the MIIM register 0. Correct the typo error for MDI/MDIX bits of the registers.                                                                             |  |  |  |

|          | 01/27/12 | Update the description for the VDDAT analog voltage.                                                                                                                                              |  |  |  |

|          | 11/08/12 | Correct typo error for the commercial temperature and Thermal Resistance $\theta_{\text{JC.}}$                                                                                                    |  |  |  |

|          | 12/12/12 | Correct typo and add notes for pins 109, 111.                                                                                                                                                     |  |  |  |

## Contents

| System Level Applications                       | 11 |

|-------------------------------------------------|----|

| Pin Configuration                               | 13 |

| Pin Description – By Number                     | 14 |

| Pin Description – By Name                       |    |

| Introduction                                    |    |

| Functional Overview: Physical Layer Transceiver |    |

| 100BASE-TX Transmit                             |    |

| 100BASE-TX Receive                              |    |

| PLL Clock Synthesizer                           | 26 |

| Scrambler/De-Scrambler (100BASE-TX Only)        | 27 |

| 100BASE-FX Operation                            | 27 |

| 100BASE-FX Signal Detection                     | 27 |

| 100BASE-FX Far End fault                        | 27 |

| 10BASE-T Transmit                               | 27 |

| 10BASE-T Receive                                | 27 |

| Power Management                                | 27 |

| MDI/MDI-X Auto Crossover                        | 27 |

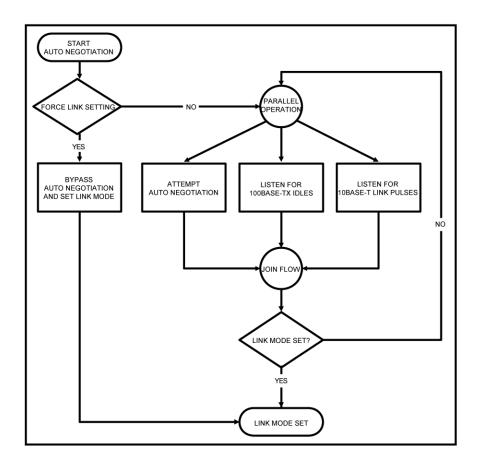

| Auto-Negotiation                                |    |

| Functional Overview: Switch Core                |    |

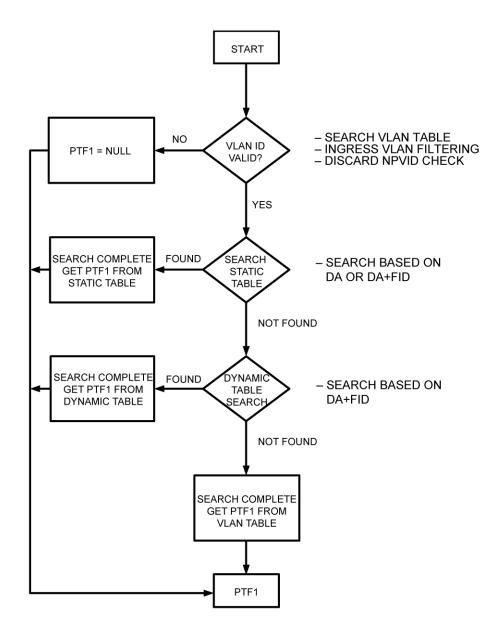

| Address Look-Up                                 | 29 |

| Learning                                        |    |

| Migration                                       |    |

| Aging                                           | 29 |

| Forwarding                                      |    |

| Switching Engine                                |    |

| Media Access Controller (MAC) Operation         |    |

| MII Interface Operation                         |    |

| SNI Interface Operation                         |    |

| Advanced Functionality                          |    |

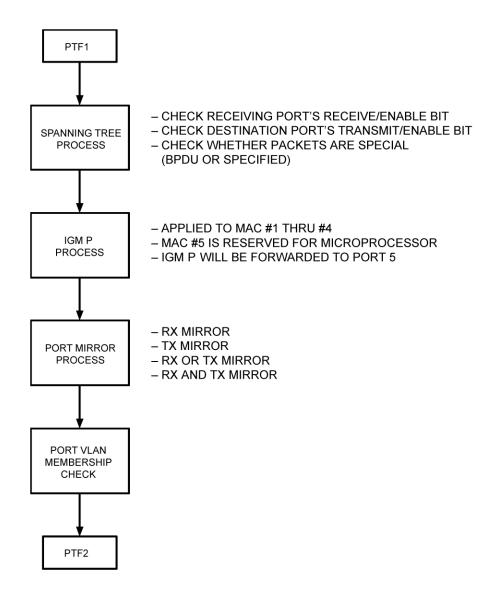

| Spanning Tree Support                           |    |

| Special Tagging Mode                            |    |

| IGMP Support                                    |    |

| Port Mirroring Support                          |    |

| VLAN Support                                    |    |

| Rate Limit Support                              |    |

| Configuration Interface              |    |

|--------------------------------------|----|

| MII Management Interface (MIIM)      |    |

| Register Description                 |    |

| Global Registers                     | 47 |

| Register 0 (0x00): Chip ID0          | 47 |

| Register 2 (0x02): Global Control 0  | 47 |

| Register 4 (0x04): Global Control 2  | 49 |

| Register 5 (0x05): Global Control 3  |    |

| Register 6 (0x07): Global Control 4  | 51 |

| Register 7 (0x07): Global Control 5  | 51 |

| Register 8 (0x08): Global Control 6  | 51 |

| Register 9 (0x09): Global Control 7  | 51 |

| Register 10 (0x0A): Global Control 8 |    |

| Register 11 (0x0B): Global Control 9 |    |

| Port Registers                       | 53 |

| Register 16 (0x10): Port 1 Control 0 | 53 |

| Register 32 (0x20): Port 2 Control 0 |    |

| Register 48 (0x30): Port 3 Control 0 |    |

| Register 64 (0x40): Port 4 Control 0 |    |

| Register 80 (0x50): Port 5 Control 0 |    |

| Register 17 (0x11): Port 1 Control 1 |    |

| Register 33 (0x21): Port 2 Control 1 | 54 |

| Register 49 (0x31): Port 3 Control 1 |    |

| Register 65 (0x41): Port 4 Control 1 | 54 |

| Register 81 (0x51): Port 5 Control 1 | 54 |

| Register 18 (0x12): Port 1 Control 2 | 54 |

| Register 34 (0x22): Port 2 Control 2 | 54 |

| Register 50 (0x32): Port 3 Control 2 | 54 |

| Register 66 (0x42): Port 4 Control 2 | 54 |

| Register 82 (0x52): Port 5 Control 2 | 54 |

| Register 19 (0x13): Port 1 Control 3 | 55 |

| Register 35 (0x23): Port 2 Control 3 | 55 |

| Register 51 (0x33): Port 3 Control 3 |    |

| Register 67 (0x43): Port 4 Control 3 |    |

| Register 83 (0x53): Port 5 Control 3 | 55 |

| Register 20 (0x14): Port 1 Control 4 |    |

| Register 36 (0x24): Port 2 Control 4 | 55 |

| Register 52 (0x34): Port 3 Control 4  | 55 |

|---------------------------------------|----|

| Register 68 (0x44): Port 4 Control 4  | 55 |

| Register 84 (0x54): Port 5 Control 4  | 55 |

| Register 21 (0x15): Port 1 Control 5  | 56 |

| Register 37 (0x25): Port 2 Control 5  | 56 |

| Register 53 (0x35): Port 3 Control 5  | 56 |

| Register 69 (0x45): Port 4 Control 5  | 56 |

| Register 85 (0x55): Port 5 Control 5  | 56 |

| Register 22 (0x16): Port 1 Control 6  | 56 |

| Register 38 (0x26): Port 2 Control 6  | 56 |

| Register 54 (0x36): Port 3 Control 6  | 56 |

| Register 70 (0x46): Port 4 Control 6  | 56 |

| Register 86 (0x56): Port 5 Control 6  | 56 |

| Register 23 (0x17): Port 1 Control 7  | 56 |

| Register 39 (0x27): Port 2 Control 7  | 56 |

| Register 55 (0x37): Port 3 Control 7  | 56 |

| Register 71 (0x47): Port 4 Control 7  | 56 |

| Register 87 (0x57): Port 5 Control 7  | 56 |

| Register 25 (0x19): Port 1 Control 9  | 57 |

| Register 41 (0x29): Port 2 Control 9  | 57 |

| Register 57 (0x39): Port 3 Control 9  | 57 |

| Register 73 (0x49): Port 4 Control 9  | 57 |

| Register 89 (0x59): Port 5 Control 9  | 57 |

| Register 26 (0x1A): Port 1 Control 10 | 57 |

| Register 42 (0x2A): Port 2 Control 10 | 57 |

| Register 58 (0x3A): Port 3 Control 10 | 57 |

| Register 74 (0x4A): Port 4 Control 10 | 57 |

| Register 90 (0x5A): Port 5 Control 10 | 57 |

| Register 28 (0x1C): Port 1 Control 12 | 58 |

| Register 44 (0x2C): Port 2 Control 12 | 58 |

| Register 60 (0x3C): Port 3 Control 12 | 58 |

| Register 76 (0x4C): Port 4 Control 12 | 58 |

| Register 92 (0x5C): Port 5 Control 12 | 58 |

| Register 29 (0x1D): Port 1 Control 13 | 59 |

| Register 45 (0x2D): Port 2 Control 13 | 59 |

| Register 61 (0x3D): Port 3 Control 13 | 59 |

| Register 77 (0x4D): Port 4 Control 13 | 59 |

|   | Register 93 (0x5D): Port 5 Control 13                | . 59 |

|---|------------------------------------------------------|------|

|   | Register 30 (0x1E): Port 1 Status 0                  | . 60 |

|   | Register 46 (0x2E): Port 2 Status 0                  | . 60 |

|   | Register 62 (0x3E): Port 3 Status 0                  | . 60 |

|   | Register 78 (0x4E): Port 4 Status 0                  | . 60 |

|   | Register 94 (0x5E): Port 5 Status 0                  | . 60 |

|   | Register 31 (0x1F): Port 1 Control 14                | . 60 |

|   | Register 47 (0x2F): Port 2 Control 14                | . 60 |

|   | Register 63 (0x3F): Port 3 Control 14                | . 60 |

|   | Register 79 (0x4F): Port 4 Control 14                | . 60 |

|   | Register 95 (0x5F): Port 5 Control 14                |      |

| A | dvanced Control Registers                            | .61  |

|   | Register 96 (0x60): TOS Priority Control Register 0  |      |

|   | Register 97 (0x61): TOS Priority Control Register 1  | . 61 |

|   | Register 98 (0x62): TOS Priority Control Register 2  | . 61 |

|   | Register 99 (0x63): TOS Priority Control Register 3  | . 61 |

|   | Register 100 (0x64): TOS Priority Control Register 4 | . 61 |

|   | Register 101 (0x65): TOS Priority Control Register 5 | . 61 |

|   | Register 102 (0x66): TOS Priority Control Register 6 | . 62 |

|   | Register 103 (0x67): TOS Priority Control Register 7 | . 62 |

|   | Register 104 (0x68): MAC Address Register 0          | . 62 |

|   | Register 105 (0x69): MAC Address Register 1          | . 62 |

|   | Register 106 (0x6A): MAC Address Register 2          | . 62 |

|   | Register 107 (0x6B): MAC Address Register 3          | . 62 |

|   | Register 108 (0x6C): MAC Address Register 4          | . 62 |

|   | Register 109 (0X6D): MAC Address Register 5          | . 63 |

|   | Register 110 (0x6E): Indirect Access Control 0       | . 63 |

|   | Register 111 (0x6F): Indirect Access Control 1       | . 63 |

|   | Register 112 (0x70): Indirect Data Register 8        | . 64 |

|   | Register 113 (0x71): Indirect Data Register 7        | . 64 |

|   | Register 114 (0x72): Indirect Data Register 6        | . 64 |

|   | Register 115 (0x73): Indirect Data Register 5        | . 64 |

|   | Register 116 (0x74): Indirect Data Register 4        | . 64 |

|   | Register 117 (0x75): Indirect Data Register 3        | . 64 |

|   | Register 118 (0x76): Indirect Data Register 2        | . 64 |

|   | Register 119 (0x77): Indirect Data Register 1        | . 64 |

|   | Register 120 (0x78): Indirect Data Register 0        | . 65 |

| Register 121 (0x79): Digital Testing Status 0                    | 65 |

|------------------------------------------------------------------|----|

| Register 122 (0x7A): Digital Testing Status 1                    | 65 |

| Register 123 (0x7B): Digital Testing Control 0                   | 65 |

| Register 124 (0x7C): Digital Testing Control 1                   | 65 |

| Register 125 (0x7D): Analog Testing Control 0                    | 65 |

| Register 126 (0x7E): Analog Testing Control 1                    | 65 |

| Register 127 (0x7F): Analog Testing Status                       | 65 |

| Static MAC Address                                               | 66 |

| Static Address Table Examples                                    | 67 |

| Static Address Table Write Examples                              | 67 |

| VLAN Address                                                     | 68 |

| VLAN Table Read Example                                          | 68 |

| VLAN Table Write Example                                         | 68 |

| Dynamic MAC Address                                              | 69 |

| Dynamic MAC Address Table Read Example                           | 69 |

| Dynamic MAC Address Table Write Example                          | 70 |

| MIB Counters                                                     | 71 |

| For port 2, the base is 0x20, same offset definition (0x20-0x3f) | 72 |

| For port 3, the base is 0x40, same offset definition (0x40-0x5f) | 72 |

| For port 4, the base is 0x60, same offset definition (0x60-0x7f) | 72 |

| MIB Counter Read Examples                                        | 73 |

| MIIM Registers                                                   | 74 |

| Absolute Maximum Ratings <sup>(1)</sup>                          | 77 |

| Operating Ratings <sup>(2)</sup>                                 | 77 |

| Electrical Characteristics <sup>(4, 5)</sup>                     | 77 |

| Timing Diagrams                                                  | 79 |

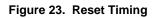

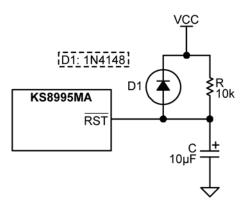

| Reset Circuit Diagram                                            | 86 |

| Selection of Isolation Transformer                               | 87 |

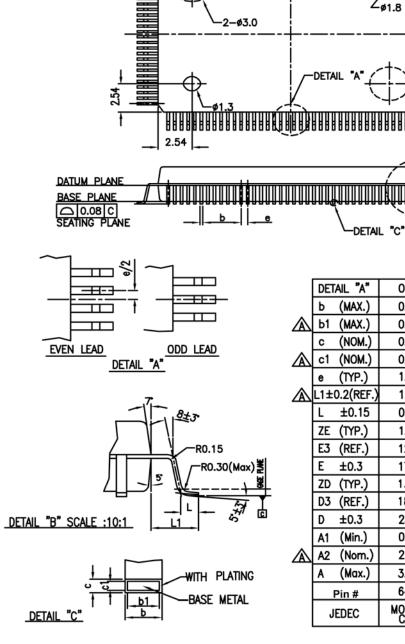

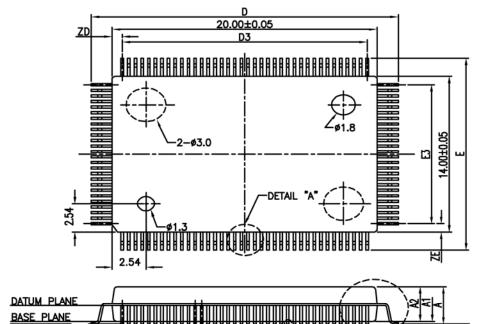

| Package Information                                              |    |

# List of Figures

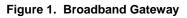

| Figure 1.  | Broadband Gateway                                                       | 11   |

|------------|-------------------------------------------------------------------------|------|

|            | Integrated Broadband Router                                             |      |

|            | Standalone Switch                                                       |      |

|            | Using KS8995FQ for Dual Media Converter or Fiber Daisy Chain Connection |      |

|            | Auto Negotiation                                                        |      |

|            | DA Look-Up Flowchart – 1                                                |      |

| Figure 7.  | DA Resolution Flowchart – Stage 2                                       | . 32 |

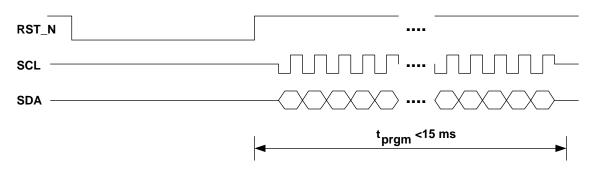

|            | KS8995MA/FQ EEPROM Configuration Timing Diagram                         |      |

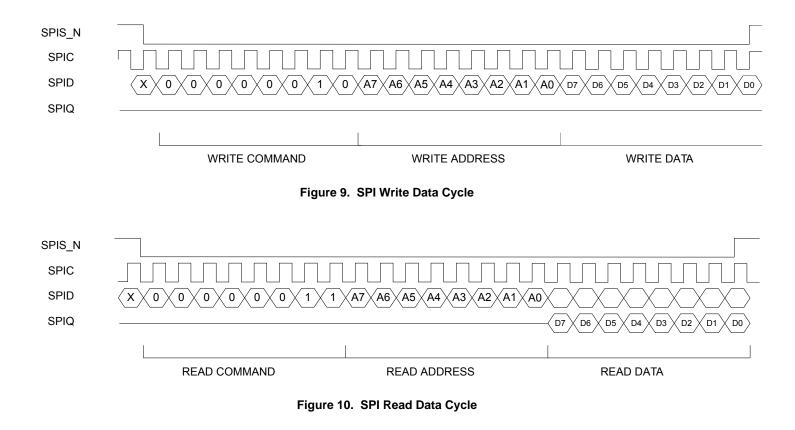

|            | SPI Write Data Cycle                                                    |      |

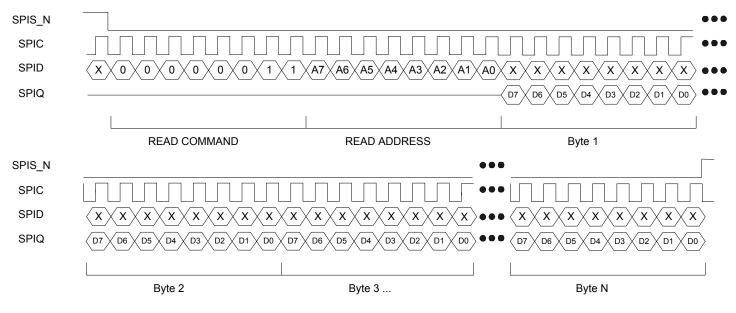

|            | SPI Read Data Cycle                                                     |      |

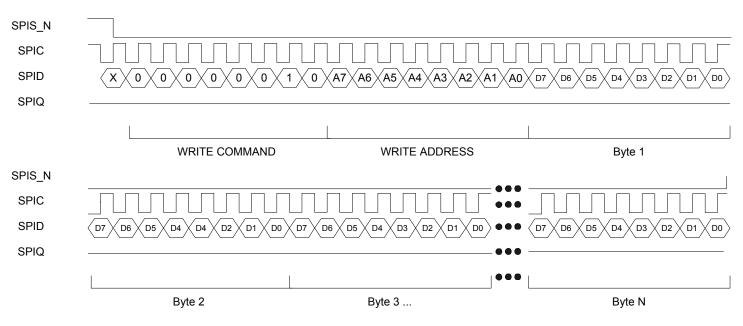

|            | SPI Multiple Write                                                      |      |

|            | SPI Multiple Read                                                       |      |

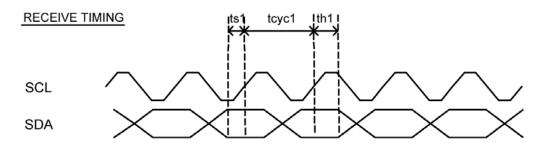

| Figure 13. | EEPROM Interface Input Receive Timing Diagram                           | .79  |

| Figure 14. | EEPROM Interface Output Transmit Timing Diagram                         | . 79 |

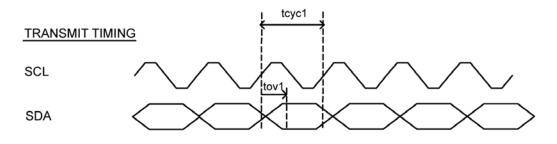

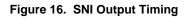

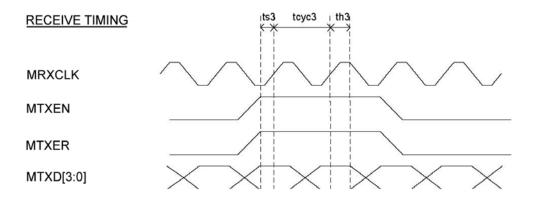

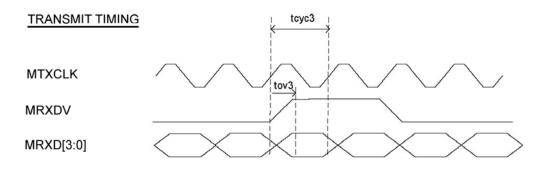

| Figure 15. | SNI Input Timing                                                        | . 80 |

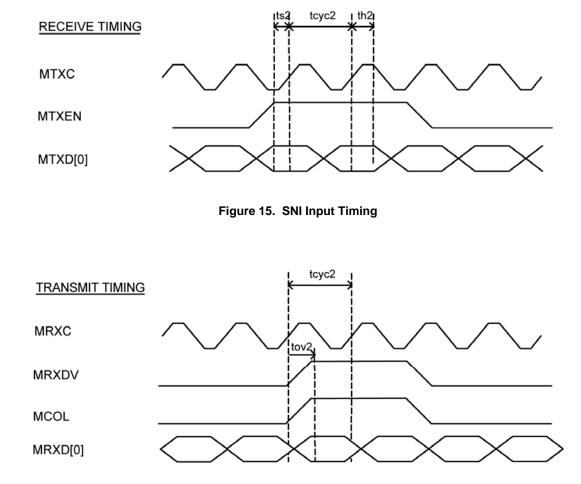

| Figure 16. | SNI Output Timing                                                       | . 80 |

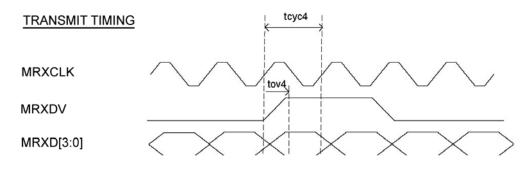

| Figure 17. | MAC Mode MII Timing – Data Received from MII                            | . 81 |

|            | MAC Mode MII Timing – Data Transmitted from MII                         |      |

| Figure 19. | PHY Mode MII Timing – Data Received from MII                            | . 82 |

| Figure 20. | PHY Mode MII Timing – Data Transmitted from MII                         | . 82 |

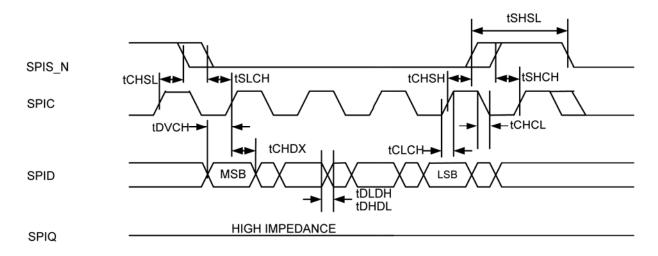

| Figure 21. | SPI Input Timing                                                        | . 83 |

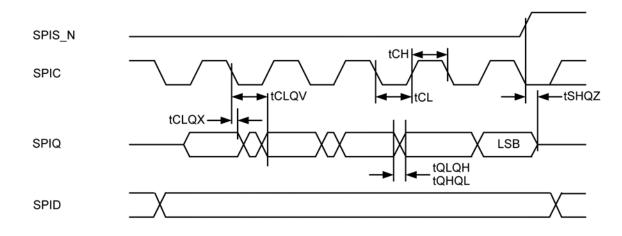

| Figure 22. | SPI Output Timing                                                       | . 84 |

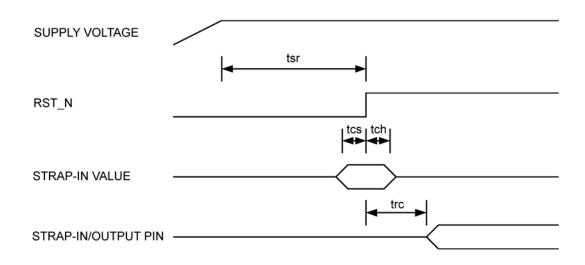

| Figure 23. | Reset Timing                                                            | . 85 |

| Figure 24. | Recommended Reset Circuit                                               | . 86 |

| Figure 25. | Recommended Circuit for Interfacing with CPU/FPGA Reset                 | . 86 |

# List of Tables

| Table 1   | MU DE Signala (DHV Moda)                        | 24 |

|-----------|-------------------------------------------------|----|

|           | MII – P5 Signals (PHY Mode)                     |    |

| Table 2.  | MII – SW Signals                                | 35 |

| Table 3.  | SNI Signals                                     |    |

|           | STPID Egress Rules (Processor to Switch Port 5) |    |

| Table 6.  | STPID Egress Rules (Switch to Processor)        |    |

| Table 7.  | FID+DA Look-Up in the VLAN Mode                 | 40 |

| Table 8.  | FID+SA Look-Up in the VLAN Mode                 | 40 |

| Table 9.  | SPI Connections                                 | 44 |

| Table 10. | EEPROM Timing Parameters                        | 79 |

| Table 11. | SNI Timing Parameters                           | 80 |

| Table 12. | MAC Mode MII Timing Parameters                  | 81 |

| Table 13. | PHY Mode MII Timing Parameters                  |    |

| Table 14. | SPI Input Timing Parameters                     |    |

| Table 15. | SPI Output Timing Parameters                    |    |

| Table 16. | Reset Timing Parameters                         |    |

| Table 17. | Qualified Magnetic Vendors                      |    |

## **System Level Applications**

Figure 2. Integrated Broadband Router

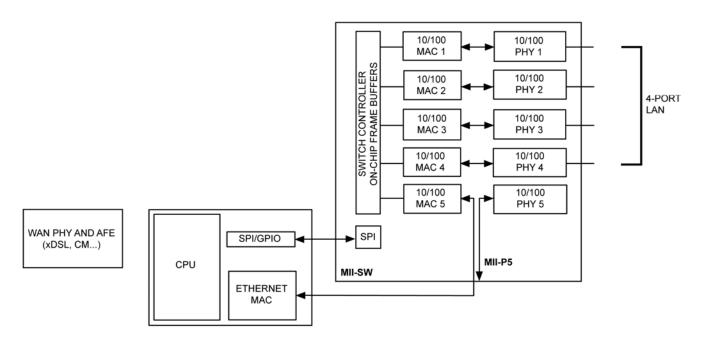

## System Level Applications (Continued)

Figure 3. Standalone Switch

Figure 4. Using KS8995FQ for Dual Media Converter or Fiber Daisy Chain Connection

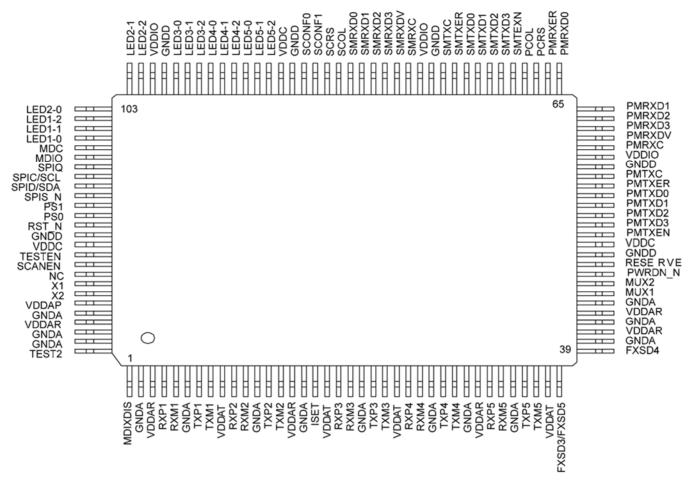

## **Pin Configuration**

128-Pin PQFP

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port  | Pin Function <sup>(2)</sup>                                                                                           |  |

|------------|----------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------|--|

| 1          | MDI-XDIS | lpd                 | 1 – 5 | Disable auto MDI/MDI-X.<br>PD (default) = normal operation.<br>PU = disable auto MDI/MDI-X on all ports.              |  |

| 2          | GNDA     | GND                 |       | Analog ground.                                                                                                        |  |

| 3          | VDDAR    | Р                   |       | 1.8V analog V <sub>DD</sub> .                                                                                         |  |

| 4          | RXP1     | I                   | 1     | Physical receive signal + (differential).                                                                             |  |

| 5          | RXM1     | I                   | 1     | Physical receive signal – (differential).                                                                             |  |

| 6          | GNDA     | GND                 |       | Analog ground.                                                                                                        |  |

| 7          | TXP1     | 0                   | 1     | Physical transmit signal + (differential).                                                                            |  |

| 8          | TXM1     | 0                   | 1     | Physical transmit signal – (differential).                                                                            |  |

| 9          | VDDAT    | Р                   |       | 3.3V analog $V_{\text{DD}}$ (2.5V or 3.3V is for B3 and previous chip revision). 3.3V is recommended for new design.  |  |

| 10         | RXP2     | I                   | 2     | Physical receive signal + (differential).                                                                             |  |

| 11         | RXM2     | I                   | 2     | Physical receive signal – (differential).                                                                             |  |

| 12         | GNDA     | GND                 |       | Analog ground.                                                                                                        |  |

| 13         | TXP2     | 0                   | 2     | Physical transmit signal + (differential).                                                                            |  |

| 14         | TXM2     | 0                   | 2     | Physical transmit signal – (differential).                                                                            |  |

| 15         | VDDAR    | Р                   |       | 1.8V analog V <sub>DD</sub> .                                                                                         |  |

| 16         | GNDA     | GND                 |       | Analog ground.                                                                                                        |  |

| 17         | ISET     |                     |       | Set physical transmit output current. Pull-down with a 3.01k $\Omega$ 1% resistor.                                    |  |

| 18         | VDDAT    | Р                   |       | 3.3V analog $V_{\text{DD}}.$ (2.5V or 3.3V is for B3 and previous chip revision). 3.3V is recommended for new design. |  |

| 19         | RXP3     | I                   | 3     | Physical receive signal + (differential).                                                                             |  |

| 20         | RXM3     | I                   | 3     | Physical receive signal - (differential).                                                                             |  |

| 21         | GNDA     | GND                 |       | Analog ground.                                                                                                        |  |

| 22         | TXP3     | 0                   | 3     | Physical transmit signal + (differential).                                                                            |  |

| 23         | TXM3     | 0                   | 3     | Physical transmit signal – (differential).                                                                            |  |

| 24         | VDDAT    | Р                   |       | 3.3V analog $V_{\text{DD}}$ (2.5V or 3.3V is for B3 and previous chip revision). 3.3V is recommended for new design.  |  |

| 25         | RXP4     | I                   | 4     | Physical receive signal + (differential).                                                                             |  |

| 26         | RXM4     | I                   | 4     | Physical receive signal - (differential).                                                                             |  |

| 27         | GNDA     | GND                 |       | Analog ground.                                                                                                        |  |

| 28         | TXP4     | 0                   | 4     | Physical transmit signal + (differential).                                                                            |  |

| 29         | TXM4     | 0                   | 4     | Physical transmit signal – (differential).                                                                            |  |

| 30         | GNDA     | GND                 |       | Analog ground.                                                                                                        |  |

Notes: 1.

P = Power supply.

I = Input.

O = Output. I/O = Bidirectional.

GND = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down. Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise. NC = No connect.

2. PU = Strap pin pull-up.

PD = Strap pull-down.

| Pin Number | Pin Name    | Type <sup>(1)</sup> | Port | Pin Function                                                              |                                                                                     |                            |

|------------|-------------|---------------------|------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------|

| 31         | VDDAR       | Р                   |      | 1.8V analog V <sub>DD</sub> .                                             |                                                                                     |                            |

| 32         | RXP5        | I                   | 5    | Physical receive signal + (diffe                                          | erential).                                                                          |                            |

| 33         | RXM5        | I                   | 5    | Physical receive signal – (diffe                                          | erential).                                                                          |                            |

| 34         | GNDA        | GND                 |      | Analog ground.                                                            |                                                                                     |                            |

| 35         | TXP5        | 0                   | 5    | Physical transmit signal + (diff                                          | erential).                                                                          |                            |

| 36         | TXM5        | 0                   | 5    | Physical transmit signal – (diff                                          | erential).                                                                          |                            |

| 37         | VDDAT       | Р                   |      | 3.3V analog V <sub>DD</sub> . (2.5V or $3.3$ ' recommended for new design | 3.3V analog $V_{DD}$ . (2.5V or 3.3V is for B3 and previous chip revision). 3.3V is |                            |

| 38         | FXSD5/FXSD3 | lpd                 | 5/3  | Fiber signal detect pin. FXSD<br>of the KS8995FQ                          | 5 is for port 5 of the KS89                                                         | 995MA. FXSD3 is for port 3 |

| 39         | FXSD4       | lpd                 | 4    | Fiber signal detect pin for port                                          | 4.                                                                                  |                            |

| 40         | GNDA        | GND                 |      | Analog ground.                                                            |                                                                                     |                            |

| 41         | VDDAR       | Р                   |      | 1.8V analog V <sub>DD</sub> .                                             |                                                                                     |                            |

| 42         | GNDA        | GND                 |      | Analog ground.                                                            |                                                                                     |                            |

| 43         | VDDAR       | Р                   |      | 1.8V analog V <sub>DD</sub> .                                             |                                                                                     |                            |

| 44         | GNDA        | GND                 |      | Analog ground.                                                            |                                                                                     |                            |

| 45         | MUX1        | NC                  |      | Factory test pins. MUX1 and I                                             | MUX2 should be left unco                                                            | onnected for normal        |

|            | MUX2        | NC                  |      | operation.                                                                | operation.                                                                          |                            |

| 46         |             |                     |      | Mode                                                                      | MUX1                                                                                | MUX2                       |

|            |             |                     |      | Normal Operation                                                          | NC                                                                                  | NC                         |

| 47         | PWRDN_N     | lpu                 |      | Full-chip power down. Active                                              | ow.                                                                                 |                            |

| 48         | RESERVE     | NC                  |      | Reserved pin. No connect.                                                 |                                                                                     |                            |

| 49         | GNDD        | GND                 |      | Digital ground.                                                           |                                                                                     |                            |

| 50         | VDDC        | Р                   |      | 1.8V digital core V <sub>DD</sub> .                                       |                                                                                     |                            |

| 51         | PMTXEN      | Ipd                 | 5    | PHY[5] MII transmit enable.                                               |                                                                                     |                            |

| 52         | PMTXD3      | lpd                 | 5    | PHY[5] MII transmit bit 3.                                                |                                                                                     |                            |

| 53         | PMTXD2      | lpd                 | 5    | PHY[5] MII transmit bit 2.                                                |                                                                                     |                            |

| 54         | PMTXD1      | lpd                 | 5    | PHY[5] MII transmit bit 1.                                                |                                                                                     |                            |

| 55         | PMTXD0      | lpd                 | 5    | PHY[5] MII transmit bit 0.                                                |                                                                                     |                            |

| 56         | PMTXER      | Ipd                 | 5    | PHY[5] MII transmit error.                                                |                                                                                     |                            |

| 57         | PMTXC       | 0                   | 5    | PHY[5] MII transmit clock. PH                                             | Y mode MII.                                                                         |                            |

| 58         | GNDD        | GND                 |      | Digital ground.                                                           |                                                                                     |                            |

| 59         | VDDIO       | Р                   |      | 3.3V digital V <sub>DD</sub> for digital I/O circuitry.                   |                                                                                     |                            |

| 60         | PMRXC       | 0                   | 5    | PHY[5] MII receive clock. PHY                                             | / mode MII.                                                                         |                            |

Note:

P = Power supply. I = Input.

1.

O = Output.

I/O = Bidirectional.

I/O = Bidirectional.

GND = Ground.

Ipu = Input w/internal pull-up.

Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

NC = No connect.

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port                                                                                                                                                          | Pin Function <sup>(2)</sup>                                                                                                                                                                                              |  |

|------------|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 61         | PMRXDV   | lpd/O               | 5                                                                                                                                                             | PHY[5] MII receive data valid.                                                                                                                                                                                           |  |

| 62         | PMRXD3   | Ipd/O               | 5                                                                                                                                                             | PHY[5] MII receive bit 3. Strap option: PD (default) = enable flow control;<br>PU = disable flow control.                                                                                                                |  |

| 63         | PMRXD2   | Ipd/O               | 5                                                                                                                                                             | PHY[5] MII receive bit 2. Strap option: PD (default) = disable back pressure;<br>PU = enable back pressure.                                                                                                              |  |

| 64         | PMRXD1   | Ipd/O               | 5                                                                                                                                                             | PHY[5] MII receive bit 1. Strap option: PD (default) = drop excessive collision packets;<br>PU = does not drop excessive collision packets.                                                                              |  |

| 65         | PMRXD0   | Ipd/O               | 5                                                                                                                                                             | PHY[5] MII receive bit 0. Strap option: PD (default) = disable aggressive back-off algorithm in half-duplex mode; PU = enable for performance enhancement.                                                               |  |

| 66         | PMRXER   | Ipd/O               | 5                                                                                                                                                             | PHY[5] MII receive error. Strap option: PD (default) = packet size 1518/1522 bytes;<br>PU = 1536 bytes.                                                                                                                  |  |

| 67         | PCRS     | lpd/O               | 5                                                                                                                                                             | PHY[5] MII carrier sense/strap option for port 4 only. PD (default) = force half-duplex if auto-negotiation is disabled or fails. PU = force full-duplex if auto negotiation is disabled or fails. Refer to Register 76. |  |

| 68         | PCOL     | lpd/O               | 5 PHY[5] MII collision detect/ strap option for port 4 only. PD (default) = no fo<br>control, normal operation. PU = force flow control. Refer to Register 66 |                                                                                                                                                                                                                          |  |

| 69         | SMTXEN   | lpd                 |                                                                                                                                                               | Switch MII transmit enable.                                                                                                                                                                                              |  |

| 70         | SMTXD3   | lpd                 |                                                                                                                                                               | Switch MII transmit bit 3.                                                                                                                                                                                               |  |

| 71         | SMTXD2   | lpd                 |                                                                                                                                                               | Switch MII transmit bit 2.                                                                                                                                                                                               |  |

| 72         | SMTXD1   | lpd                 |                                                                                                                                                               | Switch MII transmit bit 1.                                                                                                                                                                                               |  |

| 73         | SMTXD0   | lpd                 |                                                                                                                                                               | Switch MII transmit bit 0.                                                                                                                                                                                               |  |

| 74         | SMTXER   | lpd                 |                                                                                                                                                               | Switch MII transmit error.                                                                                                                                                                                               |  |

| 75         | SMTXC    | I/O                 |                                                                                                                                                               | Switch MII transmit clock. Input in MAC mode, output in PHY mode MII.                                                                                                                                                    |  |

| 76         | GNDD     | GND                 |                                                                                                                                                               | Digital ground.                                                                                                                                                                                                          |  |

| 77         | VDDIO    | Р                   |                                                                                                                                                               | 3.3V digital $V_{DD}$ for digital I/O circuitry.                                                                                                                                                                         |  |

| 78         | SMRXC    | I/O                 |                                                                                                                                                               | Switch MII receive clock. Input in MAC mode, output in PHY mode MII.                                                                                                                                                     |  |

| 79         | SMRXDV   | lpd/O               |                                                                                                                                                               | Switch MII receive data valid.                                                                                                                                                                                           |  |

| 80         | SMRXD3   | Ipd/O               |                                                                                                                                                               | Switch MII receive bit 3. Strap option: PD (default) = Disable Switch MII full-duplex flow control; PU = Enable Switch MII full-duplex flow control.                                                                     |  |

| 81         | SMRXD2   | lpd/O               |                                                                                                                                                               | Switch MII receive bit 2. Strap option: PD (default) = Switch MII in full-duplex mode;<br>PU = Switch MII in half-duplex mode.                                                                                           |  |

Notes:

2.

P = Power supply. 1.

I = Input.

O = Output.

I/O = Bidirectional.

GND = Ground.

Ipu = Input w/internal pull-up. Ipd = Input w/internal pull-down. Ipd/O = Input w/internal pull-down during reset, output pin otherwise. Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

$$NC = No connect.$$

-up. PD = Strap pull-down.

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function <sup>(2)</sup>                                                                                                      | Pin Function <sup>(2)</sup>                                                                                              |                   |                                         |  |  |

|------------|----------|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------|--|--|

| 82         | SMRXD1   | Ipd/O               |      | Switch MII receive bit 1. Strap option: PD (default) = Switch MII in 100Mbps mode; PU = Switch MII in 10Mbps mode.               |                                                                                                                          |                   |                                         |  |  |

|            |          |                     |      |                                                                                                                                  | Switch MII receive bit 0; Strap option: LED mode; PD (default) = mode 0; PU = mod<br>See "Register 11". Mode 0, link at: |                   |                                         |  |  |

|            |          |                     |      | 100/Full LEDx[2,1,0]=                                                                                                            | =0,0,0 100                                                                                                               | 0/Half L          | EDx[2,1,0]=0,1,0                        |  |  |

|            |          |                     |      | 10/Full LEDx[2,1,0]=                                                                                                             | =0,0,1 10/                                                                                                               | /Half L           | .EDx[2,1,0]=0,1,1                       |  |  |

|            |          |                     |      | Mode 1, link at                                                                                                                  |                                                                                                                          |                   |                                         |  |  |

| 83         | SMRXD0   | lpd/O               |      | 100/Full LEDx[2,1,0]=                                                                                                            | =0,1,0 100                                                                                                               | 0/Half L          | EDx[2,1,0]=0,1,1                        |  |  |

|            | _        |                     |      | 10/Full LEDx[2,1,0]=                                                                                                             | =1,0,0 10/                                                                                                               | /Half L           | .EDx[2,1,0]=1,0,1                       |  |  |

|            |          |                     |      |                                                                                                                                  | Mode 0                                                                                                                   |                   | Mode 1                                  |  |  |

|            |          |                     |      | LEDX_2                                                                                                                           | Lnk/Act                                                                                                                  |                   | 100Lnk/Act                              |  |  |

|            |          |                     |      | LEDX_1                                                                                                                           | Fulld/Col                                                                                                                |                   | 10Lnk/Act                               |  |  |

|            |          |                     |      | LEDX_0                                                                                                                           | Speed                                                                                                                    |                   | Full duplex                             |  |  |

| 84         | SCOL     | lpd/O               |      | Switch MII collision d                                                                                                           | etect.                                                                                                                   |                   |                                         |  |  |

| 85         | SCRS     | lpd/O               |      | Switch mode carrier sense.                                                                                                       |                                                                                                                          |                   |                                         |  |  |

| 86         | SCONF1   | lpd                 |      | Dual MII configuration pin. For the Switch MII, KSZ8995MA supports both MAC mode and PHY mode, KSZ8995FQ supports PHY mode only. |                                                                                                                          |                   |                                         |  |  |

|            |          |                     |      | Pin# (91, 86, 87):                                                                                                               | Switch MI                                                                                                                | II                | PHY [5] MII                             |  |  |

|            |          |                     |      | 000                                                                                                                              | Disable, Ot                                                                                                              | tri               | Disable, Otri                           |  |  |

|            |          |                     |      | 001                                                                                                                              | PHY Mode N                                                                                                               | MII               | Disable, Otri                           |  |  |

|            |          |                     |      | 010                                                                                                                              | MAC Mode I                                                                                                               | MII               | Disable, Otri                           |  |  |

|            |          |                     |      | 011                                                                                                                              | PHY Mode S                                                                                                               | SNI               | Disable, Otri                           |  |  |

|            |          |                     |      | 100                                                                                                                              | Disable                                                                                                                  |                   | Disable                                 |  |  |

|            |          |                     |      | 101                                                                                                                              | PHY Mode N                                                                                                               | MII               | PHY Mode MII                            |  |  |

|            |          |                     |      | 110                                                                                                                              | MAC Mode I                                                                                                               | MII               | PHY Mode MII                            |  |  |

|            |          |                     |      | 111                                                                                                                              | PHY Mode S                                                                                                               | SNI               | PHY Mode MII                            |  |  |

| 87         | SCONF0   | lpd                 |      | Dual MII configuration                                                                                                           | n pin.                                                                                                                   |                   |                                         |  |  |

| 88         | GNDD     | GND                 |      | Digital ground.                                                                                                                  |                                                                                                                          |                   |                                         |  |  |

| 89         | VDDC     | Р                   |      | 1.8V digital core V <sub>DD</sub> .                                                                                              |                                                                                                                          |                   |                                         |  |  |

| 90         | LED5-2   | lpu/O               | 5    | LED indicator 2. Strap option: aging setup. See "Aging" section.<br>PU (default) = aging enable; PD = aging disable.             |                                                                                                                          |                   |                                         |  |  |

| 91         | LED5-1   | lpu/O               | 5    | LED indicator 1. Stra<br>PHY[5] MII output. Se                                                                                   | p option: PU (de<br>ee "Pin 86 SCO                                                                                       | efault):<br>NF1." | enable PHY[5] MII I/F. PD: tristate all |  |  |

Notes:

1.

P = Power supply.

I = Input. O = Output.

I/O = Bidirectional. GND = Ground.

Ipu = Input w/internal pull-up. Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

NC = No connect. 2.

PU = Strap pin pull-up.

PD = Strap pull-down.

Otri = Output tristated. Fulld = Full duplex

| Pin Number | Pin Name  | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                                                                                                                                                      |                                                            |

|------------|-----------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 92         | LED5-0    | Ipu/O               | 5    | LED indicator 0.                                                                                                                                                                                                                                                  |                                                            |

| 93         | LED4-2    | Ipu/O               | 4    | LED indicator 2.                                                                                                                                                                                                                                                  |                                                            |

| 94         | LED4-1    | Ipu/O               | 4    | LED indicator 1.                                                                                                                                                                                                                                                  |                                                            |

| 95         | LED4-0    | lpu/O               | 4    | LED indicator 0.                                                                                                                                                                                                                                                  |                                                            |

| 96         | LED3-2    | lpu/O               | 3    | LED indicator 2.                                                                                                                                                                                                                                                  |                                                            |

| 97         | LED3-1    | lpu/O               | 3    | LED indicator 1.                                                                                                                                                                                                                                                  |                                                            |

| 98         | LED3-0    | lpu/O               | 3    | LED indicator 0.                                                                                                                                                                                                                                                  |                                                            |

| 99         | GNDD      | GND                 |      | Digital ground.                                                                                                                                                                                                                                                   |                                                            |

| 100        | VDDIO     | Р                   |      | 3.3V digital $V_{DD}$ for digital I/O.                                                                                                                                                                                                                            |                                                            |

| 101        | LED2-2    | lpu/O               | 2    | LED indicator 2.                                                                                                                                                                                                                                                  |                                                            |

| 102        | LED2-1    | lpu/O               | 2    | LED indicator 1.                                                                                                                                                                                                                                                  |                                                            |

| 103        | LED2-0    | lpu/O               | 2    | LED indicator 0.                                                                                                                                                                                                                                                  |                                                            |

| 104        | LED1-2    | lpu/O               | 1    | LED indicator 2.                                                                                                                                                                                                                                                  |                                                            |

| 105        | LED1-1    | Ipu/O               | 1    | LED indicator 1.                                                                                                                                                                                                                                                  |                                                            |

| 106        | LED1-0    | lpu/O               | 1    | LED indicator 0.                                                                                                                                                                                                                                                  |                                                            |

| 107        | MDC       | lpu                 | All  | Switch or PHY[5] MII management data clock.                                                                                                                                                                                                                       |                                                            |

| 108        | MDIO      | I/O                 | All  | Switch or PHY[5] MII management data<br>Features internal pull down to define pi                                                                                                                                                                                  |                                                            |

| 109        | SPIQ      | Otri                | All  | SPI serial data output in SPI slave mod<br>Note: an external pull-up is needed on                                                                                                                                                                                 |                                                            |

| 110        | SPIC/SCL  | I/O                 | All  |                                                                                                                                                                                                                                                                   | mode; (2) output clock at 61kHz in I <sup>2</sup> C master |

| 111        | SSPID/SDA | I/O                 | All  | (1) Serial data input in SPI slave mode.<br>mode. See "Pin 113."                                                                                                                                                                                                  | ; (2) serial data input/output in I <sup>2</sup> C master  |

|            |           |                     |      | Note: an external pull-up is needed on                                                                                                                                                                                                                            | this pin when it is in use.                                |

| 112        | SPIS_N    | lpu                 | All  | Active low. (1) SPI data transfer start in SPI slave mode. When SPIS_N is high, the KS8995MA/FQ is deselected and SPIQ is held in high impedance state, a high-to-low transition to initiate the SPI data transfer; (2) not used in I <sup>2</sup> C master mode. |                                                            |

|            |           |                     |      | Serial bus configuration pin. For this case, if the EEPROM is not present, the KS8995MA/FQ will start itself with the PS[1.0] = 00 default register values.                                                                                                       |                                                            |

|            |           |                     |      | Pin Configuration                                                                                                                                                                                                                                                 | Serial Bus Configuration                                   |

| 113        | PS1       | lpd                 |      | PS[1.0]=00                                                                                                                                                                                                                                                        | I <sup>2</sup> C Master Mode for EEPROM                    |

|            |           |                     |      | PS[1.0]=01                                                                                                                                                                                                                                                        | Reserved                                                   |

|            |           |                     |      | PS[1.0]=10                                                                                                                                                                                                                                                        | SPI Slave Mode for CPU Interface                           |

|            |           |                     |      | PS[1.0]=11                                                                                                                                                                                                                                                        | Factory Test Mode (BIST)                                   |

Note: 1.

P = Power supply.

I = Input.

O = Output.

I/O = Bidirectional.

GND = Ground.

Ipu = Input w/internal pull-up. Ipd = Input w/internal pull-down.

Ipd/O = Input w/internal pull-down during reset, output pin otherwise.

Ipu/O = Input w/internal pull-up during reset, output pin otherwise.

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                                   |  |

|------------|----------|---------------------|------|------------------------------------------------------------------------------------------------|--|

| 114        | PS0      | lpd                 |      | Serial bus configuration pin. See "Pin 113."                                                   |  |

| 115        | RST_N    | lpu                 |      | Reset the KS8995MA/FQ. Active low.                                                             |  |

| 116        | GNDD     | GND                 |      | Digital ground.                                                                                |  |

| 117        | VDDC     | Р                   |      | 1.8V digital core V <sub>DD</sub> .                                                            |  |

| 118        | TESTEN   | lpd                 |      | NC for normal operation. Factory test pin.                                                     |  |

| 119        | SCANEN   | lpd                 |      | NC for normal operation. Factory test pin.                                                     |  |

| 120        | NC       | NC                  |      | No connect.                                                                                    |  |

| 121        | X1       | I                   |      | 25MHz crystal clock connection/or 3.3V tolerant oscillator input. Oscillator should be ±50ppm. |  |

| 122        | X2       | 0                   |      | 25MHz crystal clock connection.                                                                |  |

| 123        | VDDAP    | Р                   |      | 1.8V analog $V_{DD}$ for PLL.                                                                  |  |

| 124        | GNDA     | GND                 |      | Analog ground.                                                                                 |  |

| 125        | VDDAR    | Р                   |      | 1.8V analog V <sub>DD</sub> .                                                                  |  |

| 126        | GNDA     | GND                 |      | Analog ground.                                                                                 |  |

| 127        | GNDA     | GND                 |      | Analog ground.                                                                                 |  |

| 128        | TEST2    | NC                  |      | NC for normal operation. Factory test pin.                                                     |  |

Note: 1.

P = Power supply. I = Input.

O = Output. I/O = Bidirectional.

GND = Ground.

Ipu = Input w/internal pull-up

$\begin{aligned} &|pu| = \text{Input w/internal pull-down.} \\ &|pd/O = \text{Input w/internal pull-down during reset, output pin otherwise.} \\ &|pu/O = \text{Input w/internal pull-up during reset, output pin otherwise.} \end{aligned}$

| Pin Number | Pin Name        | Type <sup>(1)</sup> | Port | Pin Function                                                                       |  |

|------------|-----------------|---------------------|------|------------------------------------------------------------------------------------|--|

| 39         | FXSD4           | I                   | 4    | Fiber signal detect/Factory test pin.                                              |  |

| 38         | FXSD3/FXS<br>D5 | Ι                   | 3/5  | Fiber signal detect/Factory test pin for FQ port 3 or MA port 5                    |  |

| 124        | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 42         | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 44         | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 2          | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 16         | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 30         | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 6          | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 12         | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 21         | GNDA            | GND                 |      | Analog ground.                                                                     |  |

| 27         | GNDA            | GND                 |      | Analog ground.                                                                     |  |