# SuperSpeed USB 3.1 Gen 1 to 10/100/1000 Ethernet Controller with RGMII

# **Highlights**

- Single Chip SuperSpeed (SS) USB 3.1 Gen 1 to 10/100/1000 Ethernet Controller

- RGMII output to external Gigabit PHYs

- Integrated 10/100/1000 Ethernet MAC (Full-Duplex Support)

- Integrated USB 3.1 Gen 1 SS Device Controller and PHY

- Low Power Consumption

- Compliant with Energy Efficient Ethernet IEEE 802.3az

- Wake on LAN support (WoL)

- Configuration via One Time Programmable (OTP) Memory

- NetDetach provides automatic USB attach/detach when Ethernet cable is connected/removed

- AEC-Q100 qualified for automotive applications

# **Target Applications**

- · Automotive Infotainment

- · Notebook/Tablet Docking Stations

- Detachable Laptops

- USB Port Replicators

- · Standalone USB to Ethernet Dongles

- Embedded Systems / CE Devices

- · Set-Top Boxes / Video Recorders

- · Test Instrumentation / Industrial

## **System Considerations**

- Power and I/Os

- Multiple power management features

- 12 GPIOs

- Supports bus and self-powered operation

- Variable voltage I/O supply (1.8V-3.3V)

- Software Support

- Windows 7, 8, 8.1, and 10 drivers (Microsoft Certified)

- Linux driver

- OS X and macOS driver

- uBoot support

- UEFI support

- PXE support

- FreeBSD support

- Windows OTP/EEPROM programming and testing utility

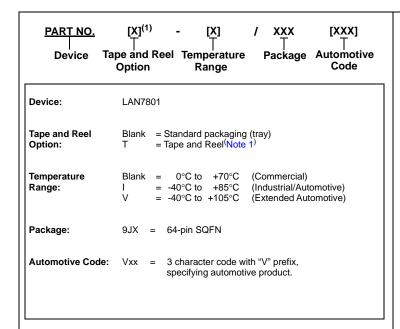

- Packaging

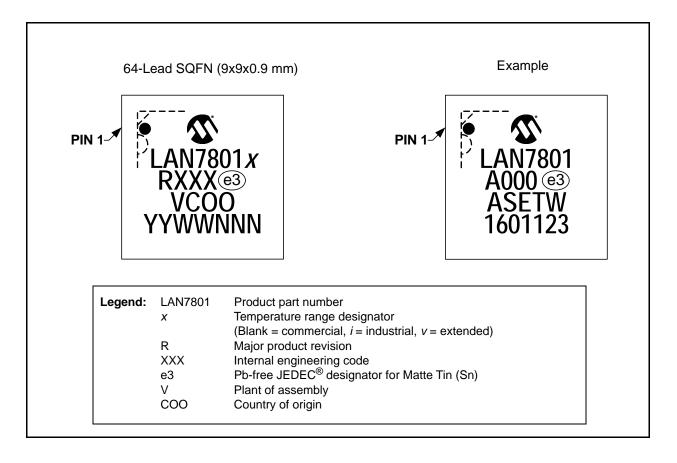

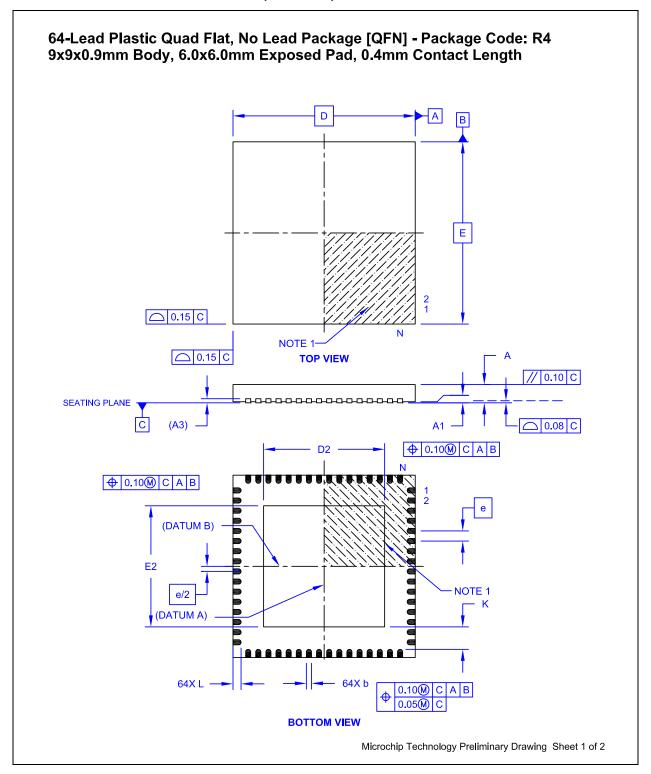

- RoHS compliant 64-pin SQFN (9 x 9 mm)

- Environmental

- Commercial temperature range (0°C to +70°C)

- Automotive temperature range (-40°C to +85°C)

- Extended automotive range (-40°C to +105°C)

## **Key Benefits**

- USB 3.1 Gen 1 Device Controller

- Supports SS (5 Gbps), HS (480 Mbps), and FS (12 Mbps) modes

- Four endpoints supported

- Supports vendor specific commands

- Remote wakeup supported

- 10/100/1000 Ethernet Controller

- Compliant with IEEE802.3/802.3u/802.3ab/802.3az

- -10BASE-T/100BASE-TX/1000BASE-T support

- -Full- and half-duplex capability (only full-duplex operation at 1000 Mbps)

- Controller Modes

- -Microsoft AOAC support (Always On Always Connected)

- -Supports Microsoft NDIS 6.2 large send offload

- -Full-duplex flow control

- -Loop-back modes

- -Supports IEEE 802.1q VLAN tagging

- -VLAN tag based packet filtering (all 4096 tags)

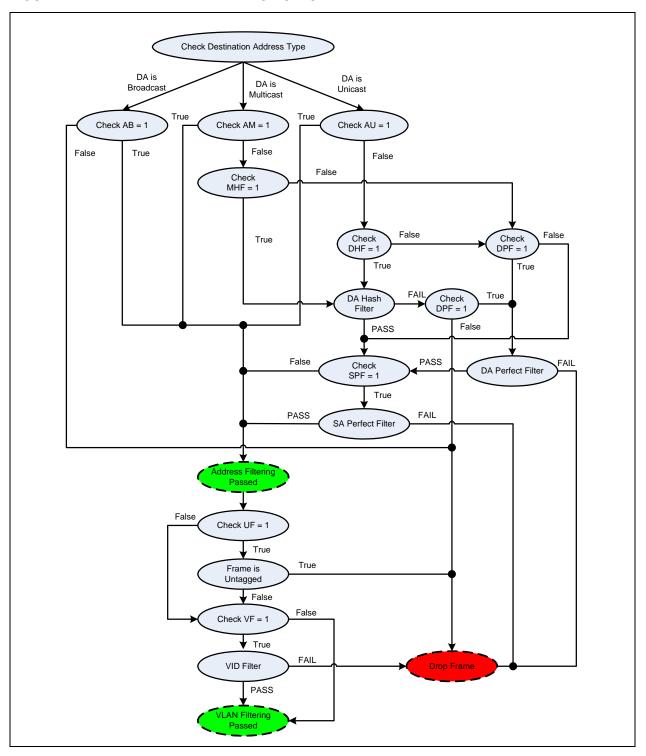

- -Flexible address filtering modes

- -33 exact matches (unicast or multicast)

- -512-bit hash filter for multicast frames

- -Pass all multicast

- -Promiscuous unicast/multicast modes

- -Inverse filtering

- -Pass all incoming with status report

- -Supports various statistical counters

- -PME pin support

- Frame Features

- -Supports 32 wake-up frame patterns

- -Preamble generation and removal

- -Automatic 32-bit CRC generation and checking

- -9 KB jumbo frame support

- -Automatic payload padding and pad removal

- -Supports Rx/Tx checksum offloads (IPv4, IPv6, TCP, UDP, IGMP, ICMP)

- -Ability to add and strip IEEE 802.1q VLAN tags

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| 1.0 Preface                                 |     |

|---------------------------------------------|-----|

| 2.0 Introduction                            | 9   |

| 3.0 Pin Descriptions and Configuration      | 10  |

| 4.0 Power Connections                       |     |

| 5.0 USB Device Controller                   |     |

| 6.0 FIFO Controller (FCT)                   | 49  |

| 7.0 Receive Filtering Engine (RFE)          | 66  |

| 8.0 10/100/1000 Ethernet MAC                | 81  |

| 9.0 EEPROM Controller (EEP)                 | 100 |

| 10.0 One Time Programmable (OTP) Memory     | 120 |

| 11.0 Resets                                 | 121 |

| 12.0 Clocks and Power Management (CPM)      | 123 |

| 13.0 Power Management Event (PME) Operation | 133 |

| 14.0 Register Descriptions                  | 137 |

| 15.0 Operational Characteristics            |     |

| 16.0 Package Information                    | 237 |

| 17.0 Data Sheet Revision History            | 240 |

# 1.0 PREFACE

# 1.1 General Terms

TABLE 1-1: GENERAL TERMS

| Term                       | Description                                                                                                                                                                                      |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10BASE-T                   | 10 Mbps Ethernet, IEEE 802.3 compliant                                                                                                                                                           |  |

| 100BASE-TX                 | 100 Mbps Fast Ethernet, IEEE802.3u compliant                                                                                                                                                     |  |

| 1000BASE-T                 | 100 Mbps Fast Ethernet, IEEE802.3ab compliant                                                                                                                                                    |  |

| ADC                        | Analog-to-Digital Converter                                                                                                                                                                      |  |

| AFE                        | Analog Front End                                                                                                                                                                                 |  |

| ALR                        | Address Logic Resolution                                                                                                                                                                         |  |

| AN                         | Auto-Negotiation                                                                                                                                                                                 |  |

| AOAC                       | Always on Always Connected                                                                                                                                                                       |  |

| ARP                        | Address Resolution Protocol                                                                                                                                                                      |  |

| BELT                       | Best Effort Latency Tolerance                                                                                                                                                                    |  |

| BLW                        | Baseline Wander                                                                                                                                                                                  |  |

| Byte                       | 8 bits                                                                                                                                                                                           |  |

| СРМ                        | Clocks and Power Management                                                                                                                                                                      |  |

| CSMA/CD                    | Carrier Sense Multiple Access/Collision Detect                                                                                                                                                   |  |

| CSR                        | Control and Status Registers                                                                                                                                                                     |  |

| CTR                        | Counter                                                                                                                                                                                          |  |

| DA                         | Destination Address                                                                                                                                                                              |  |

| DWORD                      | 32 bits                                                                                                                                                                                          |  |

| EC                         | Embedded Controller                                                                                                                                                                              |  |

| EEE                        | Energy Efficient Ethernet                                                                                                                                                                        |  |

| EP                         | USB Endpoint                                                                                                                                                                                     |  |

| EPC                        | EEPROM Controller                                                                                                                                                                                |  |

| FCS                        | Frame Check Sequence - The extra checksum characters added to the end of an Ethernet frame, used for error detection and correction.                                                             |  |

| FCT                        | FIFO Controller                                                                                                                                                                                  |  |

| FIFO                       | First In First Out buffer                                                                                                                                                                        |  |

| FS                         | Full Speed                                                                                                                                                                                       |  |

| FSM                        | Finite State Machine                                                                                                                                                                             |  |

| FW                         | Firmware                                                                                                                                                                                         |  |

| GMII                       | Gigabit Media Independent Interface                                                                                                                                                              |  |

| GPIO                       | General Purpose I/O                                                                                                                                                                              |  |

| GPHY                       | Gigabit Ethernet Physical Layer                                                                                                                                                                  |  |

| Host                       | External system (Includes processor, application software, etc.)                                                                                                                                 |  |

| HS                         | High Speed                                                                                                                                                                                       |  |

| HW                         | Hardware. Refers to function implemented by digital logic.                                                                                                                                       |  |

| IGMP                       | Internet Group Management Protocol                                                                                                                                                               |  |

| Inbound                    | Refers to data input to the device from the host                                                                                                                                                 |  |

| LDO                        | Linear Drop-Out Regulator                                                                                                                                                                        |  |

| Level-Triggered Sticky Bit | This type of status bit is set whenever the condition that it represents is asserted. The bit remains set until the condition is no longer true and the status bit is cleared by writing a zero. |  |

TABLE 1-1: GENERAL TERMS (CONTINUED)

| Term     | Description                                                                                                                                                                                                                                                                  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LFPS     | Low Frequency Periodic Signal                                                                                                                                                                                                                                                |  |

| LFSR     | Linear Feedback Shift Register                                                                                                                                                                                                                                               |  |

| LPM      | Link Power Management                                                                                                                                                                                                                                                        |  |

| Isb      | Least Significant Bit                                                                                                                                                                                                                                                        |  |

| LSB      | Least Significant Byte                                                                                                                                                                                                                                                       |  |

| LTM      | Latency Tolerance Messaging                                                                                                                                                                                                                                                  |  |

| MAC      | Media Access Controller                                                                                                                                                                                                                                                      |  |

| MDI      | Medium Dependent Interface                                                                                                                                                                                                                                                   |  |

| MDIX     | Media Dependent Interface with Crossover                                                                                                                                                                                                                                     |  |

| MEF      | Multiple Ethernet Frames                                                                                                                                                                                                                                                     |  |

| MII      | Media Independent Interface                                                                                                                                                                                                                                                  |  |

| MIIM     | Media Independent Interface Management                                                                                                                                                                                                                                       |  |

| MIL      | MAC Interface Layer                                                                                                                                                                                                                                                          |  |

| MLD      | Multicast Listening Discovery                                                                                                                                                                                                                                                |  |

| MLT-3    | Multi-Level Transmission Encoding (3-Levels). A tri-level encoding method where a change in the logic level represents a code bit "1" and the logic output remaining at the same level represents a code bit "0".                                                            |  |

| msb      | Most Significant Bit                                                                                                                                                                                                                                                         |  |

| MSB      | Most Significant Byte                                                                                                                                                                                                                                                        |  |

| NRZI     | Non Return to Zero Inverted. This encoding method inverts the signal for a "1" and leaves the signal unchanged for a "0"                                                                                                                                                     |  |

| N/A      | Not Applicable                                                                                                                                                                                                                                                               |  |

| NC       | No Connect                                                                                                                                                                                                                                                                   |  |

| ОТР      | One Time Programmable                                                                                                                                                                                                                                                        |  |

| OUI      | Organizationally Unique Identifier                                                                                                                                                                                                                                           |  |

| Outbound | Refers to data output from the device to the host                                                                                                                                                                                                                            |  |

| PCS      | Physical Coding Sublayer                                                                                                                                                                                                                                                     |  |

| PHY      | Physical Layer                                                                                                                                                                                                                                                               |  |

| PISO     | Parallel In Serial Out                                                                                                                                                                                                                                                       |  |

| PLL      | Phase Locked Loop                                                                                                                                                                                                                                                            |  |

| PMD      | Physical Medium Dependent                                                                                                                                                                                                                                                    |  |

| PME      | Power Management Event                                                                                                                                                                                                                                                       |  |

| PMIC     | Power Management IC                                                                                                                                                                                                                                                          |  |

| POR      | Power on Reset                                                                                                                                                                                                                                                               |  |

| PTP      | Precision Time Protocol                                                                                                                                                                                                                                                      |  |

| QWORD    | 64 bits                                                                                                                                                                                                                                                                      |  |

| RESERVED | Refers to a reserved bit field or address. Unless otherwise noted, reserved bits must always be zero for write operations. Unless otherwise noted, values are not guaranteed when reading reserved bits. Unless otherwise noted, do not read or write to reserved addresses. |  |

| RFE      | Receive Filtering Engine                                                                                                                                                                                                                                                     |  |

| RGMII    | Reduced Gigabit Media Independent Interface                                                                                                                                                                                                                                  |  |

| RMON     | Remote Monitoring                                                                                                                                                                                                                                                            |  |

| RMII     | Reduced Media Independent Interface                                                                                                                                                                                                                                          |  |

| RST      | Reset                                                                                                                                                                                                                                                                        |  |

| RTC      | Real-Time Clock                                                                                                                                                                                                                                                              |  |

|          |                                                                                                                                                                                                                                                                              |  |

# TABLE 1-1: GENERAL TERMS (CONTINUED)

| Term | Description                                                                                         |  |

|------|-----------------------------------------------------------------------------------------------------|--|

| SA   | Source Address                                                                                      |  |

| SCSR | System Control and Status Registers                                                                 |  |

| SEF  | Single Ethernet Frame                                                                               |  |

| SFD  | Start of Frame Delimiter - The 8-bit value indicating the end of the preamble of an Ethernet frame. |  |

| SIPO | Serial In Parallel Out                                                                              |  |

| SMI  | Serial Management Interface                                                                         |  |

| SMNP | Simple Network Management Protocol                                                                  |  |

| SQE  | Signal Quality Error (also known as "heartbeat")                                                    |  |

| SS   | SuperSpeed                                                                                          |  |

| SSD  | Start of Stream Delimiter                                                                           |  |

| TMII | Turbo Media Independent Interface                                                                   |  |

| UDP  | User Datagram Protocol - A connectionless protocol run on top of IP networks                        |  |

| URX  | USB Bulk-Out Receiver                                                                               |  |

| USB  | Universal Serial Bus                                                                                |  |

| UTX  | USB Bulk-In Transmitter                                                                             |  |

| UUID | Universally Unique IDentifier                                                                       |  |

| VSM  | Vendor Specific Messaging                                                                           |  |

| WORD | 16 bits                                                                                             |  |

| ZLP  | Zero Length USB Packet                                                                              |  |

# 1.2 Buffer Types

TABLE 1-2: BUFFER TYPES

| Buffer Type | Description                                                                                                                                                                                                                                   |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VIS         | Variable voltage Schmitt-triggered input                                                                                                                                                                                                      |  |  |

| O8          | Output with 8 mA sink and 8 mA source                                                                                                                                                                                                         |  |  |

| OD8         | Open-drain output with 8 mA sink                                                                                                                                                                                                              |  |  |

| O12         | Output with 12 mA sink and 12 mA source                                                                                                                                                                                                       |  |  |

| OD12        | Open-drain output with 12 mA sink                                                                                                                                                                                                             |  |  |

| PU          | 50 μA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                        |  |  |

|             | Note: Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.  |  |  |

| PD          | 50 μA (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                    |  |  |

|             | Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |  |  |

| Al          | Analog Input                                                                                                                                                                                                                                  |  |  |

| AIO         | Analog bidirectional                                                                                                                                                                                                                          |  |  |

| ICLK        | Crystal oscillator input pin                                                                                                                                                                                                                  |  |  |

| OCLK        | Crystal oscillator output pin                                                                                                                                                                                                                 |  |  |

| Р           | Power pin                                                                                                                                                                                                                                     |  |  |

# 1.3 Register Nomenclature

TABLE 1-3: REGISTER NOMENCLATURE

| Register Bit Type Notation | Register Bit Description                                                                                                                                                                                                                                                                                                         |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R                          | Read: A register or bit with this attribute can be read.                                                                                                                                                                                                                                                                         |

| W                          | Write: A register or bit with this attribute can be written.                                                                                                                                                                                                                                                                     |

| RO                         | Read only: Read only. Writes have no effect.                                                                                                                                                                                                                                                                                     |

| RS                         | Read to Set: This bit is set on read.                                                                                                                                                                                                                                                                                            |

| RC                         | Read to Clear: Contents is cleared after the read. Writes have no effect.                                                                                                                                                                                                                                                        |

| WO                         | Write only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                                                                                                                                              |

| WC                         | Write One to Clear: Writing a one clears the value. Writing a zero has no effect                                                                                                                                                                                                                                                 |

| WAC                        | Write Anything to Clear: Writing anything clears the value.                                                                                                                                                                                                                                                                      |

| LL                         | Latch Low: Clear on read of register.                                                                                                                                                                                                                                                                                            |

| LH                         | Latch High: Clear on read of register.                                                                                                                                                                                                                                                                                           |

| SC                         | <b>Self-Clearing:</b> Contents are self-cleared after the being set. Writes of zero have no effect. Contents can be read.                                                                                                                                                                                                        |

| SS                         | <b>Self-Setting:</b> Contents are self-setting after being cleared. Writes of one have no effect. Contents can be read.                                                                                                                                                                                                          |

| RO/LH                      | <b>Read Only, Latch High:</b> Bits with this attribute will stay high until the bit is read. After it is read, the bit will remain high, but will change to low if the condition that caused the bit to go high is removed. If the bit has not been read, the bit will remain high regardless of a change to the high condition. |

| NALR                       | <b>Not Affected by Lite Reset.</b> The state of NASR bits do not change on assertion of a lite reset.                                                                                                                                                                                                                            |

| NASR                       | <b>Not Affected by Software Reset.</b> The state of NASR bits do not change on assertion of a software reset.                                                                                                                                                                                                                    |

| RESERVED                   | <b>Reserved Field:</b> Reserved fields must be written with zeros, unless otherwise indicated, to ensure future compatibility. The value of reserved bits is not guaranteed on a read.                                                                                                                                           |

## 2.0 INTRODUCTION

# 2.1 General Description

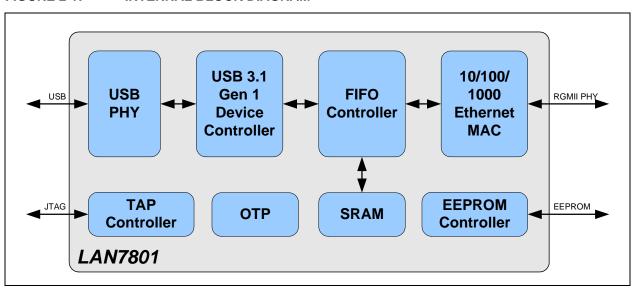

The LAN7801 is a high performance USB 3.1 Gen 1 to 10/100/1000 Ethernet controller with RGMII. With applications ranging from automotive infotainment/ADAS, notebook/tablet docking stations, set-top boxes, and PVRs, to USB port replicators, USB to Ethernet dongles, embedded systems, and test instrumentation, the LAN7801 is a high performance and cost effective USB to Ethernet connectivity solution.

The LAN7801 contains an integrated 10/100/1000 Ethernet MAC, Filtering Engine, USB PHY, SuperSpeed USB 3.1 Gen 1 device controller, TAP controller, EEPROM controller, and a FIFO controller with internal packet buffering.

The internal USB 3.1 Gen 1 device controller and USB PHY are compliant with the USB 3.1 Gen 1 SuperSpeed standard. The LAN7801 implements Control, Interrupt, Bulk-in, and Bulk-out USB Endpoints.

The Ethernet controller is compliant with the IEEE 802.3, IEEE 802.3u, IEEE 802.3ab, and 802.3az (Energy Efficient Ethernet) standards. ARP and NS offload are also supported. The integrated RGMII interface allows connection to an external RGMII Ethernet PHY.

Multiple power management features are provided, including Energy Efficient Ethernet (IEEE 802.3az), support for Microsoft's Always On Always Connected (AOAC), and "Magic Packet", "Wake On LAN", and "Link Status Change" wake events. Wake events can be programmed to initiate a USB remote wakeup. Up to 32 different AOAC wake-up frame patterns are supported along with Microsoft's WPD (Whole Packet Detection).

An internal EEPROM controller exists to load various USB and Ethernet configuration parameters. For EEPROM-less applications, the LAN7801 provides 1K Bytes of OTP memory that can be used to preload this same configuration data before enumeration. The integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

The LAN7801 is available in commercial, automotive, and extended automotive temperature range versions. An internal block diagram of the LAN7801 is shown in Figure 2-1.

FIGURE 2-1: INTERNAL BLOCK DIAGRAM

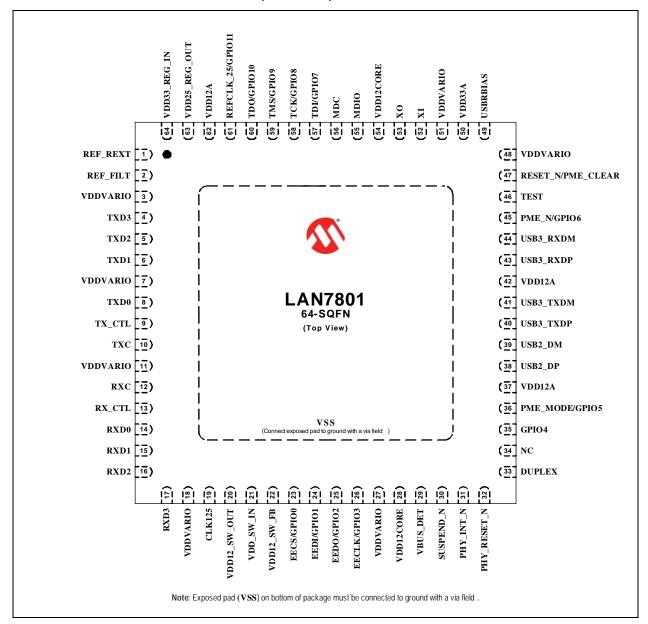

# 3.0 PIN DESCRIPTIONS AND CONFIGURATION

# 3.1 Pin Assignments

FIGURE 3-1: PIN ASSIGNMENTS (TOP VIEW)

**Note:** When an "\_N" is used at the end of the signal name, it indicates that the signal is active low. For example, **RESET\_N** indicates that the reset signal is active low.

The buffer type for each signal is indicated in the "Buffer Type" column of the pin description tables in Section 3.2, "Pin Descriptions". A description of the buffer types is provided in Section 1.2, "Buffer Types".

TABLE 3-1: PIN ASSIGNMENTS

| Pin Number | Pin Name                                      | Pin Number | Pin Name          |  |

|------------|-----------------------------------------------|------------|-------------------|--|

| 1          | REF_REXT                                      | 33         | DUPLEX            |  |

| 2          | REF_FILT                                      | 34         | NC                |  |

| 3          | VDDVARIO                                      | 35         | GPIO4             |  |

| 4          | TXD3                                          | 36         | PME_MODE/GPIO5    |  |

| 5          | TXD2                                          | 37         | VDD12A            |  |

| 6          | TXD1                                          | 38         | USB2_DP           |  |

| 7          | VDDVARIO                                      | 39         | USB2_DM           |  |

| 8          | TXD0                                          | 40         | USB3_TXDP         |  |

| 9          | TX_CTL                                        | 41         | USB3_TXDM         |  |

| 10         | TXC                                           | 42         | VDD12A            |  |

| 11         | VDDVARIO                                      | 43         | USB3_RXDP         |  |

| 12         | RXC                                           | 44         | USB3_RXDM         |  |

| 13         | RX_CTL                                        | 45         | PME_N/GPIO6       |  |

| 14         | RXD0                                          | 46         | TEST              |  |

| 15         | RXD1                                          | 47         | RESET_N/PME_CLEAR |  |

| 16         | RXD2                                          | 48         | VDDVARIO          |  |

| 17         | RXD3                                          | 49         | USBRBIAS          |  |

| 18         | VDDVARIO                                      | 50         | VDD33A            |  |

| 19         | CLK125                                        | 51         | VDDVARIO          |  |

| 20         | VDD12_SW_OUT                                  | 52         | XI                |  |

| 21         | VDD_SW_IN                                     | 53         | XO                |  |

| 22         | VDD12_SW_FB                                   | 54         | VDD12CORE         |  |

| 23         | EECS/GPIO0                                    | 55         | MDIO              |  |

| 24         | EEDI/GPIO1                                    | 56         | MDC               |  |

| 25         | EEDO/GPIO2                                    | 57         | TDI/GPIO7         |  |

| 26         | EECLK/GPIO3                                   | 58         | TCK/GPIO8         |  |

| 27         | VDDVARIO                                      | 59         | TMS/GPIO9         |  |

| 28         | VDD12CORE                                     | 60         | TDO/GPIO10        |  |

| 29         | VBUS_DET                                      | 61         | REFCLK_25/GPIO11  |  |

| 30         | SUSPEND_N                                     | 62         | VDD12A            |  |

| 31         | PHY_INT_N                                     | 63         | VDD25_REG_OUT     |  |

| 32         | PHY_RESET_N                                   | 64         | VDD33_REG_IN      |  |

|            | Exposed Pad (VSS) must be connected to ground |            |                   |  |

# 3.2 Pin Descriptions

**TABLE 3-2: PIN DESCRIPTIONS**

| Name                       | Symbol    | Buffer<br>Type | Description                                                                                                                                                                        |  |

|----------------------------|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RGMII Pins                 |           |                |                                                                                                                                                                                    |  |

| Transmit Data              | TXD[3:0]  | VIS/O12        | The MAC transmits data to the external PHY using these signals.                                                                                                                    |  |

| RGMII Transmit<br>Clock    | TXC       | VIS/O12        | Used to latch data from the MAC into the PHY.  1000BASE-T: 125MHz 100BASE-TX: 25MHz 10BASE-T: 2.5MHz                                                                               |  |

| Transmit Control           | TX_CTL    | VIS/O12        | Indicates both the transmit data enable (TXEN) and transmit error (TXER) functions per the RGMII specification. Indicates the presence of valid transmit data and control signals. |  |

| Receive Data               | RXD[3:0]  | VIS/O12        | The external PHY transfers data to the MAC using these signals.                                                                                                                    |  |

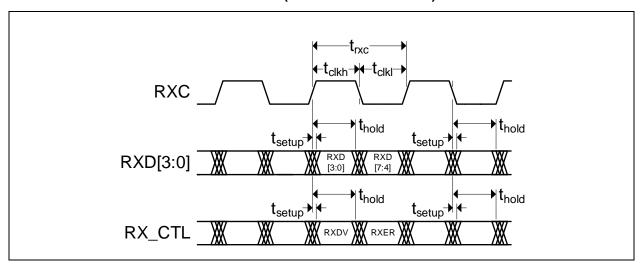

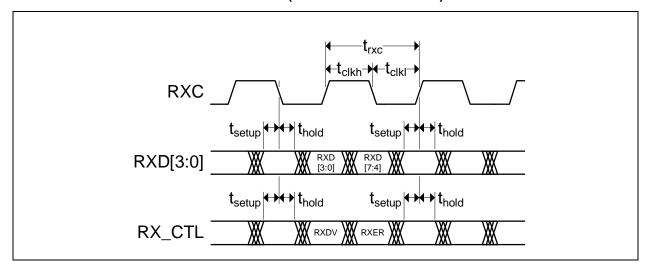

| RGMII Receive<br>Clock     | RXC       | VIS/O12        | Used to transfer data from the external PHY to the MAC.  1000BASE-T: 125MHz 100BASE-TX: 25MHz 10BASE-T: 2.5MHz                                                                     |  |

| Receive Control            | RX_CTL    | VIS/O12        | Indicates both the receive data valid (RXDV) and receive error (RXER) functions per the RGMII specification. Indicates the presence of valid receive data and carrier sense.       |  |

|                            | Seri      | al Managem     | ent Interface (SMI) Pins                                                                                                                                                           |  |

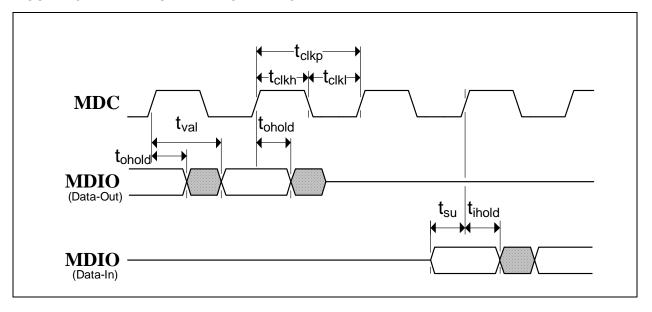

| SMI Clock                  | MDC       | O12            | Serial Management Interface Clock. This is the management clock output to an external Ethernet PHY.                                                                                |  |

| SMI Data Input/<br>Output  | MDIO      | VIS/O8<br>(PU) | Serial Management Interface data input/output. This is the management data to/from an external Ethernet PHY.                                                                       |  |

|                            |           |                | Note: To ensure that the IDLE state of the MDIO signal is a logic one, an external pull-up is required when the MII management interface is used.                                  |  |

|                            |           |                | <b>Note:</b> To avoid a floating signal, an external pull-up is recommended when the MII management interface is not used.                                                         |  |

|                            |           | U              | ISB Pins                                                                                                                                                                           |  |

| USB 3.1 Gen 1<br>DPLUS TX  | USB3_TXDP | AIO            | SuperSpeed USB transmit data plus.                                                                                                                                                 |  |

| USB 3.1 Gen 1<br>DMINUS TX | USB3_TXDM | AIO            | SuperSpeed USB transmit data minus.                                                                                                                                                |  |

| USB 3.1 Gen 1<br>DPLUS RX  | USB3_RXDP | AIO            | SuperSpeed USB receive data plus.                                                                                                                                                  |  |

| USB 3.1 Gen 1<br>DMINUS RX | USB3_RXDM | AIO            | SuperSpeed USB receive data minus.                                                                                                                                                 |  |

| USB 2.0<br>DPLUS           | USB2_DP   | AIO            | Hi-Speed USB data plus.                                                                                                                                                            |  |

| USB 2.0<br>DMINUS          | USB2_DM   | AIO            | Hi-Speed USB Speed data minus.                                                                                                                                                     |  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Name                           | Symbol      | Buffer<br>Type         | Description                                                                                                                                                                                                                                                                                              |

|--------------------------------|-------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External USB<br>Bias Resistor  | USBRBIAS    | Al                     | Used for setting HS transmit current level and on-chip termination impedance. Connect to an external 12K 1.0% resistor to ground.                                                                                                                                                                        |

|                                |             | Miscel                 | llaneous Pins                                                                                                                                                                                                                                                                                            |

| Detect Upstream<br>VBUS Power  | VBUS_DET    | VIS<br>(PD)            | Detects the state of the upstream bus power.  For bus powered operation, this pin must be tied to VDD33A.  Refer to Section 4.0, "Power Connections" for additional information.                                                                                                                         |

| PME                            | PME_N       | O8/OD8                 | This pin is used to signal PME when the PME mode of operation is in effect.                                                                                                                                                                                                                              |

| PME Mode Select                | PME_MODE    | VIS                    | This pin serves as the PME mode selection input when the PME mode of operation is in effect.                                                                                                                                                                                                             |

| PME Clear                      | PME_CLEAR   | VIS                    | This pin may serves as PME clear input when the PME mode of operation is in effect.                                                                                                                                                                                                                      |

| USB Suspend                    | SUSPEND_N   | O12                    | This pin is asserted when the device is in one of the suspend states as defined in Section 12.3, "Suspend States".  This pin may be configured to place an external switcher into a low power state such as when the device is in SUSPEND2.                                                              |

| General Purpose<br>I/O 0-11    | GPIO[0:11]  | VIS/O8/<br>OD8<br>(PU) | These general purpose I/O pins are each fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input. A programmable pull-up may optionally be enabled.                                                                                                           |

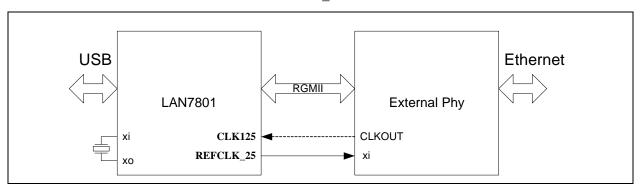

| 25 MHz Reference<br>Clock      | REFCLK_25   | O12                    | 25 MHz reference clock output to be used as a reference by the external partner Gigabit Ethernet PHY.                                                                                                                                                                                                    |

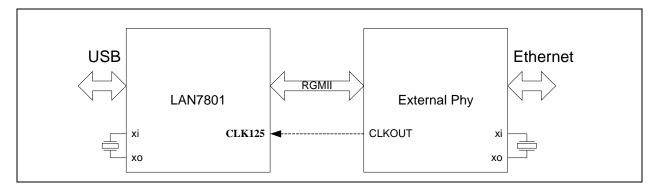

| 125 MHz Clock<br>Input         | CLK125      | VIS                    | 125 MHz clock input used to generate the RGMII TX clock.                                                                                                                                                                                                                                                 |

| Duplex Mode                    | DUPLEX      | VIS                    | Duplex Mode. This signal connects to the Duplex Mode output from the external partner PHY. When asserted, the partner PHY is in Full Duplex mode.  If the partner PHY does not have a duplex output signal then it is recommended that this signal be tied to <b>VDD</b> to force full duplex operation. |

| External<br>Reference Filter   | REF_FILT    | AI                     | External Reference Filter. Connect to an external 1uF capacitor to ground.                                                                                                                                                                                                                               |

| External<br>Reference Resistor | REF_REXT    | Al                     | External Reference Resistor. Connect to an external 2K 1.0% resistor to ground.                                                                                                                                                                                                                          |

| PHY Interrupt                  | PHY_INT_N   | VIS                    | Interrupt input from external Ethernet PHY.                                                                                                                                                                                                                                                              |

| PHY Reset                      | PHY_RESET_N | O12                    | Reset to external Ethernet PHY.                                                                                                                                                                                                                                                                          |

| System Reset                   | RESET_N     | VIS                    | System reset. This pin is active low.  If this signal is unused it must be pulled-up to VDD.                                                                                                                                                                                                             |

| Test Pin                       | TEST        | VIS                    | Test pin. This pin is used for internal purposes only and must be connected to ground for proper operation.                                                                                                                                                                                              |

| No Connect                     | NC          | -                      | No connect. For proper operation, this pin must be left unconnected.                                                                                                                                                                                                                                     |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Name                                      | Symbol        | Buffer<br>Type | Description                                                                                                                    |  |  |

|-------------------------------------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                           | EEPROM        |                |                                                                                                                                |  |  |

| EEPROM<br>Chip Select                     | EECS          | O12            | This pin drives the chip select output of the external EEPROM.                                                                 |  |  |

| EEPROM Data In                            | EEDI          | VIS            | This pin is driven by the EEDO output of the external EEPROM.                                                                  |  |  |

| EEPROM Data Out                           | EEDO          | O12            | This pin drives the EEDI input of the external EEPROM.                                                                         |  |  |

| EEPROM Clock                              | EECLK         | O12            | This pin drives the EEPROM clock of the external EEPROM.                                                                       |  |  |

|                                           |               |                | JTAG                                                                                                                           |  |  |

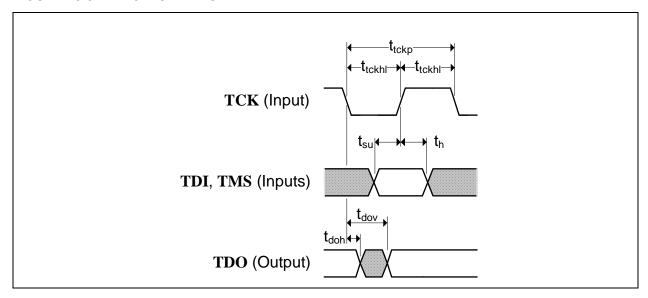

| JTAG<br>Test Mode Select                  | TMS           | VIS            | JTAG test mode select.                                                                                                         |  |  |

| JTAG<br>Test Clock                        | TCK           | VIS            | JTAG test clock.                                                                                                               |  |  |

|                                           |               |                | The maximum operating frequency of this clock is half of the system clock.                                                     |  |  |

| JTAG<br>Test Data Input                   | TDI           | VIS            | JTAG data input.                                                                                                               |  |  |

| JTAG<br>Test Data Output                  | TDO           | O12            | JTAG data output.                                                                                                              |  |  |

|                                           |               | Clo            | ck Interface                                                                                                                   |  |  |

| Crystal Input                             | XI            | ICLK           | External 25 MHz crystal input.                                                                                                 |  |  |

|                                           |               |                | Note: This pin can also be driven by a single-ended clock oscillator. When this method is used, XO should be left unconnected. |  |  |

| Crystal Output                            | XO            | OCLK           | External 25 MHz crystal output.                                                                                                |  |  |

|                                           | I/O Power     | pins, Core     | Power Pins, and Ground Pad                                                                                                     |  |  |

| Variable I/O Power<br>Supply Input        | VDDVARIO      | Р              | +1.8V - +3.3V variable supply for I/Os.                                                                                        |  |  |

|                                           |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |  |

| +3.3V Analog                              | VDD33A        | Р              | +3.3V analog power supply for USB 2.0 AFE.                                                                                     |  |  |

| Power Supply Input                        |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |  |

| +1.2V Ethernet Port<br>Power Supply Input | VDD12A        | Р              | +1.2V analog power supply input for USB PLL/AFE.                                                                               |  |  |

|                                           |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |  |

| +1.2V Digital Core<br>Power Supply Input  | VDD12CORE     | Р              | +1.2V digital core power supply input.                                                                                         |  |  |

|                                           |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |  |

| +3.3V LDO Input<br>Voltage                | VDD33_REG_IN  | Р              | +3.3V power supply input to the integrated LDO.                                                                                |  |  |

|                                           |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |  |

| +2.5V LDO Output                          | VDD25_REG_OUT | Р              | +2.5V power supply output from the integrated LDO.                                                                             |  |  |

|                                           |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Name                             | Symbol       | Buffer<br>Type | Description                                                                       |

|----------------------------------|--------------|----------------|-----------------------------------------------------------------------------------|

| Switcher Input                   | VDD_SW_IN    | Р              | +3.3V input voltage for switching regulator.                                      |

| Voltage                          |              |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information. |

| Switcher Feedback                | VDD12_SW_FB  | Р              | Feedback pin for the integrated switching regulator.                              |

|                                  |              |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information. |

|                                  |              |                | <b>Note:</b> To disable the switcher, tie this pin to VDD_SW_IN.                  |

| +1.2V Switcher<br>Output Voltage | VDD12_SW_OUT | Р              | +1.2V power supply output voltage for switching regulator.                        |

|                                  |              |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information. |

| Ground                           | VSS          | Р              | Common Ground                                                                     |

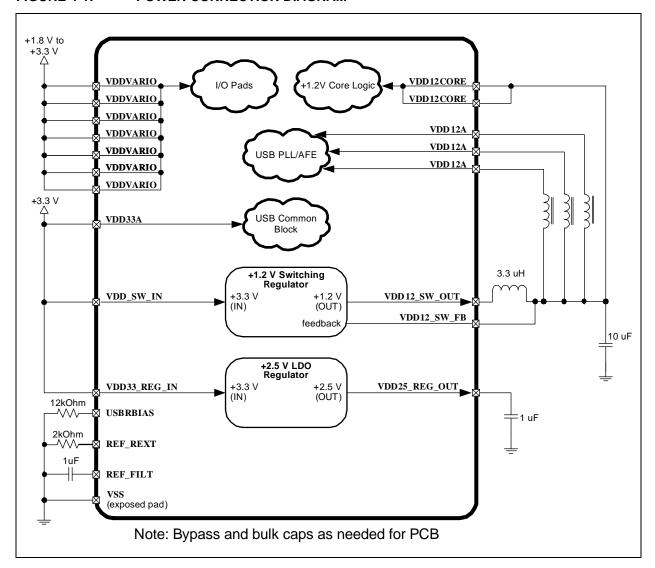

# 4.0 POWER CONNECTIONS

Figure 4-1 illustrates the device power connections in a typical application. Refer to the device reference schematic for additional information. Refer to Section 3.0, "Pin Descriptions and Configuration," on page 10 for additional pin information.

FIGURE 4-1: POWER CONNECTION DIAGRAM

Note: For 3.3V I/O operation, the VDDVARIO and +3.3V supplies may be connected together.

To disable the internal switcher, tie the VDD12\_SW\_FB pin to 3.30V and ensure that all VDD12 rails are connected to an external 1.20V supply.

## 5.0 USB DEVICE CONTROLLER

#### 5.1 Overview

The USB functionality consists of five major parts. The USB PHY, UDC (USB Device Controller), URX (USB Bulk Out Receiver), UTX (USB Bulk In Transmitter), and CTL (USB Control Block).

The UDC is configured to support one configuration, one interface, one alternate setting, and four endpoints. Streams are not supported in this device. The URX and UTX implement the Bulk-Out and Bulk-In endpoints respectively. The CTL manages Control and Interrupt endpoints.

Each USB Controller endpoint is unidirectional with even numbered endpoints handling the OUT (from the host, actually RX into the device) direction and odd numbered endpoints handling the IN (to the host, actually TX from the device) direction.

The UDC endpoint numbers start at 0 and increment. Endpoint numbers are not skipped and have a fixed mapping to the USB endpoint numbers. The corresponding USB endpoint is obtained by dividing the UDC endpoint number by 2 (rounding down). For example, single directional endpoint 0 indicates USB OUT endpoint 0, and single directional endpoint 1 corresponds to USB IN endpoint 0.

The mapping of the device's USB endpoints to the UDC endpoints is shown in Table 5-1. As can be seen, one IN and two OUT endpoints on the UDC are not utilized.

TABLE 5-1: DEVICE TO UDC ENDPOINT MAPPING

| Endpoint Function | USB EP Number |

|-------------------|---------------|

| Control OUT       | 0             |

| Control IN        | 0             |

| unused            | NA            |

| Bulk IN           | 1             |

| Bulk OUT          | 2             |

| unused            | NA            |

| unused            | NA            |

| Interrupt IN      | 3             |

# 5.2 Control Endpoint

The Control endpoint is handled by the CTL (USB Control) module. The CTL module is responsible for handling standard USB requests, as well as USB vendor commands. The UDC does not handle USB commands. These commands are passed to the CTL for completion.

#### 5.2.1 USB STANDARD COMMAND PROCESSING

This section lists the supported USB standard device requests. The basic format of a device request is shown in section 9.3 of the USB 2.0 and 3.1 Gen 1 specifications and the standard device requests are described in section 9.4. Valid values of the parameters are given below.

Per the USB specifications, if an unsupported or invalid request is made to a USB device, the device responds by returning STALL in the Data or Status stage of the request. Receipt of an unsupported or invalid request does NOT cause the optional Halt feature on the control pipe to be set.

For each request supported, the USB specifications provide details on the device behavior during the various configuration states and on the conditions which will return a Request Error. Some requests affect the state of the hardware. Table 9-9 of the USB 3.1 Gen 1 specification lists the events that affect the various parameters.

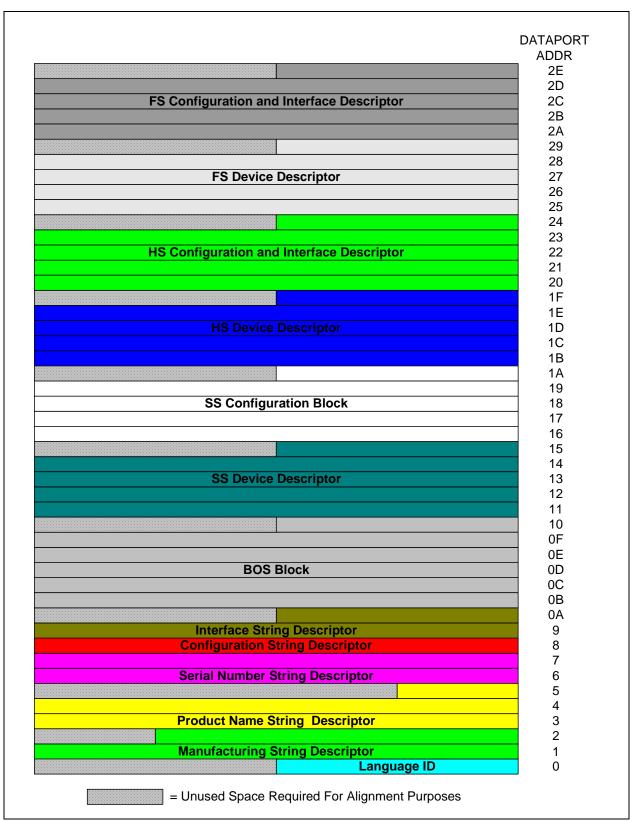

In order to implement the Get Descriptor command, the CTL manages a 128x32 Descriptor RAM. The RAMs contents are initialized via the EEPROM or OTP, after a system reset occurs. The Descriptor RAM may also be programmed by the device driver to support EEPROM-Less mode.

TABLE 5-2: STRING DESCRIPTOR INDEX MAPPINGS

| INDEX | STRING NAME          |

|-------|----------------------|

| 0     | Language ID          |

| 1     | Manufacturer ID      |

| 2     | Product ID           |

| 3     | Serial Number        |

| 4     | Configuration String |

| 5     | Interface String     |

When the UDC decodes a Get Descriptor command, it will pass a pointer to the CTL. The CTL uses this pointer to determine what the command is and how to fill it.

#### 5.2.1.1 Clear Feature

This request varies between USB2.0 (HS, FS) and USB3.1 Gen 1 (SS) modes.

#### 5.2.1.1.1 USB 2.0

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

wValue - Specifies the feature, 1=Device\_Remote\_Wakeup and 0=Endpoint\_Halt.

windex - Always 0 when the device is selected, specifies the interface number (always 0) when an interface is selected or the direction/endpoint number (0, 80h, 81h, 2 or 83h) when an endpoint is selected.

A ClearFeature(Endpoint\_Halt) request will clear the USB 2.0 data toggle for the specified endpoint.

#### 5.2.1.1.2 USB 3.1 Gen 1

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

wValue - Specifies the feature, 0=Endpoint\_Halt (for endpoints), 0=Function\_Suspend (for interfaces), 48=U1\_Enable, 49=U2\_Enable and 50=LTM\_Enable.

wlndex - Always 0 when the device is selected, specifies the interface number (always 0) when an interface is selected or the direction/endpoint number (0, 80h, 81h, 2 or 83h) when an endpoint is selected.

A ClearFeature(Endpoint\_Halt) request will reset the USB 3.1 Gen 1 sequence number for the specified endpoint.

#### 5.2.1.2 Get Configuration

All parameters are fixed per the USB specifications.

#### 5.2.1.3 Get Descriptor

wValue - The high byte selects the descriptor type. The supported descriptors for this command are 1=Device, 2=Configuration (including Interface, Endpoint descriptors and Endpoint Companion descriptors (USB 2.1 LPM/USB 3.1 Gen 1)), 3=String, 6=Device Qualifier (HS/FS), 7=Other Speed Configuration (USB2.0) and 15=BOS (USB3.1 Gen 1 only). The low byte selects the descriptor index and must be 0.

**Note:** Direct access to the Interface, Endpoint and Endpoint Companion (USB 2.1 LPM/USB3.1 Gen 1) descriptors are not supported by this command and will cause a USB stall. Access to USB 3.1 Gen 1 only descriptors while in USB 2.0 mode and access to HS and FS descriptors while in USB 3.1 Gen 1 mode are not supported by this command and will cause a USB stall.

wIndex - Specifies the Language ID for string descriptors or is 0 for other descriptors.

wLength - Specifies the number of bytes to return. If the descriptor is longer than the wLength field, only the initial bytes of the descriptor are returned. If the descriptor is shorter than the wLength field, the device indicates the end of the control transfer by sending a short packet when further data is requested. A short packet is defined as a packet shorter than the maximum payload size or a zero length data packet.

#### 5.2.1.4 Get Interface

wIndex - Specifies the interface, always 0 for this device.

#### 5.2.1.5 Get Status

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

windex - Always 0 when the device is selected, specifies the interface number (always 0) when an interface is selected or the direction/endpoint number (0, 80h, 81h, 2 or 83h) when an endpoint is selected.

Note: In USB 3.1 Gen 1 (SS) mode, only the lower byte of wIndex is used for the endpoint number.

The returned data for a device varies between USB 2.0 (FS, HS) and USB 3.1 Gen 1 (SS) modes, with USB 3.1 Gen 1 mode also returning LTM Enable, U2 Enabled and U1 Enabled. Also, the Remote Wakeup field is reserved and must return 0 for USB 3.1 Gen 1 (SS) mode.

The returned data for the first interface varies between USB 2.0 (FS, HS) and USB 3.1 Gen 1 (SS) modes, with USB 3.1 Gen 1 (SS) mode returning Function Remote Wakeup and Function Remote Wakeup Capable.

**Note:** Power Method (PWR\_SEL) in Hardware Configuration Register (HW\_CFG) is used as the source for the Self-Power bit (D0).

#### 5.2.1.6 Set Address

wValue - Specifies the new device address.

Per the USB specification, the USB device does not change its device address until after the Status stage of this request is completed successfully. This is a difference between this request and all other requests. For all other requests, the operation indicated must be completed before the Status stage.

#### 5.2.1.7 Set Configuration

wValue - The lower byte specifies the configuration value.

The device supports only one configuration. A value of 1 places the device into the Configured state while a value of 0 places the device into the Address state.

The Halt feature is reset for all endpoints upon the receipt of this request with a valid configuration value.

The USB 2.0 data toggle and the USB 3.1 Gen 1 sequence numbers for *all* endpoints are initialized upon the receipt of this request with a valid configuration value.

#### 5.2.1.8 Set Descriptor

This optional request is not supported and the device responds by returning STALL.

#### 5.2.1.9 Set Feature

This request varies between USB 2.0 (HS, FS) and USB 3.1 Gen 1 (SS) modes.

#### 5.2.1.9.1 USB 2.0

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

wValue - Specifies the feature, 1=Device\_Remote\_Wakeup, 2=device Test\_Mode, 0=Endpoint\_Halt.

Note: Endpoint\_Halt is not implemented for Endpoint 0.

windex - Specifies the interface number (always 0) when an interface is selected or the direction/endpoint number (81h, 2 or 83h) when an endpoint is selected. When the device is selected, this field is always 0 unless device Test\_Mode is selected via wValue, in which case the upper byte is the Test Selector and the lower byte a 0.

#### 5.2.1.9.2 USB 3.1 Gen 1

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

wValue - Specifies the feature, 0=Endpoint\_Halt (for endpoints), 0=Function\_Suspend (for interfaces), 48=U1\_Enabe, 49=U2\_Enable and 50=LTM\_Enable.

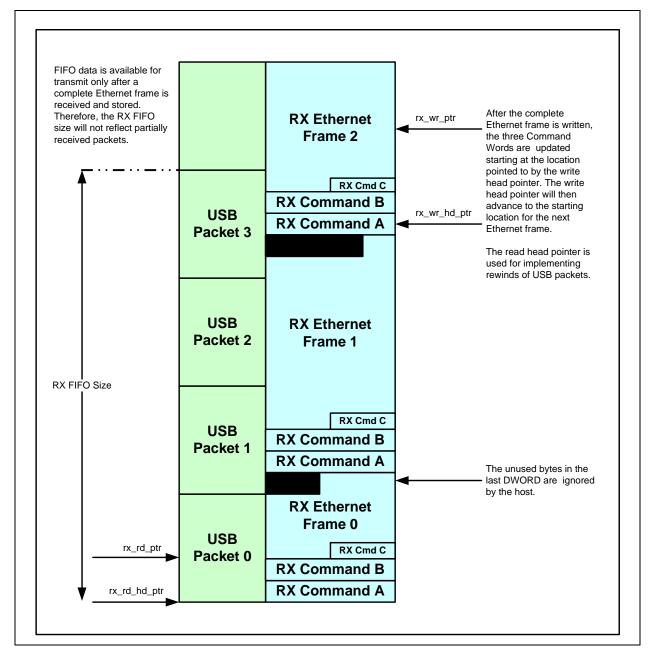

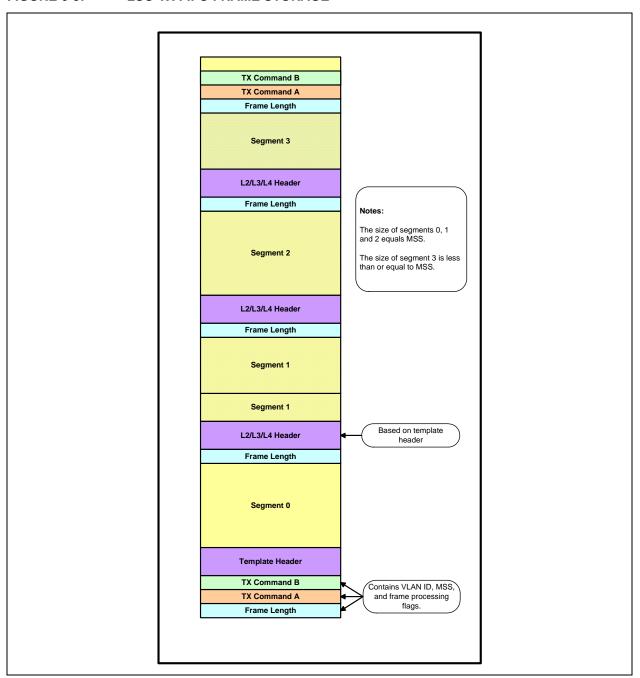

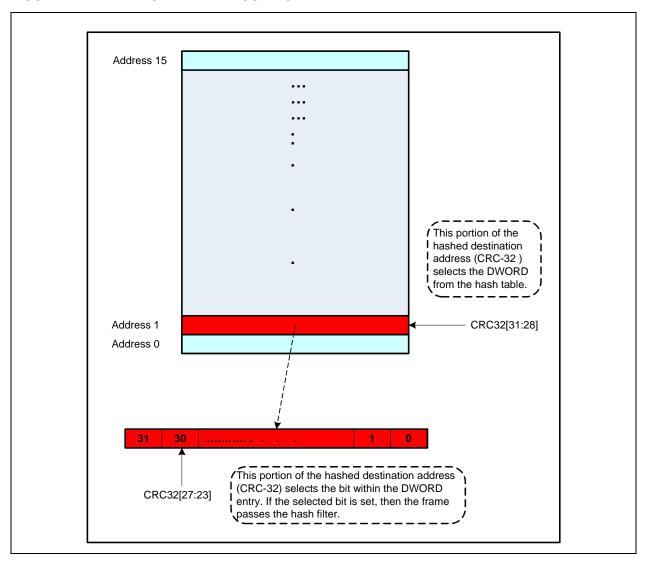

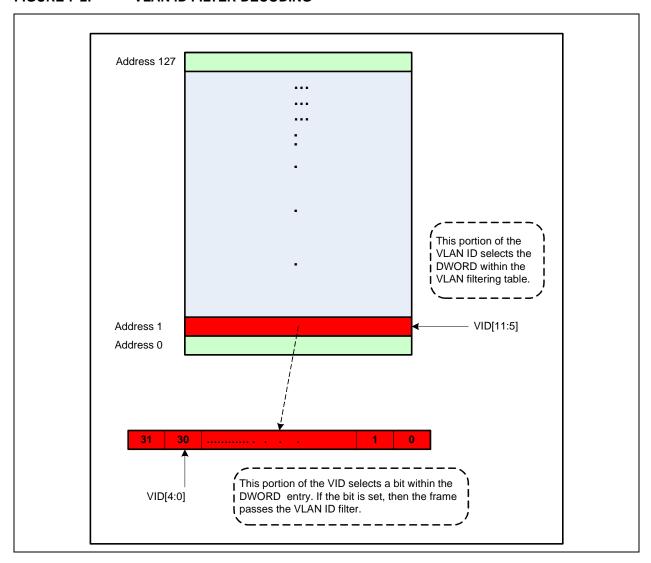

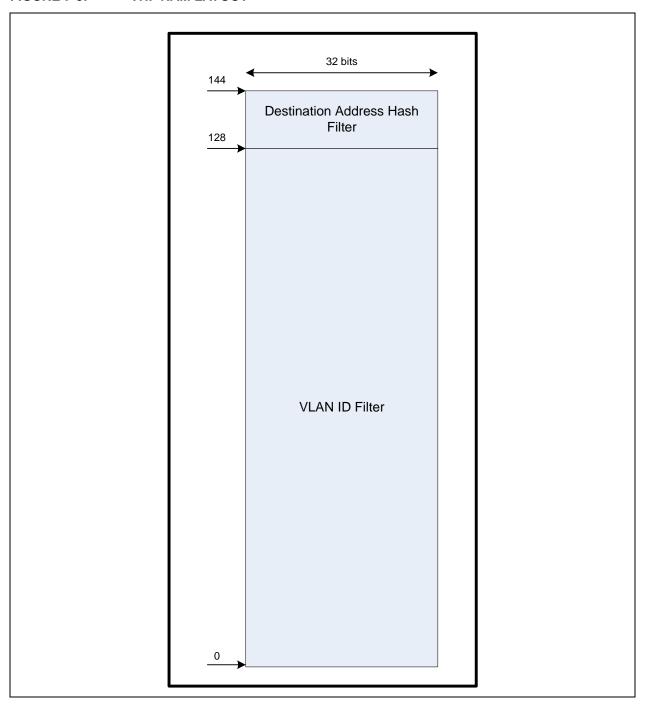

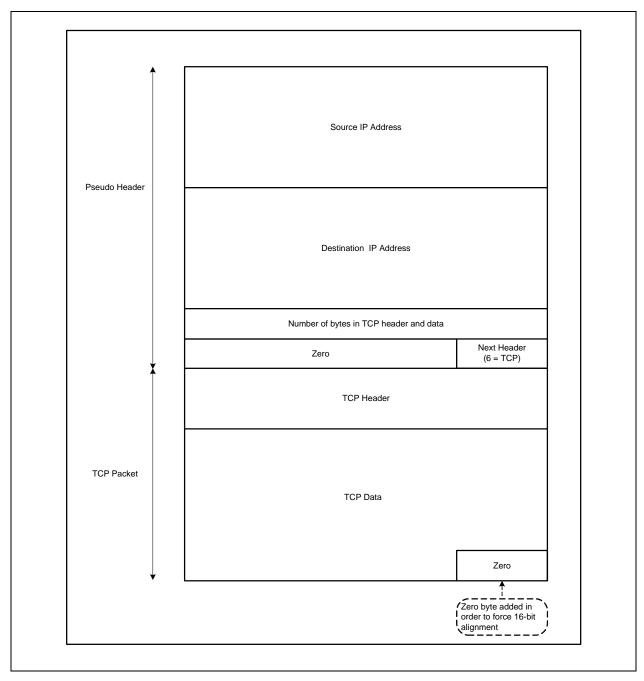

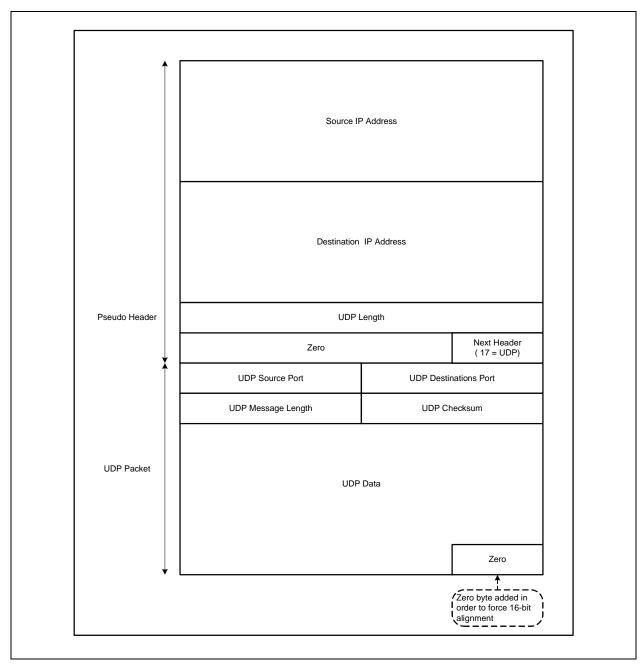

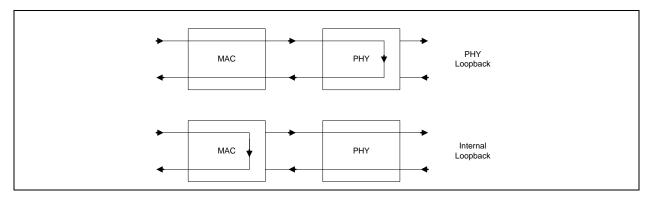

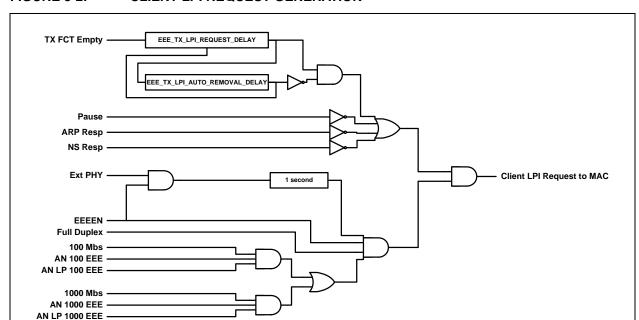

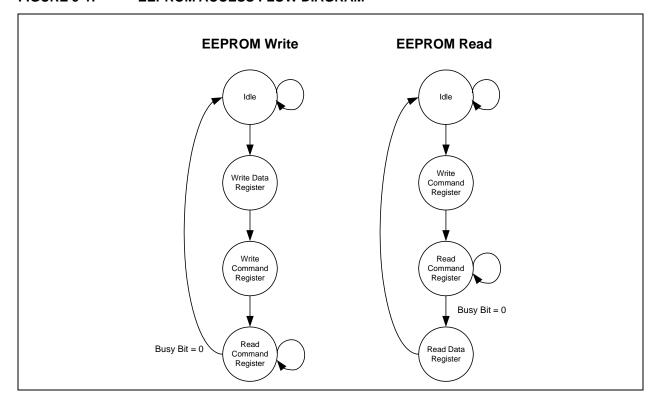

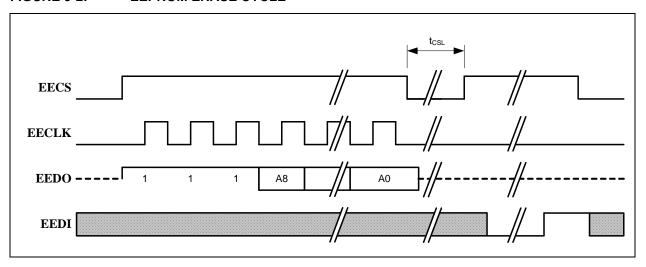

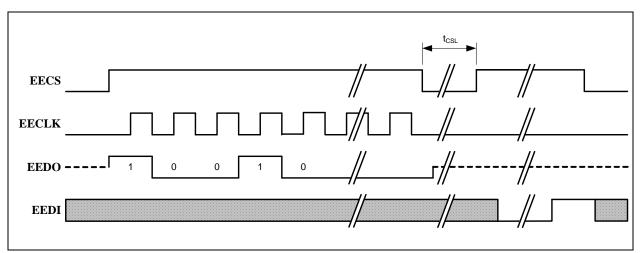

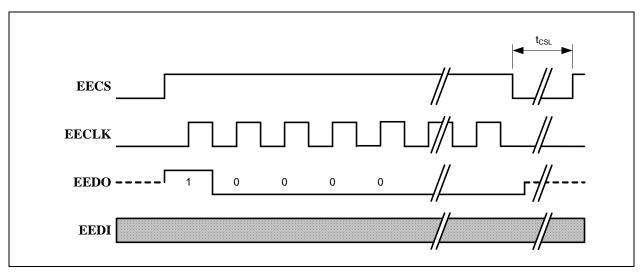

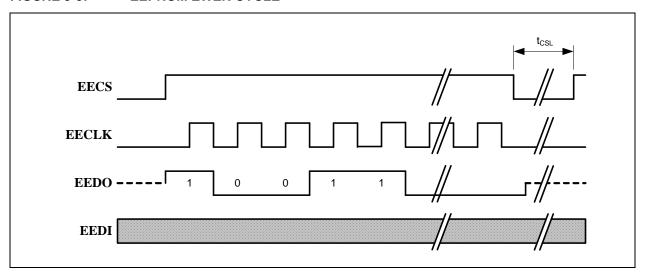

**Note:** Endpoint\_Halt is not implemented for Endpoint 0.