# Le87536 Worldwide ADSL2+ Dual Channel Line Driver BD870 Series

Advance Data Sheet

## Features

- Fixed Voltage Gain Of 13

- 450 mA Peak Output Drive Capability

- ±5 V to ±12 V Dual Supplies Or 10 V to 24 V Single Supply

- 44  $V_{p-p}$  Differential Output Into a 100  $\Omega$  Load

- 40.5  $V_{p-p}$  Differential Output Into a 60  $\Omega$  Load

- Low-power Disable Mode For Each Driver

- 4 mA Per Amplifier Quiescent Supply Current

- -75dBc THD With 1MHz Signal Into a 60  $\Omega$  load

- 16-pin (4 mm x 4 mm) QFN Package

- RoHS Compliant

# Applications

- Dual Port Full Rate ADSL2+ Line Drivers

- HDSL Line Drivers

# Description

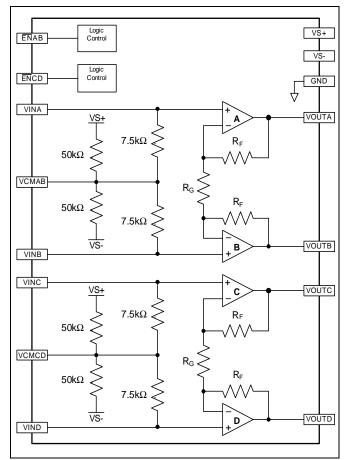

The Le87536 is a dual channel differential amplifier designed to drive full rate ADSL2+ signals with very low power dissipation. The Le87536 contains two pairs of wide band amplifiers designed with Zarlink's HV30 Bipolar SOI process for low power consumption in DSL systems. The amplifiers have an internal fixed gain, which helps to eliminate external feedback and gain setting resistors.

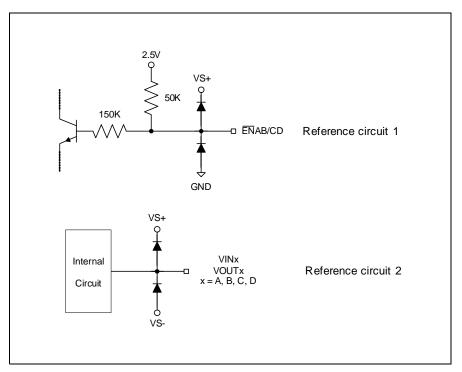

The drivers achieve better than -75 dB THD while driving a 1MHz, 16Vp\_p signal into a  $60\Omega$  load. The amplifiers are enabled by forcing the ENAB/ENCD pins to ground. Leaving the ENAB/ENCD pins floating or forcing them high will disable the two amplifiers. The ENAB and ENCD pins are pulled up to an internal 2.5V through on-chip 50k $\Omega$  resistors.

Le87536 device is one of the most cost-effective and high performance line drivers for ADSL2+ applications.

Version 2

Aug 2010

```

Document Number

```

134329

**O** a la site

Ordering Information 16 pin QFN Green Pkg.

Le87536NQC 16 pin QFN Green Pkg. Le87536NQCT 16 pin QFN Green Pkg. Tray Tape & Reel

The green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

Figure 1 - Block Diagram

| 1.0 Pin Diagram                              | 3 |

|----------------------------------------------|---|

| 1.1 Pin Description                          |   |

| 2.0 Applications                             | 5 |

| 2.1 Typical Application Circuit              |   |

| 2.1.1 Input Considerations                   | 5 |

| 2.1.2 Output Driving Considerations          | 6 |

| 2.1.3 Power Supplies and Component Placement |   |

| 2.1.4 Stability                              |   |

| 2.2 Cable Termination Technique              |   |

| 2.3 Line Driver Protection                   | 8 |

| 3.0 Absolute Maximum Ratings                 |   |

| 3.1 Thermal Resistance                       |   |

| 3.2 Package Assembly                         | 9 |

| 4.0 Operating Ranges                         | 0 |

| 5.0 Device Specifications                    | 0 |

| 6.0 Physical Dimensions                      | 2 |

| 6.1 16-Pin QFN                               | 2 |

| 7.0 Revision History                         | 3 |

| 7.1 Rev 1.0 to Rev 2.0                       |   |

Zarlink documents marked "Preliminary Data Sheet" or "Advance Data Sheet" relate to Zarlink products which are not yet released to production.

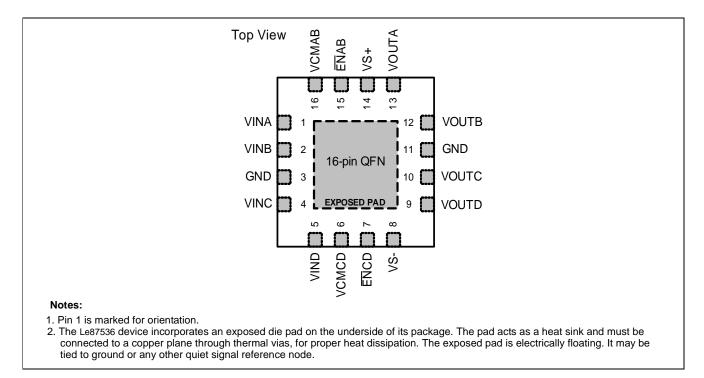

# 1.0 Pin Diagram

#### 1.1 Pin Description

| Pin Name | Туре   | Description                               | Note                |

|----------|--------|-------------------------------------------|---------------------|

| ENAB     | Input  | DSL channel #1 enable/disable control pin | Reference Circuit 1 |

| ENCD     | Input  | DSL channel #2 enable/disable control pin | Reference Circuit 1 |

| VINA     | Input  | Amplifier A non-inverting input           | Reference Circuit 2 |

| VINB     | Input  | Amplifier B non-inverting input           | Reference Circuit 2 |

| VINC     | Input  | Amplifier C non-inverting input           | Reference Circuit 2 |

| VIND     | Input  | Amplifier D non-inverting input           | Reference Circuit 2 |

| VCMAB    | Input  | Bias voltage for amplifier A and B        |                     |

| VCMCD    | Input  | Bias voltage for amplifier C and D        |                     |

| VS+      | Power  | Positive power supply                     |                     |

| VS-      | Power  | Negative power supply                     |                     |

| GND      | Ground | Ground connection                         |                     |

| VOUTA    | Output | Amplifier A output                        | Reference Circuit 2 |

| VOUTB    | Output | Amplifier B output                        | Reference Circuit 2 |

| VOUTC    | Output | Amplifier C output                        | Reference Circuit 2 |

| VOUTD    | Output | Amplifier D output                        | Reference Circuit 2 |

Note 1: Amplifiers A and B comprise DSL channel #1. ENAB allows enable/disable control for DSL channel #1.

Note 2: Amplifiers C and D comprise DSL channel #2. ENCD allows enable/disable control for DSL channel #2.

Note 3: Reference circuits 1 and 2 are shown in Figure 2.

Figure 2 - Reference Circuit

# 2.0 Applications

The Le87536 integrates two sets of high-power line driver amplifiers that can be connected for full duplex differential line transmission. The amplifiers are designed to be used with signals up to 10 MHz with low signal distortion. The driver can put out 20.5 dBm power level onto the telephone line and can drive 450 mA current, which exceeds the level required when using a transformer with 1:2 ratio.

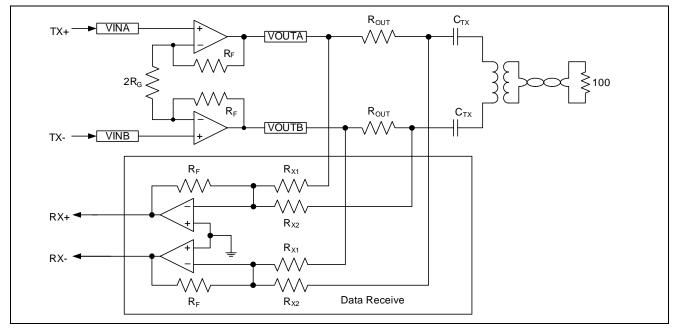

# 2.1 Typical Application Circuit

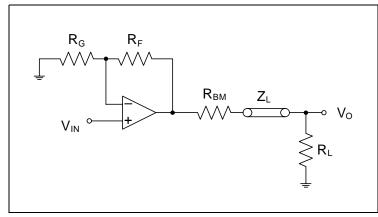

A typical application interface circuit (one channel) is shown in Figure 3.

Figure 3 - Typical Application Interface Circuit

As shown in Figure 3 the amplifiers have identical positive gain connections with common-mode rejection. Any DC input errors are duplicated and create common-mode rather than differential line errors. The component values for Typical Application is listed in Table 1.

| Item             | Quantity | Туре | Value   | Tolerance | Rating |

|------------------|----------|------|---------|-----------|--------|

| R <sub>OUT</sub> | 2        | SMT  | 49.9 Ω  | 1%        | 1/16 W |

| C <sub>TX</sub>  | 2        | X7R  | 0.22 µF | 10%       | 50V    |

Table 1 - Parts List for Typical Application Circuit

#### 2.1.1 Input Considerations

The driving source impedance should be less than 100nH to avoid any ringing or oscillation. This inductance is equivalent to about 4" of unshielded wiring, or 6" of unterminated transmission line. Normal high-frequency construction obviates any such problem.

# 2.1.2 Output Driving Considerations

While the drive amplifiers can output in excess of 450 mA peak, the internal metallization is not designed to carry more than 100 mA of steady DC current and there is no current limit mechanism. The device can safely drive sinusoidal currents of 2 x 100 mArms, or 200 mArms. This current is more than that required to drive line impedance to large output levels, but output short circuits can not be tolerated. The series output resistor will usually limit currents to safe values in the event of line shorts. Driving lines with no series resistor is not recommended.

The amplifiers are sensitive to capacitive loading. More than 100pF may cause peaking of the frequency response. The same is true of badly terminated lines connected without a series matching resistor.

When in power down mode, several volts of differential voltage may appear across the line driver outputs. If a DC current path exists between the two outputs, a large DC current can flow from the positive supply rail to the negative supply rail through the outputs. To avoid DC current flow, the most effective solution is to place DC blocking capacitors in series at the output, as shown in the typical application circuit.

# 2.1.3 Power Supplies and Component Placement

The power supplies should be well bypassed close to the Le87536 device. A 2.2  $\mu F$  tantalum capacitor and a 0.1  $\mu F$  ceramic capacitor for each supply is recommended. The ground terminal of the positive and negative bypass capacitors should be connected to each other directly and then returned to circuit ground to prevent ground current loops.

The Le87536 can also be powered from a single positive voltage supply. When operating in this mode, the VS+ pin is connected to the positive supply. The VS- pin is connected to GND.

#### 2.1.4 Stability

The Le87536 features improved frequency compensation for all applications, allowing stable operation at very low power levels and eliminating any need for external "snubber" circuit. Differential circuits, such as ADSL line driver applications, can be especially prone to common-mode oscillation. The Le87536 is specifically compensated to eliminate this type of instability and allows for reliable operation even at very low power levels.

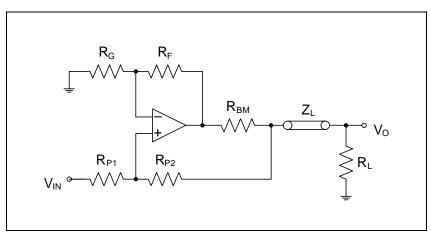

#### 2.2 Cable Termination Technique

There are various techniques available. Figure 4 shows a passive termination technique. Figure 5 shows an active termination technique. A quick comparison of the reduction in voltage and power requirements for the driver with passive or active termination is shown in Table 2.

The output impedance and the voltage gain of the circuit in Figure 5 are shown in the following equations.

$ZOUT = K \bullet RBM$

$$\frac{Vo}{VIN} = \frac{RD(P2)}{2(RD(G) - RD(P1))}$$

where

ZOUT is the output impedance. Vo/VIN represents the voltage gain.

$$K = \frac{1}{1 - \frac{RD(P1)}{RD(G)}}$$

$$RD(P1) = \frac{RP1}{RP1 + RP2}, \quad RD(P2) = \frac{RP2}{RP1 + RP2}, \quad RD(G) = \frac{RG}{RG + RF}$$

Figure 4 - Passive Termination Technique

Figure 5 - Active Termination Technique

| Passive Termination                                                         | Active Termination                                                          |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 16.5 $V_{P-P}$ into a 100 $\Omega$ line                                     | 16.5 $V_{P-P}$ into a 100 $\Omega$ line                                     |

| $V_{OUT DRIVER} = V_{RBM} + V_{RLOAD}$                                      | $V_{OUT DRIVER} = V_{RBM} + V_{RLOAD}$                                      |

| $RBM = R_{LOAD}$                                                            | $RBM = R_{LOAD}/5$                                                          |

| V <sub>RBM</sub> = V <sub>RLOAD</sub>                                       | V <sub>RBM</sub> = V <sub>RLOAD</sub> /5                                    |

| V <sub>OUT DRIVER</sub> = 33.52 V                                           | V <sub>OUT DRIVER</sub> = 20.11 V                                           |

| V <sub>SUPPLY</sub> = 37.52 V                                               | V <sub>SUPPLY</sub> = 24.11 V                                               |

| I <sub>OUT</sub> = 31.6 mA                                                  | I <sub>OUT</sub> = 31.6 mA                                                  |

| $P_{OUT DRIVER} = V_{SUPPLY} * I_{OUT} = 1.185 W$<br>(plus quiescent power) | $P_{OUT DRIVER} = V_{SUPPLY} * I_{OUT} = 0.714 W$<br>(plus quiescent power) |

# Table 2 - Passive and Active Termination Comparison

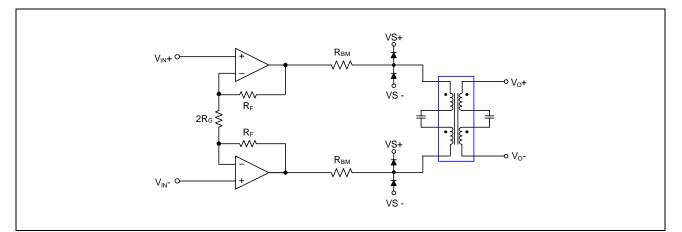

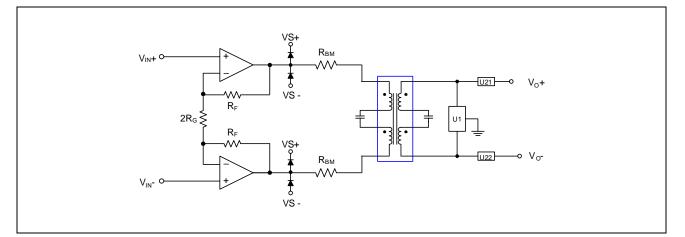

#### 2.3 Line Driver Protection

High voltage transients such as lightning can appear on the telephone lines. Transient protection devices are used to absorb the energy and clamp the voltages. However, large transient voltages can still couple to the primary side of the transformer.

As shown in Figure 6 and 7, the series output termination resistors limit the current going into the line driver. These termination resistors should be specified at 0.5W. The resistance can be  $2.2\Omega$  or greater required by the sensing and termination impedance.

A protection scheme is shown in Figure 6, assuming that the isolation of the data transformer is sufficient and the diodes on the secondary side of the data transformer are not causing degradation of data performance.

To avoid the possible concerns in Figure 6 on board secondary protection may be added, as shown in Figure 7. The external diodes may be moved to the outputs of the line driver. The grounded protector, U1, is on the line side to limit the peak surge voltage seen by the data transformer. The series components, U21 and U22, can be Positive Temperature Coefficient (PTC) devices or fuses.

The protection scheme can vary depending on the type of data transformer used, the data rate, the intended protection criteria to meet and trade offs between performance and cost. Consult your Zarlink representatives for more specific details on protection.

Figure 6 - Line Driver Protection Diagram (1)

Figure 7 - Line Driver Protection Diagram (2)

# 3.0 Absolute Maximum Ratings

Stresses above the values listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods can affect device reliability.

| Storage Temperature                                   | $-65 \le T_A \le +150^{\circ}C$ |

|-------------------------------------------------------|---------------------------------|

| Operating Ambient Temperature                         | $-40 \le T_A \le +85^{\circ}C$  |

| Operating Junction Temperature<br>(See Notes 1 and 2) | $-40 \le T_A \le +150^\circ C$  |

| VS+ to VS- Supply Voltage                             | –0.3 V to 30 V                  |

| VS+ with respect to GND                               | –0.3 V to 30 V                  |

| VS- with respect to GND                               | -30 V to +0.3 V                 |

| Driver inputs VINA/B/C/D                              | VS- to VS+                      |

| Control inputs ENAB/ENCD with respect to GND          | –0.3 V to 6 V                   |

| Maximum current on any input                          | 10 mA                           |

| Maximum current at amplifier output (DC continuous)   | 100 mA                          |

| ESD Immunity (Human Body Model)                       | JESD22 Class 2 compliant        |

| ESD Immunity (Charge Device Model)                    | JESD22 Class IV compliant       |

Note: Continuous operation above 145°C junction temperature may degrade device reliability.

#### 3.1 Thermal Resistance

The thermal performance of a thermally enhanced package is assured through optimized printed circuit board layout. Specified performance requires that the exposed thermal pad be soldered to an equally sized exposed copper surface, which, in turn, conducts heat through multiple vias to larger internal copper planes.Please refer to the *QFN Package* application note, available from <u>http://www.zarlink.com</u>, for layout and heat sinking guidelines.

When the QFN package is mounted on 4 layers JEDEC PCB in still air the following thermal characteristics are expected:

$\Theta_{JA}$  35.3°C/W,  $\Theta_{JC}$  22.0°C/W,  $\Theta_{JB}$  15.6°C/W and  $\Psi_{JT}$  0.4°C/W.

The maximum junction temperature is 150°C.

#### 3.2 Package Assembly

The green package devices are assembled with enhanced, environmental compatible lead-free, halogen-free, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes.

Refer to IPC/JEDEC J-Std-020 Table 4-2 for recommended peak soldering temperature and Table 5-2 for the recommended solder reflow temperature profile.

# 4.0 Operating Ranges

Zarlink guarantees the performance of this device over commercial (0°C to 70°C) and industrial (-40°C to 85°C) temperature ranges by conducting electrical characterization over each range and by conducting a single insertion production test coupled with periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore GR-357-CORE Component Reliability Assurance Requirements for Telecommunications Equipment.

| Ambient temperature                                            | -40°C to +85°C |

|----------------------------------------------------------------|----------------|

| VS+ with respect to GND                                        | +12 V ± 5%     |

| VS- with respect to GND                                        | -12 V ± 5%     |

| Single battery operation, VS+ with respect to GND (VS- to GND) | +24V ± 5%      |

# 5.0 Device Specifications

**Typical Conditions:** VS =  $\pm$ 12V, RL = 65 $\Omega$ , unless otherwise specified, TA = 25°C.

#### Min/Max Parameters: TA = -40 to $+85^{\circ}C$

Amplifiers are tested separately.

| Parameter           | Description                           | Condition                                                   | Min.  | Тур. | Max.  | Unit           |

|---------------------|---------------------------------------|-------------------------------------------------------------|-------|------|-------|----------------|

| Supply Current Ch   | naracteristics                        |                                                             |       | 1    |       | 1              |

| IS+ (Full IS)       | Positive Supply Current per Amplifier | All outputs at 0V, $\overline{ENAB} = \overline{ENCD} = 0V$ | 3.2   | 4.0  | 5.3   | mA             |

| IS- (Full IS)       | Negative Supply Current per Amplifier | All outputs at 0V, $\overline{EN}AB = \overline{EN}CD = 0V$ | -5.1  | -3.8 | -3.0  | mA             |

| IS+ (power down)    | Positive Supply Current per Amplifier | All outputs at 0V, $\overline{ENAB} = \overline{ENCD} = 5V$ |       | 0.2  | 0.4   | mA             |

| IS- (power down)    | Negative Supply Current per Amplifier | All outputs at 0V, $\overline{ENAB} = \overline{ENCD} = 5V$ | -0.3  | 0.1  |       | mA             |

| IGND                | GND Supply Current per<br>Amplifier   | All outputs at 0V                                           |       | 0.25 |       | mA             |

| Control Input (C0   | and C1) Characteristics               |                                                             |       |      |       |                |

| VIH                 | Input High Voltage                    | ENAB and ENCD inputs                                        | 1.6   |      |       | V              |

| VIL                 | Input Low Voltage                     | ENAB and ENCD inputs                                        |       |      | 0.8   | V              |

| IIH                 | Input High Current                    | $\overline{ENAB} = \overline{ENCD} = 5V$                    | 5     | 20   | 40    | μA             |

| IIL                 | Input Low Current                     | $\overline{ENAB} = \overline{ENCD} = 0V$                    | -85   | -50  | -30   | μA             |

| Amplifier Input (VI | Nx+ and VINx-) Characteri             | stics                                                       |       |      | 1     |                |

| VOS                 | Input Offset Voltage                  |                                                             | -10   | 0    | 10    | mV             |

| ΔVOS                | VOS mismatch                          |                                                             | -5    | 0    | 5     | mV             |

| IB                  | Input Bias Current                    |                                                             | -15   |      | 14    | μA             |

| ΔIB                 | IB Mismatch                           |                                                             | -25   | 0    | 25    | μA             |

| VCM                 | Driver common mode voltage            | pins VCMAB/CD floating, reference to VS-                    | 0.475 | 0.5  | 0.525 | VS+  +<br> VS- |

| ROL                 | Transimpedance <sup>1</sup>           |                                                             |       | 5    |       | MΩ             |

| eN                  | Input Noise Voltage <sup>1</sup>      |                                                             |       | 3.5  |       | nV/√Hz         |

| iN                  | Input Noise Current <sup>1</sup>      |                                                             |       | 13   |       | pA/√Hz         |

| Table 3 - Electrical | Specifications |

|----------------------|----------------|

|----------------------|----------------|

| Parameter        | Description                           | Condition                                     | Min.  | Тур.  | Max.  | Unit |

|------------------|---------------------------------------|-----------------------------------------------|-------|-------|-------|------|

| Amplifier Output | (VOUT) Characteristics                |                                               |       |       |       |      |

| VOUT             | Loaded Output Swing                   | RL = 100Ω                                     | ±10.3 | ±11.1 |       | V    |

|                  | (RL Single-ended to                   | $RL = 30\Omega \ (+)$                         | 10.1  | 10.7  |       | V    |

|                  | GND)                                  | $RL = 30\Omega (-)$                           |       | -10.5 | -10.1 | V    |

| IOUT             | Output Current <sup>1</sup>           | VOUT = 0.6V, RL = 1Ω                          |       | 600   |       | mA   |

| Amplifier Dynam  | ic Characteristics                    | 1                                             |       |       |       |      |

| THD              | Total Harmonic Distortion             | f = 1MHz, RL = 50Ω, VOUT = 16Vpp              |       | -75   |       | dBc  |

| MTPR             | Multi-Tone Power Ratio                | 26kHz to 1.1MHz, RL = 100Ω,<br>PLINE =20.4dBm |       | -70   |       | dBc  |

| SR               | Slew rate (single-ended) <sup>1</sup> | VOUT from -8V to +8V measured at ±4V          | 200   | 400   |       | V/µs |

| AV               | Voltage Gain                          | VOUT = 16Vpp, RL = 100Ω                       | 12.9  | 13.0  | 13.1  | V/V  |

Table 3 - Electrical Specifications

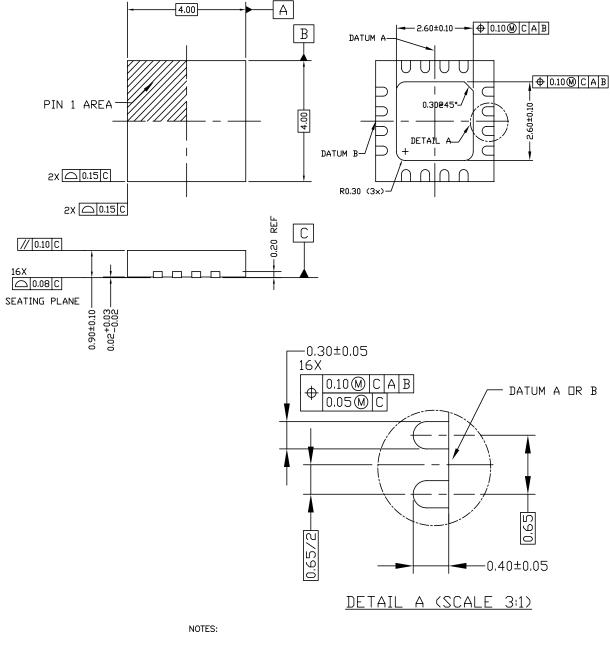

# 6.0 Physical Dimensions

#### 6.1 16-Pin QFN

QFN 16L 4×4

1. DIMENSIONING AND TOLERANCE IS IN CONFORMANCE TO ASME Y14.5-1994 ALL DIMENSIONS ARE IN MILLIMETERS \* IN DEGREES

# 7.0 Revision History

# 7.1 Rev 1.0 to Rev 2.0

• Added package thermal data on page 9.

# For more information about all Zarlink products visit our Web Site at

# www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL, the Zarlink Semiconductor logo and the Legerity logo and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Zarlink Semiconductor Inc

TECHNICAL DOCUMENTATION - NOT FOR RESALE

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Buffers & Line Drivers category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

LXV200-024SW 74AUP2G34FW3-7 HEF4043BP PI74FCT3244L MC74HCT365ADTR2G Le87401NQC Le87402MQC 028192B 042140C 051117G 070519XB NL17SZ07P5T5G NLU1GT126AMUTCG 74AUP1G17FW5-7 74LVC2G17FW4-7 CD4502BE 5962-8982101PA 5962-9052201PA 74LVC1G125FW4-7 NL17SH17P5T5G NL17SH125P5T5G NLV37WZ07USG RHRXH162244K1 74AUP1G34FW5-7 74AUP1G07FW5-7 74LVC2G126RA3-7 NLX2G17CMUTCG 74LVCE1G125FZ4-7 Le87501NQC 74AUP1G126FW5-7 TC74HC4050AP(F) 74LVCE1G07FZ4-7 NLX3G16DMUTCG NLX2G06AMUTCG NLVVHC1G50DFT2G LE87100NQC LE87290YQC LE87290YQCT LE87511NQC LE87511NQCT LE87557NQC LE87557NQCT LE87614MQC LE87614MQCT 74AUP1G125FW5-7 NLU2G16CMUTCG MC74LCX244MN2TWG NL17SG126DFT2G NLVHCT245ADTR2G NLV37WZ16USG