# **MCP2030**

# **Three-Channel Analog Front-End Device**

### **Device Features:**

- · Three input pins for analog input signals

- High input detection sensitivity (3 mV<sub>PP</sub>, typical)

- High modulation depth sensitivity (as low as 8%)

- Three output selections:

- Demodulated data

- Carrier clock

- RSSI

- Input carrier frequency: 125 kHz, typical

- Input data rate: 10 Kbps, maximum

- · 8 internal Configuration registers

- Bidirectional transponder communication (LF talk back)

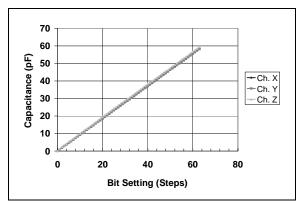

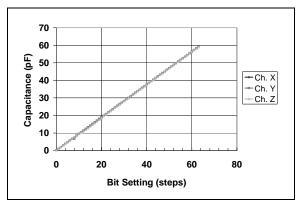

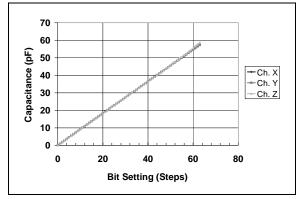

- Programmable antenna tuning capacitance (up to 63 pF, 1 pF/step)

- · Programmable output enable filter

- Low standby current: 4 μA (with 3 channels enabled), typical

- Low operating current: 13 μA (with 3 channels enabled), typical

- Serial Peripheral Interface (SPI<sup>TM</sup>) with external devices

- Supports Battery Back-Up mode and batteryless operation with external circuits

- Industrial and Extended Temperature Range: -40°C to +85°C (industrial)

# **Typical Applications:**

- · Automotive industry applications:

- Passive Keyless Entry (PKE) transponder

- Remote door locks and gate openers

- Engine immobilizer

- LF initiator sensor for tire pressure monitoring systems

- · Security Industry applications:

- Long range access control transponder

- Parking lot entry transponder

- Hands-free apartment door access

- Asset control and management

### **Description:**

The MCP2030 is a stand-alone Analog Front-End (AFE) device for Low-Frequency (LF) sensing and bidirectional communication applications. The device has eight internal Configuration registers which are readable and programmable, except the read-only STATUS register, by an external device.

The device has three low-frequency input channels. Each input channel can be individually enabled or disabled. The device can detect an input signal with amplitude as low as  $\sim 1~\text{mV}_{PP}$  and can demodulate an amplitude-modulated input signal with as low as 8% modulation depth. The device can also transmit data by clamping and unclamping the input LC antenna voltage.

The device can output demodulated data, carrier clock or RSSI current depending on the register setting. The demodulated data and carrier clock outputs are available on the LFDATA pin, while the RSSI output is available on the RSSI pin. The RSSI current output is linearly proportional to the input signal strength.

The device has programmable internal tuning capacitors for each input channel. The user can program these capacitors up to 63 pF, 1 pF per step. These internal tuning capacitors can be used effectively for fine-tuning of the external LC resonant circuit.

The device is optimized for very low current consumption and has various battery-saving low-power modes (Sleep, Standby, Active). The device can also be operated in Battery Back-up and Batteryless modes using a few external components.

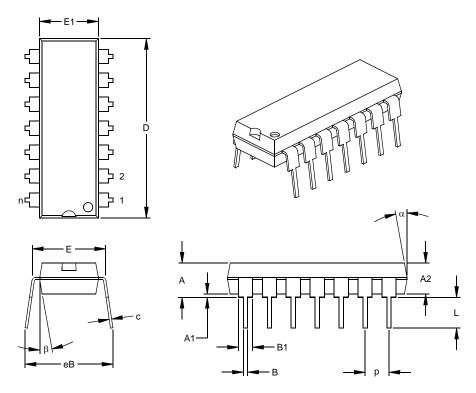

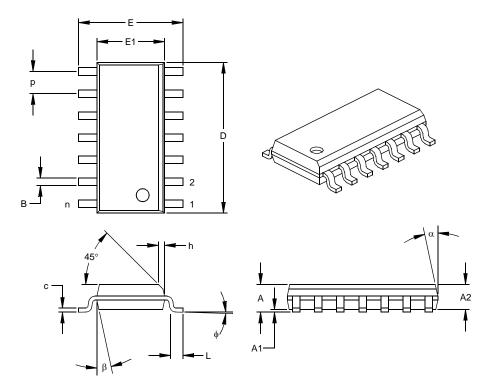

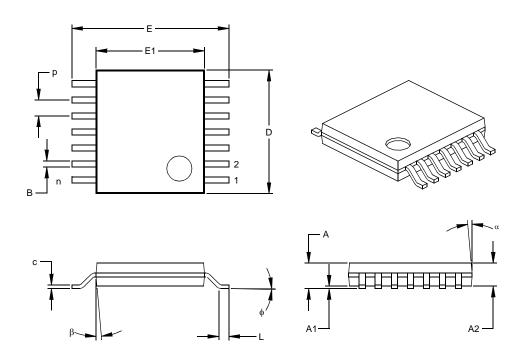

This device is available in 14-pin PDIP, SOIC, and TSSOP packages. This device is also used as the AFE in the PIC16F639.

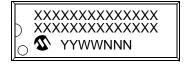

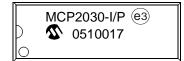

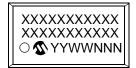

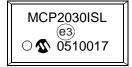

# Package Types:

# **MCP2030**

**NOTES:**

# 1.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings(†)

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## **DC Characteristics**

Electrical Specifications: Standard Operating Conditions (unless otherwise stated)

$\begin{array}{ll} \text{Operating temperature} & -40^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +85^{\circ}\text{C} \\ \text{LC Signal Input} & \text{Sinusoidal 300 mV}_{\text{PP}} \\ \end{array}$

Carrier Frequency 125 kHz

LCCOM connected to V<sub>SS</sub>

| Parameters                                                                                                                 | Sym.               | Min.                  | Typ†        | Max.                  | Units          | Conditions                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-------------|-----------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage                                                                                                             | V <sub>DD</sub>    | 2.0                   | 3.0         | 3.6                   | V              |                                                                                                                                                                                                   |

| V <sub>DD</sub> Start Voltage to ensure internal Power-on Reset signal                                                     | V <sub>POR</sub>   | _                     | _           | 1.8                   | V              |                                                                                                                                                                                                   |

| Modulation Transistor-on Resistance                                                                                        | $R_{M}$            | _                     | 50          | 100                   | Ω              | V <sub>DD</sub> = 3.0V                                                                                                                                                                            |

| Active Current (detecting signal) 1 LC Input Channel Receiving Signal 3 LC Input Channel Receiving Signals                 | I <sub>ACT</sub>   |                       | 10<br>13    | —<br>18               | μA<br>μA       | CS = V <sub>DD</sub> Input = Continuous Wave (CW); Amplitude = 300 mV <sub>PP</sub> . All channels enabled.                                                                                       |

| Standby Current (wait to detect signal) 1 LC Input Channel Enabled 2 LC Input Channels Enabled 3 LC Input Channels Enabled | I <sub>STDBY</sub> |                       | 2<br>3<br>4 | 5<br>6<br>7           | μΑ<br>μΑ<br>μΑ | $\overline{\text{CS}} = V_{\text{DD}}; \overline{\text{ALERT}} = V_{\text{DD}}$                                                                                                                   |

| Sleep Current                                                                                                              | I <sub>SLEEP</sub> | _                     | 0.2         | 1                     | μΑ             | $\overline{\text{CS}} = \text{V}_{\text{DD}}; \overline{\text{ALERT}} = \text{V}_{\text{DD}}$                                                                                                     |

| Analog Input Leakage Current<br>LCX, LCY, LCZ<br>LCCOM                                                                     | I <sub>AIL</sub>   |                       |             | ± 1<br>± 1            | μA<br>μA       | $\label{eq:VDD} V_{DD} = 3.6 \text{V, } V_{SS} \leq V_{\text{IN}} \leq 1 \text{V with respect to} \\ \text{ground. Internal tuning capacitors are switched} \\ \text{off, tested in Sleep mode.}$ |

| Digital Input Low Voltage                                                                                                  | V <sub>IL</sub>    | V <sub>SS</sub>       | _           | 0.3 V <sub>DD</sub>   | V              | SCLK, SDI, CS                                                                                                                                                                                     |

| Digital Input High Voltage                                                                                                 | V <sub>IH</sub>    | 0.8 V <sub>DD</sub>   | 1           | $V_{DD}$              | ٧              | SCLK, SDI, CS                                                                                                                                                                                     |

| Digital Input Leakage Current (Note 1)<br>SDI<br>SCLK, CS                                                                  | I <sub>IL</sub>    |                       | _           | ± 1<br>± 1            | μΑ<br>μΑ       | $\begin{aligned} &V_{DD} = 3.6V \\ &V_{SS} \leq V_{PIN} \leq V_{DD} \\ &V_{PIN} \leq V_{DD} \end{aligned}$                                                                                        |

| Digital Output Low Voltage ALERT, LFDATA/SDIO                                                                              | V <sub>OL</sub>    |                       |             | V <sub>SS</sub> + 0.4 | V              | Analog Front-End section $I_{OL} = 1.0 \text{ mA}, V_{DD} = 2.0 \text{V}$                                                                                                                         |

| Digital Output High Voltage<br>ALERT, LFDATA/SDIO                                                                          | V <sub>OH</sub>    | V <sub>DD</sub> - 0.5 | _           | _                     | V              | I <sub>OH</sub> = -400 μA, V <sub>DD</sub> = 2.0V                                                                                                                                                 |

| Digital Input Pull-Up Resistor CS, SCLK                                                                                    | R <sub>PU</sub>    | 50                    | 200         | 350                   | kΩ             | V <sub>DD</sub> = 3.6V                                                                                                                                                                            |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Negative current is defined as current sourced by the pin.

<sup>†</sup> Data in "Typ" column is at 3.0V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# **AC Characteristics**

| Parameters                                                                  | Sym.                 | Min. | Typ†                | Max.           | Units            | Conditions                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------|----------------------|------|---------------------|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

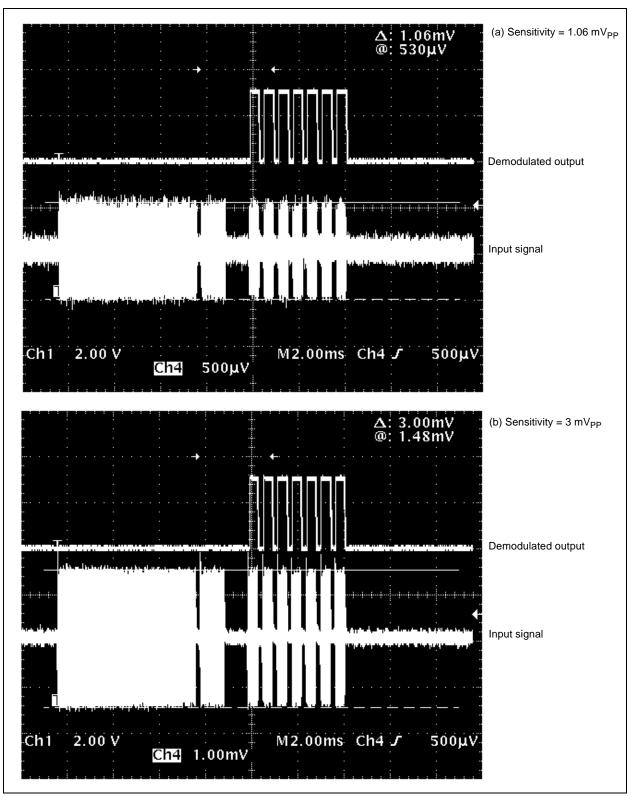

| Input Sensitivity                                                           | V <sub>SENSE</sub>   | 1    | 3.0                 | 6              | mV <sub>PP</sub> | V <sub>DD</sub> = 3.0V Output enable filter disabled AGCSIG = 0; MODMIN = 00 (33% modulation depth setting) Input = Continuous Wave (CW) Output = Logic level transition from low-to-high at sensitivity level for CW input. |

| Coil de-Q'ing Voltage -<br>RF Limiter (R <sub>FLM</sub> ) must be active    | $V_{DE_{Q}}$         | 3    | _                   | 5              | V                | $V_{DD}$ = 3.0V, Force $I_{IN}$ = 5 $\mu$ A (worst case)                                                                                                                                                                     |

| RF Limiter Turn-on Resistance (LCX, LCY, LCZ)                               | R <sub>FLM</sub>     | _    | 300                 | 700            | Ω                | $V_{DD} = 2.0V$ , $V_{IN} = 8 V_{DC}$                                                                                                                                                                                        |

| Sensitivity Reduction                                                       | S <sub>ADJ</sub>     |      | 0<br>-30            | 11             | dB<br>dB         | V <sub>DD</sub> = 3.0V<br>No sensitivity reduction selected<br>Max. reduction selected<br>Monotonic increment in attenuation value<br>from setting = 0000 to 1111 by design                                                  |

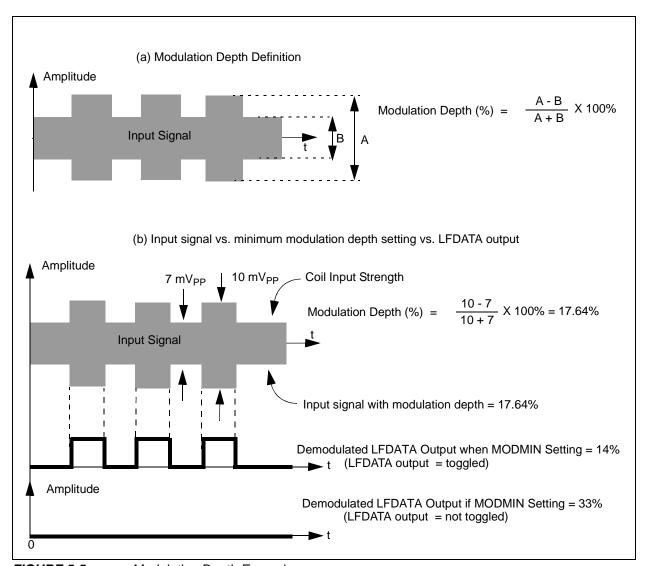

| Minimum Modulation Depth<br>60% setting<br>33% setting<br>14% setting<br>8% | V <sub>IN_MOD</sub>  |      | 60<br>33<br>14<br>8 | 84<br>49<br>26 | %<br>%<br>%      | V <sub>DD</sub> = 3.0V<br>See <b>Section 5.21 "Minimum Modulation</b><br><b>Depth Requirement for Input Signal"</b> .<br>See Modulation Depth Definition in<br>Figure 5-5.                                                   |

| Carrier frequency                                                           | F <sub>CARRIER</sub> | _    | 125                 | _              | kHz              |                                                                                                                                                                                                                              |

| Input modulation frequency                                                  | F <sub>MOD</sub>     | _    | _                   | 10             | kHz              | Input data rate with NRZ data format. $V_{DD} = 3.0V$ Minimum modulation depth setting = 33% Input conditions: Amplitude = 300 mV_{PP} Modulation depth = 100%                                                               |

| LCX Tuning Capacitor                                                        | C <sub>TUNX</sub>    | _    | 0                   | _              | pF               | V <sub>DD</sub> = 3.0V,<br>Config. Reg. 1, bits <6:1> Setting = 000000                                                                                                                                                       |

|                                                                             |                      | 44   | 59                  | 82             | pF               | 63 pF ±30% Config. Reg. 1, bits <6:1> Setting = 111111 63 steps, approx. 1 pF/step Monotonic increment in capacitor value from setting = 000000 to 111111 by design                                                          |

| LCY Tuning Capacitor                                                        | C <sub>TUNY</sub>    | _    | 0                   | _              | pF               | V <sub>DD</sub> = 3.0V,<br>Config. Reg. 2, bits <6:1> Setting = 000000                                                                                                                                                       |

|                                                                             |                      | 44   | 59                  | 82             | pF               | 63 pF ±30% Config. Reg. 2, bits <6:1> Setting = 111111 63 steps, approx. 1 pF/step Monotonic increment in capacitor value from setting = 000000 to 111111 by design                                                          |

| LCZ Tuning Capacitor                                                        | C <sub>TUNZ</sub>    | _    | 0                   | _              | pF               | V <sub>DD</sub> = 3.0V,<br>Config. Reg. 3, bits<6:1> Setting = 000000                                                                                                                                                        |

|                                                                             |                      | 44   | 59                  | 82             | pF               | 63 pF ±30% Config. Reg. 3, bits<6:1> Setting = 111111 63 steps, approx. 1 pF/step Monotonic increment in capacitor value from setting = 000000 to 111111 by design                                                           |

| Q of Internal Tuning Capacitors                                             | Q_C                  | 50 * | _                   |                |                  |                                                                                                                                                                                                                              |

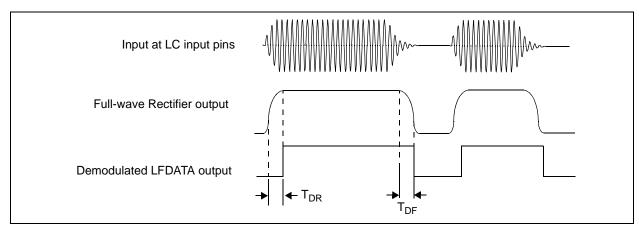

| Demodulator Charge Time (delay time of demodulated output to rise)          | T <sub>DR</sub>      | _    | 50                  | _              | μs               | V <sub>DD</sub> = 3.0V<br>Minimum modulation depth setting = 33%<br>Input conditions:<br>Amplitude = 300 mV <sub>pp</sub><br>Modulation depth = 100%                                                                         |

Parameter is characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1:

Required output enable filter high time must account for input path analog delays (=  $T_{OEH} - T_{DR} + T_{DF}$ ). Required output enable filter low time must account for input path analog delays (=  $T_{OEL} + T_{DR} - T_{DF}$ ).

# **AC Characteristics (Continued)**

**Electrical Specifications:** Standard Operating Conditions (unless otherwise stated) Supply Voltage  $2.0V \le V_{DD} \le 3.6V$  Operating temperature  $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$

LCCOM connected to V<sub>SS</sub> LC Signal Input

Sinusoidal 300 mV<sub>PP</sub>

Carrier Frequency

LCCOM connected to V<sub>SS</sub> 125 kHz

| LCCOM connected to V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                                                       |      |                                                                                                                                                                                 |                |                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sym.                 | Min.                                                  | Тур† | Max.                                                                                                                                                                            | Units          | Conditions                                                                                                                            |

| Demodulator Discharge Time (delay time of demodulated output to fall)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T <sub>DF</sub>      | _                                                     | 50   | _                                                                                                                                                                               | μs             | V <sub>DD</sub> = 3.0V<br>MOD depth setting = 33%<br>Input conditions:<br>Amplitude = 300 mV <sub>PP</sub><br>Modulation depth = 100% |

| Rise time of LFDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TR <sub>LFDATA</sub> | _                                                     | 0.5  | _                                                                                                                                                                               | μs             | $V_{DD} = 3.0V$ . Time is measured from 10% to 90% of amplitude                                                                       |

| Fall time of LFDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TF <sub>LFDATA</sub> | _                                                     | 0.5  | _                                                                                                                                                                               | μs             | V <sub>DD</sub> = 3.0V<br>Time is measured from 10% to 90% of<br>amplitude                                                            |

| AGC stabilization time (T <sub>AGC +</sub> T <sub>PAGC</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T <sub>STAB</sub>    | 4                                                     | 1    | _                                                                                                                                                                               | ms             |                                                                                                                                       |

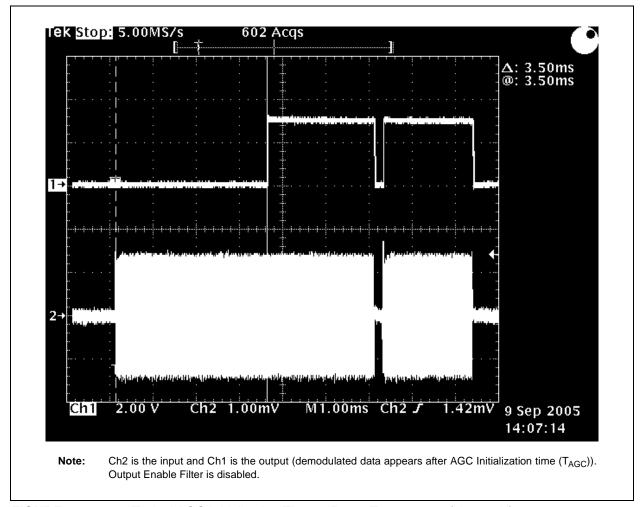

| AGC initialization time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T <sub>AGC</sub>     | _                                                     | 3.5  | _                                                                                                                                                                               | ms             |                                                                                                                                       |

| High time after AGC initialization time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T <sub>PAGC</sub>    | _                                                     | 62.5 | _                                                                                                                                                                               | μs             |                                                                                                                                       |

| Gap time after AGC stabilization time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T <sub>GAP</sub>     | 200                                                   | _    | _                                                                                                                                                                               | μs             |                                                                                                                                       |

| Time element of pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T <sub>E</sub>       | 100                                                   | _    | _                                                                                                                                                                               | μs             | Minimum pulse width                                                                                                                   |

| Time from exiting Sleep or POR to being ready to receive signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T <sub>RDY</sub>     | _                                                     | _    | 50*                                                                                                                                                                             | ms             |                                                                                                                                       |

| Minimum time AGC level must be held after receiving AGC Preserve command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | T <sub>PRES</sub>    | 5*                                                    | 1    | _                                                                                                                                                                               | ms             | AGC level must not change more than 10% during T <sub>PRES</sub> .                                                                    |

| Internal RC oscillator frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Fosc                 | 27                                                    | 32   | 35.5                                                                                                                                                                            | kHz            | Internal clock trimmed at 32 kHz during test                                                                                          |

| Inactivity timer time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | T <sub>INACT</sub>   | 13.5                                                  | 16   | 17.75                                                                                                                                                                           | ms             | 512 cycles of RC oscillator @ F <sub>OSC</sub>                                                                                        |

| Alarm timer time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T <sub>ALARM</sub>   | 27                                                    | 32   | 35.5                                                                                                                                                                            | ms             | 1024 cycles of RC oscillator @ F <sub>OSC</sub>                                                                                       |

| LC Pin Input Resistance for LCX, LCY, LCZ pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R <sub>IN</sub>      | _                                                     | 800* | _                                                                                                                                                                               | kΩ             | LCCOM grounded, $V_{DD} = 3V$ , $F_{CARRIER} = 125 \text{ kHz}$ .                                                                     |

| LC Pin Input Parasitic Capacitance for LCX, LCY, LCZ pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C <sub>IN</sub>      | _                                                     | 24*  |                                                                                                                                                                                 | pF             | LCCOM grounded, $V_{DD} = 3V$ , $F_{CARRIER} = 125 \text{ kHz}$ .                                                                     |

| Minimum output enable filter high time  OEH (Bits Config0<8:7>)  01 = 1 ms  10 = 2 ms  11 = 4 ms  00 = Filter Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | T <sub>OEH</sub>     | 32 (~1 ms)<br>64 (~2 ms)<br>128 (~4 ms)               | 1111 |                                                                                                                                                                                 | clock<br>count | RC oscillator = $F_{OSC}$ (see $F_{OSC}$ specification for variations). Viewed from the pin input: (Note 1)                           |

| Minimum output enable filter low time  OEL (Bits Config0<6:5>)  00 = 1 ms  01 = 1 ms  10 = 2 ms  11 = 4 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | T <sub>OEL</sub>     | 32 (~1 ms)<br>32 (~1 ms)<br>64 (~2 ms)<br>128 (~4 ms) |      | _<br>_<br>_<br>_                                                                                                                                                                | clock<br>count | RC oscillator = F <sub>OSC</sub> Viewed from the pin input: (Note 2)                                                                  |

| Maximum output enable filter period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T <sub>OET</sub>     |                                                       |      |                                                                                                                                                                                 |                | RC oscillator = F <sub>OSC</sub>                                                                                                      |

| OEH         OEL         Toeh         Toeh           01         00         = 1 ms         1 ms (Filter 1)           01         01         = 1 ms         1 ms (Filter 1)           01         10         = 1 ms         2 ms (Filter 2)           01         11         = 1 ms         4 ms (Filter 3)           10         00         = 2 ms         1 ms (Filter 4)           10         01         = 2 ms         1 ms (Filter 4)           10         10         = 2 ms         2 ms (Filter 5)           10         11         = 2 ms         4 ms (Filter 6)           11         00         = 4 ms         1 ms (Filter 7)           11         01         = 4 ms         2 ms (Filter 8)           11         11         = 4 ms         4 ms (Filter 9) |                      | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-   |      | 96 (~3 ms)<br>96 (~3 ms)<br>128 (~4 ms)<br>192 (~6 ms)<br>128 (~4 ms)<br>128 (~4 ms)<br>160 (~5 ms)<br>250 (~8 ms)<br>192 (~6 ms)<br>192 (~6 ms)<br>256 (~8 ms)<br>320 (~10 ms) | clock<br>count |                                                                                                                                       |

| 00 xx = Filter Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | _                                                     | _    | _                                                                                                                                                                               |                | LFDATA output appears as long as input signal level is greater than V <sub>SENSE</sub> .                                              |

Parameter is characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Required output enable filter high time must account for input path analog delays (=  $T_{OEH}$  -  $T_{DR}$  +  $T_{DF}$ ). Required output enable filter low time must account for input path analog delays (=  $T_{OEL}$  +  $T_{DR}$  -  $T_{DF}$ ). Note 1:

# **AC Characteristics (Continued)**

**Electrical Specifications:** Standard Operating Conditions (unless otherwise stated) Supply Voltage  $2.0V \leq V_{DD} \leq 3.6V$  Operating temperature  $-40^{\circ}C \leq T_{A} \leq +85^{\circ}C$

LCCOM connected to V<sub>SS</sub>

Sinusoidal 300 mV<sub>PP</sub> LC Signal Input

Carrier Frequency 125 kHz

LCCOM connected to V<sub>SS</sub>

| Parameters             | Sym.                | Min. | Тур†              | Max.           | Units          | Conditions                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------|------|-------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

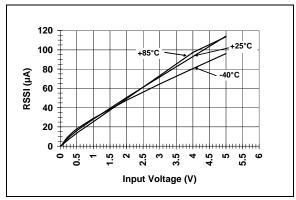

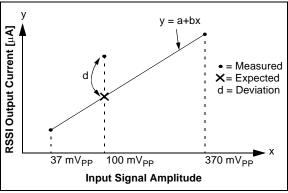

| RSSI current output    | I <sub>RSSI</sub>   | 6    | 0.65<br>12<br>100 | 2<br>20.3<br>— | μΑ<br>μΑ<br>μΑ | $\begin{array}{l} V_{IN}=37~\text{mV}_{PP} \\ V_{IN}=370~\text{mV}_{PP} \\ V_{DD}=3.0\text{V}, V_{IN}=0~\text{to}~4~\text{V}_{PP} \\ \text{Linearly increases with input signal amplitude.} \\ \text{Tested at V}_{IN}=37~\text{mV}_{PP}, 100~\text{mV}_{PP}, \text{and} \\ 370~\text{mV}_{PP}~\text{at}~+25^{\circ}\text{C}. \end{array}$ |

| RSSI current linearity | ILR <sub>RSSI</sub> | -15  | _                 | 15             | %              | Tested at room temperature only (see Equation 5-1 and Figure 5-7 for test method).                                                                                                                                                                                                                                                         |

Parameter is characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Required output enable filter high time must account for input path analog delays (= T<sub>OEH</sub> - T<sub>DR</sub> + T<sub>DF</sub>).

Required output enable filter low time must account for input path analog delays (=  $T_{OEL} + T_{DR} - T_{DF}$ ).

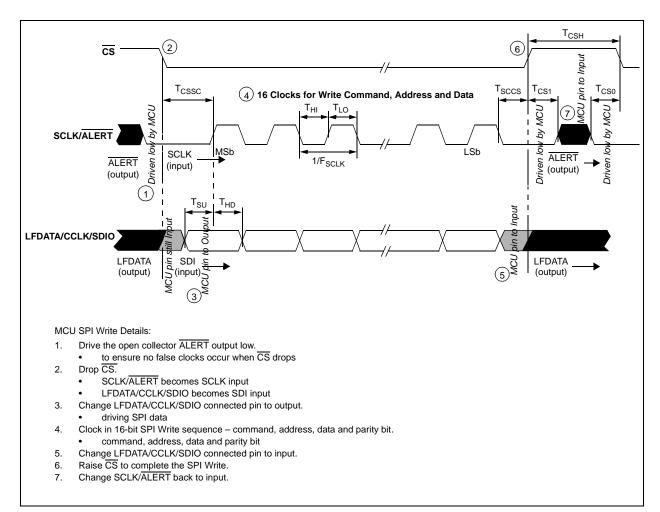

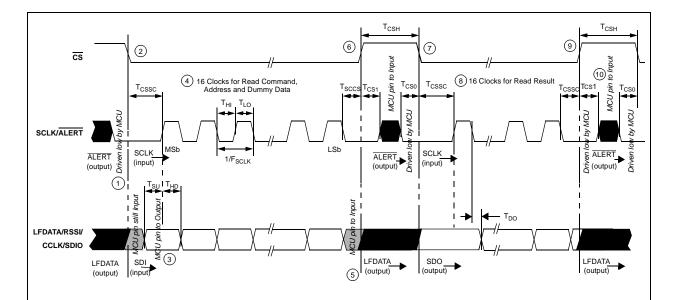

# **SPI Timing**

Electrical Specifications: Standard Operating Conditions (unless otherwise stated)

Supply Voltage

Operating temperature

LC Signal Input

Carrier Frequency  $2.0V \le V_{DD} \le 3.6V$  $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ Sinusoidal 300 mV<sub>PP</sub>

125 kHz

LCCOM connected to V<sub>SS</sub>

| Parameters                                  | Sym.              | Min. | Typ† | Max. | Units | Conditions                                                            |

|---------------------------------------------|-------------------|------|------|------|-------|-----------------------------------------------------------------------|

| SCLK Frequency                              | F <sub>SCLK</sub> | _    | _    | 3    | MHz   |                                                                       |

| CS fall to first SCLK edge setup time       | T <sub>CSSC</sub> | 100  | _    | _    | ns    |                                                                       |

| SDI setup time                              | T <sub>SU</sub>   | 30   | 1    | 1    | ns    |                                                                       |

| SDI hold time                               | $T_{HD}$          | 50   | _    | _    | ns    |                                                                       |

| SCLK high time                              | T <sub>HI</sub>   | 150  | _    | _    | ns    |                                                                       |

| SCLK low time                               | T <sub>LO</sub>   | 150  | _    | _    | ns    |                                                                       |

| SDO setup time                              | $T_{DO}$          | _    | _    | 150  | ns    |                                                                       |

| SCLK last edge to CS rise setup time        | T <sub>SCCS</sub> | 100  | _    | _    | ns    |                                                                       |

| CS high time                                | T <sub>CSH</sub>  | 500  | _    | _    | ns    |                                                                       |

| CS rise to SCLK edge setup time             | T <sub>CS1</sub>  | 50   | _    | _    | ns    |                                                                       |

| SCLK edge to CS fall setup time             | T <sub>CS0</sub>  | 50   | _    | _    | ns    | SCLK edge when CS is high                                             |

| Rise time of SPI data (SPI Read command)    | TR <sub>SPI</sub> | _    | 10   | _    | ns    | V <sub>DD</sub> = 3.0V. Time is measured from 10% to 90% of amplitude |

| Fall time of SPI data<br>(SPI Read command) | TF <sub>SPI</sub> | _    | 10   | _    | ns    | V <sub>DD</sub> = 3.0V. Time is measured from 90% to 10% of amplitude |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

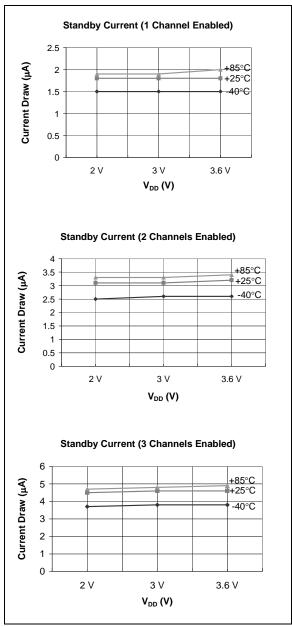

FIGURE 2-1: Typical Standby Current.

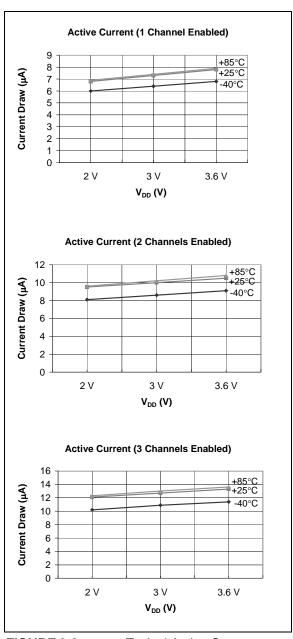

FIGURE 2-2: Typical Active Current.

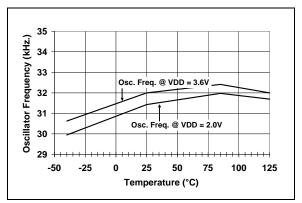

**FIGURE 2-3:** Oscillator Frequency vs. Temperature,  $V_{DD} = 3.6V$  and 2.0V.

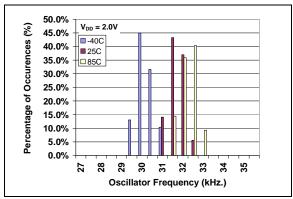

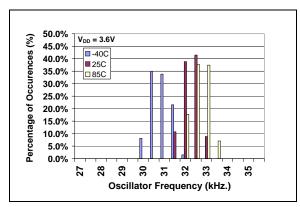

**FIGURE 2-4:** Oscillator Frequency Histograms vs. Temperature,  $V_{DD} = 2V$ .

**FIGURE 2-5:** Oscillator Frequency Histograms vs. Temperature at  $V_{DD} = 3V$ .

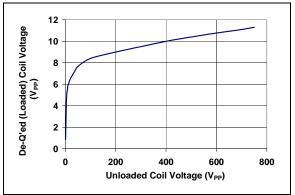

FIGURE 2-6: De-Q'ed Voltage vs. Unloaded Coil Voltage.

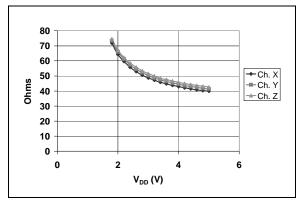

FIGURE 2-7: Modulation Transistor-on Resistance (+25°C).

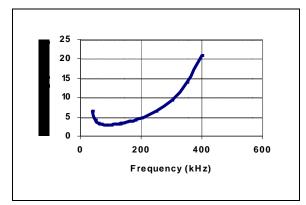

FIGURE 2-8: Channel Sensitivity vs. Bandwidth.

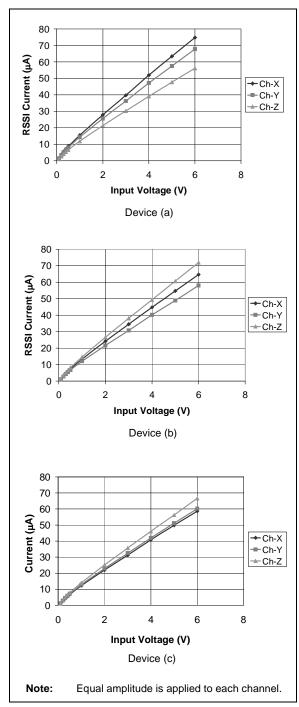

**FIGURE 2-9:** Typical RSSI Output Current vs. Input Signal Strength.

**FIGURE 2-10:** Typical Tuned Capacitance Value vs. Configuration Register Bit Setting  $(V_{DD} = 3V, Temperature = +25^{\circ}C.$

**FIGURE 2-11:** Typical Tuned Capacitance Value vs. Configuration Register Bit Setting  $(V_{DD} = 3V, Temperature = -40^{\circ}C.$

**FIGURE 2-12:** Typical Tuned Capacitance Value vs. Configuration Register Bit Setting  $(V_{DD} = 3V, Temperature = +85^{\circ}C.$

FIGURE 2-13: Examples of RSSI Output Current Variations Between Channel to Channel and Device to Device at Room Temperature.

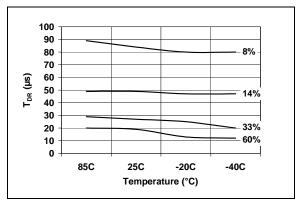

**FIGURE 2-14:** Example of Typical  $T_{DR}$  Changes over Temperature. Input Signal Condition: Amplitude = 300 mV<sub>PR</sub> Modulation Depth = 100 %.

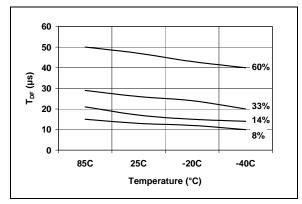

**FIGURE 2-15:** Example of Typical  $T_{DF}$  Changes over Temperature. Input Signal Condition: Amplitude = 300 mV<sub>PB</sub> Modulation Depth = 100 %.

# 2.1 Performance Plots

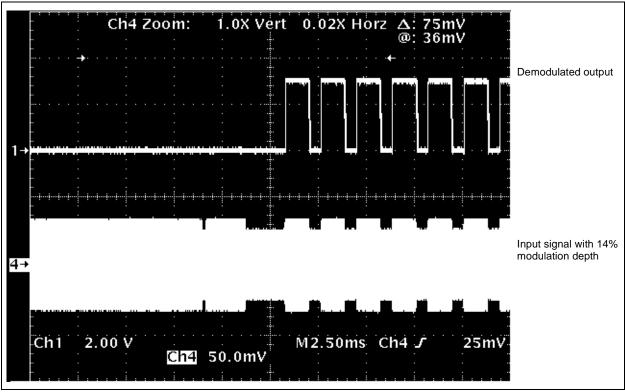

FIGURE 2-16: Input Sensitivity Example.

FIGURE 2-17: Typical AGC Initialization Time at Room Temperature ( $V_{DD} = 3V$ ).

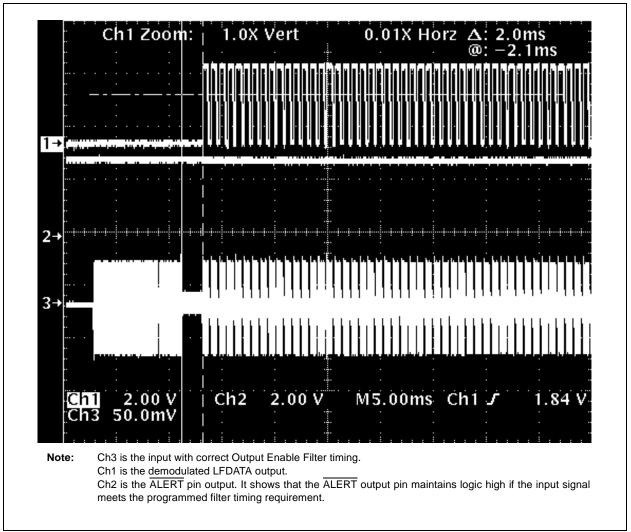

FIGURE 2-18: ALERT Output Example: With No Parity Error and no 32 ms Alarm Timer Time-out.

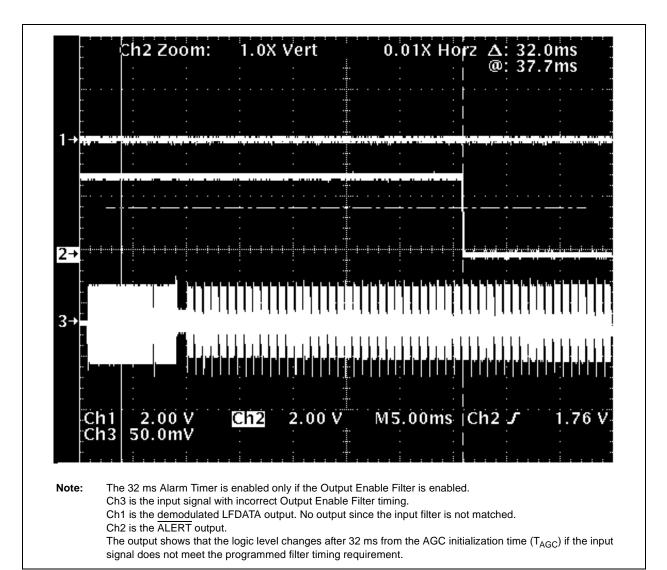

FIGURE 2-19: ALERT Output Example: With 32 ms Alarm Timer Timed out.

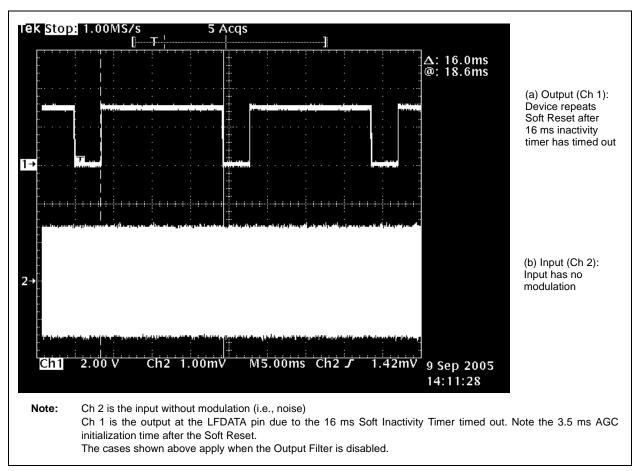

**FIGURE 2-20:** Examples of Soft Inactivity Timer Timed out: This output is available only if the Output Enable Filter is disabled.

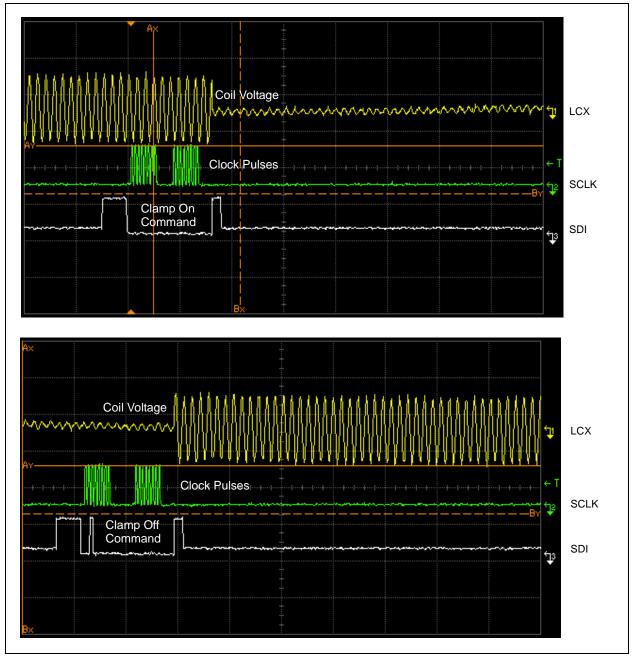

FIGURE 2-21: Examples of Clamp-On and Clamp-Off Commands and Changes in Coil Voltage.

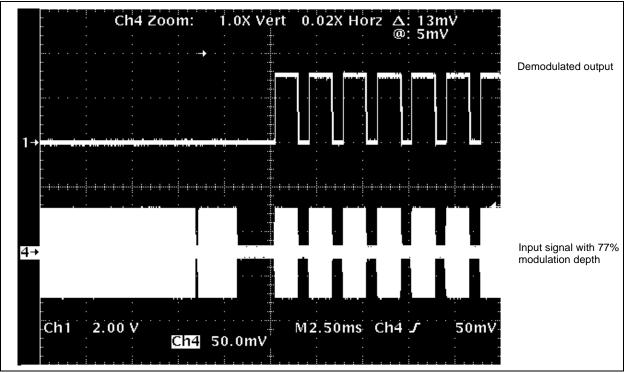

**FIGURE 2-22:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 77%, Minimum Modulation Depth (MODMIN) Setting = 60%.

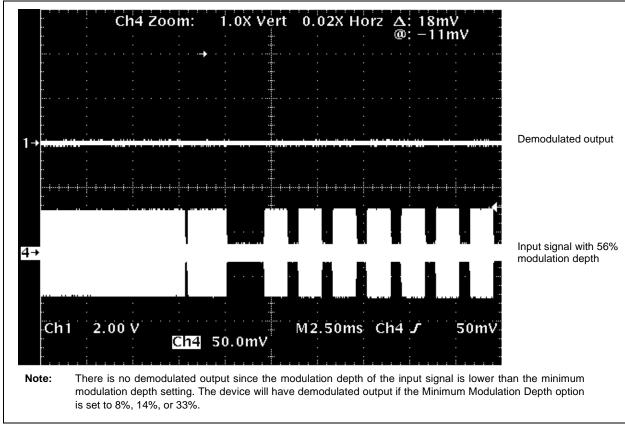

**FIGURE 2-23:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 56%, Minimum Modulation Depth (MODMIN) Setting = 60%.

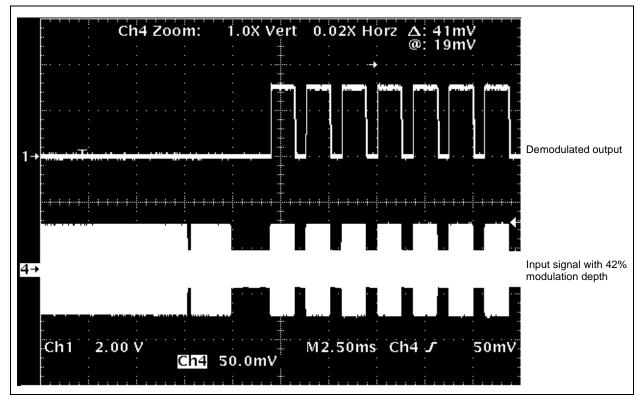

**FIGURE 2-24:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 42%, Minimum Modulation Depth (MODMIN) Setting = 33%.

**FIGURE 2-25:** Example of Minimum Modulation Depth Setting: Modulation Depth of Input Signal = 14%, Minimum Modulation Depth (MODMIN) Setting = 14%.

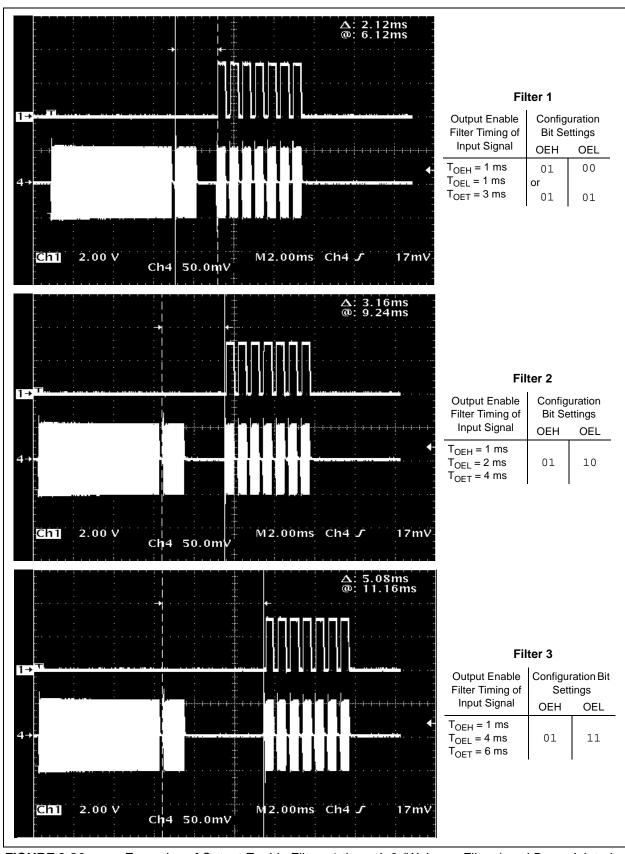

**FIGURE 2-26:** Examples of Output Enable Filters 1 through 3 (Wake-up Filters) and Demodulated Outputs.

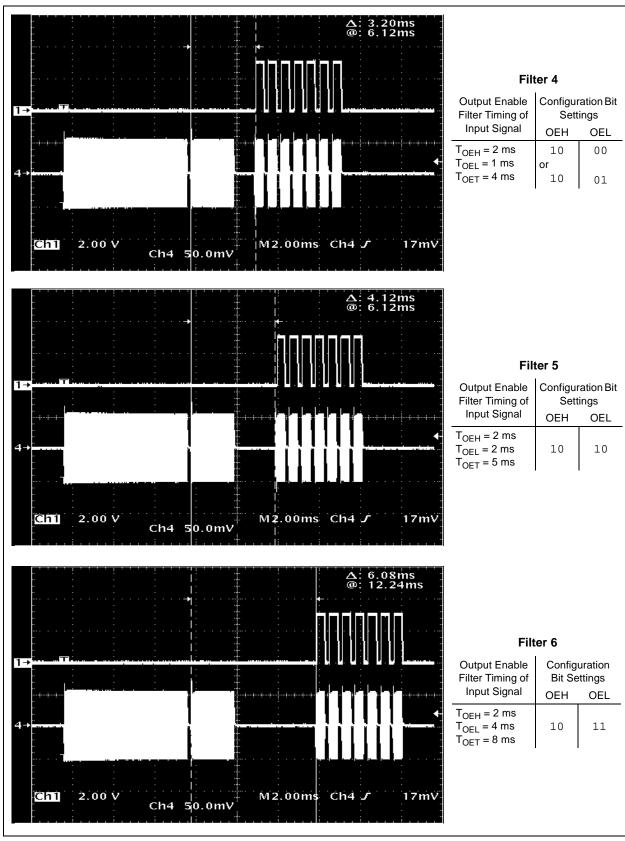

**FIGURE 2-27:** Examples of Output Enable Filters 4 through 6 (Wake-up Filters) and Demodulated Outputs.

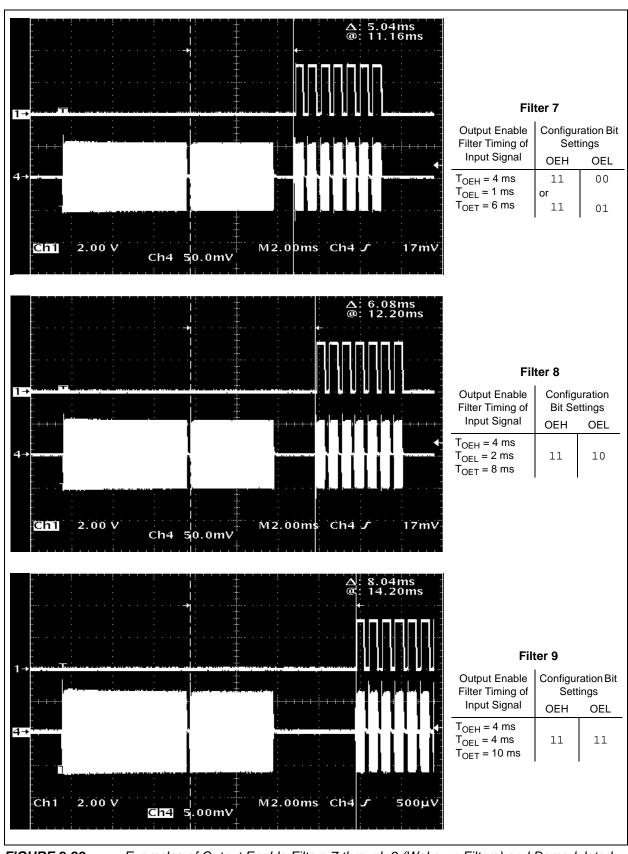

**FIGURE 2-28:** Examples of Output Enable Filters 7 through 9 (Wake-up Filters) and Demodulated Outputs.

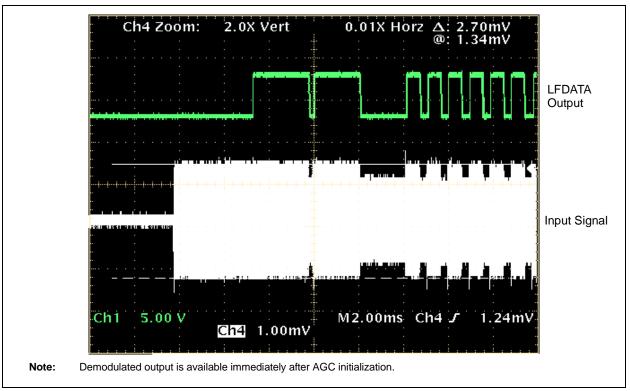

FIGURE 2-29: Input Signal and Demodulated Output When the Output Enable Filter is Disabled.

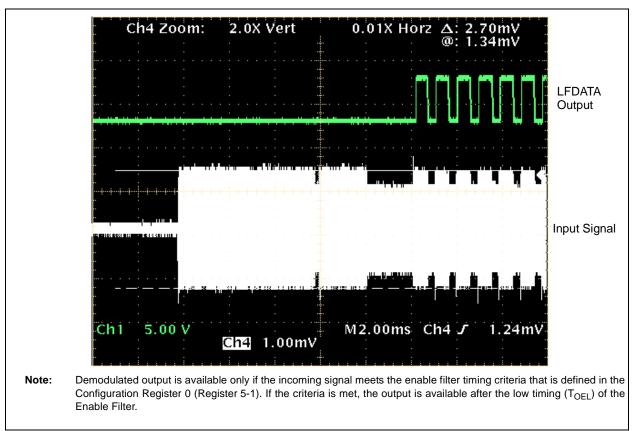

**FIGURE 2-30:** Input Signal and Demodulator Output When Output Enable Filter is Enabled and Input Meets Filter Timing Requirements.

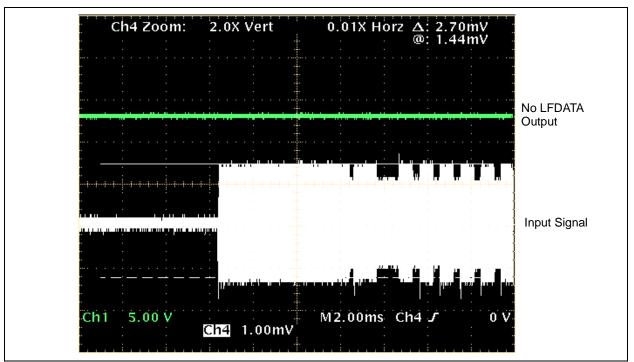

**FIGURE 2-31:** No Demodulator Output When Output Enable Filter is Enabled But Input Does Not Meet Filter Timing Requirements.

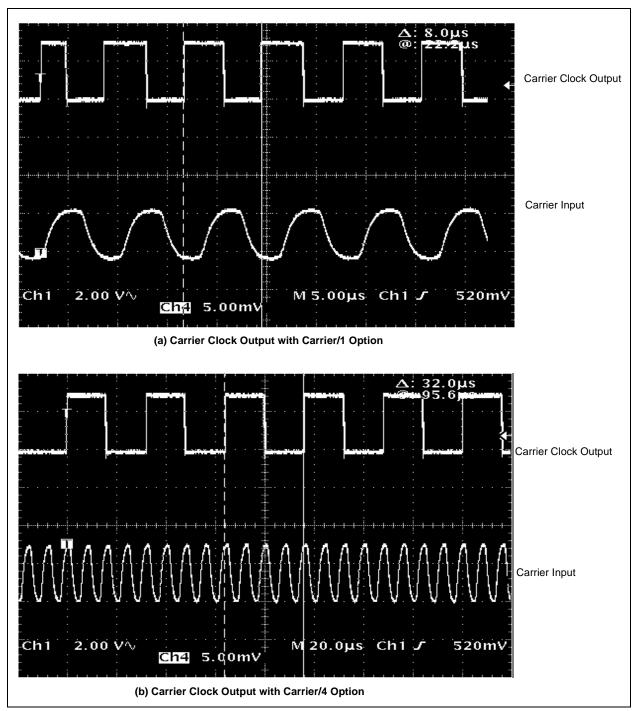

FIGURE 2-32: Carrier Clock Output Examples.

### 3.0 PIN DESCRIPTIONS

TABLE 3-1: PIN FUNCTION TABLES

| Pin No. | Symbol           | I/O/P | Function                                                                                                                                                                            |

|---------|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>SS</sub>  | Р     | Ground Pin.                                                                                                                                                                         |

| 2       | <del>CS</del>    | I     | Chip Select Digital Input Pin.                                                                                                                                                      |

| 3       | SCLK/ALERT       | I/O   | Clock input for the modified 3-wire SPI interface.  ALERT output: This pin goes low if there is a parity error in the Configuration register or the 32 ms alarm timer is timed out. |

| 4       | RSSI             | 0     | Received Signal Strength Indicator (RSSI) current output.                                                                                                                           |

| 5       | NC               | N/A   | No Connect.                                                                                                                                                                         |

| 6       | LFDATA/CCLK/SDIO | I/O   | Demodulated data output. Carrier clock output. Serial input or output data for the modified 3-wire SPI interface.                                                                   |

| 7       | V <sub>DD</sub>  | Р     | Positive Supply Voltage Pin.                                                                                                                                                        |

| 8       | V <sub>DD</sub>  | Р     | Positive Supply Voltage Pin.                                                                                                                                                        |

| 9       | LCZ              | I     | Input pin for external LC antennas.                                                                                                                                                 |

| 10      | LCY              | I     | Input pin for external LC antennas.                                                                                                                                                 |

| 11      | LCX              | I     | Input pin for external LC antennas.                                                                                                                                                 |

| 12      | NC               | N/A   | No Connect.                                                                                                                                                                         |

| 13      | LCCOM            | I     | Common reference input for the external LC antennas.                                                                                                                                |

| 14      | V <sub>SS</sub>  | Р     | Ground Pin.                                                                                                                                                                         |

Type Identification: I = Input; O = Output; P = Power

# 3.1 Supply Voltage (V<sub>DD</sub>, V<sub>SS</sub>)

The  $V_{DD}$  pin is the power supply pin for the analog and digital circuitry within the MCP2030. This pin requires an appropriate bypass capacitor of 0.1  $\mu$ F. The voltage on this pin should be maintained in the 2.0V-3.6V range for specified operation.

The  $V_{SS}$  pin is the ground pin and the current return path for both analog and digital circuitry of the MCP2030. If an analog ground plane is available, it is recommended that this device be tied to the analog ground plane of the PCB.

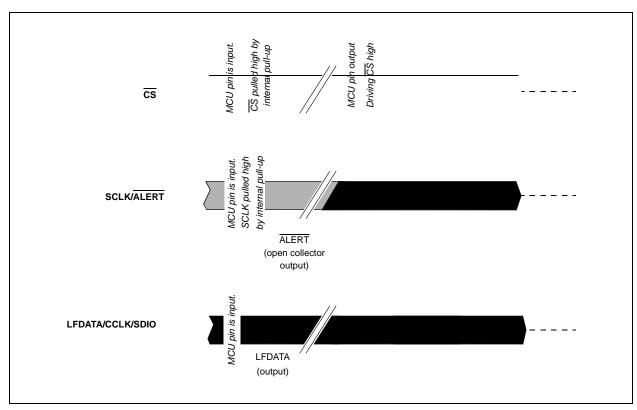

# 3.2 Chip Select (CS)

The  $\overline{CS}$  pin needs to stay high when the device is receiving input signals. Leaving the  $\overline{CS}$  pin low will place the device in the SPI Programming mode.

The  $\overline{\text{CS}}$  pin is an open collector output. This pin has an internal pull-up resistor to ensure that no spurious SPI communication occurs between power-up and pin configuration of the MCU.

# 3.3 SPI Clock Input (SCLK/ALERT)

This pin becomes the SPI clock input (SCLK) when  $\overline{CS}$  is low, and becomes the  $\overline{ALERT}$  output when  $\overline{CS}$  is high.

The ALERT pin is an open collector output. This pin has an internal pull-up resistor to ensure that no spurious SPI communication occurs between power-up and pin configuration of the MCU.

# 3.4 Received Signal Strength Indicator (RSSI)

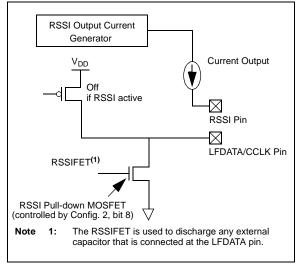

This pin becomes the Received Signal Strength Indicator (RSSI) output current sink when the RSSI output option is selected.

# 3.5 Demodulated Data Output (LFDATA) Carrier Clock Output (CCLK) SPI Data I/O (SDIO)

When the  $\overline{\text{CS}}$  pin is high, this pin is an output pin for demodulated data or carrier clock depending on output type selection. When carrier clock output (CCLK) is selected, the LFDATA output is a square pulse of the input carrier clock and is available as soon as the AGC stabilization time ( $T_{\text{STAB}}$ ) is completed.

When the  $\overline{\text{CS}}$  pin is low, this pin becomes the SPI data input and output (SDIO).

# 3.6 LC Input (LCX, LCY, LCZ)

These pins are the input pins for the external LC resonant antenna circuits. The antenna circuits are connected between the LC pin and the LCCOM pin.

# 3.7 LC Common Reference (LCCOM)

This pin is the common reference input pin for the external LC resonant circuit.

## 4.0 APPLICATION INFORMATION

The MCP2030 is a stand-alone 3-channel analog front-end device for low frequency (LF) sensing and bidirectional transponder applications. By connecting three orthogonally placed LC resonant antennas to the LC input pins, it can detect signals from all directions (x, y and z).

The device draws more current when all channels are enabled as compared to a single channel; therefore, it is recommended to disable any unused channels by setting Configuration Register 0 (Register 5-1).

The device's high input sensitivity (as low as 1  $\rm mV_{PP}$ ) and ability to detect weakly modulated (as low as 8%) input signals with its low power feature set, makes the device suitable for various applications such as a low-cost hands-free Passive Keyless Entry (PKE) transponder, an LF Initiator sensor for Tire Pressure Monitoring Systems (TPMS) and long-range access control applications in the automotive and security industries.

# 4.1 Battery Back-up and Batteryless Operation

The device supports both battery back-up and batteryless operation by the addition of external components, allowing the device to be partially or completely powered from the field.

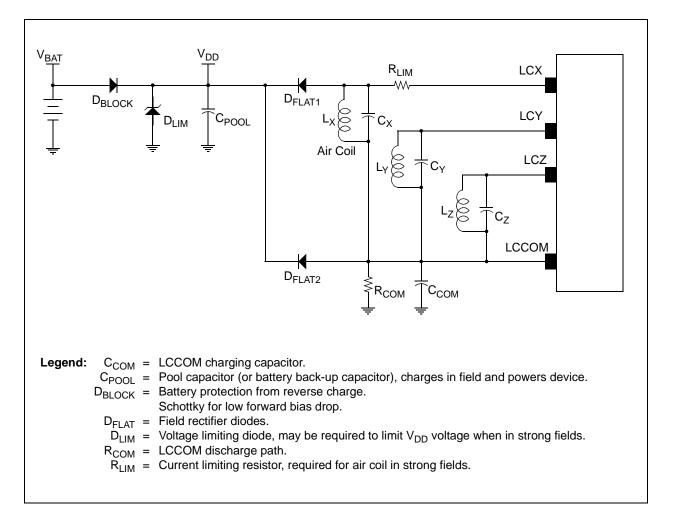

Figure 4-1 shows an example of the external circuit for the battery back-up.

Note: Voltage on LCCOM combined with coil input voltage must not exceed the maximum LC input voltage.

FIGURE 4-1: External Circuit Example for LF Field Powering and Battery Back-up Mode.

# 4.2 Application Examples

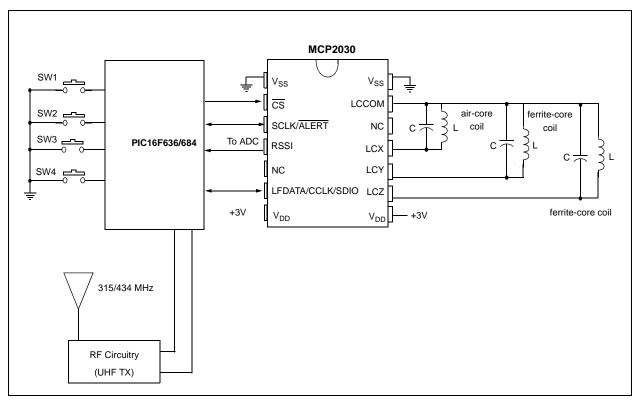

Figure 4-2 shows an example of an external circuit for a bidirectional communication transponder application.

Each LC input pin is connected to an external LC resonant circuit. To achieve the best performance, the resonant frequency of the LC circuit needs to be matched to the detecting carrier frequency of interest. The resonant frequency is given by the following equation:

$$f_o = \frac{1}{2\pi\sqrt{LC}}$$

In typical 125 kHz applications, the L value is a few mH, and the C value is a few hundred pF, for example, L=4.9 mH, and C=331 pF.

The resonant frequency can be fine-tuned by programming the internal tuning capacitors.

The output of the MCP2030 is fed into the external MCU. The external MCU can send data by clamping on and clamping off the MCP2030 coil voltages using an SPI command, or via a UHF transmitter.

The RSSI output of the MCP2030 can be digitized by the MCU firmware. Users can also consider using a MCU that has an internal analog-to-digital converter (ADC) such as the PIC16F684 or a stand-alone ADC device.

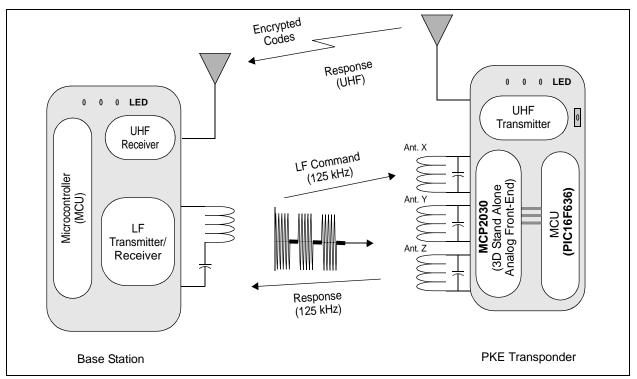

Figure 4-3 shows an example of a hands-free Passive Keyless Entry (PKE) system. The base station unit transmits an LF command. The MCP2030 detects the base station command and feeds the detected output to the external MCU (PIC16F636). If the command is correct, the MCU responds via an external UHF transmitter or by using the LF talk-back modulators of the MCP2030 device.

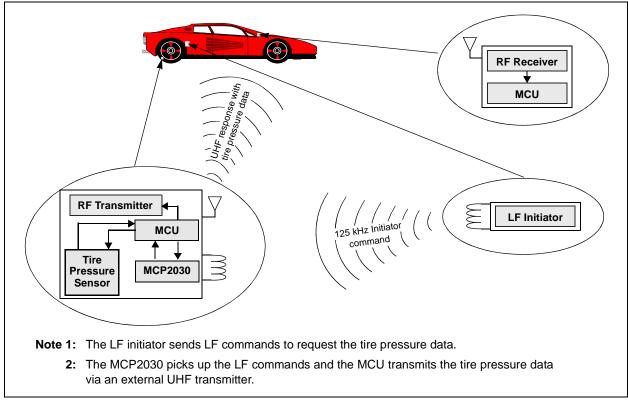

Figure 4-4 shows an example when the device is used for a tire pressure monitoring sensor application. The device detects the LF Initiator commands and transmits the tire pressure data to the base station via an external UHF transmitter.

FIGURE 4-2: Example of External Circuits for Bidirectional Communication Transponder Applications.

FIGURE 4-3: Example of Bidirectional Hand-free Passive Keyless Entry (PKE) System.

FIGURE 4-4: Example of Tire Pressure Monitoring Sensor Applications.

# **MCP2030**

**NOTES:**

# 5.0 FUNCTIONAL DESCRIPTION AND THEORY OF DEVICE OPERATION

The MCP2030 contains three analog input channels for signal detection and LF talk-back. This section provides the function description of the device.

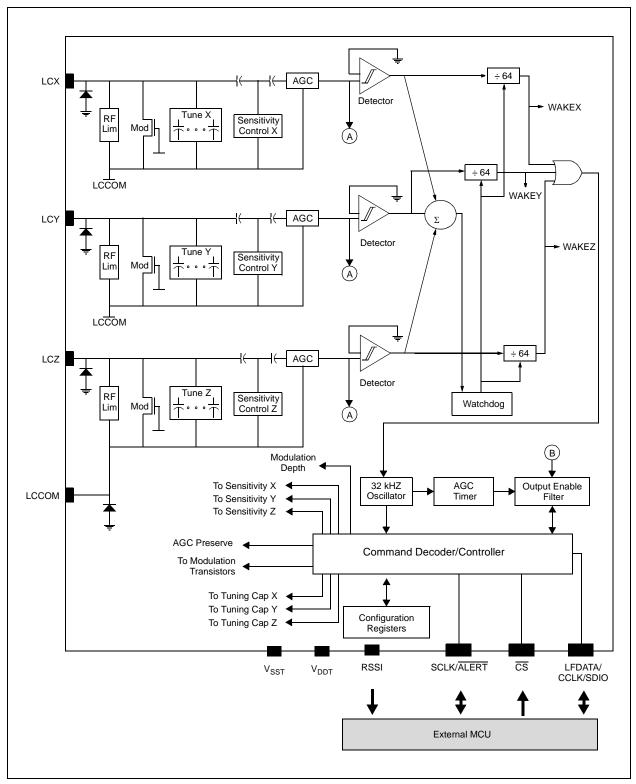

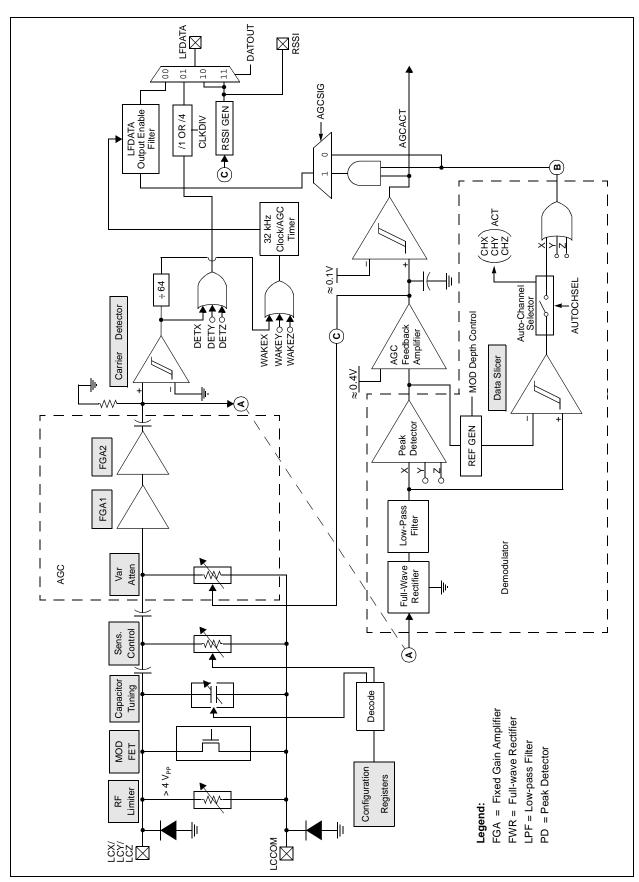

Each analog input channel has internal tuning capacitors, sensitivity control circuits, an input signal strength limiter and an LF talk-back modulation transistor. An Automatic Gain Control (AGC) loop is used for all three input channel gains. The output of each channel is OR'd and fed into a demodulator. The digital output is passed to the LFDATA pin. Figure 5-1 shows the block diagram of the device and Figure 5-2 shows the input signal path.

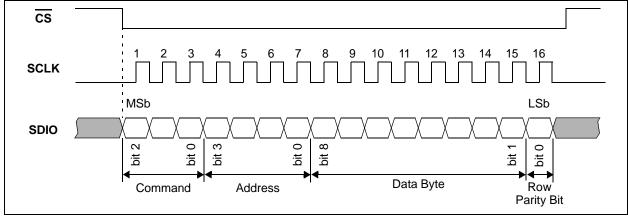

There are a total of eight Configuration registers. Six of them are used for device operation options, one for column parity bits and one for status indication of device operation. Each register has 9 bits including one row parity bit. These registers are readable and writable by SPI commands except for the STATUS register, which is read-only.

The device's features are dynamically controllable by programming the Configuration registers.

### 5.1 RF Limiter

The RF Limiter limits LC pin input voltage by de-Q'ing the external LC resonant antenna circuit. The limiter begins de-Q'ing the external LC antenna when the input voltage exceeds  $V_{DE\_Q}$ , progressively de-Q'ing harder to reduce the antenna input voltage.

The signal levels from all 3 channels are combined such that the limiter attenuates all 3 channels uniformly, in respect to the channel with the strongest signal.

### 5.2 Modulation Circuit

The modulation circuit consists of a modulation transistor (FET), internal tuning capacitors and external LC antenna components. The modulation transistor and the internal tuning capacitors are connected between the LC input pin and LCCOM pin. Each LC input has its own modulation transistor.

When the modulation transistor turns on, its low Turnon Resistance ( $R_{\rm M}$ ) clamps the induced LC antenna voltage. The coil voltage is minimized when the modulation transistor turns-on and maximized when the modulation transistor turns-off. The modulation transistor's low turn-on resistance ( $R_{\rm M}$ ) results in a high modulation depth.

The LF talk-back is achieved by turning on and off the modulation transistor.

The modulation data comes from the external microcontroller section via the digital SPI as "Clamp On", "Clamp Off" commands. Only those inputs that are enabled will execute the Clamp command. A basic block diagram of the modulation circuit is shown in Figure 5-1 and Figure 5-2.

The modulation FET is also shorted momentarily after Soft Reset and Inactivity timer time-out.

# 5.3 Tuning Capacitor

Each channel has internal tuning capacitors for external antenna tuning. The capacitor values are programmed by the Configuration registers up to 63 pF, 1 pF per step.

**Note:** The user can control the tuning capacitor by programming the Configuration registers. See Register 5-2 through Register 5-4 for details.

#### 5.4 Variable Attenuator

The variable attenuator is used to attenuate, via AGC control, the input signal voltage to avoid saturating the amplifiers and demodulators.

**Note:** The variable attenuator function is accomplished by the device itself. The user cannot control its function.

# 5.5 Sensitivity Control

The sensitivity of each channel can be reduced by the channel's Configuration register sensitivity setting. This is used to desensitize the channel from optimum.

**Note:** The user can desensitize the channel sensitivity by programming the Configuration registers. See Register 5-5 and Register 5-6 for details.

### 5.6 AGC Control

The AGC controls the variable attenuator to limit the internal signal voltage to avoid saturation of internal amplifiers and demodulators (Refer to **Section 5.4** "Variable Attenuator").

The signal levels from all 3 channels are combined such that the AGC attenuates all 3 channels uniformly in respect to the channel with the strongest signal.

**Note:** The AGC control function is accomplished by the device itself. The user cannot control its function.

### 5.7 Fixed Gain Amplifiers 1 and 2

FGA1 and FGA2 provides a maximum two-stage gain of 40 dB.

**Note:** The user cannot control the gain of these two amplifiers.

### 5.8 Auto-Channel Selection

The auto-channel selection feature is enabled if the Auto-Channel Select bit AUTOCHSEL<8> in Configuration Register 5 (Register 5-6) is set, and disabled if the bit is cleared. When this feature is active (i.e., AUTOCHSE <8> = 1), the control circuit checks the demodulator output of each input channel immediately after the AGC settling time ( $T_{STAB}$ ). If the output is high, it allows this channel to pass data, otherwise it is blocked.

The status of this operation is monitored by STATUS Register 7 bits <8:6> (Register 5-8). These bits indicate the current status of the channel selection activity, and automatically updates for every Soft Reset period. The auto-channel selection function resets after each Soft Reset (or after Inactivity timer time-out). Therefore, the blocked channels are re-enabled after Soft Reset.

This feature can make the output signal cleaner by blocking any channel that was not high at the end of  $T_{AGC}$ . This function works only for demodulated data output, and is not applied for carrier clock or RSSI output.

#### 5.9 Carrier Clock Detector

The Carrier Clock Detector senses the input carrier cycles. The output of the detector switches digitally at the signal carrier frequency. Carrier clock output is available when the output is selected by the DATOUT bit in Configuration Register 1 (Register 5-2).

### 5.10 Demodulator

The Demodulator consists of a full-wave rectifier, low pass filter, peak detector and Data Slicer that detects the envelope of the input signal.

#### 5.11 Data Slicer

The Data Slicer consists of a reference generator and comparator. The Data Slicer compares the input with the reference voltage. The reference voltage comes from the minimum modulation depth requirement setting and input peak voltage. The data from all 3 channels are OR'd together and sent to the output enable filter.

### 5.12 Output Enable Filter

The Output Enable Filter enables the LFDATA output once the incoming signal meets the wake-up sequence requirements (see Section 5.15 "Configurable Output Enable Filter").

# 5.13 Received Signal Strength Indicator (RSSI)

The RSSI provides a current which is proportional to the input signal amplitude (see Section 5.30.3 "Received Signal Strength Indicator (RSSI) Output").

### 5.14 Analog Front-End Timers

The device has an internal 32 kHz RC oscillator. The oscillator is used in several timers:

- Inactivity timer

- Alarm timer

- Pulse width timer

- · Period timer

- · AGC settling timer

#### 5.14.1 RC OSCILLATOR

The RC oscillator generates a 32 kHz internal clock.

#### 5.14.2 INACTIVITY TIMER

The Inactivity Timer is used to automatically return the device to Standby mode, if there is no input signal. The time-out period is approximately 16 ms (T<sub>INACT</sub>), based on the 32 kHz internal clock.

The purpose of the Inactivity Timer is to minimize current draw by automatically returning to the lower current Standby mode, if there is no input signal for approximately 16 ms.

The timer is reset when:

- An amplitude change in LF input signal, either high-to-low or low-to-high

- CS pin is low (any SPI command)

- · Timer-related Soft Reset

The timer starts after AGC initialization time  $(T_{AGC})$ .

The timer causes a Soft Reset when:

A previously received input signal does not change either high-to-low or low-to-high for T<sub>INACT</sub>

The Soft Reset returns the device to Standby mode where most of the analog circuits, such as the AGC, demodulator and RC oscillator, are powered down. This returns the device to the lower Standby Current mode.

### 5.14.3 ALARM TIMER

The Alarm Timer is used to notify the external MCU that the device is receiving an input signal that does not pass the output enable filter requirement. The time-out period is approximately 32 ms ( $T_{ALARM}$ ) in the presence of continuing noise.

The Alarm Timer time-out occurs if there is an input signal for longer than 32 ms that does not meet the output enable filter requirements. The Alarm Timer time-out causes:

- a) The ALERT pin to go low.

- The ALARM bit to set in the Status STATUS Register 7 (Register 5-8).

The external MCU is informed of the Alarm timer timeout by monitoring the ALERT pin. If the Alarm timer time-out occurs, the external MCU can take appropriate actions such as lowering channel sensitivity or disabling channels. If the noise source is ignored, the device can return to a lower standby current draw state. The timer is reset when the:

- $\overline{\text{CS}}$  pin is low (any SPI command).

- · Output enable filter is disabled.

- LFDATA pin is enabled (signal passed output enable filter).

The timer starts after the AGC initialization time.

The timer causes a low output on the ALERT pin when:

Output enable filter is enabled and modulated input signal is present for T<sub>ALARM</sub>, but does not pass the output enable filter requirement.

**Note:** The Alarm timer is disabled if the output enable filter is disabled.

#### 5.14.4 PULSE WIDTH TIMER

The Pulse Width Timer is used to verify that the received output enable sequence meets both the minimum  $T_{\text{OEH}}$  and minimum  $T_{\text{OEL}}$  requirements.

#### 5.14.5 PERIOD TIMER

The Period Timer is used to verify that the received output enable sequence meets the maximum  $T_{\mbox{\scriptsize OET}}$  requirement.

## 5.14.6 AGC INITIALIZATION TIMER $(T_{AGC})$

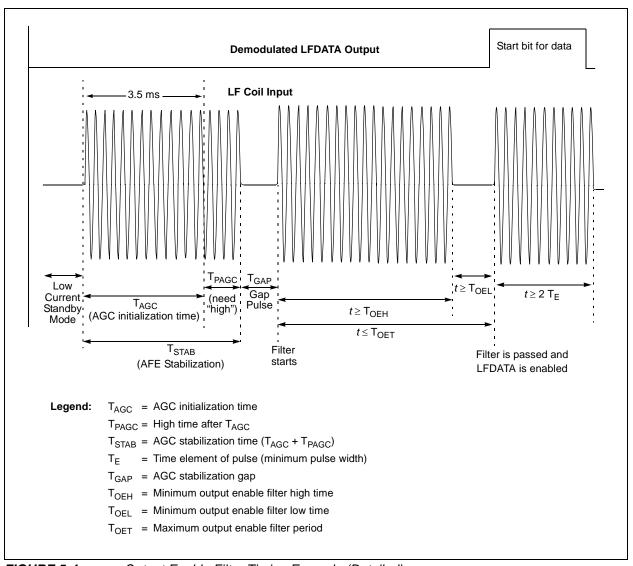

This timer is used to keep the output enable filter in Reset while the AGC settles on the input signal. The time-out period is approximately 3.5 ms. At the end of this time ( $T_{AGC}$ ), the input should remain high ( $T_{PAGC}$ ), otherwise the counting is aborted and a Soft Reset is issued. See Figure 5-4 for details.

- Note 1: The device needs continuous and uninterrupted high input signal during AGC initialization time (T<sub>AGC</sub>). Any absence of signal during this time may reset the timer and a new input signal is needed for AGC settling time, or may result in improper AGC gain settings which will produce invalid output.

- 2: The rest of the device section wakes up if any of these input channels receive the AGC settling time correctly. STATUS Register 7 bits <4:2> (Register 5-8) indicate which input channels have waken up the device first. Valid input signal on multiple input pins can cause more than one channel's indicator bit to be set.

FIGURE 5-1: Functional Block Diagram.

FIGURE 5-2: Input Signal Path.

# 5.15 Configurable Output Enable Filter

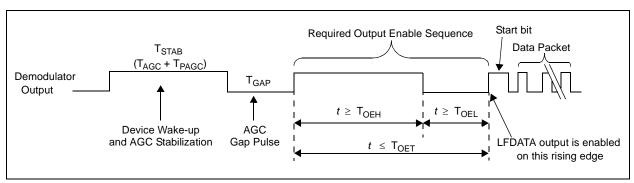

The purpose of this filter is to enable the LFDATA output and wake the external microcontroller only after receiving a specific sequence of pulses on the LC input pins. Therefore, it prevents waking up the external microcontroller due to noise or unwanted input signals. The circuit compares the timing of the demodulated header waveform with a pre-defined value, and enables the demodulated LFDATA output when a match occurs.

The output enable filter consists of a high ( $T_{OEH}$ ) and low duration ( $T_{OEL}$ ) of a pulse immediately after the AGC settling gap time. The selection of high and low times further implies a max period time. The output enable high and low times are determined by SPI programming. Figure 5-3 and Figure 5-4 show the output enable filter waveforms.

There should be no missing cycles during  $T_{\text{OEH}}$ . Missing cycles may result in failing the output enable condition.

FIGURE 5-3: Output Enable Filter Timing.

FIGURE 5-4: Output Enable Filter Timing Example (Detailed).

TABLE 5-1: OUTPUT ENABLE FILTER TIMING

| OEL<br><1:0> | T <sub>OEH</sub> (ms)                        | T <sub>OEL</sub><br>(ms)        | T <sub>OET</sub> (ms)                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|--------------|----------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 00           | 1                                            | 1                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 01           | 1                                            | 1                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |