# MRF24J40 Data Sheet

IEEE 802.15.4<sup>™</sup> 2.4 GHz RF Transceiver

© 2021 Microchip Technology Inc.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are

committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection

feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or

other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES. IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-7738-9

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **MRF24J40**

### IEEE 802.15.4<sup>™</sup> 2.4 GHz RF Transceiver

#### Features:

- IEEE 802.15.4™ Standard Compliant RF Transceiver

- Supports ZigBee<sup>®</sup>, MiWi<sup>™</sup>, MiWi P2P and Proprietary Wireless Networking Protocols

- Simple, 4-Wire Serial Peripheral Interface (SPI)

- Integrated 20 MHz and 32.768 kHz Crystal Oscillator Circuitry

- Low-Current Consumption:

- RX mode: 19 mA (typical)

- TX mode: 23 mA (typical)

- Sleep: 2 µA (typical)

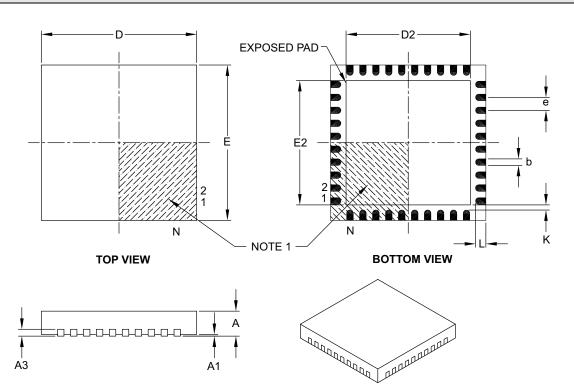

- Small, 40-Pin Leadless QFN 6x6 mm<sup>2</sup> Package

#### **RF/Analog Features:**

- · ISM Band 2.405-2.48 GHz Operation

- Data Rate: 250 kbps (IEEE 802.15.4); 625 kbps (Turbo mode)

- -95 dBm Typical Sensitivity with +5 dBm Maximum Input Level

- +0 dBm Typical Output Power with 36 dB TX Power Control Range

- Differential RF Input/Output with Integrated TX/RX Switch

- Integrated Low Phase Noise VCO, Frequency Synthesizer and PLL Loop Filter

- Digital VCO and Filter Calibration

- Integrated RSSI ADC and I/Q DACs

- · Integrated LDO

- · High Receiver and RSSI Dynamic Range

#### **MAC/Baseband Features:**

- Hardware CSMA-CA Mechanism, Automatic Acknowledgement Response and FCS Check

- Independent Beacon, Transmit and GTS FIFO

- Supports all CCA modes and RSSI/ED

- Automatic Packet Retransmit Capability

- Hardware Security Engine (AES-128) with CTR, CCM and CBC-MAC modes

- Supports Encryption and Decryption for MAC Sublayer and Upper Layer

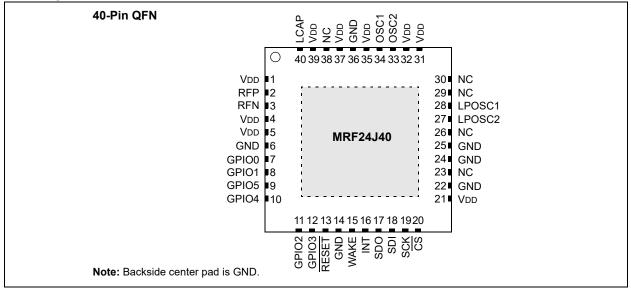

#### Pin Diagram:

# **MRF24J40**

| 1.0   | Overview                             | 5   |  |  |  |

|-------|--------------------------------------|-----|--|--|--|

|       | Hardware Description                 |     |  |  |  |

| 3.0   | Functional Description               | 89  |  |  |  |

| 4.0   | Applications                         | 135 |  |  |  |

| 5.0   | Electrical Characteristics           | 141 |  |  |  |

|       | Packaging Information                |     |  |  |  |

| Apper | ndix A: Revision History             | 147 |  |  |  |

| Produ | ct Identification System             | 149 |  |  |  |

|       | licrochip Website                    |     |  |  |  |

| Custo | Customer Change Notification Service |     |  |  |  |

| Custo | Customer Support                     |     |  |  |  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Website; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

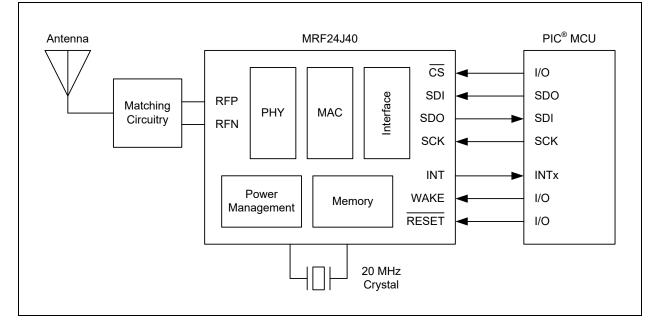

#### 1.0 OVERVIEW

The MRF24J40 is an IEEE 802.15.4<sup>™</sup> Standard compliant 2.4 GHz RF transceiver. It integrates the PHY and MAC functionality in a single chip solution. Figure 1-1 shows a simplified block diagram of a MRF24J40 wireless node. The MRF24J40 creates a low-cost, low-power, low data rate (250 or 625 kbps) Wireless Personal Area Network (WPAN) device. The MRF24J40 interfaces to many popular Microchip PIC<sup>®</sup> microcontrollers via a 4-wire serial SPI interface, interrupt, wake and Reset pins.

The MRF24J40 provides hardware support for:

- · Energy Detection

- Carrier Sense

- Three CCA Modes

- CSMA-CA Algorithm

- Automatic Packet Retransmission

- Automatic Acknowledgment

- Independent Transmit, Beacon and GTS FIFO Buffers

- Security Engine supports Encryption and Decryption for MAC Sublayer and Upper Layer

These features reduce the processing load, allowing the use of low-cost 8-bit microcontrollers.

The MRF24J40 is compatible with Microchip's ZigBee<sup>®</sup>, MiWi™ and MiWi P2P software stacks. Each software stack is available as a free download, including source code, from the Microchip web site: http://www.microchip.com/wireless.

FIGURE 1-1: WIRELESS NODE BLOCK DIAGRAM

#### 1.1 IEEE 802.15.4-2003 Standard

The MRF24J40 is compliant with the IEEE 802.15.4<sup>TM</sup>-2003 Standard. The Standard specifies the physical (PHY) and Media Access Controller (MAC) functions that form the basis for a wireless network device. Figure 1-2 shows the structure of the PHY packet and MAC frame.

It is highly recommended that the design engineer be familiar with the IEEE 802.15.4-2003 Standard in order to best understand the configuration and operation of the MRF24J40. The Standard can be downloaded from the IEEE web site: http://www.ieee.org.

#### FIGURE 1-2: IEEE 802.15.4<sup>™</sup> PHY PACKET AND MAC FRAME STRUCTURE

|                  |                      |                   |                  | 2                  | 1                   | 2 octets                    |               |                              |                |     |           |        |

|------------------|----------------------|-------------------|------------------|--------------------|---------------------|-----------------------------|---------------|------------------------------|----------------|-----|-----------|--------|

| MAC Sublayer     | Ack                  | nowledgn<br>Frame | ient             | Frame<br>Control   | Sequence<br>Number  | FCS                         |               |                              |                |     |           |        |

|                  |                      |                   |                  | М                  | HR                  | MFR                         |               |                              |                |     |           |        |

|                  |                      |                   |                  |                    |                     |                             |               |                              |                |     | 7         |        |

|                  |                      |                   |                  | 2                  | 1                   | 4 to 20                     |               |                              | n              |     | 2         | octets |

| MAC Sublayer     |                      | Data<br>Frame     |                  | Frame<br>Control   | Sequence<br>Number  | Adressing<br>Fields         |               |                              | Data Payload   |     | FCS       |        |

|                  |                      |                   |                  |                    | M                   | łR                          |               |                              | MSDU           |     | MFR       |        |

|                  |                      |                   |                  | 2                  | 1                   | 4 to 20                     | 1             |                              | r              | 1   | 2         | octets |

| MAC Sublayer     | MAC Command<br>Frame |                   | Frame<br>Control | Sequence<br>Number | Adressing<br>Fields | Command<br>Type             |               | Command                      | l Payload      | FCS |           |        |

|                  |                      |                   |                  |                    | MI                  | IR                          |               |                              | MSDU           |     | MFR       |        |

|                  |                      |                   |                  | 2                  | 1                   | 4 or 10                     | 2             | k                            | m              | п   | 2         | octets |

| MAC Sublayer     | Beacon<br>Frame      |                   | Frame<br>Control | Sequence<br>Number | Adressing<br>Fields | Superframe<br>Specification | GTS<br>Fields | Pending<br>Address<br>Fields | Beacon Payload | FCS |           |        |

|                  |                      |                   |                  |                    | Mi                  | IR                          |               |                              | MSDU           |     | MFR       |        |

|                  | 4                    | 1                 | 1                | 1                  |                     |                             |               | 5 – 127                      |                |     |           | octets |

| PHY Layer        | Preamble             | SFD               | Frame<br>Length  |                    |                     |                             |               | PSDU                         |                |     |           |        |

|                  | SH                   | łR                | PHR              |                    |                     |                             |               | PHY Payload                  |                |     |           |        |

|                  |                      |                   |                  |                    |                     |                             |               |                              |                |     | <br> <br> |        |

| On air<br>packet |                      |                   |                  |                    |                     |                             | PPDU          |                              |                |     |           |        |

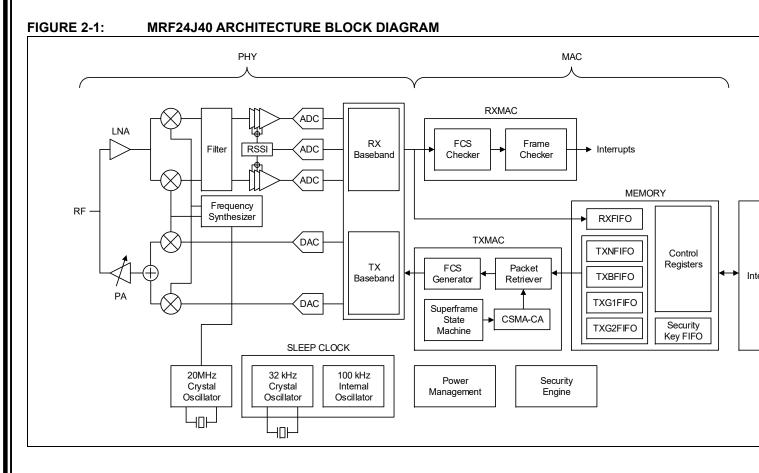

#### 2.0 HARDWARE DESCRIPTION

#### 2.1 2.1 Overview

The MRF24J40 is an IEEE 802.15.4 Standard compliant 2.4 GHz RF transceiver. It integrates the PHY and MAC functionality in a single chip solution. Figure 2-1 is a block diagram of the MRF24J40 circuitry.

A frequency synthesizer is clocked by an external 20 MHz crystal and generates a 2.4 GHz RF frequency.

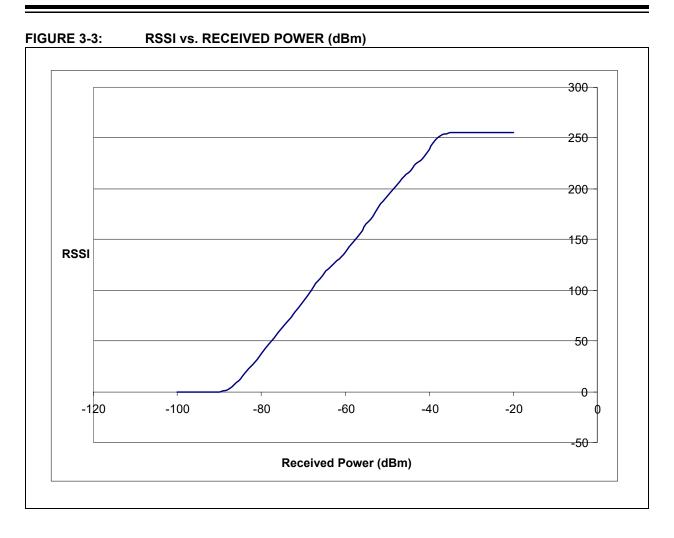

The receiver is a low-IF architecture consisting of a Low Noise Amplifier (LNA), down conversion mixers, polyphase channel filters and baseband limiting amplifiers with a Receiver Signal Strength Indicator (RSSI).

The transmitter is a direct conversion architecture with a 0 dBm maximum output (typical) and 36 dB power control range.

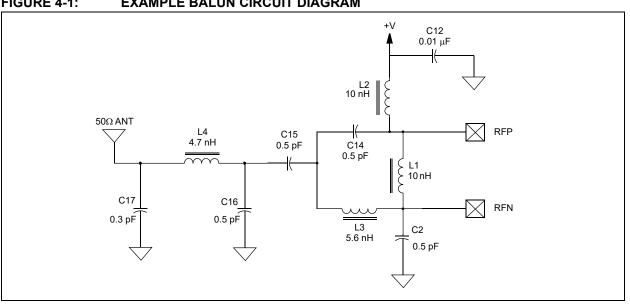

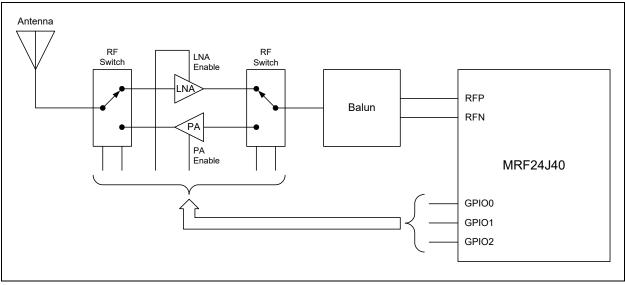

An internal Transmit/Receive (TR) switch combines the transmitter and receiver circuits into differential RFP and RFN pins. These pins are connected to impedance matching circuitry (balun) and antenna. An external Power Amplifier (PA) and/or LNA can be controlled via the GPIO pins.

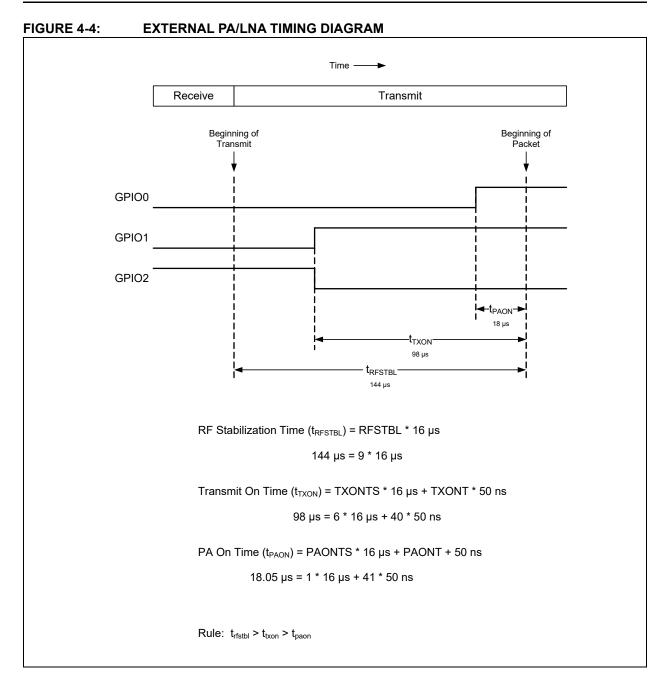

Six General Purpose Input/Output (GPIO) pins can be configured for control or monitoring purposes. They can also be configured to control external PA/LNA RF switches.

The power management circuitry consists of an integrated Low Dropout (LDO) voltage regulator. The MRF24J40 can be placed into a very low-current (2  $\mu$ A typical) Sleep mode. An internal 100 kHz oscillator or 32 kHz external crystal oscillator can be used for Sleep mode timing.

The Media Access Controller (MAC) circuitry verifies reception and formats for transmission IEEE 802.15.4 Standard compliant packets. Data is buffered in Transmit and Receive FIFOs. Carrier Sense Multiple Access-Collision Avoidance (CSMA-CA), superframe constructor, receive frame filter and security engine functionality are implemented in hardware. The security engine provides hardware circuitry for AES-128 with CTR, CCM and CBC-MAC modes.

Control of the transceiver is via a 4-wire SPI, interrupt, wake and Reset pins.

#### 2.2 Block Diagram

DS30009776E-page 8

Preliminary

#### 2.3 Pin Descriptions

| TABLE 2-1: | <b>MRF24J40 PIN DESCRIPTIONS</b> |

|------------|----------------------------------|

|            |                                  |

| Pin | Symbol | Туре   | Description                                                                                           |

|-----|--------|--------|-------------------------------------------------------------------------------------------------------|

| 1   | Vdd    | Power  | RF power supply. Bypass with a capacitor as close to the pin as possible.                             |

| 2   | RFP    | AIO    | Differential RF input/output (+).                                                                     |

| 3   | RFN    | AIO    | Differential RF input/output (-).                                                                     |

| 4   | Vdd    | Power  | RF power supply. Bypass with a capacitor as close to the pin as possible.                             |

| 5   | Vdd    | Power  | Guard ring power supply. Bypass with a capacitor as close to the pin as possible.                     |

| 6   | GND    | Ground | Guard ring ground.                                                                                    |

| 7   | GPIO0  | DIO    | General purpose digital I/O, also used as external PA enable.                                         |

| 8   | GPIO1  | DIO    | General purpose digital I/O, also used as external TX/RX switch control.                              |

| 9   | GPIO5  | DIO    | General purpose digital I/O.                                                                          |

| 10  | GPIO4  | DIO    | General purpose digital I/O.                                                                          |

| 11  | GPIO2  | DIO    | General purpose digital I/O, also used as external TX/RX switch control.                              |

| 12  | GPIO3  | DIO    | General purpose digital I/O.                                                                          |

| 13  | RESET  | DI     | Global hardware Reset pin active-low.                                                                 |

| 14  | GND    | Ground | Ground for digital circuit.                                                                           |

| 15  | WAKE   | DI     | External wake-up trigger (must be enabled in software).                                               |

| 16  | INT    | DO     | Interrupt pin to microcontroller.                                                                     |

| 17  | SDO    | DO     | Serial interface data output from MRF24J40.                                                           |

| 18  | SDI    | DI     | Serial interface data input to MRF24J40.                                                              |

| 19  | SCK    | DI     | Serial interface clock.                                                                               |

| 20  | CS     | DI     | Serial interface enable.                                                                              |

| 21  | Vdd    | Power  | Digital circuit power supply. Bypass with a capacitor as close to the pin as possible.                |

| 22  | GND    | Ground | Ground for digital circuit.                                                                           |

| 23  | NC     |        | No Connection.                                                                                        |

| 24  | GND    | Ground | Ground for digital circuit.                                                                           |

| 25  | GND    | Ground | Ground for digital circuit.                                                                           |

| 26  | NC     |        | No Connection. (Allow pin to float; do not connect signal.)                                           |

| 27  | LPOSC2 | Al     | 32 kHz crystal input.                                                                                 |

| 28  | LPOSC1 | AI     | 32 kHz crystal input.                                                                                 |

| 29  | NC     | _      | No Connection. (Allow pin to float; do not connect signal.)                                           |

| 30  | NC     | _      | No Connection. (Allow pin to float; do not connect signal.)                                           |

| 31  | Vdd    | Power  | Power supply for band gap reference circuit. Bypass with a capacitor as close to the pin as possible. |

| 32  | Vdd    | Power  | Power supply for analog circuit. Bypass with a capacitor as close to the pin as possible.             |

| 33  | OSC2   | AI     | 20 MHz crystal input.                                                                                 |

| 34  | OSC1   | AI     | 20 MHz crystal input.                                                                                 |

| 35  | Vdd    | Power  | PLL power supply. Bypass with a capacitor as close to the pin as possible.                            |

| 36  | GND    | Ground | Ground for PLL.                                                                                       |

| 37  | Vdd    | Power  | Charge pump power supply. Bypass with a capacitor as close to the pin as possible.                    |

| 38  | NC     | _      | No Connection.                                                                                        |

| 39  | Vdd    | Power  | VCO supply. Bypass with a capacitor as close to the pin as possible.                                  |

| 40  | LCAP   | _      | PLL loop filter external capacitor. Connected to external 100 pF capacitor.                           |

|     |        |        | al, I = Input, O = Output                                                                             |

**Legend:** A = Analog, D = Digital, I = Input, O = Output

#### 2.4 Power and Ground Pins

Recommended bypass capacitors are listed in Table 2-2. VDD pins 1 and 31 require two bypass capacitors to ensure sufficient bypass decoupling. Minimize trace length from the VDD pin to the bypass capacitors and make them as short as possible.

| <b>TABLE 2-2:</b> | RECOMMENDED BYPASS |  |  |

|-------------------|--------------------|--|--|

|                   | CAPACITOR VALUES   |  |  |

| VDD Pin | Bypass Capacitor  |  |

|---------|-------------------|--|

| 1       | 47 pF and 0.01 μF |  |

| 4       | 47 pF             |  |

| 5       | 0.1 μF            |  |

| 21      | 0.01 μF           |  |

| 31      | 47 pF and 0.01 μF |  |

| 32      | 47 pF             |  |

| 35      | 47 pF             |  |

| 37      | 0.01 μF           |  |

| 39      | 1 μF              |  |

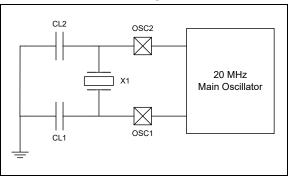

#### 2.5 20 MHz Main Oscillator

The 20 MHz main oscillator provides the main frequency (MAINCLK) signal to internal RF, baseband and MAC circuitry. An external 20 MHz quartz crystal is connected to the OSC1 and OSC2 pins as shown in Figure 2-2. The crystal parameters are listed in Table 2-3.

## TABLE 2-3:20 MHz CRYSTALPARAMETERS<sup>(1)</sup>

| Parameter                                               | Value                  |

|---------------------------------------------------------|------------------------|

| Frequency                                               | 20 MHz                 |

| Frequency Tolerance at 25°C                             | ±20 ppm <sup>(2)</sup> |

| Frequency Stability over Operating<br>Temperature Range | ±20 ppm <sup>(2)</sup> |

| Mode                                                    | Fundamental            |

| Load Capacitance                                        | 10-15 pF               |

| ESR                                                     | 80Ω max.               |

**Note 1:** These values are for design guidance only.

2: IEEE 802.15.4<sup>™</sup> Standard specifies transmitted center frequency tolerance shall be ±40 ppm maximum.

#### FIGURE 2-2: 20 MHz MAIN OSCILLATOR CRYSTAL CIRCUIT

#### 2.6 Phase-Locked Loop

The Phase-Locked Loop (PLL) circuitry requires one external capacitor connected to pin 40 (LCAP). The recommended value is 100 pF. The PCB layout around the capacitor and pin 40 should be designed carefully such as to minimize interference to the PLL.

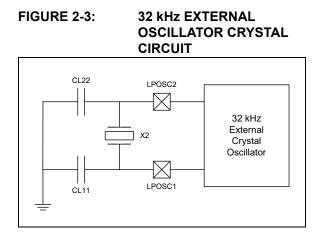

#### 2.7 32 kHz External Crystal Oscillator

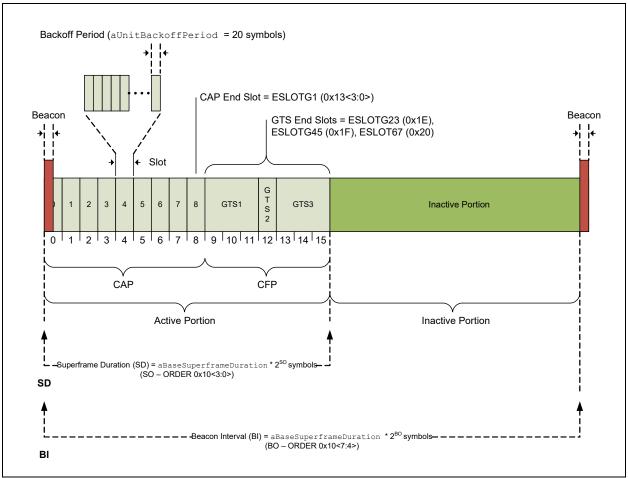

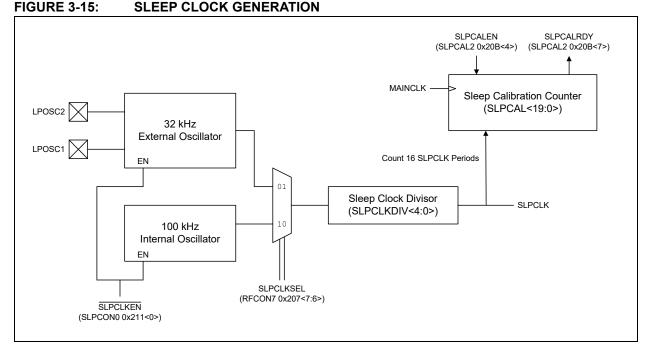

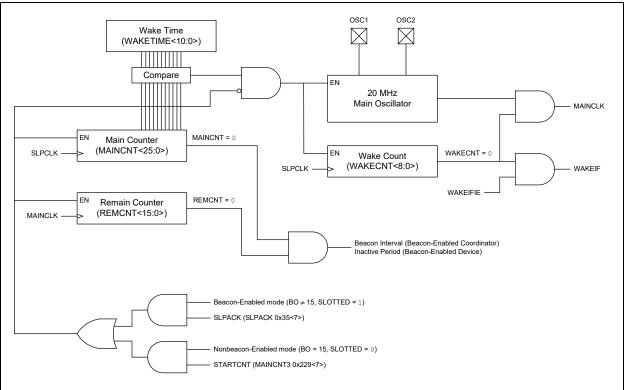

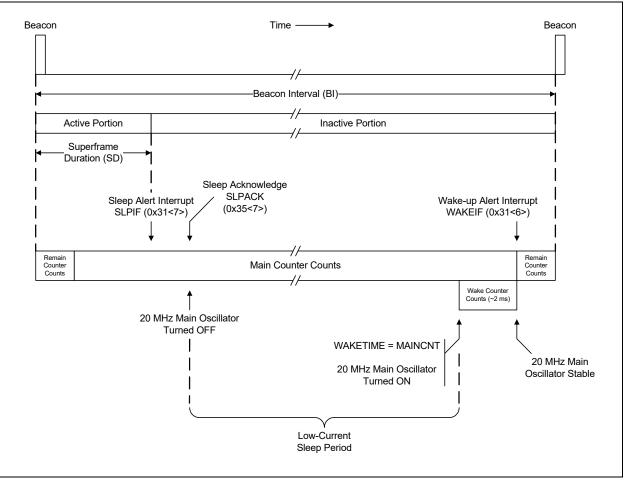

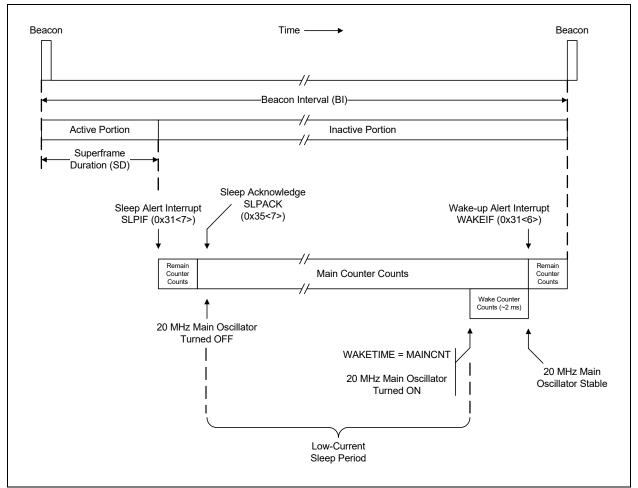

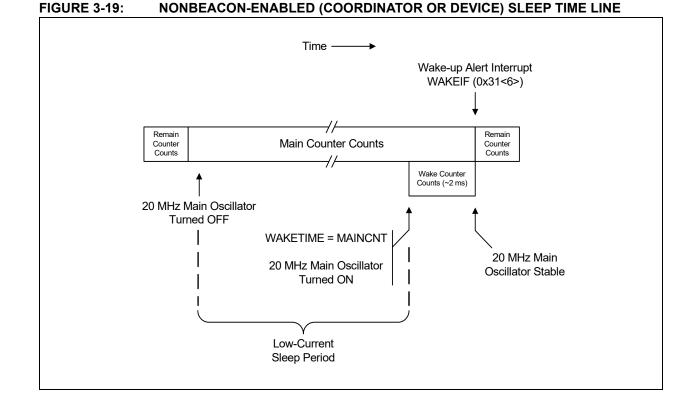

The 32 kHz external crystal oscillator provides one of two Sleep clock (SLPCLK) frequencies to Sleep mode counters. The Sleep mode counters time the Beacon Interval (BI) and inactive period for a beacon-enabled device and the Sleep interval for a nonbeacon-enabled device. Refer to **Section 3.15** "**Sleep**" for more information.

The SLPCLK frequency is selectable between the 32 kHz external crystal oscillator or 100 kHz internal oscillator. The 32 kHz external crystal oscillator provides better frequency accuracy and stability than the 100 kHz internal oscillator. An external 32 kHz tuning fork crystal is connected to the LPOSC1 and LPOSC2 pins, as shown in Figure 2-3. The crystal parameters are listed in Table 2-4.

### TABLE 2-4:32 kHz CRYSTALPARAMETERS(1)

| Parameter           | Value      |

|---------------------|------------|

| Frequency           | 32.768 kHz |

| Frequency Tolerance | ±20 ppm    |

| Load Capacitance    | 12.5 pF    |

| ESR                 | 70 kΩ max. |

Note 1: These values are for design guidance only.

#### 2.8 100 kHz Internal Oscillator

The 100 kHz internal oscillator requires no external components and provides one of two Sleep clock (SLPCLK) frequencies to Sleep mode counters. The Sleep mode counters time the Beacon Interval (BI) and inactive period for a beacon-enabled device and the Sleep interval for a nonbeacon-enabled device. Refer to **Section 3.15 "Sleep"** for more information.

The SLPCLK frequency is selectable between the 32 kHz external crystal oscillator or 100 kHz internal oscillator. The 32 kHz external crystal oscillator provides better frequency accuracy and stability than the 100 kHz internal oscillator. It is recommended that the 100 kHz internal oscillator be calibrated before use. The calibration procedure is given in **Section 3.15.1.2 "Sleep Clock Calibration"**.

#### 2.9 Reset (RESET) Pin

An external hardware Reset can be performed by asserting the RESET pin 13 low. The MRF24J40 will be released from Reset approximately 250  $\mu$ s after the RESET pin is released. The RESET pin has an internal weak pull-up resistor.

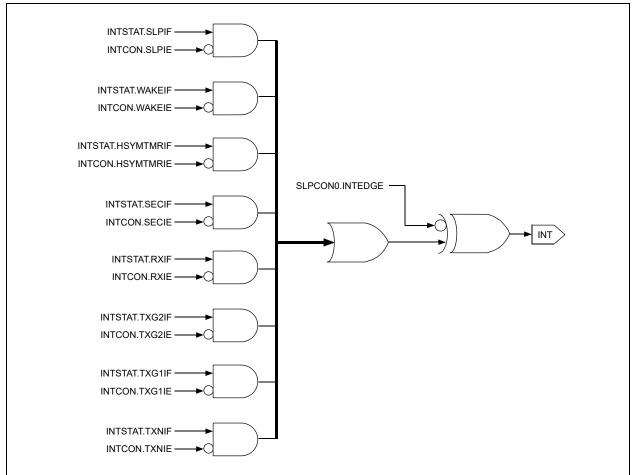

#### 2.10 Interrupt (INT) Pin

L

The Interrupt (INT) pin 16 provides an interrupt signal to the host microcontroller from the MRF24J40. The polarity is configured via the INTEDGE bit in the SLP-CON0 (0x211[1]) register. Interrupts have to be enabled and unmasked before the INT pin is active. Refer to **Section 3.3 "Interrupts"** for a functional description of interrupts.

| Note: | The                                         | INTEDGE | polarity | defaults | to,  |

|-------|---------------------------------------------|---------|----------|----------|------|

|       | 0 = Falling Edge. Ensure that the interrupt |         |          |          | rupt |

|       | polarity matches the interrupt pin polarity |         |          |          |      |

|       | on the host microcontroller.                |         |          |          |      |

| Note: | The INT pin will remain high or low,   |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|

|       | depending on INTEDGE polarity setting, |  |  |  |  |  |

|       | until INSTAT register is read.         |  |  |  |  |  |

#### 2.11 Wake (WAKE) Pin

The Wake (WAKE) pin 15 provides an external wake-up signal to the MRF24J40 from the host microcontroller. It is used in conjunction with the Sleep modes of the MRF24J40. The WAKE pin is disabled by default. Refer to **Section 3.15.2** "**Immediate Sleep and Wake-up Mode**" for a functional description of the Immediate Sleep and Wake-up modes.

#### 2.12 General Purpose Input/Output (GPIO) Pins

Six GPIO pins can be configured individually for control or monitoring purposes. Input or output selection is configured by the TRISGPIO (0x34) register. GPIO data can be read/written to via the GPIO (0x33) register.

The GPIO pins have limited output drive capability. Table 2-5 lists the individual GPIO pin source current limits.

| Pin   | Maximum Current Sourced |  |  |  |

|-------|-------------------------|--|--|--|

| GPIO0 | 4 mA                    |  |  |  |

| GPIO1 | 1 mA                    |  |  |  |

| GPIO2 | 1 mA                    |  |  |  |

| GPIO3 | 1 mA                    |  |  |  |

| GPIO4 | 1 mA                    |  |  |  |

| GPIO5 | 1 mA                    |  |  |  |

| TABLE 2-5: | <b>GPIO SOURCE CURRENT</b> |

|------------|----------------------------|

|            | LIMITS                     |

GPIO0, GPIO1 and GPIO2 can be configured to control external PA, LNA and RF switches by the internal RF state machine. This allows the external PA and LNA to be controlled by the MRF24J40 without any host microcontroller intervention. Refer to **Section 4.2 "External PA/LNA Control"** for control register configuration, timing diagrams and application information.

#### 2.13 Serial Peripheral Interface (SPI) Port Pins

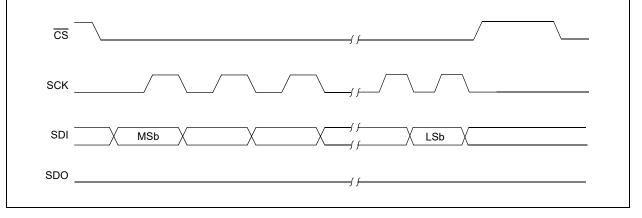

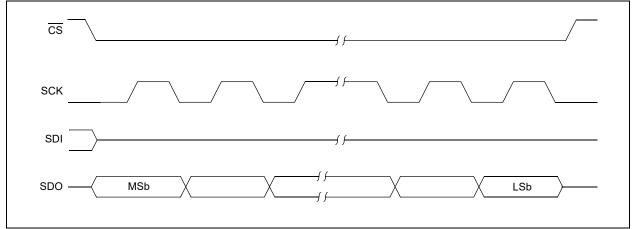

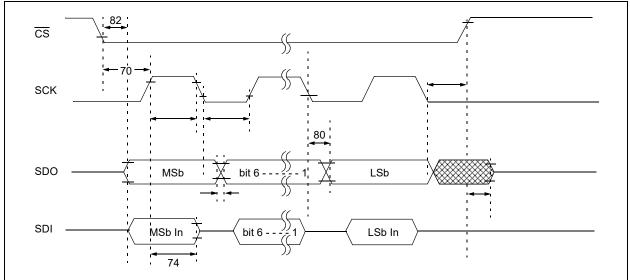

The MRF24J40 communicates with a host microcontroller via a 4-wire SPI port as a slave device. The MRF24J40 supports SPI (mode 0,0) which requires that SCK idles in a low state. The  $\overline{CS}$  pin must be held low while communicating with the MRF24J40. Figure 2-4 shows timing for a write operation. Data is received by the MRF24J40 via the SDI pin and is clocked in on the rising edge of SCK. Figure 2-5 shows timing for a read operation. Data is sent by the MRF24J40 via the SDO pin and is clocked out on the falling edge of SCK. Note: The SDO pin 17 defaults to a low state when CS is high (the MRF24J40 is not selected). If the MRF24J40 is to share a SPI bus, a tri-state buffer should be placed on the SDO signal to provide a high-impedance signal to the SPI bus. See Section 4.4 "MRF24J40 Schematic and Bill of Materials" for an example application circuit.

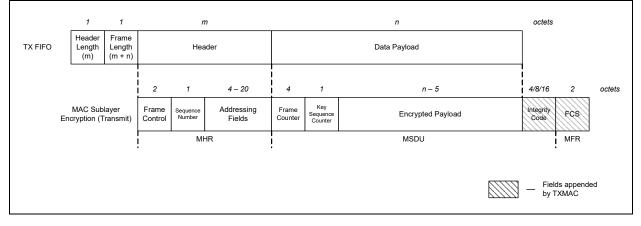

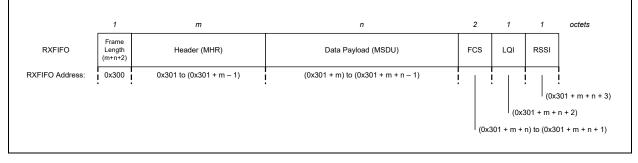

provide control, status and device addressing for MRF24J40 operations. FIFOs serve as temporary

buffers for data transmission, reception and security

keys. Memory is accessed via two addressing

methods: Short and Long.

#### 2.14 Memory Organization

Г

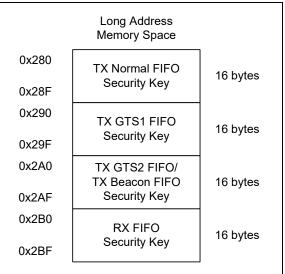

Memory in the MRF24J40 is implemented as static RAM and is accessible via the SPI port. Memory is functionally divided into control registers and data buffers (FIFOs), as shown in Figure 2-6. Control registers

FIGURE 2-6: MEMORY MAP FOR MRF24J40

|              | Short Address<br>Memory Space |          |                                  | Long Address<br>Memory Space  |           |

|--------------|-------------------------------|----------|----------------------------------|-------------------------------|-----------|

| 0x00<br>0x3F | Control Registers             | 64 bytes | 0x000<br>0x07F                   | TX Normal FIFO                | 128 bytes |

|              |                               |          | 0x07F<br>0x080<br>0x0FF          | TX Beacon FIFO                | 128 bytes |

|              |                               |          | 0x100<br>0x17F                   | TX GTS1 FIFO                  | 128 bytes |

|              |                               |          | 0x180<br>0x1FF                   | TX GTS2 FIFO                  | 128 bytes |

|              |                               |          | 0x200<br>0x27F                   | Control Registers             | 128 bytes |

|              |                               |          | 0x280<br>0x2BF<br>0x2C0<br>0x2FF | Security Key FIFO<br>Reserved | 64 bytes  |

|              |                               |          | 0x300                            | RX FIFO                       | 144 bytes |

|              |                               |          | 0x38F                            |                               |           |

© 2021 Microchip Technology Inc.

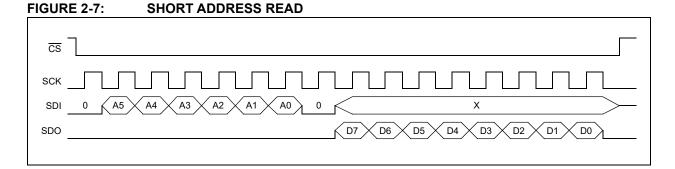

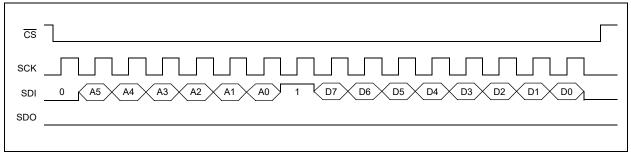

### 2.14.1 SHORT ADDRESS REGISTER INTERFACE

The short address memory space contains control registers with a 6-bit address range of 0x00 to 0x3F. Figure 2-7 shows a short address read and Figure 2-8 shows a short address write. The 8-bit SPI transfer

begins with a '0' to indicate a short address transaction. It is followed by the 6-bit register address, Most Significant bit (MSb) first. The  $8^{th}$  bit indicates if it is a read ('0') or write ('1') transaction.

#### FIGURE 2-8: SHORT ADDRESS WRITE

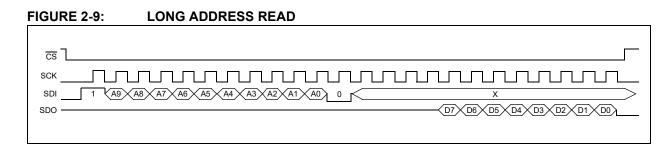

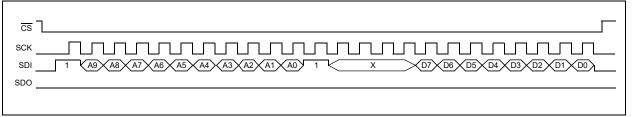

#### 2.14.2 LONG ADDRESS REGISTER INTERFACE

The long address memory space contains control registers and FIFOs with a 10-bit address range of 0x000 to 0x38F. Figure 2-9 shows a long address read and Figure 2-10 shows a long address write. The 12-bit

SPI transfer begins with a '1' to indicate a long address transaction. It is followed by the 10-bit register address, Most Significant bit (MSb) first. The  $12^{th}$  bit indicates if it is a read ('0') or write ('1') transaction.

#### FIGURE 2-10: LONG ADDRESS WRITE

#### 2.15 Control Register Description

Control registers provide control, status and device addressing for MRF24J40 operations. The following figures, tables and register definitions describe the control register operation.

#### 2.15.1 CONTROL REGISTER MAP

#### FIGURE 2-11: SHORT ADDRESS CONTROL REGISTER MAP FOR MRF24J40

| 0x00 | RXMCR    | 0x10 | ORDER    | 0x20 | ESLOTG67  | 0x30 | RXSR     |

|------|----------|------|----------|------|-----------|------|----------|

| 0x01 | PANIDL   | 0x11 | TXMCR    | 0x21 | TXPEND    | 0x31 | INTSTAT  |

| 0x02 | PANIDH   | 0x12 | ACKTMOUT | 0x22 | WAKECON   | 0x32 | INTCON   |

| 0x03 | SADRL    | 0x13 | ESLOTG1  | 0x23 | FRMOFFSET | 0x33 | GPIO     |

| 0x04 | SADRH    | 0x14 | SYMTICKL | 0x24 | TXSTAT    | 0x34 | TRISGPIO |

| 0x05 | EADR0    | 0x15 | SYMTICKH | 0x25 | TXBCON1   | 0x35 | SLPACK   |

| 0x06 | EADR1    | 0x16 | PACON0   | 0x26 | GATECLK   | 0x36 | RFCTL    |

| 0x07 | EADR2    | 0x17 | PACON1   | 0x27 | TXTIME    | 0x37 | SECCR2   |

| 0x08 | EADR3    | 0x18 | PACON2   | 0x28 | HSYMTMRL  | 0x38 | BBREG0   |

| 0x09 | EADR4    | 0x19 | Reserved | 0x29 | HSYMTMRH  | 0x39 | BBREG1   |

| 0x0A | EADR5    | 0x1A | TXBCON0  | 0x2A | SOFTRST   | 0x3A | BBREG2   |

| 0x0B | EADR6    | 0x1B | TXNCON   | 0x2B | Reserved  | 0x3B | BBREG3   |

| 0x0C | EADR7    | 0x1C | TXG1CON  | 0x2C | SECCON0   | 0x3C | BBREG4   |

| 0x0D | RXFLUSH  | 0x1D | TXG2CON  | 0x2D | SECCON1   | 0x3D | Reserved |

| 0x0E | Reserved | 0x1E | ESLOTG23 | 0x2E | TXSTBL    | 0x3E | BBREG6   |

| 0x0F | Reserved | 0x1F | ESLOTG45 | 0x2F | Reserved  | 0x3F | CCAEDTH  |

#### FIGURE 2-12: LONG ADDRESS CONTROL REGISTER MAP FOR MRF24J40

| 0x200 | RFCON0   | 0x210 | RSSI     | 0x220 | SLPCON1   | ox230 | ASSOEADR0     | 0x240 | UPNONCE0  |

|-------|----------|-------|----------|-------|-----------|-------|---------------|-------|-----------|

| 0x201 | RFCON1   | 0x211 | SLPCON0  | 0x221 | Reserved  | 0x231 | ASSOEADR1     | 0x241 | UPNONCE1  |

| 0x202 | RFCON2   | 0x212 | Reserved | 0x222 | WAKETIMEL | 0x232 | ASSOEADR2     | 0x242 | UPNONCE2  |

| 0x203 | RFCON3   | 0x213 | Reserved | 0x223 | WAKETIMEH | 0x233 | ASSOEADR3     | 0x243 | UPNONCE3  |

| 0x204 | Reserved | 0x214 | Reserved | 0x224 | REMCNTL   | 0x234 | ASSOEADR4     | 0x244 | UPNONCE4  |

| 0x205 | RFCON5   | 0x215 | Reserved | 0x225 | REMCNTH   | 0x235 | ASSOEADR5     | 0x245 | UPNONCE5  |

| 0x206 | RFCON6   | 0x216 | Reserved | 0x226 | MAINCNT0  | 0x236 | ASSOEADR6     | 0x246 | UPNONCE6  |

| 0x207 | RFCON7   | 0x217 | Reserved | 0x227 | MAINCNT1  | 0x237 | ASSOEADR7     | 0x247 | UPNONCE7  |

| 0x208 | RFCON8   | 0x218 | Reserved | 0x228 | MAINCNT2  | 0x238 | ASSOSADR0     | 0x248 | UPNONCE8  |

| 0x209 | SLPCAL0  | 0x219 | Reserved | 0x229 | MAINCNT3  | 0x239 | ASSOSADR1     | 0x249 | UPNONCE9  |

| 0x20A | SLPCAL1  | 0x21A | Reserved | 0x22A | Reserved  | 0x23A | Reserved      | 0x24A | UPNONCE10 |

| 0x20B | SLPCAL2  | 0x21B | Reserved | 0x22B | Reserved  | 0x23B | Reserved      | 0x24B | UPNONCE11 |

| 0x20C | Reserved | 0x21C | Reserved | 0x22C | Reserved  | 0x23C | Unimplemented | 0x24C | UPNONCE12 |

| 0x20D | Reserved | 0x21D | Reserved | 0x22D | Reserved  | 0x23D | Unimplemented |       |           |

| 0x20E | Reserved | 0x21E | Reserved | 0x22E | Reserved  | 0x23E | Unimplemented | ]     |           |

| 0x20F | RFSTATE  | 0x21F | Reserved | 0x22F | TESTMODE  | 0x23F | Unimplemented |       |           |

#### 2.15.2 CONTROL REGISTER SUMMARY

| Addr. | File Name | Bit 7      | Bit 6      | Bit 5     | Bit 4               | Bit 3              | Bit 2      | Bit 1     | Bit 0    | Value on<br>POR | De<br>P |

|-------|-----------|------------|------------|-----------|---------------------|--------------------|------------|-----------|----------|-----------------|---------|

| 0x00  | RXMCR     | r          | r          | NOACKRSP  | r                   | PANCOORD           | COORD      | ERRPKT    | PROMI    | 0000            |         |

| 0x01  | PANIDL    |            |            |           | PAN ID Low Byt      | te (PANIDL[7:0])   |            |           |          | 0000            |         |

| 0x02  | PANIDH    |            |            |           | PAN ID High Byte    | e (PANIDH[15:8])   |            |           |          | 0000            |         |

| 0x03  | SADRL     |            |            |           | Short Address Low   | Byte (SADRL[7:0]   | )          |           |          | 0000            |         |

| 0x04  | SADRH     |            |            | S         | Short Address High  | Byte (SADRH[15:8   | ])         |           |          | 0000            |         |

| 0x05  | EADR0     |            |            | 64        | -Bit Extended Addr  | ess bits (EADR0[7: | 0])        |           |          | 0000            | Ī       |

| 0x06  | EADR1     |            |            | 64-       | -Bit Extended Addre | ess bits (EADR1[15 | :8])       |           |          | 0000            |         |

| 0x07  | EADR2     |            |            | 64-1      | Bit Extended Addre  | ss bits (EADR2[23: | 16])       |           |          | 0000            |         |

| 0x08  | EADR3     |            |            | 64-1      | Bit Extended Addre  | ss bits (EADR3[31: | 24])       |           |          | 0000            |         |

| 0x09  | EADR4     |            |            | 64-1      | Bit Extended Addre  | ss bits (EADR4[39: | 32])       |           |          | 0000            | l       |

| 0x0A  | EADR5     |            |            | 64-1      | Bit Extended Addre  | ss bits (EADR5[47: | 40])       |           |          | 0000            |         |

| 0x0B  | EADR6     |            |            | 64-1      | Bit Extended Addre  | ss bits (EADR6[55: | 48])       |           |          | 0000            |         |

| 0x0C  | EADR7     |            |            | 64-1      | Bit Extended Addre  | ss bits (EADR7[63: | 56])       |           |          | 0000            |         |

| 0x0D  | RXFLUSH   | r          | WAKEPOL    | WAKEPAD   | r                   | CMDONLY            | DATAONLY   | BCNONLY   | RXFLUSH  | 0000            |         |

| 0x0E  | Reserved  | r          | r          | r         | r                   | r                  | r          | r         | r        | 0000            |         |

| 0x0F  | Reserved  | r          | r          | r         | r                   | r                  | r          | r         | r        | 0000            |         |

| 0x10  | ORDER     | BO3        | BO2        | BO1       | BO0                 | SO3                | SO2        | SO1       | SO0      | 1111<br>1111    |         |

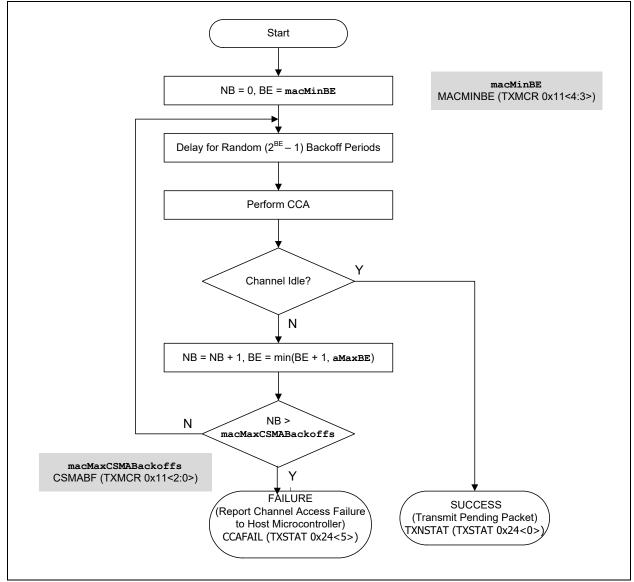

| 0x11  | TXMCR     | NOCSMA     | BATLIFEXT  | SLOTTED   | MACMINBE1           | MACMINBE0          | CSMABF2    | CSMABF1   | CSMABF0  | 0001<br>1100    |         |

| 0x12  | ACKTMOUT  | DRPACK     | MAWD6      | MAWD5     | MAWD4               | MAWD3              | MAWD2      | MAWD1     | MAWD0    | 0011<br>1001    |         |

| 0x13  | ESLOTG1   | GTS1-3     | GTS1-2     | GTS1-1    | GTS1-0              | CAP3               | CAP2       | CAP1      | CAP0     | 0000            |         |

| 0x14  | SYMTICKL  | TICKP7     | TICKP6     | TICKP5    | TICKP4              | TICKP3             | TICKP2     | TICKP1    | TICKP0   | 0100<br>0000    |         |

| 0x15  | SYMTICKH  | TXONT6     | TXONT5     | TXONT4    | TXONT3              | TXONT2             | TXONT1     | TXONT0    | TICKP8   | 0101<br>0001    |         |

| 0x16  | PACON0    | PAONT7     | PAONT6     | PAONT5    | PAONT4              | PAONT3             | PAONT2     | PAONT1    | PAONT0   | 0010<br>1001    |         |

| 0x17  | PACON1    | r          | r          | r         | PAONTS3             | PAONTS2            | PAONTS1    | PAONTS0   | PAONT8   | 0000<br>0010    |         |

| 0x18  | PACON2    | FIFOEN     | r          | TXONTS3   | TXONTS2             | TXONTS1            | TXONTS0    | TXONT8    | TXONT7   | 1000<br>1000    |         |

| 0x19  | Reserved  | r          | r          | r         | r                   | r                  | r          | r         | r        | 0000            |         |

| 0x1A  | TXBCON0   | r          | r          | r         | r                   | r                  | r          | TXBSECEN  | TXBTRIG  | 0000            |         |

| 0x1B  | TXNCON    | r          | r          | r         | FPSTAT              | INDIRECT           | TXNACKREQ  | TXNSECEN  | TXNTRIG  | 0000            |         |

| 0x1C  | TXG1CON   | TXG1RETRY1 | TXG1RETRY0 | TXG1SLOT2 | TXG1SLOT1           | TXG1SLOT0          | TXG1ACKREQ | TXG1SECEN | TXG1TRIG | 0000            |         |

| 0x1D  | TXG2CON   | TXG2RETRY1 | TXG2RETRY0 | TXG2SLOT2 | TXG2SLOT1           | TXG2SLOT0          | TXG2ACKREQ | TXG2SECEN | TXG2TRIG | 0000            |         |

| Addr. | File Name | Bit 7     | Bit 6      | Bit 5      | Bit 4      | Bit 3     | Bit 2      | Bit 1      | Bit 0      | Value on<br>POR | Details<br>on<br>Page: |

|-------|-----------|-----------|------------|------------|------------|-----------|------------|------------|------------|-----------------|------------------------|

| 0x1E  | ESLOTG23  | GTS3-3    | GTS3-2     | GTS3-1     | GTS3-0     | GTS2-3    | GTS2-2     | GTS2-1     | GTS2-0     | 0000            | 39                     |

| 0x1F  | ESLOTG45  | GTS5-3    | GTS5-2     | GTS5-1     | GTS5-0     | GTS4-3    | GTS4-2     | GTS4-1     | GTS4-0     | 0000            | 39                     |

| 0x20  | ESLOTG67  | r         | r          | r          | r          | GTS6-3    | GTS6-2     | GTS6-1     | GTS6-0     | 0000<br>0000    | 39                     |

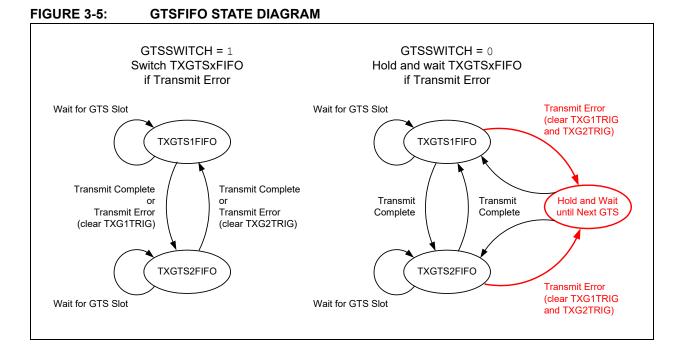

| 0x21  | TXPEND    | MLIFS5    | MLIFS4     | MLIFS3     | MLIFS2     | MLIFS1    | MLIFS0     | GTSSWITCH  | FPACK      | 1000<br>0100    | 40                     |

| 0x22  | WAKECON   | IMMWAKE   | REGWAKE    | INTL       | INTL       | INTL      | INTL       | INTL       | INTL       | 0000<br>0000    | 41                     |

| 0x23  | FRMOFFSET | OFFSET7   | OFFSET6    | OFFSET5    | OFFSET4    | OFFSET3   | OFFSET2    | OFFSET1    | OFFSET0    | 0000<br>0000    | 42                     |

| 0x24  | TXSTAT    | TXNRETRY1 | TXNRETRY0  | CCAFAIL    | TXG2FNT    | TXG1FNT   | TXG2STAT   | TXG1STAT   | TXNSTAT    | 0000<br>0000    | 43                     |

| 0x25  | TXBCON1   | TXBMSK    | WU/BCN     | RSSINUM1   | RSSINUM0   | r         | r          | r          | r          | 0011<br>0000    | 44                     |

| 0x26  | GATECLK   | r         | r          | r          | r          | GTSON     | r          | r          | r          | 0000            | 45                     |

| 0x27  | TXTIME    | TURNTIME3 | TURNTIME2  | TURNTIME1  | TURNTIME0  | r         | r          | r          | r          | 0100<br>1000    | 46                     |

| 0x28  | HSYMTMRL  | HSYMTMR7  | HSYMTMR6   | HSYMTMR5   | HSYMTMR4   | HSYMTMR3  | HSYMTMR2   | HSYMTMR1   | HSYMTMR0   | 0000            | 47                     |

| 0x29  | HSYMTMRH  | HSYMTMR15 | HSYMTMR14  | HSYMTMR13  | HSYMTMR12  | HSYMTMR11 | HSYMTMR10  | HSYMTMR09  | HSYMTMR08  | 0000<br>0000    | 47                     |

| 0x2A  | SOFTRST   | r         | r          | r          | r          | r         | RSTPWR     | RSTBB      | RSTMAC     | 0000            | 48                     |

| 0x2B  | Reserved  | r         | r          | r          | r          | r         | r          | r          | r          | 0000            | —                      |

| 0x2C  | SECCON0   | SECIGNORE | SECSTART   | RXCIPHER2  | RXCIPHER1  | RXCIPHER0 | TXNCIPHER2 | TXNCIPHER1 | TXNCIPHER0 | 0000            | 49                     |

| 0x2D  | SECCON1   | r         | TXBCIPHER2 | TXBCIPHER1 | TXBCIPHER0 | r         | r          | DISDEC     | DISENC     | 0000            | 50                     |

| 0x2E  | TXSTBL    | RFSTBL3   | RFSTBL2    | RFSTBL1    | RFSTBL0    | MSIFS3    | MSIFS2     | MSIFS1     | MSIFS0     | 0111<br>0101    | 51                     |

| 0x2F  | Reserved  | r         | r          | r          | r          | r         | r          | r          | r          | 0000            | -                      |

Legend: r = reserved

| Addr. | File Name | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>POR | Details<br>on<br>Page: |

|-------|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-----------------|------------------------|

| 0x30  | RXSR      | r           | UPSECERR    | BATIND      | r           | r           | SECDECERR   | r           | r           | 0000            | 52                     |

| 0x31  | INTSTAT   | SLPIF       | WAKEIF      | HSYMTMRIF   | SECIF       | RXIF        | TXG2IF      | TXG1IF      | TXNIF       | 0000            | 53                     |

| 0x32  | INTCON    | SLPIE       | WAKEIE      | HSYMTMRIE   | SECIE       | RXIE        | TXG2IE      | TXG1IE      | TXNIE       | 1111<br>1111    | 54                     |

| 0x33  | GPIO      | r           | r           | GPIO5       | GPIO4       | GPIO3       | GPIO2       | GPIO1       | GPIO0       | 0000            | 55                     |

| 0x34  | TRISGPIO  | r           | r           | TRISGP5     | TRISGP4     | TRISGP3     | TRISGP2     | TRISGP1     | TRISGP0     | 0000            | 55                     |

| 0x35  | SLPACK    | SLPACK      | WAKECNT6    | WAKECNT5    | WAKECNT4    | WAKECNT3    | WAKECNT2    | WAKECNT1    | WAKECNT0    | 0000<br>0000    | 56                     |

| 0x36  | RFCTL     | r           | r           | r           | WAKECNT8    | WAKECNT7    | RFRST       | RFTXMODE    | RFRXMODE    | 0000            | 57                     |

| 0x37  | SECCR2    | UPDEC       | UPENC       | TXG2CIPHER2 | TXG2CIPHER1 | TXG2CIPHER0 | TXG1CIPHER2 | TXG1CIPHER1 | TXG1CIPHER0 | 0000            | 58                     |

| 0x38  | BBREG0    | r           | r           | r           | r           | r           | r           | r           | TURBO       | 0000<br>0000    | 59                     |

| 0x39  | BBREG1    | r           | r           | r           | r           | r           | RXDECINV    | r           | r           | 0000<br>0000    | 59                     |

| 0x3A  | BBREG2    | CCAMODE1    | CCAMODE0    | CCACSTH3    | CCACSTH2    | CCACSTH1    | CCACSTH0    | r           | r           | 0100<br>1000    | 60                     |

| 0x3B  | BBREG3    | PREVALIDTH3 | PREVALIDTH2 | PREVALIDTH1 | PREVALIDTH0 | PREDETTH2   | PREDETTH1   | PREDETTH0   | r           | 1101<br>1000    | 60                     |

| 0x3C  | BBREG4    | CSTH2       | CSTH1       | CSTH0       | PRECNT2     | PRECNT1     | PRECNT0     | r           | r           | 1001<br>1100    | 61                     |

| 0x3D  | Reserved  | r           | r           | r           | r           | r           | r           | r           | r           | 0000            | -                      |

| 0x3E  | BBREG6    | RSSIMODE1   | RSSIMODE2   | r           | r           | r           | r           | r           | RSSIRDY     | 0000<br>0001    | 61                     |

| 0x3F  | CCAEDTH   | CCAEDTH7    | CCAEDTH6    | CCAEDTH5    | CCAEDTH4    | CCAEDTH3    | CCAEDTH2    | CCAEDTH1    | CCAEDTH0    | 0000            | 62                     |

Legend: r = reserved

#### TABLE 2-7: LONG ADDRESS CONTROL REGISTER SUMMARY FOR MRF24J40

| Addr. | File Name | Bit 7      | Bit 6      | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1       | Bit 0       | Value on<br>POR | Details<br>on<br>Page: |

|-------|-----------|------------|------------|----------|----------|----------|----------|-------------|-------------|-----------------|------------------------|

| 0x200 | RFCON0    | CHANNEL3   | CHANNEL2   | CHANNEL1 | CHANNEL0 | RFOPT3   | RFOPT2   | RFOPT1      | RFOPT0      | 0000 0000       | 63                     |

| 0x201 | RFCON1    | VCOOPT7    | VCOOPT6    | VCOOPT5  | VCOOPT4  | VCOOPT3  | VCOOPT2  | VCOOPT1     | VCOOPT0     | 0000 0000       | 63                     |

| 0x202 | RFCON2    | PLLEN      | r          | r        | r        | r        | r        | r           | r           | 0000 0000       | 64                     |

| 0x203 | RFCON3    | TXPWRL1    | TXPWRL0    | TXPWRS2  | TXPWRS1  | TXPWRS0  | r        | r           | r           | 0000 0000       | 64                     |

| 0x204 | Reserved  | r          | r          | r        | r        | r        | r        | r           | r           | 0000 0000       | -                      |

| 0x205 | RFCON5    | BATTH3     | BATTH2     | BATTH1   | BATTH0   | r        | r        | r           | r           | 0000 0000       | 65                     |

| 0x206 | RFCON6    | TXFIL      | r          | r        | 20MRECVR | BATEN    | r        | r           | r           | 0000 0000       | 65                     |

| 0x207 | RFCON7    | SLPCLKSEL1 | SLPCLKSEL0 | r        | r        | r        | r        | CLKOUTMODE1 | CLKOUTMODE0 | 0000 0000       | 66                     |

| 0x208 | RFCON8    | r          | r          | r        | RFVCO    | r        | r        | r           | r           | 0000 0000       | 66                     |

| 0x209 | SLPCAL0   | SLPCAL7    | SLPCAL6    | SLPCAL5  | SLPCAL4  | SLPCAL3  | SLPCAL2  | SLPCAL1     | SLPCAL0     | 0000 0000       | 67                     |

| 0x20A | SLPCAL1   | SLPCAL15   | SLPCAL14   | SLPCAL13 | SLPCAL12 | SLPCAL11 | SLPCAL10 | SLPCAL9     | SLPCAL8     | 0000 0000       | 67                     |

| 0x20B | SLPCAL2   | SLPCALRDY  | r          | r        | SLPCALEN | SLPCAL19 | SLPCAL18 | SLPCAL17    | SLPCAL16    | 0000 0000       | 68                     |

| 0x20C | Reserved  | r          | r          | r        | r        | r        | r        | r           | r           | 0000 0000       | -                      |

| 0x20D | Reserved  | r          | r          | r        | r        | r        | r        | r           | r           | 0000 0000       | -                      |

| 0x20E | Reserved  | r          | r          | r        | r        | r        | r        | r           | r           | 0000 0000       | -                      |

| 0x20F | RFSTATE   | RFSTATE2   | RFSTATE1   | RFSTATE0 | r        | r        | r        | r           | r           | 0000 0000       | 69                     |

| 0x210 | RSSI      | RSSI7      | RSSI6      | RSSI5    | RSSI4    | RSSI3    | RSSI2    | RSSI1       | RSSI0       | 0000 0000       | 69                     |

| 0x211 | SLPCON0   | r          | r          | r        | r        | r        | r        | INTEDGE     | SLPCLKEN    | 0000 0000       | 70                     |

| 0x212 | Reserved  | r          | r          | r        | r        | r        | r        | r           | r           | 0000 0000       | -                      |

Legend: r = reserved

## **MRF24J40**

| Addr.                            | File Name                                              | Bit 7     | Bit 6                    | Bit 5                  | Bit 4                   | Bit 3                  | Bit 2                 | Bit 1      | Bit 0      | Value on<br>POR | Deta<br>or<br>Pag |

|----------------------------------|--------------------------------------------------------|-----------|--------------------------|------------------------|-------------------------|------------------------|-----------------------|------------|------------|-----------------|-------------------|

| 0x213                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       |                   |

| )x214                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       |                   |

| Dx215                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x216                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       |                   |

| 0x217                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x218                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x219                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x21A                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x21B                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x21C                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x21D                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x21E                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x21F                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | _                 |

| 0x220                            | SLPCON1                                                | r         | r                        | CLKOUTEN               | SLPCLKDIV4              | SLPCLKDIV3             | SLPCLKDIV2            | SLPCLKDIV1 | SLPCLKDIV0 | 0000 0000       | 7                 |

| 0x220                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       |                   |

| 0x222                            | WAKETIMEL                                              | WAKETIME7 | WAKETIME6                | WAKETIME5              | WAKETIME4               | WAKETIME3              | WAKETIME2             | WAKETIME1  | WAKETIME0  | 0000 1010       | 7                 |

| 0x223                            |                                                        | r         | r                        | r                      | r                       | r                      | WAKETIME10            | WAKETIME9  | WAKETIME8  | 0000 0000       | 7                 |

| 0x224                            | REMCNTL                                                | REMCNT7   | REMCNT6                  | REMCNT5                | REMCNT4                 | REMCNT3                | REMCNT2               | REMCNT1    | REMCNT0    | 0000 0000       | . 7.              |

| 0x225                            |                                                        | REMCNT15  | REMCNT14                 | REMCNT13               | REMCNT12                | REMCNT11               | REMCNT10              | REMCNT9    | REMCNT8    | 0000 0000       | 7                 |

| 0x226                            | MAINCNT0                                               | MAINCNT7  | MAINCNT6                 | MAINCNT5               | MAINCNT4                | MAINCNT3               | MAINCNT2              | MAINCNT1   | MAINCNTO   | 0000 0000       | 7                 |

| 0x220                            | MAINCNT1                                               | MAINCNT15 | MAINCNT14                | MAINCNT13              | MAINCNT12               | MAINCNT11              | MAINCNT2<br>MAINCNT10 | MAINCNT9   | MAINCNT8   | 0000 0000       | 7                 |

|                                  | MAINCNT2                                               |           | MAINCINT 14<br>MAINCNT22 | MAINCNT13<br>MAINCNT21 | MAINCNT12<br>MAINCNT20  | MAINCNT11<br>MAINCNT19 |                       |            |            |                 |                   |

| 0x228                            | -                                                      | MAINCNT23 |                          | -                      |                         |                        | MAINCNT18             | MAINCNT17  | MAINCNT16  | 0000 0000       | 7.                |

| 0x229                            | MAINCNT3                                               | STARTCNT  | r                        | r                      | r                       | r                      | r                     | MAINCNT25  | MAINCNT24  | 0000 0000       | 7                 |

| 0x22A                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | -                 |

| 0x22B                            |                                                        | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       |                   |

| 0x22C                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | -                 |

| 0x22D                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | -                 |

| 0x22E                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | -                 |

| 0x22F                            | TESTMODE                                               | r         | r                        | r                      | RSSIWAIT1               | RSSIWAIT0              | TESTMODE2             | TESTMODE1  | TESTMODE0  | 0000 0000       | 7                 |

| 0x230                            | ASSOEADR0                                              |           |                          |                        |                         | ADR0[7:0]              |                       |            |            | 0000 0000       | 7                 |

| 0x231                            | ASSOEADR1                                              |           |                          |                        |                         | ADR1[15:8]             |                       |            |            | 0000 0000       | 7                 |

| 0x232                            | ASSOEADR2                                              |           |                          |                        |                         | DR2[23:16]             |                       |            |            | 0000 0000       | 7                 |

| 0x233                            | ASSOEADR3                                              |           |                          |                        |                         | DR3[31:24]             |                       |            |            | 0000 0000       | 7                 |

| 0x234                            | ASSOEADR4                                              |           |                          |                        |                         | DR4[39:32]             |                       |            |            | 0000 0000       | 7                 |

| 0x235                            | ASSOEADR5                                              |           |                          |                        |                         | DR5[47:40]             |                       |            |            | 0000 0000       | 7                 |

|                                  | ASSOEADR6                                              |           |                          |                        |                         | DR6[55:48]             |                       |            |            | 0000 0000       | 79                |

| 0x237                            | ASSOEADR7                                              |           |                          |                        |                         | DR7[63:56]             |                       |            |            | 0000 0000       | 7                 |

| 0x238                            | ASSOSADR0                                              |           |                          |                        |                         | ADR0[7:0]              |                       |            |            | 0000 0000       | 8                 |

| 0x239                            |                                                        |           |                          |                        | ASSOSA                  | ADR1[15:8]             |                       |            |            | 0000 0000       | 8                 |

| 0x23A                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       |                   |

| 0x23B                            | Reserved                                               | r         | r                        | r                      | r                       | r                      | r                     | r          | r          | 0000 0000       | -                 |

| 0x23C                            | mented                                                 | _         | -                        | -                      | -                       | -                      | -                     | -          | -          |                 | -                 |

| )x23D                            | mented                                                 | -         | -                        | _                      | -                       | -                      | -                     | -          | _          |                 | -                 |

| ∿າວ⊳⊏                            |                                                        |           | _                        |                        |                         |                        |                       | _          |            |                 |                   |

|                                  | mented                                                 | _         |                          |                        |                         |                        |                       |            | _          |                 |                   |

| 0x23F                            | Unimple-<br>mented                                     | -         | _                        |                        |                         |                        |                       |            |            |                 |                   |

| 0x23F<br>0x240                   | Unimple-<br>mented<br>UPNONCE0                         | -         | _                        |                        |                         | NCE[7:0]               |                       |            |            | 0000 0000       | -                 |

| 0x23E<br>0x23F<br>0x240<br>0x241 | Unimple-<br>mented<br>UPNONCE0<br>UPNONCE1             | -         | _                        |                        | UPNON                   | VCE[15:8]              |                       |            |            | 0000 0000       | 8                 |

| 0x23F<br>0x240<br>0x241<br>0x242 | Unimple-<br>mented<br>UPNONCE0<br>UPNONCE1<br>UPNONCE2 | _         | _                        |                        | UPNON                   | NCE[15:8]<br>CE[23:16] |                       |            |            | 0000 0000       | 8                 |

| 0x23F<br>0x240<br>0x241          | Unimple-<br>mented<br>UPNONCE0<br>UPNONCE1<br>UPNONCE2 | _         | _                        |                        | UPNON<br>UPNON<br>UPNON | VCE[15:8]              |                       |            |            | 0000 0000       | 8                 |

Legend: r = reserved

1

| TAB   | BLE 2-7:  | LONG  | G ADDRES | SS CONTR | ROL REGIS |            | IMARY FO | OR MRF24 | J40 (CO | NTINUE          | D)                   |

|-------|-----------|-------|----------|----------|-----------|------------|----------|----------|---------|-----------------|----------------------|

| Addr. | File Name | Bit 7 | Bit 6    | Bit 5    | Bit 4     | Bit 3      | Bit 2    | Bit 1    | Bit 0   | Value on<br>POR | Detail<br>on<br>Page |

| 0x246 | UPNONCE6  |       |          |          | UPNON     | CE[55:48]  |          |          |         | 0000 0000       | 84                   |

| 0x247 | UPNONCE7  |       |          |          | UPNON     | CE[63:56]  |          |          |         | 0000 0000       | 84                   |

| 0x248 | UPNONCE8  |       |          |          | UPNON     | CE[71:64]  |          |          |         | 0000 0000       | 85                   |

| 0x249 | UPNONCE9  |       |          |          | UPNON     | CE[79:72]  |          |          |         | 0000 0000       | 85                   |

| 0x24A | UPNONCE10 |       |          |          | UPNON     | CE[87:80]  |          |          |         | 0000 0000       | 86                   |

| 0x24B | UPNONCE11 |       |          |          | UPNON     | CE[95:88]  |          |          |         | 0000 0000       | 86                   |

| 0x24C | UPNONCE12 |       |          |          | UPNONO    | CE[103:96] |          |          |         | 0000 0000       | 87                   |

Legend: r = reserved

#### 2.15.3 SHORT ADDRESS CONTROL REGISTERS DETAIL

#### REGISTER 2-1: RXMCR: RECEIVE MAC CONTROL REGISTER (ADDRESS: 0x00)

| R/W-0           | R/W-0         | R/W-0                           | R/W-0         | R/W-0                | R/W-0            | R/W-0              | R/W-0         |

|-----------------|---------------|---------------------------------|---------------|----------------------|------------------|--------------------|---------------|

| r               | r             | NOACKRSP                        | r             | PANCOORD             | COORD            | ERRPKT             | PROMI         |

| bit 7           | ·             |                                 |               |                      |                  |                    | bit 0         |

|                 |               |                                 |               |                      |                  |                    |               |

| Legend:         |               | r = reserved                    |               |                      |                  |                    |               |

| R = Readable    | bit           | W = Writable b                  | oit           | U = Unimplem         | ented bit, rea   | d as '0'           |               |

| -n = Value at F | POR           | '1' = Bit is set                |               | '0' = Bit is clea    | ired             | x = Bit is unkr    | iown          |

|                 |               |                                 |               |                      |                  |                    |               |

| bit 7-6         | Reserved: M   |                                 |               |                      |                  |                    |               |

| bit 5           | NOACKRSP      | : Automatic Ackr                | nowledgeme    | ent Response bit     |                  |                    |               |

|                 |               | automatic Ackn                  |               |                      |                  |                    |               |

|                 |               | automatic Ackno<br>d (default). | owledgemer    | nt response. Ackr    | nowledgemen      | its are returned v | when they are |

| bit 4           | Reserved: M   | ( )                             |               |                      |                  |                    |               |

| bit 3           | PANCOORD      | : PAN Coordinat                 | or bit        |                      |                  |                    |               |

|                 | 1 = Set devid | ce as PAN coord                 | linator       |                      |                  |                    |               |

|                 | 0 = Device is | s not set as PAN                | coordinator   | · (default)          |                  |                    |               |

| bit 2           | COORD: Coo    | ordinator bit                   |               |                      |                  |                    |               |

|                 |               | ce as coordinato                | -             |                      |                  |                    |               |

|                 | 0 = Device is | s not set as coor               | dinator (defa | ault)                |                  |                    |               |

| bit 1           | ERRPKT: Pa    | cket Error Mode                 | bit           |                      |                  |                    |               |

|                 |               | Il packets includ               | •             |                      |                  |                    |               |

|                 | •             | nly packets with                | 0             | (default)            |                  |                    |               |

| bit 0           |               | niscuous Mode I                 |               |                      |                  |                    |               |

|                 |               | all packet types                |               | CRC<br>address misma | tch illegal fra  | me type dDAN/      |               |

|                 |               | dress mismatch                  |               |                      | ion, illegal Ifa | ine type, uPAN/    |               |

|                 |               |                                 |               |                      |                  |                    |               |

| R/W-0                            | R/W-0 | R/W-0          | R/W-0       | R/W-0             | R/W-0         | R/W-0    | R/W-0 |

|----------------------------------|-------|----------------|-------------|-------------------|---------------|----------|-------|

|                                  |       | PA             | AN ID Low B | yte (PANIDL[7:0]) |               |          |       |

| bit 7                            |       |                |             |                   |               |          | bit   |

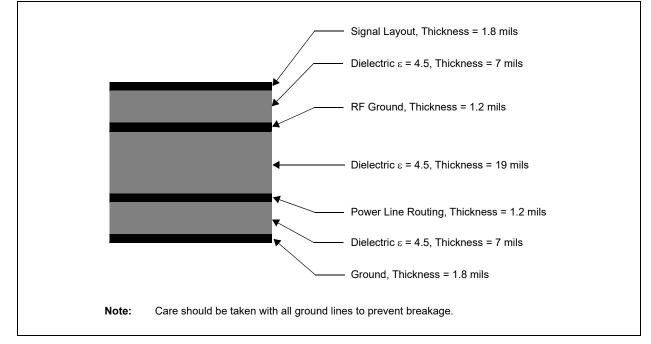

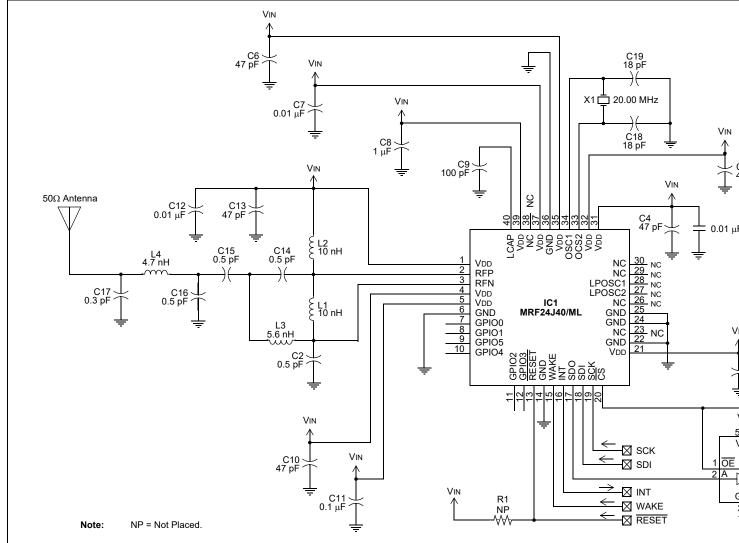

|                                  |       |                |             |                   |               |          |       |