# **MTCH112**

# **Dual-Channel Proximity/Touch Controller**

### Features:

- Capacitive Proximity Detection System:

- High Signal to Noise Ratio (SNR)

- Adjustable sensitivity

- Noise Rejection Filters

- Scanning method actively optimized to attenuate strongest noise frequencies

- Automatic calibration with optional user presets

- Dynamic threshold management adjusts sensitivity of sensor based on the level of environmental noise

- Constant press calibration tracks the expected offset when the sensor is pressed and adjusts the threshold to automatically achieve the best press/release behavior

- User-defined "minimum shift" values specify the lowest amount of signal change to activate a state transition. Automatic thresholds never decrease below these settings.

- Automatic Environmental Compensation

- Stuck release mechanism

- No Required External Components

- Low-Power mode: Highly Configurable Low-Power mode

- 1 ms to 4s Sleep interval between sensor samples

- · Response Time as Low as 10 ms

- Hardware Error Detection notifies if either sensor is shorted to VDD, VSS or the other sensor

- Operating Voltage Range:

- 1.8V to 3.3V

- Operating Temperature:

- 40°C to +85°C

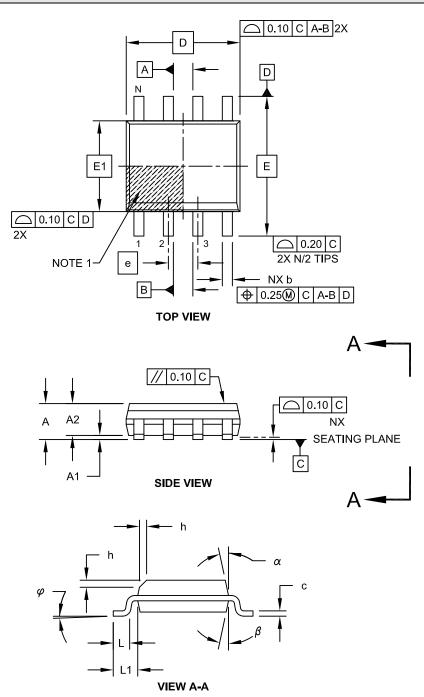

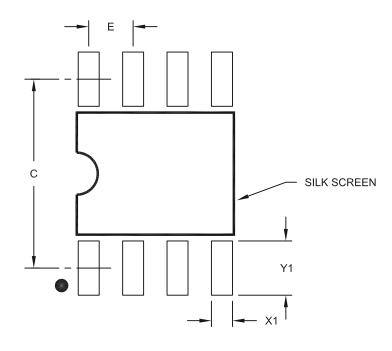

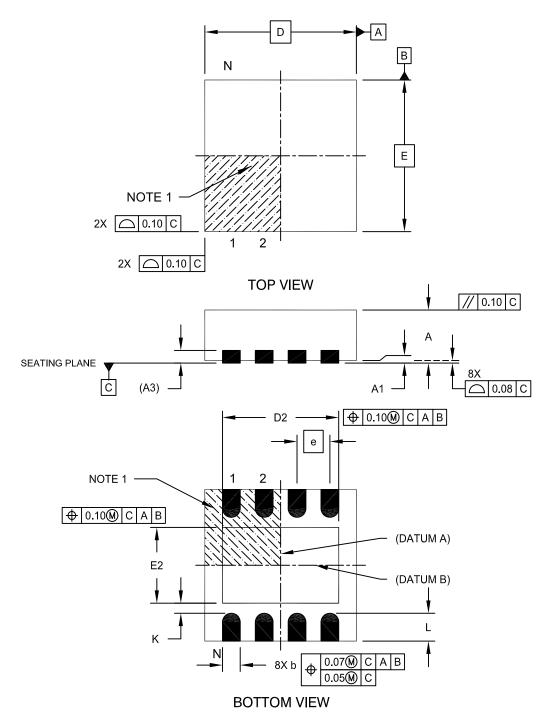

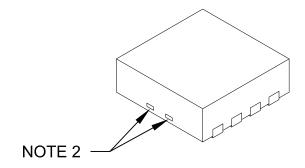

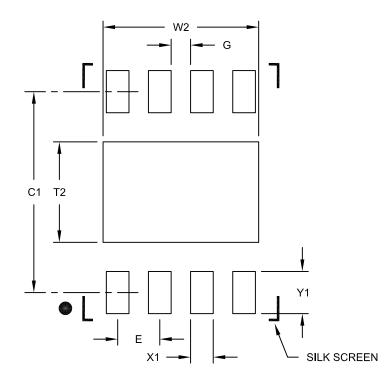

### Package Type

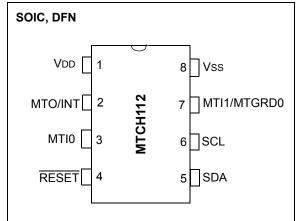

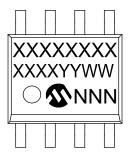

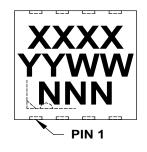

The device is available in 8-lead SOIC and DFN packaging (see Figure 1).

| FIGURE 1: | 8-PIN DIAGRAM |

|-----------|---------------|

|           | FOR MTCH112   |

# TABLE 1:8-PIN SOIC/DFN PINOUT<br/>DESCRIPTION

| I/O         | 8-Pin<br>SOIC/DFN | Description                                                  |

|-------------|-------------------|--------------------------------------------------------------|

| Vdd         | 1                 | Power Supply Input                                           |

| MTO/INT     | 2                 | Detect Output (Active-Low)<br>Notification Interrupt Pin     |

| MTI0        | 3                 | Proximity/Touch Sensor Input                                 |

| RESET       | 4                 | Device Reset (Active-Low)                                    |

| SDA         | 5                 | l <sup>2</sup> C™ Data                                       |

| SCL         | 6                 | I <sup>2</sup> C™ Clock                                      |

| MTI1/MTGRD0 | 7                 | Proximity/Touch Sensor Input<br>Active Guard Shield for MTI0 |

| Vss         | 8                 | Ground Reference                                             |

### **Table of Contents**

| 1.0    | Device Overview                                | . 3 |

|--------|------------------------------------------------|-----|

| 2.0    | I <sup>2</sup> C <sup>™</sup> Serial Interface | . 6 |

| 3.0    | Configuration Registers                        | 13  |

| 4.0    | Electrical Characteristics                     | 25  |

|        | Packaging Information                          |     |

|        |                                                |     |

| The Mi | crochip Web Site                               | 43  |

|        | ner Change Notification Service                |     |

| Custon | ner Support                                    | 43  |

| Reade  | Response                                       | 44  |

|        | t Identification System                        |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

The Microchip mTouch<sup>™</sup> sensing MTCH112 Dual-Channel Proximity/Touch Controller provides an easy way to add proximity and/or touch sensor detection to any application. The device implements either two capacitive sensors or one sensor and one active guard driver. The optional device configuration through I<sup>2</sup>C<sup>™</sup> allows presets to be loaded in a production environment. Automatic calibration routines are used by default to choose the best options, so user configuration is not required.

The MTCH112 uses a sophisticated optimization algorithm to actively eliminate noise from the signal. While the noise level is being measured, the requirements for a proximity or touch detection are updated to reflect the degree of uncertainty in the readings. When a press is detected for the first time, the threshold is automatically calibrated to choose a smart threshold for the 'release' and next press. This creates a system that dynamically optimizes the signalto-noise ratio for its environment.

### 1.1 Automatic Calibration

It measures the amount of capacitance on each sensor pin and chooses the best of three possible waveforms to capture a capacitive measurement.

It analyzes the two final settling voltages of the MTI0 pin to more closely match the waveform on the MTGRD0 pin.

The settling time for the waveform is calibrated to maximize sensitivity while minimizing the delay. This provides the best trade-off between signal and noise reduction.

Calibration results are stored in the on-board EEPROM for faster recovery time on next power-up. These memory locations are accessible for read/write through the  $I^2C$  communications to bypass the automatic calibration, if required.

### 1.2 Communications

• I<sup>2</sup>C, Slave mode

### 1.3 Touch Configurations

- MTI0 is a dedicated capacitive sensor input

- MTI1/MTGRD0 can either be another capacitive sensor or a guard driver for MTI0

### 1.4 Signal Resolution

• 13 bits

### 1.5 Pin Description

### 1.5.1 MTI0/MTI1

Connect the sensor to this input. An additional resistor of at least 4.7 k $\Omega$  is recommended for best noise immunity. Sensors up to 40 pF in capacitance are supported. Sensors work best when the base capacitance is minimized. This will maximize the percentage change in capacitance when a finger is added to the circuit.

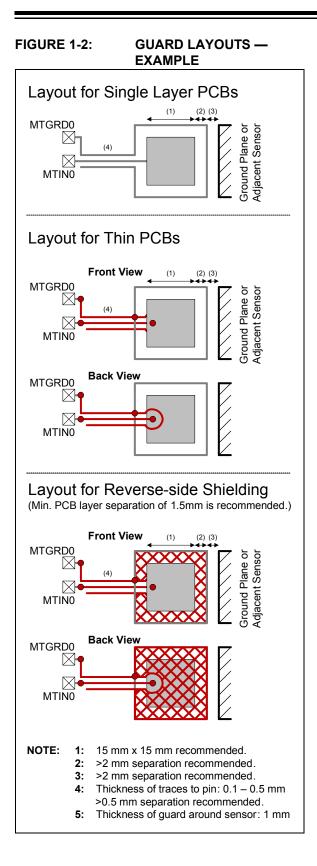

### 1.5.2 MTGRD0

When not scanning the pin for capacitance changes (MTI1 functionality), the pin will be driven in phase with MTI0 to minimize the voltage differential between the two pins. If the MTGRD0 pin's trace surrounds the MTI0 pin's trace, the waveform on MTGRD0 will shield (or guard) MTI0 from the effect of nearby noise sources or power planes.

### 1.5.3 MTO

The mTouch<sup>™</sup> sensing output pin is always driven to either VDD or VSs by the device. The MTCH112 OUTCON register (see Register 3-1) determines the behavior of the MTO/INT pin. The pin is always activelow, but the states in which this output occurs can be adjusted in the device's OUTCON register. If no options are selected for output states, the MTO pin acts as an interrupt to a master device. The MTCH112 will pulse low for at least 1 ms if any state changes occur. Further information must be determined by communicating through I<sup>2</sup>C with the device.

### 1.5.4 $I^2C - SERIAL DATA PIN (SDA)$

The SDA pin is the serial data pin of the I<sup>2</sup>C interface. The SDA pin is used to write or read the registers and Configuration bits. The SDA pin is an open-drain N-channel driver. Therefore, it needs an external pullup resistor from the V<sub>DD</sub> line to the SDA pin. The recommended resistance value is  $1.5 \text{ k}\Omega$ . Except for Start and Stop conditions, the data on the SDA pin must be stable during the high period of the clock. The high or low state of the SDA pin can only change when the clock signal on the SCL pin is low. Refer to **Section 2.1.2 "I2C Operation**" for more details on I<sup>2</sup>C Serial Interface communication.

### 1.5.5 I<sup>2</sup>C – SERIAL CLOCK PIN (SCL)

The SCL pin is the serial clock pin of the I<sup>2</sup>C interface. The I<sup>2</sup>C interface only acts as a slave and the SCL pin accepts only external serial clocks. The input data from the master device is shifted into the SDA pin on the rising edges of the SCL clock, and output from the device occurs at the falling edges of the SCL clock. The SCL pin is an open-drain N-channel driver. Therefore, it needs an external pull-up resistor from the VDD line to the SCL pin. The recommended resistance value is 1.5 k $\Omega$ . Refer to **Section 2.1.2** "**I2C Operation**" for more details on I<sup>2</sup>C Serial Interface communication.

For more details, see Figure 1 and Table 1.

### 1.6 Performance

### 1.6.1 PROXIMITY DISTANCE

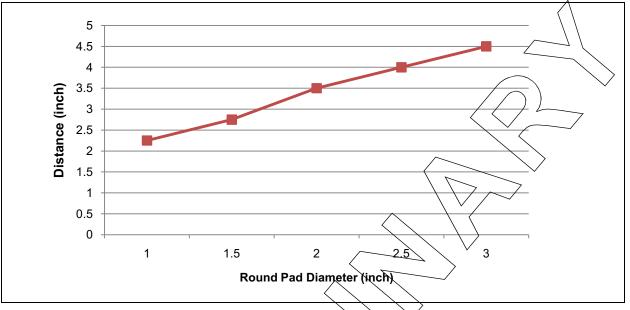

The maximum proximity distance will be highly dependent on the level of noise in the environment. To maximize the robustness of the controller, the noise level is measured and used to define how much shift is required in the signal before a reliable change in state can be determined. These values were taken in a low-noise environment. For more details, see Figure 4-2.

### 1.6.2 RESPONSE TIME

The response time is defined as the maximum amount of time delay between the sensor's capacitance significantly changing and the output being updated based on the OUTCON register's configuration.

This amount of time will be dependent on the LPCON register, as it determines how long the device will sleep after detecting no significant changes. The fastest response time can be achieved by setting the LPCON register for the minimum Sleep time (see Register 3-6). The controller only sleeps when idle and no changes in the environment are detected. If a change occurs, the device will operate without sleeping until the disturbance or capacitance is removed. For more details, see Table 4-2.

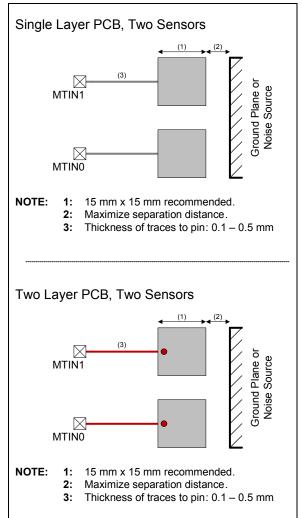

### 1.6.3 HARDWARE

Capacitive sensors are areas of metal connected through a series resistor of 4.7 k $\Omega$  to one of the MTIx pins. The following diagrams show some example layout configurations along with the recommended design guidelines. For more information about the design of capacitive sensors, see AN1334, *"Techniques for Robust Touch Sensing Design"*.

#### FIGURE 1-1: TWO-SENSOR LAYOUTS — EXAMPLE

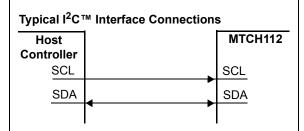

# 2.0 I<sup>2</sup>C<sup>™</sup> SERIAL INTERFACE

This device supports the  $l^2C$  serial protocol. The  $l^2C$  module operates in Slave mode, so it does not generate the serial clock.

### 2.1 Overview

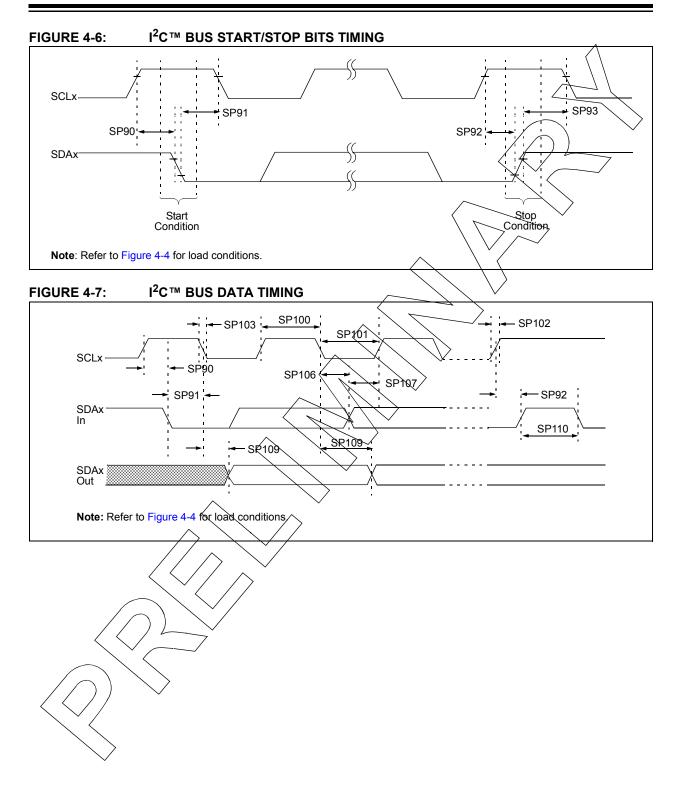

This  $I^2C$  interface is a two-wire interface. Figure 2-1 shows a typical  $I^2C$  Interface connection.

The  $I^2C$  interface specifies different communication bit rates. These are referred to as Standard, Fast or High Speed modes. The MTCH112 device supports these three modes. The bit rates of these modes are:

- · Standard Mode: Bit Rates up to 100 kbit/s

- Fast Mode: Bit Rates up to 400 kbit/s

A device that sends data onto the bus is defined as a transmitter, and a device receiving data is defined as a receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access and generates the Start and Stop conditions. The MTCH112 device works as slave. Both master and slave can operate as transmitter or receiver, but the master device determines which mode is activated. Communication is initiated by the master (microcontroller) which sends the Start bit, followed by the slave address byte. The first byte transmitted is always the slave address byte, which contains the device code, the address bits and the R/W bit.

### FIGURE 2-1: TYPICAL I<sup>2</sup>C™ INTERFACE

The  $l^2C$  serial protocol only defines the field types, field lengths, timings, etc. of a frame. The frame content defines the behavior of the device. For details on the frame content (commands/data) refer to **Section 2.3 "I2C Commands"**.

Refer to the *NXP User Manual* (UM10204\_3) for more details on the  $I^2C$  specifications.

There was some concern as to the use of the Acknowledge bit to indicate a command error condition. From Section 3.6 of the *NXP User Manual* (*UM10204\_3, Rev 03 - 19 June 2007*), the description states:

"The acknowledge takes place after every byte. The Acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. All clock pulses including the acknowledge 9th clock pulse are generated by the master."

From this we can state that the byte was not "*success-fully received*" since it is an invalid combination of Address/Command.

### 2.1.1 SIGNAL DESCRIPTIONS

The  $I^2C$  interface uses up to two pins (signals). These are:

- SDA (Serial Data) (see Section 1.5.4 "I2C Serial Data Pin (SDA)")

- SCL (Serial Clock) (see Section 1.5.5 "I2C Serial Clock Pin (SCL)")

### 2.1.2 I<sup>2</sup>C OPERATION

The MTCH112 device  $I^2C$  module is compatible with the NXP  $I^2C$  specification. The following lists some of the module's features:

- 7-bit Slave Addressing

- Supports Two Clock Rate modes:

- Standard mode, clock rates up to 100 kHz

- Fast mode, clock rates up to 400 kHz

- Support Multi-Master Applications

The I<sup>2</sup>C 10-bit addressing mode is not supported.

The NXP I<sup>2</sup>C specification only defines the field types, field lengths, timings, etc. of a frame. The frame content defines the behavior of the device. The frame content for this device is defined in **Section 2.3 "I2C Commands**".

# I<sup>2</sup>C BIT STATES AND SEQUENCE

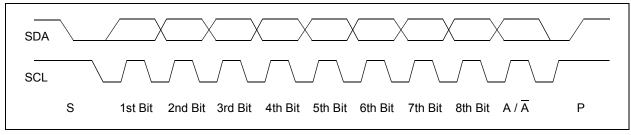

Figure 2-7 shows an  $I^2C$  8-bit transfer sequence, while Figure 2-8 shows the bit definitions. The serial clock is generated by the master. The following definitions are used for the bit states:

- Start bit (S)

- Data bit

- Acknowledge (A) bit (driven low) /

- No Acknowledge (A) bit (not driven low)

- Repeated Start bit (Sr)

- Stop bit (P)

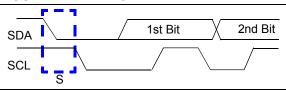

### START BIT

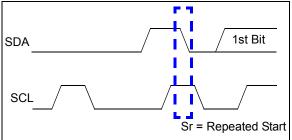

The Start bit (see Figure 2-2) indicates the beginning of a data transfer sequence. The Start bit is defined as the SDA signal falling when the SCL signal is high.

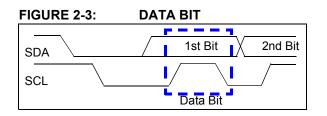

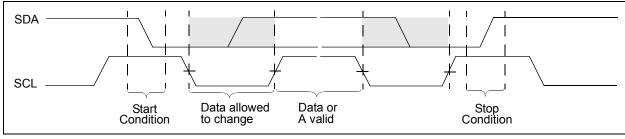

### DATA BIT

The SDA signal may change state while the SCL signal is low. While the SCL signal is high, the SDA signal MUST be stable (see Figure 2-3).

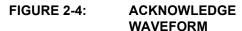

### **ACKNOWLEDGE (A) BIT**

The A bit (see Figure 2-4) is typically a response from the receiving device to the transmitting device. Depending on the context of the transfer sequence, the A bit may indicate different things. Typically, the slave device will supply an A response after the Start bit and 8 data bits have been received. An A bit has the SDA signal low.

# Not A (A) Response

The  $\overline{A}$  bit has the SDA signal high. Table 2-1 shows some of the conditions where the slave device will issue a Not A ( $\overline{A}$ ).

If an error condition occurs (such as an  $\overline{A}$  instead of A), then a Start bit must be issued to reset the command state machine.

| Event                                      | Acknowledge<br>Bit<br>Response | Comment                                                                                                            |

|--------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------|

| General Call                               | Ā                              |                                                                                                                    |

| Slave Address valid                        | А                              |                                                                                                                    |

| Slave Address not valid                    | Ā                              |                                                                                                                    |

| Communication during EEPROM<br>Write cycle | Ā                              | The device will NACK after a valid write sequence until all bytes are executed.                                    |

| Bus Collision                              | N/A                            | Treated as "Don't Care" if the collision occurs on the Start bit. Otherwise, I <sup>2</sup> C <sup>™</sup> resets. |

### TABLE 2-1: MTCH112 A / A RESPONSES

### **REPEATED START BIT**

The Repeated Start bit (see Figure 2-5) indicates that the current master device wishes to continue communicating with the current slave device without releasing the  $I^2C$  bus. The Repeated Start condition is the same as the Start condition, except that the Repeated Start bit follows a Start bit (with the data bits + A bit) and not a Stop bit.

The Start bit is the beginning of a data transfer sequence and is defined as the SDA signal falling when the SCL signal is high.

**Note 1:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

### **STOP BIT**

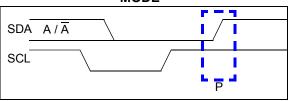

The Stop bit (see Figure 2-6) indicates the end of the  $I^2C$  data transfer sequence. The Stop bit is defined as the SDA signal rising when the SCL signal is high.

A Stop bit resets the  $\mathsf{I}^2\mathsf{C}$  interface of the MTCH112 device.

FIGURE 2-6:

STOP CONDITION RECEIVE OR TRANSMIT MODE

2.1.2.1 Clock Stretching

Clock stretching is something that the receiving device can do to allow additional time to respond to the data that has been received.

This device will stretch the clock signal (SCL) after a Write command to allow the EEPROM write operation to complete.

2.1.2.2 Aborting a Transmission

If any part of the  $l^2C$  transmission does not meet the command format, it is aborted. This can be intentionally accomplished with a Start or Stop condition. This is done so that noisy transmissions (usually an extra Start or Stop condition) are aborted before they corrupt the device.

### FIGURE 2-7: TYPICAL 8-BIT I<sup>2</sup>C<sup>™</sup> WAVEFORM FORMAT

### FIGURE 2-8: I<sup>2</sup>C<sup>™</sup> DATA STATES AND BIT SEQUENCE

### 2.1.2.3 Slope Control

This device does not implement slope control on the SDA output.

### 2.1.2.4 Device Addressing

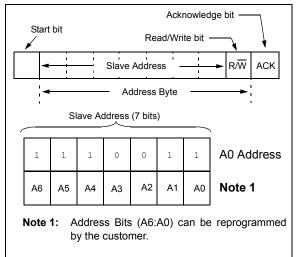

The address byte is the first byte received following the Start condition from the master device. The full 7 bits of the  $l^2C$  slave address is user programmable. The default address is "1110011".

Figure 2-9 shows the I<sup>2</sup>C slave address byte format, which contains the seven address bits and a Read/ Write  $(R/\overline{W})$  bit.

### 2.2 Device Commands

This section documents the commands that the device supports.

The commands can be grouped into the following categories:

- Write Memory

- Read Memory

| Desc.   | Start | Device | Write Protection |      | Reset Co         | ommand | Checksum <sup>(1)</sup> | Stop |

|---------|-------|--------|------------------|------|------------------|--------|-------------------------|------|

| Example | S     | 0xE6   | 0x55             | 0xAA | 0x00             | 0xFF   | 0x00                    | Р    |

| Notes   | _     | Write  | Required         |      | Factory Settings |        | —                       | —    |

Note 1: Checksum is the binary XOR of all bytes except the device address.

### TABLE 2-3: WRITE TO REGISTER

| Desc.   | Start | Device | Write Protection |      | Register | Value | Checksum <sup>(1)</sup> | Stop |

|---------|-------|--------|------------------|------|----------|-------|-------------------------|------|

| Example | S     | 0xE6   | 0x55             | 0xAA | 0x01     | 0x01  | 0xFF                    | Р    |

| Notes   | _     | Write  | Required         |      | OUTCON   |       | _                       | _    |

**Note 1:** Checksum is the binary XOR of all bytes except the device address.

### TABLE 2-4: READ FROM REGISTER

| Desc.   | Start | Device | Register | Restart | Device | Data | Stop | Start | Device | Checksum <sup>(1)</sup> | Stop |

|---------|-------|--------|----------|---------|--------|------|------|-------|--------|-------------------------|------|

| Example | S     | 0xE6   | 0x80     | S       | 0xE7   | _    | Р    | S     | 0xE7   | 0xZZ                    | Р    |

| Notes   |       | Write  | STATE    |         | Read   |      |      |       | Read   | —                       |      |

**Note 1:** Read checksum is the binary XOR of all bytes in the Data column. This is an optional step. The checksum can be ignored if the master does not wish to read it.

# 2.3 $I^2C$ COMMANDS

The  $I^2C$  protocol does not specify how commands are formatted, so this section specifies the MTCH112 device's  $I^2C$  command formats and operation.

The commands can be grouped into the following categories:

- Write Commands

- Read Commands

The supported commands are shown in Table 2-2, Table 2-3 and Table 2-4.

### 2.3.1 WRITE COMMANDS

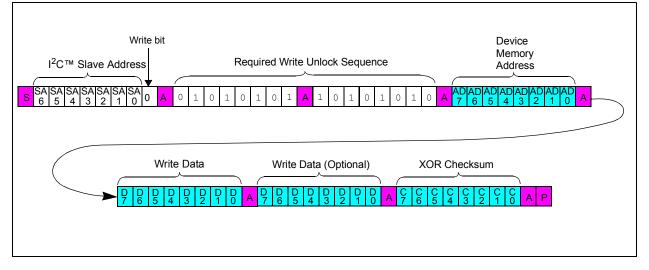

Write commands are used to transfer data to the desired memory location (from the Host controller). The Write command form writes the device address, 0x55, 0xAA, the data address, the value to write and an XOR checksum.

### 2.3.2 READ COMMANDS

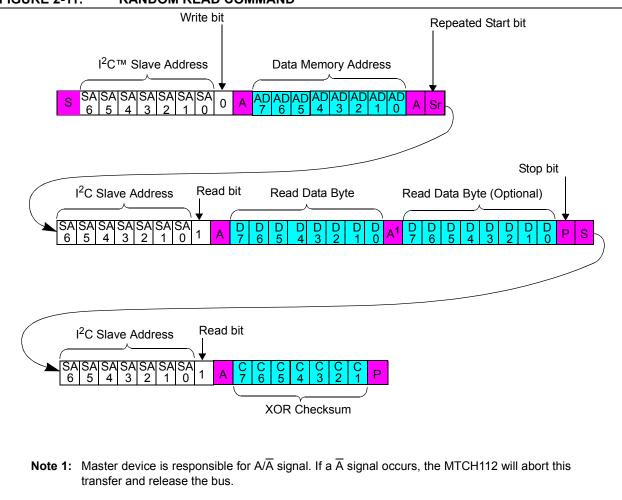

The Read command format writes two bytes, the control byte and the desired memory address byte, and then has a Restart condition. Then a second control byte is transmitted, but this control byte indicates a  $I^2C$  read operation (R/W bit = 1).

### 2.3.3 RESET TO FACTORY SETTINGS COMMAND

Resetting the device to factory settings is equivalent to writing the value 0xFF to the data address  $0 \times 00$ . The proper write protocol must be followed, including the address byte with the Write bit set, 0x55, 0xAA and a binary XOR checksum at the end.

### 2.3.4 ABORTING A COMMAND TRANSMISSION

A Restart or Stop condition in an expected data bit position will abort the current command sequence and data will not be written to the MTCH112. Write commands are automatically aborted if the binary XOR checksum is not valid.

### 2.3.5 WRITE COMMAND (NORMAL AND HIGH VOLTAGE)

The format of the command is shown in Figure 2-10. The MTCH112 generates the  $A/\overline{A}$  bits.

A Write command will only start a Write cycle after a properly formatted Write command has been received and the Stop condition has occurred.

### 2.3.5.1 Writing to Memory

The protocol allows for a variable number of bytes to be written to the device at a time. Once the Stop bit has been sent, a time delay is required while the EEPROM write cycle stores each data byte. While the device is writing the EEPROM, the address will be changed (by toggling the Least Significant address bit of the device, then toggling back once finished) to prevent accidental double writes. An error may occur if a Write command is sent while the EEPROM is still storing the previous bytes. While the writing is being performed, reads to the normal device address will result in a NACK.

Figure 2-10 shows the waveform for a single write.

### FIGURE 2-10: WRITE RANDOM ADDRESS COMMAND

### 2.3.6 READ COMMAND

The Read command can be issued to all memory locations. The format of the command (see Figure 2-11) includes the Start condition,  $I^2C$  control byte (with R/W bit set to 0), A bit, the data address byte, A bit, followed by a Repeated Start bit,  $I^2C$  control byte (with R/W bit set to 1) and the MTCH112 device transmitting the requested data bytes one at a time until the master sends a Stop condition.

The I<sup>2</sup>C control byte requires the  $R/\overline{W}$  bit equal to a logic one ( $R/\overline{W}$  = 1) to generate a read sequence. The memory location read will start at the requested data address and automatically increments by one after each byte request. Notice that the read operation packets do not include the 0x55 and 0xAA Write protection bytes.

After the Stop condition has been received, if a Start condition is followed by the device address, the device will send the XOR checksum of the data bytes from the previous read packet. This allows the checksum to be ignored by the master, if desired.

Read operations initially include the same address byte sequence as the write sequence (shown in Figure 2-10). This sequence is followed by another control byte (including the Start condition and Acknowledge) with the R/W bit equal to a logic one (R/W = 1) to indicate a read. The MTCH112 will then transmit the data contained in the addressed register. This is followed by the master generating an A bit in preparation for more data, or an  $\overline{A}$  bit followed by a Stop. The sequence is ended with the master generating a Stop or Restart condition.

Figure 2-11 shows the waveforms for a single read.

# 2.3.6.1 Ignoring an I<sup>2</sup>C Transmission and "Falling Off" the Bus

The MTCH112 device expects to receive complete, valid I<sup>2</sup>C commands and will assume any command not defined as a valid command is due to a bus corruption and will enter a passive high condition on the SDA signal. All signals will be ignored until the next valid Start condition and control byte are received.

# 3.0 CONFIGURATION REGISTERS

The registers in the MTCH112 have been organized in two groups: the Configuration registers and the output registers. The output registers are in the  $0 \times 80$  (and higher) address range and are read-only. They provide the current sensor data for each input. The Configuration registers are both writable and readable. They show the current scan options and define the systems behavior.

To restore the Configuration registers to their default states and force a recalibration of the sensors, perform a write operation of 0xFF to address 0x00.

# 3.1 Output Control Register (OUTCON)

This register contains the control bits for the MTO/INT pin to determine its behavior. If multiple bits in this register are set, the states they represent are ORd before the output is determined. For example, if the S1BOE and S0BOE bits are set, the MTO pin will output low if either MTI0 or MTI1 detect a button touch. If the S1POE and S0POE bits are set, the MTO pin will output low if either MTI0 or MTI1 make a proximity detection. If none of the bits are set, the pin will perform as a 1 ms pulsed interrupt pin for the I<sup>2</sup>C master. (see Register 3-1)

| U-0   | U-0 | U-0 | U-0 | R/W-0/u              | R/W-0/u              | R/W-1/u              | R/W-1/u              |

|-------|-----|-----|-----|----------------------|----------------------|----------------------|----------------------|

| _     | —   | —   | —   | S1POE <sup>(1)</sup> | S0POE <sup>(1)</sup> | S1BOE <sup>(1)</sup> | S0BOE <sup>(1)</sup> |

| bit 7 |     |     |     |                      |                      |                      | bit 0                |

| Legend:          |                                                                                                                                                                                                    |                                                                                                                                                                                                                                |                                                     |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|

| R = Readable bit |                                                                                                                                                                                                    | U = Unimplemented bit, read as '0'                                                                                                                                                                                             |                                                     |  |  |  |  |  |

| u = Bit is       | unchanged                                                                                                                                                                                          | -n/n = Factory setting value/Value after                                                                                                                                                                                       | -n/n = Factory setting value/Value after all Resets |  |  |  |  |  |

| '1' = Bit is     | s set                                                                                                                                                                                              | '0' = Bit is cleared                                                                                                                                                                                                           | W = Writable bit                                    |  |  |  |  |  |

| bit 7-4          | Unimplem                                                                                                                                                                                           | ented: Read as '0'                                                                                                                                                                                                             |                                                     |  |  |  |  |  |

| bit 3            | <b>S1POE:</b> Sensor 1 Proximity Output Enable bit<br>1 = Output pin activates when Sensor 1 makes a proximity detection<br>0 = Output pin does not change based on Sensor 1's proximity detection |                                                                                                                                                                                                                                |                                                     |  |  |  |  |  |

| bit 2            | 1 = Output                                                                                                                                                                                         | <b>S0POE:</b> Sensor 0 Proximity Output Enable bit<br>1 = Output pin activates when Sensor 0 makes a proximity detection<br>0 = Output pin does not change based on Sensor 0's proximity detection                             |                                                     |  |  |  |  |  |

| bit 1            | 1 = Output                                                                                                                                                                                         | <ul> <li>S1BOE: Sensor 1 Button Output Enable bit</li> <li>1 = Output pin activates when Sensor 1 makes a button press detection</li> <li>0 = Output pin does not change based on Sensor 1's button press detection</li> </ul> |                                                     |  |  |  |  |  |

| bit 0            | 1 = Output                                                                                                                                                                                         | <b>SoBOE:</b> Sensor 0 Button Output Enable bit<br>1 = Output pin activates when Sensor 0 makes a button press detection<br>0 = Output pin does not change based on Sensor 0's button press detection                          |                                                     |  |  |  |  |  |

| Note 1:          |                                                                                                                                                                                                    | le bits are '0', the output pin will behave a ever new data becomes available.                                                                                                                                                 | s a wake-up signal to the master. It will be se     |  |  |  |  |  |

# 3.2 Calibration Control Registers (CALCONx)

This register contains the calibration information for MTIx. It stores the chosen waveform type and whether or not the calibration has been completed. To recalibrate a sensor, clear its respective SxCAL bit in the CALCONx register (see Register 3-2 and Register 3-3).

### REGISTER 3-2: CALCONO: SENSOR 0'S CALIBRATION CONTROL REGISTER

| R/W-0/u   | R/W-0/u | U-0 | U-0 | U-0 | U-0 | R/W-0/u | U-1   |

|-----------|---------|-----|-----|-----|-----|---------|-------|

| S0WS<1:0> |         | —   | —   | —   | —   | S0CAL   | —     |

| bit 7     |         |     |     |     |     |         | bit 0 |

1 .....

| Legend:              |                                                     |                  |  |

|----------------------|-----------------------------------------------------|------------------|--|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |  |

|                      |                                                     |                  |  |

| bit 7-6 | SOWS<1:0>: Sensor 0 Waveform Selection bits                   |

|---------|---------------------------------------------------------------|

|         | 00 = Normal mTouch™ sensing CVD Waveform                      |

|         | 01 = Double mTouch™ sensing CVD Waveform                      |

|         | 10 = Half mTouch™ sensing CVD Waveform                        |

|         | 11 = Reserved. Results in Double mTouch™ sensing CVD Waveform |

| bit 5-2 | Unimplemented: Read as '0'                                    |

| bit 1   | S0CAL: Sensor 0 Calibrated bit                                |

|         | 1 = Sensor 0 calibration complete                             |

|         | 0 = New Sensor 0 calibration requested                        |

| bit 0   | Unimplemented: Read as '0'                                    |

|         |                                                               |

### REGISTER 3-3: CALCON1: SENSOR 1'S CALIBRATION CONTROL REGISTER

| R/W-0/u                                                                                                                                                                                                                                                                                                | R/W-0/u        | U-0                                                               | U-0  | U-0 | U-0  | R/W-0/u        | R/W-1/u |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------|------|-----|------|----------------|---------|

| S1WS                                                                                                                                                                                                                                                                                                   | S<1:0>         | —                                                                 | _    | —   | _    | S1CAL          | S1EN    |

| bit 7                                                                                                                                                                                                                                                                                                  |                |                                                                   |      |     |      |                | bit 0   |

|                                                                                                                                                                                                                                                                                                        |                |                                                                   |      |     |      |                |         |

| Legend:                                                                                                                                                                                                                                                                                                |                |                                                                   |      |     |      |                |         |

| R = Readable bit U = Unimplemented bit, read as '0'                                                                                                                                                                                                                                                    |                |                                                                   |      |     |      |                |         |

| u = Bit is unchanged -n/n = Factory setting value/Value after all Resets                                                                                                                                                                                                                               |                |                                                                   |      |     |      |                |         |

| '1' = Bit is set                                                                                                                                                                                                                                                                                       |                | '0' = Bit is clea                                                 | red  |     |      | W = Writable b | bit     |

| bit 7-6 S1WS<1:0>: Sensor 1 Waveform Selection bits<br>00 = Normal mTouch <sup>™</sup> sensing CVD Waveform<br>01 = Double mTouch <sup>™</sup> sensing CVD Waveform<br>10 = Half mTouch <sup>™</sup> sensing CVD Waveform<br>11 = Reserved. Results in Double mTouch <sup>™</sup> sensing CVD Waveform |                |                                                                   |      |     |      |                |         |

| bit 5-2                                                                                                                                                                                                                                                                                                | •              | ed: Read as '0'                                                   |      |     |      |                |         |

| bit 1                                                                                                                                                                                                                                                                                                  | 1 = Sensor 1 c | or 1 Calibrated b<br>calibration comp<br>or 1 calibration i       | lete |     |      |                |         |

| bit 0                                                                                                                                                                                                                                                                                                  |                | <sup>-</sup> 1 Enabled bit<br>s enabled. Scan<br>s disabled. No s | 0    | 0   | med. |                |         |

# 3.3 ADC Acquisition Time Registers (ADACQx)

This stores the settling delay time for the CVD waveform. This value is part of the recalibration process and will be overwritten if the SxCAL bit is cleared (see Register 3-4 and Register 3-5).

### REGISTER 3-4: ADACQ0: SENSOR 0'S ACQUISITION DELAY

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u    | R/W-0/u | R/W-0/u |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | -   |         |         | S0ACQ<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **S0ACQ<4:0>:** Sensor 0 Acquisition Delay bits

### REGISTER 3-5: ADACQ1: SENSOR 1'S ACQUISITION DELAY

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u    | R/W-0/u | R/W-0/u |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | _   |         |         | S1ACQ<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 4-0 S1ACQ<4:0>: Sensor 1 Acquisition Delay bits

### 3.4 Low-Power Control Register (LPCON)

This register provides the low-power options for the MTCH112. It determines how long the device will sleep when no detections have been made, and how fast the internal oscillator will run. If the CLKSEL bit is set, the valid VDD operating range will decrease. See the bit description in Register 3-6 for more information.

#### REGISTER 3-6: LPCON: LOW-POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0/u | R/W-0/u | R/W-0/u    | R/W-0/u | R/W-1/u | R/W-1/u |

|-------|-----|---------|---------|------------|---------|---------|---------|

| —     | —   |         |         | SLEEP<4:0> | >       |         | CLKSEL  |

| bit 7 |     |         |         |            |         |         | bit 0   |

|       |     |         |         |            |         |         |         |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

### bit 7-6 Unimplemented: Read as '0'

| bit 5-1 | <b>SLEEP&lt;4:0&gt;:</b> Sleep duration between scans when inactive<br>00000 = 1 ms, typical sleep duration<br>00001 = 2 ms, typical sleep duration |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00010 = 4 ms, typical sleep duration                                                                                                                |

|         | 00011 = 8 ms, typical sleep duration                                                                                                                |

|         | 00100 = 16 ms, typical sleep duration                                                                                                               |

|         | 00101 = 32 ms, typical sleep duration                                                                                                               |

|         | 00110 = 64 ms, typical sleep duration                                                                                                               |

|         | 00111 = 128 ms, typical sleep duration                                                                                                              |

|         | 01000 = 256 ms, typical sleep duration                                                                                                              |

|         | 01001 = 512 ms, typical sleep duration                                                                                                              |

|         | 01010 = 1 sec, typical sleep duration                                                                                                               |

|         | 01011 = 2 sec, typical sleep duration                                                                                                               |

|         | 01100 = 4 sec, typical sleep duration                                                                                                               |

|         | 01101 = 8 sec, typical sleep duration                                                                                                               |

|         | 01110 = 16 sec, typical sleep duration                                                                                                              |

|         | 01111 = 32 sec, typical sleep duration                                                                                                              |

|         | 10000 = 64 sec, typical sleep duration                                                                                                              |

|         | 10001 = 128 sec, typical sleep duration<br>10010 = 256 sec, typical sleep duration                                                                  |

|         | 10010 – 250 sec, typical sleep duration                                                                                                             |

|         | 10011 = Reserved. Results in 1 ms sleep duration.                                                                                                   |

|         | 11111 = Reserved. Results in 1 ms sleep duration.                                                                                                   |

| bit 0   | CLKSEL: Oscillator Selection bit                                                                                                                    |

| DILU    | 1 = Internal oscillator runs at 32 MHz                                                                                                              |

|         | Decreases response time                                                                                                                             |

|         | Increases power consumption                                                                                                                         |

|         | Valid VDD operating range when selected is 2.5V-3.6V                                                                                                |

|         | 0 = Internal oscillator runs at 16 MHz                                                                                                              |

|         | Decreases response time                                                                                                                             |

|         | Increases power consumption                                                                                                                         |

|         | Valid VDD operating range when selected is 1.8V-3.6V                                                                                                |

|         |                                                                                                                                                     |

### 3.5 Press Threshold Register (PRESS\_THRESH)

The register stores the minimum shift amount of the signal away from the baseline that is required to activate a sensor as "*touched*". The real-time threshold of the sensor is handled internally, based on current noise levels and the expected press amount. This value simply creates a lower bound. It is not mandatory unless the user wishes to ensure that the sensor is not too sensitive in low-noise environments (see Register 3-7).

### REGISTER 3-7: PRESS\_THRESH: PRESS THRESHOLD REGISTER

| R/W-0/u         | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |  |

|-----------------|---------|---------|---------|---------|---------|---------|---------|--|

| PRESS_THSH<7:0> |         |         |         |         |         |         |         |  |

| bit 7 bit 0     |         |         |         |         |         |         |         |  |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

### bit 7-0 **PRESS\_THSH<7:0>:** Absolute Minimum Press Threshold

# 3.6 Proximity Threshold Register (PROX\_THRESH)

This register is identical to the Press Threshold register, except that it relates to the proximity detection. Increase this value to decrease the sensitivity of the sensor in low-noise environments (see Register 3-8).

### REGISTER 3-8: PROX\_THRESH: PROXIMITY THRESHOLD REGISTER

| R/W-0/u        | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |

|----------------|---------|---------|---------|---------|---------|---------|---------|

| PROX_THSH<7:0> |         |         |         |         |         |         |         |

| bit 7          |         |         |         |         |         |         | bit 0   |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-0 **PROX\_THSH<7:0>:** Absolute Minimum Proximity Threshold

© 2012 Microchip Technology Inc.

### 3.7 16-bit Time-Out Register (TIMEOUT\_L and TIMEOUT\_H)

This set of registers determines how long the 'detected' state is able to remain activated before automatically being reset to a non-detected state. It also determines how long after no changes in the environment have occurred before setting the controller to its Idle state. When in Idle state, the system will sleep (see Register 3-6) between each reading (see Register 3-9 and Register 3-10).

### REGISTER 3-9: TIMEOUT\_L: TIME-OUT COUNTER, LOW BYTE REGISTER

| R/W-1/u      | R/W-1/u | R/W-1/u | R/W-1/u | R/W-1/u | R/W-1/u | R/W-1/u | R/W-1/u |

|--------------|---------|---------|---------|---------|---------|---------|---------|

| TIMEOUT<7:0> |         |         |         |         |         |         |         |

| bit 7        |         |         |         |         |         |         | bit 0   |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-0 TIMEOUT<7:0>: Time-out Counter Reload Value, Low Byte

### REGISTER 3-10: TIMEOUT\_H: TIME-OUT COUNTER, HIGH BYTE REGISTER

| _ |         |         | _       |         |          |         |         |         |

|---|---------|---------|---------|---------|----------|---------|---------|---------|

|   | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u  | R/W-0/u | R/W-0/u | R/W-1/u |

|   |         |         |         | TIMEOU  | JT<15:8> |         |         |         |

| b | oit 7   |         |         |         |          |         |         | bit 0   |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-0 TIMEOUT<15:8>: Time-out Counter Reload Value, High Byte

# 3.8 I<sup>2</sup>C Address Register (I<sup>2</sup>CADDR)

This register determines the  $I^2C$  address of the slave. After writing to this register, command immediately should begin using the new address value (see Register 3-11).

# Register 3-11: I<sup>2</sup>CADDR: I<sup>2</sup>C<sup>™</sup> Address Register

|         |         |         |                         | -       |         |         |       |

|---------|---------|---------|-------------------------|---------|---------|---------|-------|

| R/W-1/u | R/W-1/u | R/W-1/u | R/W-0/u                 | R/W-0/u | R/W-1/u | R/W-1/u | U-1   |

|         |         | ľ       | <sup>2</sup> CADDR<7:1> | >       |         |         | —     |

| bit 7   |         |         |                         |         |         |         | bit 0 |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-1  $I^2$ CADDR<7:1>: I<sup>2</sup>C Address for communication with the MTCH112.

bit 0 Unimplemented: Read as '0'

## 3.9 State Register (STATE)

This register is read-only. It contains the current touch and proximity state of MTI0 and MTI1, and provides error information if a short is detected on any MTIx pin to VDD, Vss or the other MTIx pin (see Register 3-12).

### REGISTER 3-12: STATE: CURRENT SENSOR STATE REGISTER

| U-0   | R-0/x         | R-0/x | R-0/x | R-0/x | R-0/x | R-0/x | R-0/x |

|-------|---------------|-------|-------|-------|-------|-------|-------|

| —     | ERRSTATE<2:0> |       |       | S1PS  | SOPS  | S1BS  | SOBS  |

| bit 7 |               |       |       |       |       |       | bit 0 |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | ERRSTATE<2:0>: Error Status Information bits<br>000 = Both sensors floating correctly<br>001 = Sensor 0 is shorted to VDD<br>010 = Sensor 1 is shorted to VDD<br>011 = Sensor 0 is shorted to VSS<br>100 = Sensor 1 is shorted to VSS<br>101 = Sensors are shorted together<br>110 = Reserved<br>111 = Reserved |

| bit 3   | <ul> <li>S1PS: Sensor 1 Proximity Status bit</li> <li>1 = Proximity detected on Sensor 1</li> <li>0 = No proximity detected on Sensor 1</li> </ul>                                                                                                                                                              |

| bit 2   | <b>SOPS:</b> Sensor 0 Proximity Status bit<br>1 = Proximity detected on Sensor 0<br>0 = No proximity detected on Sensor 0                                                                                                                                                                                       |

| bit 1   | <b>S1BS:</b> Sensor 1 Button Status bit<br>1 = Button press detected on Sensor 1<br>0 = No button press detected on Sensor 1                                                                                                                                                                                    |

| bit 0   | <b>SOBS:</b> Sensor 0 Button Status bit<br>1 = Button press detected on Sensor 0<br>0 = No button press detected on Sensor 0                                                                                                                                                                                    |

# 3.10 Reading Registers (READINGxL and READINGxH)

These registers contain the current raw value of the MTIx pins. They are 13-bit values, but it is recommended to treat them as 16-bit values to more easily support future designs (see Register 3-13 to Register 3-16).

### REGISTER 3-13: READINGOL: SENSOR 0 READING VALUE, LOW BYTE

| R-x            | R-x | R-x | R-x | R-x | R-x | R-x | R-x |

|----------------|-----|-----|-----|-----|-----|-----|-----|

| READING0L<7:0> |     |     |     |     |     |     |     |

| bit 7 bit 0    |     |     |     |     |     |     |     |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-0 READINGOL<7:0>: Sensor 0 Current Reading Value, Low Byte

### REGISTER 3-14: READING0H: SENSOR 0 READING VALUE, HIGH BYTE

| U-0   | U-0 | U-0 | R-x            | R-x | R-x | R-x | R-x   |  |

|-------|-----|-----|----------------|-----|-----|-----|-------|--|

| —     | —   | —   | READING0H<4:0> |     |     |     |       |  |

| bit 7 |     |     |                |     |     |     | bit 0 |  |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

| bit 7-5 | Unimplemented: Read as '0'                                |

|---------|-----------------------------------------------------------|

| bit 4-0 | READING0H<4:0>: Sensor 0 Current Reading Value, High Byte |

#### REGISTER 3-15: READING1L: SENSOR 1 READING VALUE, LOW BYTE

| R-x   | R-x | R-x | R-x     | R-x      | R-x | R-x | R-x   |

|-------|-----|-----|---------|----------|-----|-----|-------|

|       |     |     | READING | G1L<7:0> |     |     |       |

| bit 7 |     |     |         |          |     |     | bit 0 |

|       |     |     |         |          |     |     |       |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

### bit 7-0 **READING1L<7:0>:** Sensor 1 Current Reading Value, Low Byte

| U-0                                                    | U-0                                                                      | U-0 | R-x              | R-x | R-x | R-x | R-x   |  |

|--------------------------------------------------------|--------------------------------------------------------------------------|-----|------------------|-----|-----|-----|-------|--|

| —                                                      | —                                                                        | —   | - READING1H<4:0> |     |     |     |       |  |

| bit 7                                                  |                                                                          |     |                  |     |     |     | bit 0 |  |

|                                                        |                                                                          |     |                  |     |     |     |       |  |

| Legend:                                                |                                                                          |     |                  |     |     |     |       |  |

| R = Readable                                           | R = Readable bit U = Unimplemented bit, read as '0'                      |     |                  |     |     |     |       |  |

| u = Bit is uncha                                       | u = Bit is unchanged -n/n = Factory setting value/Value after all Resets |     |                  |     |     |     |       |  |

| '1' = Bit is set '0' = Bit is cleared W = Writable bit |                                                                          |     |                  |     | bit |     |       |  |

#### REGISTER 3-16: READING1H: SENSOR 1 READING VALUE, HIGH BYTE

bit 7-5 Unimplemented: Read as '0'

bit 4-0 READING1H<4:0>: Sensor 1 Current Reading Value, High Byte

### 3.11 Baseline Registers (BASELINExL and BASELINExH)

These registers contain the current baseline value of the MTIx pins. They are 13-bit values, but it is recommended to treat as unsigned 16-bit values to more easily support future designs (see Register 3-17 to Register 3-20).

#### REGISTER 3-17: BASELINEOL: SENSOR 0 BASELINE VALUE, LOW BYTE

| R-x             | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |  |

|-----------------|-----|-----|-----|-----|-----|-----|-------|--|

| BASELINE0L<7:0> |     |     |     |     |     |     |       |  |

| bit 7           |     |     |     |     |     |     | bit 0 |  |

|                 |     |     |     |     |     |     |       |  |

| Legend:              |                                                     |                  |  |

|----------------------|-----------------------------------------------------|------------------|--|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |  |

#### bit 7-0 BASELINE0L<7:0>: Sensor 0 Current Baseline Value, Low Byte

#### REGISTER 3-18: BASELINE0H: SENSOR 0 BASELINE VALUE, HIGH BYTE

| U-0   | U-0 | U-0 | R-x | R-x | R-x         | R-x | R-x   |

|-------|-----|-----|-----|-----|-------------|-----|-------|

| —     | —   | —   |     | B   | ASELINE0H<4 | :0> |       |

| bit 7 |     |     |     |     |             |     | bit 0 |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 BASELINE0H<4:0>: Sensor 0 Current Baseline Value, High Byte

|                   |      |                  |                 |                  | •      |                  |       |

|-------------------|------|------------------|-----------------|------------------|--------|------------------|-------|

| R-x               | R-x  | R-x              | R-x             | R-x              | R-x    | R-x              | R-x   |

|                   |      |                  | BASELIN         | IE1L<7:0>        |        |                  |       |

| bit 7             |      |                  |                 |                  |        |                  | bit 0 |

|                   |      |                  |                 |                  |        |                  |       |

| Legend:           |      |                  |                 |                  |        |                  |       |

| R = Readable bi   | it   | U = Unimplen     | nented bit, rea | id as '0'        |        |                  |       |

| u = Bit is unchar | nged | -n/n = Factory   | y setting value | /Value after all | Resets |                  |       |

| '1' = Bit is set  |      | '0' = Bit is cle | ared            |                  |        | W = Writable bit |       |

### REGISTER 3-19: BASELINE1L: SENSOR 1 BASELINE VALUE, LOW BYTE

bit 7-0 BASELINE1L<7:0>: Sensor 1 Current Baseline Value, Low Byte

### REGISTER 3-20: BASELINE1H: SENSOR 1 BASELINE VALUE, HIGH BYTE

| U-0   | U-0 | U-0 | R-x | R-x | R-x         | R-x | R-x   |

|-------|-----|-----|-----|-----|-------------|-----|-------|

| —     | —   | —   |     | В   | ASELINE1H<4 | :0> |       |

| bit 7 |     |     |     |     |             |     | bit 0 |

| Legend:              |                                                     |                  |

|----------------------|-----------------------------------------------------|------------------|

| R = Readable bit     | U = Unimplemented bit, read as '0'                  |                  |

| u = Bit is unchanged | -n/n = Factory setting value/Value after all Resets |                  |

| '1' = Bit is set     | '0' = Bit is cleared                                | W = Writable bit |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 BASELINE1H<4:0>: Sensor 1 Current Baseline Value, High Byte

| Address | Name                 | Bit7 | Bit6          | Bit5         | Bit4    | Bit3            | Bit2     | Bit1  | Bit0   |

|---------|----------------------|------|---------------|--------------|---------|-----------------|----------|-------|--------|

| 0x00    | _                    |      | _             | —            |         | _               | —        |       | _      |

| 0x01    | OUTCON               | _    | _             | _            | _       | S1POE           | S0POE    | S1BOE | SOBOE  |

| 0x02    | CALCON0              | S0   | NS            | _            | _       | _               | _        | SOCAL | —      |

| 0x03    | CALCON1              | S1\  | NS            | _            |         | —               | _        | S1CAL | S1EN   |

| 0x04    | ADACQ0               |      |               |              |         | S               | 0ACQ<4:0 | )>    |        |

| 0x05    | ADACQ1               |      |               |              |         | S               | 1ACQ<4:0 | )>    |        |

| 0x06    | LPCON                |      |               |              | ę       | SLEEP<4:0       | >        |       | CLKSEL |

| 0x07    | PRESS_THRESH         |      |               |              | PRESS_  | THSH<7:0>       | •        |       |        |

| 0x08    | PROX_THRESH          |      |               |              | PROX_1  | [HSH<7:0>       |          |       |        |

| 0x09    | TIMEOUT_L            |      | TIMEOUT<7:0>  |              |         |                 |          |       |        |

| 0x0A    | TIMEOUT_H            |      | TIMEOUT<15:8> |              |         |                 |          |       |        |

| 0x0B    | I <sup>2</sup> CADDR |      |               | <sup>2</sup> | CADDR<7 | ': <b>1&gt;</b> |          |       | —      |

| 0x0C    | —                    | _    | _             | _            | _       | _               | _        | _     | —      |

| 0x0D    | —                    |      | _             | _            |         | _               | _        |       | —      |

| 0x0E    |                      |      | _             | —            |         | _               | —        |       | —      |

| 0x0F    | —                    | _    | —             | —            | _       | —               | —        | _     | —      |

| 0x80    | STATE                |      | ER            | RSTATE<2     | 2:0>    | S1PS            | SOPS     | S1BS  | SOBS   |

| 0x81    | <b>READING0L</b>     |      |               |              | READIN  | IG0L<7:0>       |          |       |        |

| 0x82    | READING0H            | _    | —             | —            |         | REA             | ADING0H< | 4:0>  |        |

| 0x83    | READING1L            |      |               |              | READIN  | IG1L<7:0>       |          |       |        |

| 0x84    | READING1H            |      | —             | _            |         | REA             | ADING1H< | 4:0>  |        |

| 0x85    | BASELINE0L           |      |               |              | BASE    | 0L<7:0>         |          |       |        |

| 0x86    | BASELINE0H           | _    | —             | —            |         | B               | ASE0H<4: | 0>    |        |

| 0x87    | BASELINE1L           |      |               |              | BASE    | 1L<7:0>         |          |       |        |

| 0x88    | BASELINE1H           | —    | —             |              |         | B               | ASE1H<4: | 0>    |        |

# TABLE 3-1: REGISTER MAPPING

# 4.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings<sup>(†)</sup>

| $\sim$                                                              |

|---------------------------------------------------------------------|

| - <del>40°C to +</del> 125°C                                        |

| -65°C to +158°C                                                     |

|                                                                     |

|                                                                     |

| 0.3V to (VDD + 0.3V)                                                |

|                                                                     |

|                                                                     |

| 80 mA                                                               |

| ± 20 mA                                                             |

|                                                                     |

|                                                                     |

| $\pm \sum \{ (VDD - VOH) \times IOH \} + \sum (VOI \times IOL). \}$ |

|                                                                     |

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# **MTCH112**

## FIGURE 4-1:VOLTAGE FREQUENCY GRAPH, -40°C $\leq$ TA $\leq$ +125°C

## 4.1 DC Characteristics: MTCH/112

| MTCH11        | MTCH112                         |                                                           |            |       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |        |                          |  |  |  |

|---------------|---------------------------------|-----------------------------------------------------------|------------|-------|------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------|--|--|--|

| Param.<br>No. | Sym. Characteristic Min. Typ† I |                                                           | Max.       | Units | Conditions                                                                                                                         |        |                          |  |  |  |

| D001          | Vdd                             | Supply Voltage                                            | 1.8<br>2.5 | —     | 3.6<br>3.6                                                                                                                         | V<br>V | CLKSEL = 0<br>CLKSEL = 1 |  |  |  |

| D002*         | Vdr                             | RAM Data Retention Voltage (1)                            | 1.5        | _     | _                                                                                                                                  | V      | Device in Sleep mode     |  |  |  |

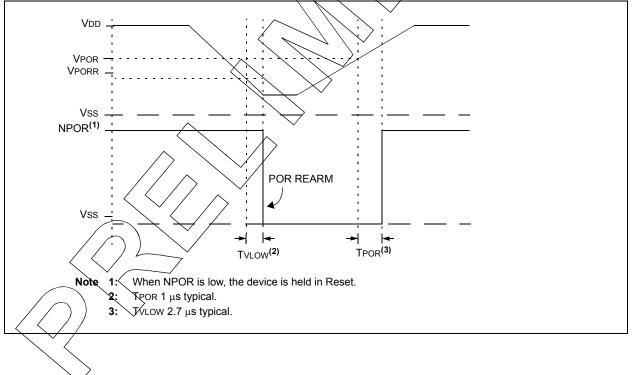

|               | VPOR*                           | Power-on Reset Release Voltage                            | _          | 1.6   | _                                                                                                                                  | V      |                          |  |  |  |

|               | VPORR*                          | Power-on Reset Rearm Voltage                              | _          | 0.8   | _                                                                                                                                  | V      | Device in Sleep mode     |  |  |  |