### Introduction

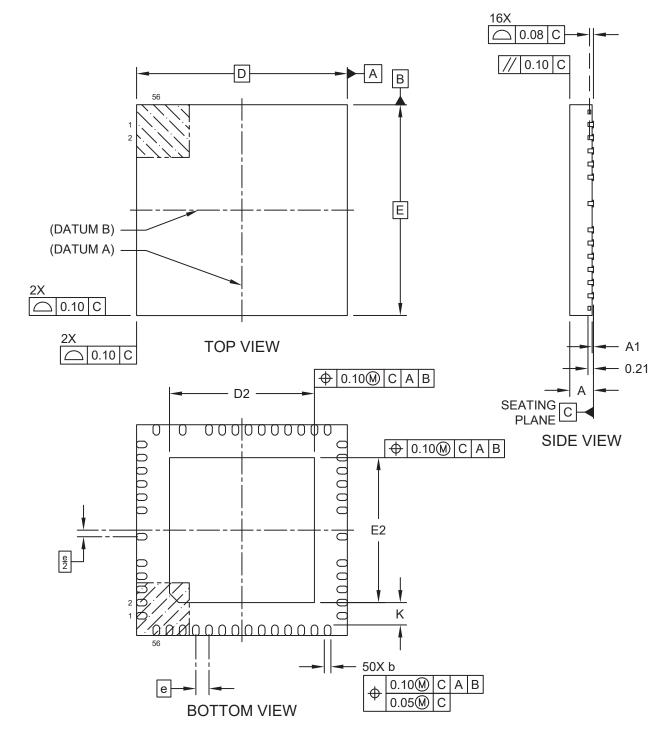

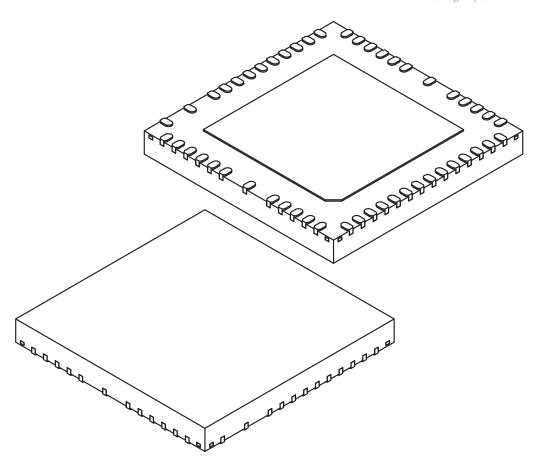

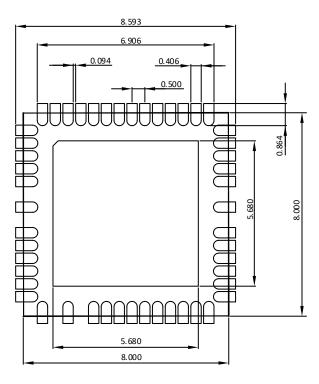

The PD77728 device is a part of Microchip's seventh generation IEEE 802.3bt compliant Power over Ethernet (PoE) Power Sourcing Equipment (PSE) family. This device is a fully integrated 8-port PoE controller and PoE manager with integrated Field Effect Transistor (FET) switches and current sense resistors. Up to 12 devices can be cascaded to provide 48 4-pair ports. The device is available in a 56-pin 8 mm × 8 mm QFN package.

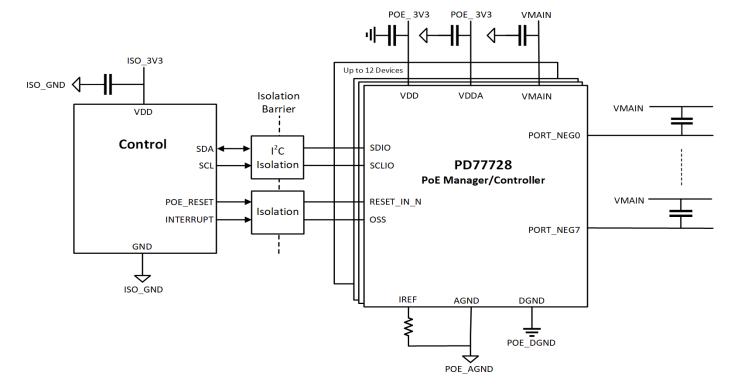

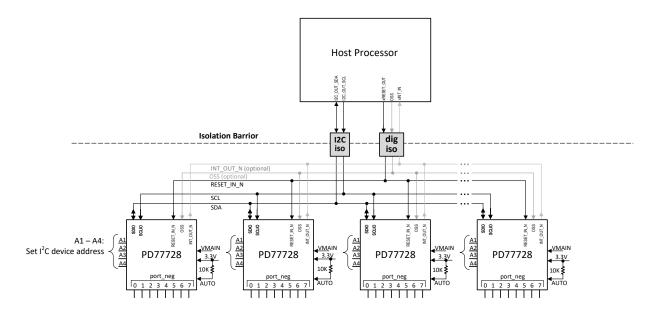

The following figure shows the typical PoE application of the PD77728 device.

Figure 1. Typical PoE Application

#### **Features**

The PD77728 device and PD77728 based PSE have the following key features:

- Supported Standards

- IEEE 802.3bt

- Supported PD Types

- Type 1, Type 2 PDs (802.3af, 802.3at)

- Single-Signature (Type 1-4) PDs

- Dual-Signature (Type 3 and 4) PDs

- Pre-Standard (Legacy) 4-pair PDs

- Supports non-compliant and legacy PDs

- · Four Operational Modes

- Controller mode in conjunction with PD77020 PSE Power Management Controller

- Semi-Auto mode

- Managed Auto mode

- Unmanaged Auto mode

- Cascade up to 12 devices to support 96 × 2-pair ports or 48 × 4-pair ports and any 4-pair/2-pair combination

- Device Features

- Stand-Alone device supports up to 8 × 2-pair ports or 4 × 4-pair ports and any 4-pair/2-pair combination

- Per-Port integrated FET, sense resistor, and port diode

- Total port resistance of 160 mΩ

- Device power dissipation ≤ 2W at full load

- Two power rails (55V and 3.3V) for maximum power efficiency

- Guaranteed 4-pair output power of > 90W

- Over Supply Signal (OSS) support

- AutoClass support

- Supports Fast and Perpetual PoE

- MarkHold function support

- Host Interface through I<sup>2</sup>C Communication

- Real-Time Protection (RTP)

- Measurements

- Per-Port voltage and current measurement

- Accurate main power measurement

- Surge

- Surge up to 2 kV without additional components per IEC61000-4-5-2014

- Surge compliance, ITU-T K.21, GR1089, IE61000-4-5-2014, EN55024

- Up to 10 kV per IEC61000-4-5-2014

- Up to 6 kV per ITU-T K.21

- Physical Characteristics

- Ambient temperature range -40 °C to 85 °C

- 56-pin 8 mm × 8 mm QFN package with thermal pad

- MSL3, RoHS compliant

## **Applications**

The PD77728 based PSE has the following typical applications:

- Switches and routers for enterprise, small and medium business, SOHO, and commercial markets

- Switches for lighting market

- PoE injectors

# **Table of Contents**

| Intr | troduction                                   | 1          |

|------|----------------------------------------------|------------|

|      | Features                                     | 2          |

|      | Applications                                 | 3          |

| 1.   | Functional Descriptions                      |            |

| ١.   | ·                                            |            |

|      | 6                                            | odule6     |

|      |                                              |            |

|      | <u> </u>                                     |            |

|      |                                              |            |

|      |                                              |            |

|      |                                              |            |

|      |                                              |            |

|      | =                                            |            |

|      | <u> </u>                                     |            |

| 2.   | . PD77020 PSE Power Management Controller    | 10         |

| 3.   | Electrical Specifications                    | 11         |

|      | 3.1. Absolute Maximum Ratings                | 11         |

|      | 3.2. Immunity                                | 11         |

|      | 3.3. Recommended Operating Conditions        | 12         |

|      | 3.4. Electrical Characteristics              |            |

| 4.   | Pin Descriptions                             | 16         |

| 5.   | Application Information                      | 19         |

|      | 5.1. Operational Modes                       | 19         |

|      | 5.2. I <sup>2</sup> C                        | 23         |

|      | ·                                            |            |

|      |                                              |            |

|      |                                              |            |

|      | 5.6. Compliance to Limited Power Source Requ | irements27 |

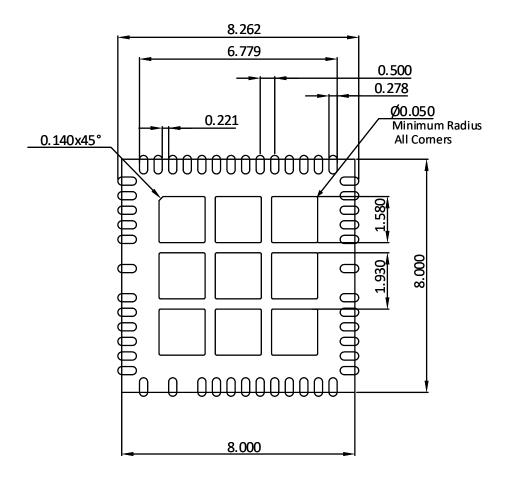

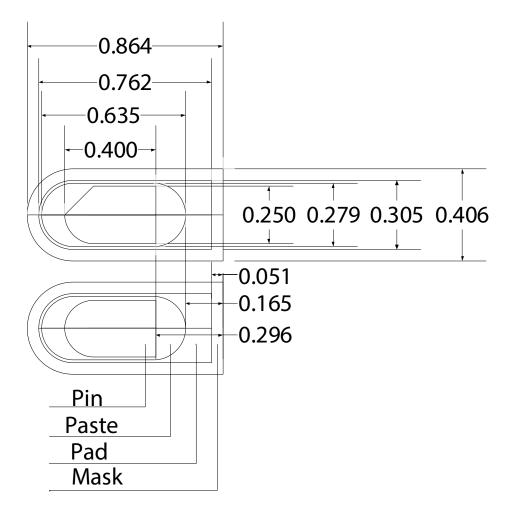

| 6.   | Package Specifications                       | 28         |

|      | 6.1. Recommended PCB Layout                  | 30         |

|      | 6.2. Thermal Properties                      | 33         |

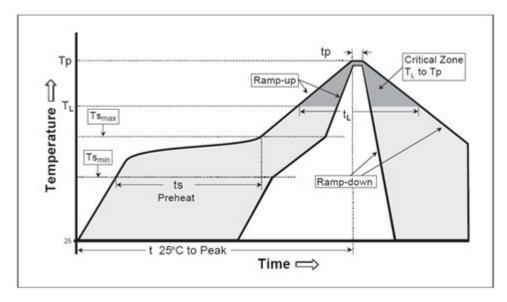

|      | 6.3. Recommended Solder Reflow Information   |            |

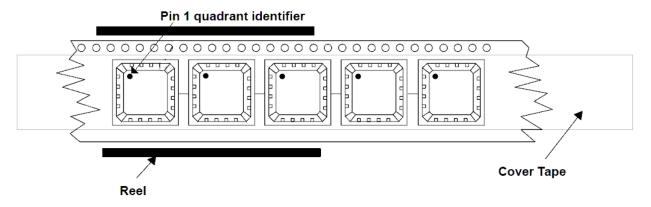

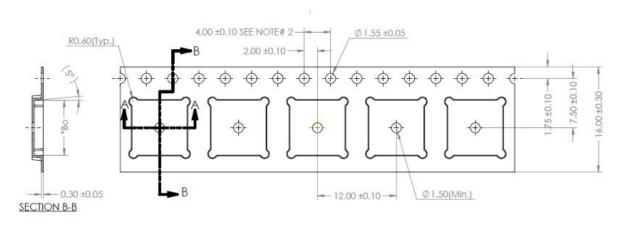

| 7.   | Tape and Reel Specifications                 | 35         |

| 8.   | Ordering Information                         |            |

| 9.   | . Reference Documents                        | 38         |

| 10.  | 0. Revision History                          | 39         |

| Mic  | licrochip Information                        | 40         |

|      | •                                            | 40         |

|      | ·                                            | 40         |

| Customer Support                          | 40 |

|-------------------------------------------|----|

| Microchip Devices Code Protection Feature |    |

| Legal Notice                              |    |

| Trademarks                                |    |

| Quality Management System                 |    |

| Worldwide Sales and Service               |    |

### 1. Functional Descriptions

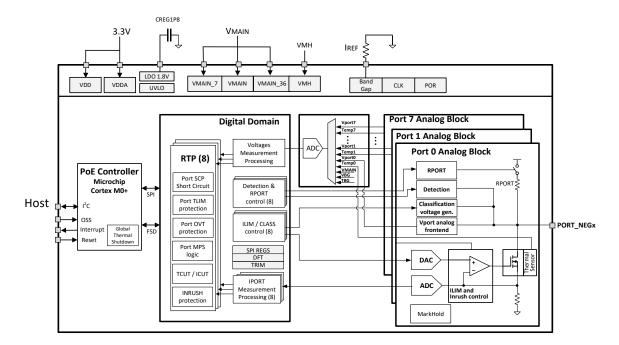

This section describes the following four main blocks of the PD77728 device:

- Analog front-end block (x8)

- Voltage and temperature measurement module

- · Digital processing and control block

- PoE controller (based on the Cortex -M device)

The following figure shows a high-level block diagram of the device.

Figure 1-1. Block Diagram

### 1.1 Analog Front-End Block

The analog front-end block of each port contains the following components:

- Current limiting block—fast acting current limiting loop

- · Classification voltage regulation

- V<sub>PORT</sub> measurement analog interface

- · Detection module

- Current measurement module

- Proprietary MarkHold analog block

This structure allows efficient and flexible port control. It also supports simultaneous power-up/power-on 8 ports control.

### 1.2 Voltage and Temperature Measurement Module

The module measures port voltages, V<sub>MAIN</sub> voltage, and temperature.

### 1.3 Digital Processing and Control Block

The digital block communicates with the integrated PoE controller and controls the analog front-end block. It consists of the following blocks:

- Ports ON/OFF control block

- I<sub>LIM</sub> and I<sub>CLASS</sub> control blocks

- I<sub>INRUSH</sub> control and protection block

- Detection and R<sub>PORT</sub> control block

- Port voltage and temperature measurement post-processing module

- Port current post-processing module

- RTP module

#### 1.4 PoE Controller

The integrated PoE controller controls both port-level and device-level PoE tasks. The firmware is pre-programmed into the integrated controller with field-upgradable capability through the I<sup>2</sup>C host interface.

The integrated PoE controller provides the following features:

- Host communication interface (Fast-Mode Plus I<sup>2</sup>C interface, INT\_OUT signal)

- · OSS fast shut-down control

- Device-level data processing

- Supports PoE firmware download capability from host

- Manages one device 2p and 4p ports configuration

- · Device-Level power budgeting and power assignment

#### 1.5 Power

The PD77728 device is designed for low power consumption and low power dissipation, using cutting-edge process technology and proprietary port's MOSFET design.

The following two parameters allow a total power dissipation of equal to or less than 2W at  $T_J$  = 125 °C:

- Very low channel (port) resistance (typically, 160 m $\Omega$  at 25 °C)

- Very low V<sub>MAIN</sub> quiescent current

The PD77728 device supports any power rail sequencing of the V<sub>MAIN</sub> and V<sub>DD</sub> rails.

### 1.6 Real-Time Protection (RTP)

This section describes the RTP blocks included in the PD77728 device. The device supports multi-level and real-time support mechanisms. All RTP mechanisms are configured by the PoE controller, implemented in the digital domain, and directly control the port analog front-end. Each port has its own RTP protection blocks. This type of design ensures fast acting protection under all conditions.

#### 1.6.1 Current Overload (T<sub>LIM</sub>/I<sub>LIM</sub>) Protection

The configurable  $I_{LIM}$  and  $T_{LIM}$  parameters are based on the IEEE 802.3bt standard.  $T_{LIM}$  and  $I_{LIM}$  threshold levels are selected by firmware based on the assigned class. The port shuts down if it enters current limit ( $I_{LIM}$ ) and maintains  $I_{LIM}$  for a period of  $T_{LIM}$ . Current overload RTP also protects against repetitive overload conditions, where the port repetitively enters current limit for a duration less than  $T_{LIM}$ , which might result in a device damage due to accumulated overheating. The PD77728 overload protection mechanism disconnects the port if the accumulated power poses danger to the Safe Operating Area (SOA) of the MOSFET.

#### 1.6.2 Short-Circuit Protection

If the port enters current limit but the port voltage (V<sub>PORT</sub>) drops below a configurable value, the port is considered to be in a short-circuit condition. In this case, the port is turned OFF within 100 µs (typical) to minimize the power dissipation on the MOSFET during such a harsh condition. The voltage below which the port is considered to be in a short-circuit condition is also configurable.

#### 1.6.3 Inrush (Power-Up) Protection

During the port inrush phase, the PD capacitor is charged with a constant current for up to 75 ms. If the PD is not limiting the current, the PSE uses its current limit to limit the capacitor inrush current (for most cases,  $I_{LIM}$  is 0.425A). Inrush current is also configurable. A failed PD capacitor, or too large a capacitor value, might result in either a true short-circuit condition on the port during inrush (leads to very high-power dissipation, equal to 0.425A ×  $V_{MAIN}$ ), or a very high-power dissipation due to the slow increase in the capacitor voltage. A dedicated inrush protection mechanism is provided to protect the device from such events, assuring that the port's MOSFET does not exceed its SOA under any condition.

#### 1.6.4 Over-Temperature (OVT) Protection

OVT protection adds an additional layer of protection to the device, and protects the device from overheating and damaging in parallel to the other protection mechanisms. An example for OVT protection is a slow increase in ambient temperature (for example, a failed fan), resulting in elevated junction temperature which exceeds the maximum operating junction temperature. In this case, OVT real-time protection either limits the number of ports that can be turned ON at such temperature, or turns OFF the port (s) with the highest junction temperature.

#### 1.6.5 T<sub>CUT</sub>/I<sub>CUT</sub> Protection

The firmware selects  $T_{CUT}$  and  $I_{CUT}$  threshold levels based on the assigned class. The port is turned OFF if the port current exceeds  $I_{CUT}$  for a cumulative time of  $T_{CUT}$  (typical 65 ms). Both  $T_{CUT}$  and  $I_{CUT}$  values are configurable.

#### 1.6.6 Maintain Power Signature

Although this condition does not endanger the PSE device, the MPS signature is required to keep a PD powered and to disconnect its power if PD is removed. The PD77728 device incorporates MPS protection, in which the port is turned OFF if the PD current does not comply with the required hold current and time, as defined in the IEEE 802.3bt standard. Both the hold current ( $I_{HOLD}/I_{HOLD-2P}$ ) and the duration ( $I_{MPS}$ ,  $I_{MPDO}$ ) are configurable parameters.

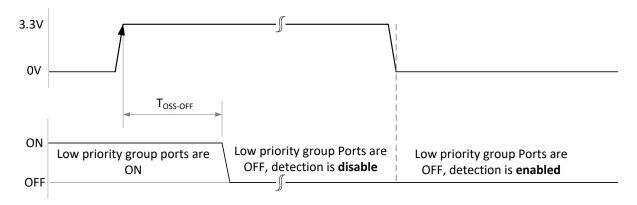

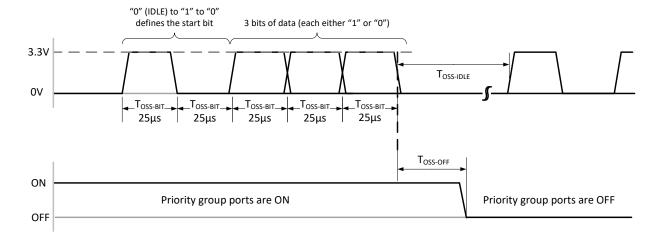

### 1.7 Over Supply Shutdown (OSS)

OSS is a control pin required to turn OFF ports of a certain priority due to failure in one of the power supplies. A dedicated fast shut-down bus is located between the PoE controller and the digital block to allow fast shut-down response to the OSS signal. Both 1-bit signal priority and 3-bit signal priority are supported.

# 1.8 V<sub>MAIN</sub> Under-Voltage Lockout (V<sub>MAIN\_UVLO</sub>)

V<sub>MAIN</sub> under-voltage lockout (V<sub>MAIN UVLO</sub>) turns OFF ports when V<sub>MAIN</sub> drops below a set threshold.

### 1.9 Surge

The PD77728 device supports up to 2 kV per IEC-61000-4-5-2014 without external protection components.

For a higher level of surge, request AN4813 Surge Protection for Systems Based on PD77728 8-Port PSE PoE Controller/Manager Application note.

### 1.10 PSE System Modes of Operation

The device supports the following PSE system modes of operation:

- Controller mode (with PD77020 PSE Power Management Controller)

- Managed Semi-Auto mode

- Managed Auto mode

- Unmanaged Auto mode

For more details, see 5. Application Information.

### 2. PD77020 PSE Power Management Controller

The PD77020 PoE Power Management Controller provides multi-port PoE functions, such as port mapping (Port Matrix), port priority, port status, and system power management. The PD77020 device is used in conjunction with the PD77728 PoE Manager/Controller. The PD77020 device is based on Microchip SAM D21 and is packaged in a 5 mm × 5 mm 32-pin QFN package.

For more details, see the PD77020 Data Sheet and Communications Protocol documents.

## 3. Electrical Specifications

This section describes the electrical specifications of the device.

### 3.1 Absolute Maximum Ratings

PoE performance is not guaranteed when it exceeds the recommended rating. Exposure to any stress in the range between the recommended rating and the absolute maximum rating must be limited to a short time. Exceeding these ratings might impact long-term operating reliability. The following table lists the absolute maximum ratings.

Table 3-1. Absolute Maximum Ratings

| Parameter                                  | Minimum           | Maximum                                  | Unit |

|--------------------------------------------|-------------------|------------------------------------------|------|

| $V_{DD}$                                   | -0.3              | 3.8                                      | ٧    |

| $V_{DDA}$                                  | -0.3              | 3.8                                      | V    |

| $V_{DDA}$ to $V_{DD}$                      | -0.3              | 0.3                                      | V    |

| V <sub>MAIN</sub>                          | -0.3              | 80                                       | V    |

| V <sub>MAIN_7</sub> , V <sub>MAIN_36</sub> | V <sub>MAIN</sub> | 80                                       | V    |

| MarkHold FET is OFF                        | 0                 | V <sub>MAIN</sub>                        | V    |

| PORT_NEGx to AGND                          | -0.3              | Lower of V <sub>MAIN_x</sub> + 0.5 or 80 | V    |

| DGND to AGND                               | -0.3              | 0.3                                      | V    |

| Digital I/O                                | -0.3              | 3.6                                      | V    |

| AUTO                                       | -0.3              | Lower of V <sub>DDA</sub> + 0.3 or 3.8   | V    |

| Junction Temperature                       | -40               | Self Protected                           | °C   |

| Storage                                    | -55               | 150                                      | °C   |

| Solder 10 Seconds                          | _                 | 260                                      | °C   |

## 3.2 Immunity

The following tables list the device immunity.

Table 3-2. ESD

| Model                     | Pins | Minimum Rating | Test Method  |

|---------------------------|------|----------------|--------------|

| Human Body Model (HBM)    | All  | ±2000V         | JS-001-2017  |

| Charge Device Model (CDM) | All  | ±1000V         | JESD22-C101F |

Table 3-3. Surge Protection

| Standard         | Application       | Minimum Rating                    |

|------------------|-------------------|-----------------------------------|

| IEC61000-4-5 Ed3 | Common mode       | 1 kV, 2 kV, 4 kV, 6 kV, and 10 kV |

| ITU-T K.21 2019  | Common mode       | 2.5 kV, 4 kV, and 6 kV            |

|                  | Differential mode | 2.5 kV and 6 kV                   |

| EN55024 2010     | Common mode       | 1 kV and 4 kV                     |

| GR1089 Issue 6   | Common mode       | 1 kV and 2.5 kV                   |

|                  | Differential mode | 1 kV                              |

**Note:** Device meets 2 kV per IEC-61000-4-5 without need for additional surge protection components. Consult Microchip for recommended protection circuitry for enhanced surge capability.

## 3.3 Recommended Operating Conditions

The following table lists the recommended operating conditions.

Table 3-4. Recommended Operating Conditions

| Parameter                                 | Conditions                                                         | Min. | Тур.              | Max. | Units |

|-------------------------------------------|--------------------------------------------------------------------|------|-------------------|------|-------|

| Junction temperature                      | _                                                                  | -40  | _                 | 125  | °C    |

| Ambient temperature                       | _                                                                  | -40  | _                 | 85   | °C    |

| V <sub>MAIN</sub>                         | Type 1: Reference to AGND                                          | 44   | _                 | 57   | V     |

|                                           | Type 2, 3: Reference to AGND                                       | 50   | _                 | 57   | V     |

|                                           | Type 4: Reference to AGND                                          | 52   | _                 | 57   | V     |

| V <sub>MAIN_7</sub> /V <sub>MAIN_36</sub> | Reference to AGND                                                  | _    | V <sub>MAIN</sub> | _    | V     |

| V <sub>MAIN</sub> slew rate               | $V_{MAIN}$ = 0V to 57V<br>$V_{DD}$ may be either present or absent | _    | _                 | 1.0  | V/µs  |

| $V_{DD}$                                  | Reference to DGND                                                  | 3.0  | 3.3               | 3.6  | V     |

| $V_{DDA}$                                 | Reference to AGND                                                  | 3.0  | 3.3               | 3.6  | V     |

| DGND-AGND voltage difference              | _                                                                  | -0.3 | _                 | 0.3  | ٧     |

#### 3.4 Electrical Characteristics

If not specified under conditions, the minimum and maximum ratings listed in the following table apply to the entire specified operating ratings of the device. Typical values stated are either by design or by production testing at 25  $^{\circ}$ C ambient.

The following tables list the electrical characteristics of the device.

**Table 3-5.** Current and Power Consumption

| Parameter                                            | Symbol               | Conditions                                                                       | Min. | Тур. | Max. | Units |

|------------------------------------------------------|----------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>MAIN</sub> current                            | I <sub>MAIN</sub>    | Ports on, normal operation. $V_{MAIN} > 12V$ .                                   | _    | _    | 1.5  | mA    |

|                                                      |                      | $0V < V_{MAIN} \le 8V$ , $V_{DD}$ , $V_{DDA}$ not present. IC is non-operational | -    | -    | 100  | μΑ    |

| V <sub>DD</sub> rail + V <sub>DDA</sub> rail current | $I_{VDD} + I_{VDDA}$ | $V_{MAIN} = 55V, V_{DD} = V_{DDA} = 3.6V$                                        | _    | _    | 30   | mA    |

Table 3-6. Port Characteristics

| Parameter                         | Symbol                 | Conditions                                                                                                                                                                       | Min.  | Тур.  | Max. | Units |

|-----------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|-------|

| Port supported continuous current | I <sub>PORT_CONT</sub> | <ul> <li>Single-Signature PD</li> <li>V<sub>MAIN</sub> = 52V, port not in current limit</li> <li>Class 8 with P<sub>CLASS_PD</sub> = 99.7W</li> <li>Maximum unbalance</li> </ul> | 1.185 | _     | _    | A     |

| Power dissipation                 | P <sub>DISS</sub>      | All ports 4P Class 8 power (90W) $V_{MAIN} = 52V V_{DD} = V_{DDA} = 3.3V$                                                                                                        | _     | _     | 2.0  | W     |

| Total channel resistance          | R <sub>CH_ON</sub>     | $T_A \le 85$ °C, $T_J \le 125$ °C                                                                                                                                                | _     | 0.160 | _    | Ω     |

| Port resistance                   | R <sub>CH_OFF</sub>    | $R_{PORT}$ connected, $T_{J}$ = 25 °C $V_{PORT}$ < 30V                                                                                                                           | 50    | 60    | 70   | kΩ    |

|                                   |                        | $R_{PORT}$ disconnected, $T_J = 25$ °C                                                                                                                                           | _     | 1.8   | _    | ΜΩ    |

| V <sub>PORT</sub> leakage         | I <sub>LEAKAGE</sub>   | V <sub>PORT_NEGx</sub> to AGND                                                                                                                                                   | _     | _     | 5    | μΑ    |

| Port capacitance                  | C <sub>PSE</sub>       | <b>Required:</b> External X7R port capacitance (typical capacitor values)                                                                                                        | 47    | 100   | 220  | nF    |

|                                   | C <sub>PD</sub>        | Supported PD capacitance for IEEE* 802.3bt compliant detection                                                                                                                   | 50    | _     | 150  | nF    |

|                                   |                        | Supported PD capacitance, non-compliant PD detection                                                                                                                             | 0.05  | _     | 12.8 | μF    |

|                                   |                        | Supported PD capacitance, inrush phase                                                                                                                                           | 5     | _     | 432  | μF    |

| Supported output power            | P <sub>PORT4P</sub>    | 2 ports power, connected to a single-signature PD, V <sub>MAIN</sub> = 52V                                                                                                       | _     | _     | 100  | W     |

Table 3-7. Current Limit (I<sub>LIM</sub>)

| Parameter            | Symbol                | Conditions                                                         | Min.  | Тур.  | Max.  | Units |

|----------------------|-----------------------|--------------------------------------------------------------------|-------|-------|-------|-------|

| Port current limit   | I <sub>LIM</sub>      | Class 0-Class 3, 2-pair single signature                           | _     | 0.720 | _     | Α     |

|                      |                       | Class 4, 2-pair single signature                                   | _     | 0.850 | _     | Α     |

|                      |                       | Class 4, 4-pair dual signature                                     | _     | 0.850 | _     | Α     |

|                      |                       | Class 5, 4-pair single signature                                   | _     | 0.850 | _     | Α     |

|                      |                       | Class 6, 4-pair single signature                                   | _     | 0.890 | _     | Α     |

|                      |                       | Class 7, 4-pair single signature                                   | _     | 1.000 | _     | Α     |

|                      |                       | Class 8, 4-pair single signature<br>Class 5, 4-pair dual signature | _     | 1.200 | _     | Α     |

| Inrush current limit | I <sub>INRUSH_B</sub> | I <sub>LIM</sub> setting I <sub>LIM_2P_B</sub>                     | 0.400 | 0.425 | 0.450 | Α     |

Table 3-8. Power Accuracy

| Parameter                            | Conditions                      | Min.  | Тур. | Max. |

|--------------------------------------|---------------------------------|-------|------|------|

| Single port (2 pairs) power accuracy | Port power: 5W to 15W           | -5.0% | _    | 5.0% |

|                                      | Port power: 15W to 55W          | -2.5% | _    | 2.5% |

| 2 ports (4 pairs) power accuracy     | Total 4-pair power: 5W to 30W   | -5.0% | _    | 5.0% |

|                                      | Total 4-pair power: 30W to 100W | -2.5% | _    | 2.5% |

**Table 3-9.** Detection and Connection Check

| Parameter                          | Symbol             | Conditions | Min. | Тур. | Max. | Units |

|------------------------------------|--------------------|------------|------|------|------|-------|

| Accept signature resistance        | R <sub>DET</sub>   | _          | 17   | 25   | 29   | kΩ    |

| Accept signature capacitance       | C <sub>DET</sub>   | _          | _    | _    | 0.15 | μF    |

| Reject signature resistance (low)  | R <sub>REJ</sub>   | _          | _    | _    | 15   | kΩ    |

| Reject signature resistance (high) | R <sub>REJ</sub>   | _          | 33   | _    | _    | kΩ    |

| Reject signature capacitance       | C <sub>REJ</sub>   | _          | 10   | _    | _    | μF    |

| Detection open circuit resistance  | R <sub>OC</sub>    | _          | 0.5  | _    | _    | ΜΩ    |

| Valid detection test voltage       | V <sub>VALID</sub> | _          | 2.8  | _    | 10   | V     |

| Detection open circuit voltage     | V <sub>OC</sub>    | _          |      |      | 30   | ٧     |

| Total detection timing             | T <sub>DET</sub>   | _          | _    | _    | 400  | ms    |

Table 3-10. Classification

| Parameter                          | Symbol             | Conditions        | Min. | Тур. | Max. | Units |

|------------------------------------|--------------------|-------------------|------|------|------|-------|

| Measured I <sub>CLASS</sub> at PSE | I <sub>CLASS</sub> | Class Signature 0 | 0    | _    | 5    | mA    |

|                                    |                    | Class Signature 1 | 8    | _    | 13   | mA    |

|                                    |                    | Class Signature 2 | 16   | _    | 21   | mA    |

|                                    |                    | Class Signature 3 | 25   | _    | 31   | mA    |

|                                    |                    | Class Signature 4 | 35   | _    | 45   | mA    |

Table 3-11. Real-Time Protection

| Parameter                                                  | Symbol                   | Conditions                                                            | Min. | Тур. | Max. | Units |

|------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------|------|------|------|-------|

| Short Circuit<br>Protection (SCP)<br>disconnection<br>time | T <sub>SCP</sub>         | Port in current limit,<br>V <sub>PORT</sub> < 40V, no bouncing        | _    | 100  | _    | μs    |

| Overload protection (T <sub>LIM</sub> )                    | T <sub>LIM_2P</sub>      | Port in current limit, V <sub>PORT</sub> ≥ 40V<br>Class 1 to Class 6  | _    | 11   | _    | ms    |

|                                                            |                          | Port in current limit, V <sub>PORT</sub> ≥ 40V<br>Class 7 and Class 8 | _    | 7    | _    | ms    |

| Port MPS current                                           | I <sub>MPS</sub>         | SSPD, Class 1–4, 4P operation                                         | 2.0  | 3.5  | 5.0  | mA    |

| threshold                                                  |                          | SSPD, Class 1–4, 2P operation                                         | 5.0  | 7.0  | 9.0  | mA    |

|                                                            |                          | SSPD, Class 5–8, 4P operation                                         | 2.0  | 4.5  | 7.0  | mA    |

|                                                            |                          | DSPD                                                                  | 2.0  | 4.5  | 7.0  | mA    |

| MPS on time detection                                      | T <sub>MPS</sub>         | _                                                                     | _    | _    | 6    | ms    |

| MPS off time                                               | T <sub>MPDO</sub>        | _                                                                     | 340  | 356  | 372  | ms    |

| Port OVT protection                                        | Reference<br>temperature | Temperature above which the OVT protection is active                  | _    | _    | 150  | °C    |

**Table 3-12.**  $I_{\text{CUT}}$  and  $T_{\text{CUT}}$  Specifications

| Parameter                        | Symbol              | Conditions                                                                              | Min. | Тур.  | Max. | Units |

|----------------------------------|---------------------|-----------------------------------------------------------------------------------------|------|-------|------|-------|

| I <sub>CUT</sub> threshold       | I <sub>CUT_2P</sub> | 44V < V <sub>MAIN</sub> < 57V<br>Class 0–3                                              | _    | 0.375 | _    | A     |

|                                  |                     | 50V < V <sub>MAIN</sub> < 57V<br>Class 4 SSPD 2P operation                              | _    | 0.644 | _    | Α     |

|                                  |                     | 50V < V <sub>MAIN</sub> < 57V<br>Class 5 SSPD 4P operation                              | _    | 0.700 | _    | А     |

|                                  |                     | 52V < V <sub>MAIN</sub> < 57V<br>Class 6 SSPD 4P operation                              | _    | 0.800 | _    | Α     |

|                                  |                     | 52V < V <sub>MAIN</sub> < 57V<br>Class 7 SSPD 4P operation                              | _    | 0.900 | _    | Α     |

|                                  |                     | 52V < V <sub>MAIN</sub> < 57V<br>Class 8 SSPD 4P operation<br>Class 5 DSPD 4P operation | _    | 1.090 | -    | Α     |

| T <sub>CUT</sub> disconnect time | T <sub>CUT_2P</sub> | _                                                                                       | _    | 65    | _    | ms    |

### Table 3-13. Inrush (Power-Up) Phase

| Parameter                                       | Symbol              | Conditions                                         | Min. | Тур. | Max. | Units |

|-------------------------------------------------|---------------------|----------------------------------------------------|------|------|------|-------|

| Inrush time                                     | T <sub>INRUSH</sub> | Per port<br>V <sub>MAIN</sub> = 57V                | _    | 65   | _    | ms    |

|                                                 |                     | $I_{INRUSH\_2P} = 0.425A$                          |      |      |      |       |

| Number ports<br>for<br>simultaneous<br>power-up | N <sub>PORT</sub>   | Power-up to maximum capacitor of 360 $\mu$ F + 20% | _    | _    | 8    | Ports |

#### Table 3-14. UVLO

| Parameter                          | Symbol                    | Conditions                                                                                           | Min. | Тур. | Max. | Unit |

|------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|------|------|------|------|

| VMAIN_UVLO Threshold voltage       | V <sub>MAIN_UVLO_F</sub>  | Threshold level below which ports are turned OFF. $\rm V_{\rm MAIN}$ falling.                        | 29.5 | 30   | 30.5 | V    |

|                                    | V <sub>MAIN_UVLO_R</sub>  | Threshold level above which ports are operational. $\ensuremath{V_{\text{MAIN}}}$ rising.            | 39.4 | 40   | 40.6 | ٧    |

| VMAIN_UVLO ports off response time | t <sub>VMAIN_UVLO_F</sub> | Time between $\rm V_{MAIN}$ falling below VMAIN_UVLO_F and ports turned off. $\rm V_{MAIN}$ falling. | 8    | _    | 24   | ms   |

#### **Table 3-15.** I<sup>2</sup>C

| Parameter                  | Symbol           | Conditions                              | Min. | Тур. | Max. | Units |

|----------------------------|------------------|-----------------------------------------|------|------|------|-------|

| I <sup>2</sup> C SCL clock | f <sub>SCL</sub> | Standard, Fast, and Fast Plus modes are | _    | _    | 1    | MHz   |

| frequency                  |                  | supported.                              |      |      |      |       |

### **Table 3-16.** External Current Reference Resistor I<sub>REF</sub>

| Parameter                                                                            | Symbol                  | Conditions                                | Min. | Тур. | Max. | Units  |

|--------------------------------------------------------------------------------------|-------------------------|-------------------------------------------|------|------|------|--------|

| $ \begin{array}{ccc} I_{REF} \ resistor & I_{REF} \\ value & I_{REF\%} \end{array} $ |                         | External 0402 reference resistor value    | _    | 10   | _    | kΩ     |

|                                                                                      |                         | External 0402 reference resistor accuracy | -0.1 | _    | 0.1  | %      |

|                                                                                      | I <sub>REF_TEMPCO</sub> | Resistor temperature coefficient          | _    | 25   | 50   | ppm/°C |

## 4. Pin Descriptions

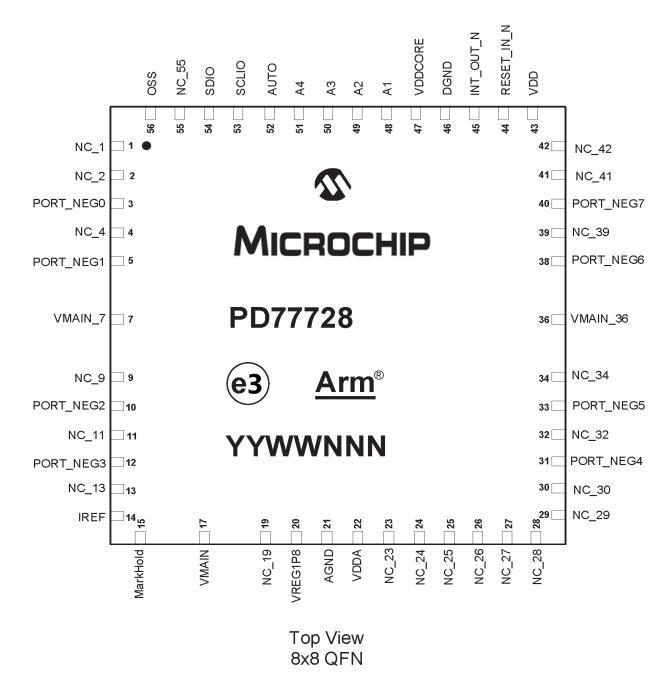

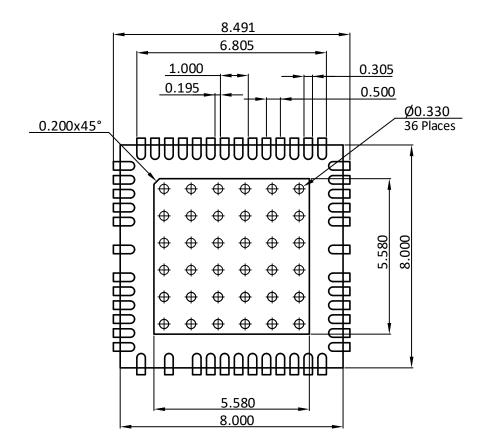

The following figure shows the device pinout.

Figure 4-1. Pinout

The following table lists the pin descriptions of the PD77728 device.

Table 4-1. Pin Descriptions

| Pin                                                                      | Designator         | Туре         | Description                                                                                                                                                                                                       |

|--------------------------------------------------------------------------|--------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 9, 11,<br>13, 19, 23, 24,<br>25, 26, 27, 28,<br>29, 30, 32, 34, | Not Connected (NC) | N/A          | NC. Leave floating.                                                                                                                                                                                               |

| 39, 41, 42, 55                                                           | WDODT NEGO         |              |                                                                                                                                                                                                                   |

| 3                                                                        | VPORT_NEG0         | Power        | Negative port 0 output                                                                                                                                                                                            |

| 5                                                                        | VPORT_NEG1         | Power        | Negative port 1 output                                                                                                                                                                                            |

| 6, 8, 16, 18, 35, 37                                                     | N/A                | N/A          | Pin removed                                                                                                                                                                                                       |

| 7                                                                        | VMAIN_7            | Power        | Connect to $V_{MAIN}$ through PCB trace or $0\Omega$ resistor for basic level protection. Leave unconnected for enhanced surge protection. See <i>PD77728 Surge Protection Application Note</i> for more details. |

| 10                                                                       | VPORT_NEG2         | Power        | Negative port 2 output                                                                                                                                                                                            |

| 12                                                                       | VPORT_NEG3         | Power        | Negative port 3 output                                                                                                                                                                                            |

| 14                                                                       | IREF               | Analog Input | Current reference resistor. Connect through 10K 0.1% to AGND.                                                                                                                                                     |

| 15                                                                       | MarkHold           | Analog Input | MarkHold input. Leave unconnected when not used.                                                                                                                                                                  |

| 17                                                                       | VMAIN              | Power        | Connect to $V_{MAIN}.$ Connect a 1 $\mu\text{F},$ 100V, X7R capacitor near each device's $V_{MAIN}$ pin.                                                                                                          |

| 20                                                                       | VREG1P8            | Power        | Internal 1.8V regulator output capacitor connection. Connect a low-ESR, 1 $\mu$ F capacitor to DGND.                                                                                                              |

| 21                                                                       | AGND               | GND          | Analog Ground. Connect to DGND through a single point connection.                                                                                                                                                 |

| 22                                                                       | VDDA               | Power        | Analog 3.3V supply. Connect a capacitor to AGND. Connected to main 3.3V supply on the board.                                                                                                                      |

| 31                                                                       | VPORT_NEG4         | Power        | Negative port 4 output                                                                                                                                                                                            |

| 33                                                                       | VPORT_NEG5         | Power        | Negative port 5 output                                                                                                                                                                                            |

| 36                                                                       | VMAIN_36           | Power        | Connect to $V_{MAIN}$ through PCB trace or $0\Omega$ resistor for basic level protection. Leave unconnected for enhanced surge protection. See <i>PD77728 Surge Protection Application Note</i> for more details. |

| 38                                                                       | VPORT_NEG6         | Power        | Negative port 6 output                                                                                                                                                                                            |

| 40                                                                       | VPORT_NEG7         | Power        | Negative port 7 output                                                                                                                                                                                            |

| 43                                                                       | VDD                | Power        | Digital 3.3V supply. Connect a capacitor to DGND. Connected to main 3.3V supply on the board.                                                                                                                     |

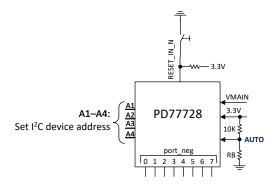

| 44                                                                       | RESET_IN_N         | Input        | Device Reset. Connect a pull-up resistor to V <sub>DD</sub> .                                                                                                                                                     |

| 45                                                                       | INT_OUT_N          | Output       | Interrupt output pin (open drain). Leave open if not used.                                                                                                                                                        |

| 46                                                                       | DGND               | GND          | Digital Ground. Connect to AGND through a single point connection.                                                                                                                                                |

| 47                                                                       | VDDCORE            | Power        | Internal 1.2V regulator output capacitor pin. Connect 1.0 $\mu\text{F}$ low ESR capacitor to DGND.                                                                                                                |

| 48                                                                       | A1                 | Input        | $\rm I^2C$ device address. Connect to $\rm V_{DD}$ or DGND.                                                                                                                                                       |

| 49                                                                       | A2                 | Input        | $\rm I^2C$ device address. Connect to $\rm V_{DD}$ or DGND.                                                                                                                                                       |

| 50                                                                       | A3                 | Input        | $\rm I^2C$ device address. Connect to $\rm V_{DD}$ or DGND.                                                                                                                                                       |

| 51                                                                       | A4                 | Input        | $\rm I^2C$ device address. Connect to $\rm V_{DD}$ or DGND.                                                                                                                                                       |

| continued |            |               |                                                                                                                                                                                                                                                   |

|-----------|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin       | Designator | Туре          | Description                                                                                                                                                                                                                                       |

| 52        | AUTO       | Input         | Connect a resistor divider comprised of a 10 k $\Omega$ resistor from V <sub>DD</sub> to AUTO pin, and a resistor from AUTO pin to DGND to select the AUTO mode configuration. See Table 5-1 for resistor selection and AUTO mode configurations. |

| 53        | SCLIO      | Bidirectional | I <sup>2</sup> C clock                                                                                                                                                                                                                            |

| 54        | SDIO       | Bidirectional | I <sup>2</sup> C data input/output                                                                                                                                                                                                                |

| 56        | OSS        | Input         | OSS is used to shut down ports based on priority settings. Connect to AGND through 10K, if unused.                                                                                                                                                |

| EPAD      | EPAD       | Analog        | Exposed Pad. Connect to AGND through short trace on PCB underneath device. AGND must have enough copper mask to ensure adequate thermal performance.                                                                                              |

## 5. Application Information

This section provides practical operation information for the PD77728 device.

### 5.1 Operational Modes

This section provides a high level description of the four available operational modes:

- Controller mode

- · Semi-Auto mode

- · Managed Auto mode

- Unmanaged Auto mode

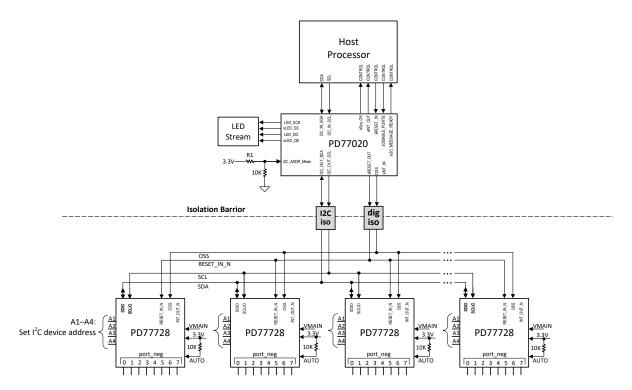

#### 5.1.1 Controller Mode

This section describes the chipset operation with PD77020 PoE Power Management Controller. The PD77020 device is used in conjunction with the PD77728 device, where the PD77020 PoE Power Management Controller provides multi-port PoE functions, such as port mapping (Port Matrix), port priority, port status, and system power management.

The following figure shows the Controller Mode application.

Figure 5-1. Controller Mode Application

#### 5.1.2 Semi-Auto Mode

In the Semi-Auto mode, the device performs periodic connection check, detection, and classification, but does not power-up the ports without a host command. Each device has initial PSE configuration containing the Port Matrix (2P/4P configuration) and stores the port investigation results in the memory for host control. The host can override these settings. In this mode, the PoE controller is responsible for the periodic or cyclic detection and classification of the ports.

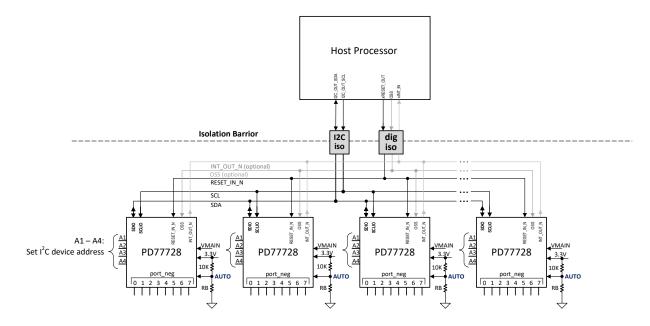

The following figure shows the Semi-Auto mode application.

Figure 5-2. Semi-Auto Mode Application

#### 5.1.3 Auto Mode

The Auto mode is an operational mode where PSE can perform the required functionality with predetermined configuration values. In this mode, the device performs connection check, detection, classification, and power-up autonomously following POR, and turning valid PoE ports ON without host intervention. A device supporting the Auto mode might either be connected to a host (Managed Auto mode) or be used as a stand-alone system without any control interface (Unmanaged Auto mode).

The following tasks are supported in the Auto mode:

- Autonomous detection, classification, power-up, and power-on ports based on configuration pins

- · Device-Level matrix configuration

#### 5.1.3.1 Managed Auto Mode

In the Managed Auto mode, the device has initial PSE configuration with which the system can be operated without the need for host communication. However, host communication allows subsequent changes to the PSE configuration.

The following figure shows the host-controlled Managed Auto mode application.

Figure 5-3. Host-Controlled Managed Auto Mode Application

#### 5.1.3.2 Unmanaged Auto Mode

In the Unmanaged Auto mode, the device is a stand-alone system. There is no host I<sup>2</sup>C communication to the device. All PSE configurations are stored within the system and are available to the device (s) without host communication. This is the typical application of a single device system. More than one device may be employed in this type of system, but each device operates interdependently of other devices.

The following figure shows the Unmanaged Auto mode application.

Figure 5-4. Unmanaged Auto Mode Application

The following table lists the values of the resistor RB that are used to set the PSE type.

Table 5-1. AUTO Pin Configuration

| Level | Level Range (V) | Mode               | RB (kΩ)        | Set Value (V) |

|-------|-----------------|--------------------|----------------|---------------|

| 0     | 0-0.278         | Class8             | 0.442          | 0.140         |

| 1     | 0.279-0.557     | Class7             | 1.47           | 0.423         |

| 2     | 0.558-0.847     | Class6             | 2.67           | 0.695         |

| 3     | 0.847-1.115     | Class5             | 4.22           | 0.979         |

| 4     | 1.115-1.393     | Class4-4P          | 6.19           | 1.262         |

| 5     | 1.394-1.693     | Class4-2P          | 8.87           | 1.551         |

| 6     | 1.694–1.951     | Class3-2P          | 12.4           | 1.827         |

| 7     | 1.951-2.23      | AUTO mode disabled | > 17.4 or open | 2.096         |

**Note:** A  $10K\Omega$  resistor from 3.3V to AUTO pin is the top resistor value, RTOP, which along with RB creates the required voltage level at AUTO pin input.

### 5.2 I<sup>2</sup>C

The port  $I^2C$  address is programmed through pins A1, A2, A3, and A4 (pins 48–51). Tie each pin to  $V_{DD}$  or DGND to set the  $I^2C$  address, as listed in the following table.

**Note:** The  $I^2C$  address is a 7-bit address.

Table 5-2. I<sup>2</sup>C Address Select

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A4 | A3 | A2 | A1 | Ports | I <sup>2</sup> C Address |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|-------|--------------------------|

| 0     0     1     0-3     0x22       4-7     0x23     0x24       0     0     1     0     0-3     0x24       4-7     0x25     0x26       0     1     1     0-3     0x26       4-7     0x27     0x27     0x27       0     1     0     0-3     0x28       4-7     0x29     0x29     0x28       0     1     0     0-3     0x2A       4-7     0x2B     0x2C       4-7     0x2D     0x2D       0     1     1     0-3     0x2E       4-7     0x2F       1     0     0-3     0x3C       4-7     0x31     0x3C       1     0     0-3     0x3C       4-7     0x33     0x3C       1     0     0-3     0x3C       4-7     0x35     0x3C       1     0     0-3     0x3C       4-7     0x3B     0x3C       4-7     0x3B       1     0     0-3     0x3C       4-7     0x3B       1     0     0-3     0x3C       4-7     0x3B       1     0     0-3     0                                                | 0  | 0  | 0  | 0  | 0-3   | 0x20                     |

| 0 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |    |    |    | 4-7   | 0x21                     |

| 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0  | 0  | 0  | 1  | 0-3   | 0x22                     |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |    |    |    | 4-7   | 0x23                     |

| 0     0     1     1     0-3     0x26       4-7     0x27       0     1     0     0-3     0x28       4-7     0x29     0     0-3     0x2A       0     1     0     0-3     0x2B       0     1     1     0-3     0x2E       4-7     0x2D     0     0-3     0x2E       1     1     1     0-3     0x2E       4-7     0x31     0x30       1     0     0     0-3     0x30       4-7     0x31     0x31       1     0     0     0-3     0x32       4-7     0x33     0x32       4-7     0x33       1     0     0-3     0x34       4-7     0x35       1     0     0-3     0x36       4-7     0x37       1     0     0-3     0x36       4-7     0x39       1     0     0-3     0x36       4-7     0x39       1     0     0-3     0x36       4-7     0x38       1     0     0-3     0x36       4-7     0x38       1     0     0     0-3     0x3                                                         | 0  | 0  | 1  | 0  | 0-3   | 0x24                     |

| 0     1     0     0     0-3     0x28       0     1     0     0     0-3     0x28       4-7     0x29       0     1     0-3     0x2A       4-7     0x2B       0     1     0     0-3     0x2C       4-7     0x2D       0     1     0     0-3     0x2E       4-7     0x2F       1     0     0     0-3     0x3C       4-7     0x31       1     0     1     0-3     0x3C       4-7     0x33       1     0     1     0-3     0x3A       1     0     1     0-3     0x36       4-7     0x35     0x36       1     0     0-3     0x36       4-7     0x37     0x37       1     1     0     0-3     0x38       4-7     0x39       1     1     0     0-3     0x3A       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B     0x3C       4-7     0x3D     0x3C                                                               |    |    |    |    | 4-7   | 0x25                     |

| 0     1     0     0     0-3     0x28       4-7     0x29       0     1     0-3     0x2A       4-7     0x2B       0     1     0     0-3     0x2C       4-7     0x2D       0     1     0     0-3     0x2E       4-7     0x2F       1     0     0     0-3     0x3C       4-7     0x31       1     0     0     0-3     0x3C       4-7     0x33       1     0     1     0-3     0x3A       1     0     1     0-3     0x3G       4-7     0x35       1     0     0-3     0x3G       4-7     0x37       1     0     0-3     0x3A       4-7     0x39       1     1     0     0-3     0x3A       4-7     0x3B       1     1     0     0-3     0x3A       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B     0x3C       4-7     0x3D     0x3C                                                                          | 0  | 0  | 1  | 1  | 0-3   | 0x26                     |

| 0     1     0     1     0-3     0x2A       0     1     0-3     0x2B       0     1     0     0-3     0x2C       4-7     0x2D       0     1     1     0-3     0x2E       4-7     0x2F       1     0     0     0-3     0x30       4-7     0x31       1     0     0     0-3     0x32       4-7     0x33       1     0     1     0-3     0x34       4-7     0x35       1     0     1     0-3     0x36       4-7     0x37       1     0     0-3     0x36       4-7     0x37       1     0     0-3     0x38       4-7     0x39       1     0     0-3     0x3A       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B       1     0     0     0-3     0x3C       4-7     0x3B <td< td=""><td></td><td></td><td></td><td></td><td>4-7</td><td>0x27</td></td<> |    |    |    |    | 4-7   | 0x27                     |

| 0 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0  | 1  | 0  | 0  | 0-3   | 0x28                     |

| 0     1     1     0     0-3     0x2C       4-7     0x2D       0     1     1     0-3     0x2E       4-7     0x2F       1     0     0     0-3     0x30       1     0     0     0-3     0x30       1     0     0     1     0-3     0x31       1     0     0     0-3     0x31       1     0     1     0-3     0x33       1     0     1     0-3     0x34       4-7     0x35       1     0     0-3     0x36       4-7     0x37       1     0     0-3     0x38       4-7     0x39       1     0     0-3     0x3A       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3D       1     1     1     0-3     0x3C       4-7     0x3D                                                                                                                                                                                                                                             |    |    |    |    | 4–7   | 0x29                     |

| 0     1     1     0     0-3     0x2C       4-7     0x2D       0     1     1     0-3     0x2E       4-7     0x2F       1     0     0     0-3     0x30       1     0     0     4-7     0x31       1     0     0     1     0-3     0x32       1     0     1     0     0-3     0x34       4-7     0x35       1     0     1     0-3     0x36       4-7     0x37       1     1     0     0-3     0x38       4-7     0x39       1     1     0     1     0-3     0x3A       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3D       1     1     1     0-3     0x3C       4-7     0x3D                                                                                                                                                                                                                                                                                         | 0  | 1  | 0  | 1  | 0-3   | 0x2A                     |

| 0     1     1     1     0-3     0x2E       1     1     1     0-3     0x2F       1     0     0     0-3     0x30       1     0     0     0-3     0x31       1     0     0     1     0-3     0x32       4-7     0x33     0x34       4-7     0x35       1     0     1     0-3     0x36       4-7     0x37       1     1     0     0-3     0x38       4-7     0x39       1     1     0     0-3     0x3A       4-7     0x3B       1     1     0     0-3     0x3C       4-7     0x3B       1     1     1     0     0-3     0x3C       4-7     0x3B       1     1     1     0     0-3     0x3C       4-7     0x3D     0x3C                                                                                                                                                                                                                                                                       |    |    |    |    | 4–7   | 0x2B                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0  | 1  | 1  | 0  | 0-3   | 0x2C                     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |    |    |    | 4–7   | 0x2D                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0  | 1  | 1  | 1  | 0-3   | 0x2E                     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |    |    |    | 4–7   | 0x2F                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  | 0  | 0  | 0  | 0-3   | 0x30                     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |    |    |    | 4–7   | 0x31                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  | 0  | 0  | 1  | 0-3   | 0x32                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |    |    |    |       | 0x33                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  | 0  | 1  | 0  |       | 0x34                     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |    |    |    | 4-7   | 0x35                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  | 0  | 1  | 1  |       | 0x36                     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |    |    |    | 4–7   | 0x37                     |

| 1 1 0 1 0 1 0-3 0x3A 0x3B 1 1 0-3 0x3B 1 1 1 0 0 0x3B 1 1 1 0 0 0x3C 0x3C 0x3D 1 1 1 1 1 1 0-3 0x3E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1  | 1  | 0  | 0  | 0-3   | 0x38                     |