#### **FEATURES**

- Frequency Range 10MHz to 134 MHz

- Output Options:

- 5 outputs PL123-05

- o 9 outputs PL123-09

- Zero input output delay

- Optional Drive Strength:

Standard (8mA) *PL123-05/-09* High (12mA) *PL123-05H/-09H*

- 3.3V, ±10% operation

- Available in Commercial and Industrial temperature ranges

- Available in 16-Pin SOP or TSSOP (PL123-09), and 8-Pin SOP (PL123-05) packages

### DESCRIPTION

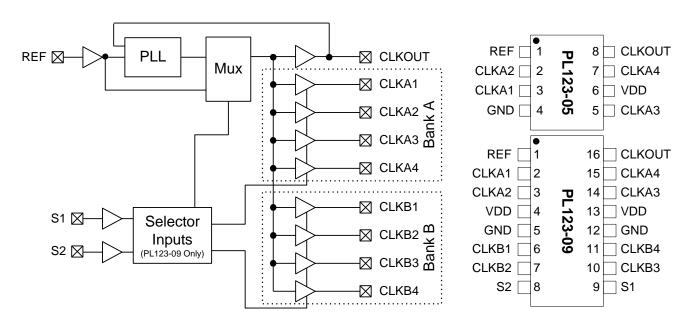

The PL123-05/-09 (-05H/-09H for High Drive) are high performance, low skew, low jitter zero delay buffers designed to distribute high speed clocks. They have one (PL123-05) or two (PL123-09) low-skew output banks, of 4 outputs each, that are synchronized with the input. The PL123-09 allows control of the banks of outputs by using the S1 and S2 inputs as shown in the Selector Definition table on page 2.

The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than  $\pm 100 ps$ , the device acts as a zero delay buffer. The input output propagation delay can be advanced or delayed by adjusting the load on the CLKOUT pin.

These parts are not intended for 5V input-tolerant applications.

#### **BLOCK DIAGRAM**

#### **PIN DESCRIPTIONS**

| Nama                  | PL123-09  |         | PL123-05 | Tuma | December 1                                            |

|-----------------------|-----------|---------|----------|------|-------------------------------------------------------|

| Name                  | TSSOP-16L | SOP-16L | SOP-8L   | Type | Description                                           |

| REF <sup>[1]</sup>    | 1         | 1       | 1        | I    | Input reference frequency.                            |

| CLKA1 <sup>[2]</sup>  | 2         | 2       | 3        | 0    | Buffered clock output, Bank A                         |

| CLKA2 <sup>[2]</sup>  | 3         | 3       | 2        | 0    | Buffered clock output, Bank A                         |

| VDD                   | 4,13      | 4,13    | 6        | Р    | VDD connection                                        |

| GND                   | 5,12      | 5,12    | 4        | Р    | GND connection                                        |

| CLKB1 <sup>[2]</sup>  | 6         | 6       | -        | 0    | Buffered clock output, Bank B                         |

| CLKB2 <sup>[2]</sup>  | 7         | 7       | -        | 0    | Buffered clock output, Bank B                         |

| S2 <sup>[3]</sup>     | 8         | 8       | -        | I    | Selector input                                        |

| S1 <sup>[3]</sup>     | 9         | 9       | -        | 1    | Selector input                                        |

| CLKB3 <sup>[2]</sup>  | 10        | 10      | -        | 0    | Buffered clock output, Bank B                         |

| CLKB4 <sup>[2]</sup>  | 11        | 11      | -        | 0    | Buffered clock output, Bank B                         |

| CLKA3 <sup>[2]</sup>  | 14        | 14      | 5        | 0    | Buffered clock output, Bank A                         |

| CLKA4 <sup>[2]</sup>  | 15        | 15      | 7        | 0    | Buffered clock output, Bank A                         |

| CLKOUT <sup>[2]</sup> | 16        | 16      | 8        | 0    | Buffered clock output. Internal feedback on this pin. |

Notes: 1: Weak pull-down. 2: Weak pull-down on all outputs. 3: Weak Pull-Up on S1 and S2

## **SELECTOR DEFINITION FOR PL123-09**

| <b>S2</b> | <b>S</b> 1 | CLOCK A1-A4<br>(Bank A) | CLOCK B1-B4<br>(Bank B) | CLKOUT | Output Source | PLL Shutdown |

|-----------|------------|-------------------------|-------------------------|--------|---------------|--------------|

| 0         | 0          | Three-state             | Three-state             | Driven | PLL           | N            |

| 0         | 1          | Driven                  | Three-state             | Driven | PLL           | N            |

| 1         | 0          | Driven                  | Driven                  | Driven | Reference     | Y            |

| 1         | 1          | Driven                  | Driven                  | Driven | PLL           | N            |

## **INPUT / OUTPUT SKEW CONTROL**

The PL123-05/-09 will achieve Zero Delay from input to output when all the outputs are loaded equally. Adjustments to the input/output delay can be made by adding additional loading to the CLKOUT pin. Please contact Micrel for more information.

#### LAYOUT RECOMMENDATIONS

The following guidelines are to assist you with a performance optimized PCB design:

# Signal Integrity and Termination Considerations

- Keep traces short!

- Trace = Inductor. With a capacitive load this equals ringing!

- Long trace = Transmission Line. Without proper termination this will cause reflections (looks like ringing).

- Design long traces as "striplines" or "microstrips" with defined impedance.

- Match trace at one side to avoid reflections bouncing back and forth.

# Decoupling and Power Supply Considerations

- Place decoupling capacitors as close as possible to the VDD pin(s) to limit noise from the power supply

- Addition of a ferrite bead in series with VDD can help prevent noise from other board sources

- Value of decoupling capacitor is frequency dependant. Typical values to use are  $0.1\mu F$  for designs using frequencies < 50MHz and  $0.01\mu F$  for designs using frequencies > 50MHz.

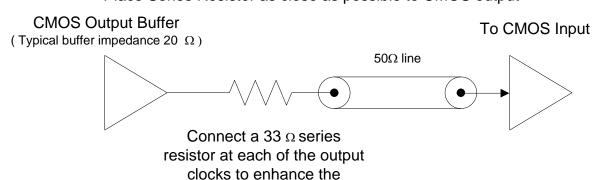

## **Typical CMOS termination**

Place Series Resistor as close as possible to CMOS output

stability of the output signal

## **ABSOLUTE MAXIMUM CONDITIONS**

| Supply Voltage to Ground Potential | l−0.5V to 4.6V                     |

|------------------------------------|------------------------------------|

| DC Input Voltage                   | $. V_{SS} - 0.5V \text{ to } 4.6V$ |

| Storage Temperature                | 65°C to 150°C                      |

| Junction Temperature            | 150°C |

|---------------------------------|-------|

| Static Discharge Voltage        |       |

| (per MIL-STD-883, Method 3015)> | 2000V |

## **OPERATING CONDITIONS**

| Parameter                        | Description                                                                                                | Min. | Max. | Unit |

|----------------------------------|------------------------------------------------------------------------------------------------------------|------|------|------|

| $V_{DD}$                         | Supply Voltage                                                                                             | 3.0  | 3.6  | V    |

| т                                | Commercial Operating Temperature (ambient temperature)                                                     | 0    | 70   | °C   |

| T <sub>A</sub> Industrial Operat | Industrial Operating Temperature (ambient temperature)                                                     | -40  | 85   | °C   |

| C                                | Load Capacitance, below 100 MHz                                                                            | _    | 30   | pF   |

| CL                               | Load Capacitance, above 100 MHz                                                                            | _    | 10   | pF   |

| C <sub>IN</sub>                  | Input Capacitance                                                                                          | _    | 7    | pF   |

| t <sub>PU</sub>                  | Power-up time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | 250  | ms   |

## **ELECTRICAL CHARACTERISTICS**

| Parameter       | Description                        | Test Conditions                                       | Min. | Max. | Unit |

|-----------------|------------------------------------|-------------------------------------------------------|------|------|------|

| V <sub>IL</sub> | Input LOW Voltage                  |                                                       | _    | 0.8  | V    |

| V <sub>IH</sub> | Input HIGH Voltage                 |                                                       | 2.5  | -    | V    |

| I <sub>IL</sub> | Input LOW Current                  | V <sub>IN</sub> = 0V                                  | _    | 50   | μA   |

| I <sub>IH</sub> | Input HIGH Current                 | $V_{IN} = V_{DD}$                                     | _    | 100  | μA   |

| V <sub>OL</sub> | Output LOW Voltage <sup>[4]</sup>  | $I_{OL} = 8 \text{ mA}$<br>$I_{OL} = 12 \text{ mA}$   | _    | 0.4  | V    |

| V <sub>OH</sub> | Output HIGH Voltage <sup>[4]</sup> | $I_{OH} = -8 \text{ mA}$<br>$I_{OL} = -12 \text{ mA}$ | 2.4  | _    | V    |

| l               | Supply Current                     | 66.67MHz with unloaded outputs Commercial Temp.       | _    | 32   | mA   |

| I <sub>DD</sub> | (Unloaded Outputs)                 | 66.67MHz with unloaded outputs Industrial Temp.       | _    | 45   | mA   |

Notes: 4. Parameter is guaranteed by design and characterization. Not 100% tested in production.

# SWITCHING CHARACTERISTICS [5]

| Parameter             | Name                                             | Test Conditions                                                        | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| 1                     | Outrat Francisco                                 | 30-pF load                                                             | 10   | _    | 100  | MHz  |

| t <sub>1</sub>        | Output Frequency                                 | 10-pF load                                                             | 10   | _    | 134  | MHz  |

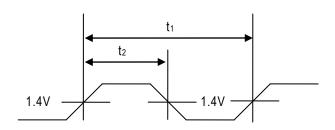

|                       | Duty Cycle [4] = t2 ÷ t1                         | Measured at 1.4V, F <sub>OUT</sub> = 66.67MHz                          | 40   | 50   | 60   | %    |

|                       | Duty Cycle [4] = t2 ÷ t1                         | Measured at 1.4V, F <sub>OUT</sub> <50MHz                              | 45   | 50   | 55   | %    |

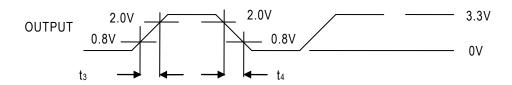

|                       | Rise Time [4]                                    | Measured between 0.8V and 2.0V                                         | _    | _    | 2.5  | ns   |

| t <sub>3</sub>        | Rise Time [4] (High Drive)                       | Measured between 0.8V and 2.0V                                         | -    | _    | 1.5  | ns   |

| 1                     | Fall Time [4]                                    | Measured between 0.8V and 2.0V                                         | _    | _    | 2.5  | ns   |

| <b>t</b> <sub>4</sub> | Fall Time [4] (High Drive)                       | Measured between 0.8V and 2.0V                                         | _    | _    | 1.5  | ns   |

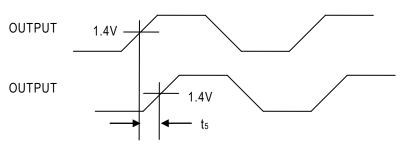

| <b>t</b> <sub>5</sub> | Output to Output Skew                            | All outputs equally loaded                                             | _    | _    | 250  | ps   |

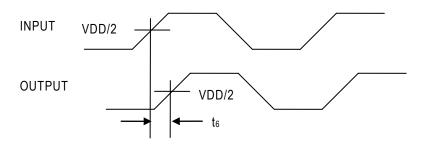

| t <sub>6A</sub>       | Delay, REF Rising Edge to CLKOUT Rising Edge [4] | Measured at VDD/2                                                      | -    | 0    | ±350 | ps   |

| t <sub>6B</sub>       | Delay, REF Rising Edge to CLKOUT Rising Edge [4] | Measured at VDD/2. Measured in PLL bypass mode, <i>PL123-09 only</i> . | 1    | 5    | 8.5  | ns   |

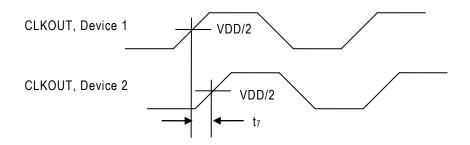

| t <sub>7</sub>        | Device to Device Skew [4]                        | Measured at VDD/2 on the CLKOUT pin                                    | _    | 0    | 700  | ps   |

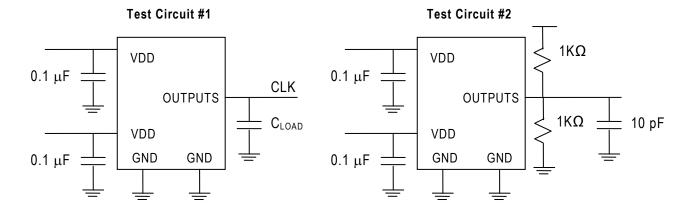

| t <sub>8</sub>        | Output Slew Rate [4]                             | Measured between 0.8V and 2.0V using Test Circuit #2                   | 1    | -    | -    | V/ns |

| tJ                    | Cycle to Cycle Jitter [4]                        | Measured at 66.67 MHz, loaded outputs                                  | _    | 75   | 200  | ps   |

| tLOCK                 | PLL Lock Time [4]                                | Stable power supply, valid clock presented on REF pin                  | -    | _    | 1    | ms   |

- 4. Parameter is guaranteed by design and characterization. Not 100% tested in production.

- 5. All parameters are specified with loaded outputs.

## **SWITCHING WAVEFORMS**

**Duty Cycle Timing**

All Outputs Rise/Fall Time

**Output-Output Skew**

**Input-Output Propagation Delay**

**Device-Device Skew**

## **TEST CIRCUITS**

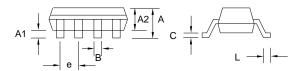

# PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

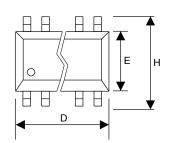

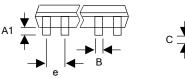

# SOP-16L and TSSOP-16L (mm)

|        | SOP  |       | TSS      | OP   |  |

|--------|------|-------|----------|------|--|

| Symbol | Min. | Max.  | Min.     | Max. |  |

| Α      | 1.35 | 1.75  | -        | 1.20 |  |

| A1     | 0.10 | 0.25  | 0.05     | 0.15 |  |

| В      | 0.33 | 0.51  | 0.19     | 0.30 |  |

| С      | 0.19 | 0.25  | 0.09     | 0.20 |  |

| D      | 9.80 | 10.00 | 4.90     | 5.10 |  |

| Е      | 3.80 | 4.00  | 4.30     | 4.50 |  |

| Н      | 5.80 | 6.20  | 6.40 BSC |      |  |

| L      | 0.40 | 1.27  | 0.45     | 0.75 |  |

| е      | 1.27 | BSC   | 0.65 BSC |      |  |

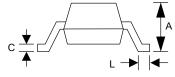

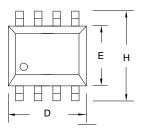

#### SOP 8L

| Symbol | Dimension in MM |      |  |

|--------|-----------------|------|--|

| Symbol | Min.            | Max. |  |

| Α      | 1.35            | 1.75 |  |

| A1     | 0.10            | 0.25 |  |

| A2     | 1.25            | 1.50 |  |

| В      | 0.33            | 0.53 |  |

| С      | 0.19            | 0.27 |  |

| D      | 4.80            | 5.00 |  |

| E      | 3.80            | 4.00 |  |

| Н      | 5.80            | 6.20 |  |

| L      | 0.40            | 0.89 |  |

| е      | e 1.27 BSC      |      |  |

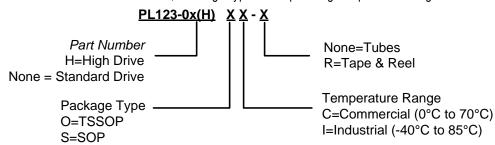

#### ORDERING INFORMATION

# For part ordering, please contact our Sales Department:

2180 Fortune Drive, San Jose, CA 95131, USA Tel: (408) 944-0800 Fax: (408) 474-1000

#### PART NUMBER

The order number for this device is a combination of the following: Part number, Package type and Operating temperature range

| Part/Order Number (Commercial) | Marking*<br>(Commercial) | Part/Order Number<br>(Industrial) | Marking*<br>(Industrial) | Package Option                  |  |

|--------------------------------|--------------------------|-----------------------------------|--------------------------|---------------------------------|--|

| PL123-05SC                     | P12305                   | PL123-05SI                        | P12305                   | 8-Pin SOP Tube                  |  |

| PL123-05SC-R                   | SC<br>LLLLL              | PL123-05SI-R                      | SI<br>LLLLL              | 8-Pin SOP (Tape<br>and Reel)    |  |

| PL123-05HSC                    | P12305H                  | PL123-05HSI                       | P12305H                  | 8-Pin SOP Tube                  |  |

| PL123-05HSC-R                  | SC<br>LLLLL              | PL123-05HSI-R                     | SI<br>LLLLL              | 8-Pin SOP (Tape<br>and Reel)    |  |

| PL123-09OC                     | P12309<br>OC             | PL123-090I                        | P12309                   | 16-Pin TSSOP<br>Tube            |  |

| PL123-09OC-R                   | LLLLL                    | PL123-090I-R                      | LLLLL                    | 16-Pin TSSOP<br>(Tape and Reel) |  |

| PL123-09HOC                    | P12309H<br>OC            | PL123-09HOI                       | P12309H                  | 16-Pin TSSOP<br>Tube            |  |

| PL123-09HOC-R                  | LLLLL                    | PL123-09HOI-R                     | LLLLL                    | 16-Pin TSSOP<br>(Tape and Reel) |  |

| PL123-09SC                     | P12309                   | PL123-09SI                        | P12309                   | 16-Pin SOP Tube                 |  |

| PL123-09SC-R                   | SC<br>LLLLL              | PL123-09SI-R                      | SI<br>LLLLL              | 16-Pin SOP (Tape and Reel)      |  |

| PL123-09HSC                    | P12309H                  | PL123-09HSI                       | P12309H                  | 16-Pin SOP Tube                 |  |

| PL123-09HSC-R                  | SC<br>LLLLL              | PL123-09HSI-R                     | SI<br>LLLLL              | 16-Pin SOP (Tape<br>and Reel)   |  |

<sup>\*</sup>Note: LLLLL designates lot number

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Buffer category:

Click to view products by Microchip manufacturer:

Other Similar products are found below:

MPC962309EJ-1H NB4N121KMNG IDT49FCT805ASO MK2308S-1HILF PL133-27GI-R NB3L02FCT2G NB3L03FCT2G

ZL40203LDG1 ZL40200LDG1 ZL40205LDG1 9FG1200DF-1LF 9FG1001BGLF ZL40202LDG1 PI49FCT20802QE SL2305SC-1T

NB7L1008MNG NB7L14MN1G PI49FCT20807QE PI6C4931502-04LIEX ZL80002QAB1 PI6C4931504-04LIEX PI6C10806BLEX

ZL40226LDG1 8T73S208B-01NLGI SY75578LMG PI49FCT32805QEX PL133-27GC-R CDCV304PWG4 MC10LVEP11DG

MC10EP11DTG MC100LVEP11DG MC100E111FNG MC100EP11DTG NB6N11SMNG NB7L14MMNG NB6L11MMNG

NB6L14MMNR2G NB6L611MNG PL123-02NGI-R NB3N111KMNR4G ADCLK944BCPZ-R7 ZL40217LDG1 NB7LQ572MNG

HMC940LC4BTR ADCLK946BCPZ-REEL7 ADCLK946BCPZ ADCLK854BCPZ ADCLK905BCPZ-R2 ADCLK905BCPZ-R7

ADCLK905BCPZ-WP