# **PL602-XX**

### **HCSL Compatible Clock Generator for PCI Express**

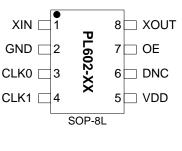

PIN CONFIGURATION

### FEATURES

- Input Frequency:

- Fundamental Crystal or Reference Input: 25MHz

- Output Frequency:

- PL602-21: 100MHz differential outputs.

- o PL602-22: 125MHz differential outputs.

- PL602-23: 200MHz differential outputs.

- PL602-26: 25MHz differential outputs.

- o PL602-27: 250MHz differential outputs.

- o PL602-15: 156.25 MHz differential outputs.

- Very low Jitter: 28ps Pk-Pk typ.

- Very low Phase Noise:

- -130 dBc at 10kHz offset at 100MHz

- No external loop filter is required

- Power supply range: 2.25V to 3.63V

- Operating temperature range from -40°C to 85°C

- Available in 6-pin SOT or 8-pin SOP Green/RoHS compliant package.

### DESCRIPTION

The PL602-XX is the smallest, high performance, lowest power differential output clock IC available for HCSL timing applications. PL602-XX offers -130dBc at 10kHz offset at 100MHz, with a very low jitter (2 ps TIE RMS), making it ideal for HCSL applications requiring small size and low power.

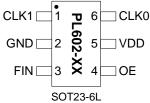

### **BLOCK DIAGRAM**

### **PIN DESCRIPTION**

| Nome     | Pin # |       | Turne | Description                                                       |  |

|----------|-------|-------|-------|-------------------------------------------------------------------|--|

| Name     | SOP   | SOT23 | Туре  |                                                                   |  |

| XIN      | 1     | -     | Ι     | Crystal input (SOP package only)                                  |  |

| FIN      | -     | 3     | Ι     | Reference clock input (SOT23 package only)                        |  |

| GND      | 2     | 2     | Р     | GND connection                                                    |  |

| CLK[0:1] | 3,4   | 1,6   | 0     | Differential clock outputs [note:CLK0=~CLK1]                      |  |

| VDD      | 5     | 5     | Р     | VDD connection                                                    |  |

| DNC      | 6     | -     | -     | Do not connect                                                    |  |

| OE       | 7     | 4     | I     | Output enable (OE) input. Internal 60K $\Omega$ pull up resistor. |  |

| XOUT     | 8     | -     | 0     | Crystal output pin.                                               |  |

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1(408) 944-0800 • fax +1(408) 474-1000 • www.micrel.com Rev 02/08/11 Page 1

## **HCSL Compatible Clock Generator for PCI Express**

### **ELECTRICAL SPECIFICATIONS**

#### ABSOLUTE MAXIMUM RATINGS

| PARAMETERS                     | SYMBOL          | MIN. | MAX.                 | UNITS |

|--------------------------------|-----------------|------|----------------------|-------|

| Supply Voltage Range           | V <sub>DD</sub> | -0.5 | 4.6                  | V     |

| Input Voltage Range            | V <sub>1</sub>  | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage Range           | Vo              | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Soldering Temperature          |                 |      | 260                  | °C    |

| Storage Temperature            | Ts              | -65  | 150                  | °C    |

| Ambient Operating Temperature* |                 | -40  | +85                  | °C    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied. \*Operating temperature is guaranteed by design. Parts are tested to commercial grade only.

### **AC SPECIFICATIONS**

| PARAMETERS                                | CONDITIONS                                                                                       | MIN. | TYP. | MAX.            | UNITS |

|-------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|-----------------|-------|

| Crystal Input Frequency                   | Fundamental Crystal                                                                              |      | 25   |                 | MHz   |

| Input (F <sub>IN</sub> ) Frequency        |                                                                                                  |      | 25   |                 | MHz   |

| Input (F <sub>IN</sub> ) Signal Amplitude | Internally AC coupled                                                                            | 0.9  |      | V <sub>DD</sub> | Vpp   |

| Output Frequency                          |                                                                                                  | 25   |      | 200             | MHz   |

| Output Enable Time                        | OE Function; Ta=25° C, Add one clock<br>period to this measurement for a usable<br>clock output. |      |      | 10              | ns    |

| Output Disable Time                       | OE Function; Ta=25° C                                                                            |      |      | 10              | ns    |

| Settling Time                             | At power-up ( $V_{DD} \ge 2.25V$ )                                                               |      |      | 10              | ms    |

| VDD Sensitivity                           | Frequency vs. V <sub>DD</sub> , ±10%                                                             | -2   |      | 2               | ppm   |

| Output Rise Time                          | 10/90%V <sub>он</sub>                                                                            |      | 0.3  | 0.5             | ns    |

| Output Fall Time                          | 90/10%V <sub>он</sub>                                                                            |      | 0.3  | 0.5             | ns    |

| Skew Between Outputs                      | Measured at 50% $V_{\text{OH}}$                                                                  |      |      | 250             | ps    |

| Duty Cycle                                | At V <sub>DD</sub> /2                                                                            | 45   | 50   | 55              | %     |

| Period Jitter, peak-to-peak               | With conscitive descupling between V                                                             |      | 28   |                 | ps    |

| Cycle-to-Cycle, RMS                       | - With capacitive decoupling between $V_{\mbox{\scriptsize DD}}$ and GND                         |      | 9    |                 | ps    |

| Cycle-to-Cycle, peak                      | - At 100MHz                                                                                      |      | 25   |                 | ps    |

| TIE, RMS                                  | - 20,000 samples measured                                                                        |      | 2    |                 | ps    |

# **HCSL Compatible Clock Generator for PCI Express**

### **DC SPECIFICATIONS**

| PARAMETERS              | SYMBOL           | CONDITIONS                   | MIN. | TYP. | MAX. | UNITS |

|-------------------------|------------------|------------------------------|------|------|------|-------|

| Supply Current, Dynamic | I <sub>DD</sub>  | At 100MHz, No Load           |      | 25   |      | mA    |

| Operating Voltage       | V <sub>DD</sub>  |                              | 2.25 |      | 3.63 | V     |

| Output Low Voltage      | V <sub>OL</sub>  | HCSL termination,            |      |      | 0.05 | V     |

| Output High Voltage     | V <sub>OH</sub>  | (RS = 150Ω, RT = 49.9Ω) 3.3V | 0.65 | 0.75 | 0.85 | V     |

| Output Current          | I <sub>OSD</sub> | (RS = 100Ω, RT = 49.9Ω) 2.5V | 13   | 15   | 17   | mA    |

### **CRYSTAL SPECIFICATIONS**

| PARAMETERS                               | SYMBOL                | MIN. | TYP. | MAX. | UNITS |

|------------------------------------------|-----------------------|------|------|------|-------|

| Fundamental Crystal Resonator Frequency  | F <sub>XIN</sub>      |      | 25   |      | MHz   |

| Crystal Loading Rating                   | C <sub>L (xtal)</sub> |      | 18   |      | pF    |

| Maximum Sustainable Drive Level          |                       |      |      | 500  | μW    |

| Operating Drive Level                    |                       |      | 100  |      | μW    |

| Crystal Shunt Capacitance                | C0                    |      |      | 6    | pF    |

| Effective Series Resistance, Fundamental | ESR                   |      |      | 45   | Ω     |

### **HCSL Compatible Clock Generator for PCI Express**

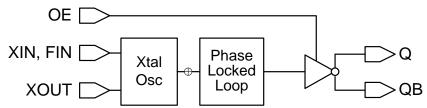

### PCI EXPRESS/HCSL COMPATIBLE LAYOUT GUIDELINES

Figure 1 below describes how to terminate the complementary LVCMOS outputs of PL602-XX for use with HCSL inputs.

LVCMOS Output

### PCB LAYOUT CONSIDERATIONS FOR PERFORMANCE OPTIMIZATION

The following guidelines are to assist you with a performance optimized PCB design:

- Keep all the PCB traces to PL602-XX as short as possible, as well as keeping all other traces as far away from it as possible.

- Place the crystal as close as possible to both crystal pins of the device. This will reduce the cross-talk between the crystal and the other signals.

- Separate crystal pin traces from the other signals on the PCB, but allow ample distance between the two crystal pin traces.

- Place a 0.01µF~0.1µF decoupling capacitor between VDD and GND, on the component side of the PCB, close to the VDD pin. It is not recommended to place this component on the backside of the PCB.

- It is highly recommended to keep the VDD and GND traces as short as possible.

- When connecting long traces (> 1 inch) to a CMOS output, it is important to design the traces as a transmission line or 'stripline', to avoid reflections or ringing. In this case, the CMOS output needs to be matched to the trace impedance. Usually 'striplines' are designed for  $50\Omega$  impedance and CMOS outputs usually have lower than  $50\Omega$  impedance so matching can be achieved by adding a resistor in series with the CMOS output pin to the 'stripline' trace.

# **PL602-XX**

# **HCSL Compatible Clock Generator for PCI Express**

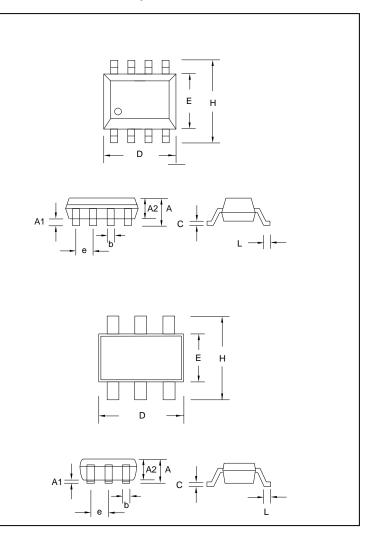

### PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

#### SOP-8L

| Symbol | Dimension in MM |      |  |  |

|--------|-----------------|------|--|--|

| Symbol | Min.            | Max. |  |  |

| Α      | 1.35            | 1.75 |  |  |

| A1     | 0.10            | 0.25 |  |  |

| A2     | 1.25            | 1.50 |  |  |

| В      | 0.33            | 0.53 |  |  |

| С      | 0.19            | 0.27 |  |  |

| D      | 4.80            | 5.00 |  |  |

| E      | 3.80            | 4.00 |  |  |

| Н      | 5.80            | 6.20 |  |  |

| L      | 0.40            | 0.89 |  |  |

| е      | 1.27 BSC        |      |  |  |

#### SOT23-6L

| Cumphal | Dimension in MM |      |  |  |

|---------|-----------------|------|--|--|

| Symbol  | Min.            | Max. |  |  |

| Α       | 1.05            | 1.35 |  |  |

| A1      | 0.05            | 0.15 |  |  |

| A2      | 1.00            | 1.20 |  |  |

| В       | 0.30            | 0.50 |  |  |

| С       | 0.08            | 0.20 |  |  |

| D       | 2.80            | 3.00 |  |  |

| E       | 1.50            | 1.70 |  |  |

| Н       | 2.60            | 3.0  |  |  |

| L       | 0.35            | 0.55 |  |  |

| е       | 0.95 BSC        |      |  |  |

**PL602-XX**

### **HCSL Compatible Clock Generator for PCI Express**

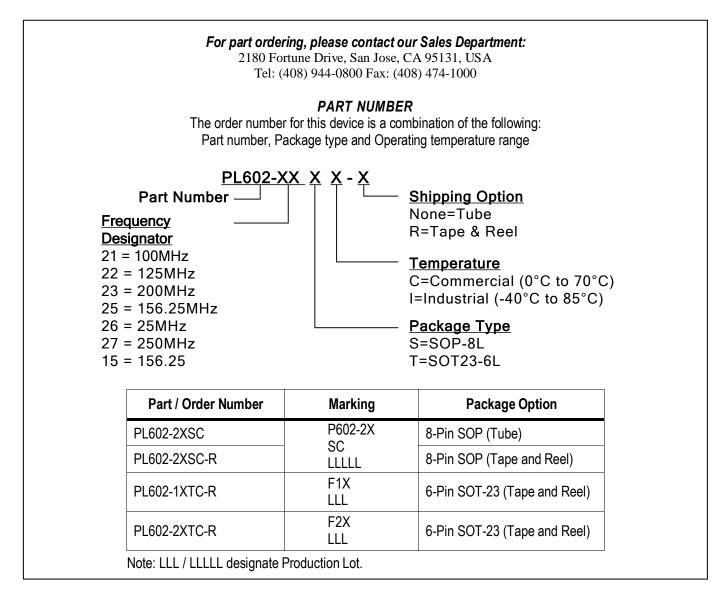

### **ORDERING INFORMATION (GREEN PACKAGE COMPLIANT)**

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Generators & Support Products category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

5P49V5901B744NLGI 5P49V5929B502NLGI 5P49V5935B520LTGI CV183-2TPAG 8T49N004A-039NLGI 9FGV0631CKLF 9FGV0641AKLFT 9LRS3197AKLF 9VRS4450AKLF NB3N51132DTR2G P1P3800AG12CRTWG 932SQ426AKLF 950810CGLF 9DBV0531AKILF 9DBV0741AKILF 9FGV0641AKLF 9UMS9633BKLF 9VRS4420DKILF 9VRS4420DKLF CY25404ZXI226 CY25422SXI-004 NB3H5150-01MNTXG 6INT61041NDG P3MS650100H-4CR P3P8203AMTTBG PL602-20-K52TC PL613-51QC 9FGV0641AKILF ZL30314GKG2 ZL30250LDG1 ZL30142GGG2 9UMS9633BKILFT 9FGV0631CKLFT 9FGV0631CKILF PI6LC48P0101LIE DS1099U-ST+ MAX24305EXG+ PI6LC48H02-01LIE 82P33814ANLG 932SQ426AGLFT 840021AGLF MAX3674ECM+ 5V49EE901-064PGGI ZL30244LFG7 DS1089LU-23C+ PI6LC48C21LE ZL30106QDG1 ZL30245LFG7 PI6LC48L0201LIE 8T49N283C-998NLGI