PM5316

# SPECTRA<sup>™</sup> 4x155

# SONET/SDH Payload Extractor/Aligner 4 x 155 Mbit/s

# **Data Sheet**

Released Issue No. 6: November 2005

# Legal Information

### Copyright

Copyright 2005 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

#### Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### Trademarks

PMC-Sierra, PMCS, PMC, SPECTRA, and TUPP are trademarks of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

## Patents

The technology discussed in this document is protected by one or more of the following patent grants:

U.S. Patent No. 5,959,490; 6,246,738. Canadian Patent No. 2,254,285; 2,245,757

Other relevant patent grants may also exist.

# **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7 Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200

PMC-SIERRA

Document Information: <u>document@pmc-sierra.com</u> Corporate Information: <u>info@pmc-sierra.com</u> Technical Support: <u>apps@pmc-sierra.com</u> Web Site: <u>http://www.pmc-sierra.com</u>

# **Revision History**

| Issue No. | Issue Date       | Details of Change                                                                                                                                                               |

|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Issue 6   | November<br>2005 | Updated ordering information including RoHS compliant device details.                                                                                                           |

| Issue 5   | September        | Update pin diagram to include reserved[1:5] and correct pin descriptions                                                                                                        |

|           | 2002             | Add Reserved5, VBIAS[1:0], QAVD[2:1], QAVS[2:1] to pin description                                                                                                              |

|           |                  | Add granted patents                                                                                                                                                             |

|           |                  | Replace all references to DISDV1 with ENDV1                                                                                                                                     |

|           |                  | Clarify apparent contradiction of IR drop across series resistors in power supply filtering diagram                                                                             |

|           |                  | Add RTAL/TTAL FIFO initialization procedure to Section 13.1                                                                                                                     |

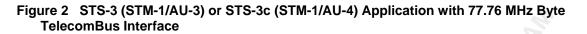

|           |                  | Correct Figure 2 to show only 8-bit TelecomBus mode                                                                                                                             |

|           |                  | Correct typographical error: change RPOHCLK nominal frequency from 12.92MHz to 12.96MHz                                                                                         |

|           |                  | Removed references to TPOH.                                                                                                                                                     |

| Issue 4   | Mar 2001         | De-documented all Transport Path Overhead port (TPOH) functionality                                                                                                             |

|           |                  | Added Overhead byte processing information in operation section.                                                                                                                |

| Issue 3   | Jan 2001         | Removed TIU2E and TIU2I register bits from registers 1n2Dh and 1n31h respectively.                                                                                              |

|           |                  | DOPJ[1:0] register bit in the TTAL block (register 1nD1h) has been removed.                                                                                                     |

|           |                  | DOPJ[1:0] register bit in the RTAL block (register 1n59h) has been redefined.                                                                                                   |

|           |                  | PRBS monitoring mode needs two bits to be programmed. Mode setting in both the DPGM (register 1n7Ah) and APGM (register 1nFAh) is now defined via two mode bits MON_GMODE[1:0]. |

|           |                  | RSOP Section B1 error counters (0m16h and Om17h registers) may also be transferred upon a write to either register.                                                             |

|           | 20               | Master test register bit 3 to 7 is defined as R/W instead of just W.                                                                                                            |

|           | Q'O'             | Pin out diagram has changed format to improve readability but the pinout remains the SAME.                                                                                      |

|           |                  | Due to clear on write auxiliary interrupts, tZint timing is specified for microprocessor writes to clear device interrupt pin.                                                  |

|           |                  | Analog supplies AVD/AVS are specified at 5% instead of 10%.                                                                                                                     |

|           |                  | Consistent naming or STM1-CONCAT to STM1_CONCAT (underscore) register bit in registers 1n00h and 1n80h.                                                                         |

|           |                  | Power supply board recommendations have been changed in section 13.8. Separate supplies are no longer recommended.                                                              |

|           |                  | Specific PECL input currents are given in section 17, D.C. Characteristics                                                                                                      |

|           |                  | RAD does not contain transmitted K1/K2 bytes under generation of AIS-L on the transmit stream.                                                                                  |

|           |                  | TAD port is limited to accumulating a maximum of 15 REI                                                                                                                         |

| Issue 2   | Sept 2000        | Additional feature explanations/ clarifications                                                                                                                                 |

|           |                  | Timing Change on drop interface in 19.44 Mhz mode                                                                                                                               |

|           |                  | Addition of register bits CONCAT, TPOH_DIS, ATSI_FORCE and ATSI_RESET                                                                                                           |

|           |                  | Definition changes of LOPCONRALM and PAISCONRALM.                                                                                                                               |

| Issue No. | Issue Date | Details of Change                          | 2  |

|-----------|------------|--------------------------------------------|----|

|           |            | Added Section describing loopbacks         | A. |

|           |            | DC Characteristics up to date and complete |    |

|           |            | Added RTC_EN register bit.                 |    |

| Issue 1   | June 2000  | Preliminary release of datasheet           | .5 |

## **Table of Contents**

| Leç  | gal Info | ormation                                                       | 2  |

|------|----------|----------------------------------------------------------------|----|

|      | Сору     | right                                                          | 2  |

|      |          | aimer                                                          |    |

|      | Trade    | emarks                                                         | 2  |

|      | Pater    | nts                                                            | 2  |

| Co   | ntactin  | ng PMC-Sierra                                                  | 2  |

| Re   | vision   | History                                                        | 4  |

| Tab  | le of C  | Contents                                                       | 6  |

| List | t of Re  | egisters                                                       | 9  |

| List | t of Fig | gures                                                          | 19 |

| List | t of Tal | bles                                                           | 21 |

| 1    | Featu    | ures                                                           |    |

|      | 1.1      | General                                                        | 23 |

|      | 1.2      | SONET Section and Line/SDH Regenerator and Multiplexer Section | 23 |

|      | 1.3      | SONET Path / SDH High Order Path                               | 24 |

|      | 1.4      | System Side Interfaces                                         | 25 |

| 2    | Appli    | cations                                                        | 26 |

| 3    | Refer    | rences                                                         | 27 |

| 4    | Docu     | ment Conventions & Definitions                                 | 28 |

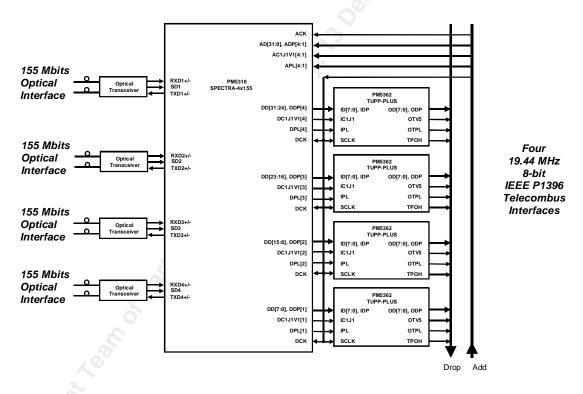

| 5    | Appli    | cation Examples                                                | 30 |

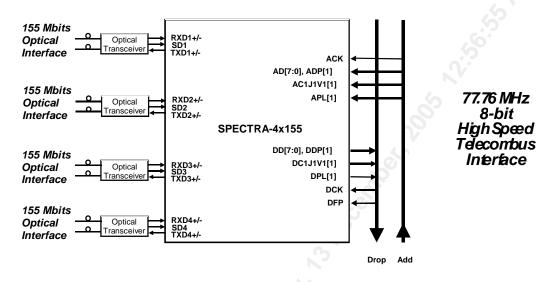

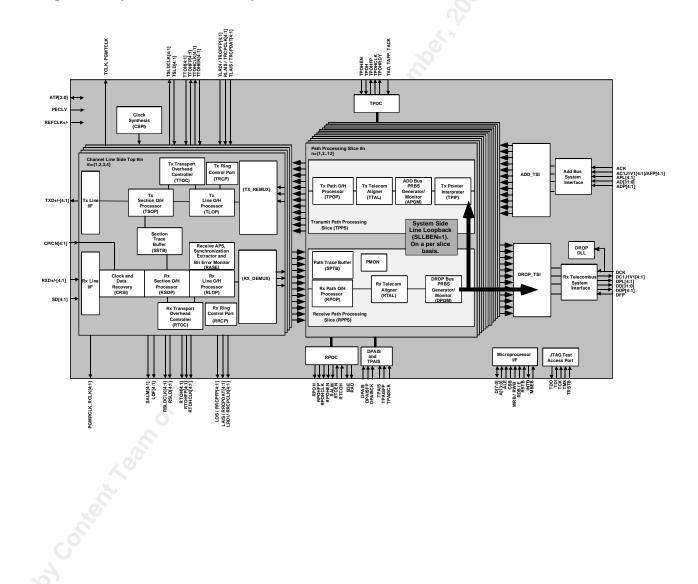

| 6    | Block    | CDiagram                                                       |    |

| 7    | Func     | tional Description                                             | 33 |

| 8    | Pin D    | Diagrams                                                       | 35 |

| 9    | Pin D    | Description (SBGA 520)                                         |    |

|      | 9.1      | Serial Line side Interface Signals                             |    |

|      | 9.2      | Section/Line/Path Status and Alarm Signals                     | 40 |

|      | 9.3      | Receive Section/Line/Path Overhead Extraction Signals          | 45 |

|      | 9.4      | Transmit Section/Line/Path Overhead Insertion Signals          |    |

|      | 9.5      | Receive Section/Line DCC Extraction Signals                    | 51 |

|      | 9.6      | Transmit Section/Line DCC Insertion Signals                    | 51 |

|      | 9.7      | Transmit Path AIS Insertion Signals                            | 52 |

|      | 9.8      | Drop Bus Telecom Interface Signals                             | 53 |

|      | 9.9      | Add Bus Telecom Interface Signals                              | 58 |

|      | 9.10     | Microprocessor Interface Signals                               | 65 |

|      |          |                                                                |    |

# PMC-SIERRA

|    | 9.11  | Analog Miscellaneous Signals                                            | 66  |

|----|-------|-------------------------------------------------------------------------|-----|

|    | 9.12  | JTAG Test Access Port (TAP) Signals                                     | 66  |

|    | 9.13  | Power and Ground                                                        | 67  |

| 10 | Func  | tional Description                                                      | 70  |

|    | 10.1  | Receive Line Interface and CRSI                                         | 70  |

|    |       | Receive Section Overhead Processor (RSOP)                               |     |

|    |       | Receive Section Trace Buffer (SSTB)                                     |     |

|    | 10.4  | Receive Line Overhead Processor (RLOP)                                  | 74  |

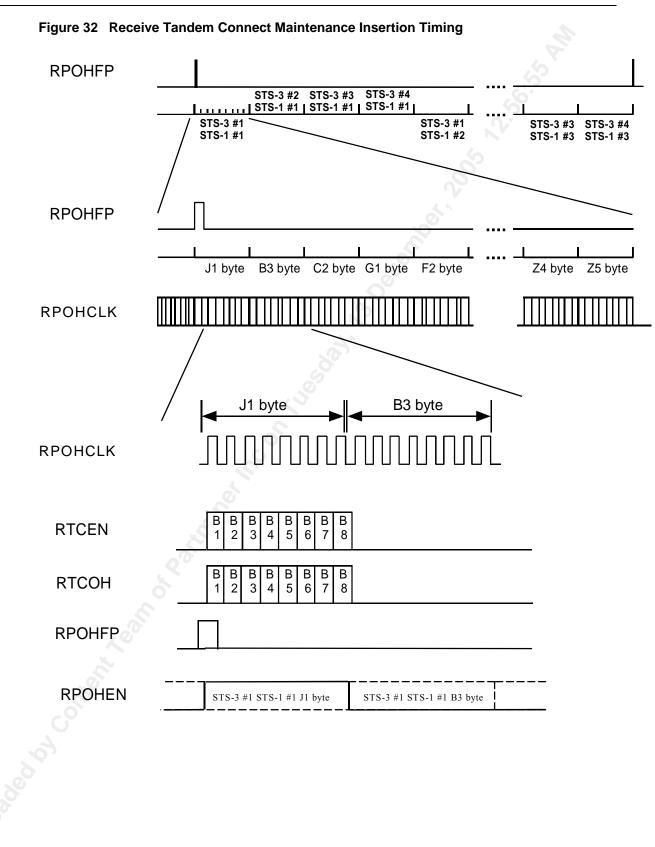

|    | 10.5  | The Receive APS, Synchronization Extractor and Bit Error Monitor (RASE) | 75  |

|    | 10.6  | Receive Transport Overhead Controller (RTOC)                            | 77  |

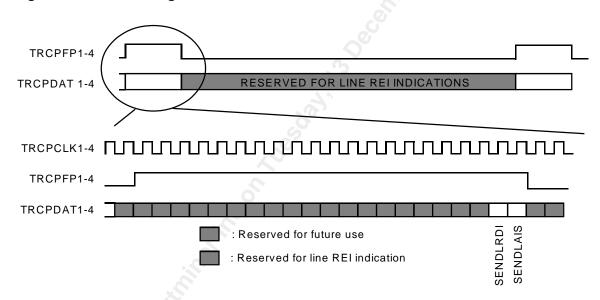

|    | 10.7  | Ring Control Port                                                       | 77  |

|    | 10.8  | Receive De-multiplexer (RX_DEMUX)                                       | 78  |

|    | 10.9  | Receive Path Processing Slice (RPPS)                                    | 78  |

|    | 10.10 | Transmit Path Processing Slice (TPPS)                                   | 91  |

|    | 10.11 | Transmit Multiplexer (TX_REMUX)                                         | 96  |

|    | 10.12 | 2 Transmit Transport Overhead Controller (TTOC)                         | 96  |

|    | 10.13 | 3 Transmit Line Overhead Processor (TLOP)                               | 98  |

|    | 10.14 | Transmit Section Overhead Processor (TSOP)                              | 99  |

|    | 10.15 | Transmit Section Trace Buffer (SSTB)                                    | 100 |

|    | 10.16 | Transmit Line Interface                                                 | 100 |

|    | 10.17 | 7 Add/Drop Bus Time-Slot Interchange (TSI)                              | 101 |

|    | 10.18 | System Side Interfaces                                                  | 102 |

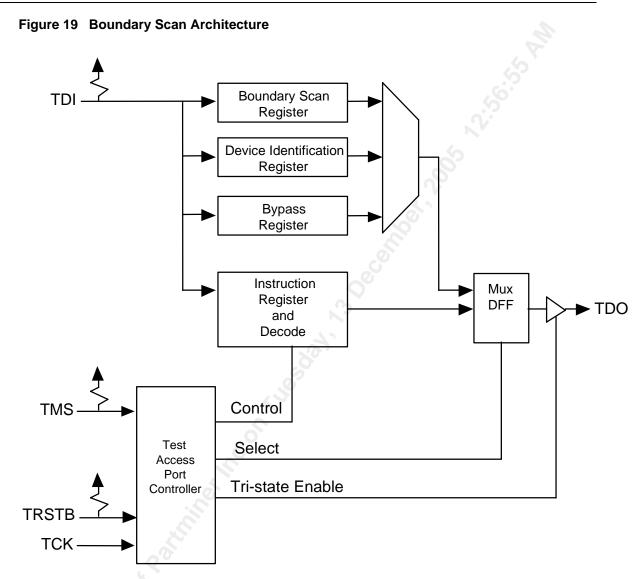

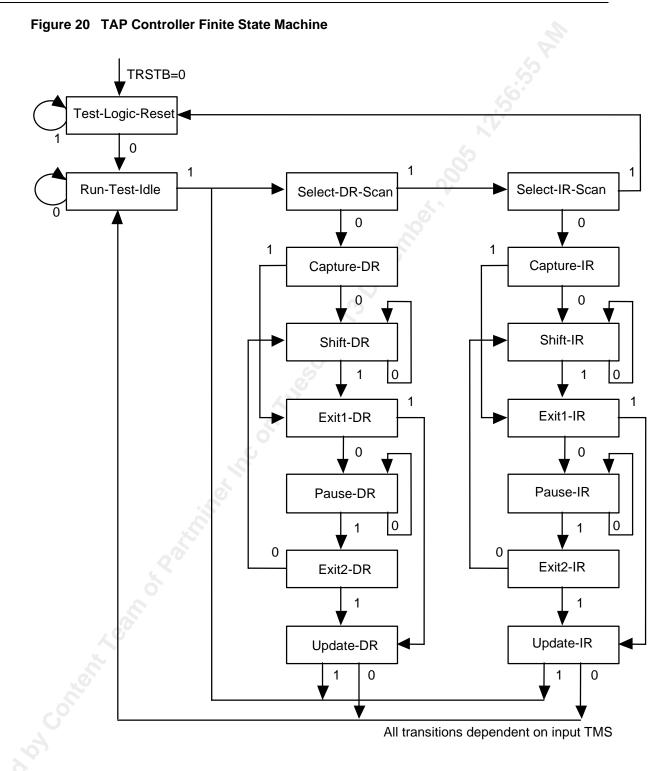

|    | 10.19 | JTAG Test Access Port Interface                                         | 103 |

|    | 10.20 | Microprocessor Interface                                                | 104 |

| 11 | Norm  | al Mode Register Description                                            | 114 |

| 12 | Test  | Features Description                                                    | 385 |

|    | 12.1  | Master Test and Test Configuration Registers                            | 385 |

|    | 12.2  | JTAG Test Port                                                          | 389 |

| 13 | Oper  | ation                                                                   | 396 |

|    | 13.1  | Software Initialization Sequence                                        | 396 |

|    | 13.2  | SONET/SDH Overhead Byte Processing                                      | 397 |

|    | 13.3  | Path Processing Slice Configuration Options                             | 403 |

|    | 13.4  | Time Slot Interchange (Grooming) Configuration Options                  | 405 |

|    | 13.5  | System Interface Configuration Options                                  | 406 |

|    | 13.6  | Bit Error Rate Monitor (BERM)                                           | 407 |

|    | 13.7  | Clocking Options                                                        | 408 |

|    |       |                                                                         |     |

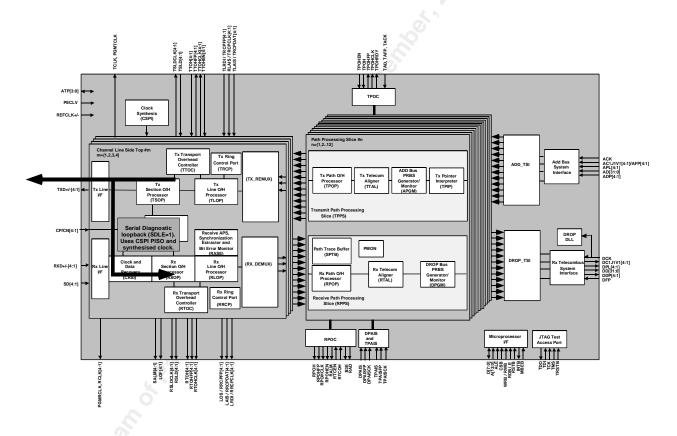

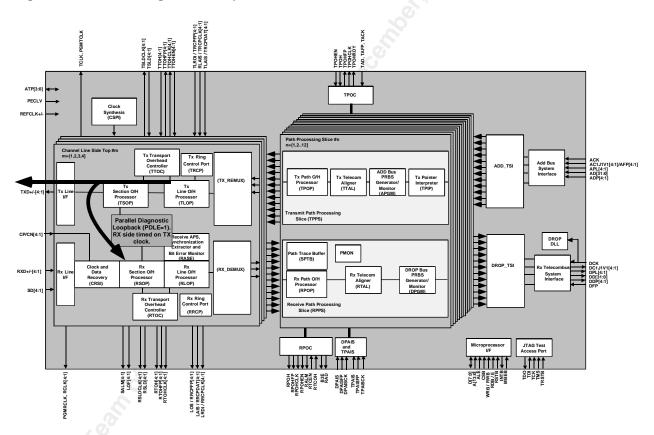

|    | 13.8 Loop Back Modes                            | 409 |

|----|-------------------------------------------------|-----|

|    | 13.9 Loop Back Operation                        | 413 |

|    | 13.10 JTAG Support                              | 414 |

|    | 13.11 Board Design Recommendations              | 419 |

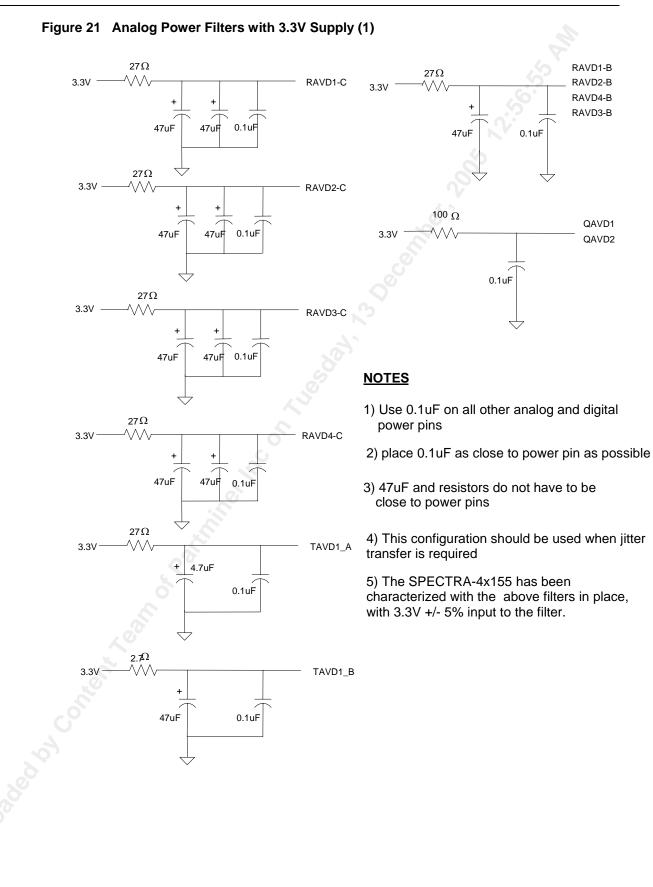

|    | 13.12 Analog Power Supply Filtering             | 420 |

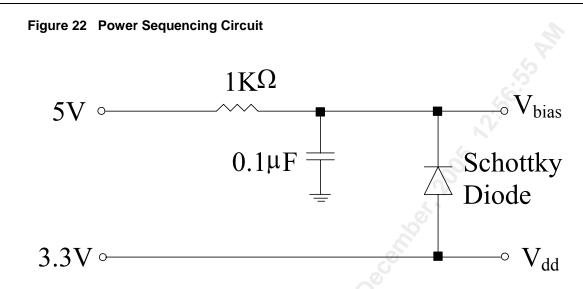

|    | 13.13 Power Supplies Sequencing                 | 422 |

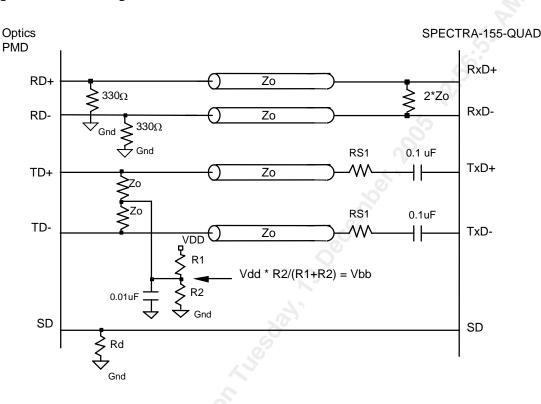

|    | 13.14 Interfacing to ECL or PECL Devices        | 423 |

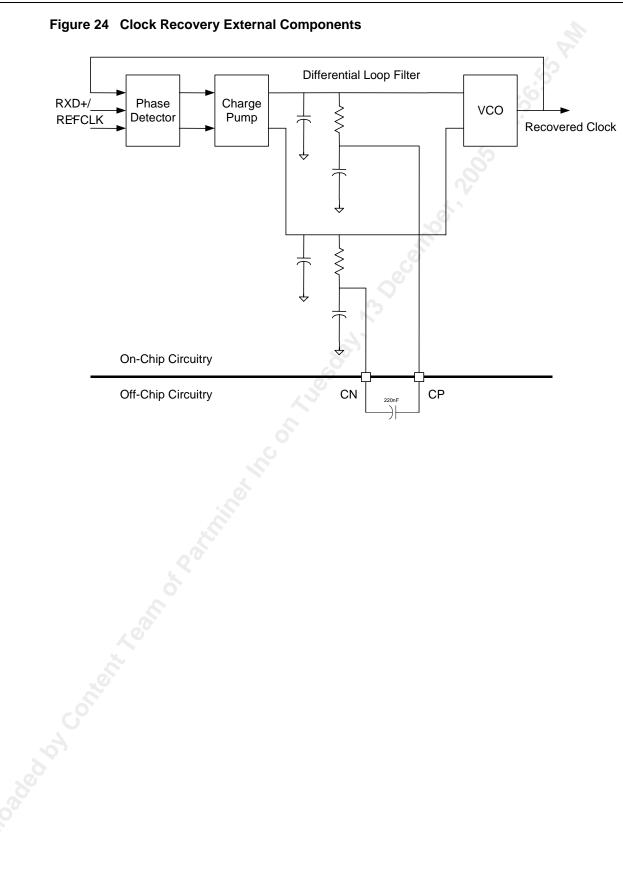

|    | 13.15 Clock Recovery                            | 424 |

| 14 | Functional Timing                               | 426 |

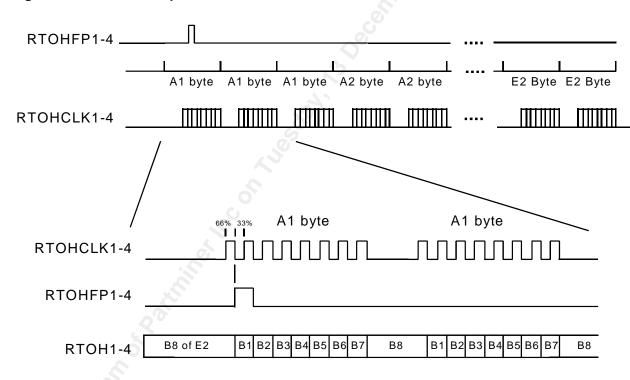

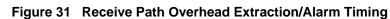

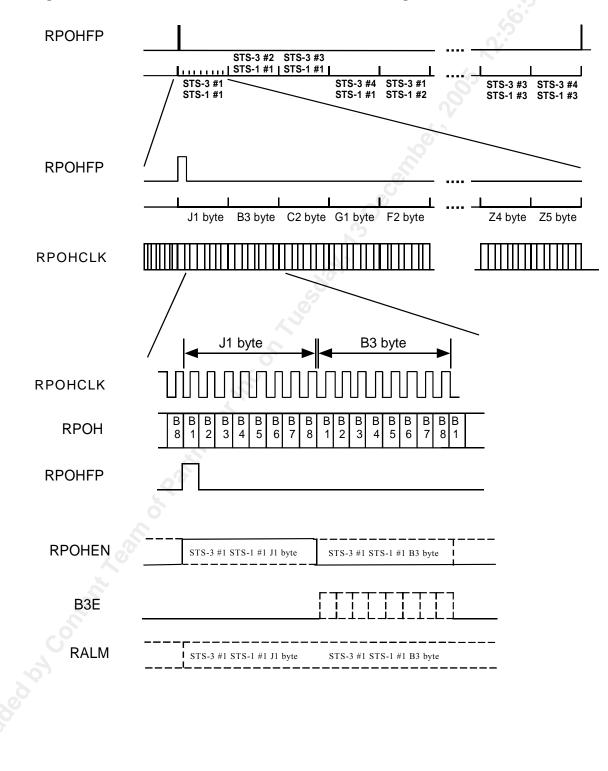

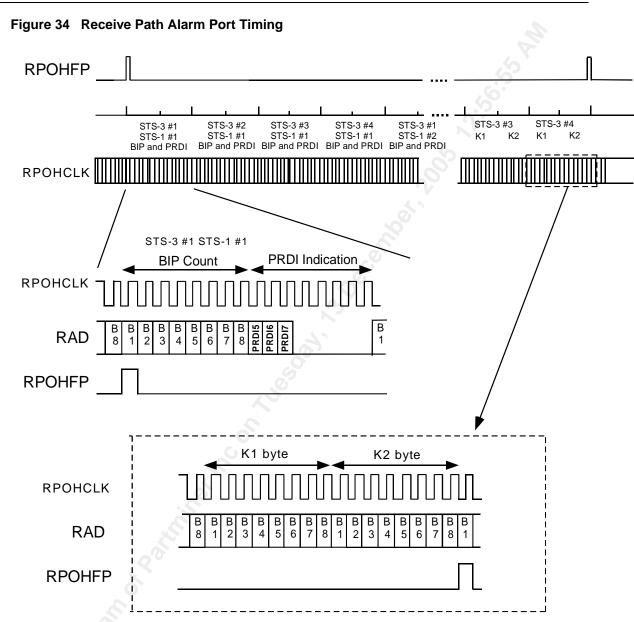

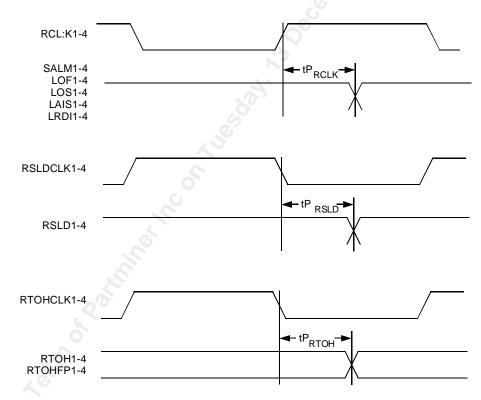

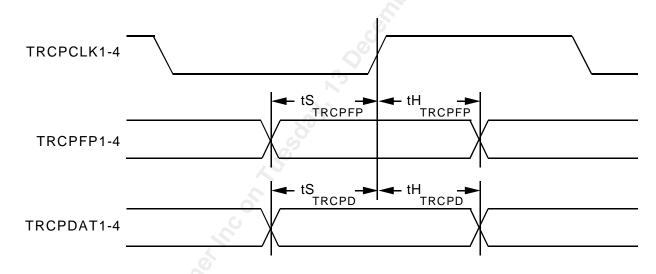

|    | 14.1 Receive Transport Overhead Extraction      | 426 |

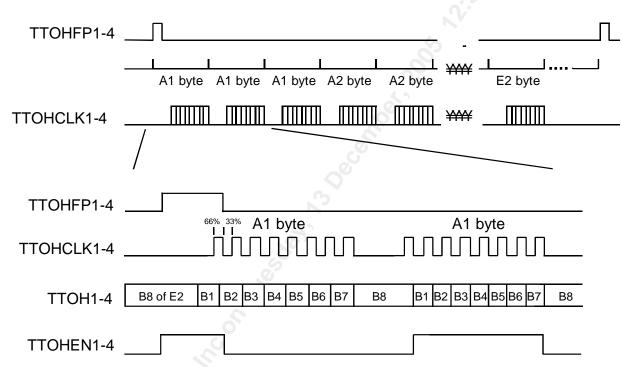

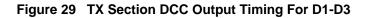

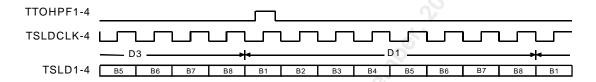

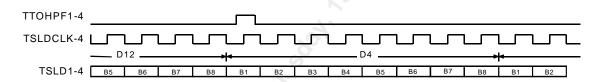

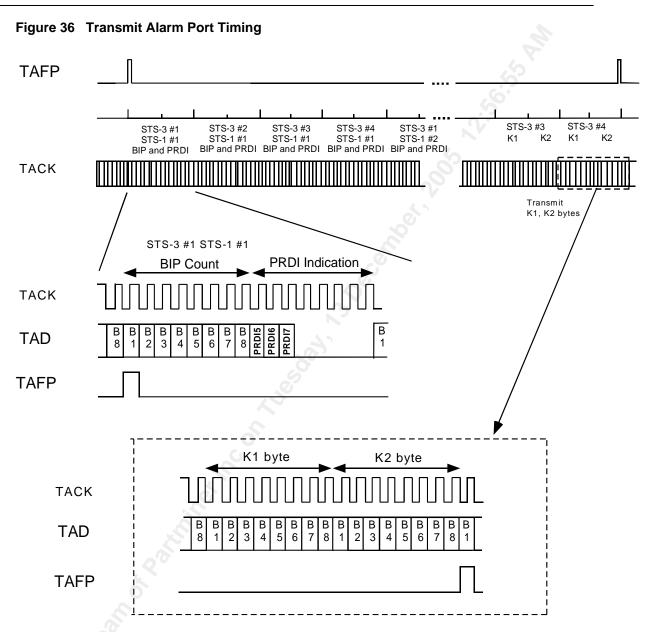

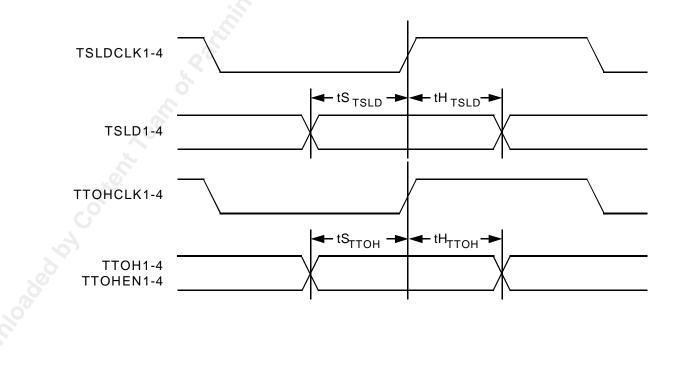

|    | 14.2 Transmit Transport Overhead Insertion      | 428 |

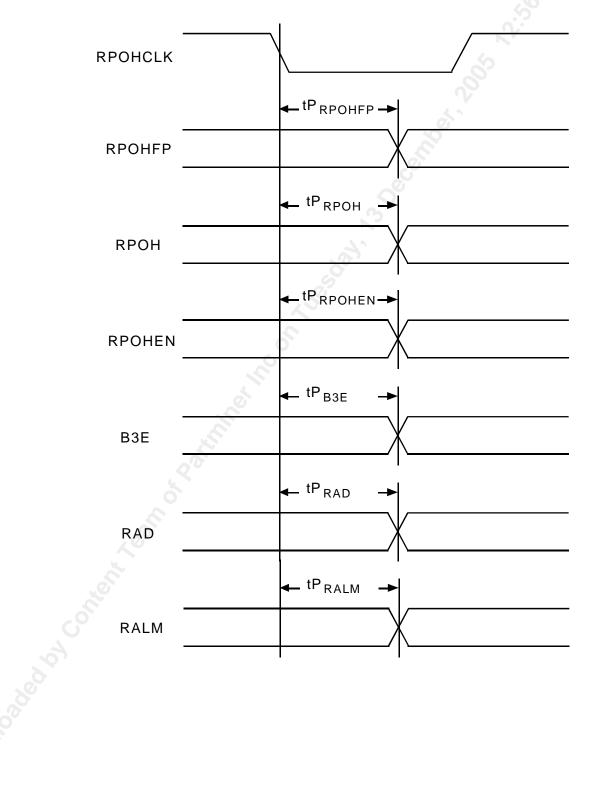

|    | 14.3 Receive Path Overhead Extraction           | 430 |

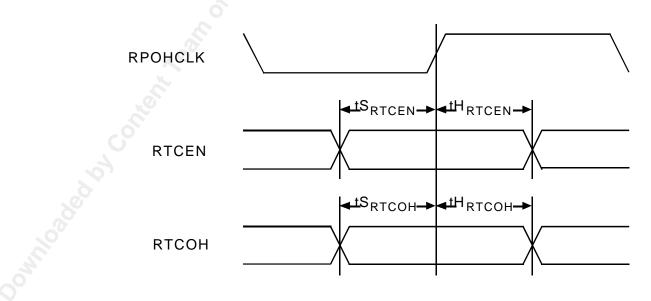

|    | 14.4 Mate SPECTRA 4x155 Interfaces              | 433 |

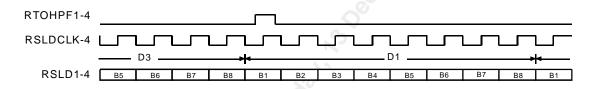

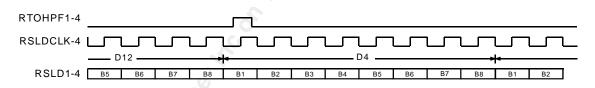

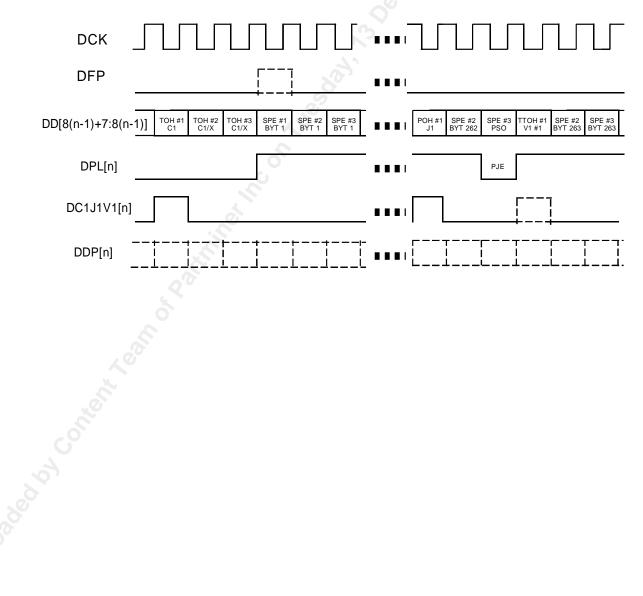

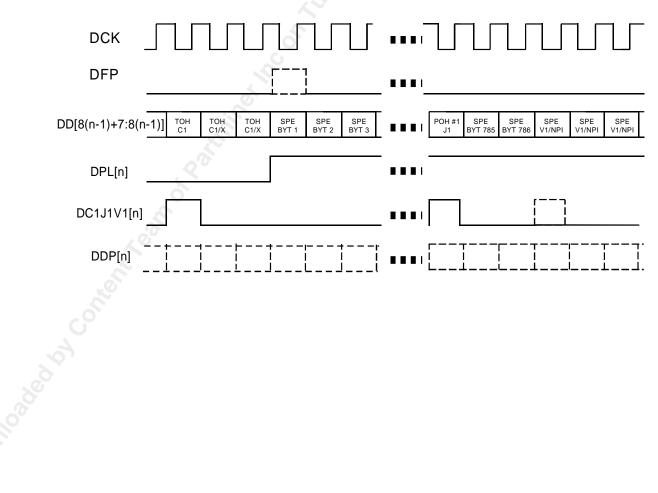

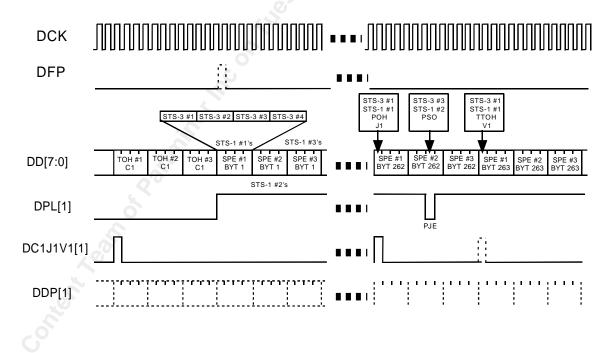

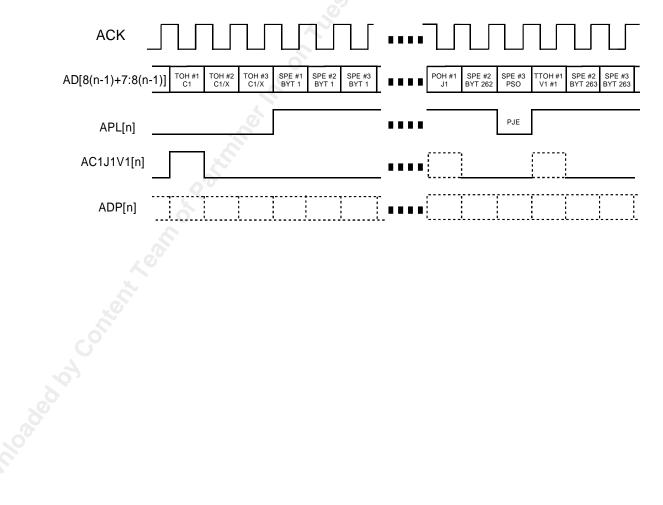

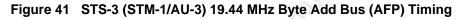

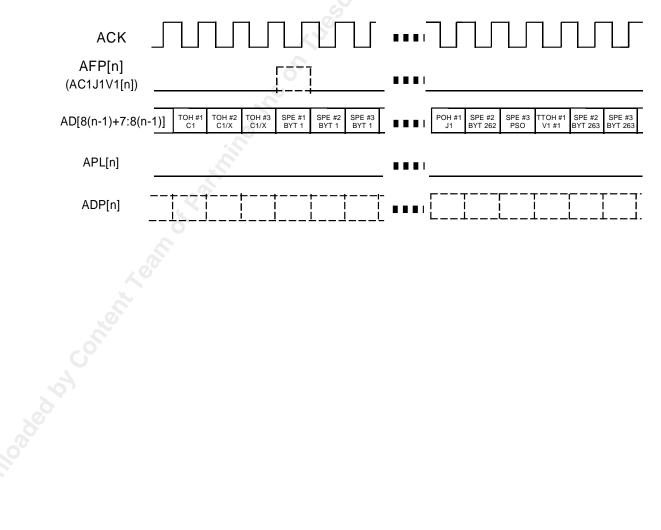

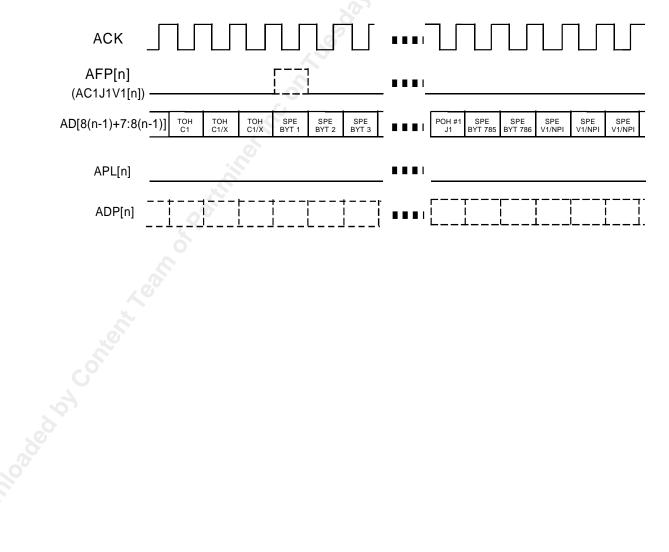

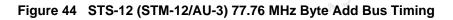

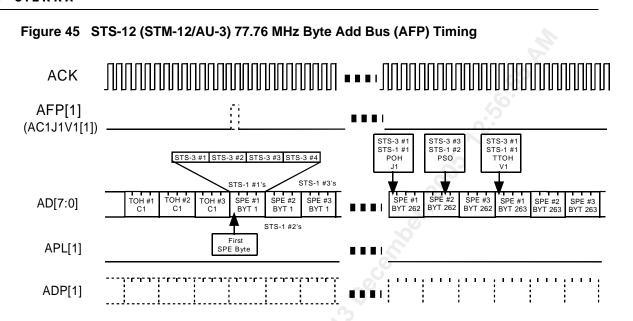

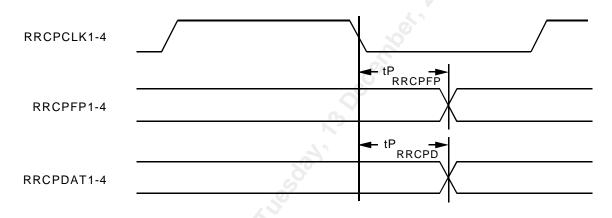

|    | 14.5 Telecom Bus System Side                    | 438 |

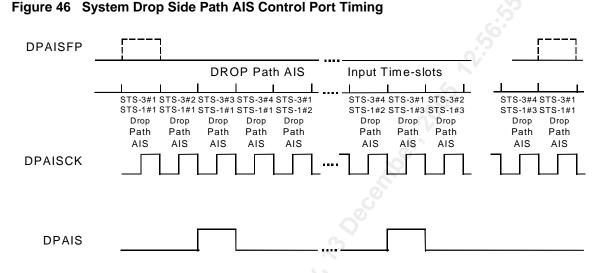

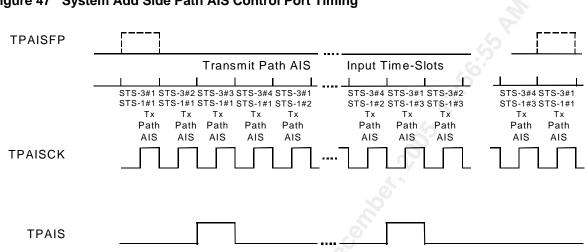

|    | 14.6 System Side Path AIS Control Port          | 447 |

| 15 | Absolute Maximum Ratings                        | 449 |

| 16 | D.C. Characteristics                            | 450 |

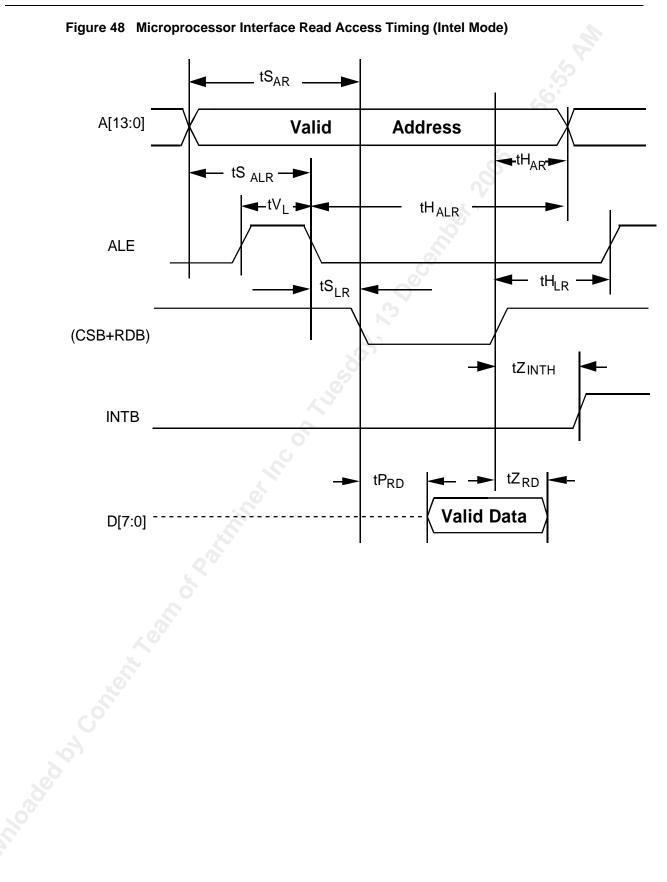

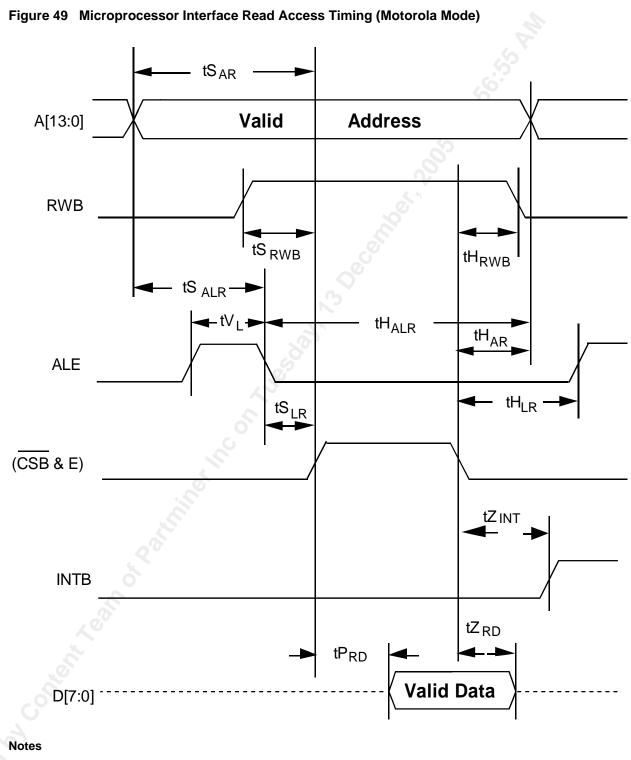

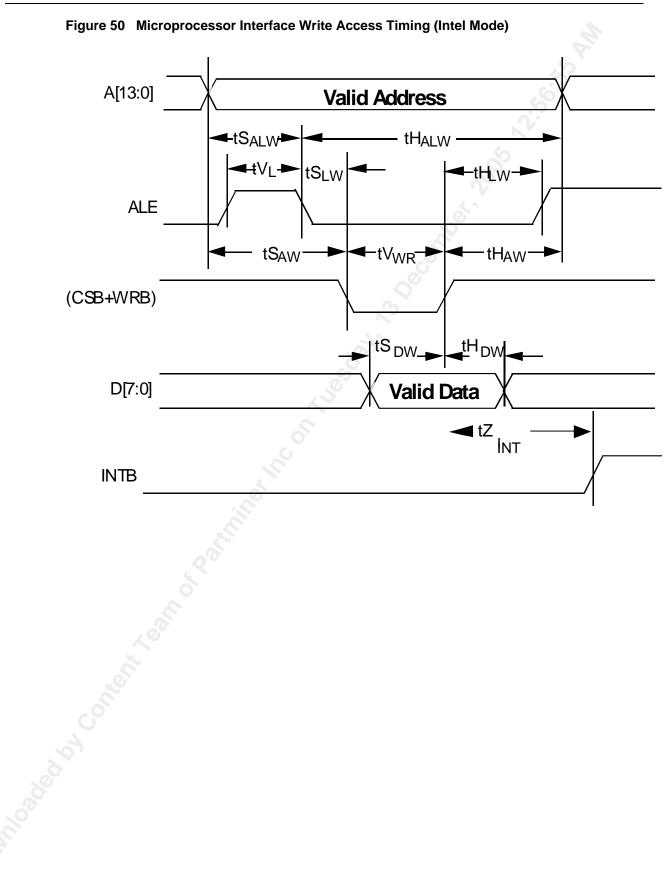

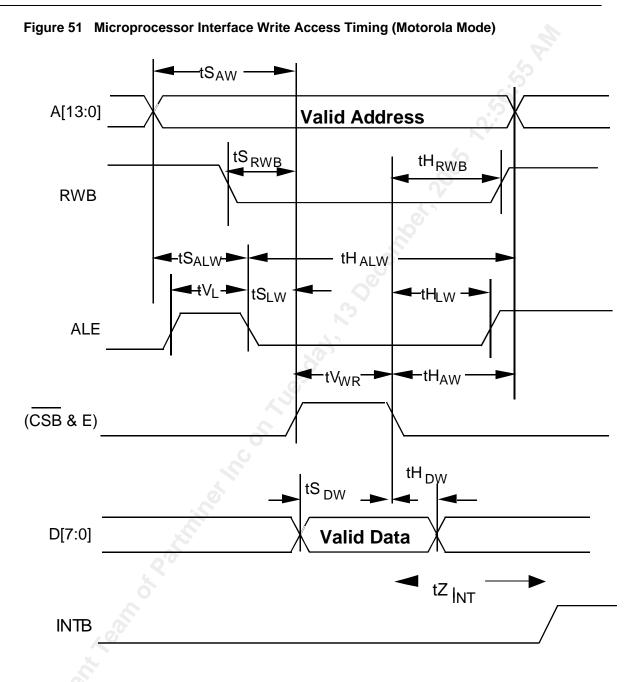

| 17 | Microprocessor Interface Timing Characteristics | 452 |

| 18 | A.C. Timing Characteristics                     | 459 |

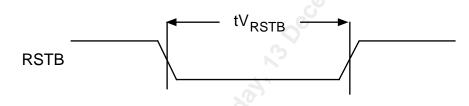

|    | 18.1 System Reset Timing                        | 459 |

|    | 18.2 Receive Timing                             | 459 |

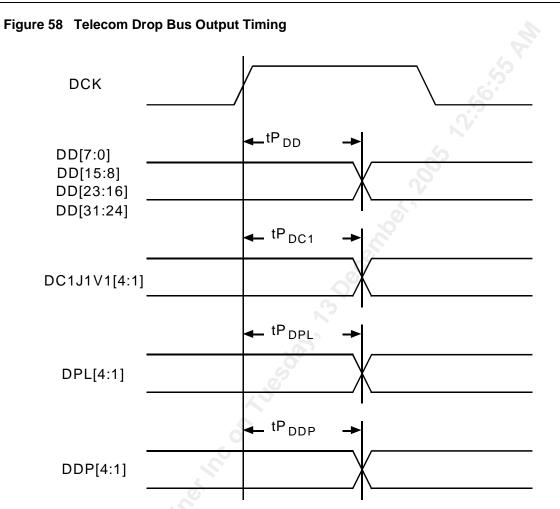

|    | 18.3 Telecom Drop Bus Timing                    | 463 |

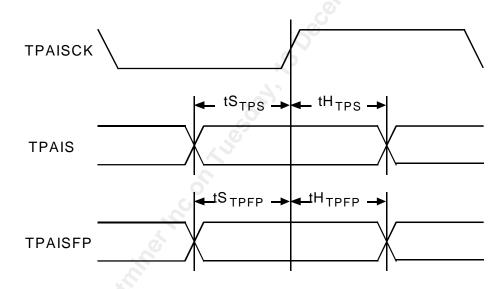

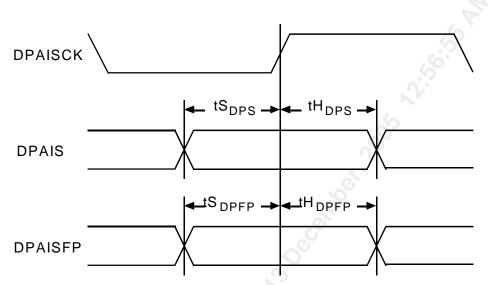

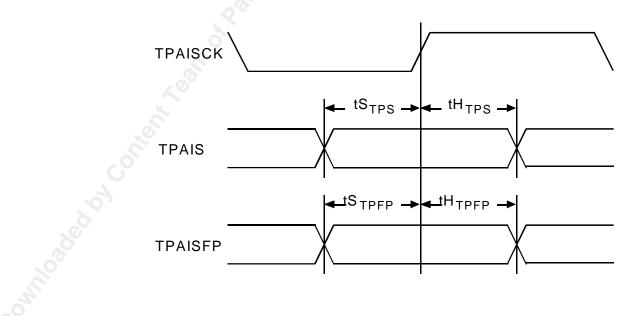

|    | 18.4 System-side Path Alarm Input Timing        | 464 |

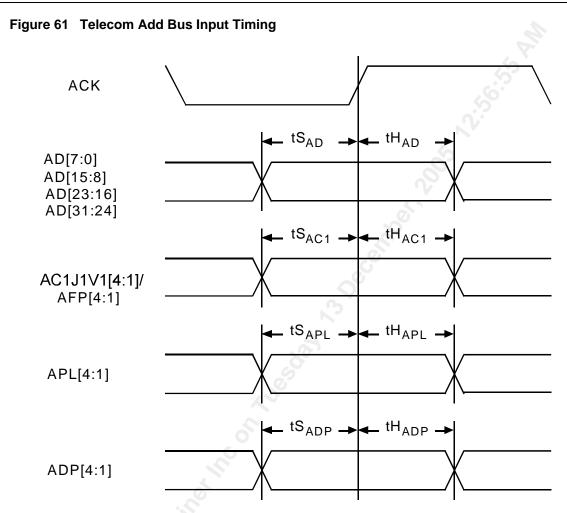

|    | 18.5 Telecom Add Bus Timing                     | 466 |

|    | 18.6 Transmit Timing                            | 467 |

|    | 18.7 JTAG Timing                                | 469 |

| 19 | Ordering and Thermal Information                | 471 |

| 20 | Mechanical Information                          | 473 |

| No | tes                                             | 474 |

|    |                                                 |     |

|    |                                                 |     |

|    |                                                 |     |

|    |                                                 |     |

|    |                                                 |     |

|    |                                                 |     |

|    |                                                 |     |

|    |                                                 |     |

# **List of Registers**

| Register 0000H: SPECTRA 4x155 Reset, Identity and Accumulation Trigger                    | 115 |

|-------------------------------------------------------------------------------------------|-----|

| Register 0001H: Master Clock Activity Monitor                                             | 116 |

| Register 0002H: Master Clock Control                                                      |     |

| Register 0003H: Master Interrupt Status                                                   | 119 |

| Register 0004H: Path Processing Slice Interrupt Status #1                                 | 121 |

| Register 0005H: Path Processing Slice Interrupt Status #2                                 | 121 |

| Register 0006H: Path Processing Slice Interrupt Status #3                                 | 121 |

| Register 0007H: Path Reset                                                                | 123 |

| Register 000AH: FREE                                                                      | 124 |

| Register 0010H: CSPI Control and Status                                                   | 125 |

| Register 0011H: CSPI Reserved                                                             | 126 |

| Register 0100H, 0200H, 0300H, and 0400H: Channel Reset, Identity and Accumulation Trigger | 127 |

| Register 0101H, 0201H, 0301H, and 0401H: Line Configuration #1                            | 128 |

| Register 0102H, 0202H, 0302H, and 0402H: Line Configuration #2                            | 130 |

| Register 0103H, 0203H, 0303H, and 0403H: Receive Line AIS Control                         | 131 |

| Register 0104H, 0204H, 0304H, and 0404H: Ring Control                                     | 133 |

| Register 0105H, 0205H, 0305H, and 0405H: Transmit Line RDI Control                        | 135 |

| Register 0106H, 0206H, 0306H, and 0406H: Section Alarm Output Control #1                  | 137 |

| Register 0107H, 0207H, 0307H, and 0407H: Section Alarm Output Control #2                  | 139 |

| Register 0108H, 0208H, 0308H, and 0408H: Section/Line Block Interrupt<br>Status           | 140 |

| Register 0109H, 0209H, 0309H, and 0409H: Auxiliary Section/Line Interrupt                 |     |

| Enable                                                                                    | 142 |

| Register 010AH, 020AH, 030AH, and 040AH: Auxiliary Section/Line Interrupt Status          | 144 |

| Register 010BH, 020BH, 030BH, and 040BH: Auxiliary Signal Interrupt Enable                | 145 |

| Register 010CH, 020CH, 030CH, and 040CH: Auxiliary Signal Status/Interrupt                | 146 |

| Registers 0110H, 0210H, 0310H, and 0410H: CRSI Configuration and Interrupt Status         | 147 |

| Registers 0111H, 0211H, 0311H, and 0411H: CRSI Reserved                                   | 149 |

| Registers 0114H, 0214H, 0314H, and 0414H: RSOP Control and Interrupt<br>Enable            | 150 |

| Registers 0115H, 0215H, 0315H, and 0415H: RSOP Status and Interrupt                       | 152 |

| Registers 0116H, 0216H, 0316H, 0416H: RSOP Section BIP (B1) Error Count                   |     |

| #1                                                                                        | 154 |

| Register 0117H, 0217H, 0317H, 0417H: RSOP Section BIP (B1) Error Count<br>#2     |

|----------------------------------------------------------------------------------|

| Register 0118H, 0218H, 0318H, and 0418H: RLOP Control and Status                 |

| Registers 0119H, 0219H, 0319H, and 0419H: RLOP Interrupt Enable and<br>Status    |

| Registers 011AH, 021AH, 031AH, 041AH: RLOP Line BIP (B2) Error Count #1          |

| Registers 011BH, 021BH, 031BH, 041BH: RLOP Line BIP (B2) Error Count #2          |

| Registers 011CH, 021CH, 031CH, 041CH: RLOP Line BIP (B2) Error Count #3          |

| Registers 011DH, 021DH, 031DH, and 041DH: RLOP REI Error Count #1                |

| Registers 011EH, 021EH, 031EH, and 041EH: RLOP REI Error Count #2                |

| Registers 011FH, 021FH, 031FH, and 041FH: RLOP REI Error Count #3                |

| Registers 0120H, 0220H, 0320H, and 0420H: SSTB Section Trace Control             |

| Registers 0121H, 0221H, 0321H, and 0421H: SSTB Section Trace Status              |

| Registers 0122H, 0222H, 0322H, and 0422H: SSTB Section Trace Indirect<br>Address |

| Registers 0123H, 0223H, 0323H, and 0423H: SSTB Section Trace Indirect            |

| Data                                                                             |

| Registers 0124H, 0224H, 0324H, and 0424H: SSTB Reserved                          |

| Registers 0125H, 0225H, 0325H, and 0425H: SSTB Reserved                          |

| Registers 0126H, 0226H, 0326H, and 0426H: SSTB Section Trace Operation           |

| Registers 0130H, 0230H, 0330H, and 0430H: RTOC Overhead Control                  |

| Registers 0131H, 0231H, 0331H, and 0431H: RTOC AIS Control                       |

| Registers 0140H, 0240H, 0340H, 0440H: RASE Interrupt Enable                      |

| Registers 0141H, 0241H, 0341H, 0441H: RASE Interrupt Status                      |

| Registers 0142H, 0242H, 0342H, 0442H: RASE Configuration/Control175              |

| Registers 0143H, 0243H, 0343H, and 0443H: RASE SF Accumulation Period            |

| Registers 0144H, 0244H, 0344H, and 0444H: RASE SF Accumulation Period 177        |

| Registers 0145H, 0245H, 0345H, and 0445H: RASE SF Accumulation Period 177        |

| Registers 0146H, 0246H, 0346H, and 0446H: RASE SF Saturation Threshold           |

| Registers 0147H, 0247H, 0347H, and 0447H: RASE SF Saturation Threshold           |

| Registers 0148H, 0248H, 0348H, and 0448H: RASE SF Declaring Threshold            |

| Registers 0149H, 0249H, 0349H, and 0449H: RASE SF Declaring Threshold            |

| Registers 014AH, 024AH, 034AH, and 044AH: RASE SF Clearing Threshold             |

| Registers 014BH, 024BH, 034BH, and 044BH: RASE SF Clearing Threshold             |

| Registers 014CH, 024CH, 034CH, and 044CH: RASE SD Accumulation Period            |

| Registers 014DH, 024DH, 034DH, and 044DH: RASE SD Accumulation Period            |

| Registers 014EH, 024EH, 034EH, and 044EH: RASE SD Accumulation Period            |

| Registers 014FH, 024FH, 034FH, and 044FH: RASE SD Saturation Threshold           |

| Registers 0150H, 0250H, 0350H, and 0450H: RASE SD Saturation Threshold | . 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers 0151H, 0251H, 0351H, and 0451H: RASE SD Declaring Threshold  | . 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0152H, 0252H, 0352H, and 0452H: RASE SD Declaring Threshold  | . 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0153H, 0253H, 0353H, and 0453H: RASE SD Clearing Threshold   | . 184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0154H, 0254H, 0354H, and 0454H: RASE SD Clearing Threshold   | . 184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0155H, 0255H, 0355H, 0455H: RASE Receive K1                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Registers 0156H, 0256H, 0356H, 0456H: RASE Receive K2                  | . 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0157H, 0257H, 0357H, 0457H: RASE Receive Z1/S1               | . 187                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0180H, 0280H, 0380H, and 0480H: TSOP Control                 | . 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0181H, 0281H, 0381H, and 0481H: TSOP Diagnostic              | . 189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0184H, 0284H, 0384H, and 0484H: TLOP Control                 | . 190                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0185H, 0285H, 0385H, and 0485H: TLOP Diagnostic              | . 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0186H, 0286H, 0386H, and 0486H: TLOP Transmit K1             | . 192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0187H, 0287H, 0387H, and 0487H: TLOP Transmit K2             | . 193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 0188H, 0288H, 0388H, and 0488H: TTOC Transmit Overhead       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                        | . 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Control                                                                | . 195                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 018AH, 028AH, 038AH, and 048AH: TTOC Transmit Z0             | . 198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Registers 018BH, 028BH, 038BH, and 048BH: TTOC Transmit S1             | . 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1001H: Drop Bus STM-1 #1 AU-3 #1 Select                       | . 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1002H: Drop Bus STM-1 #2 AU-3 #1 Select                       | . 201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1003H: Drop Bus STM-1 #3 AU-3 #1 Select                       | . 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1004H: Drop Bus STM-1 #4 AU-3 #1 Select                       | . 203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1005H: Drop Bus STM-1 #1 AU-3 #2 Select                       | . 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1006H: Drop Bus STM-1 #2 AU-3 #2 Select                       | . 205                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1007H: Drop Bus STM-1 #3 AU-3 #2 Select                       | . 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1008H: Drop Bus STM-1 #4 AU-3 #2 Select                       | . 207                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 1009H: Drop Bus STM-1 #1 AU-3 #3 Select                       | . 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 100AH: Drop Bus STM-1 #2 AU-3 #3 Select                       | . 209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register 100BH: Drop Bus STM-1 #3 AU-3 #3 Select                       | .210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Register 100CH: Drop Bus STM-1 #4 AU-3 #3 Select                       | .211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Register: Register 1020H: Drop Bus DLL Configuration                   | .212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

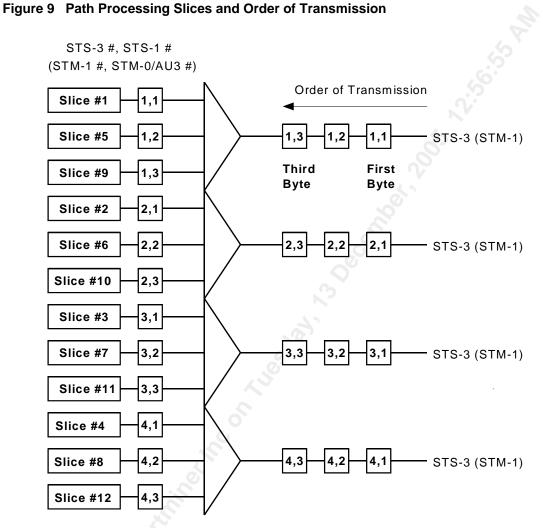

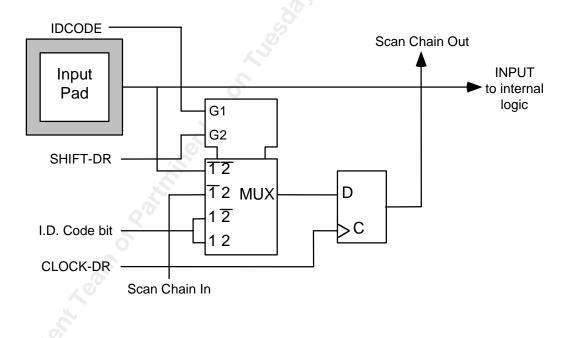

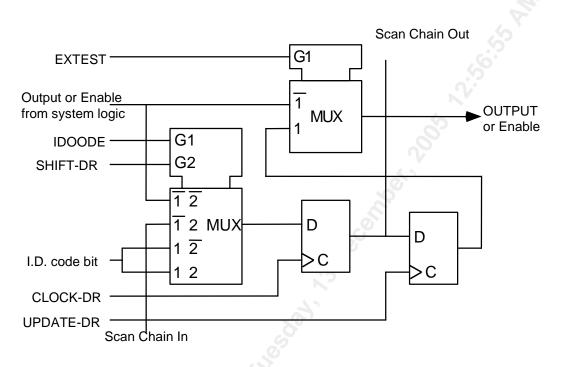

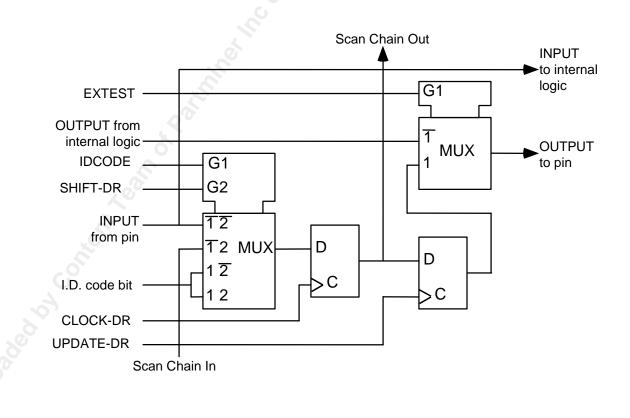

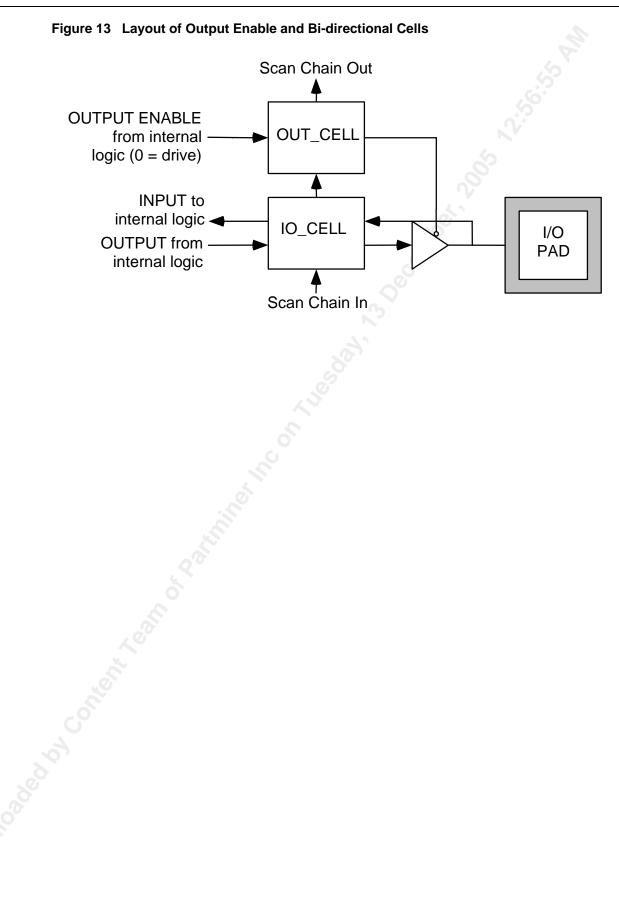

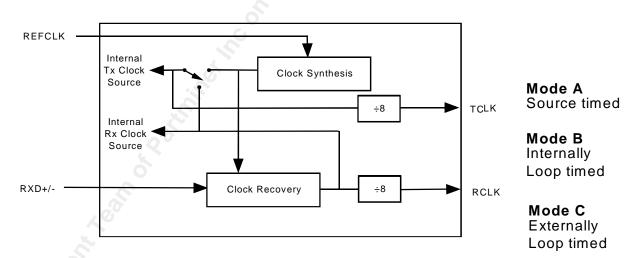

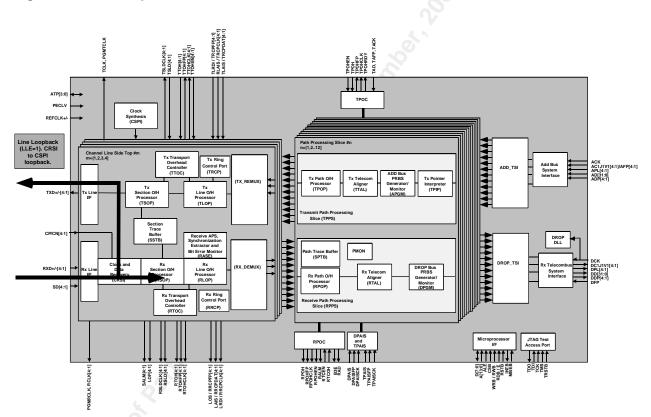

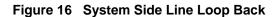

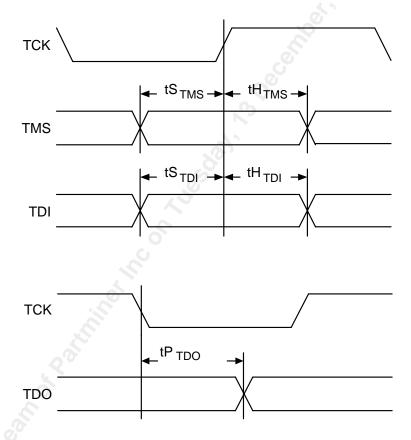

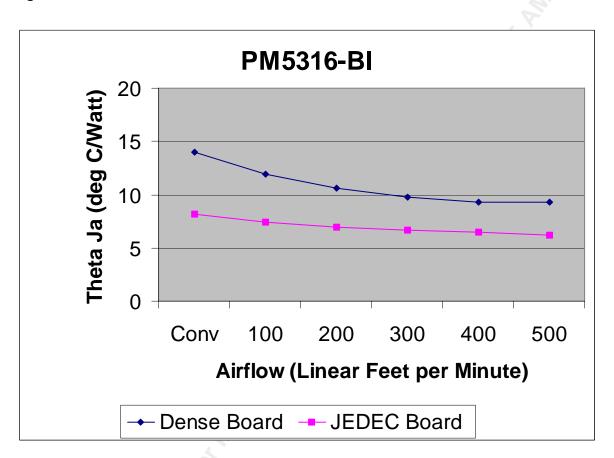

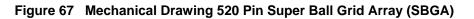

| Register 1021H: Drop Bus DLL Reserved                                  | . 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |