# PM5360

# S/UNI® MULTI-48™

# Multi-rate SATURN® User Network Interface for 1x2488, 4x622, and 4x155

# DATA SHEET

Released

Issue No. 5: September 2003

# Legal Information

## Copyright

Copyright 2003 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

PMC-2020735 (R5)

### Disclaimer

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

## Trademarks

SATURN and S/UNI are registered trademarks of PMC-Sierra, Inc. PMC-Sierra and POS-PHY Level 3 are trademarks of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

## Patents

#### Granted

The technology discussed in this document is protected by one or more of the following patent grants:

U.S. Patent Numbers: 5,606,563; 5,640,398; 5,835,602; 6,052,073; 6,150,965; 6,188,692; 6,301,318; 6,621,360

Canadian Patent Numbers: 2,149,076; 2,159,763; 2,161,921; 2,194,919; 2,245,760

U.K. Patent Number 2,290,438

Other relevant patent grants may also exist.

## **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200

Document Information: <u>document@pmc-sierra.com</u> Corporate Information: <u>info@pmc-sierra.com</u> Technical Support: <u>apps@pmc-sierra.com</u> Web Site: <u>http://www.pmc-sierra.com</u>

# **Revision History**

| Issue No. | Issue Date        | Details of Change                                                                                    |

|-----------|-------------------|------------------------------------------------------------------------------------------------------|

| 1         | July 2002         | Document created.                                                                                    |

| 2         | Sept 2002         | Added pin-out diagram and mappings.                                                                  |

| 3         | February 2003     | Major post tape-out update. Changes in all major sections.                                           |

| 4         | September<br>2003 | Minor updates in all major sections.                                                                 |

| 5         | September<br>2003 | Included Register bits added with Rev B and operation section on interoperability via 777LVDS links. |

|           |                   | Updated status to reflect production release                                                         |

# **Table of Contents**

| Le             | gal Inf  | ormation                                                         |    |

|----------------|----------|------------------------------------------------------------------|----|

| ·              | -        | Copyright                                                        |    |

|                |          | Disclaimer                                                       |    |

|                |          | Frademarks                                                       |    |

|                |          | Patents 2                                                        |    |

| Со             | ntactir  | ng PMC-Sierra                                                    | 3  |

| Re             | vision   | History                                                          | 4  |

|                |          | Contents                                                         |    |

| Lis            | t of Re  | egisters                                                         | 11 |

| Lis            | t of Fig | gures                                                            | 24 |

| Lis            |          | bles                                                             |    |

| 1              | Defir    | nitions                                                          |    |

| 2              | Feat     | ures                                                             | 32 |

|                | 2.1      | General                                                          |    |

|                | 2.2      | SONET Section and Line / SDH Regenerator and Multiplexer Section |    |

|                | 2.3      | SONET Path / SDH High Order Path                                 | 34 |

|                | 2.4      | APS Interface                                                    | 34 |

|                | 2.5      | X-Bar                                                            |    |

|                | 2.6      | The Receive ATM Processor                                        | 35 |

|                | 2.7      | The Receive POS Processor                                        | 35 |

|                | 2.8      | The Transmit ATM Processor                                       |    |

|                | 2.9      | The Transmit POS Processor                                       |    |

| 3 Applications |          | ications                                                         |    |

| 4              | Refe     | rences                                                           |    |

| 5              | Appli    | ication Examples                                                 |    |

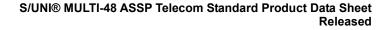

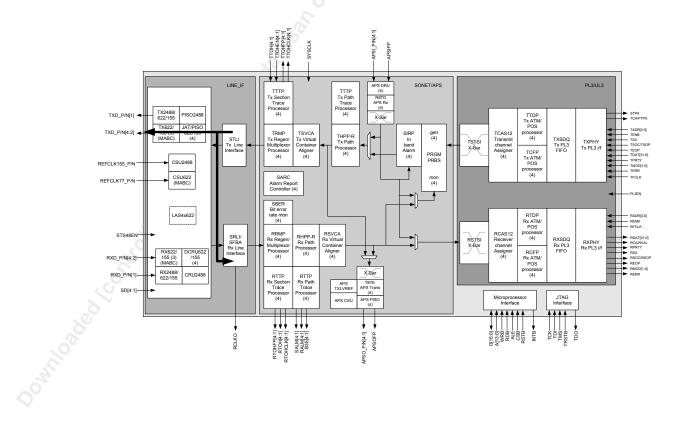

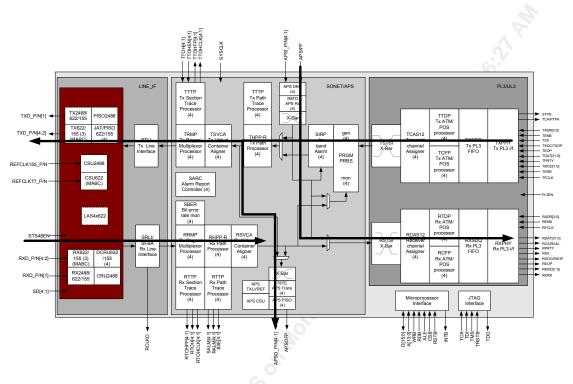

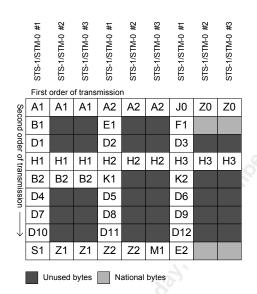

| 6              | Bloc     | k Diagram                                                        | 43 |

| 7              | Desc     | cription                                                         | 47 |

| 8              | Pin D    | Diagram                                                          |    |

| 9              | Pin D    | Description                                                      | 54 |

|                | 9.1      | Serial Line Side Interface Signals (26)                          | 54 |

|                | 9.2      | Alarms Signals and B3 Error Indications (12)                     |    |

|                | 9.3      | Receive Section/Line Overhead Extraction Signals (12)            | 57 |

|                | 9.4      | Transmit Section/Line Overhead Insertion Signals (16)            | 58 |

|                | 9.5      | System Side UTOPIA and POS-PHY L3 Signals (94)                   | 59 |

|                | 9.6      | System Clock and APS Serial Data Interface (19)                  | 67 |

|    | 9.7   | Micro   | pprocessor Interface and Test Signals(37)                | 68      |

|----|-------|---------|----------------------------------------------------------|---------|

|    | 9.8   | JTAG    | G Test Access Port (TAP) Signals (5)                     | 70      |

|    | 9.9   | Analo   | og Miscellaneous Signals (15)                            | 70      |

|    | 9.10  | Analo   | og Power                                                 | 71      |

|    | 9.11  | Digita  | al Power                                                 | 73      |

|    | ç     | 9.11.1  | Ground                                                   | 74      |

| 10 |       |         | Description                                              |         |

|    | 10.1  | Rece    | vive Line Interface                                      | 77      |

|    | 10.2  | SON     | ET STS-48/QUAD STS-12/3 Receive Line Interface (SRLI/S   | SFBA)78 |

|    | 10.3  | Rece    | vive Regenerator and Multiplexer Processor (RRMP)        | 78      |

|    |       |         | vive High Order Path Processor (RHPP)                    |         |

|    | 1     | 0.4.1   | Pointer Interpreter                                      |         |

|    | 1     | 0.4.2   | Concatenation Pointer Interpreter State Machine          |         |

|    | 1     | 0.4.3   | Error Monitoring                                         |         |

|    | 10.5  | Rece    | vive Section and Path Trace Processor (RTTP)             |         |

|    | 10.6  | SON     | ET Bit Error Rate Monitor (SBER)                         |         |

|    | 10.7  | SON     | ET Alarm Report Controller (SARC)                        | 91      |

|    | 10.8  | Rece    | vive SONET Virtual Container Aligner (RSVCA)             | 91      |

|    | 1     | 0.8.1   | Elastic Store                                            |         |

|    | 10.9  | Trans   | smit Line Interface                                      |         |

|    | 10.10 | SON     | ET STS-48/QUAD STS-12/3 Transmit Line Interface (STLI)   |         |

|    | 10.11 | 1 Trans | smit Regenerator and Multiplexer Section Processor (TRMF | ?)95    |

|    | 10.12 | 2 Trans | smit Path High Order Processor (THPP)                    |         |

|    | 10.13 | 3 Trans | smit Section and Path Trace Processor (TTTP)             |         |

|    | 10.14 | 4 Trans | smit SONET Virtual Container Aligner (TSVCA)             |         |

|    | 10.1  | 5 APS   | Serial TelecomBus (LVDS)                                 |         |

|    | 1     | 0.15.1  | LVDS Overview                                            | 101     |

|    | 1     | 0.15.2  | 2 LVDS Receiver (RXLV)                                   | 103     |

|    | 1     | 10.15.3 | 3 APS Data Recovery Unit (APSDRU)                        | 103     |

|    | 2     | 0.15.4  | APS Parallel to Serial Converter (APISO)                 |         |

|    | 6 1   | 0.15.5  | 5 LVDS Transmitter (TXLV)                                | 103     |

|    | 10.16 | 6 Rece  | vive 8B/10B TelecomBus Decoder (R8TD)                    |         |

|    | 1     | 0.16.1  | I Character Alignment                                    |         |

|    | 1     | 0.16.2  | 2 Frame Alignment                                        |         |

|    | 1     | 0.16.3  | 3 Character Decode                                       |         |

|    | 10.17 | 7 Trans | smit 8B/10B TelecomBus Encoder (T8TE)                    |         |

|    | 1     | 0.17.1  | I Character Encode                                       | 105     |

|    | 10.18 Space Slot Interchange (X-BAR)                                | 106 |

|----|---------------------------------------------------------------------|-----|

|    | 10.19 SONET In-band Error Report Processor (SIRP)                   | 106 |

|    | 10.20 Pseudo-Random Bit Sequence Generator and Monitor (PRGM)       | 106 |

|    | 10.21 SONET Timeslot Interchange (STSI)                             |     |

|    | 10.22 Receive Channel Assigner (RCAS12)                             |     |

|    | 10.23 Receive Time-sliced Datacom Processor (RTDP)                  | 108 |

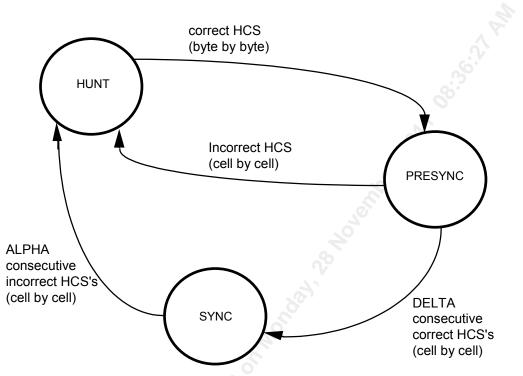

|    | 10.23.1 RTDP ATM Processor                                          |     |

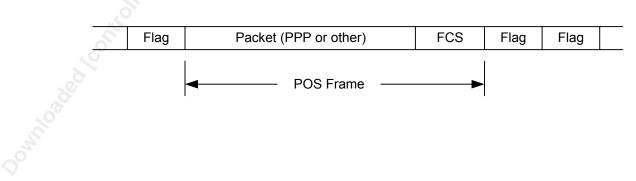

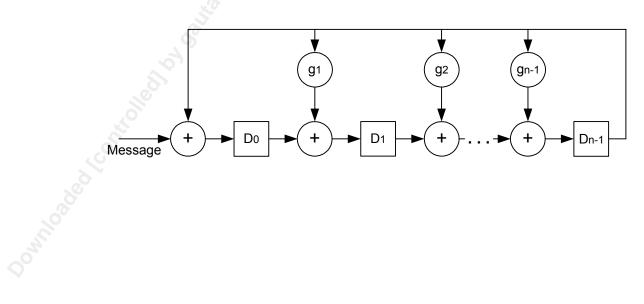

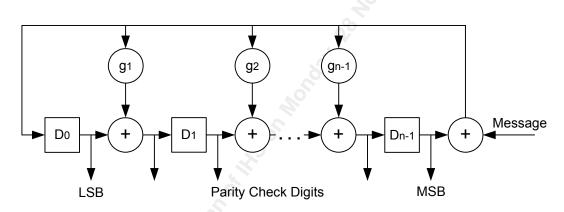

|    | 10.23.2 RTDP Packet Processor                                       | 110 |

|    | 10.24 Receive Cell and Frame Processor (RCFP)                       | 112 |

|    | 10.25 Receive ATM and Packet FIFO (RXSDQ)                           | 113 |

|    | 10.26 Receive UL3 and PL3 Interface (RXPHY)                         | 114 |

|    | 10.27 Transmit Channel Assigner (TCAS12)                            | 114 |

|    | 10.28 Transmit Time-sliced Datacom Processor (TTDP)                 | 114 |

|    | 10.28.1 TTDP ATM Processor                                          | 114 |

|    | 10.28.2 TTDP Packet Processor                                       | 115 |

|    | 10.29 Transmit Cell and Frame Processor (TCFP)                      | 117 |

|    | 10.30 Transmit ATM and Packet FIFO (TXSDQ)                          | 118 |

|    | 10.31 Transmit UL3 and PL3 Interface (TXPHY)                        | 118 |

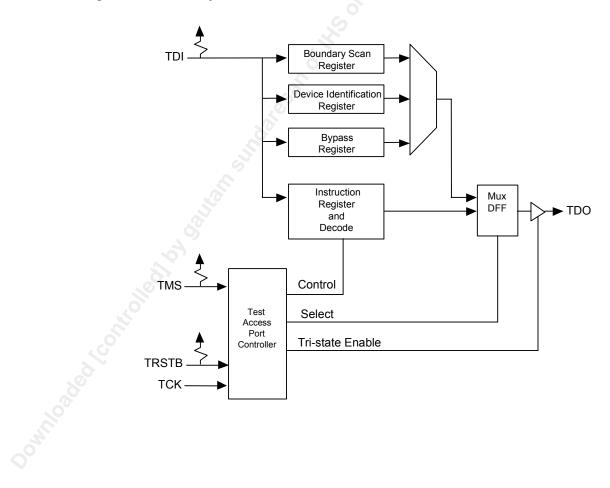

|    | 10.32 JTAG Test Access Port                                         | 118 |

|    | 10.33 Microprocessor Interface                                      | 119 |

| 11 | Normal Mode Register Description                                    | 132 |

|    | 11.1 Registers                                                      | 133 |

| 12 | Test Features Description                                           | 637 |

|    | 12.1 Master Test and Test Configuration Registers                   | 638 |

|    | 12.2 JTAG Test Port                                                 | 658 |

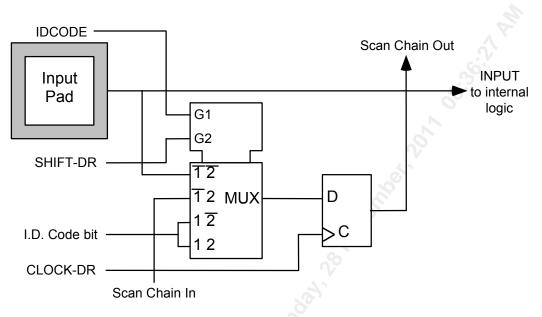

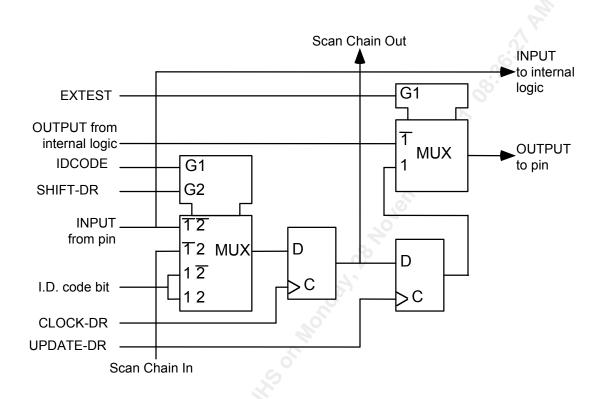

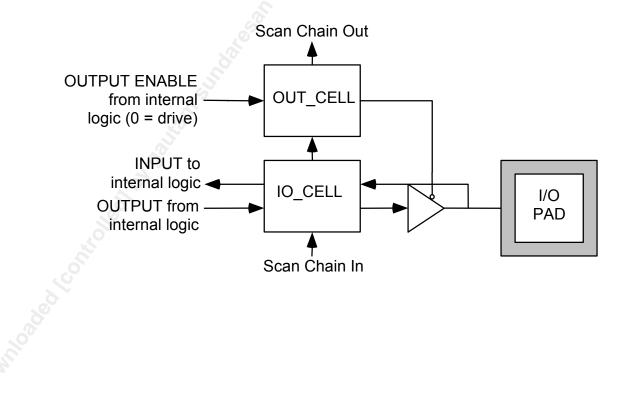

|    | 12.3 Boundary Scan Cells                                            | 658 |

| 13 | Operation                                                           | 661 |

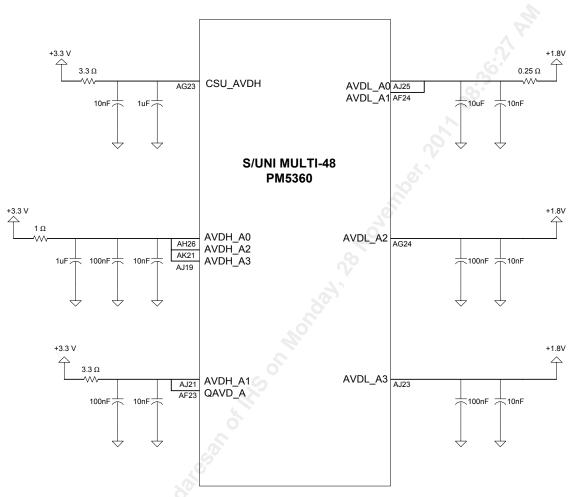

|    | 13.1 Board Design Recommendations                                   | 661 |

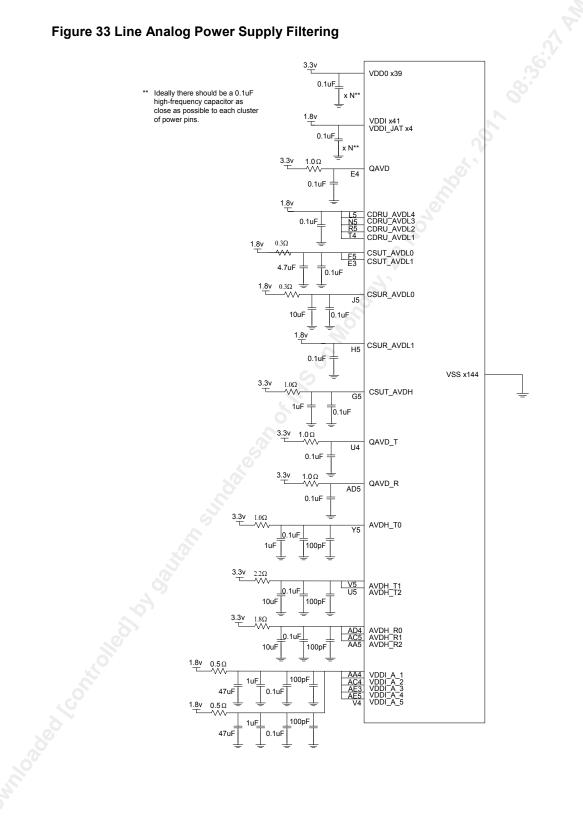

|    | 13.2 Power Supplies filtering                                       | 662 |

|    | 13.3 Power Up/Down Sequence                                         | 663 |

|    | 13.4 Device Initialization                                          | 664 |

|    | 13.4.1 Device Reset                                                 | 664 |

|    | 13.4.2 Register Initialization                                      | 664 |

|    | 13.5 Programming the Line Side Configuration Registers              | 664 |

|    | 13.5.1 STS-48/STM-16 Line Side Mode of Operation                    | 665 |

|    | 13.5.2 Quad STS-12/STM-4 or STS-3/STM-1 Line Side Mode of Operation | 665 |

|    | 13.6 Preventing Errors Due to Unstable Clocks                       | 666 |

|    |                                                                     |     |

| 13.6.1 SYSCLK_EN value change                                                            | 667        |

|------------------------------------------------------------------------------------------|------------|

| 13.6.2 Line Side Initialization                                                          |            |

| 13.7 Interrupt Service Routine                                                           | 667        |

| 13.8 Accessing Indirect Registers                                                        |            |

| 13.9 Using the Performance Monitoring Features                                           | 669        |

| 13.10 Configuring SONET/SDH Payload from a Concatenated Stream to a Channe<br>Stream     |            |

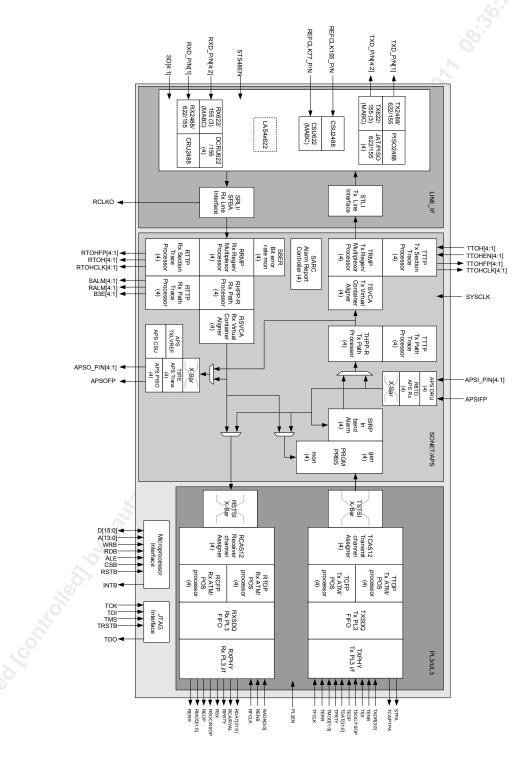

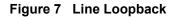

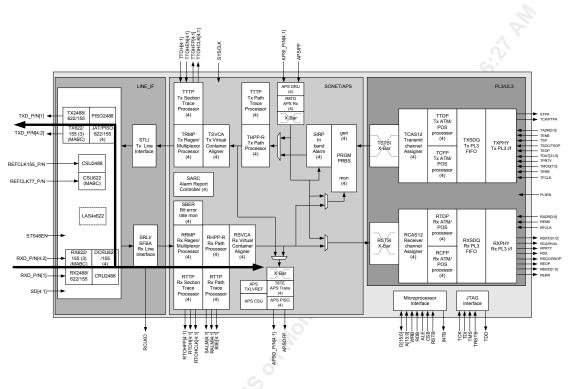

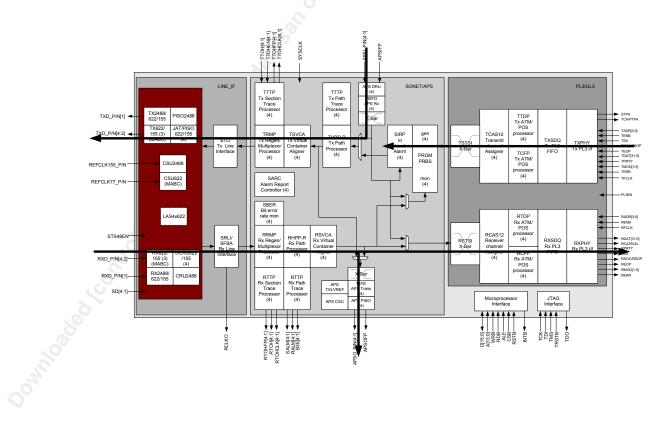

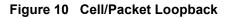

| 13.11 Loopback Operation                                                                 | 669        |

| 13.12 Invalid Receive Line Timing Recovery                                               | 670        |

| 13.13 Using The Section/Line Bit Error Rate Monitoring Features                          | 671        |

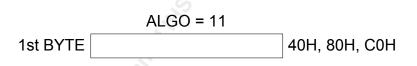

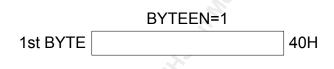

| 13.14 Using The Receive Trail Trace Processor Features                                   |            |

| 13.15 Using the Transmit Trail trace Processor                                           | 676        |

| 13.16 LCD Defect Processing and ERDI-P/REI-P Insertion                                   |            |

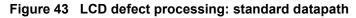

| 13.16.1 Standard Datapath LCD Defect Processing                                          | 677        |

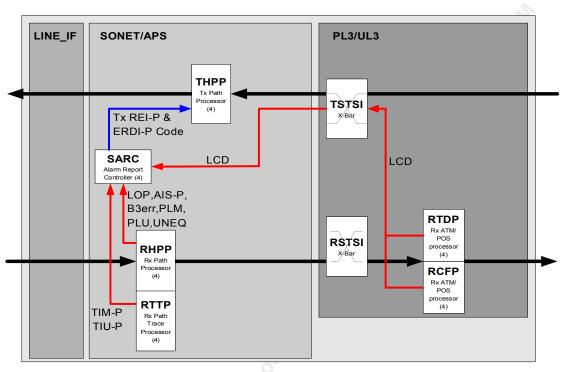

| 13.16.2 APS Datapath LCD Defect Processing                                               | 679        |

| 13.17 APS Interface Operation                                                            | 681        |

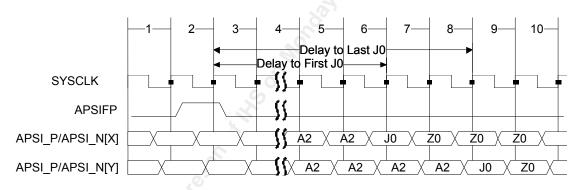

| 13.17.1 Receive APS Port Synchronization                                                 |            |

| 13.17.2 Receive APS Port SMART Framing                                                   | 682        |

| 13.17.3 APS Port Error Recovery Guidelines                                               |            |

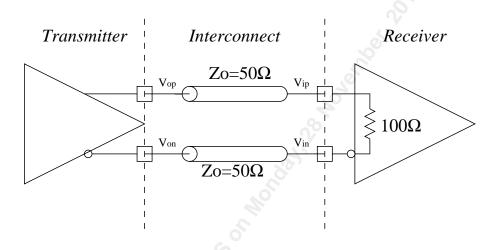

| 13.18 Interoperability via the 777MHz LVDS Interface                                     |            |

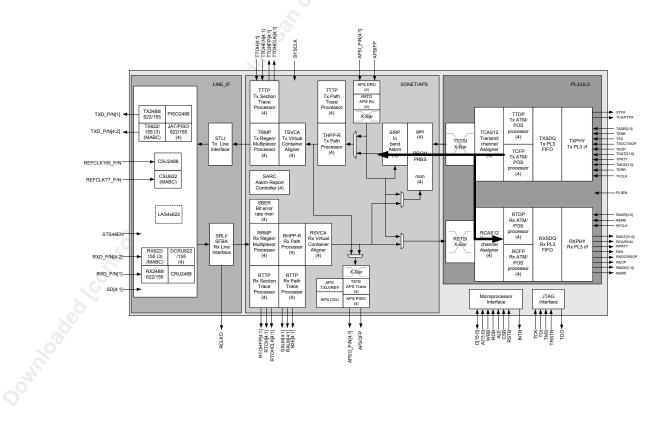

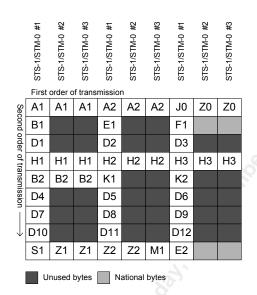

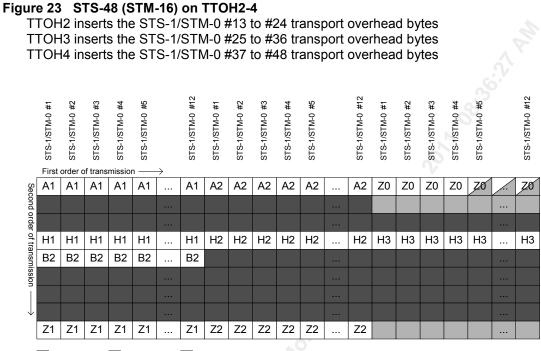

| 13.19 SONET/SDH Frame Mappings and Overhead Byte Usage                                   | 687        |

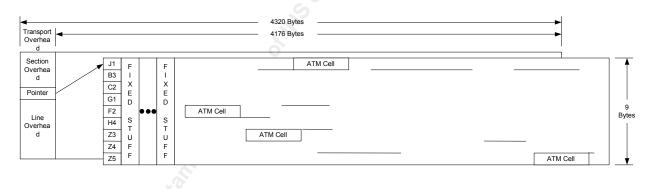

| 13.19.1 ATM Mapping                                                                      | 687        |

| 13.19.2 Packet Over SONET Mapping                                                        | 687        |

| 13.20 ATM Cell Data Structure                                                            |            |

| 13.21 POS/HDLC Data Structure                                                            | 688        |

| 13.21.1 Limitation When Using Externally Generated FCS in STS-48c Mode                   |            |

| 13.21.2 Limitations on Small Packets                                                     | 689        |

| 13.22 Transport and Path Overhead Bytes                                                  | 690        |

| 13.23 Using the SONET/SDH Inband Error Report Processor (SIRP)                           | 693        |

| 13.24 Using the PRBS Generator and Monitor (PRGM)                                        | 693        |

| 213.24.1 Synchronization                                                                 | 693        |

| 13.24.2 Error Detection and Accumulation                                                 | 694        |

| 13.24.3 Monitoring and Generating a Single STS-3c/VC-4 PRBS Payload in S<br>3/STM-1 Mode |            |

| 13.25 Setting up Timeslot Assignments in the UL3/PL3 X-Bar                               | 695        |

| 13.25.1 Standard Line-Side (SONET sub-system) Timeslot Map                               | 695        |

| 13.25.2 Required System-Side Timeslot Map for Sub-STS-48c/VC-4-16c Data                  | Streams696 |

|    | 13.25.3 Required System-Side Timeslot Map for STS-48c/VC-4-16c Data Streams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 696                                                                              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|    | 13.25.4 Custom Timeslot Mappings and Movement of Timeslots Associated with a Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 697                                                                              |

|    | 13.25.5 Active and Standby Pages in the STSI Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 698                                                                              |

|    | 13.26 Setting up Channels for Different Payload Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 698                                                                              |

|    | 13.26.1 Receive and Transmit Channel Assigner Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 699                                                                              |

|    | 13.27 Receive and Transmit Cell Processors Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 701                                                                              |

|    | 13.28 RXSDQ and TXSDQ Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 702                                                                              |

|    | 13.29 RXSDQ and TXSDQ Dynamic Reconfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 704                                                                              |

|    | 13.30 TXSDQ Buffer Available Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 705                                                                              |

|    | 13.31 RXSDQ and TXSDQ Data Available and Burst-Size Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|    | 13.32 RXPHY POS-PHY L3 Servicing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|    | 13.32.1 RXPHY POS-PHY L3 Servicing Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 707                                                                              |

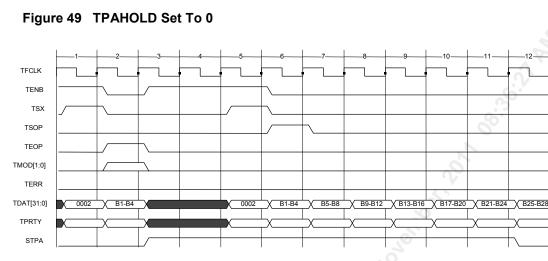

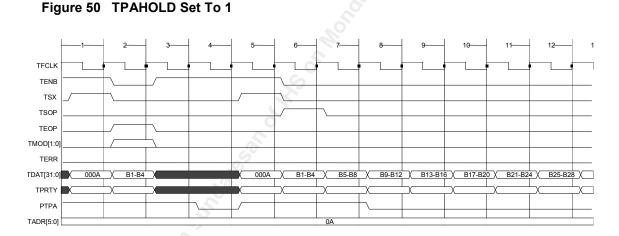

|    | 13.33 Transmit PL3 STPA and PTPA Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 710                                                                              |

|    | 13.33.1 TPAHOLD = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

|    | 13.33.2 TPAHOLD = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 713                                                                              |

|    | 13.34 Setting ATM Mode of Operation over Utopia L3 or POS-PHY L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 714                                                                              |

|    | 13.35 Setting Packet Mode of Operation Over POS-PHY L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 715                                                                              |

|    | 13.36 Setting Transparent Mode of Operation Over POS-PHY L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|    | 13.37 Example Set-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 716                                                                              |

|    | 13.38 Dynamically Reprovisioning Channels to Different Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 718                                                                              |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

|    | 13.39 Cell/packet processors and FIFOs Error Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 719                                                                              |

|    | 13.39.1 RXSDQ FIFOs losing ATM cell alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 719                                                                              |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 719                                                                              |

|    | 13.39.1 RXSDQ FIFOs losing ATM cell alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 719<br>719                                                                       |

|    | 13.39.1 RXSDQ FIFOs losing ATM cell alignment<br>13.40 System Interface Error Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 719<br>719<br>719                                                                |

|    | 13.39.1 RXSDQ FIFOs losing ATM cell alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 719<br>719<br>719<br>720                                                         |

|    | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> </ul>                                                                                                                                                                                                                                                                                                                                                           | 719<br>719<br>719<br>720<br>720                                                  |

|    | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery</li> </ul>                                                                                                                                                                                                                                                                                     | 719<br>719<br>719<br>720<br>720<br>720                                           |

|    | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery</li> <li>13.40.4 UTOPIA Level 3 Receive Clock (RFCLK) Error Recovery</li> </ul>                                                                                                                                                                                                                | 719<br>719<br>719<br>720<br>720<br>720<br>720<br>721                             |

|    | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery</li> <li>13.40.4 UTOPIA Level 3 Receive Clock (RFCLK) Error Recovery</li> <li>13.40.5 POS Level 3 Transmit (TFCLK) Error Recovery</li> </ul>                                                                                                                                                   | 719<br>719<br>720<br>720<br>720<br>720<br>721<br>721                             |

|    | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery</li> <li>13.40.4 UTOPIA Level 3 Receive Clock (RFCLK) Error Recovery</li> <li>13.40.5 POS Level 3 Transmit (TFCLK) Error Recovery</li> <li>13.40.6 POS Level 3 Receive (RFCLK) Error Recovery</li> </ul>                                                                                       | 719<br>719<br>720<br>720<br>720<br>720<br>721<br>721<br>721<br>722               |

|    | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery</li> <li>13.40.4 UTOPIA Level 3 Receive Clock (RFCLK) Error Recovery</li> <li>13.40.5 POS Level 3 Transmit (TFCLK) Error Recovery</li> <li>13.40.6 POS Level 3 Receive (RFCLK) Error Recovery</li> <li>13.41 JTAG Support</li> </ul>                                                           | 719<br>719<br>720<br>720<br>720<br>721<br>721<br>721<br>722<br>723               |

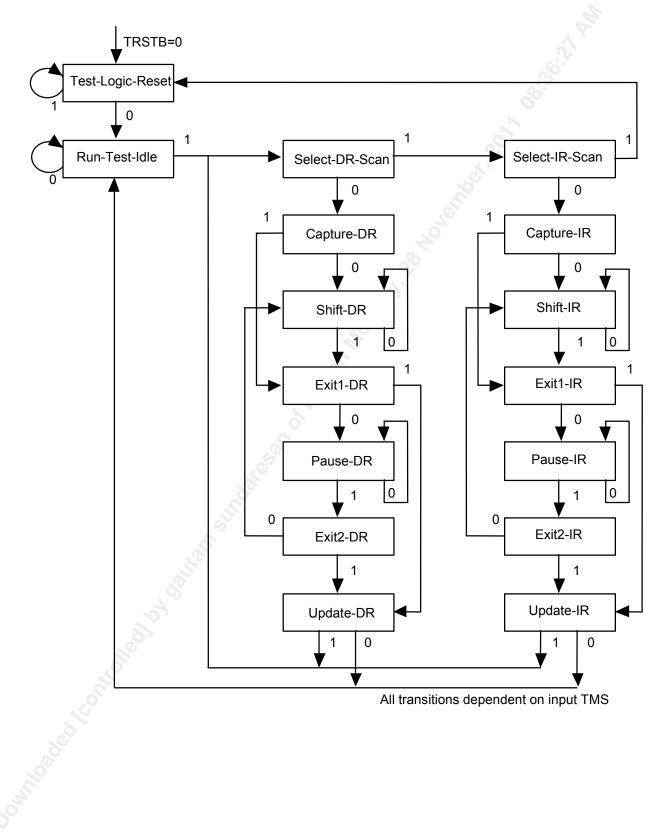

|    | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery.</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery.</li> <li>13.40.4 UTOPIA Level 3 Receive Clock (RFCLK) Error Recovery</li> <li>13.40.5 POS Level 3 Transmit (TFCLK) Error Recovery</li> <li>13.40.6 POS Level 3 Receive (RFCLK) Error Recovery.</li> <li>13.41 JTAG Support.</li> <li>13.41.1 TAP Controller</li> </ul>                       | 719<br>719<br>720<br>720<br>720<br>721<br>721<br>721<br>722<br>723<br>725        |

| 14 | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery</li> <li>13.40.4 UTOPIA Level 3 Receive Clock (RFCLK) Error Recovery</li> <li>13.40.5 POS Level 3 Transmit (TFCLK) Error Recovery</li> <li>13.40.6 POS Level 3 Receive (RFCLK) Error Recovery</li> <li>13.41.1 TAP Controller</li> <li>13.41.2 States</li> </ul>                               | 719<br>719<br>720<br>720<br>720<br>721<br>721<br>721<br>722<br>723<br>725<br>726 |

| 14 | <ul> <li>13.39.1 RXSDQ FIFOs losing ATM cell alignment</li> <li>13.40 System Interface Error Recovery</li> <li>13.40.1 UTOPIA Level 3 Transmit Interface Misalignment Recovery</li> <li>13.40.2 UTOPIA Level 3 Receive Interface Misalignment Recovery</li> <li>13.40.3 UTOPIA Level 3 Transmit Clock (TFCLK) Error Recovery</li> <li>13.40.4 UTOPIA Level 3 Receive Clock (RFCLK) Error Recovery</li> <li>13.40.5 POS Level 3 Transmit (TFCLK) Error Recovery</li> <li>13.40.6 POS Level 3 Receive (RFCLK) Error Recovery</li> <li>13.41.1 TAP Controller</li> <li>13.41.2 States</li> <li>13.41.3 Instructions</li> </ul> | 719<br>719<br>720<br>720<br>720<br>721<br>721<br>722<br>723<br>725<br>726<br>727 |

| 1         | 4.3 Receive SONET Path Alarms                           | 729 |

|-----------|---------------------------------------------------------|-----|

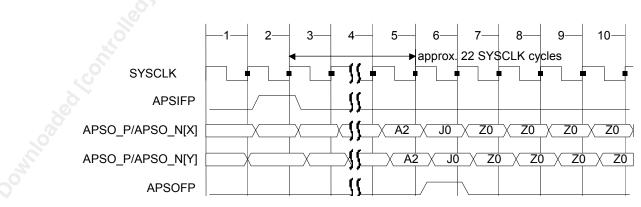

| 1         | 4.4 Incoming APS Serial TelecomBus                      |     |

| 1         | 4.5 Outgoing APS Serial TelecomBus                      |     |

| 1         | 4.6 ATM UTOPIA Level 3 System Interface                 |     |

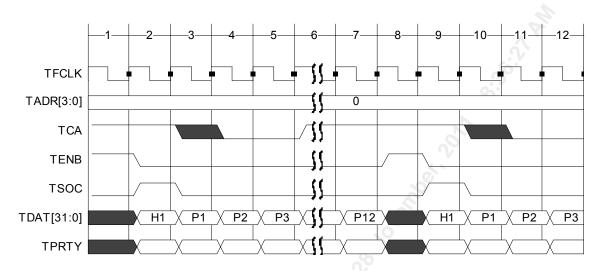

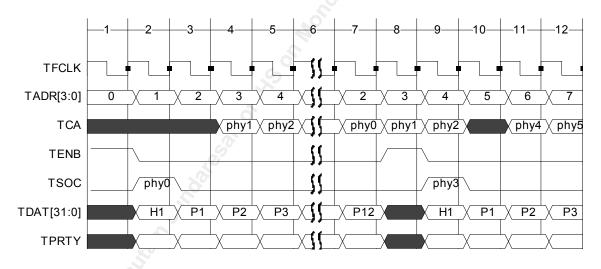

|           | 14.6.1 Transmit UL3 Interface                           | 731 |

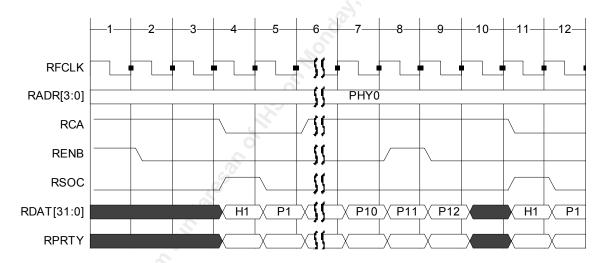

|           | 14.6.2 Receive UL3 Interface                            | 732 |

| 1         | 4.7 Packet over SONET (POS) Level 3 System Interface    | 734 |

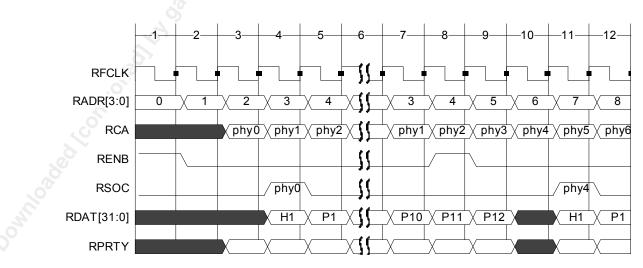

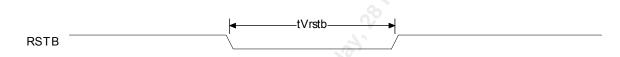

|           | 14.7.1 Transmit PL3 Interface                           | 734 |

|           | 14.7.2 Receive PL3 Interface                            | 735 |

| 15 A      | bsolute Maximum Ratings                                 | 737 |

| 16 F      | Power Information                                       | 738 |

| 1         | 6.1 Power Requirements                                  | 738 |

|           | D.C. Characteristics                                    |     |

| 18 A      | .C. Timing Characteristics                              | 743 |

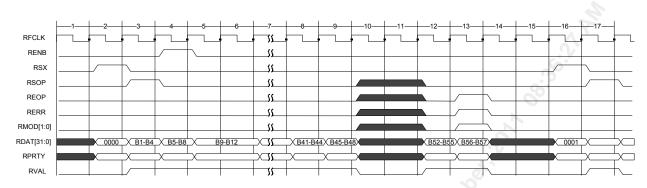

| 1         | 8.1 Reset Pulse Width Timing Characteristics            | 743 |

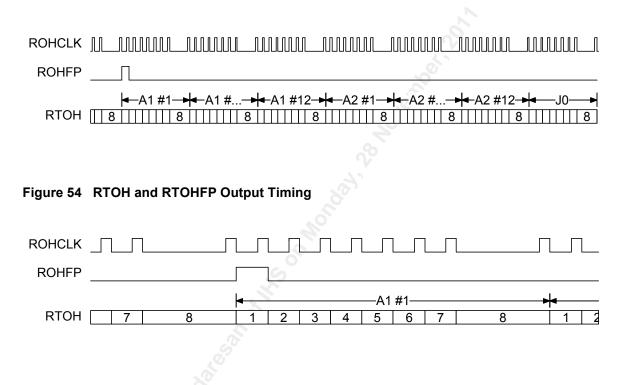

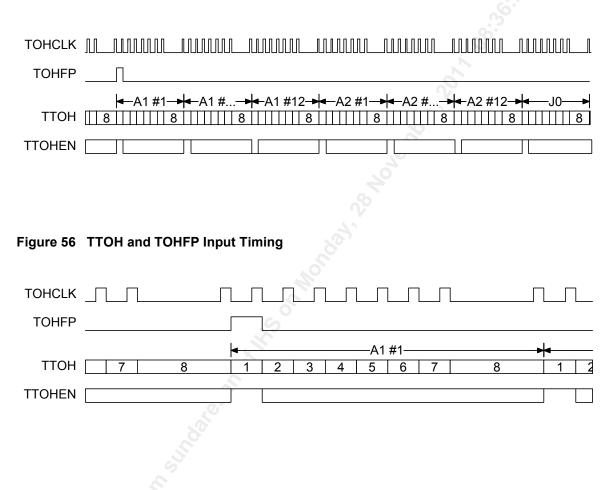

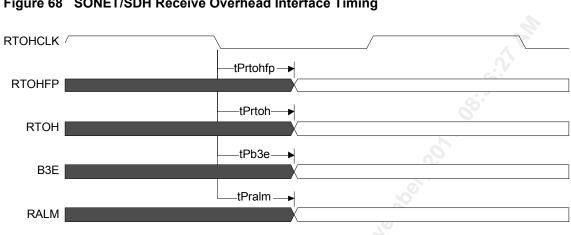

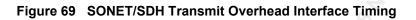

| 1         | 8.2 SONET/SDH Overhead Interface Timing Characteristics | 743 |

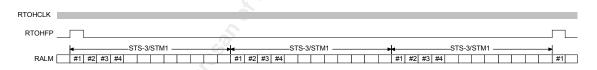

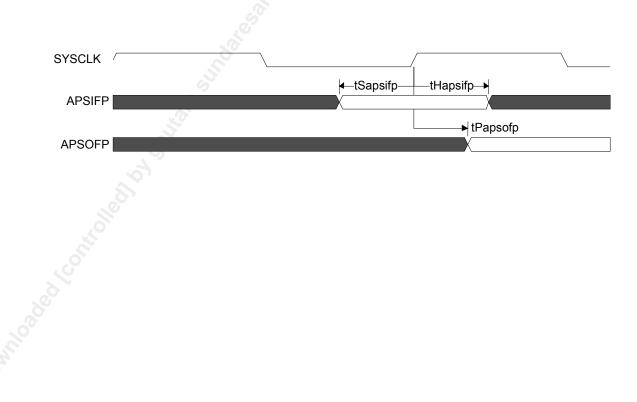

| 1         | 8.3 APS Port Interface Timing Characteristics           | 744 |

| 1         | 8.4 OC-48 Interface Timing Characteristics              | 746 |

| 1         | 8.5 OC-12 and OC-3 Interface Timing Characteristics     | 747 |

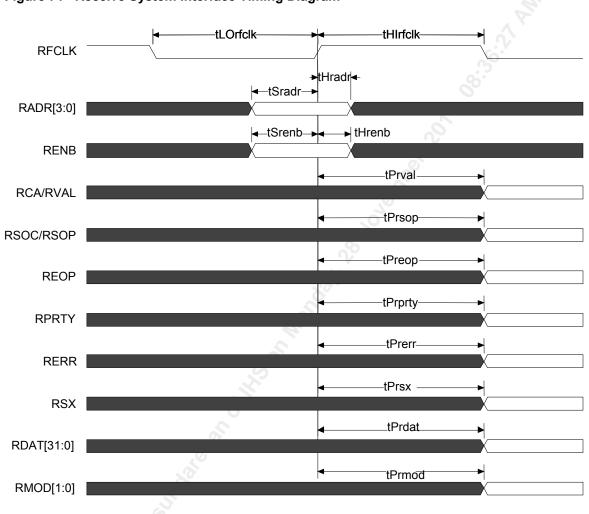

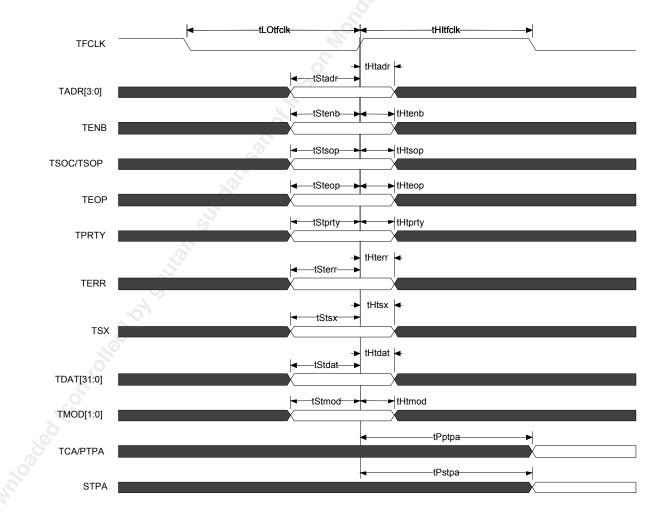

| 1         | 8.6 System Interface Timing                             | 747 |

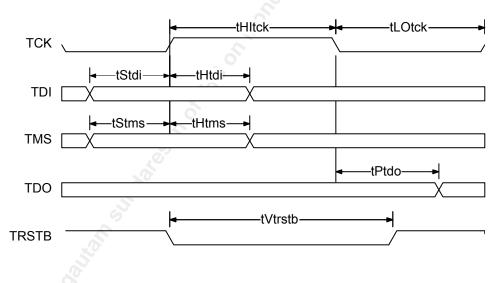

| 1         | 8.7 JTAG Test Port Timing                               | 751 |

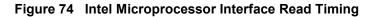

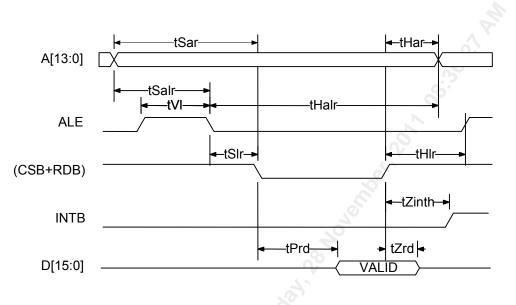

| 1         | 8.8 Microprocessor Interface Timing Characteristics     | 752 |

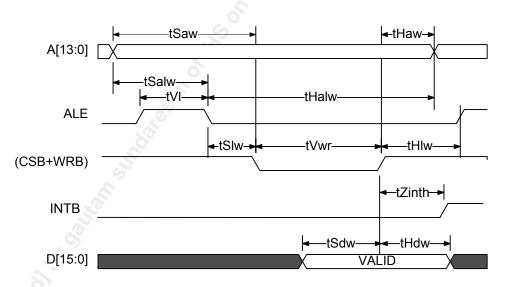

| 19 T      | hermal Information                                      |     |

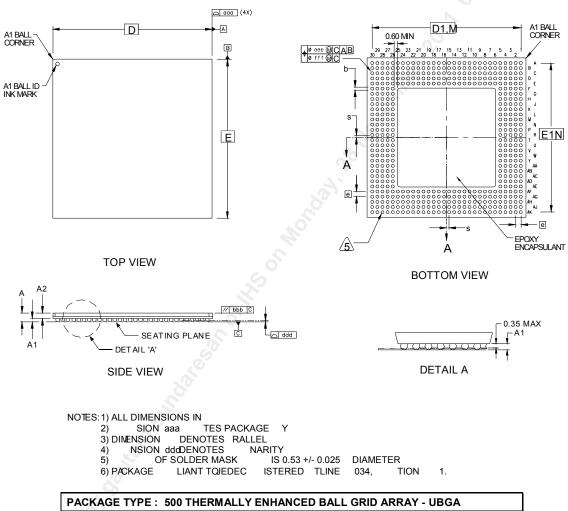

| 20 N      | lechanical Information                                  | 757 |

| Notes     | 3                                                       |     |

| Commonded |                                                         |     |

# **List of Registers**

| Register 0000H: S/UNI MULTI-48 DEVICE ID Register                                              | 13/ |

|------------------------------------------------------------------------------------------------|-----|

| Register 0001H: S/UNI MULTI-48 Manufacturer Code and Revision Number                           |     |

| Register 0002H: S/UNI MULTI-48 Global Performance Monitor Update and                           |     |

| Clock Activity Monitor.                                                                        | 136 |

| Register 0003H: S/UNI MULTI-48 Master Software Resets Register                                 | 137 |

| Register 0004H: S/UNI MULTI-48 Master Configuration Register #1                                | 140 |

| Register 0005H: S/UNI MULTI-48 Master Configuration Register #2                                | 142 |

| Register 0006H: S/UNI MULTI-48 Line Side Receive Configuration                                 | 144 |

| Register 0007H: S/UNI MULTI-48 Line Side Transmit Configuration                                | 146 |

| Register 0008H: S/UNI MULTI-48 Diagnostic                                                      | 148 |

| Register 0009H: S/UNI MULTI-48 Transmit PAIS Enable                                            | 150 |

| Register 000AH: S/UNI MULTI-48 APS X-Bar Configuration                                         | 151 |

| Register 000BH: S/UNI MULTI-48 Master Interrupt Status #1                                      | 152 |

| Register 000CH: S/UNI MULTI-48 Master Interrupt Status #2                                      | 153 |

| Register 000DH: S/UNI MULTI-48 Master Interrupt Status #3                                      | 154 |

| Register 000EH: S/UNI MULTI-48 Master Interrupt Status #4                                      | 155 |

| Register 000FH: S/UNI MULTI-48 Master Interrupt Status #5                                      | 156 |

| Register 0010H: S/UNI MULTI-48 Master Interrupt Status #6                                      | 158 |

| Register 0011H: S/UNI MULTI-48 Master Interrupt Status #7                                      | 160 |

| Register 0012H: S/UNI MULTI-48 Master Interrupt Status #8                                      | 162 |

| Register 0013H: S/UNI MULTI-48 System Side Receive and Transmit                                |     |

| Configuration                                                                                  |     |

| Register 0014H: S/UNI MULTI-48 General Purpose Configuration #2                                | 165 |

| Register 0015H: S/UNI MULTI-48 APSIFP Enable and APS Input TelecomBus<br>Synchronization Delay |     |

| Register 0016H: S/UNI MULTI-48 APS Output TelecomBus Synchronization                           |     |

| Delay                                                                                          |     |

| Register 0017H: S/UNI MULTI-48 Rx APS J0 FIFO Interrupt Enable                                 |     |

| Register 0018H: S/UNI MULTI-48 Rx APS J0 FIFO Interrupt Status                                 |     |

| Register 0019H: S/UNI MULTI-48 APS SMART Framing Configuration                                 |     |

| Register 001AH: S/UNI MULTI-48 Miscellaneous Defect Configuration #1                           | 172 |

| Register 001BH: S/UNI MULTI-48 Miscellaneous Defect Configuration #2                           | 173 |

| Register 001CH: S/UNI MULTI-48 Miscellaneous Defect Configuration #3                           | 175 |

| Register 001DH: S/UNI MULTI-48 Miscellaneous Defect Configuration #4                           | 177 |

| Register 001EH: S/UNI MULTI-48 Free Register                                                   |     |

| Register 0020H: Rx2488 Analog Interrupt Status                                                 | 179 |

| Register 0021H: Rx2488 Analog Interrupt Control                                          | 181 |

|------------------------------------------------------------------------------------------|-----|

| Register 0022H: Rx2488 Analog CRU Control                                                | 183 |

| Register 0023H: Rx2488 Analog CRU Clock Training Configuration and Status                | 185 |

| Register 0024H: Rx2488 Analog PRBS Control                                               | 188 |

| Register 0030H: Quad 622 Rx MABC General Control Register                                | 190 |

| Register 0031H: Quad 622 Rx MABC Control Register                                        | 191 |

| Register 0033H: Quad 622 Rx MABC Interrupt Enable Register                               |     |

| Register 0034H: Quad 622 Rx MABC Interrupt Status Register                               | 194 |

| Register 0035H 0435H 0835H 0C35H: Quad 622 Rx MABC Channel Control Register              | 196 |

| Register 0036H 0436H 0836H 0C36H: Quad 622 Rx Channel Data Path<br>Control Register      | 197 |

| Register 0037H 0437H 0837H 0C37H: Quad 622 Rx Channel Data Path PRBS<br>Control Register | 200 |

| Register 0038H 0438H 0838H 0C38H: Quad 622 Rx Channel Data Interrupt<br>Status Register  | 201 |

| Register 0039H 0439H 0839H 0C39H: Quad 622 Rx Channel Data Path PRBS<br>Status Register  | 203 |

| Register 0040H: SRLI Configuration                                                       | 205 |

| Register 0060H 0460H 0860H 0C60H: SBER Configuration                                     | 206 |

| Register 0061H 0461H 0861H 0C61H: SBER Status                                            | 208 |

| Register 0062H 0462H 0862H 0C62H: SBER Interrupt Enable                                  | 209 |

| Register 0063H 0463H 0863H 0C63H: SBER Interrupt Status                                  | 210 |

| Register 0064H 0464H 0864H 0C64H: SBER SF BERM Accumulation Period (LSB)                 | 211 |

| Register 0065H 0465H 0865H 0C65H: SBER SF BERM Accumulation Period (MSB)                 | 212 |

| Register 0066H 0466H 0866H 0C66H: SBER SF BERM Saturation Threshold (LSB)                | 213 |

| Register 0067H 0467H 0867H 0C67H: SBER SF BERM Saturation Threshold (MSB)                | 214 |

| Register 0068H 0468H 0868H 0C68H: SBER SF BERM Declaring Threshold (LSB)                 | 215 |

| Register 0069H 0469H 0869H 0C69H: SBER SF BERM Declaring Threshold (MSB)                 | 216 |

| Register 006AH 046AH 086AH 0C6AH: SBER SF BERM Clearing Threshold (LSB)                  | 217 |

| Register 006BH 046BH 086BH 0C6BH: SBER SF BERM Clearing Threshold (MSB)                  | 218 |

| Register 006CH 046CH 086CH 0C6CH: SBER SD BERM Accumulation Period (LSB)                 | 219 |

|                                                                                          |     |

|                                                                | -48 ASSP Telecom Standard Product Data Sheet<br>Released |

|----------------------------------------------------------------|----------------------------------------------------------|

| Register 006DH 046DH 086DH 0C6DH: SBER SD<br>(MSB)             |                                                          |

| Register 006EH 046EH 086EH 0C6EH: SBER SD<br>(LSB)             |                                                          |

| Register 006FH 046FH 086FH 0C6FH: SBER SD (<br>(MSB)           |                                                          |

| Register 0070H 0470H 0870H 0C70H: SBER SD E<br>(LSB)           |                                                          |

| Register 0071H 0471H 0871H 0C71H: SBER SD E<br>(MSB)           |                                                          |

| Register 0072H 0472H 0872H 0C72H: SBER SD E<br>(LSB)           |                                                          |

| Register 0073H 0473H 0873H 0C73H: SBER SD E<br>(MSB)           |                                                          |

| Register 0080H 0480H 0880H 0C80H: RRMP Con                     | figuration227                                            |

| Register 0081H 0481H 0881H 0C81H: RRMP Stat                    | us                                                       |

| Register 0082H 0482H 0882H 0C82H: RRMP Inter                   | rrupt Enable232                                          |

| Register 0083H 0483H 0883H 0C83H: RRMP Inter                   | rrupt Status233                                          |

| Register 0084H 0484H 0884H 0C84H: RRMP Rec                     | eive APS236                                              |

| Register 0085H 0485H 0885H 0C85H: RRMP Rec                     | eive SSM237                                              |

| Register 0086H 0486H 0886H 0C86H: RRMP AIS                     | Enable                                                   |

| Register 0087H 0487H 0887H 0C87H: RRMP Sec                     | tion BIP Error Counter240                                |

| Register 0088H 0488H 0888H 0C88H: RRMP Line                    | BIP Error Counter (LSB)                                  |

| Register 0089H 0489H 0889H 0C89H: RRMP Line                    | BIP Error Counter (MSB)242                               |

| Register 008AH 048AH 088AH 0C8AH: RRMP Lin                     | e REI Error Counter (LSB)243                             |

| Register 008BH 048BH 088BH 0C8BH: RRMP Lin                     | e REI Error Counter (MSB)244                             |

| Register 00A0H 04A0H 08A0H 0CA0H: RTTP SEC                     | CTION Indirect Address245                                |

| Register 00A1H 04A1H 08A1H 0CA1H: RTTP SEC                     | CTION Indirect Data247                                   |

| Register 00A2H 04A2H 08A2H 0CA2H: RTTP SEC<br>Status           |                                                          |

| Register 00A3H 004A3H 08A3H 0CA3H: RTTP SE<br>Interrupt Enable |                                                          |

| Register 00A4H 04A4H 08A4H 0CA4H: RTTP SEC<br>Interrupt Status |                                                          |

| Register 00A5H 04A5H 08A5H 0CA5H: RTTP SEC<br>Status           |                                                          |

| Register 00A6H 04A6H 08A6H 0CA6H: RTTP SEC<br>Interrupt Enable | CTION Trace Mismatch                                     |

| Register 00A7H 04A7H 08A7H 0CA7H: RTTP SEC<br>Interrupt Status |                                                          |

| Indirect Register 00H: RTTP SECTION Trace Cont                 |                                                          |

| Indirect Register 40H to 7FH: RTTP SECTION Captured Trace                          | . 256 |

|------------------------------------------------------------------------------------|-------|

| Indirect Register 80H to BFH: RTTP SECTION Accepted Trace                          | . 257 |

| Indirect Register C0H to FFH: RTTP SECTION Expected Trace                          | . 258 |

| Register 00C0H 04C0H 08C0H 0CC0H: RTTP PATH Indirect Address                       |       |

| Register 00C1H 04C1H 08C1H 0CC1H: RTTP PATH Indirect Data                          | . 261 |

| Register 00C2H 04C2H 08C2H 0CC2H: RTTP PATH Trace Unstable Status                  | . 262 |

| Register 00C3H 04C3H 08C3H 0CC3H: RTTP PATH Trace Unstable Interrupt<br>Enable     | . 263 |

| Register 00C4H 04C4H 08C4H 0CC4H: RTTP PATH Trace Unstable Interrupt<br>Status     | . 264 |

| Register 00C5H 04C5H 08C5H 0CC5H: RTTP PATH Trace Mismatch Status                  | . 265 |

| Register 00C6H 04C6H 08C6H 0CC6H: RTTP PATH Trace Mismatch Interrupt<br>Enable     | . 266 |

| Register 00C7H 04C7H 08C7H 0CC7H: RTTP PATH Trace Mismatch Interrupt<br>Status     | . 267 |

| Indirect Register 00H: RTTP PATH Trace Configuration                               | . 268 |

| Indirect Register 40H to 7FH: RTTP PATH Captured Trace                             | . 270 |

| Indirect Register 80H to BFH: RTTP PATH Accepted Trace                             | . 271 |

| Indirect Register C0H to FFH: RTTP PATH Expected Trace                             | . 272 |

| Register 0100H 0500H 0900H 0D00H: RHPP Indirect Address                            | . 273 |

| Register 0101H 0501H 0901H 0D01H: RHPP Indirect Data                               | . 275 |

| Indirect Register 00H: RHPP Pointer Interpreter Configuration                      | . 276 |

| Indirect Register 01H: RHPP Error Monitor Configuration                            | . 278 |

| Indirect Register 02H: RHPP Pointer Value and ERDI                                 | . 281 |

| Indirect Register 03H: RHPP Captured and Accepted PSL                              | . 282 |

| Indirect Register 04H: RHPP Expected PSL and PDI                                   | . 283 |

| Indirect Register 05H: RHPP Pointer Interpreter Status                             | . 284 |

| Indirect Register 06H: RHPP Path BIP Error Counter                                 | . 286 |

| Indirect Register 07H: RHPP Path REI Error Counter                                 | . 287 |

| Indirect Register 08H: RHPP Path Negative Justification Event Counter              | . 288 |

| Indirect Register 09H: RHPP Path Positive Justification Event Counter              | . 289 |

| Register 0102H 0502H 0902H 0D02H: RHPP Reserved                                    | . 290 |

| Register 0103H 0503H 0903H 0D03H: RHPP Counters Update                             | . 291 |

| Register 0104H 0504H 0904H 0D04H: RHPP Path Interrupt Status                       | . 292 |

| Register 0105H 0505H 0905H 0D05H: RHPP Pointer Concatenation<br>Processing Disable | . 293 |

|                                                                                    |       |

| Register 0108H 0110H 0118H 0120H 0128H 0130H 0138H 0140H 0148H<br>0150H 0158H 0160H 0508H 0510H 0518H 0520H 0528H 0530H 0538H<br>0540H 0548H 0550H 0558H 0560H 0908H 0910H 0918H 0920H 0928H<br>0930H 0938H 0940H 0948H 0950H 0958H 0960H 0D08H 0D10H 0D18H<br>0D20H 0D28H 0D30H 0D38H 0D40H 0D48H 0D50H 0D58H 0D60H:<br>RHPP STS-1/STM-0 #N (Where N=1 to 48) Pointer Interpreter Status              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Register 0109H 0111H 0119H 0121H 0129H 0131H 0139H 0141H 0149H<br>0151H 0159H 0161H 0509H 0511H 0519H 0521H 0529H 0531H 0539H<br>0541H 0549H 0551H 0559H 0561H 0909H 0911H 0919H 0921H 0929H<br>0931H 0939H 0941H 0949H 0951H 0959H 0961H 0D09H 0D11H 0D19H<br>0D21H 0D29H 0D31H 0D39H 0D41H 0D49H 0D51H 0D59H 0D61H:<br>RHPP STS-1/STM-0 #N (where N=1 to 48) Pointer Interpreter Interrupt<br>Enable |  |

| Register 010AH 0112H 011AH 0122H 012AH 0132H 013AH 0142H 014AH<br>0152H 015AH 0162H 050AH 0512H 051AH 0522H 052AH 0532H 053AH<br>0542H 054AH 0552H 055AH 0562H 090AH 0912H 091AH 0922H 092AH<br>0932H 093AH 0942H 094AH 0952H 095AH 0962H 0D0AH 0D12H 0D1AH<br>0D22H 0D2AH 0D32H 0D3AH 0D42H 0D4AH 0D52H 0D5AH 0D62H:<br>RHPP STS-1/STM-0 #N (where N=1 to 48) Pointer Interpreter Interrupt<br>Status |  |

| Register 010BH 0113H 011BH 0123H 012BH 0133H 013BH 0143H 014BH<br>0153H 015BH 0163H 050BH 0513H 051BH 0523H 052BH 0533H 053BH<br>0543H 054BH 0553H 055BH 0563H 090BH 0913H 091BH 0923H 092BH<br>0933H 093BH 0943H 094BH 0953H 095BH 0963H 0D0BH 0D13H 0D1BH<br>0D23H 0D2BH 0D33H 0D3BH 0D43H 0D4BH 0D53H 0D5BH 0D63H:<br>RHPP STS-1/STM-0 #N (where N=1 to 48) Error Monitor Status                    |  |

| Register 010CH 0114H 011CH 0124H 012CH 0134H 013CH 0144H 014CH<br>0154H 015CH 0164H 050CH 0514H 051CH 0524H 052CH 0534H 053CH<br>0544H 054CH 0554H 055CH 0564H 090CH 0914H 091CH 0924H 092CH<br>0934H 093CH 0944H 094CH 0954H 095CH 0964H 0D0CH 0D14H 0D1CH<br>0D24H 0D2CH 0D34H 0D3CH 0D44H 0D4CH 0D54H 0D5CH 0D64H:<br>RHPP STS-1/STM-0 #N (where N=1 to 48) Error Monitor Interrupt Enable          |  |

| Register 010DH 0115H 011DH 0125H 012DH 0135H 013DH 0145H 014DH<br>0155H 015DH 0165H 050DH 0515H 051DH 0525H 052DH 0535H 053DH<br>0545H 054DH 0555H 055DH 0565H 090DH 0915H 091DH 0925H 092DH<br>0935H 093DH 0945H 094DH 0955H 095DH 0965H 0D0DH 0D15H 0D1DH<br>0D25H 0D2DH 0D35H 0D3DH 0D45H 0D4DH 0D55H 0D5DH 0D65H:<br>RHPP STS-1/STM-0 #N (where N=1 to 48) Error Monitor Interrupt Status          |  |

| Register 0200H 0600H 0A00H 0E00H: RSVCA Indirect Address                                                                                                                                                                                                                                                                                                                                               |  |

| Register 0201H 0601H 0A01H 0E01H: RSVCA Indirect Data                                                                                                                                                                                                                                                                                                                                                  |  |

| Register 0202H 0602H 0A02H 0E02H: RSVCA Reserved #1                                                                                                                                                                                                                                                                                                                                                    |  |

| Register 0203H 0603H 0A03H 0E03H: RSVCA Positive Justification Interrupt<br>Status                                                                                                                                                                                                                                                                                                                     |  |

| Register 0204H 0604H 0A04H 0E04H: RSVCA Negative Justification Interrupt<br>Status                                                                                                                                                                                                                                                                                                                     |  |

| Register 0205H 0605H 0A05H 0E05H: RSVCA FIFO Overflow Interrupt Status                                                                                                                                                                                                                                                                                                                                 |  |

| Register 0206H 0606H 0A06H 0E06H: RSVCA FIFO Underflow Interrupt<br>Status                                                                                                                                                                                                                                                                                                                             |  |

| Register 0207H 0607H 0A07H 0E07H: RSVCA Pointer Justification Interru<br>Enable |        |

|---------------------------------------------------------------------------------|--------|

| Register 0208H 0608H 0A08H 0E08H: RSVCA FIFO Interrupt Enable                   |        |

| Register 0209H 0609H 0A09H 0E09H: RSVCA Reserved #2                             |        |

| Register 020AH 060AH 0A0AH 0E0AH: RSVCA Reserved #3                             |        |

| Register 020BH 060BH 0A0BH 0E0BH: RSVCA Performance Monitor Trig                | Jger   |

| Indirect Register 00H: RSVCA Positive Justifications Performance Monitor        |        |

| Indirect Register 01H: RSVCA Negative Justifications Performance Monito         | or 324 |

| Indirect Register 02H: RSVCA Diagnostic/Configuration                           |        |

| Register 0260H 0660H 0A60H 0E60H: SARC Indirect Path Register                   |        |

| Register 0262H 0662H 0A62H 0E62H: SARC Section Configuration                    |        |

| Register 0263H 0663H 0A63H 0E63H: SARC Section SALM Enable                      |        |

| Register 0264H 0664H 0A64H 0E64H: SARC Section RLAISINS Enable                  |        |

| Register 0265H 0665H 0A65H 0E65H: SARC Section TLRDIINS Enable                  |        |

| Register 0268H 0668H 0A68H 0E68H: SARC Path Configuration                       |        |

| Register 0269H 0669H 0A69H 0E69H: SARC Path RALM Enable                         |        |

| Register 026AH 066AH 0A6AH 0E6AH: SARC Path RPAISINS Enable                     |        |

| Register 0270H 0670H 0A70H 0E70H: SARC LOP Pointer Status                       |        |

| Register 0271H 0670H 0A71H 0E71H: SARC LOP Pointer Interrupt Enable             | e 343  |

| Register 0272H 0672H 0A72H 0E72H: SARC LOP Pointer Interrupt Status             | 3      |

| Register 0273H 0673H 0A73H 0E73H: SARC AIS Pointer Status                       |        |

| Register 0274H 0674H 0A74H 0E74H: SARC AIS Pointer Interrupt Enable             |        |

| Register 0275H 0675H 0A75H 0E75H: SARC AIS Pointer Interrupt Status             |        |

| Register 0280H 0680H 0A80H 0E80H: R8TD APS Control and Status                   |        |

| Register 0281H 0681H 0A81H 0E81H: R8TD APS Interrupt Status                     |        |

| Register 0282H 0682H 0A82H 0E82H: R8TD APS Line Code Violation Co               | unt352 |

| Register 0283H 0683H 0A83H 0E83H: R8TD APS Analog Control 1                     |        |

| Register 0284H 0684H 0A84H 0E84H: R8TD APS Analog Control 2                     | 355    |

| Register 0290H: CSTR Control                                                    |        |

| Register 0291H: CSTR Interrupt Enable and APS CSU Lock Status                   | 357    |

| Register 0292H: CSTR APS CSU Lock Interrupt Indication                          |        |

| Register 02A0H: RDLL Configuration                                              |        |

| Register 02A1H: RDLL Reserved #1                                                |        |

| Register 02A2H: RDLL Reserved #2                                                |        |

| Register 02A3H: RDLL Control Status                                             |        |

| Register 0300H: RSTSI Control Page Indirect Address                             |        |

| Register 0301H: RSTSI Control Page Indirect Data                                |        |

| Register 0302H: RSTSI Configuration                                                   |     |

|---------------------------------------------------------------------------------------|-----|

| Register 0303H: RSTSI Interrupt Status                                                |     |

| Register 0310H 0710H 0B10H 0F10H: RCFP Configuration                                  |     |

| Register 0311H 0711H 0B11H 0F11H: RCFP Interrupt Enable                               |     |

| Register 0312H 0712H 0B12H 0F12H: RCFP Interrupt Indication and Status                |     |

| Register 0313H 0713H 0B13H 0F13H: RCFP Minimum Packet Length                          |     |

| Register 0314H 0714H 0B14H 0F14H: RCFP Maximum Packet Length                          |     |

| Register 0315H 0715H 0B15H 0F15H: RCFP LCD Count Threshold                            |     |

| Register 0316H 0716H 0B16H 0F16H: RCFP Receive Idle Cell Header and<br>Mask           |     |

| Register 0317H 0717H 0B17H 0F17H: RCFP Receive Byte/Idle Cell Counter<br>(LSB)        |     |

| Register 0318H 0718H 0B18H 0F18H: RCFP Receive Byte/Idle Cell Counter                 |     |

| Register 0319H 0719H 0B19H 0F19H: RCFP Receive Byte/Idle Cell Counter (MSB)           |     |

| Register 031AH 071AH 0B1AH 0F1AH: RCFP Receive Packet/Cell Counter<br>(LSB)           |     |

| Register 031BH 071BH 0B1BH 0F1B: RCFP Receive Packet/Cell Counter<br>(MSB)            |     |

| Register 031CH 071CH 0B1CH 0F1CH: RCFP Receive Erroneous FCS/HCS<br>Counter           |     |

| Register 031DH 071DH 0B1DH 0F1DH: RCFP Receive Aborted Packet<br>Counter              |     |

| Register 031EH 071EH 0B1EH 0F1EH: RCFP Receive Minimum Length<br>Packet Error Counter |     |

| Register 031FH 071FH 0B1FH 0F1FH: RCFP Receive Maximum Length<br>Packet Error Counter |     |

| Register 0320H: RXSDQ FIFO Reset                                                      |     |

| Register 0321H: RXSDQ FIFO Interrupt Enable                                           |     |

| Register 0323H: RXSDQ FIFO Overflow Port and Interrupt Indication                     |     |

| Register 0324H: RXSDQ FIFO EOP Error Port and Interrupt Indication                    |     |

| Register 0325H: RXSDQ FIFO SOP Error Port and Interrupt Indication                    | 395 |

| Register 0328H: RXSDQ FIFO Indirect Address                                           |     |

| Register 0329H: RXSDQ FIFO Indirect Configuration                                     |     |

| Register 032AH: RXSDQ FIFO Indirect Data Available Threshold                          | 400 |

| Register 032BH: RXSDQ FIFO Indirect Cell and Packet Count                             | 401 |

| Register 032CH: RXSDQ FIFO Cells and Packets Accepted Aggregate Count (LSB)           | 402 |

| Register 032DH: RXSDQ FIFO Cells and Packets Accepted Aggregate Count (MSB)           | 403 |

| Register 032EH: RXSDQ FIFO Cells and Packets Dropped Aggregate Count                           | 404 |

|------------------------------------------------------------------------------------------------|-----|

| Register 0330H: RXPHY Configuration                                                            | 405 |

| Register 0331H: RXPHY Interrupt Status                                                         | 407 |

| Register 0332H: RXPHY Interrupt Enable                                                         | 408 |

| Register 0333H: RXPHY Indirect Burst Size                                                      | 409 |

| Register 0334H: RXPHY Calendar Length                                                          | 411 |

| Register 0335H: RXPHY Calendar Indirect Address Data                                           | 412 |

| Register 0336H: RXPHY Data Type Field                                                          | 414 |

| Register 0340H 0740H 0B40H 0F40H: RTDP Indirect Channel Select                                 | 415 |

| Register 0341H 0741H 0B41 0F41H: RTDP Indirect Configuration                                   | 417 |

| Register 0342H 0742H 0B42 0F42H: RTDP Indirect Minimum Packet Length and Bit Order             | 421 |

| Register 0343H 0743H 0B43H 0F43H: RTDP Indirect Maximum Packet Length                          | 423 |

| Register 0344H 0744H 0B44 0F44H: RTDP Indirect LCD Count Threshold                             | 424 |

| Register 0345H 0745H 0B45H 0F45H: RTDP Indirect Idle Cell Header and<br>Mask                   | 425 |

| Register 0346H 0746H 0B46H 0F46H: RTDP Indirect Receive Byte/Idle Cell<br>Counter (LSB)        | 427 |

| Register 0347H 0747H 0B47H 0F47H: RTDP Indirect Receive Byte/Idle Cell<br>Counter (MSB)        | 428 |

| Register 0348H 0748H 0B48H 0F48H: RTDP Indirect Packet/Cell Counter (LSB)                      | 429 |

| Register 0349H 0749H 0B49H 0F49H: RTDP Indirect Packet/Cell Counter<br>(MSB)                   | 430 |

| Register 034AH 074AH 0B4AH 0F4AH: RTDP Indirect Receive Erroneous<br>FCS/HCS Counter           | 431 |

| Register 034BH 074BH 0B4BH 0F4BH: RTDP Indirect Receive Aborted Packet<br>Counter              | 432 |

| Register 034CH 074CH 0B4CH 0F4CH: RTDP Indirect Receive Minimum<br>Length Packet Error Counter | 433 |

| Register 034DH 074DH 0B4DH 0F4DH: RTDP Indirect Receive Maximum<br>Length Packet Error Counter | 434 |

| Register 0350H 0750H 0B50H 0F50H + <i>n</i> : RTDP Interrupt Enable ( <i>n</i> = 0, 1)         | 435 |

| Register 0356H 0756H 0B56H 0F56H + n: RTDP Interrupt Indication (n = 0, 1)                     |     |

| Register 035CH 075CH 0B5CH 0F5CH: RTDP OOF Status                                              | 439 |

| Register 035DH 075DH 0B5DH 0F5DH: RTDP LOF Status                                              | 440 |

| Register 0360H 0760H 0B60H 0F60H: RCAS12 Channel Disable                                       | 441 |

| Register 0361H 0761H 0B61H 0F61H: RCAS12 Channel Loopback Enable                               |     |

| Register 0362H 0762H 0B62H 0F62H + x: RCAS12 Timeslot x Configuration (x                       |     |

| = 0H to BH)                                                                                    | 443 |

| Register 0370H 0770H 0B70H 0F70H: SFBA Configuration and Status                                      | 445 |

|------------------------------------------------------------------------------------------------------|-----|

| Register 0371H 0771H 0B71H 0F71H: SFBA Interrupt Enable                                              | 447 |

| Register 0372H 0772H 0B72H 0F72H: SFBA Interrupt Status                                              | 448 |

| Register 0380H 0780H 0B80H 0F80H: DCRU155_622 Configuration                                          | 449 |

| Register 0381H 0781H 0B81H 0F81H: DCRU155_622 Status and Interrupt<br>Enable                         | 450 |

| Register 0382H 0782H 0B82H 0F82H: DCRU155_622 Interrupt Status                                       | 452 |

| Register 0383H 0783H 0B83H 0F83H: DCRU155_622 Powerdown                                              | 453 |

| Register 1020H: Tx2488 Analog Control/Status                                                         | 454 |

| Register 1021H: TX2488 ABC Control                                                                   | 458 |

| Register 1022H: TX2488 Fixed Pattern Register                                                        | 461 |

| Register 1030H: Quad 622 Tx MABC CSUT Control Register                                               | 462 |

| Register 1031H: Quad 622 Tx CSUT Clock Detector Control Register                                     | 463 |

| Register 1032H: Quad 622 Tx CSUT Interrupt Status Register                                           | 464 |

| Register 1033H 1433H 1833H 1C33H: Quad 622 Tx MABC and JAT622<br>Channel Control and Status Register | 465 |

| Register 1034H 1434H 1834H 1C34H: Quad 622 Tx Channel Data Path and PRBS Control Register            | 467 |

| Register 1040H: STLI Clock Configuration                                                             | 468 |

| Register 1060H 1460H 1860H 1C60H: JAT622 Configuration                                               | 469 |

| Register 1061H 1461H 1861H 1C61H: JAT622 Configuration and Interrupt<br>Enable                       | 470 |

| Register 1062H 1462H 1862H 1C62H: JAT622 Status                                                      | 472 |

| Register 1063H 1463H 1863H 1C63H: JAT622 Powerdown                                                   | 473 |

| Register 1080H 1480H 1880H 1C80H: TRMP Configuration                                                 | 474 |