1.25Gbps Burst-Mode Limiting Amplifier with Ultra-Fast Signal Assert Timing

#### **General Description**

The SY88149NDL is a high-sensitivity, burst-mode capable limiting post amplifier designed for Optical Line Terminal (OLT) receiver applications. The SY88149NDL satisfies the strict timing restrictions of the GPON standards by providing ultra-fast Loss-of-Signal (LOS) or Signal-Detect (SD) output. Auto Reset and Manual Reset options are provided to control LOS/SD output timing. For increased flexibility, this device also includes an option to select between LOS or SD output. The device can be connected to burst-mode capable transimpedance amplifiers (TIAs) using AC or DC coupling.

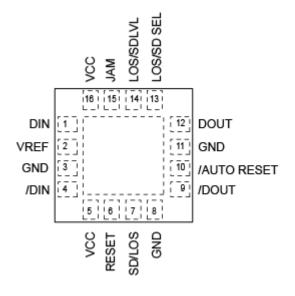

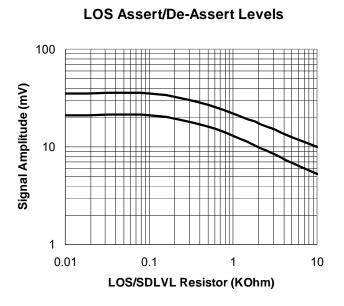

The SY88149NDL generates a high-gain LOS or SD LVTTL output. A programmable LOS/SD level set pin (LOS/SD<sub>LVL</sub>) sets the sensitivity of the input amplitude detection. When LOS/SD SEL pin is left open or tied to Vcc, JAM is active high, SD is selected and asserts high if the input amplitude rises above the threshold sets by LOS/SD<sub>LVL</sub> and de-asserts low otherwise. When LOS/SD SEL pin is selected and asserts low, LOS is selected and asserts low if the input amplitude rises above the threshold sets by LOS/SD<sub>LVL</sub> and de-asserts low if the input amplitude rises above the threshold sets by LOS/SD<sub>LVL</sub> and de-asserts low if the input amplitude rises above the threshold sets by LOS/SD<sub>LVL</sub> and de-asserts high otherwise. The LOS/SD output can be fed back to the JAM input to maintain output stability under an invalid signal conditions. Typically, 4–5 dB SD hysteresis is provided to prevent chattering.

The SY88149NDL also features a selectable proprietary Noise Discriminator that aids by filtering out input signals that do not qualify as a 1.25Gbps GPON preamble signal in the initial startup phase. This feature minimizes false SD Asserts that can be triggered by random noise.

The SY88149NDL operates from a single +3.3V power supply, over temperatures ranging from  $-40^{\circ}$ C to  $+85^{\circ}$ C. With its wide bandwidth and high gain, signals up to 1.25Gbps and as small as 5mVpp can be amplified to drive devices with LVPECL inputs.

All support documentation can be found on Micrel's web site at: <u>www.micrel.com</u>.

#### Features

- <5ns SD Assert (LOS Deassert) time

- Option to AUTO RESET or manual RESET LOS/SD output

- Selectable LOS/SD output option

- High-sensitivity LOS/SD signal detect

- Low-noise LVPECL data outputs

- · Squelching function to maintain output stability

- Programmable LOS/SD level set (LOS/SD<sub>LVL</sub>)

- 5mVpp input sensitivity

- 1.25Gbps operation

- Single 3.3V power supply

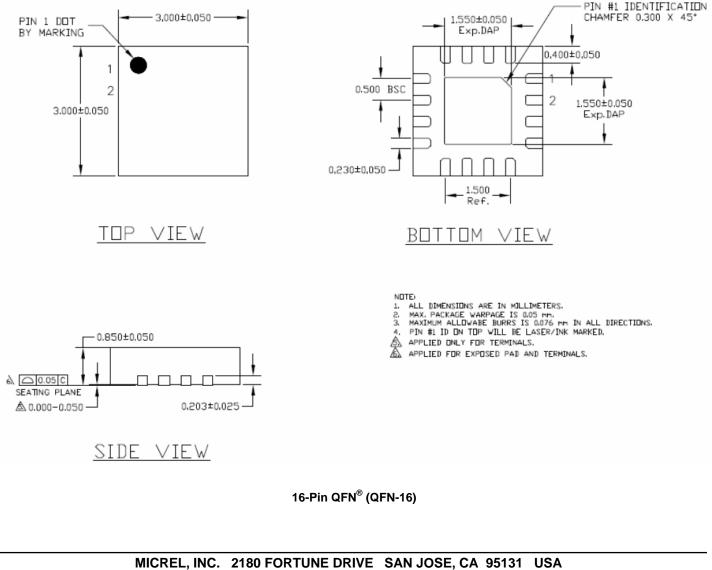

- Available in a 16-pin (3mm  $\times$  3mm) QFN<sup>®</sup> package

#### **Applications**

- GE-PON/GPON OLT

- Gigabit Ethernet

- Fibre Channel

- OC-3/12/24 SONET/SDH

- High-gain line driver and line receiver

- Low-gain TIA interface

#### Markets

- FTTH PON

- Datacom/Telecom

- Optical transceiver

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

### **Ordering Information**

| Part Number                    | Package Type     | Operating Range | Package Marking                      |

|--------------------------------|------------------|-----------------|--------------------------------------|

| SY88149NDLMG                   | Lead-Free QFN-16 | Industrial      | 149N with Pb-Free bar-line indicator |

| SY88149NDLMG TR <sup>(1)</sup> | Lead-Free QFN-16 | Industrial      | 149N with Pb-Free bar-line indicator |

Notes:

1. Tape and Reel.

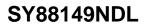

### **Pin Configuration**

16-Pin QFN<sup>®</sup> (QFN-16)

### Truth Table for SD/LOS Select and Noise Discriminator function

| LOS/SDSEL PIN | LOS/SD SELECTION | NOISE DISCRIMINATOR | INPUT TO JAM | OUTPUTS  |

|---------------|------------------|---------------------|--------------|----------|

| 0Ω to VCC     | SD               | Enabled             | HIGH         | Enabled  |

| 0Ω to VCC     | SD               | Enabled             | LOW          | Disabled |

| 16KΩ to VCC   | SD               | Disabled            | HIGH         | Enabled  |

| 16KΩ to VCC   | SD               | Disabled            | LOW          | Disabled |

| 16KΩ to GND   | LOS              | Disabled            | HIGH         | Disabled |

| 16KΩ to GND   | LOS              | Disabled            | LOW          | Enabled  |

| 0Ω to GND     | LOS              | Enabled             | HIGH         | Disabled |

| 0Ω to GND     | LOS              | Enabled             | LOW          | Enabled  |

### **Pin Description**

| Pin Number | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4       | DIN, /DIN   | Differential Data Inputs. If AC-coupled, terminate each pin to $V_{REF}$ with 50 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                              |

| 2          | VREF        | Reference Voltage Output. Typically V <sub>CC</sub> – 1.3V.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3, 11, 8   | GND         | Device Ground. Exposed pad must be soldered (or equivalent) to the same potential as the ground pins.                                                                                                                                                                                                                                                                                                                                                                    |

| 10         | /AUTO RESET | LVTTL Input. This pin is internally connected to a $25k\Omega$ pull-up resistor and defaults to HIGH. When this pin is LOW or tied to ground, the /AUTO RESET function is enabled and SD deasserts or LOS asserts within 120ns (typical) after the last high-to-low transition of the burst input. When this pin is left floating or tied high, the AUTO RESET function is disabled and the SD deassert or LOS assert must be forced by using the manual RESET function. |

| 5, 16      | VCC         | Positive power supply. Bypass with 0.1uF    0.01uF low ESR capacitors. 0.01uF capacitors should be as close as possible to VCC pins.                                                                                                                                                                                                                                                                                                                                     |

| 6          | RESET       | LVTTL Input. Apply a high-level signal (>2V) to this pin to reset the SD deassert time or LOS assert within 5ns. RESET defaults to LOW if left floating. If the /AUTO RESET function is not used, this RESET function needs to be used to quickly deassert the SD or assert LOS. This pin is internally connected to a $25k\Omega$ pull-down resistor and defaults to LOW.                                                                                               |

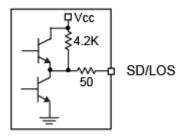

| 7          | SD/LOS      | LVTTL Output. Signal detect (SD) asserts high when the data input amplitude rises above the threshold sets by SD <sub>LVL</sub> . Conversely, loss-of-signal (LOS) deasserts low when the data input amplitude rises above the threshold set by LOS/SD <sub>LVL</sub> .                                                                                                                                                                                                  |

| 12, 9      | DOUT, /DOUT | LVPECL Outputs. When JAM disables the device, output DOUT is forced to logic LOW and output /DOUT is forced to logic HIGH.                                                                                                                                                                                                                                                                                                                                               |

| 13         | LOS/SD SEL  | Allows the user to select between whether LOS or SD is outputted on the LOS/SD pin. Also controls the polarity of the JAM input. When SD is selected, JAM is active HIGH and LOS/SD (Pin 7) operates as signal detect. Conversely, when LOS is selected, JAM is active LOW and LOS/SD operates as loss-of-signal. This pin is internally connected to a $25k\Omega$ pull-up resistor and defaults to HIGH (SD output selected).                                          |

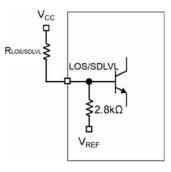

| 14         | LOS/SDLVL   | Voltage Input. Sets the LOS/SD level. A resistor from this pin to $V_{CC}$ sets the threshold for the data input amplitude at which LOS/SD will be asserted.                                                                                                                                                                                                                                                                                                             |

| 15         | JAM         | LVTTL Input. This JAM input acts as a squelch function and switches its polarity depending on LOS/SD SEL status. When LOS is selected, this pin is active LOW. When SD is selected, this pin is Active HIGH. To create a squelch function, connect JAM to LOS/SD. When JAM disables the device, output Q is forced to logic LOW and output /Q is forced to logic HIGH. Note that this input is internally connected to a $25k\Omega$ pull-up resistor.                   |

### Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>CC</sub> )     | 0V to +4.0V                         |

|---------------------------------------|-------------------------------------|

| Input Voltage (DIN, /DIN)             | 0 to V <sub>CC</sub>                |

| Output Current (I <sub>OUT</sub> )    |                                     |

| Continuous                            | ±50mA                               |

| Surge                                 | ±100mA                              |

| EN Voltage                            | 0 to V <sub>CC</sub>                |

| V <sub>REF</sub> Current              | 800µA to +500µA                     |

| SD <sub>LVL</sub> Voltage             | V <sub>REF</sub> to V <sub>CC</sub> |

| Lead Temperature (soldering, 20s)     | 260°C                               |

| Storage Temperature (T <sub>s</sub> ) | <i>–</i> 65°C to +150°C             |

## **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>CC</sub> )                     | +3.0V to +3.6V  |

|-------------------------------------------------------|-----------------|

| Ambient Temperature (T <sub>A</sub> )                 | 40°C to +85°C   |

| Junction Temperature (T <sub>J</sub> )                | –40°C to +125°C |

| Junction Thermal Resistance <sup>(3)</sup>            |                 |

| $QFN^{\mathbb{R}}_{I}(\theta_{JA})$ Still-Air         | 60°C/W          |

| $QFN^{	extsf{B}}$ ( $\Psi_{JB}$ ) Junction-to-Board . | 38°C/W          |

### **DC Electrical Characteristics**

$V_{CC}$  = 3.0 to 3.6V;  $T_A$  = -40°C to +85°C, typical values at  $V_{CC}$  = 3.3V,  $T_A$  = 25°C.

| Symbol                 | Parameter                         | Condition          | Min.                    | Тур.                    | Max.                    | Units |

|------------------------|-----------------------------------|--------------------|-------------------------|-------------------------|-------------------------|-------|

| Icc                    | Power Supply Current              | No output load     |                         | 77                      | 105                     | mA    |

| LOS/SD <sub>LVL</sub>  | LOS/SD <sub>LVL</sub> Voltage     |                    | V <sub>REF</sub>        |                         | V <sub>CC</sub>         | V     |

| V <sub>OH</sub>        | LVPECL Output HIGH Voltage        | 50  to $V_{CC}-2V$ | V <sub>CC</sub> - 1.085 | $V_{CC} - 0.955$        | $V_{CC} - 0.880$        | V     |

| V <sub>OL</sub>        | LVPECL Output LOW Voltage         | 50  to $V_{CC}-2V$ | V <sub>CC</sub> - 1.830 | V <sub>CC</sub> - 1.705 | V <sub>CC</sub> – 1.555 | V     |

| IOFFSET                | Input Offset Voltage              |                    |                         |                         | 1                       | mV    |

| VIHCMR(Diff)           | Common-Mode Range (Differential)  | Note 4             | GND + 1.4               |                         | Vcc                     |       |

| V <sub>IHCMR(SE)</sub> | Common-Mode Range (Single Ended ) | Note 4             | GND + 1.2               |                         | Vcc                     | V     |

| V <sub>REF</sub>       | Reference Voltage                 |                    | V <sub>CC</sub> - 1.48  | V <sub>CC</sub> - 1.32  | V <sub>CC</sub> – 1.16  | V     |

| I <sub>DIN</sub>       | Input Sink Current (DIN & /DIN)   | No Input Load      | 1.5                     | 7                       | 14                      | uA    |

### LVTTL DC Electrical Characteristics

$V_{CC}$  = 3.0 to 3.6V;  $T_A$  = -40°C to +85°C, typical values at  $V_{CC}$  = 3.3V,  $T_A$  = 25°C.

| Symbol                | Parameter                     | Condition                            | Min. | Тур. | Max.       | Units |

|-----------------------|-------------------------------|--------------------------------------|------|------|------------|-------|

| VIH                   | LVTTL Input HIGH Voltage      |                                      | 2.0  |      |            | V     |

| VIL                   | LVTTL Input LOW Voltage       |                                      |      |      | 0.8        | V     |

| I <sub>IH_JAM</sub>   | JAM Input HIGH Current        | $V_{IN} = V_{CC}$<br>$V_{IN} = 2.7V$ |      |      | 20<br>20   | μA    |

| I <sub>IL_JAM</sub>   | JAM Input LOW Current         | V <sub>IN</sub> = 0.5V               | -0.3 |      |            | mA    |

| I <sub>IH_AR</sub>    | /AUTORESET Input HIGH Current | $V_{IN} = V_{CC}$<br>$V_{IN} = 2.7V$ |      |      | 100<br>20  | μA    |

| I <sub>IL_AR</sub>    | /AUTORESET Input LOW Current  | V <sub>IN</sub> = 0.5V               | -0.3 |      |            | mA    |

| I <sub>IH_RESET</sub> | RESET Input HIGH Current      | $V_{IN} = V_{CC}$<br>$V_{IN} = 2.7V$ |      |      | 300<br>250 | μA    |

| $I_{IL\_RESET}$       | RESET Input LOW Current       | V <sub>IN</sub> = 0.5V               | 0    |      |            | mA    |

| V <sub>OH</sub>       | SD/LOS Output HIGH Level      | I <sub>OH</sub> = -100uA             | 2.1  | 2.7  |            | V     |

| V <sub>OL</sub>       | SD/LOS Output LOW Level       | I <sub>OL</sub> = 100uA              |      | 0.35 | 0.5        | V     |

### **AC Electrical Characteristics**

| $V_{CC} = 3.0V$ to 3.6V; F | $R_{IOAD} = 50\Omega$ to Vcc – | - 2V; T <sub>A</sub> = -40°C to +85°C.         |   |

|----------------------------|--------------------------------|------------------------------------------------|---|

|                            |                                | <b>_</b> , , , , , , , , , , , , , , , , , , , | • |

| Symbol                               | Parameter                                          | Condition                                                  | Min. | Тур. | Max. | Units             |

|--------------------------------------|----------------------------------------------------|------------------------------------------------------------|------|------|------|-------------------|

| t <sub>r</sub> , t <sub>f</sub>      | Output Rise/Fall Time (20% to 80%)                 | Note 5                                                     |      |      | 260  | ps                |

| t <sub>JAM</sub>                     | JAM Enable/Disable Time                            |                                                            |      |      | 2    | ns                |

| t <sub>AUTORESET</sub>               | SD Deassert or LOS Assert with Auto Reset Enabled. |                                                            | 100  | 120  | 150  | ns                |

| t <sub>RESET</sub>                   | RESET Disable Time                                 | Note 6                                                     |      |      | 5    | ns                |

| t <sub>ON</sub>                      | SD Assert Time/LOS Deassert time                   |                                                            |      |      | 5    | ns                |

| •                                    | Deterministic                                      | Note 7                                                     |      | 15   |      | ps <sub>PP</sub>  |

| t <sub>JITTER</sub>                  | Random                                             | Note 8                                                     |      | 5    |      | ps <sub>RMS</sub> |

| VID                                  | Differential Input Voltage Swing                   | Figure 1                                                   | 5    |      | 1800 | mV <sub>PP</sub>  |

| V <sub>OD</sub>                      | Differential Output Voltage Swing                  | $V_{ID} \ge 18mV_{PP}$                                     |      | 1500 |      | mV <sub>PP</sub>  |

| SD <sub>AL</sub> /LOS <sub>DL</sub>  | Low SD Assert/LOS De- Assert Level                 | $R_{LOS/SDLVL}$ = 10k $\Omega$ , Notes <sup>(9, 10)</sup>  |      | 4    |      | mV <sub>PP</sub>  |

| SD <sub>DL</sub> //LOS <sub>AL</sub> | Low SD Deassert /LOS Assert Level                  | $R_{LOS/SDLVL}$ = 10k $\Omega$ , Notes <sup>(10, 12)</sup> |      | 3    |      | $mV_{PP}$         |

| HYS∟                                 | Low SD/LOS Hysteresis                              | $R_{LOS/SDLVL}$ = 10k $\Omega$ , Notes <sup>(11, 12)</sup> |      | 5    |      | dB                |

| SD <sub>AM</sub> /LOS <sub>DM</sub>  | Medium SD Assert/LOS Deassert Level                | $R_{LOS/SDLVL}$ = 5k $\Omega$ , Notes <sup>(10, 12)</sup>  | 9.5  | 12.5 | 16   | $mV_{PP}$         |

| SD <sub>DM</sub> /LOS <sub>AM</sub>  | Medium SD Deassert /LOS Assert Level               | $R_{LOS/SDLVL}$ = 5k $\Omega$ , Notes <sup>(10,12)</sup>   | 5    | 7    | 8.5  | $mV_{PP}$         |

| HYS <sub>M</sub>                     | Medium SD/LOS Hysteresis                           | $R_{LOS/SDLVL}$ = 5k $\Omega$ , Notes <sup>(11, 12)</sup>  | 3.0  | 4.5  | 6.5  | dB                |

| SD <sub>AH</sub> /LOS <sub>DH</sub>  | High SD Assert/LOS De- Assert Level                | $R_{LOS/SDLVL}$ = 50 $\Omega$ , Notes <sup>(10, 12)</sup>  | 27   | 35   | 45   | $mV_{PP}$         |

| SD <sub>DH</sub> /LOS <sub>AH</sub>  | High SD Deassert/ LOS Assert Level                 | $R_{LOS/SDLVL}$ = 50 $\Omega$ , Notes <sup>(10, 12)</sup>  | 15   | 21   | 28   | $mV_{PP}$         |

| HYS <sub>H</sub>                     | High SD/LOS Hysteresis                             | $R_{LOS/SDLVL}$ = 50 $\Omega$ , Notes <sup>(11, 12)</sup>  | 2.0  | 3    | 6    | dB                |

| B-3dB                                | 3dB Bandwidth                                      |                                                            |      | 750  |      | MHz               |

| A <sub>V(Diff)</sub>                 | Differential Voltage Gain                          |                                                            |      | 48   |      | dB                |

| S <sub>21</sub>                      | Single-Ended Small-Signal Gain                     |                                                            |      | 42   |      | dB                |

Notes:

1. Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

- 3. Thermal performance assumes the use of a 4-layer PCB. Exposed pad must be soldered to the device's most negative potential on the PCB.

- 4. VIHCMR is defined as common mode range of the VIH level on DIN and /DIN. It is the most positive level of the differential input signal when driven differentially or is the reference level on Din\ when being driven single ended.

- 5. Amplifier in limiting mode. Input is a 200MHz square wave.

- 6. The time between applying RESET and outputs being disabled.

- 7. Deterministic jitter measured using 1.25Gbps K28.7 pattern,  $V_{ID}$  = 10m $V_{PP}$ .

- 8. Random jitter measured using 1.25Gbps K28.7 pattern,  $V_{ID}$  = 10m $V_{PP}$ .

- 9. SD is the opposite polarity of LOS. Therefore, an SD Assert parameter is equivalent to a LOS deassert parameter and vice versa.

- 10. See "Typical Operating Characteristics" for a graph showing how to choose a particular R<sub>LOS/SDLVL</sub> for a particular assert and its associated deassert amplitude.

- 11. This specification defines electrical hysteresis as 20log(SD assert/SD deassert). The ratio between optical hysteresis and electrical hysteresis is found to vary between 1.5 and 2 depending upon the level of received optical power and ROSA characteristics. Based upon that ratio, the optical hysteresis corresponding to the electrical hysteresis range 3dB 6dB, shown in the AC Characteristics table, will be 1.5dB-4dB optical hysteresis.

- 12. All SD Assert (LOS De-Assert) level, SD De-assert (LOS Assert) level and Hysteresis specifications listed above are specified using a 1010 PON Preamble data pattern at the specified data rate of 1.288 Gbps.

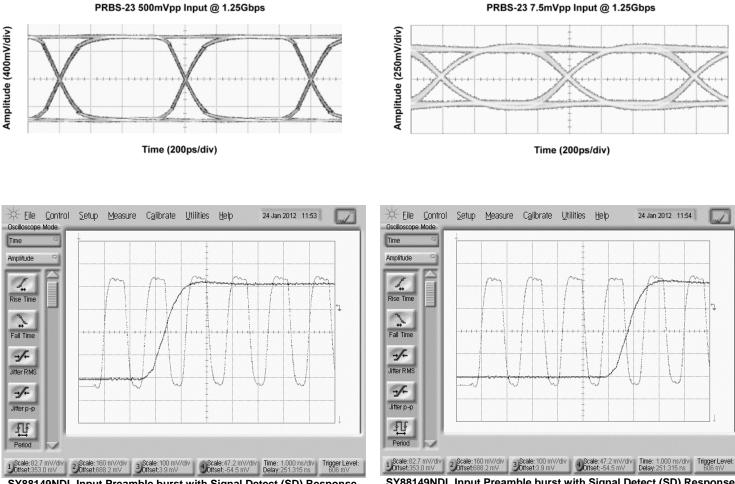

#### **Typical Operating Characteristics**

$V_{CC}$  = 3.3V,  $T_A$  = 25°C,  $R_L$  = 50 $\Omega$  to  $V_{CC}$  – 2V, unless otherwise stated.

SY88149NDL Input Preamble burst with Signal Detect (SD) Response, with Noise Discriminator disengaged

SY88149NDL Input Preamble burst with Signal Detect (SD) Response, with Noise Discriminator engaged

#### LOS/SDLVL RESET LOS 0 LVTTL LOS/SD AR BUFFER SD EDGE/LEVEL 1 DETECTOR /AUTO RESET LOS/SDSEL OE JAM DIN DOUT LIMITING LVPECL AMPLIFIER BUFFER /DIN /DOUT

#### Functional Block Diagram

### **Detailed Description**

The SY88149NDL is a high-sensitivity limiting post amplifier which operates on a +3.3V power supply over the industrial temperature range. Signals with data rates up to 1.25Gbps and as small as 5mVpp can be amplified. Depending on the LOS/SD SEL option, the SY88149NDL can generate an SD or LOS output, and allow feedback to the JAM input for output stability. LOS/SD<sub>LVL</sub> sets the sensitivity of the input amplitude detection.

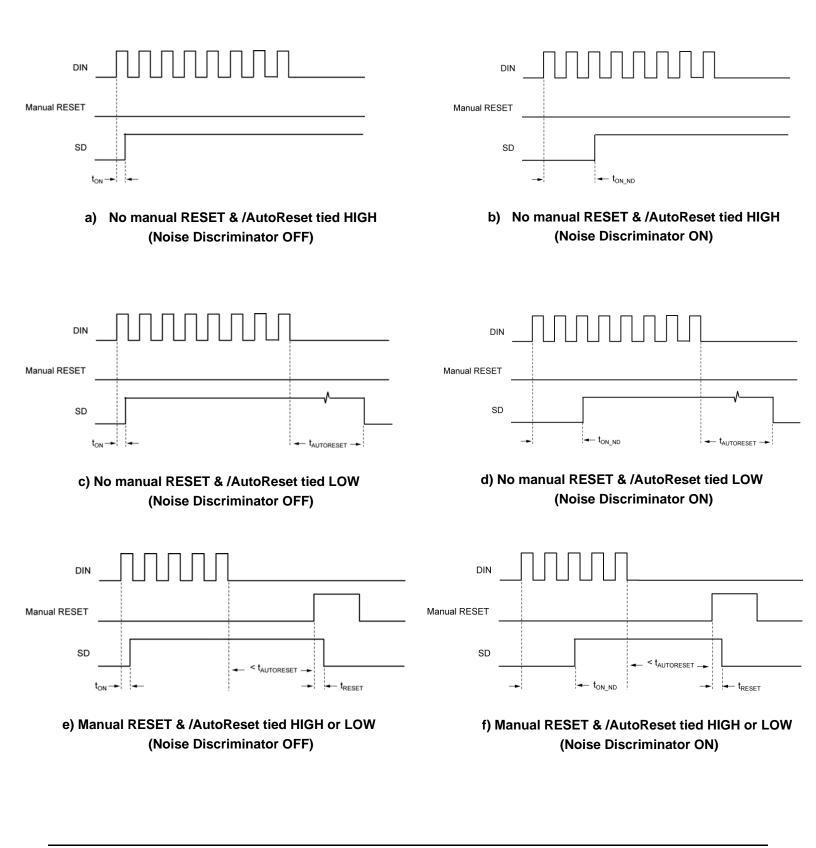

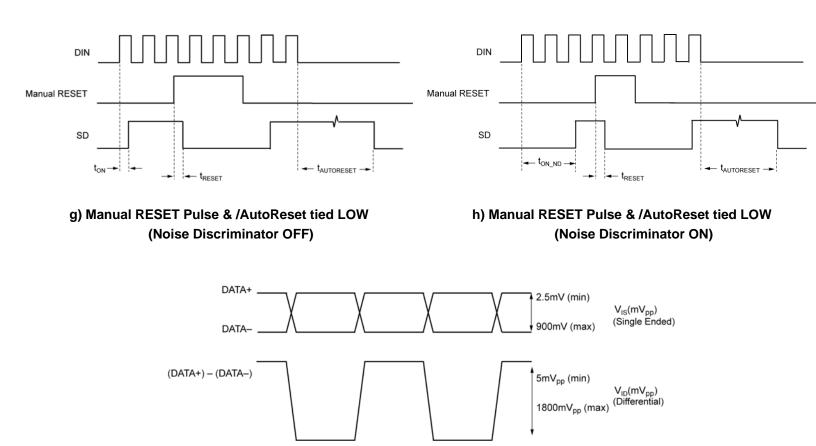

To satisfy the stringent timing requirements of the GPON specifications, the signal detect circuit offers 5ns SD assert (LOS deassert) time and the option to deassert SD (assert LOS) using the /AUTO RESET or manual RESET function. When /AUTO RESET is enabled, SD deasserts/LOS asserts automatically within 120ns after the last high-to-low transition of the input burst. When the /AUTORESET function is disabled, the SD deassert/LOS assert time can be reset by using the provided RESET pin.

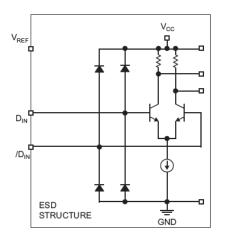

#### Input Buffer

Figure 2 shows a simplified schematic of the input stage. The high sensitivity of the input amplifier allows signals as small as 5mVpp to be detected and amplified. The input buffer can allow input signals as large as  $1800mV_{PP}$ . Input signals are linearly amplified with a typically 48dB differential voltage gain until the outputs reach  $1500mV_{PP}$  (typical). Applications requiring the SY88149NDL to operate with high-gain should have the upstream TIA placed as close as possible to the SY88149NDL's input pins. This ensures the best performance of the device.

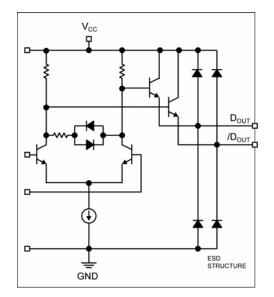

#### **Output Buffer**

The SY88149NDL's LVPECL output buffer is designed to drive 50 $\Omega$  lines. The output buffer requires appropriate termination for proper operation. An external 50 $\Omega$  resistor to V<sub>CC</sub> – 2V for each output pin provides this. Figure 3 shows a simplified schematic of the output stage

#### Loss of Signal/Signal Detect

The SY88149NDL generates a chatter-free Signal-Detect (SD) or Loss of Signal (LOS) LVTTL output, as shown in Figure 4. A highly-sensitive signal detect circuit is used to determine that the input amplitude is too small to be considered a valid input. LOS asserts high if the input amplitude falls below the threshold sets by LOS/SDLVL and deasserts low otherwise. SD asserts high if the input amplitude rises above threshold set by LOS/SDLVL and deasserts low otherwise. LOS/SD can be fed back to the JAM input to maintain output stability under the absence of an invalid signal condition Typically, a 3dB to 4 dB hysteresis is provided to minimize or prevent chattering.

#### LOS/SD Level Set

A programmable LOS/SD level pin (LOS/SD<sub>LVL</sub>) sets the threshold of the input amplitude detection. Connecting an external resistor between  $V_{CC}$  and LOS/SD<sub>LVL</sub> sets the voltage at LOS/SD<sub>LVL</sub>. This voltage ranges from  $V_{CC}$  to  $V_{REF}$ . The external resistor creates a voltage divider between  $V_{CC}$  and  $V_{REF}$ , as shown in Figure 5. Set the LOS/SD<sub>LVL</sub> voltage closer to  $V_{REF}$  or more sensitive LOS/SD detection or closer to  $V_{CC}$  for higher inputs.

Note that the SY88149NDL is designed for use in the burst mode PON application, where every burst is preceded with several bytes of a 1010 PON preamble pattern. Therefore, the SD Assert (LOS De-assert) is designed to trigger on the first few bits of this preamble pattern and therefore the SD/LOS thresholds outlined in the AC electrical characteristics are specified using this preamble pattern. Once the SD is Asserted (LOS Deasserted), the SD is De-asserted (LOS Asserted) only by the application of a Manual RESET or an AUTO RESET if the Auto Reset is activated, The auto reset asserts a reset approximately 120 nS after the last negative going transition of the data as explained earlier.

#### Noise Discriminator

The noise discriminator feature is intended for the highgain burst-mode TIAs where noise can trigger a false LOS deassert or SD assert while no input data is present. The noise discriminator will filter input data through a series of specialized circuitry that will only trigger LOS/SD on the rising edge of a valid PON 1.244 Gbps preamble bit stream (10101). The SY88149NDL noise discriminator is designed to accept a 1.244 Gbps +/-300 MBPS preamble burst. Any other bit pattern will be rejected. If this part is used at any other data rate, the Noise Discriminator should be disengaged. The noise discriminator, implemented in the edge detector circuit, can be selected or bypassed by selecting the proper resistor value using the settings at LOS/SDSEL pin. Refer to the "Truth Table for SD/LOS select and Noise Discriminator function" found on page 2 for more detailed information.

### **Timing Diagrams**

Figure 1. VIS (single ended) and VID (differential) Definition

Figure 2. Simplified Input Structure

Figure 4. Simplified LOS/SD Output Structure

Figure 3. Simplified Output Structure

Figure 5. Simplified LOS/SD<sub>LVL</sub> Setting Circuit

#### **Package Information**

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2012 Micrel, Incorporated.

# **HBW Datasheet Revision History**

#### Part Number: SY88149NDL

#### Initial Release Date:

| Rev. | Date     | Revisions                                          | Reason                                                         | Engineer |

|------|----------|----------------------------------------------------|----------------------------------------------------------------|----------|

| А    | 4/29/10  | Made from SY88149HL DS                             | New version of part. Contains fixed JAM Tpd & RESET Hysteresis | D. Cheng |

|      | 5/11/10  | Changed Package Marking to<br>"149A" from "149H"   | Mistake left over from 149HL                                   | D. Cheng |

|      |          | Revised AC-table specs                             |                                                                |          |

|      |          | LOS Assert/Deassert                                |                                                                |          |

|      | 8/31/10  | Hysteresis                                         | Design Tweak to address chattering issue                       | D. Cheng |

|      |          | Removed RESET Hyst.                                |                                                                |          |

|      |          | Changed 3dB value                                  |                                                                |          |

|      | 01/7/11  | Added Noise Discriminator description              | New feature                                                    | D. Cheng |

|      | 01/8/11  | Multiple error fixes                               | After peer review                                              | D. Cheng |

|      | 2/11/11  | Added Dieter's comments                            | Only partially completed. Waiting for bench char               | D. Cheng |

|      | 6/9/2011 | Signoff                                            | Signoff purposes                                               | D. Cheng |

|      | 7/1/2011 | Implement sign-off changes                         | Recommended changes from reviewers                             | D. Cheng |

|      | 7/28/11  | Change in EPN from<br>SY88149HAL to SY88149NDL     | Misc. changes in organization, figures and EPN change          | D. Cheng |

|      | 8/11/11  | Add LOS Deassert time waveforms and other art      | Finalize Data sheet.                                           | G.Brown  |

|      | 9/01/11  | Add comments in Noise<br>Discriminator Description | Add Comments to ND description and do minor cleanup            | GBrown   |

|      | 9/31/11  | Update Icc                                         | Update Icc typical to 77 mA/105 mA max                         | GBrown   |

|      | 01/27/12 | Update to make compatible with SY88349NDL          | Upgrade waveforms and add notes and updates to DC/AC tables    | GBrown   |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Limiting Amplifiers category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

HMC750LP4E HMC865LC3 HMC866LC3 SY88403BLEY MAX3747BEUB+T MAX3272AETP+T MAX3711ETG+ MAX3645EEE+ MAX3645EEE+T MAX3861ETG+ SY88993AVKG MAX3748HETE+T SY88083LMG SY88773VMG SY88053CLMG SY88073LMG SY88149HLMG SY88923VKG SY88903VKG-TR SY88903ALKG-TR SY88813VKG SY88303BLMG SY88149NDLMG-TR SY88303BLEY SY88349NDLMG SY88803VKG SY88933VKG SY88053CLMG-TR ONET1191PRGTT ONET4201PARGTR ONET4251PARGTR ONET8501PBRGTR ONET8501PBRGTT ONET1191PRGTR MAX3945ETE+ MAX3748HETE#G16 MAX3268CUB+ SY88943VKG SY88149HALMG MAX3945ETE+T ONET4201PARGTT