# **UTC2000**

## Basic USB Type-C™ Controller

#### **Highlights**

- Transition any existing USB Type-A design to a USB Type-C<sup>™</sup> Downstream Facing Port or any existing Type-B design to a USB Type-C Upstream Facing Port

- Leverage the USB Type-C reversible cable and compact form factor

- · For use with USB 2.0, USB 3.0 or USB 3.1

- Supports legacy, 1.5A, & 3.0A USB Type-C charging profiles

- · Compact 3 x 3mm 16-pin QFN package

- Commercial, industrial, and automotive extended temperature support

- · Requires minimal design effort

#### **Target Applications**

- Laptops

- Desktop PCs

- · Monitors

- USB Hubs

- · USB Wall Chargers

- Industrial

- Automotive

#### **Key Benefits**

- USB Type-C cable connection and orientation detection

- Orientation detection indicator for optional USB switch control

- Powered cable detection with VCONN powered cable supply control

- · CFG SEL pin configurable charging profiles:

- 5V Legacy DFP mode (500mA for USB 2.0, 900mA for USB 3.0/USB 3.1)

- 5V @ 1.5A DFP mode

- 5V @ 3.0A DFP mode

- UFP mode

- · ENABLE pin for host/hub port control

- · VMON pin monitors VBUS overvoltage conditions

- · USB Type-C Audio Adapter detection and control

- OCS# fault input pin

- FAULT\_IND fault indicator output pin

- · Operating Voltage Range:

- 4.5V to 5.5V

- Package

- 16-pin QFN (3 x 3 x 0.9mm)

- Environmental

- Commercial temperature range (0°C to +70°C)

- Industrial temperature range (-40°C to +85°C)

- Extended temperature range (-40°C to +125°C)

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **UTC2000**

## **Table of Contents**

| 1.0 Introduction                        | 4  |

|-----------------------------------------|----|

| 2.0 Pin Descriptions                    | 7  |

| 3.0 Functional Description              |    |

| 4.0 Operational Characteristics         |    |

| 5.0 UTC2000 System Application          |    |

| 6.0 Packaging Information               | 33 |

| Appendix A: Data Sheet Revision History | 37 |

| The Microchip Web Site                  |    |

| Customer Change Notification Service    |    |

| Customer Support                        | 39 |

| Product Identification System           |    |

#### 1.0 INTRODUCTION

#### 1.1 General Description

The USB Type-C<sup>TM</sup> Specification was introduced in August 2014 and substantially expands the capabilities of USB. The key new features include:

- · New Connector

- Smaller Form Factor

- 24 Pins

- Reversible Insertion

- · Simplified Current Capability Marking

- Resistor-divider implementation instead of DP/DM "handshake"

The Microchip UTC2000 USB Type-C controller targets designers who wish to gain the benefits of the small, reversible form factor and elevated charging current abilities of a USB Type-C solution while minimally impacting the overall cost per port.

The UTC2000 USB Type-C controller is a cost-effective, simple solution that facilitates rapid migration of legacy USB 2.0/3.0 designs to the USB Type-C connector. The UTC2000 controller is designed for USB 2.0/3.0 Downstream Facing Port (DFP) and Upstream Facing Port (UFP) applications and performs all of the necessary detection and control required for implementing a basic USB Type-C connector. The UTC2000 features ADCs that monitor the CC1 and CC2 pins of the USB Type-C receptacle to detect various connection events.

In a DFP application, passive cables, powered cables, and USB audio adapters can all be detected. Controls for enabling a USB +5V port power switch, VCONN 5V active cable supply, and audio adapter enable are all included. Additional features include host enable control and overcurrent detection.

In a UFP application, the UTC2000 detects a valid USB Type-C connection, the plug orientation, and the charging capability of the DFP. The UTC2000 also monitors VBUS to ensure a valid VBUS range and detected overcurrent.

The UTC2000 can operate from a single 4.5V-5.5V supply and is available in commercial, industrial and extended temperature range options.

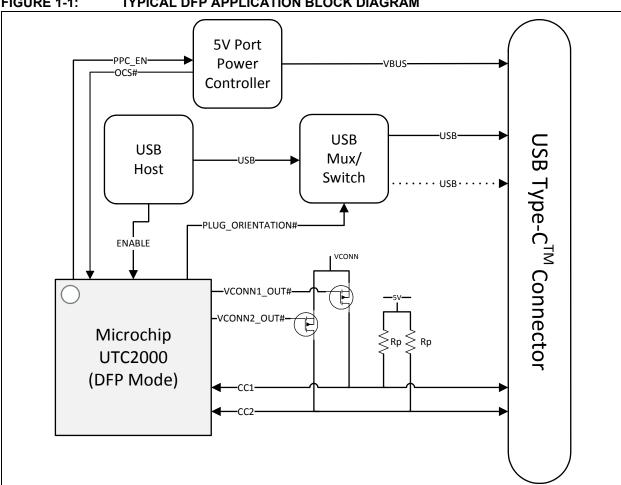

## 1.2 USB Type-C<sup>TM</sup> Downstream Facing Port (DFP) Implementation Overview

A UTC2000 Implementation of a DFP minimally requires 5 major components/circuitry blocks:

- Microchip UTC2000

- A USB 2.0 downstream port (USB 3.0/USB 3.1 may optionally be implemented based upon system requirements)

- A USB Type-C Receptacle

- A 5V Port Power Controller capable of supplying the advertised current capability (advertised with the value of Rp and the pull-up voltage)

- · CC Pin Circuitry:

- Rp Pull-Up Resistors

- VCONN Control/Switching

Note:

A High-Speed or Super Speed USB switch is also recommended but optional. For USB 2.0 applications, this component may be omitted. For USB 3.0/USB 3.1 applications, this component may only be omitted if two USB 3.0/USB 3.1 downstream ports are dedicated for use on the USB Type-C port.

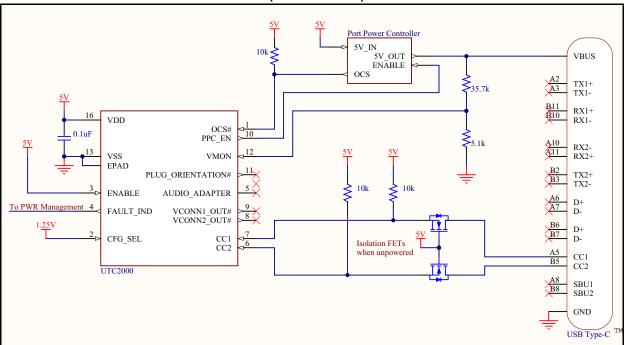

A system diagram utilizing the UTC2000 in a DFP application is shown in Figure 1-1.

#### FIGURE 1-1: TYPICAL DFP APPLICATION BLOCK DIAGRAM

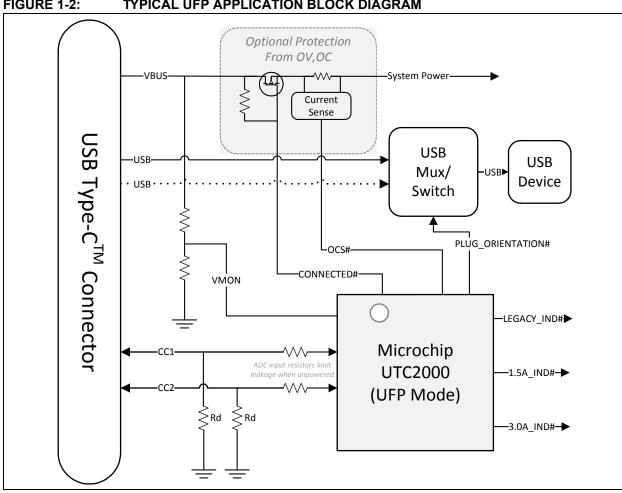

#### 1.3 Type-C Upstream Facing Port (UFP) Implementation Overview

A UTC2000 Implementation of a UFP minimally requires 4 major components/circuitry blocks:

- Microchip UTC2000

- A USB 2.0 upstream port (USB 3.0/USB 3.1 may optionally be implemented based upon system requirements)

- A USB Type-C Receptacle

- · CC Pin Circuitry:

- Rd Pull-Up Resistors

A High-Speed or Super Speed USB switch is also recommended but optional. For USB 2.0 applications, this component may be omitted. For USB 3.0/USB 3.1 applications, this component may not be omitted unless a Microchip Hub with FlexConnect is utilized. Refer to the Microchip USB5734 USB Type-C Evaluation Board for details on implementation.

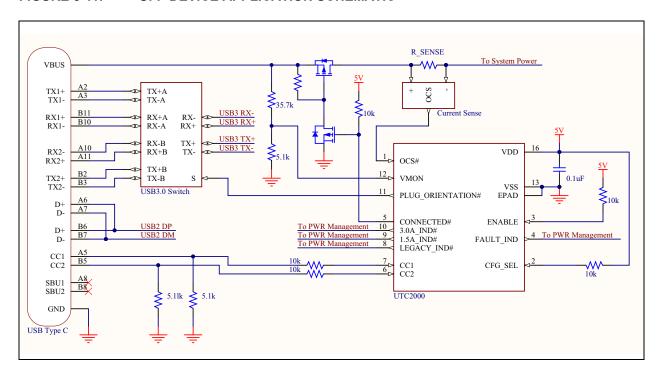

A system diagram utilizing the UTC2000 in a UFP application is shown in Figure 1-2.

FIGURE 1-2: TYPICAL UFP APPLICATION BLOCK DIAGRAM

#### 1.4 **Glossary of Terms**

**TABLE 1-1: GLOSSARY OF TERMS**

| .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ECOCART OF TERMIO                                                                |

|-----------------------------------------|----------------------------------------------------------------------------------|

| Term                                    | Definition                                                                       |

| ADC                                     | Analog to Digital Converter                                                      |

| AFE                                     | Analog Front End                                                                 |

| CC                                      | Generic reference to USB Type-C <sup>TM</sup> Cable / Connector CC1/CC2 pins     |

| DFP                                     | Downstream Facing Port (USB Type-C Cable and Connector Specification definition) |

| DRP                                     | Dual Role Port (USB Type-C Cable and Connector Specification definition)         |

| Microchip                               | Microchip Technology Incorporated                                                |

| POR                                     | Power-On Reset                                                                   |

| USB Type-C                              | USB Type-C Cable / Connector                                                     |

| UFP                                     | Upstream Facing Port (USB Type-C Cable and Connector Specification definition)   |

#### 1.5 References

• USB Type-C<sup>TM</sup> Cable and Connector Specification: http://www.usb.org/developers/docs/

USB Type-C<sup>TM</sup> and USB-C<sup>TM</sup> are trademarks of USB Implementers Forum. Note:

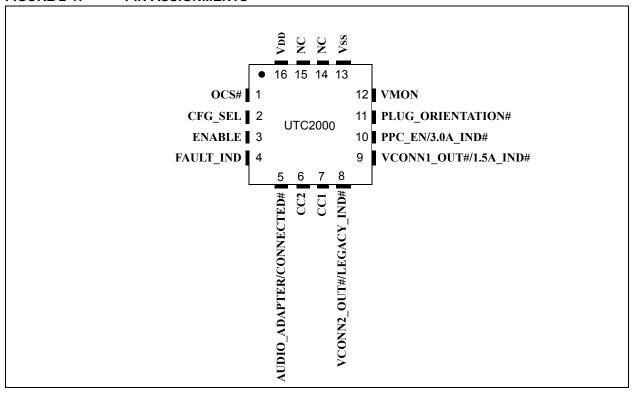

#### 2.0 PIN DESCRIPTIONS

The UTC2000 pin diagram can be seen in Figure 2-1. Table 2-1 provides a pin assignment table. Pin descriptions are provided in **Section 2.2 "Pin Descriptions"**.

#### 2.1 Pin Assignments

FIGURE 2-1: PIN ASSIGNMENTS

TABLE 2-1: PIN ASSIGNMENTS

| ., .,      | 1 114 7400101111121110   |

|------------|--------------------------|

| Pin Number | Pin Name                 |

| 1          | OCS#                     |

| 2          | CFG_SEL                  |

| 3          | ENABLE                   |

| 4          | FAULT_IND                |

| 5          | AUDIO_ADAPTER/CONNECTED# |

| 6          | CC2                      |

| 7          | CC1                      |

| 8          | VCONN2_OUT#/LEGACY_IND#  |

| 9          | VCONN1_OUT#/1.5A_IND#    |

| 10         | PPC_EN/3.0A_IND#         |

| 11         | PLUG_ORIENTATION#        |

| 12         | VMON                     |

| 13         | VSS                      |

| 14         | NC                       |

| 15         | NC                       |

| 16         | VDD                      |

Note 1: The exposed pad should be connected to VSS.

## 2.2 Pin Descriptions

TABLE 2-2: PIN DESCRIPTIONS

| IADLE Z-Z:                 | PIN DESCRIPTIONS |                |                                                                                                                                                                                                                                                                                                                |

|----------------------------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                       | Symbol           | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                    |

|                            |                  | D              | Digital Inputs                                                                                                                                                                                                                                                                                                 |

| Controller<br>Enable       | ENABLE           | IS             | Active high enable signal. The UTC2000 will remain in its default, inactive state unless this pin is asserted high.                                                                                                                                                                                            |

|                            |                  |                | If unused, tie this pin to $\mathbf{VDD}$ through a $10k\Omega$ pull-up resistor.                                                                                                                                                                                                                              |

| Fault Input                | OCS#             | IS<br>(PU)     | This active low signal is asserted by the +5V VBUS power supplying device to notify the UTC2000 when a system fault condition has occurred. Typically, this signal is used for overcurrent or overvoltage conditions, but it can be used for any system related failure.                                       |

|                            |                  |                | All digital control outputs will revert to their default, deasserted state when this pin is asserted. Normal operation will resume after deassertion of this pin.                                                                                                                                              |

|                            |                  |                | After any OCS# assertion, a fault flag will be set and the FAULT_IND pin will assert. This flag is only cleared after a device reset or power cycle.                                                                                                                                                           |

|                            |                  |                | If unused, this pin can be left floating.                                                                                                                                                                                                                                                                      |

|                            |                  | Α              | nalog Inputs                                                                                                                                                                                                                                                                                                   |

| Configuration<br>Selection | CFG_SEL          | ADC            | This analog to digital converter pin is sampled at power-on at Vcfg_samp to place the UTC2000 in either DFP or UFP mode.                                                                                                                                                                                       |

|                            |                  |                | Once in UFP mode, the UTC2000 will always remain in UFP mode and can only switch to DFP mode after a power-on reset.                                                                                                                                                                                           |

|                            |                  |                | Once in DFP mode, the UTC2000 can actively switch between 3.0A, 1.5A, or the default legacy (500mA USB 2.0, 900mA USB 3.0/USB 3.1) DFP modes without power cycling. When switching between DFP modes, the voltage thresholds and ranges for connection detection on the CC1/CC2 pins are modified accordingly. |

|                            |                  |                | Refer to Table 3-1 for additional details.                                                                                                                                                                                                                                                                     |

| VBUS Voltage<br>Monitor    | VMON             | ADC            | This analog to digital converter pin monitors the input voltage on the VBUS pin of the USB receptacle.                                                                                                                                                                                                         |

|                            |                  |                | The UTC2000 will enter the fault state and deassert all outputs if the voltage exceeds 0.8V on the VMON pin (>6.4V on VBUS).                                                                                                                                                                                   |

|                            |                  |                | A fault flag will be set and the FAULT_IND will assert after any overvoltage occurrence. This flag is only cleared after a device reset or power cycle.                                                                                                                                                        |

|                            |                  |                | This pin is required for UFP Modes. If unused in DFP Modes, tie this pin to GND through a $10k\Omega$ pull-down resistor.                                                                                                                                                                                      |

TABLE 2-2: PIN DESCRIPTIONS (CONTINUED)

| ., .= == = = :                            | OLD)              |                |                                                                                                                                                                                                                                                 |  |  |

|-------------------------------------------|-------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name                                      | Symbol            | Buffer<br>Type | Description                                                                                                                                                                                                                                     |  |  |

| CC1 Monitor                               | CC1               | ADC            | This analog to digital converter input pin monitors the USB Type-C <sup>TM</sup> CC1 signal to detect various USB Type-C connections.                                                                                                           |  |  |

|                                           |                   |                | Refer to Table 3-1for additional details.                                                                                                                                                                                                       |  |  |

| CC2 Monitor                               | CC2               | ADC            | This analog to digital converter input pin monitors the USB Type-C CC2 signal to detect various USB Type-C connections.                                                                                                                         |  |  |

|                                           |                   |                | See Table 3-1 for additional details.                                                                                                                                                                                                           |  |  |

|                                           |                   | Di             | gital Outputs                                                                                                                                                                                                                                   |  |  |

| +5V VBUS<br>Power Supply<br>Enable        | PPC_EN            | O25            | <b>DFP Modes Only.</b> Active high output which controls the 5V supply to VBUS. This pin only asserts when a valid USB Type-C connection is detected.                                                                                           |  |  |

| Plug<br>Orientation<br>Indicator          | PLUG_ORIENTATION# | OD25           | This active low output pin indicates the USB Type-C cable plug orientation.                                                                                                                                                                     |  |  |

|                                           |                   |                | This pin remains high in the default unconnected state or when an Rd pull-down resistor is detected on CC1.                                                                                                                                     |  |  |

|                                           |                   |                | The pin will assert low when an Rd pull-down resistor is detected on CC2.                                                                                                                                                                       |  |  |

| CC1 VCONN<br>Supply Control               | VCONN1_OUT#       | OD25           | DFP Modes Only. Open drain, active low VCONN supply control to CC1 for supplying 5V to active cable circuitry. See Section 3.4 "VCONN Supply Control (DFP Modes Only)" additional details.                                                      |  |  |

| CC2 VCONN<br>Supply Control               | VCONN2_OUT#       | OD25           | <b>DFP Modes Only.</b> Open drain, active low VCONN supply control to CC2 for supplying 5V to active cable circuitry. See <b>Section 3.4 "VCONN Supply Control (DFP Modes Only)"</b> for additional details.                                    |  |  |

| Audio Adapter<br>Indicator and<br>Control | AUDIO_ADAPTER     | O25            | <b>DFP Modes Only.</b> Active high pin which indicates the detection of a USB audio adapter device. This pin is intended to control high speed USB and audio switch which toggles between standard USB 2.0 DP/DM Signaling and audio signaling. |  |  |

| Fault Indicator                           | FAULT_IND         | O25            | Active high fault indicator output. Output is asserted after an overcurrent event on <b>OCS</b> # is detected. Output is deasserted after toggling the ENABLE input pin or after a power-on reset.                                              |  |  |

| Connected<br>State Indicator              | CONNECTED#        | OD25           | UFP Mode Only. Open drain pin which asserts when a valid USB Type-C connection is detected on the CC pin, and when VBUS is within the valid voltage range.                                                                                      |  |  |

| Legacy<br>Charging Indi-<br>cator         | LEGACY_IND#       | OD25           | <b>UFP Mode Only.</b> Open drain pin which asserts low when a valid USB Type-C connection is detected and Legacy 500mA/ 900mA charging capability is detected.                                                                                  |  |  |

| 1.5A Charging<br>Indicator                | 1.5A_IND#         | OD25           | <b>UFP Mode Only.</b> Open drain pin which asserts low when a valid USB Type-C connection is detected and 1.5A USB Type-C charging capability is detected.                                                                                      |  |  |

| 3.0A Charging<br>Indicator                | 3.0A_IND#         | OD25           | <b>UFP Mode Only.</b> Open drain pin which asserts low when a valid USB Type-C connection is detected and 3.0A USB Type-C charging capability is detected.                                                                                      |  |  |

# **UTC2000**

TABLE 2-2: PIN DESCRIPTIONS (CONTINUED)

| Name   | Symbol | Buffer<br>Type | Description                                                                                                                                                                              |  |  |  |

|--------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        |        | Pow            | ver and Ground                                                                                                                                                                           |  |  |  |

| Power  | VDD    | Р              | 5.0V Power Input. A minimum of one 0.1uF bypass capacitor placed close to the pin is recommended.  The "high" level of all digital outputs will be equivalent to the VDD supply voltage. |  |  |  |

| Ground | VSS    | Р              | Ground. The exposed pad must also be connected to VSS/ ground.                                                                                                                           |  |  |  |

## 2.3 Buffer Types

**TABLE 2-3: BUFFER TYPES**

| Buffer Type | Description                                                                                                                                                                                                                                  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ADC         | Analog to digital input                                                                                                                                                                                                                      |  |  |  |  |

| IS          | Schmitt-triggered input                                                                                                                                                                                                                      |  |  |  |  |

| O25         | Output with 25mA sink and 25mA source                                                                                                                                                                                                        |  |  |  |  |

| OD25        | Open-drain output with 25mA sink and 25mA source                                                                                                                                                                                             |  |  |  |  |

| Р           | Power                                                                                                                                                                                                                                        |  |  |  |  |

| PU          | 100 μA (typical) internal pull-up.                                                                                                                                                                                                           |  |  |  |  |

|             | Note: Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added. |  |  |  |  |

**Note:** Refer to Section 4.3, DC Characteristics for electrical characteristics.

#### 3.0 FUNCTIONAL DESCRIPTION

This chapter describes the functional descriptions for the following device sub-systems.

- Section 3.1, Configuration Selection

- · Section 3.2, DFP Modes Functional State Machine

- · Section 3.3, UFP Mode Functional State Machine

- Section 3.4, VCONN Supply Control (DFP Modes Only)

- Section 3.5, USB Audio Adapter (DFP Modes Only)

- Section 3.6, UFP Mode Connection and Charging Capability Detection Indicator

- · Section 3.7, Connection and Disconnection Detection Debounce

#### 3.1 Configuration Selection

The CFG\_SEL pin is sampled at power-on at Vcfg\_samp and the UTC2000 is placed in either UFP or DFP modes of operation.

If the CFG\_SEL pin is within one of the DFP mode ranges upon power-on, it will operate in DFP mode. While in DFP mode, the CFG\_SEL pin is constantly monitored and can be placed in any of the DFP modes at any time by the system controller. Switching from DFP to UFP modes cannot be achieved without a power-on reset. Table 3-1 displays the voltage ranges for the DFP profile.

If the CFG\_SEL pin is within the UFP mode range upon power-on, it will operate in UFP mode. For UFP designs, it is recommended to tie CFG\_SEL to VDD through a pull-up resistor to ensure that UFP mode is entered when VDD crosses the POR threshold. Switching from UFP to DFP modes cannot be achieved without a power-on reset. Table 3-2 displays the voltage ranges for the UFP profile.

TABLE 3-1: DFP CONFIGURATION SELECTION VOLTAGE MONITORING THRESHOLDS

| CFG_SEL<br>Voltage | Profile                           | CC1/CC2 No<br>Connection Voltage<br>Range | CC1/CC2 Rd<br>Detection Voltage<br>Range | CC1/CC2 Ra<br>Detection Voltage<br>Range |

|--------------------|-----------------------------------|-------------------------------------------|------------------------------------------|------------------------------------------|

| 1.2V - 1.3V        | 3A Capable DFP                    | 5.0V - 2.75V                              | 2.60V - 0.85V                            | 0.80V - 0.00V                            |

| 0.7V - 0.8V        | 1.5A Capable DFP                  | 5.0V - 1.65V                              | 1.60V - 0.45V                            | 0.40V - 0.00V                            |

| 0.0V - 0.30V       | Default Legacy USB<br>Capable DFP | 5.0V - 1.65V                              | 1.60V - 0.25V                            | 0.20V - 0.00V                            |

TABLE 3-2: UFP CONFIGURATION SELECTION VOLTAGE MONITORING THRESHOLDS

| CFG_SEL<br>Voltage | No Connection<br>Voltage Range | CC1/CC2 Legacy<br>Charging Connection<br>Voltage Range | CC1/CC2 1.5A<br>Charging Connection<br>Voltage Range | CC1/CC2 3.0A<br>Charging Connection<br>Voltage Range |

|--------------------|--------------------------------|--------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| 1.75V - VDD        | 0.0V - 0.25V                   | 0.25V - 0.70V                                          | 0.70V-1.31V                                          | > 1.31V                                              |

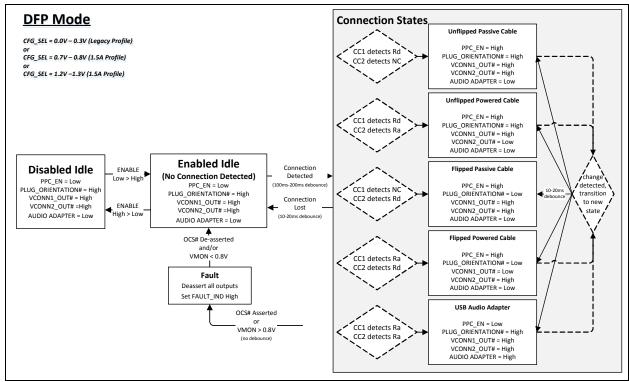

#### 3.2 DFP Modes Functional State Machine

A visual representation of the UTC2000 DFP state machine behavior is shown in Figure 3-1. The various states are detailed in the following sub-sections.

FIGURE 3-1: DFP MODES STATE MACHINE DIAGRAM

#### 3.2.1 DISABLED IDLE

The UTC2000 will remain in a disabled, inactive state if **ENABLE** is asserted low, or the voltage on **CFG\_SEL** is not within a valid configuration range.

While in this state, the state of the digital outputs are as follows:

- PPC\_EN: Low

- PLUG\_ORIENTATION#: High

- VCONN1\_OUT#: High

- VCONN2\_OUT#: High

- · AUDIO ADAPTER: Low

#### 3.2.2 ENABLED IDLE

If both ENABLE is asserted high and CFG\_SEL is in a valid configuration range, the UTC2000 will actively monitor the CC1 and CC2 pins for a connect event.

While in this state, the state of the digital outputs are as follows:

- PPC\_EN: Low

- PLUG\_ORIENTATION#: High

- VCONN1 OUT#: High

- VCONN2 OUT#: High

- AUDIO\_ADAPTER: Low

#### 3.2.3 CONNECTED (UNFLIPPED PASSIVE CABLE)

If both ENABLE is asserted high and CFG\_SEL is in a valid configuration range and an Rd pull-down resistor is sensed on the CC1 pin, the UTC2000 will enter the "CONNECTED (UNFLIPPED PASSIVE CABLE)" state.

While in this state, the state of the digital outputs are as follows:

• PPC EN: High

• PLUG\_ORIENTATION#: High

VCONN1\_OUT#: High VCONN2\_OUT#: High AUDIO ADAPTER: Low

#### 3.2.4 CONNECTED (UNFLIPPED ACTIVE CABLE)

If ENABLE is asserted high, CFG\_SEL is in a valid configuration range, an Rd pull-down resistor is sensed on the CC1 pin, and an Ra pull-down resistor is sensed on the CC2 pin, the UTC2000 will enter the "CONNECTED (UNFLIPPED ACTIVE CABLE)" state.

While in this state, the state of the digital outputs are as follows:

· PPC EN: High

• PLUG\_ORIENTATION#: High

VCONN1\_OUT#: High VCONN2\_OUT#: Low AUDIO ADAPTER: Low

#### 3.2.5 CONNECTED (FLIPPED PASSIVE CABLE)

If both ENABLE is asserted high and CFG\_SEL is in a valid configuration range and an Rd pull-down resistor is sensed on the CC2 pin, the UTC2000 will enter the "CONNECTED (FLIPPED PASSIVE CABLE)" state.

While in this state, the state of the digital outputs are as follows:

· PPC EN: High

• PLUG ORIENTATION#: Low

VCONN1\_OUT#: High VCONN2\_OUT#: High AUDIO\_ADAPTER: Low

#### 3.2.6 CONNECTED (FLIPPED ACTIVE CABLE)

If ENABLE is asserted high, CFG\_SEL is in a valid configuration range, an Rd pull-down resistor is sensed on the CC2 pin, and an Ra pull-down resistor is sensed on the CC1 pin, the UTC2000 will enter the "CONNECTED (UNFLIPPED ACTIVE CABLE)" state.

While in this state, the state of the digital outputs are as follows:

• PPC EN: High

• PLUG\_ORIENTATION#: Low

VCONN1\_OUT#: LowVCONN2\_OUT#: HighAUDIO\_ADAPTER: Low

## **UTC2000**

#### 3.2.7 CONNECTED (USB AUDIO ADAPTER)

If ENABLE is asserted high, CFG\_SEL is in a valid configuration range, and Ra pull-down resistors are sensed on both CC1 and CC2 pins the UTC2000 will enter the "CONNECTED (UNFLIPPED ACTIVE CABLE)" state.

**Note:** A typical USB audio adapter device will simply short CC1 and CC2 to ground. This implementation is functionally equivalent to using two Ra resistors.

While in this state, the state of the digital outs are as follows:

· PPC EN: Low

• PLUG\_ORIENTATION#: High

VCONN1\_OUT#: High VCONN2\_OUT#: High AUDIO\_ADAPTER: High

#### 3.2.8 FAULT (OVERCURRENT OR OVERVOLTAGE)

If OCS# is asserted low while in any state, the UTC2000 will set all of its outputs to the default state and will transition into the fault state. An internal overcurrent flag will be set and FAULT\_IND will drive high. Normal operation will resume after OCS# is deasserted. The FAULT\_IND pin will continue to drive low until a power cycle occurs.

If VMON exceeds 0.8V at any state, the UTC2000 will set all of its outputs to the default state and will transition into the fault state. An internal overvoltage flag will be set and FAULT\_IND will drive high. Normal operation will resume after VMON is deasserted. The FAULT\_IND pin will continue to drive low until a power cycle occurs.

#### 3.3 UFP Mode Functional State Machine

A visual representation of the UTC2000 UFP state machine behavior is shown in Figure 3-2. The various states are detailed in the following sub-sections.

**UFP Mode Connection States** 0.5 < VMON < 0.6875V CFG\_SEL = 1.75V - VDD (4.0 < VBUS < 5.5V)**Unflipped Legacy Connection** CONNECTED# = Low CC1 detects Legacy PLUG\_ORIENTATION# = High CC2 detects NC LEGACY\_IND# = Low 1.5A IND# = High 3.0A\_IND# = High **Unflipped 1.5A Connection** CONNECTED# = Low CC1 detects 1.5A PLUG ORIENTATION# = High CC2 detects NC LEGACY IND# = High 1.5A\_IND# = Low 3.0A\_IND# = High **Unflipped 3.0A Connection** Idle Connection (No Connection Detected) Detected CONNECTED# = Low CC1 detects 3.0A CONNECTED# = High (100-150ms debounce) PLUG\_ORIENTATION# = High CC2 detects NC PLUG ORIENTATION# = High LEGACY\_IND# = High LEGACY IND# = High 1.5A IND# = High change 1.5A\_IND# = High Lost 3.0A\_IND# = Low detected (10-20ms debouce) 10-20n 3.0A IND# = High transition to new Flipped Legacy Connection OCS# De-asserted and/or CONNECTED# = Low CC1 detects NC VMON < 0.8V PLUG\_ORIENTATION# = Low C2 detects Legacy LEGACY IND# = Low 1.5A\_IND# = High Fault 3.0A\_IND# = High Deassert all outputs Set FAULT IND High Fllipped 1.5A Connection OCS# Asserted CONNECTED# = Low CC1 detects NC PLUG ORIENTATION# = Low VMON > 0.8V CC2 detects 1.5A LEGACY\_IND# = High 1.5A IND# = Low 3.0A IND# = High Fllipped 3.0A Connection CONNECTED# = Low CC1 detects NC PLUG\_ORIENTATION# = Low CC2 detects 3.0A LEGACY\_IND# = High 1.5A\_IND# = High 3.0A IND# = Low

FIGURE 3-2: UFP MODE STATE MACHINE DIAGRAM

#### 3.3.1 IDLE

The UTC2000 will remain in a disabled, inactive state if ENABLE is asserted low, or the voltage on CFG\_SEL is not within a valid configuration range.

While in this state, the state of the digital outputs are as follows:

- CONNECTED#: High (Not Asserted)

- PLUG\_ORIENTATION#: High (Not Asserted)

- LEGACY\_IND#: High (Not Asserted)

- 1.5A\_IND#: High (Not Asserted)

- 3.0A IND#: High (Not Asserted)

#### 3.3.2 CONNECTED (UNFLIPPED LEGACY CONNECTION)

If VBUS is in a valid range (4.5V-5.5V) and a Legacy Rp pull-up resistor is sensed on the CC1 pin (and no connection detected on the CC2 pin) the UTC2000 will enter the "CONNECTED (UNFLIPPED LEGACY CONNECTION)" state.

While in this state, the state of the digital outputs are as follows:

- CONNECTED#: Low (Asserted)

- PLUG ORIENTATION#: High (Not Asserted)

- LEGACY\_IND#: Low (Asserted)

- 1.5A\_IND#: High (Not Asserted)

- 3.0A IND#: High (Not Asserted)

#### 3.3.3 CONNECTED (UNFLIPPED 1.5A CONNECTION)

If VBUS is in a valid range (4.5V-5.5V) and a 1.5A Rp pull-up resistor is sensed on the CC1 pin (and no connection detected on the CC2 pin) the UTC2000 will enter the "CONNECTED (UNFLIPPED 1.5A CONNECTION)" state.

While in this state, the state of the digital outputs are as follows:

- CONNECTED#: Low (Asserted)

- PLUG ORIENTATION#: High (Not Asserted)

- LEGACY IND#: High (Not Asserted)

- 1.5A IND#: Low (Asserted)

- 3.0A IND#: High (Not Asserted)

#### 3.3.4 CONNECTED (UNFLIPPED 3.0A CONNECTION)

If VBUS is in a valid range (4.5V-5.5V) and a 3.0A Rp pull-up resistor is sensed on the CC1 pin (and no connection detected on the CC2 pin) the UTC2000 will enter the "CONNECTED (UNFLIPPED 3.0A CONNECTION)" state.

While in this state, the state of the digital outputs are as follows:

- CONNECTED#: Low (Asserted)

- PLUG\_ORIENTATION#: High (Not Asserted)

- LEGACY IND#: High (Not Asserted)

- 1.5A\_IND#: High (Not Asserted)

- 3.0A IND#: Low (Asserted)

#### 3.3.5 CONNECTED (FLIPPED LEGACY CONNECTION)

If VBUS is in a valid range (4.5V-5.5V) and a Legacy Rp pull-up resistor is sensed on the CC2 pin (and no connection detected on the CC1 pin) the UTC2000 will enter the "CONNECTED (FLIPPED LEGACY CONNECTION)" state.

While in this state, the state of the digital outputs are as follows:

- CONNECTED#: Low (Asserted)

- PLUG ORIENTATION#: Low (Asserted)

- · LEGACY IND#: High (Asserted)

- 1.5A IND#: High (Not Asserted)

- 3.0A IND#: High (Not Asserted)

#### 3.3.6 CONNECTED (FLIPPED L1.5A CONNECTION)

If VBUS is in a valid range (4.5V-5.5V) and a 1.5A Rp pull-up resistor is sensed on the CC2 pin (and no connection detected on the CC1 pin) the UTC2000 will enter the "CONNECTED (FLIPPED 1.5A CONNECTION)" state.

While in this state, the state of the digital outputs are as follows:

- CONNECTED#: Low (Asserted)

- PLUG ORIENTATION#: Low (Asserted)

- LEGACY IND#: High (Not Asserted)

- 1.5A\_IND#: Low (Asserted)

- 3.0A IND#: High (Not Asserted)

#### 3.3.7 CONNECTED (FLIPPED 3.0A CONNECTION)

If VBUS is in a valid range (4.5V-5.5V) and a 3.0A Rp pull-up resistor is sensed on the CC2 pin (and no connection detected on the CC1 pin) the UTC2000 will enter the "CONNECTED (FLIPPED 3.0A CONNECTION)" state.

While in this state, the state of the digital outputs are as follows:

- CONNECTED#: Low (Asserted)

- PLUG ORIENTATION#: Low (Asserted)

- LEGACY IND#: High (Not Asserted)

- 1.5A IND#: High (Not Asserted)

- 3.0A\_IND#: Low (Asserted)

#### 3.3.8 FAULT (OVERCURRENT OR OVERVOLTAGE)

If OCS# is asserted low while in any state, the UTC2000 will set all of its outputs to the default state and will transition into the fault state. An internal overcurrent flag will be set and FAULT\_IND will drive high. Normal operation will resume after OCS# is deasserted. The FAULT\_IND pin will continue to drive low until a reset or power cycle occurs.

If VMON exceeds 0.8V (6.4V on VBUS) at any state, the UTC2000 will set all of its outputs to the default state and will transition into the fault state. An internal overvoltage flag will be set and FAULT\_IND will drive high. Normal operation will resume after VMON is deasserted. The FAULT\_IND pin will continue to drive low until a reset or power cycle occurs.

#### 3.4 VCONN Supply Control (DFP Modes Only)

VCONN1\_OUT# and VCONN2\_OUT# are open drain, active low output signals used to control a 5V voltage supply to power a powered USB Type-C cable. Powered cable support is mandatory for all USB Type-C applications which implement USB 3.0/USB 3.1. For USB 2.0 systems, powered cable support is optional. The VCONN supply control signals will assert low when one of the following conditions are met:

- VCONN1\_OUT# will assert low if an Rd resistor is detected on CC2 and an Ra resistor is detected on CC1. The signal will remain asserted until the Rd resistor on CC2 is no longer sensed (USB cable is detached).

- VCONN2\_OUT# will assert low if an Rd resistor is detected on CC1 and an Ra resistor is detected on CC2. The signal will remain to asserted until the Rd resistor on CC1 is no longer sensed (USB cable is detached).

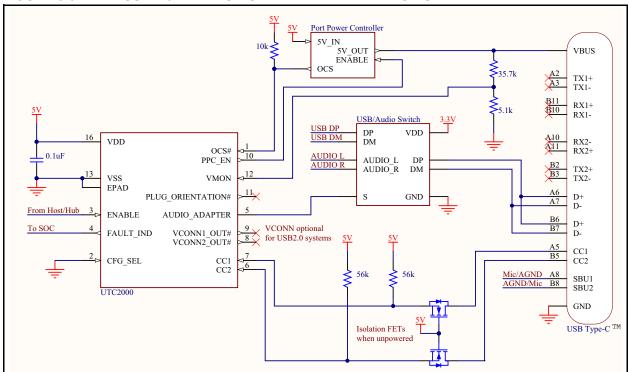

#### 3.5 USB Audio Adapter (DFP Modes Only)

**Note:** Additional details for implementing Audio Adapter mode are detailed in Appendix A of the USB Type-C<sup>TM</sup> Cable and Connector Specification.

**AUDIO\_ADAPTER** is an active high output signal that is used to indicate when a USB audio adapter is detected. **AUDIO\_ADAPTER** will assert high when an Ra resistor is detected on both CC1 and CC2 pins. The signal will remain asserted until either or both Ra resistors is no longer sensed. This signal is intended to control a high-speed switch that toggles between USB differential data and an audio signal. The switch that is selected must be capable of supporting USB 2.0 as well as audio signals ranging from -3.0V to +3.0V. Additional electrical details can be found in section A-3 of the *USB Type-C<sup>TM</sup> Cable and Connector Specification*.

## **UTC2000**

Two additional signals are also used when operating in Audio Adapter mode. These signals are Mic/AGND and AGND/ Mic which should be connected to SBU1 and SBU2 respectively.

#### 3.6 UFP Mode Connection and Charging Capability Detection Indicator

While operating in UFP mode, there are 4 outputs that indicate connection state.

CONNECTED# is an open drain output that asserts when any of the three valid USB Type-C connections are detected. Legacy charging mode (500mA for USB 2.0 connections, 900mA for USB 3.0/USB 3.1 connections) is detected when a DFP with a 56k Rp pull-up resistor is detected. 1.5A charging is detected when a DFP with a 22k Rp pull-up resistor is detected. 3.0A charging is detected when a DFP with a 10k Rp pull-up resistor is detected.

The LEGACY\_IND#, 1.5A\_IND#, and 3.0A\_IND# open drain outputs assert low to indicate which type of connection was detected. These outputs can be fed to the battery charging management circuitry of the USB device to appropriately regulate the amount of current draw.

The CONNECTED# signal may also be used to gate the VBUS voltage to system power if an added level of protection from high voltage is desired.

#### 3.7 Connection and Disconnection Detection Debounce

A debounce is implemented to eliminate unwanted connect/disconnect events due to cable jostling or USB Power Delivery messaging.

A transition from the ENABLED IDLE state to any connected state is debounced by 100ms-200ms.

A transition from any connected state to any other connected state or from any connected state to the **ENABLED IDLE** state is debounced by 10ms-20ms.

#### 4.0 OPERATIONAL CHARACTERISTICS

#### 4.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias4                                                                | 0°C to +125°C  |

|------------------------------------------------------------------------------------------------|----------------|

| Storage temperature69                                                                          | 5°C to +150°C  |

| Voltage on pins with respect to Vss                                                            |                |

| on VDD pin                                                                                     | -0.3V to +6.5V |

| on all other pins0.3V to                                                                       | o (VDD + 0.3V) |

| Maximum current                                                                                |                |

| on Vss pin <sup>(</sup> 4-1)                                                                   |                |

| $0^{\circ}C \le TA \le +70^{\circ}C$                                                           | 95 mA          |

| -40°C ≤ TA ≤ +85°C                                                                             | 85 mA          |

| -40°C ≤ TA ≤ +125°C                                                                            | 35 mA          |

| on VDD pin(1)                                                                                  |                |

| $0^{\circ}C \le TA \le +70^{\circ}C$                                                           | 95 mA          |

| -40°C ≤ TA ≤ +85°C                                                                             | 85 mA          |

| -40°C ≤ TA ≤ +125°C                                                                            | 35 mA          |

| on any I/O pin                                                                                 | ±25 mA         |

| Clamp current, IK (VPIN < 0 or VPIN > VDD)                                                     |                |

| Note 4-1 Maximum current rating requires even load distribution across I/O pins. Maximum curre | ent rating may |

Note 4-1 Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

#### 4.2 Standard Operating Conditions

The standard operating conditions for this device are defined as:

$\begin{array}{ll} \text{Operating Voltage:} & \text{VDDMIN} \leq \text{VDD} \leq \text{VDDMAX} \\ \text{Operating Temperature:} & \text{Ta\_MIN} \leq \text{Ta} \leq \text{Ta\_MAX} \end{array}$

VDD — Operating Supply Voltage<sup>(4-2)</sup>

VDDMIN

+4.5V

VDDMAX

+5.5V

TA — Operating Ambient Temperature Range

Commercial Temperature

Extended Temperature

Ta\_MIN -40°C

Ta\_MAX +125°C

**Note 4-2** Refer to Parameter D001, DC Characteristics: Supply Voltage.

#### 4.3 DC Characteristics

TABLE 4-1: SUPPLY VOLTAGE

| Param.<br>No. | Sym.      | Characteristic                     | Min.          | Тур†    | Max.          | Units                 | Conditions                                                   |

|---------------|-----------|------------------------------------|---------------|---------|---------------|-----------------------|--------------------------------------------------------------|

| D001          | VDD       | Supply Voltage                     |               |         |               |                       |                                                              |

|               |           |                                    | Vddmin<br>4.5 | _       | Vddmax<br>5.5 | V                     |                                                              |

| D002*         | Vpor      |                                    | Power-o       | n Rese  | t Release Vo  | oltage <sup>(1)</sup> |                                                              |

|               |           |                                    | _             | 1.6     | _             | V                     |                                                              |

| D003          | VPORR*    |                                    | Power-        | on Rese | et Rearm Vo   | Itage <sup>(1)</sup>  |                                                              |

|               |           |                                    | _             | 0.8     | _             | V                     |                                                              |

| D004          | SVDD      | VDD Rise Rate <sup>(2)</sup>       | 0.05          | _       | _             | V/ms                  | Ensures that the Power-on Reset signal is released properly. |

| D005          | VCFG_SAMP | CFG_SEL Sampling Threshold Voltage |               |         |               |                       |                                                              |

|               |           |                                    | _             | 3.6     |               | V                     |                                                              |

<sup>\*</sup> These parameters are characterized but not tested.

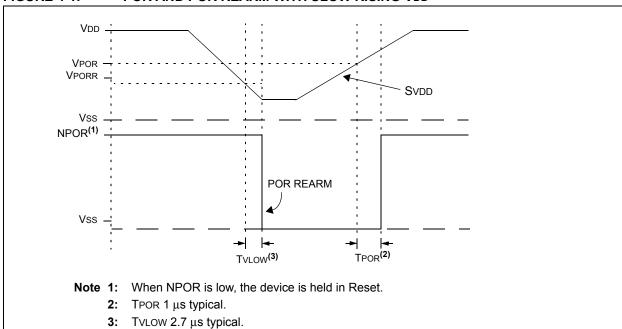

Note 1: See Figure 4-1, POR and POR REARM with Slow Rising VDD.

FIGURE 4-1: POR AND POR REARM WITH SLOW RISING VDD

TABLE 4-2: SUPPLY CURRENT (IDD)<sup>(1)</sup>

| Param. Device |                     | Min. Typ |      | Max.     | Units - | Conditions |                    |  |

|---------------|---------------------|----------|------|----------|---------|------------|--------------------|--|

| No.           | Characteristics     | IVIIII.  | тур  | ур імах. | Units   | VDD        | Note               |  |

| D006          | Disabled            | _        | 185  | 205      | uA      | 5.0        | -40°C ≤ TA ≤ +85°C |  |

| D007          | Enabled             | _        | 185  | 205      | uA      | 5.0        | -40°C ≤ TA ≤ +85°C |  |

| D008          | Enabled & Connected | _        | 1.30 | 1.35     | mA      | 5.0        | -40°C ≤ TA ≤ +85°C |  |

**Note 1:** The supply current is mainly a function of the operating voltage. Other factors, such as I/O pin loading and switching rate also have an impact on the current consumption.

TABLE 4-3: I/O PORTS

| IABLE         | 4-3. | I/O PORTS                            |                   |            |                |         |                                                                            |  |  |

|---------------|------|--------------------------------------|-------------------|------------|----------------|---------|----------------------------------------------------------------------------|--|--|

|               |      | Standard C                           | perating Conditi  | ons (unles | s otherwise    | stated) |                                                                            |  |  |

| Param.<br>No. | Sym. | Characteristic                       | Min.              | Typ†       | Max.           | Units   | Conditions                                                                 |  |  |

|               | VIL  | Input Low Voltage                    |                   |            |                |         |                                                                            |  |  |

|               |      |                                      |                   | I/O P      | ORT:           |         |                                                                            |  |  |

| D009          |      |                                      | _                 |            | 8.0            | V       | $4.5V \le V_{DD} \le 5.5V$                                                 |  |  |

| D009A         |      |                                      | _                 | 1          | 0.15 VDD       | V       | $3.0 \text{V} \leq \text{V}_{DD} \leq 4.5 \text{V}$                        |  |  |

|               | VIH  |                                      |                   | Input Hig  | h Voltage      |         |                                                                            |  |  |

|               |      |                                      | <u></u>           |            |                |         |                                                                            |  |  |

| D010          |      |                                      | 2.0               | _          | _              | V       | $4.5V \le VDD \le 5.5V$                                                    |  |  |

| D010A         |      |                                      | 0.25 VDD +<br>0.8 | l          | _              | V       | $3.0V \le VDD \le 4.5V$                                                    |  |  |

|               | lıL  | Input Leakage Current <sup>(1)</sup> |                   |            |                |         |                                                                            |  |  |

| D011          |      | I/O Ports                            |                   | ± 5        | ± 125          | nA      | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance, 85°C                           |  |  |

|               |      |                                      | _                 | ± 5        | ± 1000         | nA      | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance, 125°C                          |  |  |

|               | Vol  |                                      |                   | Output Lo  | w Voltage      |         |                                                                            |  |  |

| D012          |      | I/O Ports                            | _                 | _          | 0.6            | V       | Iol = 8 mA, Vdd = 5V<br>Iol = 6 mA, Vdd = 3.3V<br>Iol = 1.8 mA, Vdd = 1.8V |  |  |

|               | Voh  | Output High Voltage                  |                   |            |                |         |                                                                            |  |  |

| D013          |      | I/O Ports                            | Vdd - 0.7         | _          | _              | V       | Ioh = 3.5 mA, Vdd = 5V<br>Ioh = 3 mA, Vdd = 3.3V<br>Ioh = 1 mA, Vdd = 1.8V |  |  |

|               |      |                                      | Capacitive Lo     | ading Spec | cifications or | Output  | Pins                                                                       |  |  |

| D014*         | CIO  | All I/O pins                         | _                 | _          | 50             | pF      |                                                                            |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Negative current is defined as current sourced by the pin.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

**TABLE 4-4: TIMING PARAMETERS**

| Standard Operating Conditions (unless otherwise stated) |                                  |                                                           |                                             |      |       |  |  |  |

|---------------------------------------------------------|----------------------------------|-----------------------------------------------------------|---------------------------------------------|------|-------|--|--|--|

| Param. No.                                              | Sym.                             | Min.                                                      | Typ†                                        | Max. | Units |  |  |  |

|                                                         | tconnect_debounce                | CC                                                        | CC1/CC2 Connection Detection Debounce Delay |      |       |  |  |  |

| D015                                                    |                                  | 100                                                       | 160                                         | 200  | ms    |  |  |  |

|                                                         | t <sub>DISCONNECT_DEBOUNCE</sub> | CC1/CC2 Disconnection or Connection Change Debounce Delay |                                             |      |       |  |  |  |

| D016                                                    |                                  | 10                                                        | 16                                          | 20   | ms    |  |  |  |

|                                                         | t <sub>VMON_FAULT</sub>          | VMON Fault Detection Reaction Delay                       |                                             |      |       |  |  |  |

| D017                                                    |                                  | _                                                         | 0.460                                       | 1    | ms    |  |  |  |

|                                                         | tocs#_fault                      | OCS# Fault Detection Reaction Delay                       |                                             |      |       |  |  |  |

| D018                                                    |                                  | _                                                         | 0.410                                       | 1    | ms    |  |  |  |

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

#### TABLE 4-5: THERMAL CHARACTERISTICS

| Standard      | Standard Operating Conditions (unless otherwise stated) |                                           |      |       |                                                          |  |  |

|---------------|---------------------------------------------------------|-------------------------------------------|------|-------|----------------------------------------------------------|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                            | Тур. | Units | Conditions                                               |  |  |

| TH01          | θЈА                                                     | Thermal Resistance Junction to<br>Ambient | 55.3 | °C/W  | 16-pin QFN 3x3x0.9mm package                             |  |  |

| TH02          | θЈС                                                     | Thermal Resistance Junction to<br>Case    | 10   | °C/W  | 16-pin QFN 3x3x0.9mm package                             |  |  |

| TH03          | TJMAX                                                   | Maximum Junction Temperature              | 150  | °C    |                                                          |  |  |

| TH04          | PD                                                      | Power Dissipation                         | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |

| TH05          | Pinternal                                               | Internal Power Dissipation                | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06          | Pı/o                                                    | I/O Power Dissipation                     | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07          | PDER                                                    | Derated Power                             | _    | W     | PDER = PDMAX (TJ - TA)/θJA <sup>(2)</sup>                |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

<sup>2:</sup> TA = Ambient Temperature; TJ = Junction Temperature

#### 5.0 UTC2000 SYSTEM APPLICATION

This chapter explains external requirements for UTC2000 applications and provides some example diagrams.

- Section 5.1, 5V VBUS Switch (DFP Modes Only)

- · Section 5.2, Rp Pull-Up Resistor (DFP Modes Only)

- Section 5.3, Rd Pull-Down Resistor (UFP Mode Only)

- Section 5.4, VCONN Active Cable Supply (DFP Modes Only)

- Section 5.5, CC Pin Isolation (DFP Only)

- Section 5.6, CC Pin Current Limiting Resistors (UFP Only)

- · Section 5.7, VBUS Monitoring

- · Section 5.8, USB Signal Multiplexer

- Section 5.9, Application Example: 3.0A Capable USB 3.0/USB 3.1 DFP

- Section 5.10, Application Example: 1.5A Capable USB 2.0 DFP

- Section 5.11, Application Example: 500mA Capable USB 2.0 DFP with Audio Adapter Support

- Section 5.12, Application Example: 3.0A Capable USB Type-CTM Charging Port (AC Adapter)

- · Section 5.13, Application Example: UFP Device

#### 5.1 5V VBUS Switch (DFP Modes Only)

A 5V USB port power switch with active high enable input and an overcurrent indicator output is required. The USB Type-C receptacle must not supply 5V to the VBUS pins until a valid connection is detected. The UTC2000 controller asserts the active high PPC\_EN signal to control the 5V port power supply to VBUS upon detection of a valid USB Type-C connection. The port power switch controlled by the UTC2000 shall also have built in overcurrent detection set to a threshold that is appropriate for the current capability profile that is being selected per Table 5-1. An overcurrent threshold of 125% (of the selected DFP profile current) is appropriate, as the threshold may not be tripped at any current less than or equal to the selected current profile. The 5V VBUS port power controller should indicate that an overcurrent event has occurred by pulling the OCS# signal to the UTC2000 controller low.

#### 5.2 Rp Pull-Up Resistor (DFP Modes Only)

A Downstream Facing Port is required to supply voltage to both CC pins through a pull-up resistor. The pull-up voltage may be either 5.0V volts or 3.3V. A UFP must implement a Rd pull-down resistor to ground. When a DFP to UFP connection is made, a resistor divider is formed, and the voltage at the CC pin can be measured to interpret the type of connection. Table 5-1 describes the possible values of the Rp pull-up resistor.

Note: A constant current source may also be implemented instead of a pull-up resistor.

TABLE 5-1: RP PULL-UP RESISTOR VALUES

| DFP Advertisement                                     | Resistor Pull-Up<br>to 4.75 - 5.5V | Resistor Pull-Up<br>to 3.3V ± 5% | Current Source |

|-------------------------------------------------------|------------------------------------|----------------------------------|----------------|

| Legacy USB:<br>500mA USB 2.0<br>900mA USB 3.0/USB 3.1 | 56 kΩ ± 20%                        | 36 kΩ ± 20%                      | 80 μA ± 20%    |

| 1.5A                                                  | 22 kΩ ± 5%                         | 12 kΩ ± 5%                       | 180 μA ± 8%    |

| 3.0A                                                  | 10 kΩ ± 5%                         | $4.7 \text{ k}\Omega \pm 5\%$    | 330 μA ± 8%    |

The UTC2000 measures the voltages on both CC pins via it's internal ADCs. The CC pin voltage ranges, as defined in the USB Type- $C^{TM}$  Cable and Connector Specification, are shown in Table 3-1.

#### 5.3 Rd Pull-Down Resistor (UFP Mode Only)

An Upstream Facing Port is required to implement a 5.1k +/- 10% Rd pull-down resistor to ground connected to both CC1 and CC2 pins on the Type-C receptacle. When a DFP to UFP connection is made, a resistor divider is formed, and the voltage at the CC pin can be measured to interpret the charging capability of the DFP.

#### 5.4 VCONN Active Cable Supply (DFP Modes Only)

All USB Type-C receptacles must be able to supply power to an active cable if USB 3.0/USB 3.1 signaling is implemented. Supplying VCONN is optional if only USB 2.0 is implemented. The simplest implementation is to add a FET (or series of FETs) that switches in the VCONN voltage directly to the CC pin node. The VCONN supply must be capable of supplying 1.0W of continuous power and may not supply more than 1.25A at the moment of plug contact. A bulk capacitance of 10µF to 220µF must also be switched in with VCONN. The bulk capacitance may not need to be a discrete capacitor if the supply's output capacitance already meets this requirement. Overcurrent detection is recommended, but not required per the USB Type-C<sup>TM</sup> Cable and Connector Specification. A simple implementation example is shown in Figure 5-1 below.

**Note:** Rds\_on must be carefully considered to ensure that the *USB Type-C<sup>TM</sup> Cable and Connector Specification* requirements for VCONN supply current and voltage range are met.

VCONN 1.0W Supply

Rp Pull-Up Voltage

VCONN1 OUT#

VCONN2 OUT#

Rp Pull-Up Voltage

Rp Rp Rp

Rp Rp

Rp Rp

FIGURE 5-1: EXAMPLE VCONN SUPPLY CONNECTION

**Note:** It is also recommended to implement additional circuitry to make the CC1 and CC2 pins high impedance when the DFP is in an unpowered state. Refer to Figure 5-7 for an example.

#### 5.5 CC Pin Isolation (DFP Only)

The CC pins on a DFP must be high-impedance when the DFP is powered off. This is to prevent VBUS backdrive in a situation when a DFP connects to an unpowered DFP and detects the Rp pull-up resistors as an Rd pull-down. Therefore, it is recommended that some isolation FETs are implemented that disconnect the CC pins from the Rp pull-up resistors and VCONN supply circuitry when powered off.

#### 5.6 CC Pin Current Limiting Resistors (UFP Only)

Because most UFP designs require operation even when unpowered, resistors placed directly in front of the CC1 and CC2 pins are recommended to limit the amount of leakage current through the UTC2000 ADC inputs when unpowered.  $10k\Omega$  resistors are the recommended value.

Failure to place current limiting resistors could result in a failure to detect a USB attach due to a shift in CC voltage.

#### 5.7 VBUS Monitoring

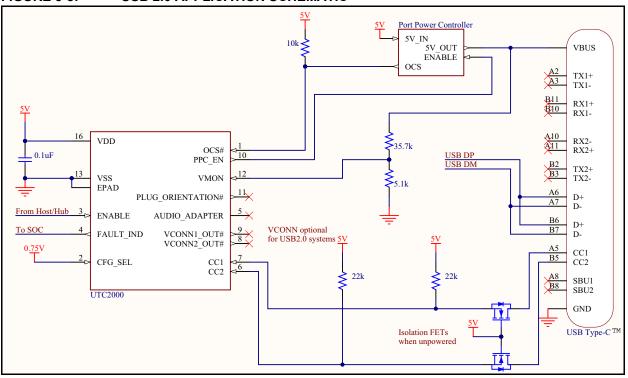

**DFP Modes:** An optional VBUS monitoring function may be implemented to protect the system from higher than expected voltages on VBUS (from a malfunctioning connected USB device) by preventing the UTC2000 from enabling the 5V port switch. Additional back-drive protection or isolation circuitry must be implemented for thorough protection. This feature requires the **VMON** pin to be connected to VBUS through a resistor divider network that divides the VBUS voltage by a factor of 8. A 35.7kΩ resistor over a  $5.1k\Omega$  resistor is recommended, as shown in the Figure 5-7, Figure 5-8, and Figure 5-9 below.

**UFP Mode:** The VBUS monitoring function is required and used to verify a valid VBUS range before asserting the CONNECTED pin or any charge capability indicator outputs. A fault condition will also be flagged if higher than expected voltage on VBUS (from a malfunctioning connected USB device) is detected. Additional back-drive protection or isolation circuitry must be implemented for thorough protection. This features requires the **VMON** pin to be connected to VBUS through a resistor divider network that divides the VBUS voltage by a factor of 8.

#### 5.8 USB Signal Multiplexer

There are several options for connecting the USB signals to the USB Type-C receptacles. These options differ slightly between USB 2.0 and USB 3.0/USB 3.1 applications, as detailed in the following sub-sections.

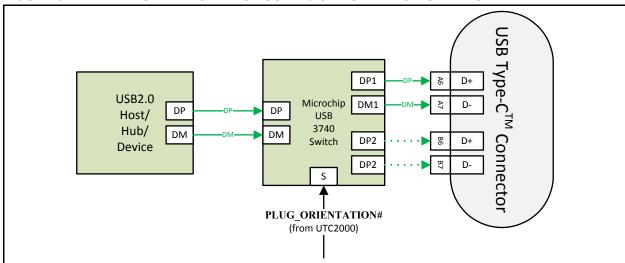

#### 5.8.1 USB 2.0 OPTION 1: HIGH-SPEED MULTIPLEXER/SWITCH

The most robust solution for USB 2.0 applications is to use a USB High-Speed switch to control the routing of the USB signals. The Microchip USB3740 is a cost-effective solution for this purpose and offers several benefits:

Extreme ESD: +- 15KV (IEC)

Low Power: 5uA(on), 1uA (off)

Off Isolation: less than -40dB

High bandwidth: up to 1 GHz

· Preserves signal integrity

Small Package: 1.3 x 1.8 mm – 10pin DFN (.4mm pitch)

#### FIGURE 5-2: BLOCK DIAGRAM OF USB 2.0 OPTION 1: HIGH-SPEED SWITCH

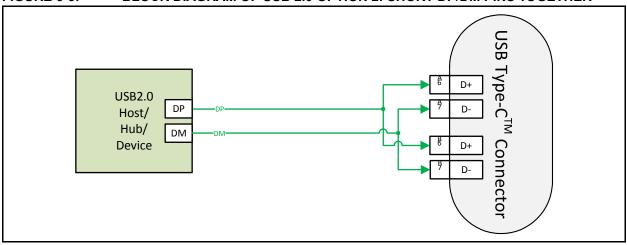

#### 5.8.2 USB 2.0 OPTION 2: SHORT DP/DM PINS TOGETHER

The simplest solution is to short together the DP / DM pins at the receptacle. Only one DP / DM pair at the connector will be active at once. Note that this implementation will negatively affect the integrity of the USB signals because of the creation of stubs on the USB traces.

FIGURE 5-3: BLOCK DIAGRAM OF USB 2.0 OPTION 2: SHORT DP/DM PINS TOGETHER

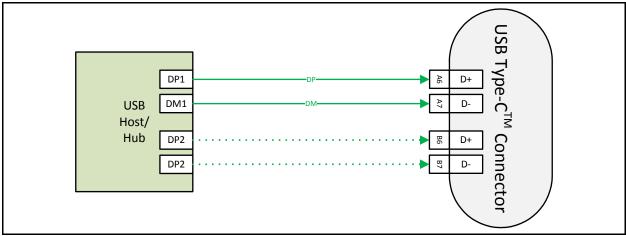

#### 5.8.3 USB 2.0 OPTION 3: USE TWO DOWNSTREAM PORTS (DFP ONLY)

If two downstream ports are available, then they may both be connected to the DP / DM pins on the USB Type-C receptacle. Only one of the ports will be active and able to be used at once.

**Note:** If using a Microchip Hub with FlexConnect, a muxless UFP design is possible. Refer to the Microchip USB5734 USB Type-C Reference Design and Evaluation Platform for details.

FIGURE 5-4: BLOCK DIAGRAM OF USB 2.0 OPTION 3: USE TWO DOWNSTREAM PORTS

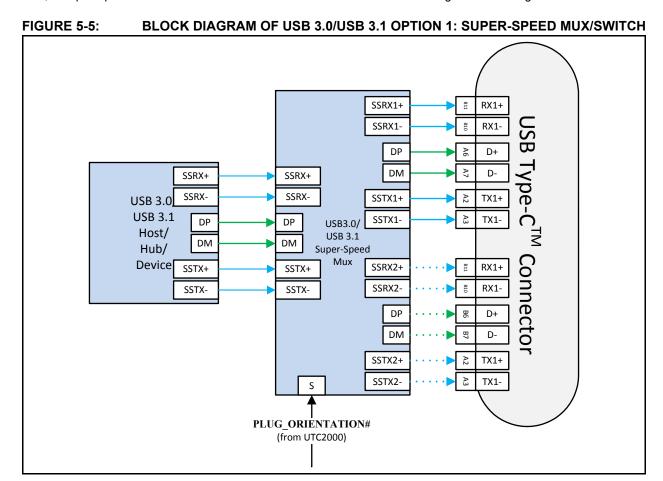

#### 5.8.4 USB 3.0/USB 3.1 OPTION 1: SUPER SPEED MULTIPLEXER/SWITCH

In a USB 3.0/USB 3.1 UFP application, or a USB 3.0/USB 3.1 DFP application where only one downstream port is available, a Super-Speed USB 3.0/USB 3.1 switch must be used to control the routing of the USB signals.

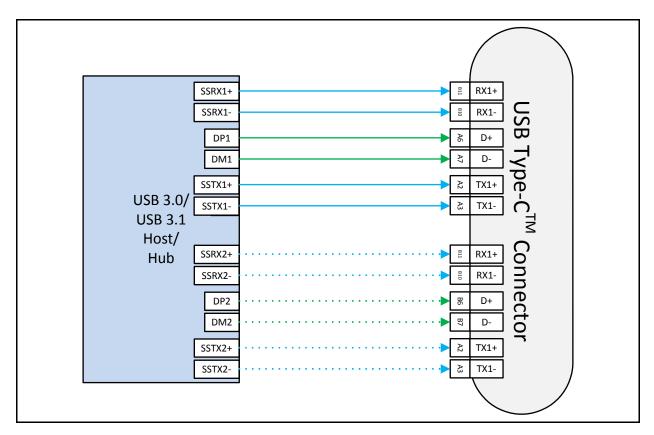

#### 5.8.5 USB 3.0/USB 3.1 OPTION 2: USE TWO DOWNSTREAM PORTS (DFP ONLY)

If two downstream ports are available, then they may both be connected to the USB pins on the USB Type-C receptacle. Only one of the ports will be active and able to be used at once.

**Note:** If using a Microchip Hub with FlexConnect, a muxless UFP design is possible. Refer to the Microchip USB5734 Type-C Reference Design and Evaluation Platform for details.

FIGURE 5-6: BLOCK DIAGRAM OF USB 3.0/USB 3.1 OPTION 2: USE TWO DOWNSTREAM PORTS

#### 5.9 Application Example: 3.0A Capable USB 3.0/USB 3.1 DFP

FIGURE 5-7: USB 3.0/USB 3.1 APPLICATION SCHEMATIC

#### 5.10 Application Example: 1.5A Capable USB 2.0 DFP

FIGURE 5-8: USB 2.0 APPLICATION SCHEMATIC

### 5.11 Application Example: 500mA Capable USB 2.0 DFP with Audio Adapter Support

FIGURE 5-9: USB 2.0 WITH AUDIO ADAPTER APPLICATION SCHEMATIC

## 5.12 Application Example: 3.0A Capable USB Type-C<sup>TM</sup> Charging Port (AC Adapter)

FIGURE 5-10: 3.0A CHARGING PORT (AC ADAPTER) APPLICATION SCHEMATIC

#### 5.13 Application Example: UFP Device

#### FIGURE 5-11: UFP DEVICE APPLICATION SCHEMATIC

## **UTC2000**

Note:

The pass FET and current sense circuitry connected to VBUS are for high voltage protection and are optional. If high voltage protection is required and the device is bus powered or battery powered (and may have a dead battery), a high voltage tolerant regulator must also be implemented to power the UTC2000 while it qualifies the USB Type-C connection.

#### 6.0 PACKAGING INFORMATION

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

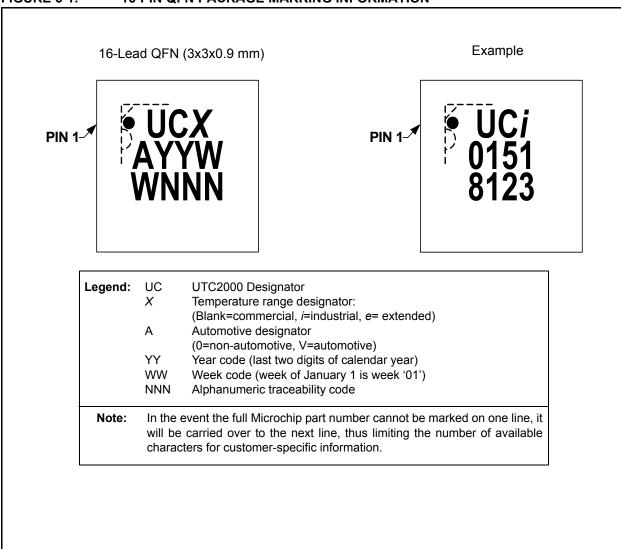

#### 6.1 Package Marking Information

#### FIGURE 6-1: 16-PIN QFN PACKAGE MARKING INFORMATION

## 6.2 Package Details

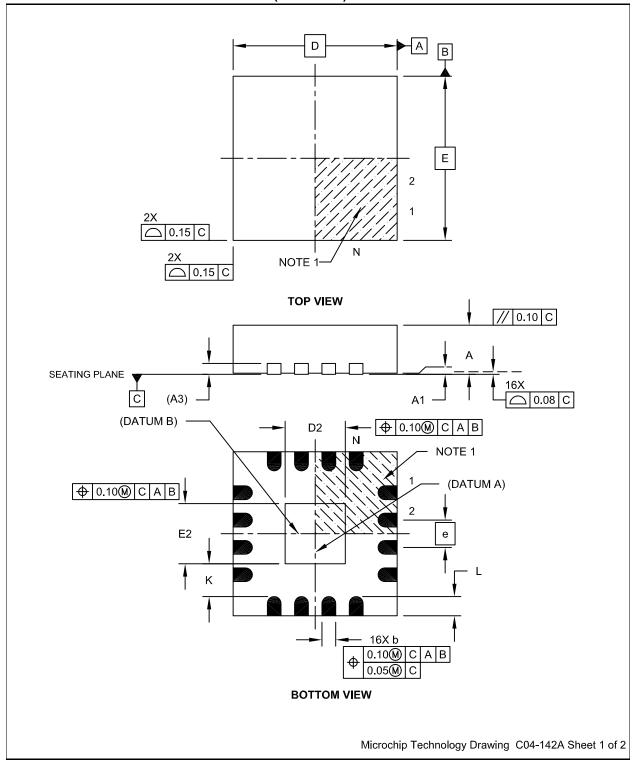

FIGURE 6-2: 16-PIN QFN PACKAGE (DRAWING)

FIGURE 6-3: **16-PIN QFN PACKAGE (DIMENSIONS)**

|                        | MILLIMETERS         |          |      |      |

|------------------------|---------------------|----------|------|------|

| Dimension              | Dimension Limits    |          | NOM  | MAX  |

| Number of Pins         | Number of Pins N 16 |          |      |      |

| Pitch                  | е                   | 0.50 BSC |      |      |

| Overall Height         | Α                   | 0.80     | 0.85 | 0.90 |

| Standoff               | A1                  | 0.00     | 0.02 | 0.05 |

| Contact Thickness      | A3                  | 0.20 REF |      |      |

| Overall Width          | Е                   | 3.00 BSC |      |      |

| Exposed Pad Width      | E2                  | 1.00     | 1.10 | 1.50 |

| Overall Length         | D                   | 3.00 BSC |      |      |

| Exposed Pad Length     | D2                  | 1.00     | 1.10 | 1.50 |

| Contact Width          | b                   | 0.18     | 0.25 | 0.30 |

| Contact Length         | L                   | 0.25     | 0.35 | 0.45 |

| Contact-to-Exposed Pad | K                   | 0.20     | -    | -    |

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-142A Sheet 2 of 2

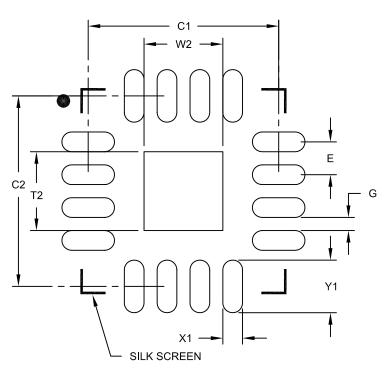

FIGURE 6-4: 16-PIN QFN PACKAGE (LAND PATTERN)

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension                  | MIN         | NOM      | MAX  |      |

| Contact Pitch E            |             | 0.50 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 1.20 |

| Optional Center Pad Length | T2          |          |      | 1.20 |

| Contact Pad Spacing        | C1          |          | 2.90 |      |

| Contact Pad Spacing        | C2          |          | 2.90 |      |

| Contact Pad Width (X16)    | X1          |          |      | 0.30 |

| Contact Pad Length (X16)   | Y1          |          |      | 0.80 |

| Distance Between Pads      | G           | 0.20     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2142A

## APPENDIX A: DATA SHEET REVISION HISTORY

TABLE A-1: REVISION HISTORY

| Revision Level & Date  | Section/Figure/Entry                                                                                                                                                        | Correction                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS00001957C (08-06-15) | Cover, Section 1.1, "General<br>Description", Section 4.2,<br>"Standard Operating Condi-<br>tions", Figure 6-1, Product<br>Identification System on<br>page 40              | <ul> <li>Changed "Automotive extended temperature" to "extended temperature" as the extended temperature range is available in automotive and non-automotive versions.</li> <li>Updated "XXX" automotive code description.</li> </ul>                                                                                                                                      |

|                        | Table 2.2, "Pin Descriptions"                                                                                                                                               | Updated first sentence of CFG_SEL description                                                                                                                                                                                                                                                                                                                              |