# Dual Channel Wideband Auto Battery Switching (ABS) VoicePort Device - ZL880 Series

**Data Sheet**

#### **Features**

- Next Generation ZL880 VoicePort Family with Enhanced Features and Performance

- Same API interface as the VE880 Series

- Low Bill of Materials (BOM) cost for 2 to 8 channel applications

- Complete BORSCHT Functions for Two FXS Channels in a Single 64-Pin QFN Package

- Battery feed, Over-voltage support, integrated Ringing, line Supervision, Codec, Hybrid (2W/4W), and Test

#### • Integrated Power Management

- Single power supply using integrated battery switches for lowest BOM cost

- Low Power Idle Mode with 60 mW consumption

- Internal FET drive circuit for lower BOM count

- Integrated real-time power monitoring tool

#### Ringing

- 5 REN with pin for pin compatible 100-V (ZL88601) and 120-V (ZL88602) devices

- Internally generated sinusoidal or trapezoidal ringing with programmable DC offset

#### Worldwide Programmability

- Input impedance, balance impedance, gain

- DC feed voltage and current limit

- Ringing frequency, voltage and current limit

- G.711 A-law, μ-law, or 16 bit linear coding

- Call progress tone and Caller ID generation

- Sample coefficients for more than 70 countries

- Per channel Wideband support

#### Pin-Selectable PCM/SPI or ZSI Interfaces

- SPI Mode 0 and 3 support with no inter byte CS off time. Also supports legacy MPI Interface

- ZSI Mode for a smaller number of interface signals to the host and less expensive isolation

- VoicePath SDK and VP-API-II Software Available to Implement FXS Functions

- VeriVoice Software Suites Available for Manufacturing and Subscriber Loop Testing

Document ID# 141956

October 2013

| Ordering Information |                            |             |                                      |         |

|----------------------|----------------------------|-------------|--------------------------------------|---------|

| I                    | Device OPN(1               | Device Type | Package                              | Packing |

| ı                    | ZL88601LDF1                | 100V-ABS    | 64-pin QFN (9x9)                     |         |

| ı                    | ZL88601LDG1<br>ZL88602LDF1 |             | 64-pin QFN (9x9)<br>64-pin QFN (9x9) |         |

| ı                    | ZL88602LDG1                |             | 64-pin QFN (9x9)                     | Tray    |

The Green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

### **Applications**

- DSL Residential Gateways and Integrated Access Devices (IADs)

- Cable eMTAs

- PON Single Family Units (SFUs)

- Fiber to the Premise/Home/Building (FTTx)

Multiple Dwelling Units (MDUs)

### Description

The Microsemi<sup>®</sup> Dual Channel Wideband ZL88601/602 Automatic Battery Switching (ABS) VoicePort Device provides complete BORSCHT functions for two telephone line FXS ports. This device is a part of the new ZL880 Series featuring enhanced functionality, lower BOM cost, and greater power efficiency, while maintaining software compatibility with the industry leading VE880 Series.

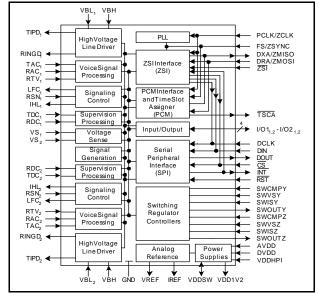

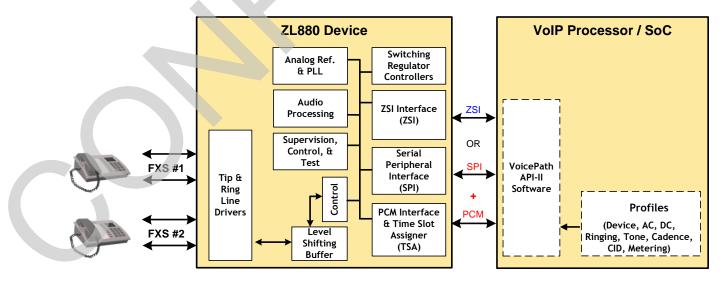

Figure 1 - ZL88601/602 Device Block Diagram

### **Table of Contents**

| 2.0 ZL88601/602 Device Overview and Block Diagram                 |    |

|-------------------------------------------------------------------|----|

|                                                                   | 9  |

| 2.1 VE880 Series Features                                         |    |

| 2.2 New and Enhanced Features                                     |    |

| 2.3 Device Block Diagram                                          |    |

|                                                                   |    |

| 3.0 Functional Description                                        |    |

| 3.1 Host Port Interface.                                          |    |

| 3.1.1 PCM Interface and Time Slot Assigner                        |    |

| 3.1.2 Serial Peripheral Interface (SPI)                           |    |

| 3.1.3 ZSI Serial Mode                                             |    |

| 3.2 Input / Output Block                                          |    |

| 3.3 Voltage Sense                                                 | 18 |

| 3.4 Voice Signal Processor                                        | 18 |

| 3.4.1 Impedance Synthesis                                         |    |

| 3.4.2 Frequency Response Correction and Equalization              |    |

| 3.4.3 Transhybrid Balancing                                       |    |

| 3.4.4 Gain Adjustment.                                            |    |

| 3.4.5 Transmit Signal Processing                                  |    |

| 3.4.6 Receive Signal Processing                                   |    |

|                                                                   |    |

| 3.4.7 Speech Coding.                                              | 20 |

| 3.4.8 Wideband Operation                                          | 20 |

| 3.5 Signal Generation                                             |    |

| 3.5.1 Multi-Tone Generation                                       |    |

| 3.5.2 Frequency and Amplitude Modulation                          | 21 |

| 3.5.3 Triangular and Trapezoidal Signal Generation                | 22 |

| 3.6 Low Power DC Feed                                             | 22 |

| 3.7 Normal DC Feed                                                |    |

| 3.8 Test Feed                                                     |    |

| 3.9 Ringing                                                       | 24 |

| 3.9.1 Balanced Ringing                                            | 24 |

| 3.9.2 Unbalanced Ringing                                          | 24 |

| 3.9.3 Switch Hook Detection                                       | 25 |

| 3.9.4 Ring Trip Detection                                         |    |

| 3.10 Subscriber Line Testing.                                     |    |

| 3.10.1 VeriVoice Professional Test Suite Software for the ZL880   |    |

| 3.11 Manufacturing Testing                                        |    |

| 3.12 Metering                                                     |    |

| 3.13 Switching Regulator Controller                               |    |

| 3.14 Charge Pump Regulator and MOSFET Gate Driver                 |    |

|                                                                   |    |

| 4.0 Electrical Specifications                                     |    |

| 4.1 Absolute Maximum Ratings                                      |    |

| 4.2 Thermal Performance                                           |    |

| 4.3 Operating Ranges                                              |    |

| 4.3.1 Recommended Operating Conditions                            | 30 |

| 5.0 Electrical Characteristics                                    | 31 |

| 5.1 Test Conditions                                               |    |

| 5.2 Supply Currents and Power Dissipation                         |    |

| 5.3 DC Characteristics.                                           |    |

| 5.4 DC Feed and Signaling - All States Except Low Power Idle Mode |    |

| 5.5 DC Feed and Signaling - All States Except Low Power Idle Mode |    |

| a a roch eeu anu ammu - row eower me wode alaie                   |    |

|                                                                   | 22 |

| 5.6 Metering                                                      |    |

| 5.8 Switching Regulator Controller                                                  |    |

|-------------------------------------------------------------------------------------|----|

| 5.9 Charge Pump Controller and MOSFET Driver                                        | 35 |

| 5.10 Voice ADC Signal Sense Accuracy                                                | 35 |

| 5.11 Supervision ADC Signal Sense Accuracy                                          | 36 |

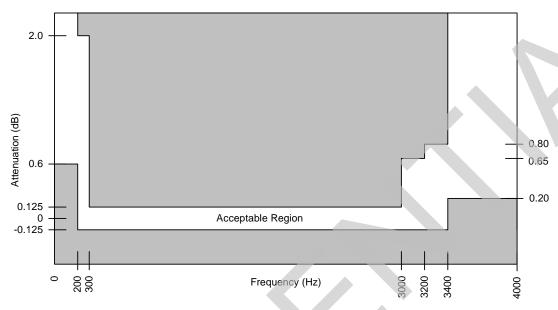

| 5.12 Transmission Characteristics - Narrowband Codec Mode                           |    |

| 5.13 Attenuation Distortion - Narrowband Codec Mode                                 |    |

| 5.14 Discrimination Against Out-of-Band Input Signals - Narrowband Codec Mode       |    |

| 5.15 Discrimination Against 12- and 16-kHz Metering Signals - Narrowband Codec Mode | 39 |

| 5.16 Spurious Out-of-Band Signals at the Analog Output - Narrowband Codec Mode      | 39 |

| 5.17 Overload Compression - Narrowband Codec Mode                                   | 40 |

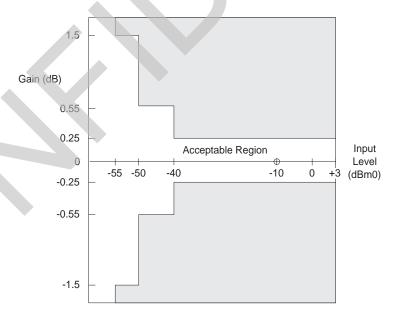

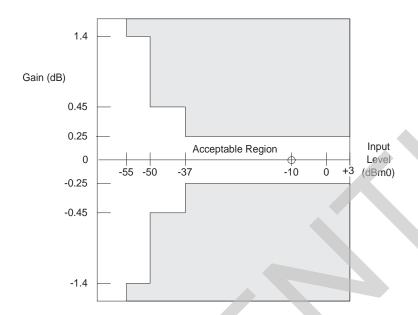

| 5.18 Gain Linearity - Narrowband Codec Mode                                         | 41 |

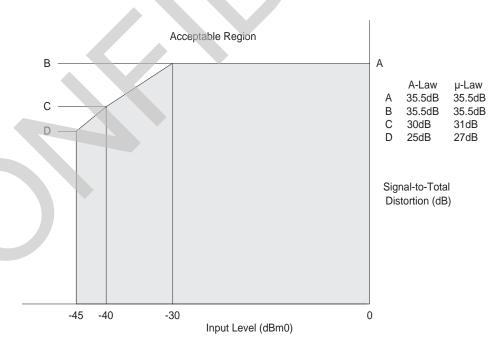

| 5.19 Total Distortion Including Quantizing Distortion - Narrowband Codec Mode       | 42 |

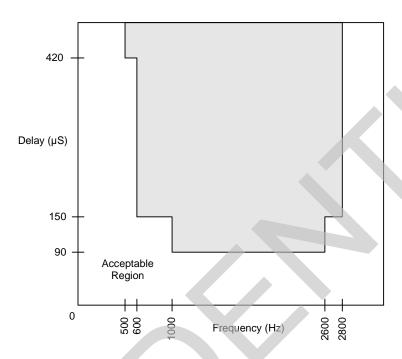

| 5.20 Group Delay Distortion - Narrowband Codec Mode                                 | 43 |

| 5.21 Transmission Characteristics - Wideband Codec Mode                             | 44 |

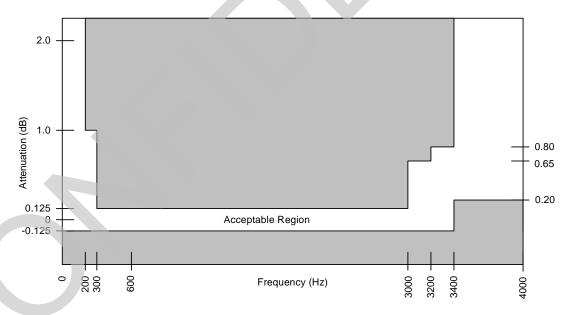

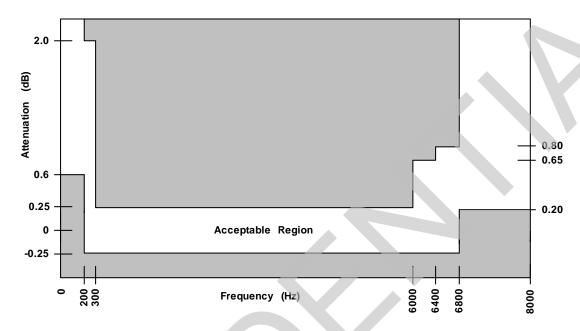

| 5.22 Attenuation Distortion - Wideband Codec Mode                                   | 45 |

| 5.23 Group Delay Distortion - Wideband Codec Mode                                   |    |

| 6.0 Switching Characteristics and Waveforms                                         | 47 |

| 6.1 PCM and SPI Mode.                                                               |    |

| 6.1.1 SPI Interface                                                                 |    |

| 6.1.2 PCM Interface                                                                 | 49 |

| 6.2 ZSI Interface                                                                   |    |

| 6.3 Switcher Output Timing                                                          |    |

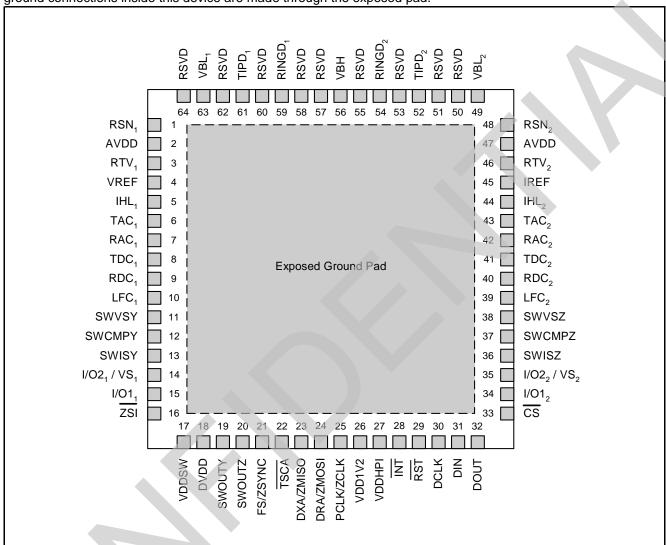

| 7.0 Device Pinout                                                                   |    |

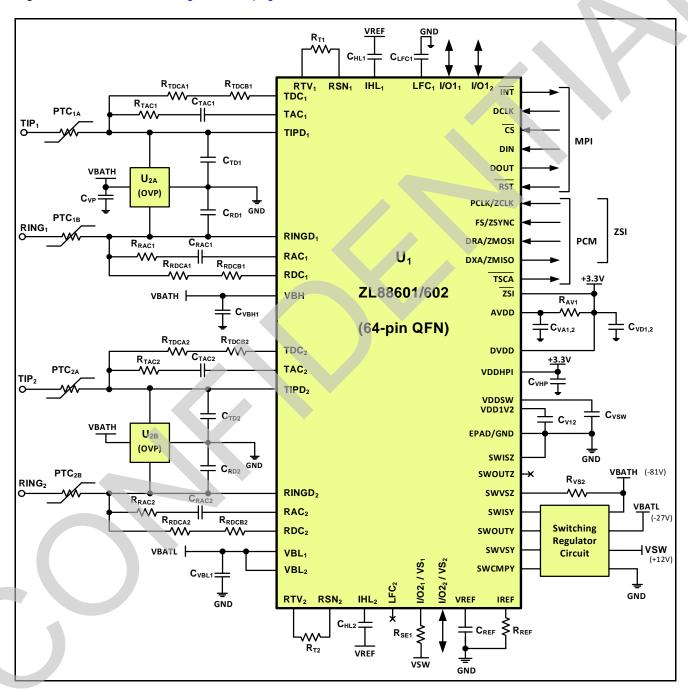

| 8.0 Application Information.                                                        |    |

| 8.1 Line Interface Circuit                                                          |    |

| 8.2 Line Interface Circuit Bill of Materials                                        |    |

| 8.3 Switching Regulator Circuit                                                     |    |

| 8.4 Switching Regulator Circuit Bill of Materials                                   |    |

|                                                                                     |    |

| 9.0 Programming the ZL88601/602                                                     | 61 |

| 9.1 Programmable Features                                                           | 61 |

| 9.2 VoicePath SDK Overview                                                          | 61 |

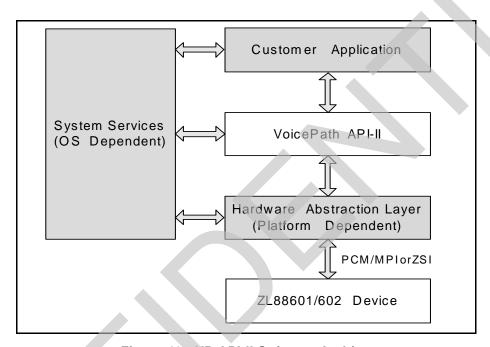

| 9.3 VoicePath API-II Software Overview                                              | 62 |

| 9.3.1 Introduction                                                                  |    |

| 9.3.2 Customer Application                                                          |    |

| 9.3.3 VoicePath API-II.                                                             |    |

| 9.3.4 Hardware Abstraction Layer                                                    |    |

| 9.3.5 System Services Layer                                                         |    |

|                                                                                     |    |

| 9.5 Initialization                                                                  |    |

| 9.6.1 VP LINE DISABLED.                                                             |    |

| 9.6.2 VP LINE DISCONNECT.                                                           |    |

| 9.6.3 VP_LINE_STANDBY                                                               |    |

| 9.6.4 VP_LINE_OHT.                                                                  |    |

| 9.6.5 VP_LINE_ACTIVE, VP_LINE_TALK                                                  |    |

| 9.6.6 VP_LINE_TIP_OPEN.                                                             |    |

| 9.6.7 VP_LINE_RINGING.                                                              |    |

| 9.6.8 VP LINE HOWLER.                                                               |    |

| 9.7 Line Status Monitoring.                                                         |    |

| 9.8 Input / Output Control                                                          |    |

|                                                                                     |    |

| 10.0 VP-API-II Profiles                                                             |    |

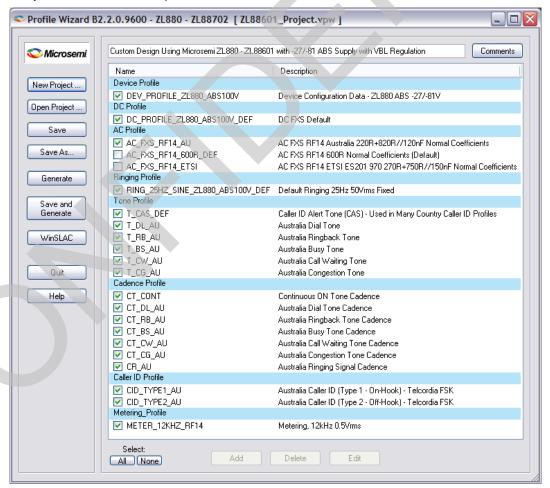

| 10.1 Profile Wizard Project Definition                                              |    |

| 10.2 Profile Wizard Main Menu                                                       |    |

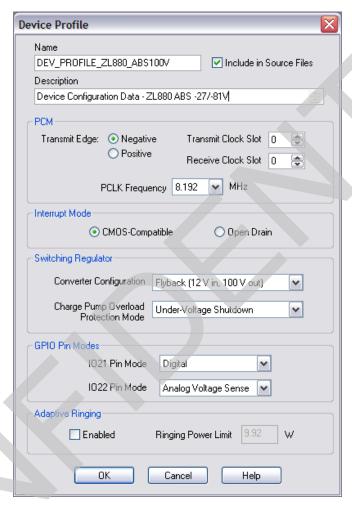

| 10.3 Device Profile                                                                 | 69 |

|      | 10.3.1 Overview              | 69   |

|------|------------------------------|------|

|      | 10.4 AC FXS Profiles         | 70   |

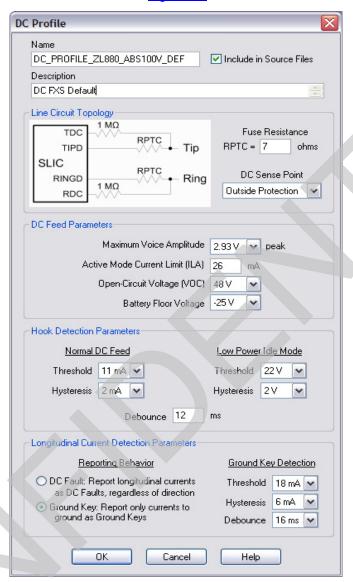

|      | 10.5 DC Profile              | 71   |

|      | 10.6 Ringing Profile         | 72   |

|      | 10.7 Tone Profile            | . 73 |

|      | 10.8 Tone Cadence Profile    |      |

|      | 10.9 Ringing Cadence Profile | 75   |

|      | 10.10 Caller ID Profile      | 76   |

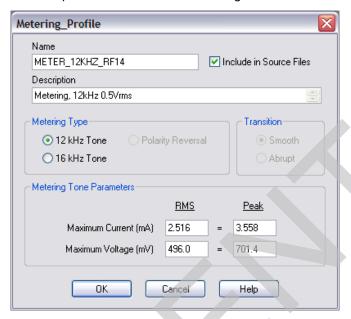

|      | 10.11 Metering Profile       | 77   |

| 11.0 | 0 Package Outline            | 78   |

| 12.0 | D Related Collateral         | 80   |

|      | 12.1 Documentation           | 80   |

|      | 12.2 Development Hardware    | 80   |

|      | 12.3 Development Software    | 80   |

|      |                              |      |

# **List of Figures**

| Figure 1 - ZL88601/602 Device Block Diagram                                                   |    |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2 - ZL880 Dual-Channel VoicePort Solution Diagram                                      |    |

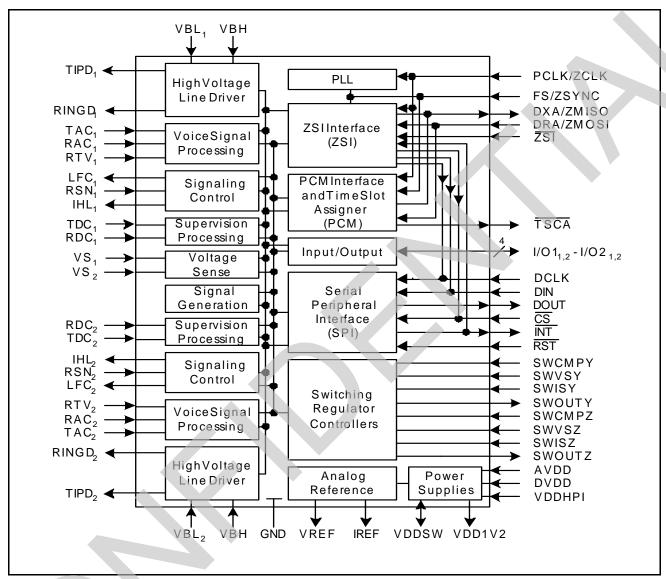

| Figure 3 - ZL88601/602 Device Block Diagram                                                   | 11 |

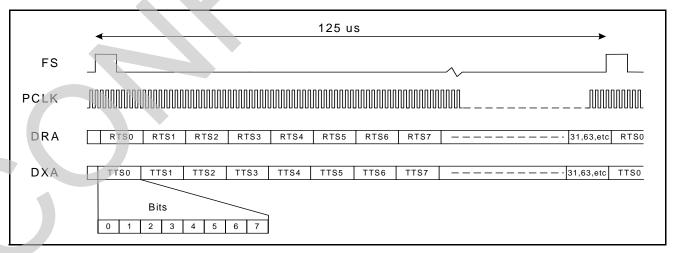

| Figure 4 - PCM Highway Structure                                                              | 12 |

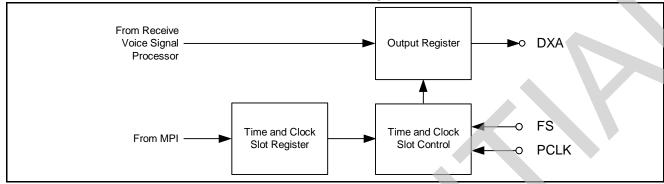

| Figure 5 - Transmit PCM Interface                                                             | 13 |

| Figure 6 - Receive PCM Interface                                                              | 13 |

| Figure 7 - PCM Data Flow Transmit and Receive Data (Transmit Data on Negative PCLK Edge)      | 14 |

| Figure 8 - 4-Wire SPI Connection to Host Processor.                                           | 15 |

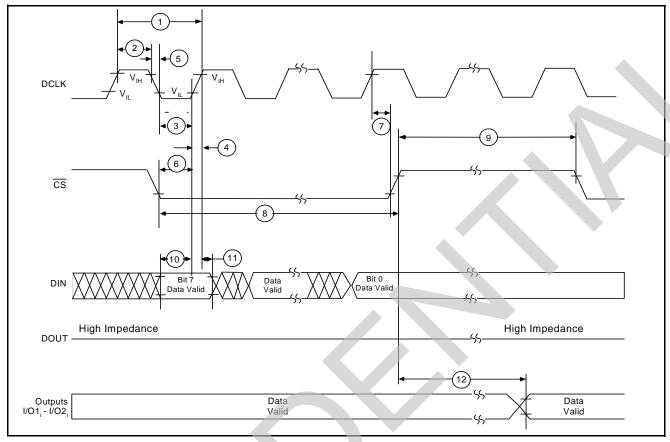

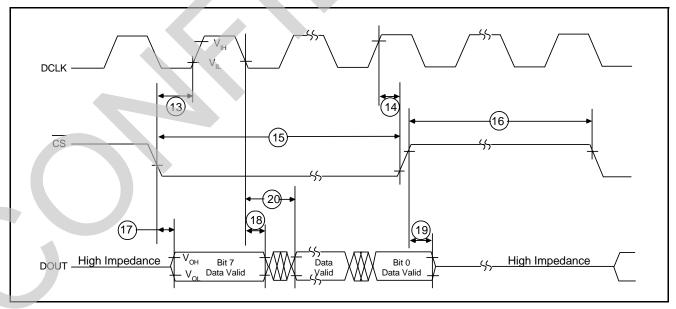

| Figure 9 - SPI Mode 3 Interface Timing                                                        | 16 |

| Figure 10 - MPI Interface Timing                                                              |    |

| Figure 11 - ZSI Timing Protocol                                                               |    |

| Figure 12 - Voice Signal Processing Block Diagram                                             | 18 |

| Figure 13 - Multi-Tone Generation                                                             |    |

| Figure 14 - Frequency Tone Modulation                                                         | 21 |

| Figure 15 - Trapezoidal Signal Generation                                                     |    |

| Figure 16 - Normal DC Feed I / V Characteristic                                               |    |

| Figure 17 - Balanced Ringing with Fixed Supply                                                |    |

| Figure 18 - Unbalanced Ringing with Fixed Supply                                              | 24 |

| Figure 19 - Metering Pulse Definitions                                                        |    |

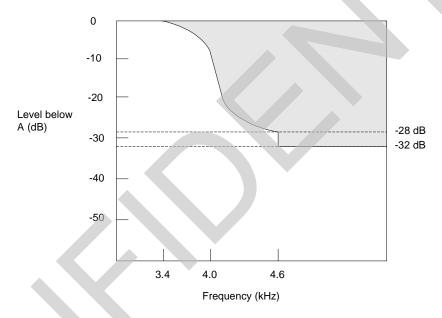

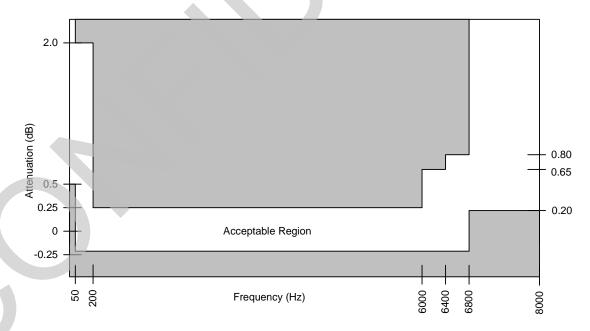

| Figure 20 - Transmit (A to D) Path Attenuation vs. Frequency                                  | 38 |

| Figure 21 - Receive (D to A) Path Attenuation vs. Frequency                                   |    |

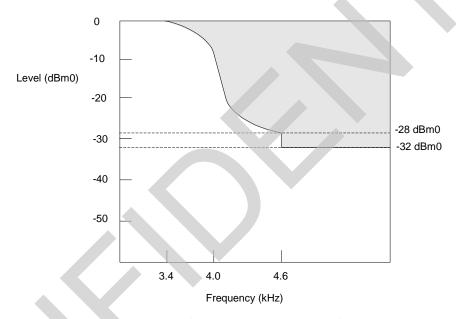

| Figure 22 - Discrimination Against Out-of-Band Signals                                        |    |

| Figure 23 - Spurious Out-of-Band Signals                                                      | 40 |

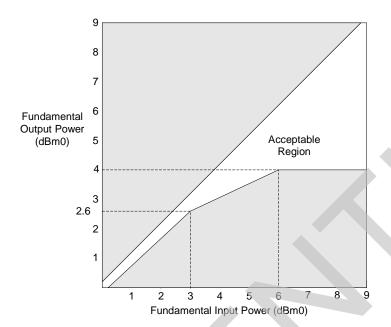

| Figure 24 - Analog-to-Analog Overload Compression                                             | 41 |

| Figure 25 - A-law Gain Linearity with Tone Input (Both Paths)                                 | 41 |

| Figure 26 - μ-law Gain Linearity with Tone Input (Both Paths)                                 | 42 |

| Figure 27 - Total Distortion with Tone Input (Both Paths)                                     |    |

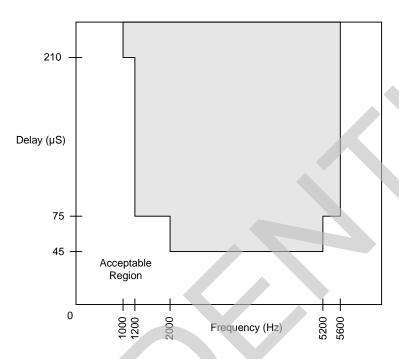

| Figure 28 - Group Delay Distortion                                                            |    |

| Figure 29 - Transmit (A to D) Path Attenuation vs. Frequency- (with High-Pass Filter Enabled) | 45 |

| Figure 30 - Receive (D to A) Path Attenuation vs. Frequency                                   |    |

| Figure 31 - Group Delay Distortion                                                            |    |

| Figure 32 - SPI Interface (Input Mode)                                                        |    |

| Figure 33 - SPI Interface (Output Mode)                                                       |    |

| Figure 34 - PCM Highway Timing for XE = 0 (Transmit on Negative PCLK Edge)                    |    |

| Figure 35 - PCM Highway Timing for XE = 1 (Transmit on Positive PCLK Edge)                    |    |

| Figure 36 - PCM Clock Timing.                                                                 |    |

| Figure 37 - ZSI Interface Timing Protocol                                                     |    |

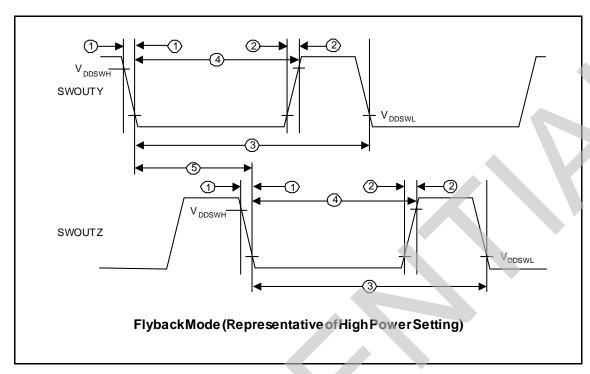

| Figure 38 - Switcher Output Waveform SWOUTY, SWOUTZ                                           |    |

| Figure 39 - ZL88601/602 Device Pinout (QFN-64) - Top View                                     |    |

| Figure 40 - ZL88601/602 Line Interface Circuit                                                |    |

| Figure 41 - ABS Switching Regulator Circuit                                                   |    |

| Figure 42 - VP-API-II Software Architecture                                                   |    |

| Figure 43 - Profile Wizard Screen - Creating a New Project                                    |    |

| Figure 44 - Profile Wizard - Main Menu                                                        |    |

| Figure 45 - Profile Wizard - Device Profile Configuration                                     |    |

| Figure 46 - Profile Wizard - DC Profile Configuration Example                                 |    |

| Figure 47 - Profile Wizard - Ringing Profile Configuration Example                            |    |

| Figure 48 - Profile Wizard - Tone Profile Configuration Example                               | 73 |

| Figure 49 - Profile Wizard - Tone Cadence Profile Example     | . 74 |

|---------------------------------------------------------------|------|

| Figure 50 - Profile Wizard - Ringing Cadence Profile Example  | . 7  |

| Figure 51 - Profile Wizard - Type 1 Caller ID Profile Example | . 76 |

| Figure 52 - Profile Wizard - Metering Profile Example         | . 7  |

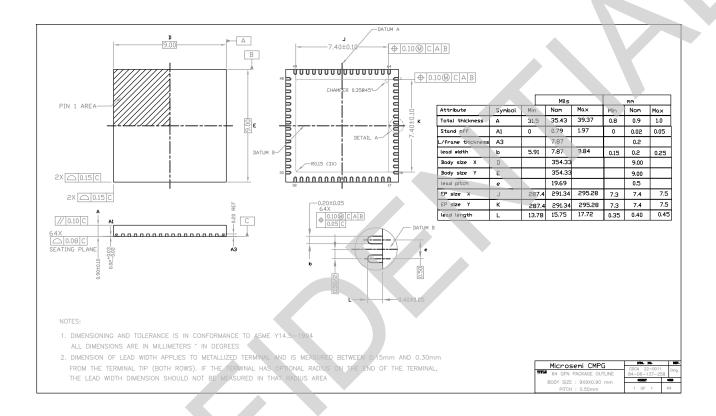

| Figure 53 - ZL88601/602 (QFN-64) Package Drawing              | . 78 |

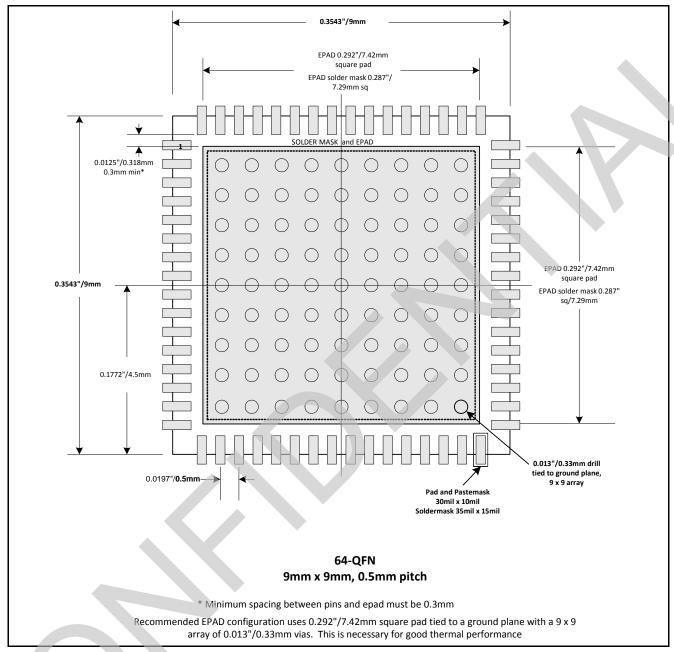

| Figure 54 - Recommended Land Pattern (QFN-64) - Top View      | . 79 |

|                                                               |      |

### **List of Tables**

| Table 1 - Maximum Number of Transmit or Receive Channels                    | 13 |

|-----------------------------------------------------------------------------|----|

| Table 1 - SPI Interface Signals                                             | 14 |

| Table 2 - VP-API-II Functions for Gain Adjustment                           | 19 |

| Table 3 - VP-API-II Functions for Speech Coding                             | 20 |

| Table 4 - VP-API-II Functions Using Signal Generators                       | 20 |

| Table 5 - VP-API-II Functions for Howler Tone Generation                    | 22 |

| Table 6 - DC Feed and Battery Switch Programmable Parameters                | 23 |

| Table 7 - Ring Trip Parameters                                              | 25 |

| Table 8 - Power Dissipation                                                 | 31 |

| Table 9 - Out of Band Discrimination, Narrowband Codec Mode                 | 39 |

| Table 10 - VP-API-II Functions for System Services                          | 63 |

| Table 11 - VP-API-II Functions for System Configuration                     | 63 |

| Table 12 - VP-API-II Functions for Line State Control                       |    |

| Table 13 - VP-API-II Functions for Line Status Monitoring                   |    |

| Table 14 - VP-API-II Functions for Configuring and Accessing I/O Lines      | 66 |

| Table 15 - VP-API-II Profile Types                                          |    |

| Table 16 - VP-API-II Functions for Device Configuration                     |    |

| Table 17 - Supported AC Source Impedances                                   |    |

| Table 18 - VP-API-II Functions Using AC FXS Profile                         | 70 |

| Table 19 - VP-API-II Functions for DC Feed and Hook Detection Configuration |    |

| Table 20 - VP-API-II Functions for Ringing and Ring Trip Definition         |    |

| Table 21 - VP-API-II Function Using Tone Profile                            | 73 |

| Table 22 - VP-API-II Function For Tone Cadencing                            |    |

| Table 23 - VP-API-II Functions For Ringing Cadencing                        |    |

| Table 24 - VP-API-II Functions for Caller ID                                | 76 |

| Table 25 - VP-API-II Functions for Metering                                 | 77 |

### 1.0 Solution Overview

The *ZL880 VoicePort Series* represents Microsemi's next generation solution for cable eMTAs, fiber PON SFUs, Integrated Access Devices, DSL Gateways, and other telephony products for worldwide markets.

The ZL880 VoicePort Series consists of the following three components:

- 1. ZL88601/602 Auto Battery Switching (ABS) or the ZL88701/702 Tracking Battery Device

- 2. VoicePath API-II (VP-API-II) Software

- 3. Profiles Data Structures

To support the ZL880 VoicePort Series, Microsemi offers a comprehensive VoicePath Software Development Kit (SDK) and hardware reference designs.

The ZL88601/602 device implements a dual-channel Automatic Battery Switching (ABS) universal telephone line interface with pin-selectable PCM and SPI or ZSI serial digital interfaces. The ZL88601/602 device performs all necessary voice telephony functions from driving a high voltage subscriber telephone line to DSP codec functions for two lines. All AC, DC, and signaling parameters are fully programmable via the PCM and SPI or reduced pincount ZSI interfaces. The ZL88601/602 device features integrated switching controllers which generate the high voltages needed for efficiently powering and ringing analog telephones. The high performance architecture permits high efficiency in all operating states and corresponding low power consumption. Additionally, the ZL88601/602 has self-test and line test support to allow the system to resolve faults to the line or line circuit. The integrated digital access to important line information such as AC and DC line voltages on Tip or Ring and Metallic or Longitudinal currents is crucial for remote applications where dedicated test hardware is not cost effective.

The *VoicePath API-II (VP-API-II)* software initializes each FXS port coefficient data containing application or country-specific AC and DC parameters, ringing and other signaling characteristics, and configures the switcher. *VP-API-II* resides on the customer's VoIP processor or SoC and provides high-level control over the telephony functions. *VP-API-II* offers a seamless migration between products utilizing its common software architecture and interfaces with the Microsemi *VeriVoice Professional Test Suite Software*.

A *Microsoft*<sup>®</sup> *Windows*<sup>®</sup> GUI (Graphical User Interface) application, *VoicePath Profile Wizard* (*VP Profile Wizard*), allows the user to select the operating parameters of the FXS channels and to automatically generate the sets of data structures, called *Profiles*, that are required by the *VP-API-II* for integration with the VoIP host software.

Figure 2 shows a high-level solution diagram with a ZL880 device, VP-API-II and Profiles.

Figure 2 - ZL880 Dual-Channel VoicePort Solution Diagram

### 2.0 ZL88601/602 Device Overview and Block Diagram

#### 2.1 VE880 Series Features

The ZL88601/602 device supports the following standard FXS features, which are common with the VE880 Series:

- Performs all Battery feed, Ringing, Signaling, Coding, Hybrid and Test (BORSCHT) functions

- Single chip solution provides high voltage line driving, digital signal processing, and high voltage power generation for two lines

- Wideband 7 kHz and Narrowband 3.4 kHz codec modes

- Exceeds Telcordia<sup>®</sup> GR-909-CORE transmission requirements

- Single hardware design meets worldwide requirements through software programming of:

- -Ringing waveform, frequency and amplitude

- -DC loop-feed characteristics and current limit

- -Loop-supervision detection thresholds

- -Off-hook debounce circuit

- -Ground-key and ring-trip filters

- -Two-wire AC impedance

- -Transhybrid balance impedance

- -Transmit and receive gains

- -Transmit and receive equalization

- -Digital I/O pins

- -A-law/μ-law and linear coding selection

- -Switching power supply

- Supports both loop-start and ground-start signaling

- On-hook transmission

- Power/service denial mode

- Smooth polarity reversal

- Supports wink function

- Metering generation with envelope shaping

Programmable frequency and duration

- Internal Test Termination

- Compatible with inexpensive protection networks

- Self-contained ringing generation and control

- Programmable ringing cadencing

- Internal battery-backed balanced or unbalanced, sinusoidal or trapezoidal ringing

- Integrated ring-trip filter and software enabled manual or automatic ring-trip mode

- Flexible tone generation

- Call progress tone generation

- DTMF tone generation

- Universal Caller ID generation (FSK and DTMF signaling)

- Howler tone generation with VP-API-II

- Integrated switching regulator controller

- Can generate the battery voltages for each line

- Good efficiency in all states

- Low idle-power per line

- Line-feed characteristics independent of battery voltage

- Monitors two-wire interface voltages and currents for subscriber line diagnostics implemented by VeriVoice Professional Test Suite Software

- Supported by VeriVoice Manufacturing Test Package

- Can monitor and/or drive Tip and Ring independently

- · Built-in voice-path test modes

- Integrated self-test features

- 100% compatible with VoicePath SDK and VP-API-II

- Small physical size in 9x9 mm 64-pin QFN

- –40°C to 85°C operation

#### 2.2 New and Enhanced Features

In addition to the standard *VE880 Series* FXS features, the ZL88601/602 features the following enhancements and new capabilities for greater power efficiency and lower system cost:

- New ZL880 Series family with a core operating at 1.2 V<sub>DC</sub>

- Internal 1.2 V<sub>DC</sub> regulator

- Lowers BOM cost:

- Direct FET driver

- Smaller value/size/cost switcher output capacitors

- Eliminates the need for external diodes for protecting SLIC against positive surges

- Smaller and less expensive capacitors at the SLIC battery input pins

- Smaller and less expensive C<sub>TAC</sub> and C<sub>RAC</sub> capacitors

- Low-Power Idle Mode (LPIM) with 60 mW typical power consumption per channel

- Voltage-based off-hook detection

- Supervision ADC for advanced testing, improved calibration and adaptive power management

- Can monitor up to 5 signals in multiplexed mode, such as VTIP, VRING, IM, IL, and VBH

- Two pins for sensing external voltages ranging from -180 V to +60 V

- Improved DC leakage measurements

- Facilitated by increasing the value of the DC sense resistors to 1.0  $M\Omega$

- · Over current monitoring and blanking

- New programmable options and thresholds

- Improved hook and ground key detection with hysteresis and calibrated thresholds

- Simultaneous ground key / DC fault detection

- · Enhanced SPI Interface

- Eliminates the need for  $\overline{\text{CS}}$  off requirement between data bytes

- Up to 3 times higher effective bandwidth

- Support for SPI Modes 0 and 3

- ZSI Interface option requires fewer serial interface signals to the host

- Only 4 ZSI signals required compared to 9 for PCM and SPI

- Less expensive system isolation cost

- Programmable PCM and SPI or ZSI interface voltage

- Supports communication with host processors at 1.8 V, 2.5 V or 3.3 V

- Upgraded command set

- Per-channel Wideband sampling mode

- On-chip timer functions

- Tone generators add frequency modulation capability for compliance with *BT*, *NTT*, and *Austel* special Howler tone requirements

- Upgraded ring-trip algorithm

- · Comprehensive device calibration capabilities

- Shorter calibration time

- No need to generate voltages to the Tip/Ring interface

- Longitudinal operating point calibration

- Programmable loop current dependent overhead

#### 2.3 Device Block Diagram

Figure 3 shows the major functional blocks of the ZL88601/602 device.

Figure 3 - ZL88601/602 Device Block Diagram

### 3.0 Functional Description

#### 3.1 Host Port Interface

The ZL88601/602 device features a flexible host port interface which is hardware-selectable for communicating with VoIP processors and SoCs using standard PCM and SPI or the reduced pin-count ZSI interfaces.

The host port interface voltage level (VDDHPI) can be set for 1.8 V, 2.5 V, or 3.3 V for maximum system-level compatibility. The host port interface supports the standard telecommunications clock rates of 1.024 MHz, 1.536 MHz, 2.048 MHz, 3.072 MHz, 4.096 MHz, 6.144 MHz, and 8.192 MHz with a Frame Sync (FS) of 8 kHz.

The host port supports two modes of operation: 1) PCM and SPI and 2) ZSI, selected by the ZSI pin.

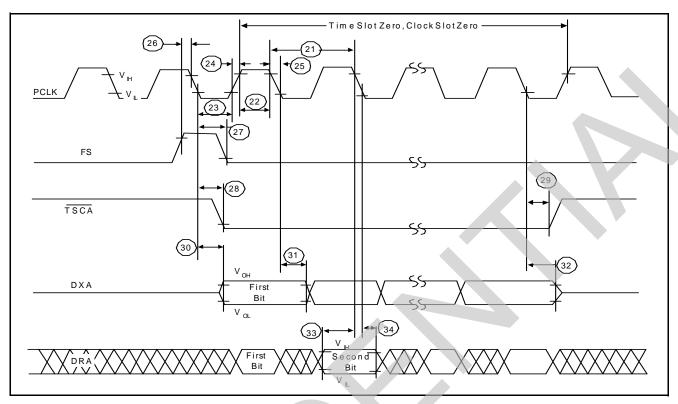

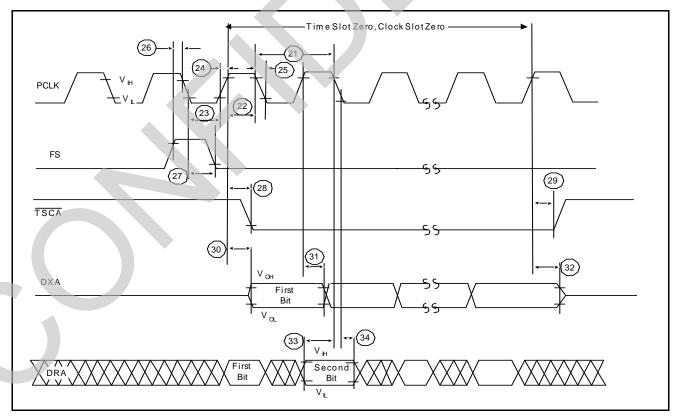

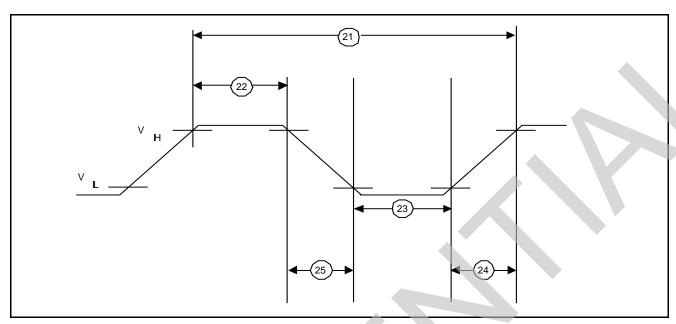

### 3.1.1 PCM Interface and Time Slot Assigner

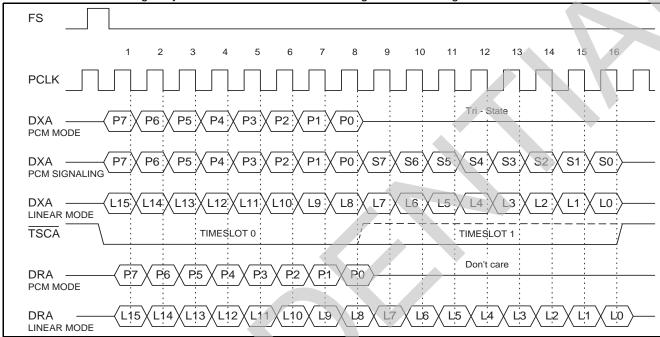

The PCM Interface and Time Slot Assigner (PCM block) is a synchronized serial mode of communication between the system and the ZL88601/602 device. In PCM mode, voice data can be transmitted/received on a serial PCM highway. This highway uses Frame Sync (FS) and PCLK as reference. The host port interface operates in this mode if the ZSI pin is pulled high.

Data is transmitted out of the DXA pin and received on the DRA pin. The ZL88601/602 device transmits/receives single 8-bit time slot (A-law/µ-law) compressed voice data or two contiguous time slot 16-bit two's complement linear voice data. The PCLK is a data clock supplied to the device that determines the rate at which the data is shifted in/out of the PCM ports. The FS pulse identifies the beginning of a transmit/receive frame and all time slots are referenced to it. For the ZL88601/602 device, the frequency of the FS signal is 8 kHz. In Wideband mode, two evenly spaced sets of time slots are exchanged in each frame. The PCLK frequency can be a number of fixed frequencies as defined by the *VP-API-II*. Please refer to Figure 45, "Profile Wizard - Device Profile Configuration" on page 69 for an example setting of the Transmit and Receive Clock Slots, PCM Transmit Edge, and PCLK Frequency.

The VP-API-II allows the time slots to be offset to eliminate any clock skew in the system. The Transmit Clock Slot and Receive Clock Slot fields are each three bits wide to offset the time slot assignment by 0 to 7 PCLK periods. The Transmit and Receive Clock Slot is a global command that is applied at the device level. Thus, for each channel, two time slots must be assigned: one for transmitting voice data and the other for receiving voice data. Figure 4 shows the PCM highway time slot structure.

Figure 4 - PCM Highway Structure

#### 3.1.1.1 Transmit PCM Interface

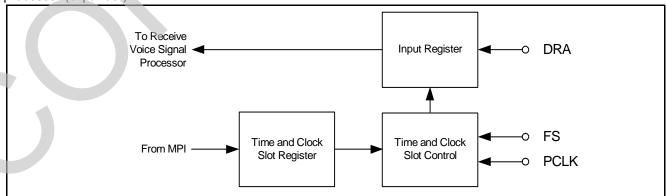

The Transmit PCM interface receives an 8-bit compressed code (A-law/µ-law) or a 16-bit two's complement linear code from the voice signal processor (compressor). The transmit PCM interface logic (shown in Figure 5) controls the transmission of the data onto the PCM highway through the output port selection circuitry and the time and clock slot control block. The data can be transmitted on either edge of the PCLK, as selected in the *Device Profile*.

Figure 5 - Transmit PCM Interface

The VP-API-II allows the time slot of the selected channel to be programmed. The Transmit Time Slot Register is 7 bits wide and allows up to 128 8-bit time slots in each frame, depending on the value of the PCLK frequency, the encoding scheme, and whether Narrowband or Wideband modes are selected. Refer to <u>Table 1</u> below for the maximum number of available channels. Please note that linear mode requires two back-to-back time slots to transmit one voice channel. The data is transmitted in bytes with the most significant bit first. Wideband mode requires twice the number of transmit time slots as Narrowband linear mode.

| Audio Mode                    | Encoding                     | 1.024 MHz | 2.048 MHz | 4.096 MHz | 8.192 MHz |

|-------------------------------|------------------------------|-----------|-----------|-----------|-----------|

| Narrowband                    | 8-bit compressed A-law/μ-law | 16        | 32        | 64        | 128       |

| (8 kHz sampling)              | 16-bit linear                | 8         | 16        | 32        | 64        |

| Wideband<br>(16 kHz sampling) | 16-bit linear                | 4         | 8         | 16        | 32        |

**Table 1 - Maximum Number of Transmit or Receive Channels**

#### 3.1.1.2 Receive PCM Interface

The receive PCM interface logic (see Figure 6) controls the reception of data bytes from the PCM highway. 8-bit compressed (A-law/µ-law) or 16-bit two's complement linear data is formatted and passed to the voice signal processor (expander).

Figure 6 - Receive PCM Interface

The *VP-API-II* allows the time slot of the selected channel to be programmed. The Receive Time Slot Register is 7 bits wide and allows up to 128 8-bit time slots in each frame. Refer to <u>Table 1 on page 13</u> for the maximum number of available channels. Please note that linear mode requires two back-to-back time slots to receive one voice channel. The data is transmitted in bytes with the most significant bit first. Wideband mode requires twice the numbers of receive time slots as Narrowband linear mode. Please refer to <u>"VP-API-II Functions for Speech Coding" on page 20</u> for more details about setting the codec mode and transmit and receive time slots. <u>Figure 7</u> illustrates data flow on the PCM highway with data transmitted on the negative PCLK edge.

Figure 7 - PCM Data Flow Transmit and Receive Data (Transmit Data on Negative PCLK Edge)

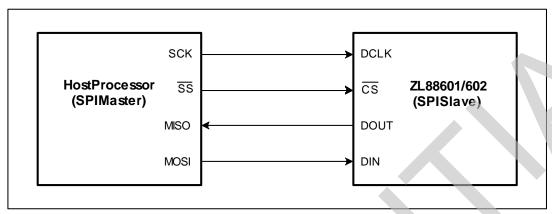

### 3.1.2 Serial Peripheral Interface (SPI)

The Serial Peripheral Interface (SPI) block communicates with external VoIP processors over a flexible half-duplex synchronous serial interface. This port is always a slave to the host processor's SPI port which provides clocking, chip select and initiates transactions.

#### 3.1.2.1 SPI Signals

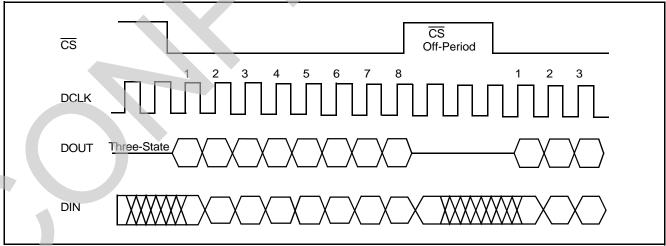

The SPI port physically consists of a serial data input (DIN) serial data output (DOUT), a data clock (DCLK), and a chip select (CS).

| Signal Name | Туре   | Description                      |

|-------------|--------|----------------------------------|

| DCLK        | Input  | Serial Clock                     |

| CS          | Input  | Chip or Slave Select, active low |

| DOUT        | Output | Master Input Slave Output        |

| DIN         | Input  | Master Output Slave Input        |

**Table 1 - SPI Interface Signals**

#### 3.1.2.2 Interrupt Signal

An optional interrupt signal (INT) is available to alert the host processor that the device has status information. It is recommended that the INT signal be tied to an interrupt-generating pin on the host processor. If the interrupt signal is not used, the host processor will need to regularly poll the device.

#### 3.1.2.3 SPI Connection Diagram

Figure 8 below shows a the standard 4-Wire SPI connection to the host processor. The optional INT signal is also shown here.

Figure 8 - 4-Wire SPI Connection to Host Processor

The ZL88601/602 device also supports 2- and 3-wire variants of the SPI interface in case of limitations on the host's serial port. Contact *Microsemi CMPG Customer Applications* for more information.

### 3.1.2.4 Chip Select Settings

Three chip select settings are supported:

- 1. <u>Low for each Byte or Word: CS</u> goes inactive between bytes or words. This mode is compatible with the legacy MPI mode.

- 2. <u>Command Framing: CS</u> goes inactive on some command boundaries. Commands cannot be aborted in this mode. All required bytes are expected even if CS is de-asserted in the middle.

- 3. <u>CS Hard-Wired Low:</u> This can be used when the ZL88601/602 device is the only slave on the SPI bus, but additional measures are required to acquire synchronization if it is ever lost.

Whenever  $\overline{CS}$  goes inactive the bit state machine is reset. Also, if  $\overline{CS}$  has not been active for *exactly* a multiple of 8 bit times, any byte which was partially received when  $\overline{CS}$  goes inactive is ignored.

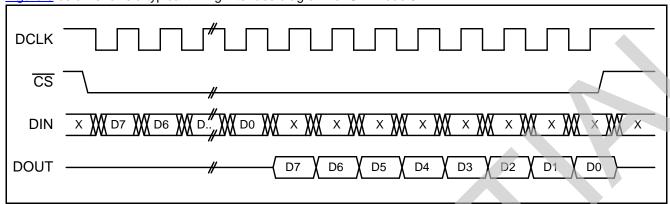

### 3.1.2.5 DCLK Polarity and Phase Settings

The SPI standards include four modes, defined by the polarity of DCLK and the phase relationship between data and DCLK. The clock polarity (CPOL) is determined by the idle state of DCLK. If the idle state is low, CPOL is 0. If the idle state is high, CPOL is 1. The clock phase (CPHA) is determined by which edge that data is valid. If the data is valid on the first edge of DCLK, CPHA is 0. If the data is valid on the second edge of DCLK, CPHA is 1.

The ZL88601/602 device supports SPI Modes 0 (CPOL =0 and CPHA = 0) and 3 (CPOL =1 and CPHA = 1) and contains a logic block to automatically conform to the selected Mode. SPI Modes 1 (CPOL =0 and CPHA = 1) and 2 (CPOL =1 and CPHA = 0) are not supported.

Since the host processor is the master, it must place DCLK in the proper idle state before  $\overline{\text{CS}}$  is asserted.

### 3.1.2.6 Length of Data Transactions

The SPI port on the ZL88601/602 device supports 8-bit (byte-wide) transactions. 16-bit transactions are not supported.

### 3.1.2.7 SPI Interface Timing

Figure 9 below shows a typical timing interface diagram for SPI Mode 3.

Figure 9 - SPI Mode 3 Interface Timing

#### 3.1.2.8 MPI Interface

The Microprocessor Interface (MPI) is essentially a 4-Wire SPI Mode 3, with CS low for each byte and 8-bit data transactions. This interface has been historically used on numerous Microsemi *VoicePort* devices such as the *VE880 Series*. With the MPI interface, 8-bit commands can be followed with additional bytes of input data, or can be followed by the ZL88601/602 device sending out bytes of data. All data input and output is MSB (D7) first and LSB (D0) last. All data bytes are read or written one at a time, with  $\overline{\text{CS}}$  going high for at least a minimum off period before the next byte is read or written. Only a single channel should be enabled during read commands.

All commands that require additional input data to the device must have the input data as the next N words written into the device (for example, framed by the next N transitions of  $\overline{CS}$ ). All unused bits must be programmed to 0 to ensure compatibility with future parts. All commands that are followed by output data will cause the device to output data for the next N transitions of  $\overline{CS}$  going low. The ZL88601/602 device will not accept any commands until all the data has been shifted in or out. The output values of unused bits are not specified.

<u>Figure 10</u> shows an example MPI mode interface timing, with DOUT changing on the negative edge of DCLK. DIN is sampled on the rising edge of DCLK.

Figure 10 - MPI Interface Timing

An MPI cycle is defined by transitions of  $\overline{CS}$  and DCLK. If the  $\overline{CS}$  lines are held in the high state between accesses, the DCLK may run continuously with no change to the internal control data. Using this method, the same DCLK can be run to a number of ZL88601/602 devices and the individual  $\overline{CS}$  lines will select the appropriate device to access. Between command sequences, DCLK can stay in a static state indefinitely with no loss of internal control

information regardless of any transitions on the  $\overline{\text{CS}}$  lines. Between bytes of a multi byte read or write command sequence, DCLK can also stay in a static high state indefinitely. If the host controller has a single bidirectional serial data pin, the DOUT pin of the ZL88601/602 device can be connected to its DIN pin.

If a low period of  $\overline{CS}$  contains less than 8 positive DCLK transitions, it is ignored. If it contains 8 or more positive transitions, the first 8 transitions will be interpreted as the first byte and the next 8 transitions will be treated as the second byte, etc. This allows the chip select input to be tied low permanently if desired.

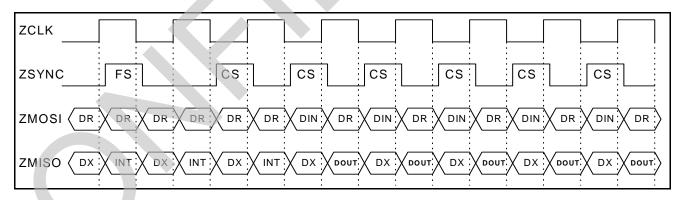

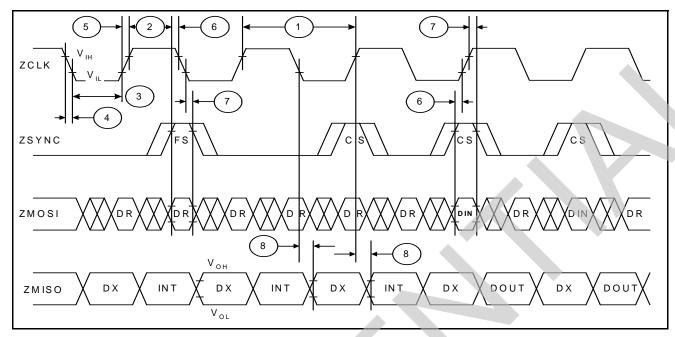

#### 3.1.3 ZSI Serial Mode

An alternative host interface supported by the ZL88601/602 device is a 4-wire interface called ZSI and is illustrated in <u>Figure 11</u>. It is active when the <u>ZSI</u> pin is tied to ground. Note that the <u>ZSI</u> serial interface must also be supported by the host processor or by a PCM/SPI to ZSI bus translator device such as the Le88004.

This interface supports separate PCM and control channels based on the level of the ZCLK. For receive signals (ZSYNC, ZMOSI) PCM data is valid when ZCLK is high and control data is valid when ZCLK is low. For the transmit ZMISO, PCM data is valid when ZCLK is low and control data valid when ZCLK is high. The control data is framed byte by byte in a similar way to the separate MPI interface on other VoicePort family products. Chip select status is carried on the ZSYNC signal and requires a chip select off time of at least one clock period. Interrupt status is communicated on the ZMISO control channel whenever the previous ZSYNC CS status is low. This is achieved by XORing the DXA data with the active high INT status.

The ZCLK rate can be 1.024 MHz, 1.536 MHz, 2.048 MHz, 3.072 MHz, 4.096 MHz, 6.144 MHz, or 8.192 MHz. The ZL88601/602 must be programmed to match the applied ZCLK frequency using the control channel. Both PCM and control data are transferred at the same ZCLK rate over the ZSI.

### 3.1.3.1 **ZSI Timing**

Figure 11 shows the protocol for multiplexing the PCM and control signals onto the ZSI.

Note that chip select must be de-asserted at least one clock between bytes or a reset will be generated after 16 clocks.

Figure 11 - ZSI Timing Protocol

### 3.2 Input / Output Block

The ZL88601/602 device features two dedicated and two optional general purpose input / output (I/O) pins. I/O1<sub>1</sub> and I/O1<sub>2</sub> can be configured by the user as inputs, outputs, or as high-current LED or relay drivers. I/O2<sub>1</sub> and I/O2<sub>2</sub> may be configured as general purpose digital inputs or outputs or as voltage sense pins (VS1 and VS2). When configured as inputs, I/O2<sub>1</sub> and I/O2<sub>2</sub> are capable of generating interrupts.

### 3.3 Voltage Sense

The voltage sense block allows the measurement of analog voltages at the pins VS1 and VS2, when they are configured as analog inputs. This makes it possible to monitor VSW and VBH or VBL in real time and make switcher optimizations based on their levels and to measure power consumption. An external 1.0-M $\Omega$ , 1% resistor needs to be connected between each of these pins and the voltages to be measured.

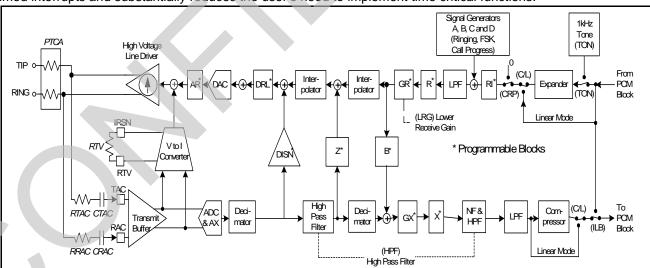

### 3.4 Voice Signal Processor

This block, shown in Figure 12, performs digital signal processing for the transmission and reception of voice. It includes *G.711* compression/decompression, impedance matching, filtering, gain scaling, DTMF generation and general-purpose tone generators for each channel. Additionally Caller ID (FSK and DTMF) and metering generation are provided.

This block performs the codec and filter functions associated with the four-wire section of the subscriber line circuitry in a digital switch. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. During conversion, digital filters are used to band-limit the voice signals.

The user-programmable filters perform the following functions:

- · Sets the receive and transmit gain

- · Performs the transhybrid balancing function

- · Permits adjustment of the two-wire termination impedance

- · Provides frequency attenuation adjustment (equalization) of the receive and transmit paths

Country- and standards-specific *Profiles* are available from Microsemi with pre-computed digital filter coefficients. The PCM codes can be either 16-bit linear two's-complement or 8-bit companded A-law or  $\mu$ -law.

The ZL88601/602 device is architected in such a way as to reduce the real time demands on the host processor. An integrated cadencer/sequencer controls ringing and call progress tone generation. This feature can also generate timed interrupts and substantially reduces the user's need to implement time critical functions.

Figure 12 - Voice Signal Processing Block Diagram

### 3.4.1 Impedance Synthesis

The analog impedance synthesis loop is comprised of the SLIC block, the AC sense path components, the transmit amplifier, and a voltage to current converter. An external resistor, R<sub>TV</sub>, synthesizes the nominal impedance in the analog domain. Additional refinement of the impedance is done in the DSP via the Digital Impedance Scaling Network (DISN) and Z-blocks.

The DISN path is comprised of the voice A/D and its first stage of decimation, a DISN, and the voice DAC. The 8-bit DISN synthesizes a portion of the AC impedance which appears in parallel with R<sub>TV</sub> and is used to modify the impedance set by the external analog network.

The Z Filter is a programmable digital filter providing an additional path and programming flexibility over the DISN in modifying the transfer function of the synthesis loop. Together  $R_{TV}$ , DISN, and the Z Filter enable the user to synthesize virtually all required telephony device input impedances.

### 3.4.2 Frequency Response Correction and Equalization

The voice signal processor contains programmable filters in the receive (R) and transmit (X) directions that may be programmed for line equalization and to correct any attenuation distortion caused by the Z Filter.

### 3.4.3 Transhybrid Balancing

The voice signal processor's programmable B Filter is used to adjust transhybrid balance. The filter has a single pole Infinite Impulse Response (IIR) section and an eight-tap Finite Impulse Response (FIR) section, both operating at 16 kHz.

### 3.4.4 Gain Adjustment

The transmit path of the FXS has two programmable gain blocks. Gain block AX is an analog gain of 0 dB or 6.02 dB (unity gain or gain of 2.0), located immediately before the A/D converter. GX is a digital gain block that is programmable from 0 dB to +12 dB, with a worst-case step size of 0.1 dB for gain settings below +10 dB, and a worst-case step size of 0.3 dB for gain settings above +10 dB. The filters provide a net gain in the range of 0 dB to 18 dB. The receive voice path has three programmable gain blocks. GR is a digital loss block that is programmable from 0 dB to 12 dB, with a worst-case step size of 0.1 dB. DRL is a digital loss block of 0 dB or 6.02 dB. AR is an analog gain of 0 dB or 6.02 dB (unity gain or gain of 2) or a loss of 6.02 dB (gain of 0.5), located immediately after the D/A converter. This provides an attenuation in the range of 0 dB to 18 dB.

The gain adjustment block can also be accessed by a VP-API-II function directly, without using an AC FXS Profile.

| Function Name  | Description                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VpSetRelGain() | Adjusts transmit and/or receive gain up to +/-6 dB. Relative gain of 1 (0 dB) defined as initial value programmed by AC FXS Profile. Note that the supplied AC FXS Profiles have initial gains of -6 dBr receive and 0 dBr transmit |

| VpSetOption()  | VP_OPTION_ID_ABS_GAIN Programs absolute gain                                                                                                                                                                                        |

Table 2 - VP-API-II Functions for Gain Adjustment

### 3.4.5 Transmit Signal Processing

In the transmit path (A/D) of the FXS, the AC Tip - Ring analog input signal is sensed by the TAC and RAC pins, buffered, amplified by the analog AX gain and sampled by the A/D converter, filtered, companded (for A-law or  $\mu$ -law), and made available to the PCM blocks. If linear format is selected, the 16-bit data will be transmitted in two consecutive time slots starting at the programmed time slot. The B, X, and GX digital filter blocks are user-programmable digital filter sections. The first high-pass filter is for DC rejection, and the second high pass and notch filters reject low frequencies such as 50 Hz or 60 Hz.

#### 3.4.6 Receive Signal Processing

In the receive path (D/A) of the FXS port, the digital signal is expanded (for A-law or  $\mu$ -law), filtered, interpolated, converted to analog, and driven onto TIP and RING by the SLIC block. The AR, DRL, DISN, Z, R, and GR blocks are user-programmable filter sections.

### 3.4.7 Speech Coding

The A/D and D/A conversion follows either the A-law or the  $\mu$ -law standard as defined in *ITU-T Recommendation* G.711. Alternate bit inversion is performed as part of the A-law coding. Linear code is an option on both the transmit and receive sides of the device. Two successive time slots are required for linear code operation. The linear code is a 16-bit two's-complement number which appears sign bit first on the PCM highway.

#### 3.4.8 Wideband Operation

Each channel on the ZL88601/602 device can be set to operate in either Narrowband or Wideband mode under *VP-API-II* software control. In the Wideband mode, the nominal voice bandwidth is expanded and starts at 50 Hz or 200 Hz (depending on whether or not a high-pass and 50/60 Hz notch filter is enabled) to 7000 Hz to provide better voice quality. The *AC FXS Profiles* must be programmed with wideband coefficients. In the Wideband mode, the increased data rate is processed by accessing a second set of timeslots equally spaced in the frame.

| Function Name | Description                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| VpSetOption() | VP_OPTION_ID_TIMESLOT Programs transmit and receive timeslot. VP_OPTION_ID_CODEC Programs speech coding mode.                             |

| VpGetOption() | VP_OPTION_ID_TIMESLOT Retrieves current values of transmit and receive timeslot. VP_OPTION_ID_CODEC Retrieves current speech coding mode. |

Table 3 - VP-API-II Functions for Speech Coding

### 3.5 Signal Generation

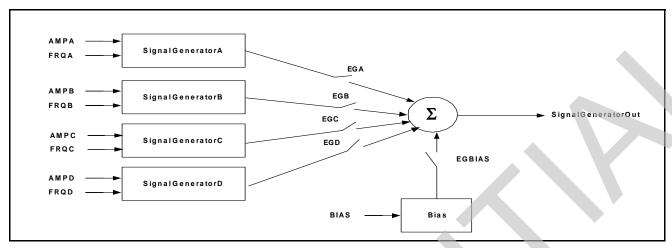

Up to four programmable digital signal generators are available for the FXS channel. These signal generators can be programmed for multi-tone generation, amplitude and frequency modulation, and or the generation of complex sine, triangular or trapezoidal signals.

#### 3.5.1 Multi-Tone Generation

In this configuration, up to four tone generators are summed into the output path, as shown in <u>Figure 13 on page 21</u>. The Bias generator produces a DC bias that can be used to provide DC offset during ringing or DC test signals during diagnostics. This generator is automatically enabled when entering the VP LINE RINGING state.

| Function Name    | Description                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VpSetLineTone()  | Provides simultaneous generation of up to four tones. Note that with Tone Cadencing, tones can be enabled/disabled individually to provide Special Indication Tone (SIT). |

| VpSetLineState() | VP_LINE_RINGING and VP_LINE_RINGING_POLREV Uses Signal Generator A (and B for trapezoidal type ringing) with user selected frequency, offset, amplitude, and type.        |

| VpSendSignal()   | VP_SENDSIG_DTMF_DIGIT Generates a DTMF digit on the line.                                                                                                                 |

| VpInitCid()      |                                                                                                                                                                           |

| VpSendCid()      | Sending Caller ID (FSK and DTMF message data supported) on an FXS line.  Providing Type 2 CID Alerting tone.                                                              |

| VpContinueCid()  | 1 Toylding Type 2 Old Merting tone.                                                                                                                                       |

Table 4 - VP-API-II Functions Using Signal Generators

Figure 13 - Multi-Tone Generation

Signal Generator A is also used by the *VeriVoice* test suites to produce slow ramps. This allows a complex sequence of diagnostic test voltages to be generated in a controlled manner without generating unwanted transients on the line.

Each generator has independent frequency and amplitude parameters. The frequency accuracy is basically the same as the crystal accuracy of the system.

The EGA/B/C/D bits are controlled by the VP-API-II Cadencing engine.

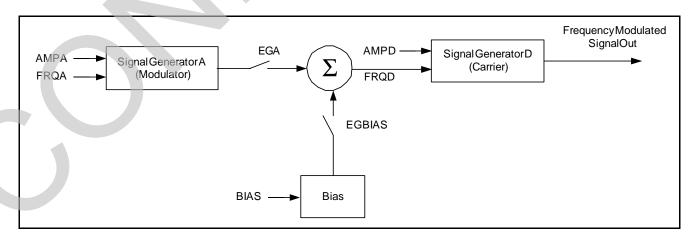

### 3.5.2 Frequency and Amplitude Modulation

The signal generators can also be used to generate frequency- and/or amplitude-modulated tones in conformance with worldwide Howler (receiver off-hook) and call progress tone requirements. Frequency modulation is performed in a dedicated hardware block, while amplitude modulation is performed in software by *VP-API-II*.

To generate frequency-modulated tones, Signal Generator A is configured as a modulator, while Signal Generator D is configured as a carrier. The output of Signal Generator A is the frequency input to Signal Generator D as shown in <a href="Figure 14">Figure 14</a>. Note that Signal Generator A needs a positive DC bias so that its output is always positive. Caller ID generation is not available while frequency modulation is taking place. Note that Signal Generators B and C are available to be summed to the frequency-modulated signal, if necessary.

Figure 14 - Frequency Tone Modulation

Frequency and amplitude modulation allow the ZL88601/602 device to meet exacting Howler tone requirements such as those specified in *BTNR 1080 Version 15* and *Draft 960-G, NTT Edition 5* and *Austel AUS002:2001*.

<u>Table 5</u> lists the *VP-API-II* functions that are used for Howler tone generation.

| Function Name    | Description                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VpSetLineState() | VP_LINE_HOWLER Places the device in a high gain state for Howler tone generation.                                                                                               |

| VpSetLineTone()  | Provides simultaneous generation of up to four tones. Note that with Tone Cadencing, tones can be enabled/disabled individually or modulated in order to generate Howler tones. |

Table 5 - VP-API-II Functions for Howler Tone Generation

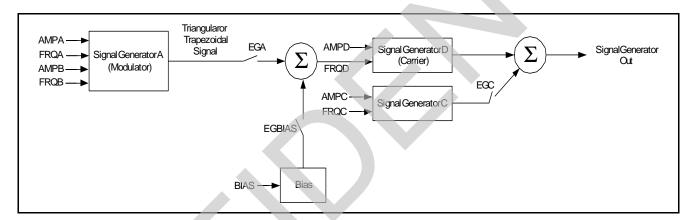

### 3.5.3 Triangular and Trapezoidal Signal Generation

The signal generators can also be used to generate trapezoidal waveforms for ringing. Figure 15 shows a configuration that is typically used to generate trapezoidal waveforms. Triangular waveforms can also be generated.

Figure 15 - Trapezoidal Signal Generation

#### 3.6 Low Power DC Feed

The ZL88601/602 device supports Low Power Idle Mode (LPIM), which reduces the system power consumption during idle (On-Hook) state. LPIM provides a weak DC feed capable of at least 5 mA to the line and reacts to a change in the line voltage to create an off-hook indication when a telephone goes off-hook.

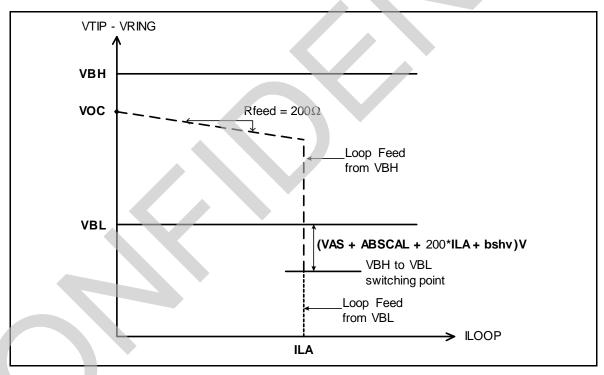

#### 3.7 Normal DC Feed

DC feed is active in normal idle, talk and ringing states and the programmed characteristics appear between Tip and Ring. VAS is chosen to ensure that sufficient headroom is available for the amplifiers when on-hook to support On-Hook Transmission with the programmed open circuit (VOC) voltage. The parameters that control DC feed are summarized in Table 6 on page 23. Their values are determined by the VP-API-II using the VpCalLine() function to ensure circuit performance. In addition, the VP-API-II handles some internal programming depending on the selected VOC voltage.

| Parameter | Range           | Description                                                                          |

|-----------|-----------------|--------------------------------------------------------------------------------------|

| ILA       | 20 – 30 mA      | Sets the current limit for DC feed                                                   |

| VOC       | 12 – 57 V       | Sets open circuit DC feed voltage. Two ranges, 12 - 33 V and 36 - 57 V are supported |

| VAS       | 1.5 – 7.25 V    | Allows for some programmability for the automatic battery switching point            |

| ABSCAL    | -5.25 – +5.25 V | Allows calibration of the battery switching point per channel                        |

| bshv      | 1.0 – 7.0 V     | Battery switch hysteresis voltage                                                    |

**Table 6 - DC Feed and Battery Switch Programmable Parameters**

The DC Profile produces a DC feed curve at Tip and Ring when the fuse resistors are inside the feedback loop formed by the RTDC, RRDC feedback network. Note that the value of the combined Tip and Ring feed resistors Rfeed is programmable to 0, 50, 100, or 200  $\Omega$  to correspond to the choice of PTCs or fuse resistors that are used. Please refer to Figure 16 below for the active state I/V feed curve for Rfeed = 200  $\Omega$ .

Figure 16 - Normal DC Feed I / V Characteristic

Figure 46, "Profile Wizard - DC Profile Configuration Example" on page 71 shows typical DC feed parameters.

### 3.8 Test Feed

The Tip Open test state presents the DC feed characteristic shown in Figure 16 between the Ring lead and ground.

#### 3.9 Ringing

The ZL88601/602 device supports balanced and unbalanced ringing.

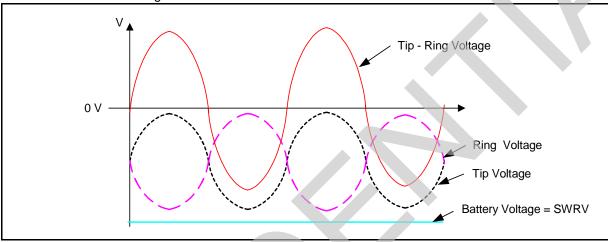

#### 3.9.1 Balanced Ringing

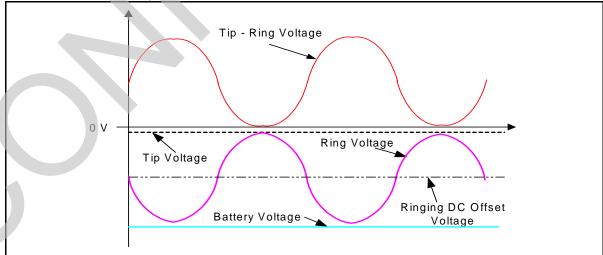

Internal balanced ringing drives the subscriber line with balanced ringing voltage waveforms (see Figure 17). In the balanced ringing mode, the ringing signal is driven differentially, thus maximizing the ringing signal swing. In this mode, the SLIC appears to the subscriber line as a voltage source with an output impedance of 200  $\Omega$ . The maximum ringing signal possible in the balanced mode for the ZL88602 is 100-V<sub>PK</sub> (80-V<sub>PK</sub> for the ZL88601), corresponding to the maximum AC + DC voltages.

Figure 17 - Balanced Ringing with Fixed Supply

#### 3.9.2 Unbalanced Ringing

Unbalanced ringing holds the Tip output to a voltage close to ground while applying the ringing in a single ended fashion to the ring lead (see <u>Figure 18</u>). When in the unbalanced ringing mode, the ZL88601/602 chipset appears to the subscriber line as a voltage source with an output impedance of 200  $\Omega$ . Unbalanced ringing is recommended only with the ZL88602 due to its higher voltage rating. The maximum unbalanced ringing signal possible with that device is 80-V<sub>PK</sub> with a 20-V<sub>DC</sub> offset.

Figure 18 - Unbalanced Ringing with Fixed Supply

#### 3.9.3 Switch Hook Detection

The FXS supervision circuits of the ZL88601/602 device provide debounced off-hook indications to an external processor via the host port interface. The supervision circuit compares a scaled version of the Tip-Ring current to a programmed off-hook threshold, TSH. The output of the comparator is debounced by a programmable debounce timer, DSH. A debounced *Off-Hook* indication generates an interrupt to the host processor.

### 3.9.4 Ring Trip Detection

Ring trip is the process of sensing a subscriber's off-hook event during ringing. This is accomplished by sensing the rise in loop current which occurs when a phone goes Off-Hook. The ZL88601/602 device can detect ring trip when the ringing signal is purely AC and/or when the ringing signal has a DC bias on it. To do so, the ring trip algorithm is automatically altered internally by the ZL88601/602 device based on the user-programmed parameters.

The ring trip detector uses the Tip-Ring current as an input. This current is rectified so that AC + DC ring trip can be detected. The output of the rectified signal is compared to a programmable ring trip threshold and the output is digitally debounced. The output is blanked upon ring entry to avoid false ring trips.

The ring trip detection circuit provides debounced ring trip indications to an external processor via the host port interface. The ring trip circuit compares a scaled version of the Tip-Ring current to a programmed Ring Trip Threshold (RTTH). The output of the comparator is processed by the ring trip algorithm on a cycle by cycle basis to provide immunity to false ring trips. In addition, spending more than 50% of the time in ringing current limit will generate a trip indication. A positive ring trip occurs if a trip indication is present for one (optional) or two (default) complete ring cycles, and an interrupt can be raised to the host processor. For AC-only ringing, the signal is half-wave rectified.

The Ring Trip Threshold (RTTH), integration method (positive half-wave for AC only or full-wave for AC+DC), the number of cycles (1 or 2), and Ringing Current Limit (ILR) are programmed in the *Ringing Profile*. Microsemi provides a number of example *Ringing Profiles* for most common ringing requirements incorporating the ringing signal parameters and corresponding ring trip settings.

The following equations can be used to select new ring trip settings when using different ringing waveforms and different loads. They allow the ratio of the open circuit ringing voltage to the ringing threshold current to vary by +/-20%, which is conservative.

| Name   | Description                                                                                        |

|--------|----------------------------------------------------------------------------------------------------|

| AMPA   | Amplitude of signal generator A which is used for ringing                                          |

| FREQA  | Frequency of signal generator A which is used for ringing                                          |

| BIAS   | DC bias for ringing                                                                                |

| RTDCAC | Ringing trip based on AC only or Battery Backed (DC) Ringing                                       |

| RTTH   | Ringing trip threshold in 0.5 mA steps from 0 to 63.5 mA                                           |

| ILR    | Ringing current limit programmed in 2 mA steps. ILR=0 represents 50 mA. ILR = 31 represents 112 mA |

| HOOK   | Interrupt in signalling register indicating a ring trip occurred                                   |

**Table 7 - Ring Trip Parameters**

For AC only ringing, RTDCAC is 1 and the ringing current is half-wave rectified and averaged over a ringing cycle. If this result exceeds the RTTH threshold for two successive cycles, the HOOK bit will be set. This method limits the supported loop length x depending on the minimum must not trip ringing impedance (Rmnt in Ohms) and allowing for errors in the applied ringing voltage and trip level. The maximum loop resistance is given by:

$RLOOP(max) = 0.67xRmnt - Rphone - 66\Omega$

RLOOP (max) excludes the DC resistance of the phone (Rphone, typically 430  $\Omega$  in the U.S.), and the fuse resistance if DC line sensing is behind the fuse resistors.

For a sinusoidal ringing waveform of VRING (RMS) volts, and Rmnt impedance, the following ring trip settings should be used:

$$RTTH = \frac{0.54 \text{xVRING}}{\text{Rmnt} + 200\Omega}$$

$$ILR = \frac{1.4 \text{xVRING}}{\text{Rmnt} + 200\Omega}$$

In general for short loop applications, it is recommended to use AC ring trip even in the presence of a DC bias that could allow a DC based ring trip, and the above equations still apply. Note that the ringing source impedance is nominally  $200 \Omega$ .

### 3.10 Subscriber Line Testing

The ZL88601/602 device provides the ability for the user to perform the *Telcordia GR-909-CORE / TIA-1063* diagnostic testing for the voice ports. In Test mode, a variety of input signals can be read from the voice ADC converter. These signals include the switching regulator voltage and the line DC and AC voltages.

#### 3.10.1 VeriVoice Professional Test Suite Software for the ZL880

VeriVoice Professional Test Suite Software is an advanced test suite featuring the following tests:

Line Voltage: Checks for hazardous and foreign AC and DC voltages.

Receiver Off-Hook: Checks for longitudinal fault, off-hook resistive fault and receiver off-hook.

Regular REN: Tests the impedance of the line and returns a fail if the Ringer Equivalence Number

(REN) is too low or high.

Electronic REN: Provides REN Tip to Ring, Tip to ground and Ring to ground based on capacitance

Resistive Fault: Measures three-element resistance.

GR-909-CORE / TIA-1063: Performs all of the GR-909-CORE outward tests in the correct sequence.

Capacitance: Measures three element capacitance

Master Socket: Detects master socket terminations

Cross Connect: Detects cross connected FXS

Loopback: Enables receive-to-transmit signal loopback using two different methods

Read Loop Conditions: Measures voltages between Tip and Ring, Tip to ground, Ring to ground, and VBH or

VBL to ground. Also measures metallic and longitudinal line currents in supported

states.

Read Battery Conditions: Reads the battery voltages connected to the line circuit.

• DC Voltage Self-Test: Verifies that the line circuit has the ability to drive the voltage ranges required for the

normal operation of the line circuit.

DC Feed Self-Test

Measures the voltage and current across a known internal test termination using the

DC Profile that has been programmed.

Ringing Self-Test

Verifies ring signal generation, drive capability, and ring trip.

On/Off Hook Self Test Creates on-hook and off-hook conditions on the line using the internal test termination

and verifies that they are properly reported.

#### 3.11 Manufacturing Testing

The ZL88601/602 is supported by the *VeriVoice Manufacturing Test Package (VVMT)*, a platform-independent 'C' source code module which facilitates factory testing and calibration of assembled boards with this and other Microsemi voice products.

#### 3.12 Metering

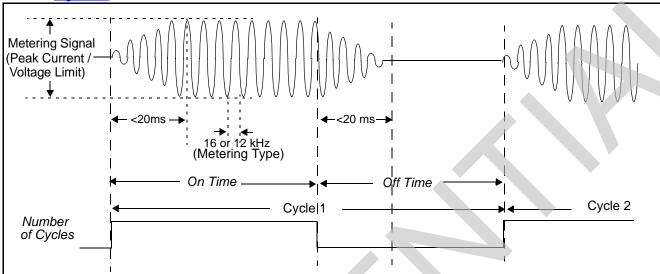

The ZL88601/602 device is capable of 0.5  $V_{RMS}$  metering into a 200  $\Omega$  metering load at either 12 kHz or 16 kHz. Smooth metering application and abrupt metering application are supported. A typical metering sequence is shown below in Figure 19.

Figure 19 - Metering Pulse Definitions

The metering on time, off-time, and number of cycles are programmed in the VP-API-II function  $v_p \text{StartMeter}()$ . This off-loads much of the timing from the host processor. Note that a ramp up / ramp down period of up to 20 ms is possible. The metering type (12 or 16 kHz), peak current and voltage limit are set in the  $Metering\ Profile$  and are used by the VP-API-II function  $v_p \text{InitMeter}()$ . Note that in a normal configuration, some of the metering current flows into the CTD and CRD capacitors, so that the current sourced into an external load will be less than that programmed peak current parameter even when the metering voltage limit is not reached. The metering voltage that reaches the load is also dependent on the total fuse resistance and the minimum load resistance, which is typically 200  $\Omega$

#### 3.13 Switching Regulator Controller

The switching regulator controller and the external power train circuitry provide a flexible switching regulator that produces the negative supply voltages required by the high voltage line drivers to drive each line.

The recommended ABS flyback application circuit is shown in Figure 41 on page 59.

Switcher Y has been configured to generate two fixed supplies, VBH and VBL, where the VBL supply is regulated. By regulating VBL at around -27 V and using a transformer with an output winding split into three equal sections, VBH will be centered around -81 V. Refer to Figure 41 on page 59 for a more complete schematic of the external components needed to implement the regulator. The regulator shown is a typical flyback configuration with a multitap transformer configured for two outputs.

The LFC pins support a soft start for the switching regulator controllers by filtering the internally generated switcher output reference using an external capacitor. LFC<sub>1</sub> is associated with Switcher Y, and LFC<sub>2</sub> is associated with Switcher Z. The pole is set with a nominal 4 k $\Omega$  internal resistance, allowing a 0.1  $\mu$ F capacitor to provide a 10 ms ramp time. It is also possible to control the power-up of the switching regulators by appropriate use of the switcher power modes, eliminating the need for external capacitors. If the switcher controller is not being used, the corresponding LFC pin can be left open.

Even if the ZL88601/602 device is not using the switching regulator controllers to generate the battery supplies, it must sense each of the applied batteries through the SWVSY and SWVSZ pins for correct longitudinal control and battery switching.

Switching regulator parameters are set in the *Device Profile* and control the switching frequency. In addition, the controller detects over current events and terminates the output pulse on a cycle by cycle basis.

### 3.14 Charge Pump Regulator and MOSFET Gate Driver

The ZL88601/602 device features an internal charge pump regulator to generate a supply voltage suitable to drive a wide range of external MOSFETs. The charge pump regulator steps up the DVDD voltage to a value required by the MOSFET supply (VDDSW) to drive a logic level MOSFET (between 4.3 V to 5 V). The charge pump regulator has an output undervoltage protection circuit with a threshold about 0.2 V below the target voltage. The internal charge pump voltage is filtered by an external capacitor at the VDDSW node. For any other use or connection to VDDSW, contact Microsemi Customer Applications.

The charge pump converter configuration is selected in the Device Profile.

## 4.0 Electrical Specifications

### 4.1 Absolute Maximum Ratings

Stresses above those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Ambient temperature, under Bias                                                                                         | -40°C < T <sub>A</sub> < +85°C                                                               |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Ambient relative humidity (non condensing)                                                                              | 5 to 95%                                                                                     |

| VBH, VBL <sub>1</sub> , VBL <sub>2</sub> with respect to GND for the ZL88601 device for the ZL88602 device              | -105 V <sub>DC</sub> to +0.5 V <sub>DC</sub><br>-125 V <sub>DC</sub> to +0.5 V <sub>DC</sub> |

| VBH with respect to GND (both lines active VBL, VBL $_{\rm i}$ <  -50  V) for the ZL88601 device for the ZL88602 device | -125 V <sub>DC</sub> to +0.5 V <sub>DC</sub><br>-160 V <sub>DC</sub> to +0.5 V <sub>DC</sub> |

| AVDD, DVDD, VDDHPI voltages with respect to GND                                                                         | -0.4 V <sub>DC</sub> to + 4.0 V <sub>DC</sub>                                                |

| AVDD voltage with respect to DVDD                                                                                       | $-0.4 \text{ V}_{DC}$ to + 0.4 $\text{V}_{DC}$                                               |

| I/O1 <sub>1</sub> , I/O1 <sub>2</sub> current sink to GND <sup>(1)</sup>                                                | 70 mA                                                                                        |

| TIPD <sub>i</sub> or RINGD <sub>i</sub> voltage with respect to GND (continuous)                                        | VBH – 1 V <sub>DC</sub> to + 1.0 V <sub>DC</sub>                                             |

| TIPD <sub>i</sub> or RINGD <sub>i</sub> voltage with respect to GND (10 ms, F = 0.1Hz)                                  | VBH – 5 V <sub>DC</sub> to + 5.0 V <sub>DC</sub>                                             |

| TIPD <sub>i</sub> or RINGD <sub>i</sub> voltage with respect to GND (1 $\mu$ s, F = 0.1Hz)                              | VBH – 10 V <sub>DC</sub> to + 10 V <sub>DC</sub>                                             |

| $TIPD_i$ or $RINGD_i$ voltage with respect to GND (250 ns, F = 0.1Hz)                                                   | VBH – 15 V <sub>DC</sub> to + 15 V <sub>DC</sub>                                             |

| TIPD <sub>i</sub> or RINGD <sub>i</sub> current (continuous)                                                            | ± 150 mA                                                                                     |

| TIPD <sub>i</sub> or RINGD <sub>i</sub> current (1 μs)                                                                  | ± 400 mA                                                                                     |

| Latch up immunity (any pin)                                                                                             | ± 100 mA                                                                                     |

| Maximum device power dissipation, continuous $^{(2)}$ - $T_A = 85^{\circ}C$ $P_D$                                       | 2.1 W                                                                                        |

| Junction to ambient thermal resistance $^{(2)}$ $\theta_{JA}$                                                           | 26°C/W                                                                                       |

| Junction to board thermal resistance $^{(2)}$ $\theta_{JB}$                                                             | 7°C/W                                                                                        |

| Junction to case bottom (exposed pad) thermal resistance $\theta_{\text{JC (BOTTOM)}}$                                  | 3.6°C/W                                                                                      |

| Junction-to-top characterization parameter $^{(2)}$ $\psi_{\text{JT}}$                                                  | 0.8°C/W                                                                                      |