# **Micron Serial NOR Flash Memory**

# 3V, Multiple I/O, 4KB, 32KB, 64KB Sector Erase MT25QL01GBBB

| Features                                                                                     | Options                                                       | Marking |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------|

| <ul><li>Stacked device (two 512Mb die)</li><li>SPI-compatible serial bus interface</li></ul> | <ul><li>Voltage</li><li>2.7–3.6V</li><li>Density</li></ul>    | L       |

| Single and double transfer rate (STR/DTR)                                                    | – 1Gb                                                         | 01G     |

| <ul> <li>Clock frequency</li> <li>133 MHz (MAX) for all protocols in STR</li> </ul>          | <ul> <li>Device stacking</li> </ul>                           |         |

| <ul><li>90 MHz (MAX) for all protocols in DTR</li></ul>                                      | - 2 die stacked                                               | В       |

| Dual/quad I/O commands for increased through-                                                | • Device generation                                           | В       |

| put up to 90 MB/s                                                                            | Die revision     Die configuration                            | В       |

| Supported protocols in both STR and DTR                                                      | <ul><li>Pin configuration</li><li>HOLD#</li></ul>             | 1       |

| <ul> <li>Extended I/O protocol</li> </ul>                                                    | <ul><li>RESET and HOLD#</li></ul>                             | 8       |

| <ul> <li>Dual I/O protocol</li> </ul>                                                        | • Sector Size                                                 | O       |

| <ul> <li>Quad I/O protocol</li> </ul>                                                        | - 64KB                                                        | Е       |

| • Execute-in-place (XIP)                                                                     | <ul> <li>Packages – JEDEC-standard, RoHS-</li> </ul>          |         |

| PROGRAM/ERASE SUSPEND operations                                                             | compliant                                                     |         |

| Volatile and nonvolatile configuration settings                                              | <ul> <li>24-ball T-PBGA 05/6mm x 8mm</li> </ul>               | 12      |

| <ul><li>Software reset</li><li>Additional reset pin for selected part numbers</li></ul>      | (TBGA24)                                                      |         |

| 3-byte and 4-byte address modes – enable memory                                              | <ul> <li>16-pin SOP2, 300 mils (SO16W,</li> </ul>             | SF      |

| access beyond 128Mb                                                                          | SO16-Wide, SOIC-16)                                           |         |

| Dedicated 64-byte OTP area outside main memory                                               | - W-PDFN-8 8mm x 6mm (MLP8 8mm                                | W9      |

| <ul> <li>Readable and user-lockable</li> </ul>                                               | x 6mm)                                                        |         |

| <ul> <li>Permanent lock with PROGRAM OTP command</li> </ul>                                  | <ul><li>Security features</li><li>Standard security</li></ul> | 0       |

| Erase capability                                                                             | <ul><li>Standard security</li><li>Special options</li></ul>   | U       |

| – Die Erase                                                                                  | - Standard                                                    | S       |

| <ul> <li>Sector erase 64KB uniform granularity</li> </ul>                                    | <ul><li>Automotive</li></ul>                                  | Ä       |

| <ul> <li>Subsector erase 4KB, 32KB granularity</li> </ul>                                    | Operating temperature range                                   |         |

| Security and write protection                                                                | - From -40°C to +85°C                                         | IT      |

| <ul> <li>Volatile and nonvolatile locking and software</li> </ul>                            | - From $-40^{\circ}$ C to $+105^{\circ}$ C                    | AT      |

| write protection for each 64KB sector                                                        | - From $-40$ °C to $+125$ °C                                  | UT      |

| Nonvolatile configuration locking  Persylverd protection                                     |                                                               |         |

| <ul> <li>Password protection</li> </ul>                                                      |                                                               |         |

· Electronic signature

Minimum 100,000 ERASE cycles per sector

JEDEC-standard 3-byte signature (BA21h)

- Extended device ID: two additional bytes identify

Hardware write protection: nonvolatile bits (BP[3:0] and TB) define protected area size

Program/erase protection during power-up

CRC detects accidental changes to raw data

- Data retention: 20 years (TYP)

device factory options

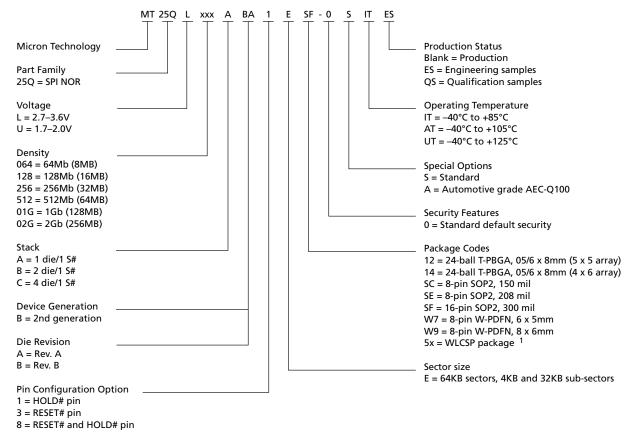

#### **Part Number Ordering**

Micron Serial NOR Flash devices are available in different configurations and densities. Verify valid part numbers by using Micron's part catalog search at www.micron.com. To compare features and specifications by device type, visit www.micron.com/products. Contact the factory for devices not found.

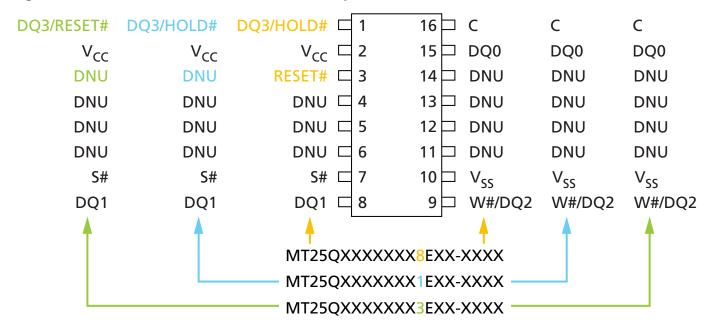

**Figure 1: Part Number Ordering Information**

Note: 1. WLCSP package codes, package size, and availability are density-specific. Contact the factory for availability.

# 1Gb, 3V Multiple I/O Serial Flash Memory Features

#### **Contents**

| Important Notes and Warnings                       |      |

|----------------------------------------------------|------|

| Device Description                                 | 9    |

| Device Logic Diagram                               |      |

| Advanced Security Protection                       |      |

| Signal Assignments – Package Code: 12              |      |

| Signal Assignments – Package Code: SF              |      |

| Signal Assignments – Package Code: W9              |      |

| Signal Descriptions                                |      |

| Package Dimensions – Package Code: 12              | . 16 |

| Package Dimensions – Package Code: SF              |      |

| Package Dimensions – Package Code: W9              |      |

| Memory Map – 1Gb Density                           | . 19 |

| Status Register                                    |      |

| Block Protection Settings                          |      |

| Flag Status Register                               |      |

| Extended Address Register                          |      |

| Internal Configuration Register                    | . 24 |

| Nonvolatile Configuration Register                 |      |

| Volatile Configuration Register                    |      |

| Supported Clock Frequencies                        |      |

| Enhanced Volatile Configuration Register           |      |

| Security Registers                                 |      |

| Sector Protection Security Register                |      |

| Nonvolatile and Volatile Sector Lock Bits Security |      |

| Volatile Lock Bit Security Register                |      |

| Device ID Data                                     |      |

| Serial Flash Discovery Parameter Data              |      |

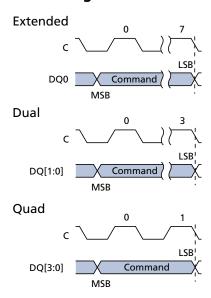

| Command Definitions                                |      |

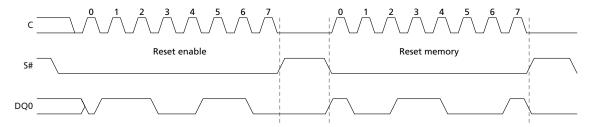

| Software RESET Operations                          |      |

| RESET ENABLE and RESET MEMORY Commands             |      |

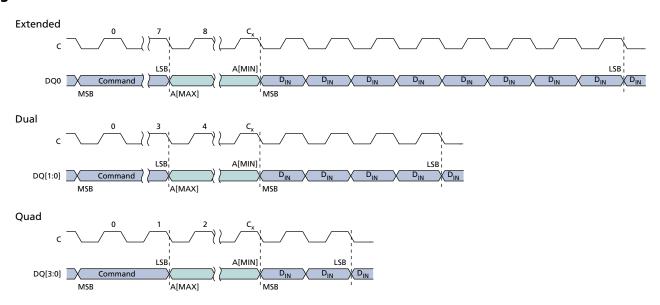

| READ ID Operations                                 |      |

| READ ID and MULTIPLE I/O READ ID Commands          |      |

| READ SERIAL FLASH DISCOVERY PARAMETER Operation    |      |

| READ SERIAL FLASH DISCOVERY PARAMETER Command      |      |

| READ MEMORY Operations                             |      |

| 4-BYTE READ MEMORY Operations                      |      |

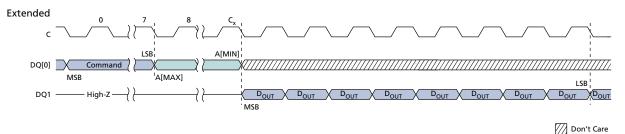

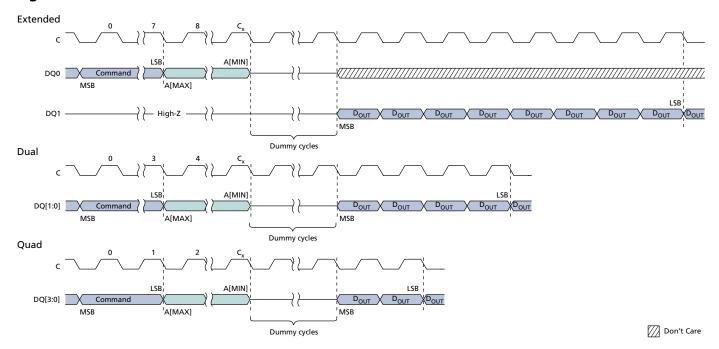

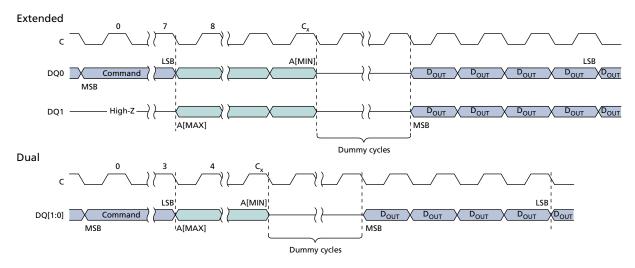

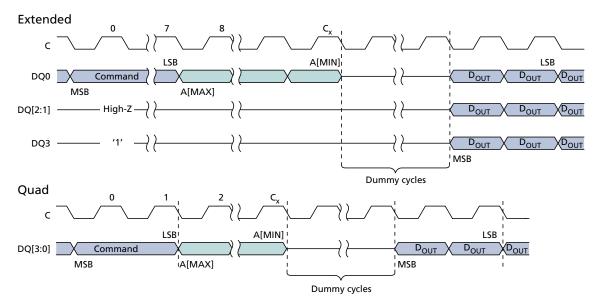

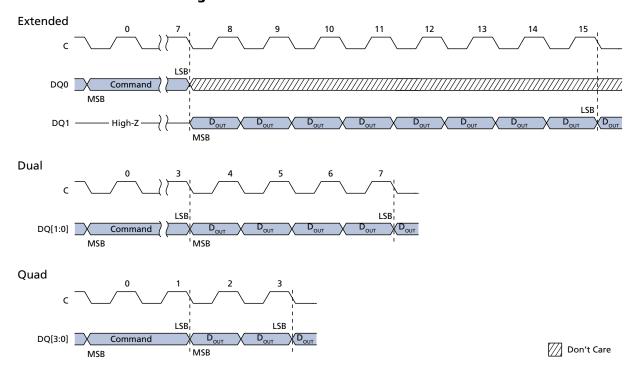

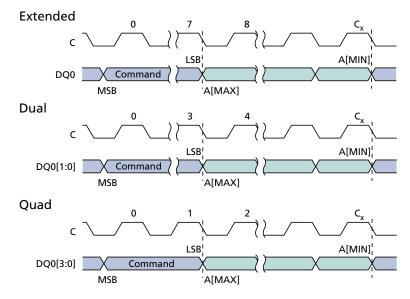

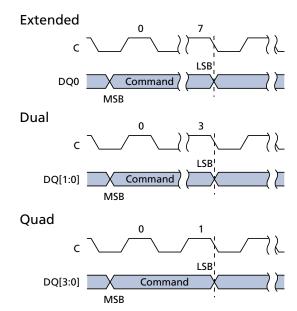

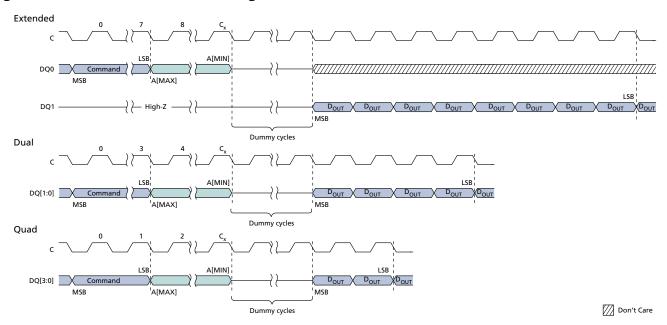

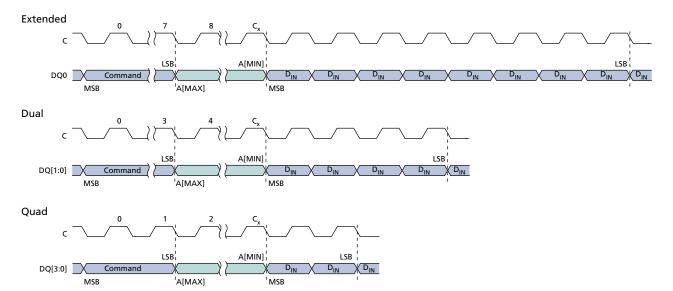

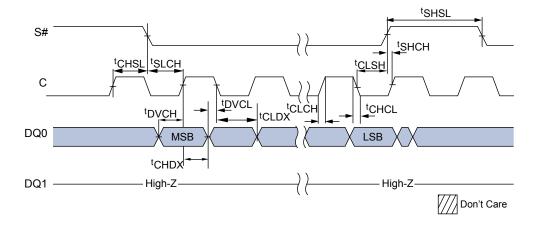

| READ MEMORY Operations Timings                     | 47   |

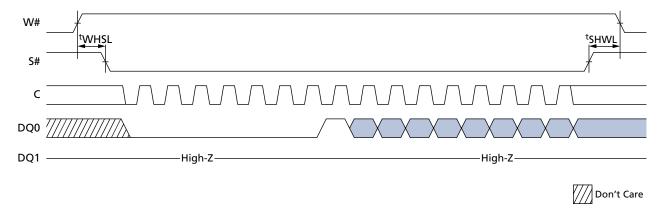

| WRITE ENABLE/DISABLE Operations                    | . 54 |

| READ REGISTER Operations                           |      |

| WRITE REGISTER Operations                          |      |

| CLEAR FLAG STATUS REGISTER Operation               |      |

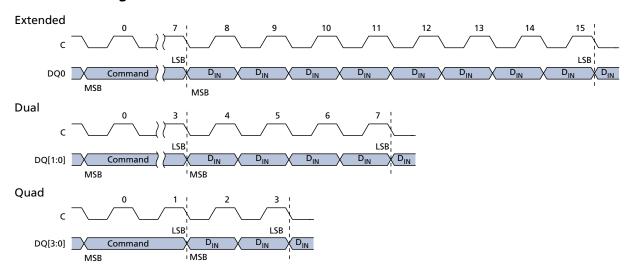

| PROGRAM Operations                                 |      |

| 4-BYTE PROGRAM Operations                          |      |

| PROGRAM Operations Timings                         |      |

| ERASE Operations                                   |      |

| SUSPEND/RESUME Operations                          |      |

| PROGRAM/ERASE SUSPEND Operations                   |      |

| PROGRAM/ERASE RESUME Operations                    |      |

| ONE-TIME PROGRAMMABLE Operations                   |      |

| READ OTP ARRAY Command                             | . 68 |

#### 1Gb, 3V Multiple I/O Serial Flash Memory Features

| PROGRAM OTP ARRAY Command                                           |    |

|---------------------------------------------------------------------|----|

| ADDRESS MODE Operations                                             |    |

| ENTER and EXIT 4-BYTE ADDRESS MODE Command                          | 70 |

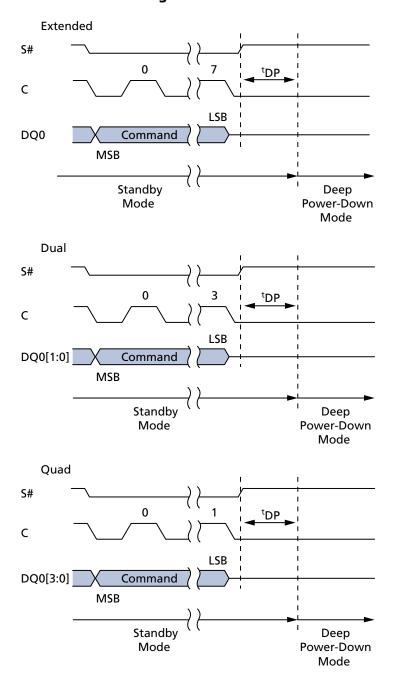

| DEEP POWER-DOWN Operations                                          |    |

| ENTER DEEP POWER-DOWN Command                                       |    |

| RELEASE FROM DEEP POWER-DOWN Command                                | 71 |

| DEEP POWER-DOWN Timings                                             | 72 |

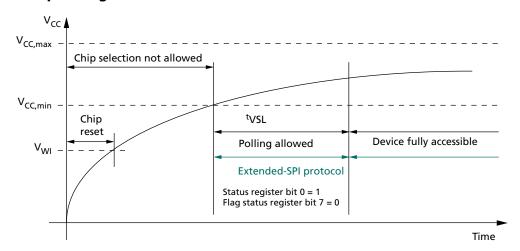

| QUAD PROTOCOL Operations                                            |    |

| ENTER or RESET QUAD INPUT/OUTPUT MODE Command                       | 74 |

| CYCLIC REDUNDANCY CHECK Operations                                  | 75 |

| Cyclic Redundancy Check                                             | 75 |

| State Table                                                         | 77 |

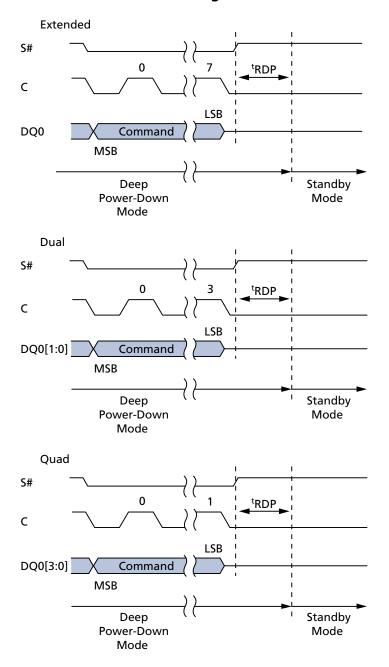

| XIP Mode                                                            |    |

| Activate and Terminate XIP Using Volatile Configuration Register    | 78 |

| Activate and Terminate XIP Using Nonvolatile Configuration Register |    |

| Confirmation Bit Settings Required to Activate or Terminate XIP     |    |

| Terminating XIP After a Controller and Memory Reset                 | 79 |

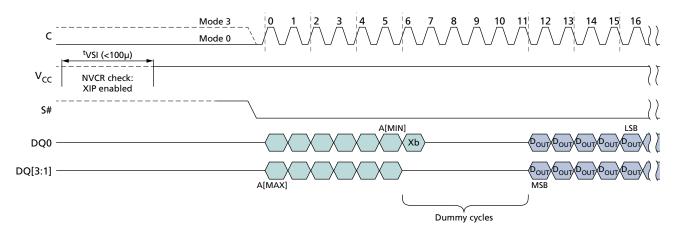

| Power-Up and Power-Down                                             |    |

| Power-Up and Power-Down Requirements                                |    |

| Active, Standby, and Deep Power-Down Modes                          |    |

| Power Loss and Interface Rescue                                     | 83 |

| Recovery                                                            | 83 |

| Power Loss Recovery                                                 | 83 |

| Interface Rescue                                                    | 83 |

| Absolute Ratings and Operating Conditions                           | 84 |

| DC Characteristics and Operating Conditions                         | 86 |

| AC Characteristics and Operating Conditions                         | 88 |

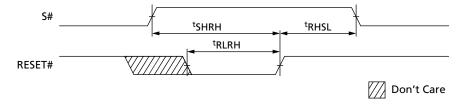

| AC Reset Specifications                                             |    |

| Program/Erase Specifications                                        | 94 |

| Revision History                                                    | 95 |

| Rev. E - 12/17                                                      | 95 |

| Rev. D - 06/16                                                      | 95 |

| Rev. C - 04/16                                                      | 95 |

| Rev. B - 9/15                                                       | 95 |

| Rev. A – 08/15                                                      | 95 |

# 1Gb, 3V Multiple I/O Serial Flash Memory Features

# **List of Figures**

|            | Part Number Ordering Information                                               |    |

|------------|--------------------------------------------------------------------------------|----|

| Figure 2:  | Block Diagram                                                                  | 9  |

| Figure 3:  | Logic Diagram                                                                  | 10 |

|            | 24-Ball T-BGA, 5 × 5 (Balls Down)                                              |    |

| Figure 5:  | 16-Pin, Plastic Small Outline – SO16 (Top View)                                | 12 |

| Figure 6:  | 8-Pin, W-PDFN (Top View)                                                       | 13 |

| Figure 7:  | 24-Ball T-PBGA (5 × 5 ball grid array) – 6mm × 8mm                             | 16 |

|            | 16-Pin SOP2 – 300 mil Body Width                                               |    |

| Figure 9:  | W-PDFN-8 (MLP8) – 8mm × 6mm                                                    | 18 |

| Figure 10: | Internal Configuration Register                                                | 24 |

| Figure 11: | Sector and Password Protection                                                 | 31 |

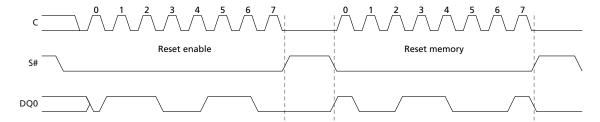

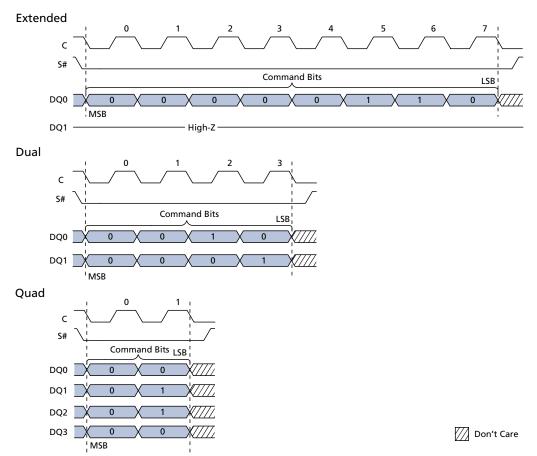

| Figure 12: | RESET ENABLE and RESET MEMORY Command                                          | 42 |

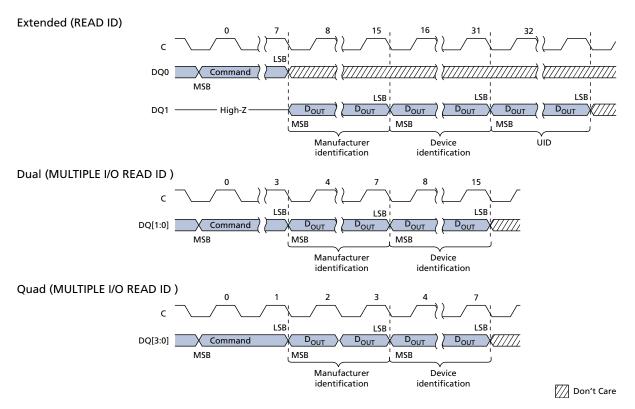

| Figure 13: | READ ID and MULTIPLE I/O READ ID Commands                                      | 43 |

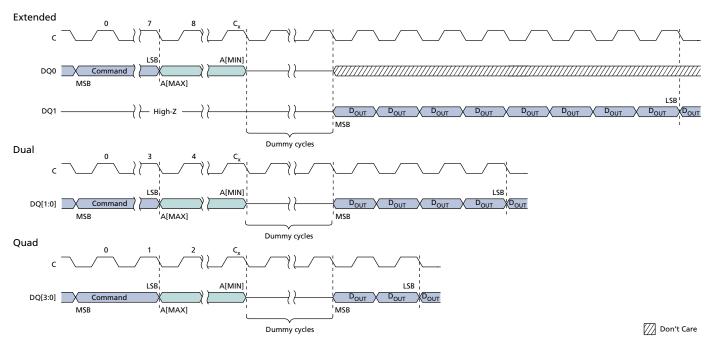

| Figure 14: | READ SERIAL FLASH DISCOVERY PARAMETER Command – 5Ah                            | 44 |

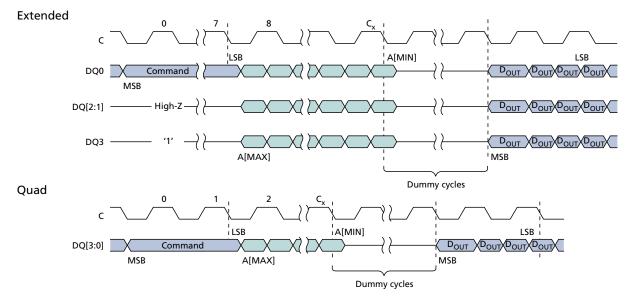

| Figure 15: | READ – 03h/13h <sup>3</sup>                                                    | 47 |

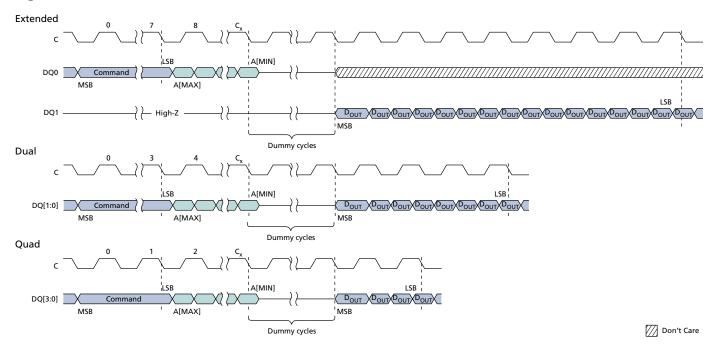

| Figure 16: | FAST READ – 0Bh/0Ch <sup>3</sup>                                               | 47 |

| Figure 17: | DUAL OUTPUT FAST READ – 3Bh/3Ch <sup>3</sup>                                   | 48 |

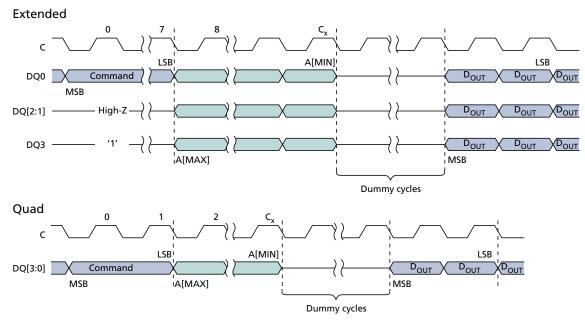

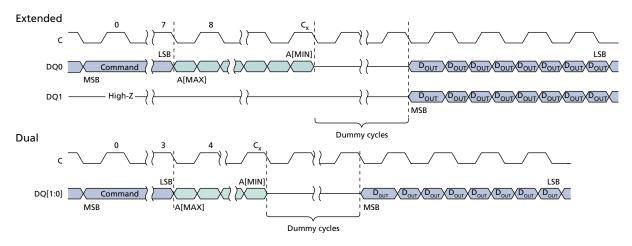

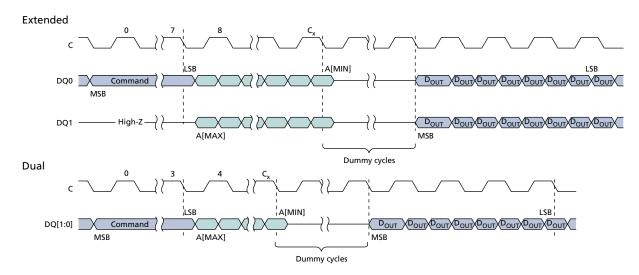

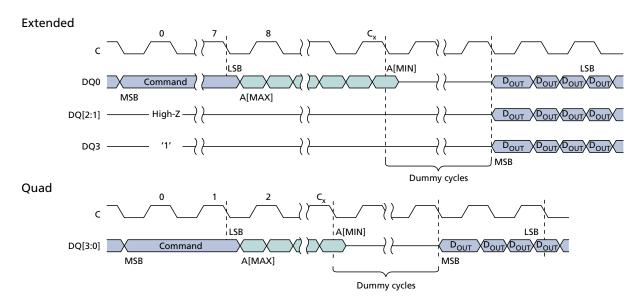

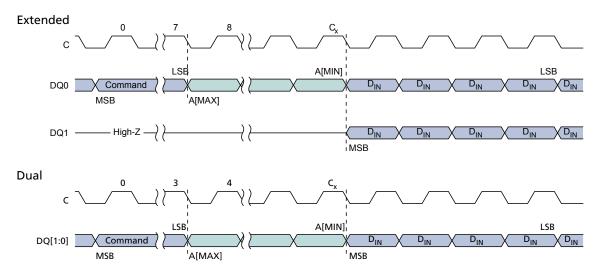

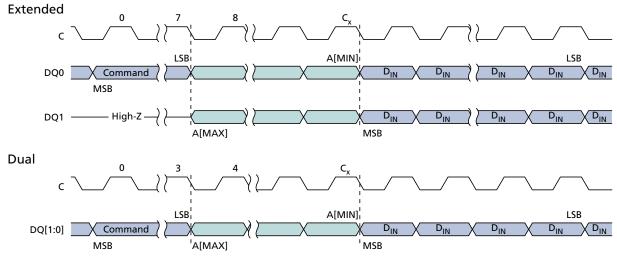

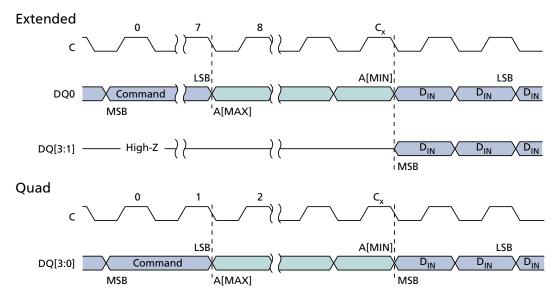

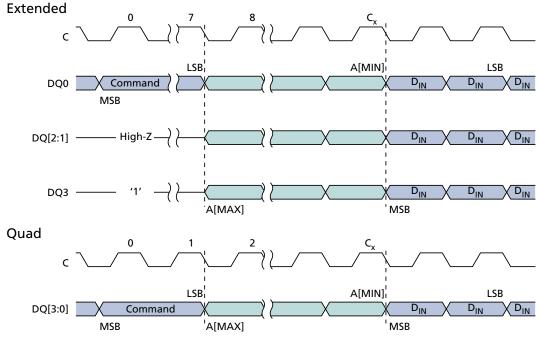

| Figure 18: | DUAL INPUT/OUTPUT FAST READ – BBh/BCh <sup>3</sup>                             | 48 |

| Figure 19: | QUAD OUTPUT FAST READ – 6Bh/6Ch <sup>3</sup>                                   | 49 |

| Figure 20: | QUAD INPUT/OUTPUT FAST READ – EBh/ECh <sup>3</sup>                             | 49 |

| Figure 21: | QUAD INPUT/OUTPUT WORD READ – E7h <sup>3</sup>                                 | 50 |

| Figure 22: | DTR FAST READ – 0Dh/0Eh <sup>3</sup>                                           | 51 |

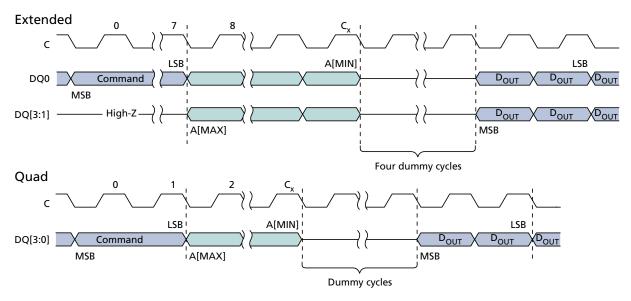

| Figure 23: | DTR DUAL OUTPUT FAST READ – 3Dh <sup>3</sup>                                   | 51 |

| Figure 24: | DTR DUAL INPUT/OUTPUT FAST READ – BDh <sup>3</sup>                             | 52 |

| Figure 25: | DTR QUAD OUTPUT FAST READ – 6Dh <sup>3</sup>                                   | 53 |

| Figure 26: | DTR QUAD INPUT/OUTPUT FAST READ – EDh <sup>3</sup>                             | 53 |

| Figure 27: | WRITE ENABLE and WRITE DISABLE Timing                                          | 54 |

|            | READ REGISTER Timing                                                           |    |

|            | WRITE REGISTER Timing                                                          |    |

|            | CLEAR FLAG STATUS REGISTER Timing                                              |    |

|            | PAGE PROGRAM Command                                                           |    |

| Figure 32: | DUAL INPUT FAST PROGRAM Command                                                | 62 |

| Figure 33: | EXTENDED DUAL INPUT FAST PROGRAM Command                                       | 62 |

| Figure 34: | QUAD INPUT FAST PROGRAM Command                                                | 63 |

| Figure 35: | EXTENDED QUAD INPUT FAST PROGRAM Command                                       | 63 |

| Figure 36: | SUBSECTOR, SECTOR ERASE and DIE ERASE Timing                                   | 65 |

|            | PROGRAM/ERASE SUSPEND and RESUME Timing                                        |    |

|            | READ OTP Command Timing                                                        |    |

| -          | PROGRAM OTP Command Timing                                                     |    |

|            | ENTER DEEP POWER-DOWN Timing                                                   |    |

|            | RELEASE FROM DEEP POWER-DOWN Timing                                            |    |

|            | XIP Mode Directly After Power-On                                               |    |

|            | Power-Up Timing                                                                |    |

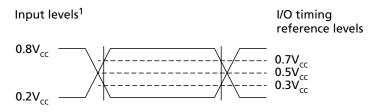

| Figure 44: | AC Timing Input/Output Reference Levels                                        | 85 |

|            | Reset AC Timing During PROGRAM and ERASE Cycle                                 |    |

|            | Reset Enable and Reset Memory Timing                                           |    |

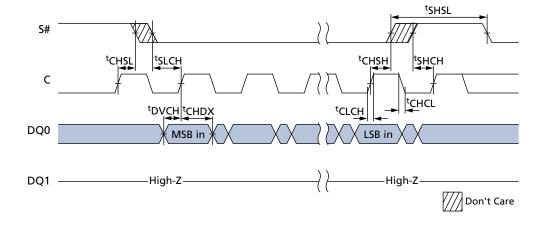

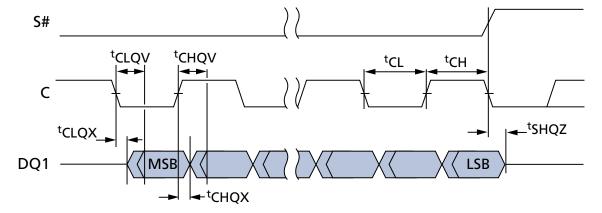

|            | Serial Input Timing STR                                                        |    |

|            | Serial Input Timing DTR                                                        |    |

|            | Write Protect Setup and Hold During WRITE STATUS REGISTER Operation (SRWD = 1) |    |

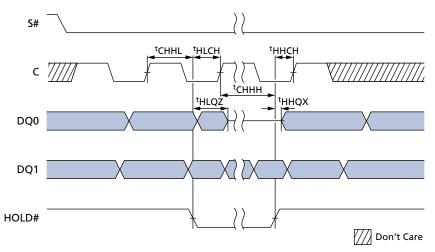

|            | Hold Timing                                                                    |    |

#### 1Gb, 3V Multiple I/O Serial Flash Memory Features

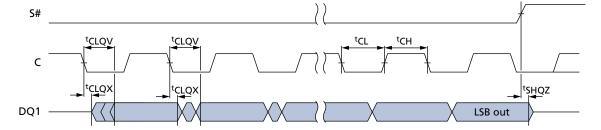

| Figure 51: | Output Timing for STR | 93 |

|------------|-----------------------|----|

| Figure 52: | Output Timing for DTR | 93 |

# 1Gb, 3V Multiple I/O Serial Flash Memory Features

# **List of Tables**

| Table 1: S | Signal Descriptions                                 | 14 |

|------------|-----------------------------------------------------|----|

| Table 2: 1 | Memory Map                                          | 19 |

| Table 3: 5 | Status Register                                     | 20 |

|            | Protected Area                                      |    |

|            | Flag Status Register                                |    |

| Table 6: 1 | Extended Address Register                           | 23 |

| Table 7: I | Nonvolatile Configuration Register                  | 25 |

| Table 8: V | Volatile Configuration Register                     | 27 |

|            | Sequence of Bytes During Wrap                       |    |

| Table 10:  | Clock Frequencies – STR (in MHz)                    | 28 |

|            | Clock Frequencies – DTR (in MHz)                    |    |

| Table 12:  | Enhanced Volatile Configuration Register            | 30 |

| Table 13:  | Sector Protection Register                          | 32 |

| Table 14:  | Global Freeze Bit                                   | 32 |

| Table 15:  | Nonvolatile and Volatile Lock Bits                  | 33 |

| Table 16:  | Volatile Lock Bit Register                          | 33 |

| Table 17:  | Device ID Data                                      | 34 |

| Table 18:  | Extended Device ID Data, First Byte                 | 34 |

|            | Command Set                                         |    |

| Table 20:  | RESET ENABLE and RESET MEMORY Operations            | 42 |

| Table 21:  | READ ID and MULTIPLE I/O READ ID Operations         | 43 |

| Table 22:  | READ MEMORY Operations                              | 45 |

| Table 23:  | 4-BYTE READ MEMORY Operations                       | 46 |

| Table 24:  | WRITE ENABLE/DISABLE Operations                     | 54 |

| Table 25:  | READ REGISTER Operations                            | 55 |

| Table 26:  | WRITE REGISTER Operations                           | 57 |

| Table 27:  | CLEAR FLAG STATUS REGISTER Operation                | 59 |

|            | PROGRAM Operations                                  |    |

| Table 29:  | 4-BYTE PROGRAM Operations                           | 61 |

|            | ERASE Operations                                    |    |

| Table 31:  | SUSPEND/RESUME Operations                           | 66 |

|            | OTP Control Byte (Byte 64)                          |    |

| Table 33:  | ENTER and EXIT 4-BYTE ADDRESS MODE Operations       | 70 |

|            | DEEP POWER-DOWN Operations                          |    |

|            | ENTER and RESET QUAD PROTOCOL Operations            |    |

|            | CRC Command Sequence on a Range                     |    |

| Table 37:  | Operations Allowed/Disallowed During Device States  | 77 |

|            | XIP Confirmation Bit                                |    |

|            | Effects of Running XIP in Different Protocols       |    |

|            | Power-Up Timing and V <sub>WI</sub> Threshold       |    |

|            | Absolute Ratings                                    |    |

|            | Operating Conditions                                |    |

|            | Input/Output Capacitance                            |    |

|            | AC Timing Input/Output Conditions                   |    |

|            | DC Current Characteristics and Operating Conditions |    |

|            | DC Voltage Characteristics and Operating Conditions |    |

|            | AC Characteristics and Operating Conditions         |    |

|            | AC RESET Conditions                                 |    |

| Table 49:  | Program/Erase Specifications                        | 94 |

### **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

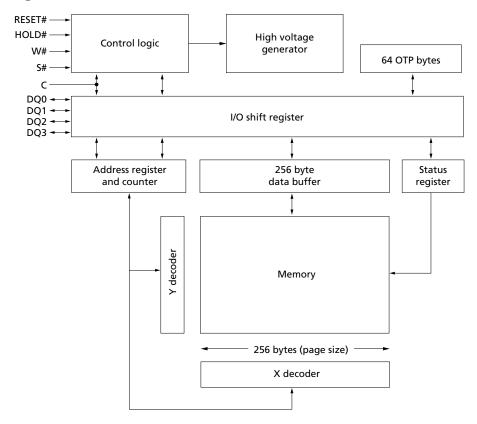

# **Device Description**

The MT25Q is a high-performance multiple input/output serial Flash memory device. It features a high-speed SPI-compatible bus interface, execute-in-place (XIP) functionality, advanced write protection mechanisms, and extended address access. Innovative, high-performance, dual and quad input/output commands enable double or quadruple the transfer bandwidth for READ and PROGRAM operations.

Figure 2: Block Diagram

Note: 1. Each page of memory can be individually programmed, but the device is not page-erasable.

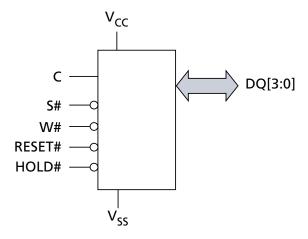

#### **Device Logic Diagram**

#### **Figure 3: Logic Diagram**

Notes:

- 1. Depending on the selected device (see Part Numbering Ordering Information), DQ3 = DQ3/RESET# or DQ3/HOLD#.

- 2. A separate RESET pin is available on dedicated part numbers (see Part Numbering Ordering Information).

#### **Advanced Security Protection**

The device offers an advanced security protection scheme where each sector can be independently locked, by either volatile or nonvolatile locking features. The nonvolatile locking configuration can also be locked, as well password-protected. See Block Protection Settings and Sector and Password Protection for more details.

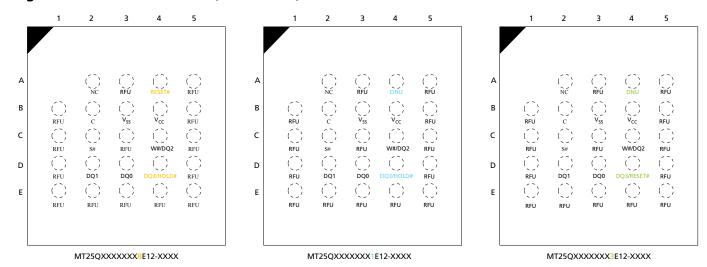

### Signal Assignments - Package Code: 12

Figure 4: 24-Ball T-BGA, 5 × 5 (Balls Down)

Notes:

- 1. RESET# or HOLD# signals can share Ball D4 with DQ3, depending on the selected device (see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven high by the host, or an external pull-up resistor must be placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.

- 2. Ball A4 = RESET# or DNU, depending on the part number. This signal has an internal pull-up resistor and may be left unconnected if not used.

#### **Signal Assignments - Package Code: SF**

Figure 5: 16-Pin, Plastic Small Outline - SO16 (Top View)

Notes:

- 1. RESET# or HOLD# signals can share Pin 1 with DQ3, depending on the selected device (see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven high by the host, or an external pull-up resistor must be placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.

- 2. Pin 3 = RESET# or DNU, depending on the part number. This signal has an internal pull-up resistor and may be left unconnected if not used.

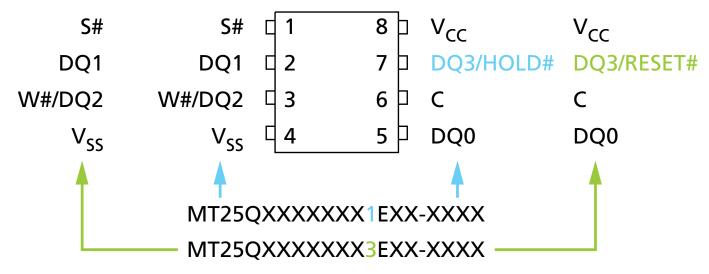

### Signal Assignments – Package Code: W9

Figure 6: 8-Pin, W-PDFN (Top View)

- Notes: 1. RESET# or HOLD# signals can share Pin 7 with DQ3, depending on the selected device (see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven high by the host, or an external pull-up resistor must be placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.

- 2. On the underside of the W-PDFN package, there is an exposed central pad that is pulled internally to V<sub>SS</sub>. It can be left floating or can be connected to V<sub>SS</sub>. It must not be connected to any other voltage or signal line on the PCB.

- 3. MT25QXXXXXX8EXX-XXXX not available on 8 pin package

# **Signal Descriptions**

The signal description table below is a comprehensive list of signals for the MT25Q family devices. All signals listed may not be supported on this device. See Signal Assignments for information specific to this device.

**Table 1: Signal Descriptions**

| Symbol          | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S#              | Input  | <b>Chip select:</b> When S# is driven HIGH, the device will enter standby mode, unless an internal PROGRAM, ERASE, or WRITE STATUS REGISTER cycle is in progress. All other input pins are ignored and the output pins are tri-stated. On parts with the pin configuration offering a dedicated RESET# pin, however, the RESET# input pin remains active even when S# is HIGH.                                                                                                                                                                                                                                                     |

|                 |        | Driving S# LOW enables the device, placing it in the active mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |        | After power-up, a falling edge on S# is required prior to the start of any command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| С               | Input  | <b>Clock:</b> Provides the timing of the serial interface. Command inputs are latched on the rising edge of the clock. In STR commands or protocol, address and data inputs are latched on the rising edge of the clock, while data is output on the falling edge of the clock. In DTR commands or protocol, address and data inputs are latched on both edges of the clock, and data is output on both edges of the clock.                                                                                                                                                                                                        |

| RESET#          | Input  | <b>RESET#:</b> When RESET# is driven LOW, the device is reset and the outputs are tri-stated. If RE-SET# is driven LOW while an internal WRITE, PROGRAM, or ERASE operation is in progress, data may be lost. The RESET# functionality can be disabled using bit 4 of the nonvolatile configuration register or bit 4 of the enhanced volatile configuration register.                                                                                                                                                                                                                                                             |

|                 |        | For pin configurations that share the DQ3 pin with RESET#, the RESET# functionality is disabled in QIO-SPI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HOLD#           | Input  | <b>HOLD:</b> Pauses serial communications with the device without deselecting or resetting the device. Outputs are tri-stated and inputs are ignored. The HOLD# functionality can be disabled using bit 4 of the nonvolatile configuration register or bit 4 of the enhanced volatile configuration register.                                                                                                                                                                                                                                                                                                                      |

|                 |        | For pin configurations that share the DQ3 pin with HOLD#, the HOLD# functionality is disabled in QIO-SPI mode or when DTR operation is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| W#              | Input  | <b>Write protect:</b> Freezes the status register in conjunction with the enable/disable bit of the status register. When the enable/disable bit of the status register is set to 1 and the W# signal is driven LOW, the status register nonvolatile bits become read-only and the WRITE STATUS REGISTER operation will not execute. During the extended-SPI protocol with QOFR and QIOFR instructions, and with QIO-SPI protocol, this pin function is an input/output as DQ2 functionality. This signal does not have internal pull-ups, it cannot be left floating and must be driven, even if none of W#/DQ2 function is used. |

| DQ[3:0]         | I/O    | Serial I/O: The bidirectional DQ signals transfer address, data, and command information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |        | When using legacy (x1) SPI commands in extended I/O protocol (XIO-SPI), DQ0 is an input and DQ1 is an output. DQ[3:2] are not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |        | When using dual commands in XIO-SPI or when using DIO-SPI, DQ[1:0] are I/O. DQ[3:2] are not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |        | When using quad commands in XIO-SPI or when using QIO-SPI, DQ[3:0] are I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>CC</sub> | Supply | Core and I/O power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# 1Gb, 3V Multiple I/O Serial Flash Memory Signal Descriptions

#### **Table 1: Signal Descriptions (Continued)**

| Symbol   | Туре   | Description                                                                                                                                                                                                                 |  |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{SS}$ | Supply | ore and I/O ground connection.                                                                                                                                                                                              |  |

| DNU      | -      | <b>Do not use:</b> Do not connect to any other signal, or power supply; must be left floating.                                                                                                                              |  |

| RFU      | _      | <b>Reserved for future use:</b> Reserved by Micron for future device functionality and enhancement. Recommend that these be left floating. May be connected internally, but external connections will not affect operation. |  |

| NC       | _      | No connect : No internal connection; can be driven or floated.                                                                                                                                                              |  |

### Package Dimensions - Package Code: 12

Figure 7: 24-Ball T-PBGA (5 × 5 ball grid array) - 6mm × 8mm

Notes: 1. All dimensions are in millimeters.

2. See Part Number Ordering Information for complete package names and details.

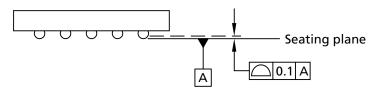

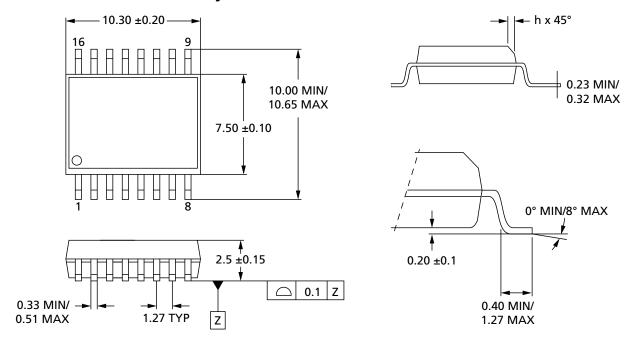

# Package Dimensions - Package Code: SF

Figure 8: 16-Pin SOP2 - 300 mil Body Width

Notes: 1. All dimensions are in millimeters.

2. See Part Number Ordering Information for complete package names and details.

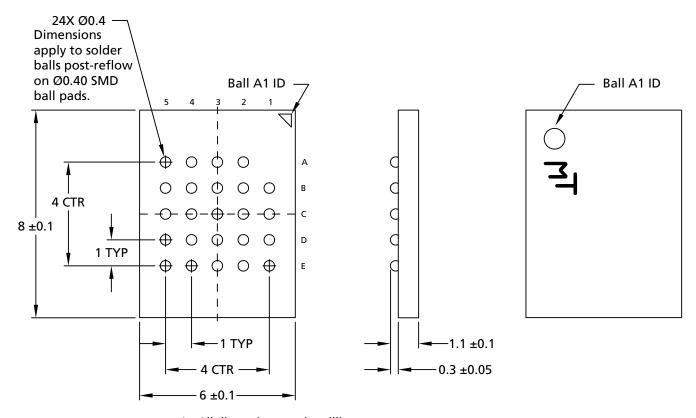

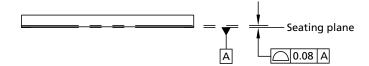

# Package Dimensions - Package Code: W9

Figure 9: W-PDFN-8 (MLP8) - 8mm × 6mm

Notes: 1. All dimensions are in millimeters.

2. See Part Number Ordering Information for complete package names and details.

# **Memory Map - 1Gb Density**

**Table 2: Memory Map**

|        |                  |                 | Address Range |            |

|--------|------------------|-----------------|---------------|------------|

| Sector | Subsector (32KB) | Subsector (4KB) | Start         | End        |

| 2047   | 4095             | 32767           | 07FF F000h    | 07FF FFFFh |

|        |                  | :               | <u>:</u>      | :          |

|        |                  | 32760           | 07FF 8000h    | 07FF 8FFFh |

|        | 4094             | 32759           | 07FF 7000h    | 07FF 7FFFh |

|        |                  | i i             | <u>:</u>      | i i        |

|        |                  | 32752           | 07FF 0000h    | 07FF 0FFFh |

| :      | :                | i i             | <u>:</u>      | i i        |

| 1023   | 2047             | 16383           | 03FF F000h    | 03FF FFFFh |

|        |                  | i               | <u>:</u>      | :          |

|        |                  | 16376           | 03FF 8000h    | 03FF 8FFFh |

|        | 2046             | 16375           | 03FF 7000h    | 03FF 7FFFh |

|        |                  | :               | <u>:</u>      | :          |

|        |                  | 16368           | 03FF 0000h    | 03FF 0FFFh |

| E      | :                | :               | <u>:</u>      | :          |

| 511    | 1023             | 8191            | 01FF F000h    | 01FF FFFFh |

|        |                  | :               | i i           | :          |

|        |                  | 8184            | 01FF 8000h    | 01FF 8FFFh |

|        | 1022             | 8183            | 01FF 7000h    | 01FF 7FFFh |

|        |                  | i i             | i i           | :          |

|        |                  | 8176            | 01FF 0000h    | 01FF 0FFFh |

| i i    | :                | i i             | i i           | :          |

| 0      | 1                | 15              | 0000 F000h    | 0000 FFFFh |

|        |                  | :               | i i           | :          |

|        |                  | 8               | 0000 8000h    | 0000 8FFFh |

|        | 0                | 7               | 0000 7000h    | 0000 7FFFh |

|        |                  | i i             | i             | :          |

|        |                  | 0               | 0000 0000h    | 0000 0FFFh |

Note: 1. See Part Number Ordering Information, Sector Size – Part Numbers table for options.

#### **Status Register**

Status register bits can be read from or written to using READ STATUS REGISTER or WRITE STATUS REGISTER commands, respectively. When the status register enable/ disable bit (bit 7) is set to 1 and W# is driven LOW, the status register nonvolatile bits become read-only and the WRITE STATUS REGISTER operation will not execute. The only way to exit this hardware-protected mode is to drive W# HIGH.

**Table 3: Status Register**

| Bit    | Name                                         | Settings                              | Description                                                                                                                                                                                                                         | Notes |

|--------|----------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7      | Status register<br>write enable/disa-<br>ble | 0 = Enabled (Default)<br>1 = Disabled | <b>Nonvolatile control bit:</b> Used with W# to enable or disable writing to the status register.                                                                                                                                   |       |

| 5      | Top/bottom                                   | 0 = Top (Default)<br>1 = Bottom       | <b>Nonvolatile control bit:</b> Determines whether the protected memory area defined by the block protect bits starts from the top or bottom of the memory array.                                                                   |       |

| 6, 4:2 | BP[3:0]                                      | See Protected Area tables             | Nonvolatile control bit: Defines memory to be software protected against PROGRAM or ERASE operations. When one or more block protect bits is set to 1, a designated memory area is protected from PROGRAM and ERASE operations.     | 1     |

| 1      | Write enable latch                           | 0 = Clear (Default)<br>1 = Set        | Volatile control bit: The device always powers up with this bit cleared to prevent inadvertent WRITE, PRO-GRAM, or ERASE operations. To enable these operations, the WRITE ENABLE operation must be executed first to set this bit. |       |

| 0      | Write in progress                            | 0 = Ready<br>1 = Busy                 | Status bit: Indicates if one of the following command cycles is in progress: WRITE STATUS REGISTER WRITE NONVOLATILE CONFIGURATION REGISTER PROGRAM ERASE                                                                           | 2     |

- Notes: 1. The DIE ERASE command is executed only if all bits = 0.

- 2. Status register bit 0 is the inverse of flag status register bit 7.

#### **Block Protection Settings**

**Table 4: Protected Area**

| Status Register Content |     |     |     |     |                          |                               |

|-------------------------|-----|-----|-----|-----|--------------------------|-------------------------------|

| Top/<br>Bottom          | BP3 | BP2 | BP1 | BP0 | Protected Area (Sectors) | Unprotected Area<br>(Sectors) |

| 0                       | 0   | 0   | 0   | 0   | None                     | All                           |

| 0                       | 0   | 0   | 0   | 1   | 2047                     | 2046:0                        |

| 0                       | 0   | 0   | 1   | 0   | 2047:2046                | 2045:0                        |

| 0                       | 0   | 0   | 1   | 1   | 2047:2044                | 2043:0                        |

| 0                       | 0   | 1   | 0   | 0   | 2047:2040                | 2039:0                        |

| 0                       | 0   | 1   | 0   | 1   | 2047:2032                | 2031:0                        |

| 0                       | 0   | 1   | 1   | 0   | 2047:2016                | 2015:0                        |

| 0                       | 0   | 1   | 1   | 1   | 2047:1984                | 1983:0                        |

| 0                       | 1   | 0   | 0   | 0   | 2047:1920                | 1919:0                        |

| 0                       | 1   | 0   | 0   | 1   | 2047:1792                | 1791:0                        |

| 0                       | 1   | 0   | 1   | 0   | 2047:1536                | 1535:0                        |

| 0                       | 1   | 0   | 1   | 1   | 2047:1024                | 1023:0                        |

| 0                       | 1   | 1   | 0   | 0   | All                      | None                          |

| 0                       | 1   | 1   | 0   | 1   | All                      | None                          |

| 0                       | 1   | 1   | 1   | 0   | All                      | None                          |

| 0                       | 1   | 1   | 1   | 1   | All                      | None                          |

| 1                       | 0   | 0   | 0   | 0   | None                     | All                           |

| 1                       | 0   | 0   | 0   | 1   | Sector 0                 | 2047:1                        |

| 1                       | 0   | 0   | 1   | 0   | 1:0                      | 2047:2                        |

| 1                       | 0   | 0   | 1   | 1   | 3:0                      | 2047:4                        |

| 1                       | 0   | 1   | 0   | 0   | 7:0                      | 2047:8                        |

| 1                       | 0   | 1   | 0   | 1   | 15:0                     | 2047:16                       |

| 1                       | 0   | 1   | 1   | 0   | 31:0                     | 2047:32                       |

| 1                       | 0   | 1   | 1   | 1   | 63:0                     | 2047:64                       |

| 1                       | 1   | 0   | 0   | 0   | 127:0                    | 2047:128                      |

| 1                       | 1   | 0   | 0   | 1   | 255:0                    | 2047:256                      |

| 1                       | 1   | 0   | 1   | 0   | 511:0                    | 2047:512                      |

| 1                       | 1   | 0   | 1   | 1   | 1023:0                   | 2047:1024                     |

| 1                       | 1   | 1   | 0   | 0   | All                      | None                          |

| 1                       | 1   | 1   | 0   | 1   | All                      | None                          |

| 1                       | 1   | 1   | 1   | 0   | All                      | None                          |

| 1                       | 1   | 1   | 1   | 1   | All                      | None                          |

# Flag Status Register

Flag status register bits are read by using READ FLAG STATUS REGISTER command. All bits are volatile and are reset to zero on power-up.

Status bits are set and reset automatically by the internal controller. Error bits must be cleared through the CLEAR STATUS REGISTER command.

**Table 5: Flag Status Register**

| Bit | Name                        | Settings                                       | Description                                                                                                                                                                                        |

|-----|-----------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Program or erase controller | 0 = Busy<br>1 = Ready                          | Status bit: Indicates whether one of the following command cycles is in progress: WRITE STATUS REGISTER, WRITE NONVOLATILE CONFIGURATION REGISTER, PROGRAM, or ERASE.                              |

| 6   | Erase suspend               | 0 = Clear<br>1 = Suspend                       | <b>Status bit:</b> Indicates whether an ERASE operation has been or is going to be suspended.                                                                                                      |

| 5   | Erase                       | 0 = Clear<br>1 = Failure or protection error   | <b>Error bit:</b> Indicates whether an ERASE operation has succeeded or failed.                                                                                                                    |

| 4   | Program                     | 0 = Clear<br>1 = Failure or protection error   | <b>Error bit:</b> Indicates whether a PROGRAM operation has succeeded or failed. It indicates, also, whether a CRC check has succeeded or failed.                                                  |

| 3   | Reserved                    | 0                                              | Reserved                                                                                                                                                                                           |

| 2   | Program sus-<br>pend        | 0 = Clear<br>1 = Suspend                       | <b>Status bit:</b> Indicates whether a PROGRAM operation has been or is going to be suspended.                                                                                                     |

| 1   | Protection                  | 0 = Clear<br>1 = Failure or protection error   | <b>Error bit:</b> Indicates whether an ERASE or PROGRAM operation has attempted to modify the protected array sector, or whether a PROGRAM operation has attempted to access the locked OTP space. |

| 0   | Addressing                  | 0 = 3-byte addressing<br>1 = 4-byte addressing | <b>Status bit:</b> Indicates whether 3-byte or 4-byte address mode is enabled.                                                                                                                     |

# **Extended Address Register**

The 3-byte address mode can only access 128Mb of memory. To access the full device in 3-byte address mode, the device includes an extended address register that indirectly provides a fourth address byte A[31:24]. The extended address register bits [2:0] operate as memory address bit A[26:24] to select one of the eight 128Mb segments of the memory array.

If 4-byte addressing is enabled, the extended address register settings are ignored.

**Table 6: Extended Address Register**

| Bit | Name     | Settings                                                                                                                                                                                                                                    | Description                                                                                                                                                             |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | A[31:27] | 00000                                                                                                                                                                                                                                       | Reserved                                                                                                                                                                |

| 2:0 | A[26:24] | 111 = Highest 128Mb segment<br>110 = Seventh 128Mb segment<br>101 = Sixth 128Mb segment<br>100 = Fifth 128Mb segment<br>011 = Fourth 128Mb segment<br>010 = Third 128Mb segment<br>001 = Second 128Mb segment<br>000 = Lowest 128Mb segment | Enables specified 128Mb memory segment. The default setting (lowest) can be changed to the highest 128Mb segment using bit 1 of the nonvolatile configuration register. |

The PROGRAM and ERASE operations act upon the 128Mb segment selected in the extended address register. The DIE ERASE operation erases the selected die.

The READ operation begins reading in the selected 128Mb segment, but is not bound by it.

In a continuous READ, when the last byte of the segment is read, the next byte output is the first byte of the next segment. The operation wraps to 0000000h; therefore, a download of the whole array is possible with one READ operation.

The value of the extended address register does not change when a READ operation crosses the selected 128Mb boundary.

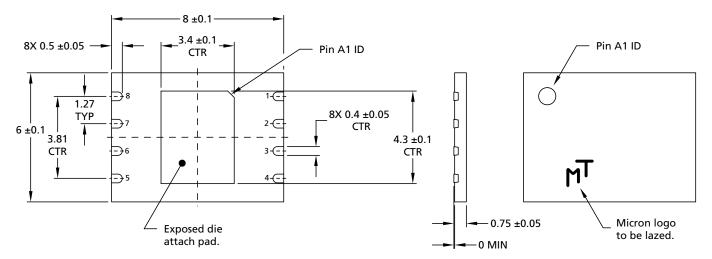

### **Internal Configuration Register**

The memory configuration is set by an internal configuration register that is not directly accessible to users.

The user can change the default configuration at power up by using the WRITE NON-VOLATILE CONFIGURATION REGISTER. Information from the nonvolatile configuration register overwrites the internal configuration register during power-on or after a reset.

The user can change the configuration during operation by using the WRITE VOLATILE CONFIGURATION REGISTER or the WRITE ENHANCED VOLATILE CONFIGURATION REGISTER commands. Information from the volatile configuration registers overwrite the internal configuration register immediately after the WRITE command completes.

**Figure 10: Internal Configuration Register**

# **Nonvolatile Configuration Register**

This register is read from and written to using the READ NONVOLATILE CONFIGURATION REGISTER and the WRITE NONVOLATILE CONFIGURATION REGISTER commands, respectively. A register download is executed during power-on or after reset, overwriting the internal configuration register settings that determine device behavior.

**Table 7: Nonvolatile Configuration Register**

| Bit   | Name                                 | Settings                                                                                                                                                                                                                       | Description                                                                                                                         | Notes |

|-------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| 15:12 | Number of<br>dummy clock cy-<br>cles | 0000 = Identical to 1111<br>0001 = 1<br>0010 = 2<br>:<br>1101 = 13<br>1110 = 14<br>1111 = Default                                                                                                                              | Sets the number of dummy clock cycles subsequent to all FAST READ commands. (See the Command Set Table for default setting values.) | 1     |

| 11:9  | XIP mode at power-on reset           | 000 = XIP: Fast read<br>001 = XIP: Dual output fast read<br>010 = XIP: Dual I/O fast read<br>011 = XIP: Quad output fast read<br>100 = XIP: Quad I/O fast read<br>101 = Reserved<br>110 = Reserved<br>111 = Disabled (Default) | Enables the device to operate in the selected XIP mode immediately after power-on reset.                                            |       |

| 8:6   | Output driver strength               | 000 = Reserved<br>001 = 90 Ohms<br>010 = Reserved<br>011 = 45 Ohms<br>100 = Reserved<br>101 = 20 Ohms<br>110 = Reserved<br>111 = 30 Ohms (Default)                                                                             | Optimizes the impedance at V <sub>CC</sub> /2 output voltage.                                                                       |       |

| 5     | Double transfer rate protocol        | 0 = Enabled<br>1 = Disabled (Default)                                                                                                                                                                                          | Set DTR protocol as current one. Once enabled, all commands will work in DTR.                                                       |       |

| 4     | Reset/hold                           | 0 = Disabled<br>1 = Enabled (Default)                                                                                                                                                                                          | Enables or disables HOLD# or RESET# on DQ3.                                                                                         |       |

| 3     | Quad I/O<br>protocol                 | 0 = Enabled<br>1 = Disabled (Default)                                                                                                                                                                                          | Enables or disables quad I/O command input (4-4-4 mode).                                                                            | 2     |

| 2     | Dual I/O<br>protocol                 | 0 = Enabled<br>1 = Disabled (Default)                                                                                                                                                                                          | Enables or disables dual I/O command input (2-2-2 mode).                                                                            | 2     |

| 1     | 128Mb<br>segment select              | 0 = Highest 128Mb segment<br>1 = Lowest 128Mb segment (Default)                                                                                                                                                                | Selects the power-on default 128Mb segment for 3-byte address operations. See also the extended address register.                   |       |

# 1Gb, 3V Multiple I/O Serial Flash Memory Nonvolatile Configuration Register

#### **Table 7: Nonvolatile Configuration Register (Continued)**

| Bit | Name           | Settings                       | Description                                    | Notes |

|-----|----------------|--------------------------------|------------------------------------------------|-------|

| 0   | Number of      | 0 = Enable 4-byte address mode | Defines the number of address bytes for a com- |       |

|     | address bytes  | 1 = Enable 3-byte address mode | mand.                                          |       |

|     | during command | (Default)                      |                                                |       |

|     | entry          |                                |                                                |       |

- Notes: 1. The number of cycles must be set to accord with the clock frequency, which varies by the type of FAST READ command (See Supported Clock Frequencies table). Insufficient dummy clock cycles for the operating frequency causes the memory to read incorrect data.

- 2. When bits 2 and 3 are both set to 0, the device operates in quad I/O protocol.

### **Volatile Configuration Register**

This register is read from and written to by the READ VOLATILE CONFIGURATION REGISTER and the WRITE VOLATILE CONFIGURATION REGISTER commands, respectively. A register download is executed after these commands, overwriting the internal configuration register settings that determine device memory behavior.

**Table 8: Volatile Configuration Register**

| Bit | Name                               | Settings                                                                                          | Description                                                                                                                         | Notes |

|-----|------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7:4 | Number of<br>dummy clock<br>cycles | 0000 = Identical to 1111<br>0001 = 1<br>0010 = 2<br>:<br>1101 = 13<br>1110 = 14<br>1111 = Default | Sets the number of dummy clock cycles subsequent to all FAST READ commands. (See the Command Set Table for default setting values.) | 1     |

| 3   | XIP                                | 0 = Enable<br>1 = Disable (Default)                                                               | Enables or disables XIP.                                                                                                            |       |

| 2   | Reserved                           | 0                                                                                                 | 0b = Fixed value.                                                                                                                   |       |

| 1:0 | Wrap                               | 00 = 16-byte boundary<br>aligned                                                                  | 16-byte wrap: Output data wraps within an aligned 16-byte boundary starting from the 3-byte address issued after the command code.  | 2     |

|     |                                    | 01 = 32-byte boundary<br>aligned                                                                  | 32-byte wrap: Output data wraps within an aligned 32-byte boundary starting from the 3-byte address issued after the command code.  |       |

|     |                                    | 10 = 64-byte boundary<br>aligned                                                                  | 64-byte wrap: Output data wraps within an aligned 64-byte boundary starting from the 3-byte address issued after the command code.  |       |

|     |                                    | 11 = Continuous (Default)                                                                         | Continuously sequences addresses through the entire array.                                                                          |       |

- Notes: 1. The number of cycles must be set according to and sufficient for the clock frequency, which varies by the type of FAST READ command, as shown in the Supported Clock Frequencies table. An insufficient number of dummy clock cycles for the operating frequency causes the memory to read incorrect data.

- 2. See the Sequence of Bytes During Wrap table.

**Table 9: Sequence of Bytes During Wrap**

| Starting Address | 16-Byte Wrap     | 32-Byte Wrap     | 64-Byte Wrap   |

|------------------|------------------|------------------|----------------|

| 0                | 0-1-215-0-1      | 0-1-231-0-1      | 0-1-263-0-1    |

| 1                | 1-215-0-1-2      | 1-231-0-1-2      | 1-263-0-1-2    |

|                  |                  |                  |                |

| 15               | 15-0-1-2-315-0-1 | 15-16-1731-0-1   | 15-16-1763-0-1 |

|                  |                  |                  |                |

| 31               | -                | 31-0-1-2-331-0-1 | 31-32-3363-0-1 |

|                  |                  |                  |                |

| 63               | -                | -                | 63-0-163-0-1   |

#### **Supported Clock Frequencies**

#### **Table 10: Clock Frequencies - STR (in MHz)**

Notes apply to entire table

| Number of<br>Dummy<br>Clock Cycles | FAST READ | DUAL OUTPUT<br>FAST READ | DUAL I/O FAST<br>READ | QUAD OUTPUT<br>FAST READ | QUAD I/O FAST<br>READ |

|------------------------------------|-----------|--------------------------|-----------------------|--------------------------|-----------------------|

| 1                                  | 94        | 79                       | 60                    | 44                       | 39                    |

| 2                                  | 112       | 97                       | 77                    | 61                       | 48                    |

| 3                                  | 129       | 106                      | 86                    | 78                       | 58                    |

| 4                                  | 133       | 115                      | 97                    | 97                       | 69                    |

| 5                                  | 133       | 125                      | 106                   | 106                      | 78                    |

| 6                                  | 133       | 133                      | 115                   | 115                      | 86                    |

| 7                                  | 133       | 133                      | 125                   | 125                      | 97                    |

| 8                                  | 133       | 133                      | 133                   | 133                      | 106                   |

| 9                                  | 133       | 133                      | 133                   | 133                      | 115                   |

| 10                                 | 133       | 133                      | 133                   | 133                      | 125                   |

| 11 : 14                            | 133       | 133                      | 133                   | 133                      | 133                   |

- Notes: 1. Values are guaranteed by characterization and not 100% tested in production.

- 2. A tuning data pattern (TDP) capability provides applications with data patterns for adjusting the data latching point at the host end when the clock frequency is set higher than 133 MHz in STR mode and higher than 66 MHz in double transfer rate (DTR) mode. For additional details, refer to TN-25-07: Tuning Data Pattern for MT25Q and MT25T Devices.

#### **Table 11: Clock Frequencies - DTR (in MHz)**

Notes apply to entire table

| Number of<br>Dummy<br>Clock Cycles | FAST READ | DUAL OUTPUT<br>FAST READ | DUAL I/O FAST<br>READ | QUAD OUTPUT<br>FAST READ | QUAD I/O FAST<br>READ |

|------------------------------------|-----------|--------------------------|-----------------------|--------------------------|-----------------------|

| 1                                  | 59        | 45                       | 40                    | 26                       | 20                    |

| 2                                  | 73        | 59                       | 49                    | 40                       | 30                    |

| 3                                  | 82        | 68                       | 59                    | 59                       | 39                    |

| 4                                  | 90        | 76                       | 65                    | 65                       | 49                    |

| 5                                  | 90        | 83                       | 75                    | 75                       | 58                    |

| 6                                  | 90        | 90                       | 83                    | 83                       | 68                    |

| 7                                  | 90        | 90                       | 90                    | 90                       | 78                    |

| 8                                  | 90        | 90                       | 90                    | 90                       | 85                    |

| 9                                  | 90        | 90                       | 90                    | 90                       | 90                    |

| 10 : 14                            | 90        | 90                       | 90                    | 90                       | 90                    |

- Notes: 1. Values are guaranteed by characterization and not 100% tested in production.

- 2. A tuning data pattern (TDP) capability provides applications with data patterns for adjusting the data latching point at the host end when the clock frequency is set higher than 133 MHz in STR mode and higher than 66 MHz in double transfer rate (DTR) mode. For additional details, refer to TN-25-07: Tuning Data Pattern for MT25Q and MT25T Devices.

### **Enhanced Volatile Configuration Register**

This register is read from and written to using the READ ENHANCED VOLATILE CONFIGURATION REGISTER and the WRITE ENHANCED VOLATILE CONFIGURATION REGISTER commands, respectively. A register download is executed after these commands, overwriting the internal configuration register settings that determine device memory behavior.

**Table 12: Enhanced Volatile Configuration Register**

| Bit | Name                          | Settings                                                                                                                                           | Description                                                                             | Notes |

|-----|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|

| 7   | Quad I/O protocol             | 0 = Enabled<br>1 = Disabled (Default)                                                                                                              | Enables or disables quad I/O command input (4-4-4 mode).                                | 1     |

| 6   | Dual I/O protocol             | 0 = Enabled<br>1 = Disabled (Default)                                                                                                              | Enables or disables dual I/O command input (2-2-2 mode).                                | 1     |

| 5   | Double transfer rate protocol | 0 = Enabled<br>1 = Disabled (Default,<br>single transfer rate)                                                                                     | Set DTR protocol as current one. Once enabled, all commands will work in DTR.           |       |

| 4   | Reset/hold                    | 0 = Disabled<br>1 = Enabled (Default)                                                                                                              | Enables or disables HOLD# or RESET# on DQ3. (Available only on specified part numbers.) |       |

| 3   | Reserved                      | 1                                                                                                                                                  |                                                                                         |       |

| 2:0 | Output driver strength        | 000 = Reserved<br>001 = 90 ohms<br>010 = Reserved<br>011 = 45 ohms<br>100 = Reserved<br>101 = 20 ohms<br>110 = Reserved<br>111 = 30 ohms (Default) | Optimizes the impedance at V <sub>CC</sub> /2 output voltage.                           |       |

Note: 1. When bits 6 and 7 are both set to 0, the device operates in quad I/O protocol. When either bit 6 or 7 is set to 0, the device operates in dual I/O or quad I/O respectively. When a bit is set, the device enters the selected protocol immediately after the WRITE ENHANCED VOLATILE CONFIGURATION REGISTER command. The device returns to the default protocol after the next power-on or reset. Also, the rescue sequence or another WRITE ENHANCED VOLATILE CONFIGURATION REGISTER command will return the device to the default protocol.

# **Security Registers**

Security registers enable sector and password protection on multiple levels using non-volatile and volatile register and bit settings (shown below). The applicable register tables follow.

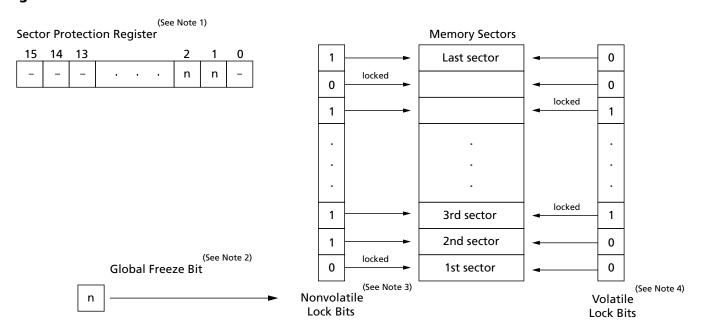

**Figure 11: Sector and Password Protection**

Notes:

- 1. **Sector protection register.** This 16-bit nonvolatile register includes two active bits[2:1] to enable sector and password protection.

- 2. Global freeze bit. This volatile bit protects the settings in all nonvolatile lock bits.

- 3. **Nonvolatile lock bits.** Each nonvolatile bit corresponds to and provides nonvolatile protection for an individual memory sector, which remains locked (protection enabled) until its corresponding bit is cleared to 1.

- 4. **Volatile lock bits.** Each volatile bit corresponds to and provides volatile protection for an individual memory sector, which is locked temporarily (protection is cleared when the device is reset or powered down).

- 5. The first and last sectors will have volatile protections at the 4KB subsector level. Each 4KB subsector in these sectors can be individually locked by volatile lock bits setting; nonvolatile protections granularity remain at the sector level.

#### **Sector Protection Security Register**

**Table 13: Sector Protection Register**