# gDDR3 SDRAM Graphics Addendum

# MT41J128M16 - 16 Meg x 16 x 8 Banks

#### **Features**

- $V_{DD} = V_{DDO} = +1.5V (1.425-1.575V)$

- $V_{DD} = V_{DDO} = +1.35V (1.283-1.45V)$  capable at down clocked speeds

- Differential bidirectional data strobe

- 8*n*-bit prefetch architecture

- Differential clock inputs (CK, CK#)

- · 8 internal banks

- Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals

- Programmable CAS READ latency (CL)

- Posted CAS additive latency (AL): 0, CL 1, CL 2

- Programmable CAS WRITE latency (CWL)

- Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS])

- Selectable BC4 or BL8 on-the-fly (OTF)

- · Self refresh mode

- T<sub>C</sub> of 0°C to 95°C

- 64ms, 8192 cycle refresh at 0°C to 85°C

- 32ms at 85°C to 115°C

- Self refresh temperature (SRT)

- Automatic self refresh (ASR)

- Write leveling

- Multipurpose register

- · Output driver calibration

| Options                                              | Marking             |

|------------------------------------------------------|---------------------|

| Configuration                                        | _                   |

| - 128 Meg x 16                                       | 128M16              |

| • FBGA package (Pb-free) – x16                       |                     |

| <ul> <li>96-ball (9mm x 14mm) Rev. D</li> </ul>      | HA                  |

| <ul> <li>96-ball (8mm x 14mm) Rev. K</li> </ul>      | JT                  |

| • Timing – cycle time                                |                     |

| - 1.0ns @ CL = 14 (gDDR3-2000)                       | -093G <sup>1</sup>  |

| - 1.1ns @ CL = 13 (gDDR3-1800)                       | -107G               |

| - 1.25ns @ CL = 11 (gDDR3-1600)                      | -125G               |

| Operating temperature                                |                     |

| - Commercial (0°C $\leq$ T <sub>C</sub> $\leq$ 95°C) | None                |

| Revision                                             | :D <sup>2</sup> /:K |

- Notes: 1. Only available on Revision K.

- 2. Revision D is not 1.35V capable.

- 3. For complete device functionality and specifications, refer to the standard 2Gb DDR3 SDRAM data sheet found at www.micron.com. The information in this data sheet supersedes the standard data sheet.

#### **Table 1: Key Timing Parameters**

| Speed Grade        | Data Rate (MT/s) | Target <sup>t</sup> RCD- <sup>t</sup> RP-CL | <sup>t</sup> RCD (ns) | <sup>t</sup> RP (ns) | CL (ns) |

|--------------------|------------------|---------------------------------------------|-----------------------|----------------------|---------|

| -093G <sup>1</sup> | 2000             | 14-14-14                                    | 14                    | 14                   | 14      |

| -107G <sup>2</sup> | 1800             | 13-13-13                                    | 14.3                  | 14.3                 | 14.3    |

| -125G <sup>2</sup> | 1600             | 11-11-11                                    | 13.75                 | 13.75                | 13.75   |

- 1. Requires  $V_{DD} = V_{DDO} = +1.5V_{NOM}$

- 2.  $V_{DD} = V_{DDO} = +1.35V_{NOM}$  capable

#### **Table 2: Addressing**

| Parameter         | 64 Meg x 16           |

|-------------------|-----------------------|

| Configuration     | 16 Meg x 16 x 8 banks |

| Refresh count     | 8K                    |

| Row addressing    | 16K (A[13:0])         |

| Bank addressing   | 8 (BA[2:0])           |

| Column addressing | 1K (A[9:0])           |

# 2Gb: x16 gDDR3 SDRAM Graphics Addendum Features

#### **Table 3: Part Number Cross Reference**

| Micron Part Number   | FBGA Code |

|----------------------|-----------|

| MT41J128M16JT-093G:K | D9PTD     |

| MT41J128M16JT-107G:K | D9PRS     |

| MT41J128M16JT-125G:K | D9PRV     |

| MT41J128M16HA-107G:D | D9PFS     |

| MT41J128M16HA-125G:D | D9MGG     |

# **FBGA Part Marking Decoder**

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the part number. Micron's FBGA part marking decoder is available at <a href="https://www.micron.com/decoder">www.micron.com/decoder</a>.

# **Ball Assignments**

Figure 1: 96-Ball FBGA - x16 (Top View)

|   | 1                                                                               | 2                   | 3                         | 4 | 5 | 6 | 7                  | 8                           | 9                                                                                         |

|---|---------------------------------------------------------------------------------|---------------------|---------------------------|---|---|---|--------------------|-----------------------------|-------------------------------------------------------------------------------------------|

|   |                                                                                 |                     |                           |   |   |   |                    |                             |                                                                                           |

| Α | V <sub>DDQ</sub>                                                                | DQ13                | DQ15                      |   |   |   | DQ12               | $V_{DDQ}$                   | $\bigcup_{V_{SS}}$                                                                        |

| В | V <sub>SSQ</sub>                                                                | $\bigvee_{V_{DD}}$  | $\bigvee_{V_{SS}}$        |   |   |   | UDQS#              | DQ14                        | V <sub>SSQ</sub>                                                                          |

| С | V <sub>DDQ</sub>                                                                | DQ11                | DQ9                       |   |   |   | UDQS               | DQ10                        | O <sub>DDQ</sub>                                                                          |

| D | V <sub>DDQ</sub> V <sub>SSQ</sub> V <sub>SSS</sub>                              | $\bigvee_{V_{DDQ}}$ | UDM                       |   |   |   | DQ8                | $\bigcup_{V_{SSQ}}$         | V <sub>DD</sub>                                                                           |

| Е | V <sub>SS</sub>                                                                 | $\bigvee_{V_{SSQ}}$ | DQ0                       |   |   |   | LDM                | $\bigvee_{V_{SSQ}}$         | ○ V <sub>DDQ</sub>                                                                        |

| F | V <sub>DDQ</sub>                                                                | DQ2                 | DQ15 Vss DQ9 UDM DQ0 LDQS |   |   |   | UDQS DQ8 LDM DQ1   | DQ14  DQ10  Vssq  Vssq  DQ3 | Vsss Vssq VDDQ VDDQ Vssq Vssq Vssq Vssq Vssq Vssq Vssq Vss                                |

| G | V <sub>SSQ</sub>                                                                | DQ6                 | LDQS#                     |   |   |   | $\bigvee_{V_{DD}}$ | V <sub>SS</sub>             | V <sub>SSQ</sub>                                                                          |

| Н | VREFDQ                                                                          | $\bigvee_{V_{DDQ}}$ | DQ4                       |   |   |   | DQ7                | DQ5                         | V <sub>DDQ</sub>                                                                          |

| J | NC NC                                                                           | $\bigcup_{V_{SS}}$  | RAS#                      |   |   |   | CK                 | $\bigvee_{V_{SS}}$          | O<br>NC                                                                                   |

| K | ODT                                                                             | $\bigvee_{V_{DD}}$  | CAS#                      |   |   |   | CK#                | $\bigvee_{V_{DD}}$          | CKE                                                                                       |

| L | NC NC                                                                           | CS#                 | WE#                       |   |   |   | A10/AP             | ZQ                          | NC NC                                                                                     |

| М | V <sub>SS</sub>                                                                 | BA0                 | $\bigcirc$                |   |   |   | NC                 | V <sub>REFCA</sub>          | Vss                                                                                       |

| N | $V_{DD}$                                                                        | A3                  | AO                        |   |   |   | A12/BC#            | BA1                         | V <sub>DD</sub>                                                                           |

| Р | V <sub>SS</sub>                                                                 | A5                  | A2                        |   |   |   | A1                 | A4                          | $\bigcup_{V_{SS}}$                                                                        |

| R | V <sub>SS</sub> V <sub>DD</sub> V <sub>SS</sub> V <sub>DD</sub> V <sub>SS</sub> | A7                  | Δ9                        |   |   |   | A11                | 0                           | ○ V <sub>DD</sub>                                                                         |

| Т | V <sub>SS</sub>                                                                 | RESET#              | NC NC                     |   |   |   | NC NC              | A8                          | NC CKE NC V <sub>SS</sub> V <sub>DD</sub> V <sub>SS</sub> V <sub>DD</sub> V <sub>SS</sub> |

|   |                                                                                 |                     |                           |   |   |   |                    |                             |                                                                                           |

- Notes: 1. Ball descriptions are listed in the main 2Gb DDR3 data sheet.

- 2. A comma separates the configuration; a slash defines a selectable function. Example D7 = NF, NF/TDQS# is selectable between NF or TDQS# via MRS.

# **Package Dimensions**

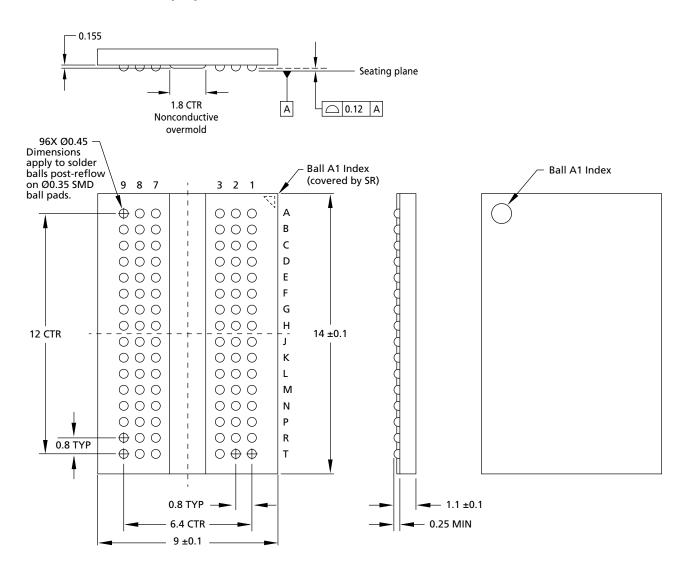

Figure 2: 96-Ball FBGA - x16 (HA)

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC 305: 96.5% Sn, 3% Ag, 0.5% Cu.

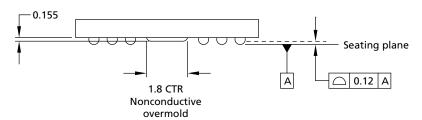

Figure 3: 96-Ball FBGA - x16 (JT)

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC 305: 96.5% Sn, 3% Ag, 0.5% Cu.

# **Electrical Specifications**

#### **Table 4: DC Electrical Characteristics and Operating Conditions**

All voltages are referenced to V<sub>ss</sub>

| Parameter/Condition | Symbol    | Min   | Nom  | Мах   | Unit | Notes   |

|---------------------|-----------|-------|------|-------|------|---------|

| Supply voltage      | $V_{DD}$  | 1.425 | 1.5  | 1.575 | V    | 1, 2, 3 |

| I/O supply voltage  | $V_{DDQ}$ | 1.425 | 1.5  | 1.575 | V    | 1, 2 ,3 |

| Supply voltage      | $V_{DD}$  | 1.283 | 1.35 | 1.45  | V    | 1, 2, 4 |

| I/O supply voltage  | $V_{DDQ}$ | 1.283 | 1.35 | 1.45  | V    | 1, 2, 4 |

- Notes: 1.  $V_{DD}$  and  $V_{DDQ}$  must track one another.  $V_{DDQ}$  must be  $\leq V_{DD}$ .  $V_{SS} = V_{SSQ}$ .

- 2.  $V_{DD}$  and  $V_{DDQ}$  may include AC noise of ±50mV (250 kHz to 20 MHz) in addition to the DC (0 Hz to 250 kHz) specifications.  $V_{DD}$  and  $V_{DDO}$  must be at same level for valid AC timing parameters.

- 3. Valid with all speed bins.

- 4. Not for use with -093 speed bin.

#### **Table 5: Input/Output Capacitance**

Note 1 applies to the entire table

| Capacitance                                 |                         | gDDR3-1600 |      | gDDR3-1800 |      | gDDR3-2000 |      |      |       |

|---------------------------------------------|-------------------------|------------|------|------------|------|------------|------|------|-------|

| Parameters                                  | Symbol                  | Min        | Max  | Min        | Max  | Min        | Max  | Unit | Notes |

| CK and CK#                                  | C <sub>CK</sub>         | 0.8        | 1.4  | 0.8        | 1.3  | 0.8        | 1.3  | pF   |       |

| ΔC: CK to CK#                               | C <sub>DCK</sub>        | 0          | 0.15 | 0          | 0.15 | 0          | 0.15 | pF   |       |

| Single-end I/O: DQ, DM                      | C <sub>IO</sub>         | 1.5        | 2.3  | 1.5        | 2.2  | 1.5        | 2.1  | pF   | 2     |

| Differential I/O: DQS, DQS#, TDQS,<br>TDQS# | C <sub>IO</sub>         | 1.5        | 2.3  | 1.5        | 2.2  | 1.5        | 2.1  | pF   | 3     |

| ΔC: DQS to DQS#, TDQS, TDQS#                | C <sub>DDQS</sub>       | 0          | 0.15 | 0          | 0.15 | 0          | 0.15 | pF   | 3     |

| ΔC: DQ to DQS                               | C <sub>DIO</sub>        | -0.5       | 0.3  | -0.5       | 0.3  | -0.5       | 0.3  | pF   | 4     |

| Inputs (CTRL, CMD, ADDR)                    | C <sub>I</sub>          | 0.75       | 1.3  | 0.75       | 1.2  | 0.75       | 1.2  | pF   | 5     |

| ΔC: CTRL to CK                              | C <sub>DI_CTRL</sub>    | -0.4       | 0.2  | -0.4       | 0.2  | -0.4       | 0.2  | pF   | 6     |

| ΔC: CMD_ADDR to CK                          | C <sub>DI_CMD_ADD</sub> | -0.4       | 0.4  | -0.4       | 0.4  | -0.4       | 0.4  | pF   | 7     |

| ZQ pin capacitance                          | C <sub>zO</sub>         | _          | 3.0  | _          | 3.0  | _          | 3.0  | pF   |       |

| Reset pin capacitance                       | C <sub>RE</sub>         | _          | 3.0  | _          | 3.0  | -          | 3.0  | pF   |       |

- Notes: 1.  $V_{DD} = 1.5V \pm 0.075 \text{mV}$ ,  $V_{DDQ} = V_{DD}$ ,  $V_{REF} = V_{SS}$ , f = 100 MHz,  $T_C = 25^{\circ}\text{C}$ .  $V_{OUT(DC)} = 0.5 \times 10^{-5} \text{ MHz}$  $V_{DDO}$ ,  $V_{OUT} = 0.1V$  (peak-to-peak).

- 2. DM input is grouped with I/O pins, reflecting the fact that they are matched in loading.

- 3. Includes TDQS, TDQS#. CDDOS is for DQS vs. DQS# and TDQS vs. TDQS# separately.

- 4.  $C_{DIO} = C_{IO(DQ)} 0.5 \times (C_{IO(DQS)} + C_{IO(DQS\#)}).$

- 5. Excludes CK, CK#; CTRL = ODT, CS#, and CKE; CMD = RAS#, CAS#, and WE#; ADDR = A[n:0], BA[2:0].

- 6.  $C_{DI\_CTRL} = C_{I(CTRL)} 0.5 \times (C_{CK(CK)} + C_{CK(CK\#)}).$

- 7.  $C_{DI\_CMD\_ADDR} = C_{I(CMD\_ADDR)} 0.5 \times (C_{CK(CK)} + C_{CK(CK\#)})$ .

# **Electrical Characteristics – IDD Specifications**

$I_{\mbox{\scriptsize DD}}$  values are for full operating range of voltage and temperature unless otherwise noted.

Table 6: I<sub>DD</sub> Maximum Limits - Die Rev D

| Speed Bin                 |                          |                          |       |         |

|---------------------------|--------------------------|--------------------------|-------|---------|

| I <sub>DD</sub>           | gDDR3-1600               | gDDR3-1800               | Units | Notes   |

| I <sub>DD0</sub>          | 110                      | 120                      | mA    | 1, 2    |

| I <sub>DD1</sub>          | 135                      | 140                      | mA    | 1, 2    |

| I <sub>DD2P0</sub> (slow) | 12                       | 12                       | mA    | 1, 2    |

| I <sub>DD2P1</sub> (fast) | 40                       | 45                       | mA    | 1, 2    |

| I <sub>DD2Q</sub>         | 40                       | 45                       | mA    | 1, 2    |

| I <sub>DD2N</sub>         | 42                       | 47                       | mA    | 1, 2    |

| I <sub>DD2NT</sub>        | 65                       | 70                       | mA    | 1, 2    |

| I <sub>DD3P</sub>         | 45                       | 50                       | mA    | 1, 2    |

| I <sub>DD3N</sub>         | 45                       | 50                       | mA    | 1, 2    |

| I <sub>DD4R</sub>         | 270                      | 295                      | mA    | 1, 2    |

| I <sub>DD4W</sub>         | 280                      | 315                      | mA    | 1, 2    |

| I <sub>DD5B</sub>         | 215                      | 220                      | mA    | 1, 2    |

| I <sub>DD6</sub>          | 12                       | 12                       | mA    | 1, 2, 3 |

| I <sub>DD6ET</sub>        | 15                       | 15                       | mA    | 2, 4    |

| I <sub>DD7</sub>          | 475                      | 525                      | mA    | 1, 2    |

| I <sub>DD8</sub>          | I <sub>DD2P0</sub> + 2mA | I <sub>DD2P0</sub> + 2mA | mA    | 1, 2    |

Table 7: I<sub>DD</sub> Maximum Limits - Die Rev K

| Speed Bin                 |            |            |            |       |         |

|---------------------------|------------|------------|------------|-------|---------|

| I <sub>DD</sub>           | gDDR3-1600 | gDDR3-1800 | gDDR3-2000 | Units | Notes   |

| I <sub>DD0</sub>          | 49         | 51         | 55         | mA    | 1, 2    |

| I <sub>DD1</sub>          | 69         | 72         | 75         | mA    | 1, 2    |

| I <sub>DD2P0</sub> (slow) | 12         | 12         | 12         | mA    | 1, 2    |

| I <sub>DD2P1</sub> (fast) | 15         | 15         | 15         | mA    | 1, 2    |

| I <sub>DD2Q</sub>         | 22         | 22         | 22         | mA    | 1, 2    |

| I <sub>DD2N</sub>         | 23         | 23         | 23         | mA    | 1, 2    |

| I <sub>DD2NT</sub>        | 37         | 39         | 43         | mA    | 1, 2    |

| I <sub>DD3P</sub>         | 22         | 22         | 22         | mA    | 1, 2    |

| I <sub>DD3N</sub>         | 37         | 39         | 43         | mA    | 1, 2    |

| I <sub>DD4R</sub>         | 135        | 155        | 180        | mA    | 1, 2    |

| I <sub>DD4W</sub>         | 146        | 164        | 184        | mA    | 1, 2    |

| I <sub>DD5B</sub>         | 182        | 184        | 190        | mA    | 1, 2    |

| I <sub>DD6</sub>          | 12         | 12         | 12         | mA    | 1, 2, 3 |

#### Table 7: IDD Maximum Limits - Die Rev K (Continued)

| Speed Bin          |                          |                          |                          |       |       |

|--------------------|--------------------------|--------------------------|--------------------------|-------|-------|

| I <sub>DD</sub>    | gDDR3-1600               | gDDR3-1800               | gDDR3-2000               | Units | Notes |

| I <sub>DD6ET</sub> | 15                       | 15                       | 15                       | mA    | 2, 4  |

| I <sub>DD7</sub>   | 202                      | 226                      | 248                      | mA    | 1, 2  |

| I <sub>DD8</sub>   | I <sub>DD2P0</sub> + 2mA | I <sub>DD2P0</sub> + 2mA | I <sub>DD2P0</sub> + 2mA | mA    | 1, 2  |

Note

- 1.  $T_C = 85$ °C; SRT and ASR are disabled.

- 2. Enabling ASR could increase  $I_{DDx}$  by up to an additional 2mA.

- 3. Restricted to  $T_C$  (MAX) = 85°C.

- 4.  $T_C = 85$ °C; ASR and ODT are disabled; SRT is enabled.

- 5. The  $I_{DD}$  values must be derated (increased) on IT-option devices when operated outside of the range  $0^{\circ}C \le T_C \le 85^{\circ}C$ :

5a. When  $T_C < 0$ °C:  $I_{DD2P}$  and  $I_{DD3P}$  must be derated by 4%;  $I_{DD4R}$  and  $I_{DD5W}$  must be derated by 2%; and  $I_{DD6}$  and  $I_{DD7}$  must be derated by 7%.

5b. When  $T_C > 85^{\circ}C$ :  $I_{DD0}$ ,  $I_{DD1}$ ,  $I_{DD2N}$ ,  $I_{DD2NT}$ ,  $I_{DD2Q}$ ,  $I_{DD3N}$ ,  $I_{DD3P}$ ,  $I_{DD4R}$ ,  $I_{DD4W}$ , and  $I_{DD5W}$  must be derated by 2%;  $I_{DD2Px}$  must be derated by 30%.

# **Speed Bin Tables**

#### Table 8: gDDR3-1600 Speed Bins

| gDDR3-1600 Speed Bin                  | -125G                 |                       |                       |                      |      |       |

|---------------------------------------|-----------------------|-----------------------|-----------------------|----------------------|------|-------|

| CL- <sup>t</sup> RCD- <sup>t</sup> RP |                       | 11-1                  | 1-11                  | 1                    |      |       |

| Parameter                             |                       | Symbol                | Min                   | Max                  | Unit | Notes |

| ACTIVATE to internal READ             | or WRITE delay time   | <sup>t</sup> RCD      | 13.75                 | _                    | ns   |       |

| PRECHARGE command perio               | od                    | <sup>t</sup> RP       | 13.75                 | _                    | ns   |       |

| ACTIVATE-to-ACTIVATE or RI            | EFRESH command period | <sup>t</sup> RC       | 48.75                 | _                    | ns   |       |

| ACTIVATE-to-PRECHARGE co              | mmand period          | <sup>t</sup> RAS      | 35                    | 9 x <sup>t</sup> REF | ns   | 1     |

| CL = 5                                | CWL = 5               | <sup>t</sup> CK (AVG) | 3.0                   | 3.3                  | ns   | 2     |

|                                       | CWL = 6, 7, 8         | <sup>t</sup> CK (AVG) | Rese                  | rved                 | ns   | 3     |

| CL = 6                                | CWL = 5               | <sup>t</sup> CK (AVG) | 2.5                   | 3.3                  | ns   | 2     |

|                                       | CWL = 6, 7, 8         | <sup>t</sup> CK (AVG) | Reserved              |                      | ns   | 3     |

| CL = 7                                | CWL = 5               | <sup>t</sup> CK (AVG) | Reserved              |                      | ns   | 3     |

|                                       | CWL = 6               | tCK (AVG)             | 1.875                 | <2.5                 | ns   | 2     |

|                                       | CWL = 7, 8            | tCK (AVG)             | Reserved              |                      | ns   | 3     |

| CL = 8                                | CWL = 5               | tCK (AVG)             | Reserved              |                      | ns   | 3     |

|                                       | CWL = 6               | tCK (AVG)             | 1.875                 | <2.5                 | ns   | 2     |

|                                       | CWL = 7, 8            | <sup>t</sup> CK (AVG) | Rese                  | rved                 | ns   | 3     |

| CL = 9                                | CWL = 5, 6            | <sup>t</sup> CK (AVG) | Rese                  | rved                 | ns   | 3     |

|                                       | CWL = 7               | <sup>t</sup> CK (AVG) | 1.5                   | <1.875               | ns   | 2     |

|                                       | CWL = 8               | <sup>t</sup> CK (AVG) | Rese                  | rved                 | ns   | 3     |

| CL = 10                               | CWL = 5, 6            | <sup>t</sup> CK (AVG) | Rese                  | rved                 | ns   | 3     |

|                                       | CWL = 7               | <sup>t</sup> CK (AVG) | 1.5                   | <1.875               | ns   | 2     |

|                                       | CWL = 8               | tCK (AVG)             | Rese                  | rved                 | ns   | 3     |

| CL = 11                               | CWL = 5, 6, 7         | tCK (AVG)             | Rese                  | rved                 | ns   | 3     |

|                                       | CWL = 8               | tCK (AVG)             | 1.25                  | <1.5                 | ns   | 2     |

| Supported CL settings                 |                       |                       | 5, 6, 7, 8, 9, 10, 11 |                      | СК   |       |

| Supported CWL settings                |                       |                       | 5, 6,                 | 7, 8                 | CK   |       |

- Notes: 1. <sup>t</sup>REFI depends on T<sub>OPER</sub>.

- 2. The CL and CWL settings result in <sup>t</sup>CK requirements. When making a selection of <sup>t</sup>CK, both CL and CWL requirement settings need to be fulfilled.

- 3. Reserved settings are not allowed.

# 2Gb: x16 gDDR3 SDRAM Graphics Addendum Speed Bin Tables

Table 9: gDDR3-1800 Speed Bins

| gDDR3-1800 Speed Bin                  | -10                    | 7G                    |               |                       |      |       |

|---------------------------------------|------------------------|-----------------------|---------------|-----------------------|------|-------|

| CL- <sup>t</sup> RCD- <sup>t</sup> RP |                        |                       | 13-1          | 3-13                  |      |       |

| Parameter                             |                        | Symbol                | Min           | Мах                   | Unit | Notes |

| ACTIVATE to internal READ             | or WRITE delay time    | <sup>t</sup> RCD      | 14.3          | _                     | ns   |       |

| PRECHARGE command peri                | od                     | <sup>t</sup> RP       | 14.3          | -                     | ns   |       |

| ACTIVATE-to-ACTIVATE or F             | REFRESH command period | <sup>t</sup> RC       | 48.91         | -                     | ns   |       |

| ACTIVATE-to-PRECHARGE of              | ommand period          | <sup>t</sup> RAS      | 35            | 9 x <sup>t</sup> REFI | ns   | 1     |

| CL = 5                                | CWL = 5                | <sup>t</sup> CK (AVG) | 3.0           | 3.3                   | ns   | 3     |

|                                       | CWL = 6, 7, 8, 9       | <sup>t</sup> CK (AVG) | Rese          | rved                  | ns   | 3     |

| CL = 6                                | CWL = 5                | <sup>t</sup> CK (AVG) | 2.5           | 3.3                   | ns   | 2     |

|                                       | CWL = 6, 7, 8, 9       | <sup>t</sup> CK (AVG) | Rese          | rved                  | ns   | 3     |

| CL = 7                                | CWL = 5, 7, 8, 9       | <sup>t</sup> CK (AVG) | Reserved      |                       | ns   | 3     |

|                                       | CWL = 6                | <sup>t</sup> CK (AVG) | 2.5           | 3.3                   | ns   | 3     |

| CL = 8                                | CWL = 5, 7, 8, 9       | <sup>t</sup> CK (AVG) | Reserved      |                       | ns   | 3     |

|                                       | CWL = 6                | <sup>t</sup> CK (AVG) | 1.875         | <2.5                  | ns   | 2     |

| CL = 9                                | CWL = 5, 6, 8, 9       | <sup>t</sup> CK (AVG) | Reserved      |                       | ns   | 3     |

|                                       | CWL = 7                | tCK (AVG)             | 1.875         | <2.5                  | ns   | 3     |

| CL = 10                               | CWL = 5, 6, 9          | <sup>t</sup> CK (AVG) | Rese          | erved                 | ns   | 3     |

|                                       | CWL = 7                | tCK (AVG)             | 1.5           | <1.875                | ns   | 2     |

|                                       | CWL = 8                | <sup>t</sup> CK (AVG) | Rese          | erved                 | ns   | 3     |

| CL = 11                               | CWL = 5, 6, 7          | <sup>t</sup> CK (AVG) | Rese          | rved                  | ns   | 3     |

|                                       | CWL = 8                | <sup>t</sup> CK (AVG) | 1.5           | <1.875                | ns   | 3     |

|                                       | CWL = 9                | <sup>t</sup> CK (AVG) | Rese          | rved                  | ns   | 3     |

| CL - 12                               | CWL = 5, 6, 7, 8       | tCK (AVG)             | Rese          | rved                  | ns   | 3     |

|                                       | CWL = 9                | tCK (AVG)             | Rese          | rved                  | ns   | 3     |

| CL = 13                               | CWL = 5, 6, 7, 8       | tCK (AVG)             | Rese          | rved                  | ns   | 3     |

|                                       | CWL = 9                | tCK (AVG)             | 1.1           | <1.25                 | ns   | 2     |

| Supported CL settings                 |                        | '                     | 5, 6, 7, 8, 9 | , 10, 11, 13          | CK   |       |

| Supported CWL settings                |                        |                       | 5, 6,         | 7, 8, 9               | CK   |       |

- Notes: 1. <sup>t</sup>REFI depends on T<sub>OPER</sub>.

- 2. The CL and CWL settings result in <sup>t</sup>CK requirements. When making a selection of <sup>t</sup>CK, both CL and CWL requirement settings need to be fulfilled.

- 3. Reserved settings are not allowed.

# 2Gb: x16 gDDR3 SDRAM Graphics Addendum Speed Bin Tables

Table 10: gDDR3-2000 Speed Bins

| gDDR3-2000 Speed Bin                  |                      | -0                    | 93G            |                       |      |       |

|---------------------------------------|----------------------|-----------------------|----------------|-----------------------|------|-------|

| CL- <sup>t</sup> RCD- <sup>t</sup> RP |                      |                       | 14-            | 14-14                 |      |       |

| Parameter                             |                      | Symbol                | Min            | Max                   | Unit | Notes |

| ACTIVATE to internal READ o           | r WRITE delay time   | <sup>t</sup> RCD      | 14             | -                     | ns   |       |

| PRECHARGE command period              | I                    | <sup>t</sup> RP       | 14             | _                     | ns   |       |

| ACTIVATE-to-ACTIVATE or RE            | FRESH command period | <sup>t</sup> RC       | 50             | _                     | ns   |       |

| ACTIVATE-to-PRECHARGE command period  |                      | <sup>t</sup> RAS      | 36             | 9 x <sup>t</sup> REFI | ns   | 1     |

| CL = 5                                | CWL = 5              | <sup>t</sup> CK (AVG) | 3.0            | 3.3                   | ns   | 3     |

|                                       | CWL = 6, 7, 8, 9     | <sup>t</sup> CK (AVG) | Res            | served                | ns   | 3     |

| CL = 6                                | CWL = 5              | <sup>t</sup> CK (AVG) | 2.5            | 3.3                   | ns   | 2     |

|                                       | CWL = 6, 7, 8, 9     | <sup>t</sup> CK (AVG) | Res            | served                | ns   | 3     |

| CL = 7                                | CWL = 5, 7, 8, 9     | <sup>t</sup> CK (AVG) | 2.5            | 3.3                   | ns   | 3     |

|                                       | CWL = 6              |                       | Reserved       |                       | ns   | 3     |

| CL = 8                                | CWL = 5, 7, 8, 9     | <sup>t</sup> CK (AVG) | Reserved       |                       | ns   | 3     |

|                                       | CWL = 6              | <sup>t</sup> CK (AVG) | 1.875          | <2.5                  | ns   | 2     |

| CL = 9                                | CWL = 5, 6, 8, 9     | <sup>t</sup> CK (AVG) | Reserved       |                       | ns   | 3     |

|                                       | CWL = 7              | <sup>t</sup> CK (AVG) | 1.875          | <2.5                  | ns   | 3     |

| CL = 10                               | CWL = 5, 6, 9        | <sup>t</sup> CK (AVG) | Res            | served                | ns   | 3     |

|                                       | CWL = 7              | <sup>t</sup> CK (AVG) | 1.5            | <1.875                | ns   | 2     |

|                                       | CWL = 8              | <sup>t</sup> CK (AVG) | Res            | served                | ns   | 3     |

| CL = 11                               | CWL = 5, 6, 7        | tCK (AVG)             | Res            | served                | ns   | 3     |

|                                       | CWL = 8              | tCK (AVG)             | 1.5            | <1.875                | ns   | 3     |

|                                       | CWL = 9              | tCK (AVG)             | Res            | served                | ns   | 3     |

| CL - 12                               | CWL = 5, 6, 7, 8     | tCK (AVG)             | Res            | served                | ns   | 3     |

|                                       | CWL = 9              | tCK (AVG)             | Res            | served                | ns   | 3     |

| CL = 13                               | CWL = 5, 6, 7, 8     | <sup>t</sup> CK (AVG) | Res            | served                | ns   | 3     |

|                                       | CWL = 9              | <sup>t</sup> CK (AVG) | 1.1            | <1.25                 | ns   | 2     |

| CL = 14                               | CWL = 5, 6, 7, 8, 9  | tCK (AVG)             | 1              | <1.1                  | ns   | 2     |

|                                       | CWL = 10             |                       |                |                       |      |       |

| Supported CL settings                 |                      |                       | 5, 6, 7, 8, 9, | 10, 11, 13, 14        | CK   |       |

| Supported CWL settings                |                      |                       | 5, 6, 7        | , 8, 9, 10            | CK   |       |

- Notes: 1. <sup>t</sup>REFI depends on T<sub>OPER</sub>.

- 2. The CL and CWL settings result in <sup>t</sup>CK requirements. When making a selection of <sup>t</sup>CK, both CL and CWL requirement settings need to be fulfilled.

- 3. Reserved settings are not allowed.

# **Electrical Characteristics and AC Operating Conditions**

#### **Table 11: Electrical Characteristics and AC Operating Conditions for Speed Extensions**

|                                 |                                   |                                      | gDDR:   | 3-1600                | gDDR: | 3-1800                 | gDDR:                  | 3-2000   |                          |        |

|---------------------------------|-----------------------------------|--------------------------------------|---------|-----------------------|-------|------------------------|------------------------|----------|--------------------------|--------|

| Parameter                       |                                   | Symbol                               | Min     | Max                   | Min   | Max                    | Min                    | Max      | Unit                     | Notes  |

|                                 |                                   |                                      | Clock   | Timing                |       |                        |                        |          |                          |        |

| Clock period aver-              | $T_C = 0$ °C to 85°C              | <sup>t</sup> CK                      | 8       | 7800                  | 8     | 7800                   | 8                      | 7800     | ns                       | 9, 42  |

| age: DLL disable<br>mode        | T <sub>C</sub> = >85°C to<br>95°C | (DLL_DIS)                            | 8       | 3900                  | 8     | 3900                   | 8                      | 3900     | ns                       | 42     |

| Clock period averag             | e: DLL enable                     | <sup>t</sup> CK (AVG)                | See co  | rresondin             |       | oin table ved          | for <sup>t</sup> CK ra | inge al- | ns                       | 10, 11 |

| High pulse width av             | erage                             | <sup>t</sup> CH (AVG)                | 0.47    | 0.53                  | 0.47  | 0.53                   | 0.47                   | 0.53     | CK                       | 12     |

| Low pulse width ave             | erage                             | tCL (AVG)                            | 0.47    | 0.53                  | 0.47  | 0.53                   | 0.47                   | 0.53     | CK                       | 12     |

| Clock period jitter             | DLL locked                        | <sup>t</sup> JIT <sub>PER</sub>      | -80     | 80                    | -70   | 70                     | -60                    | 60       | ps                       | 13     |

|                                 | DLL locking                       | <sup>t</sup> JIT <sub>PER</sub> ,lck | -70     | 70                    | -60   | 60                     | -50                    | 50       | ps                       | 13     |

| Clock absolute perio            | od                                | <sup>t</sup> CK (ABS)                |         | MIN = tC              |       | MIN + <sup>t</sup> JI7 |                        | <b>(</b> | ps                       |        |

| Clock absolute high             | pulse width                       | <sup>t</sup> CH (ABS)                | 0.43    | -                     | 0.43  | _                      | 0.43                   | _        | <sup>t</sup> CK<br>(AVG) | 14     |

| Clock absolute low              | pulse width                       | <sup>t</sup> CL (ABS)                | 0.43    | -                     | 0.43  | -                      | - 0.43                 |          | <sup>t</sup> CK<br>(AVG) | 15     |

| Cycle-to-cycle jitter           | DLL locked                        | <sup>t</sup> JIT <sub>CC</sub>       | 160     |                       | 14    | 40                     | 12                     | 20       | ps                       | 16     |

|                                 | DLL locking                       | <sup>t</sup> JIT <sub>CC</sub> ,lck  | 14      | 40                    | 1:    | 20                     | 100                    |          | ps                       | 16     |

| Cumulative error                | 2 cycles                          | tERR2 <sub>PER</sub>                 | -118    | 118                   | -103  | 103                    | -88                    | 88       | ps                       | 17     |

| across                          | 3 cycles                          | tERR3 <sub>PER</sub>                 | -140    | 140                   | -122  | 122                    | -105                   | 105      | ps                       | 17     |

|                                 | 4 cycles                          | tERR4 <sub>PER</sub>                 | -155    | 155                   | -136  | 136                    | -117                   | 117      | ps                       | 17     |

|                                 | 5 cycles                          | tERR5 <sub>PER</sub>                 | -168    | 168                   | -147  | 147                    | -126                   | 126      | ps                       | 17     |

|                                 | 6 cycles                          | tERR6 <sub>PER</sub>                 | -177    | 177                   | -155  | 155                    | -133                   | 133      | ps                       | 17     |

|                                 | 7 cycles                          | tERR7 <sub>PER</sub>                 | -186    | 186                   | -163  | 163                    | -139                   | 139      | ps                       | 17     |

|                                 | 8 cycles                          | tERR8 <sub>PER</sub>                 | -193    | 193                   | -169  | 169                    | -145                   | 145      | ps                       | 17     |

|                                 | 9 cycles                          | tERR9 <sub>PER</sub>                 | -200    | 200                   | -175  | 175                    | -150                   | 150      | ps                       | 17     |

|                                 | 10 cycles                         | tERR10 <sub>PER</sub>                | -205    | 205                   | -180  | 180                    | -154                   | 154      | ps                       | 17     |

|                                 | 11 cycles                         | tERR11 <sub>PER</sub>                | -210    | 210                   | -184  | 184                    | -158                   | 158      | ps                       | 17     |

|                                 | 12 cycles                         | tERR12 <sub>PER</sub>                | -215    | 215                   | -188  | 188                    | -161                   | 161      | ps                       | 17     |

|                                 | n = 13, 1449,<br>50 cycles        | <sup>t</sup> ERR <i>n</i> per        |         | R <sub>nper</sub> MIN |       |                        |                        |          | ps                       | 17     |

|                                 |                                   |                                      | DQ Inpu | ut Timing             | g     |                        |                        |          |                          |        |

| Data setup time to<br>DQS, DQS# | Base (specifica-tion)             | <sup>t</sup> DS<br>(AC175)           | _       | _                     | _     | _                      | _                      | _        | ps                       | 18, 19 |

|                                 | V <sub>REF</sub> @ 1 V/ns         |                                      | _       | _                     | _     | _                      | _                      | _        | ps                       | 19, 20 |

| Data setup time to DQS, DQS#    | Base (specifica-tion)             | <sup>t</sup> DS<br>(AC150)           | 30      | -                     | 10    | -                      | -                      | _        | ps                       | 18, 19 |

**Table 11: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

|                                              |                                   |                                 | gDDR     | 3-1600    | gDDR3-1800 |      | gDDR3-2000 |      |                          |        |

|----------------------------------------------|-----------------------------------|---------------------------------|----------|-----------|------------|------|------------|------|--------------------------|--------|

| Parameter                                    | arameter                          |                                 | Min      | Max       | Min        | Max  | Min        | Max  | Unit                     | Notes  |

|                                              | V <sub>REF</sub> @ 1 V/ns         |                                 | 180      | _         | 160        | _    | _          | _    | ps                       | 19, 20 |

| Data setup time to<br>DQS, DQS#              | Base (specifica-<br>tion)@ 2 V/ns | <sup>t</sup> DS<br>(AC135)      | -        | -         | -          | -    | 68         | -    | ps                       | 19, 20 |

|                                              | V <sub>REF</sub> @ 2 V/ns         |                                 | _        | _         | _          | _    | 135        | _    | ps                       | 19, 20 |

| Data hold time<br>from DQS, DQS#             | Base (specifica-tion)             | <sup>t</sup> DH<br>(DC100)      | 65       | -         | 45         | _    | 70         | -    | ps                       | 18, 19 |

|                                              | V <sub>REF</sub> @ 1 V/ns         |                                 | 165      | _         | 145        | _    | 120        | _    | ps                       | 19, 20 |

| Minimum data puls                            | e width                           | <sup>t</sup> DIPW               | 400      | _         | 360        | _    | 320        | _    | ps                       | 41     |

|                                              |                                   |                                 | DQ Outp  | ut Timir  | ng         | !    | !          |      |                          | !      |

| DQS, DQS# to DQ sk                           | cew, per access                   | <sup>t</sup> DQSQ               | _        | 125       | _          | 100  | _          | 85   | ps                       |        |

| DQ output hold tim<br>DQS#                   | e from DQS,                       | <sup>t</sup> QH                 | 0.38     | -         | 0.38       | _    | 0.38       | -    | <sup>t</sup> CK<br>(AVG) | 21     |

| DQ Low-Z time fron                           | n CK, CK#                         | tLZ (DQ)                        | -500     | 250       | -450       | 225  | -390       | 195  | ps                       | 22, 23 |

| DQ High-Z time from CK, CK#                  |                                   | <sup>t</sup> HZ (DQ)            | _        | 250       | _          | 225  | _          | 195  | ps                       | 22, 23 |

|                                              |                                   | DQ                              | Strobe   | Input Tir | ning       | !    | !          | '    |                          | !      |

| DQS, DQS# rising to CK, CK# rising           |                                   | <sup>t</sup> DQSS               | -0.25    | 0.25      | -0.27      | 0.27 | -0.27      | 0.27 | CK                       | 25     |

| DQS, DQS# differential input low pulse width |                                   | <sup>t</sup> DQSL               | 0.45     | 0.55      | 0.45       | 0.55 | 0.45       | 0.55 | CK                       |        |

| DQS, DQS# differen pulse width               | tial input high                   | <sup>t</sup> DQSH               | 0.45     | 0.55      | 0.45       | 0.55 | 0.45       | 0.55 | CK                       |        |

| DQS, DQS# falling serising                   | etup to CK, CK#                   | <sup>t</sup> DSS                | 0.2      | -         | 0.18       | _    | 0.18       | _    | CK                       | 25     |

| DQS, DQS# falling h                          | old from CK, CK#                  | <sup>t</sup> DSH                | 0.2      | -         | 0.18       | _    | 0.18       | _    | CK                       | 25     |

| DQS, DQS# differen amble                     | tial WRITE pre-                   | <sup>t</sup> WPRE               | 0.9      | -         | 0.9        | _    | 0.9        | -    | CK                       |        |

| DQS, DQS# differen amble                     | tial WRITE post-                  | tWPST                           | 0.3      | _         | 0.3        | _    | 0.3        | -    | CK                       |        |

|                                              |                                   | DQ                              | Strobe C | utput Ti  | ming       |      | •          | •    | •                        | •      |

| DQS, DQS# rising to CK#                      | /from rising CK,                  | <sup>t</sup> DQSCK              | -255     | 255       | -225       | 225  | -195       | 195  | ps                       | 23     |

| DQS, DQS# rising to CK# when DLL is dis      | •                                 | <sup>t</sup> DQSCK<br>(DLL_DIS) | 1        | 10        | 1          | 10   | 1          | 10   | ns                       | 26     |

| DQS, DQS# differen                           | tial output high                  | <sup>t</sup> QSH                | 0.40     | -         | 0.40       | -    | 0.40       | -    | CK                       | 21     |

| DQS, DQS# differen<br>time                   | tial output low                   | <sup>t</sup> QSL                | 0.40     | -         | 0.40       | -    | 0.40       | -    | CK                       | 21     |

| DQS, DQS# Low-Z ti                           | me (RL - 1)                       | tLZ (DQS)                       | -500     | 250       | -450       | 225  | -390       | 195  | ps                       | 22, 23 |

| DQS, DQS# High-Z t                           | ime (RL + BL/2)                   | tHZ (DQS)                       | _        | 250       | _          | 225  | _          | 195  | ps                       | 22, 23 |

#### **Table 11: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

| Notes 1–8 apply to t                                                    | Critic table              |                            | qDDR                                     | 3-1600                | qDDR      | 3-1800                | qDDR       | 3-2000              |      |               |

|-------------------------------------------------------------------------|---------------------------|----------------------------|------------------------------------------|-----------------------|-----------|-----------------------|------------|---------------------|------|---------------|

| Parameter                                                               |                           | Symbol                     | Min                                      | Max                   | Min       | Max                   | Min        | Max                 | Unit | Notes         |

| DQS, DQS# differential READ preamble                                    |                           | <sup>t</sup> RPRE          | 0.9                                      | Note 24               | 0.9       | Note 24               | 0.9        | Note 24             | CK   | 23, 24        |

| DQS, DQS# differen<br>amble                                             | tial READ post-           | <sup>t</sup> RPST          | 0.3                                      | Note 27               | 0.3       | Note 27               | 0.3        | Note 27             | CK   | 23, 27        |

|                                                                         |                           | Comm                       | and and                                  | Address               | Timing    | l                     |            |                     |      |               |

| DLL locking time                                                        |                           | <sup>t</sup> DLLK          | 512                                      | _                     | 512       | _                     | 512        | -                   | CK   | 28            |

| CTRL, CMD, ADDR setup to CK,CK#                                         | Base (specification)      | <sup>t</sup> IS<br>(AC175) | 65                                       | _                     | 45        | -                     | _          | _                   | ps   | 29, 30        |

|                                                                         | V <sub>REF</sub> @ 1 V/ns |                            | 240                                      | _                     | 220       | _                     | _          | _                   | ps   | 20, 30        |

| CTRL, CMD, ADDR setup to CK,CK#                                         | Base (specifica-tion)     | <sup>t</sup> IS<br>(AC150) | 190                                      | _                     | 170       | _                     | _          | _                   | ps   | 29, 30        |

|                                                                         | V <sub>REF</sub> @ 1 V/ns |                            | 340                                      | _                     | 320       | _                     | _          | _                   | ps   | 20, 30        |

| CTRL, CMD, ADDR setup to CK,CK#                                         | Base (specification)      | <sup>t</sup> IS<br>(AC135) | _                                        | _                     | _         | _                     | 65         | -                   | ps   |               |

|                                                                         | V <sub>REF</sub> @ 1 V/ns |                            | _                                        | _                     | _         | _                     | 200        | _                   | ps   |               |

| CTRL, CMD, ADDR setup to CK,CK#                                         | Base (specifica-tion)     | <sup>t</sup> IS<br>(AC125) | -                                        | _                     | -         | _                     | 150        | _                   | ps   |               |

|                                                                         | V <sub>REF</sub> @ 1 V/ns |                            | _                                        | _                     | _         | _                     | 275        | _                   | ps   |               |

| CTRL, CMD, ADDR<br>hold from CK,CK#                                     | Base (specifica-tion)     | <sup>t</sup> IH<br>(DC100) | 140                                      | _                     | 120       | _                     | 100        | _                   | ps   | 29, 30        |

|                                                                         | V <sub>REF</sub> @ 1 V/ns |                            | 240                                      | _                     | 220       | _                     | 200        | _                   | ps   | 20, 30        |

| Minimum CTRL, CM width                                                  | D, ADDR pulse             | <sup>t</sup> IPW           | 620                                      | _                     | 560       | -                     | 535        | -                   | ps   | 41            |

| ACTIVATE to internated                                                  | al READ or WRITE          | <sup>t</sup> RCD           | See                                      | correspo              | nding sp  | eed bin to            | able for 1 | RCD                 | ns   | 31            |

| PRECHARGE comma                                                         | and period                | <sup>t</sup> RP            | Se                                       | e corresp             | onding s  | peed bin t            | table for  | <sup>t</sup> RP     | ns   | 31            |

| ACTIVATE-to-PRECH period                                                | IARGE command             | <sup>t</sup> RAS           | See                                      | e correspo            | nding sp  | eed bin t             | able for   | <sup>t</sup> RAS    | ns   | 31, 32        |

| ACTIVATE-to-ACTIV                                                       | ATE command pe-           | <sup>t</sup> RC            | Se                                       | e correspo            | onding s  | peed bin t            | table for  | <sup>t</sup> RC     | ns   | 31            |

| ACTIVATE-to-ACTIV                                                       |                           | <sup>t</sup> RRD           |                                          | reater of<br>or 7.5ns |           | reater of<br>or 7.5ns |            | reater of<br>or 6ns | CK   | 31            |

| Four ACTIVATE windows                                                   |                           | <sup>t</sup> FAW           | 45                                       | _                     | 40        | _                     | 35         | _                   | ns   | 31            |

| Write recovery time                                                     |                           | <sup>t</sup> WR            | 15                                       | N/A                   | 15        | N/A                   | 15         | N/A                 | ns   | 31, 32,<br>33 |

| Delay from start of internal WRITE transaction to internal READ command |                           | <sup>t</sup> WTR           | MIN = greater of 4CK or 7.5ns; MAX = N/A |                       |           |                       |            |                     | CK   | 31, 34        |

| READ-to-PRECHARG                                                        | GE time                   | tRTP                       | М                                        | IN = great            | er of 4CI | K or 7.5ns            | ; MAX =    | N/A                 | CK   | 31, 32        |

|                                                                         |                           |                            | <del></del>                              |                       |           |                       |            |                     |      |               |

#### **Table 11: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

|                                                                 | gDDR3-1600 gDDR3-1800 gDI    |                                                        | gDDR                                        | 3-2000    |                                    |            |          |     |      |       |

|-----------------------------------------------------------------|------------------------------|--------------------------------------------------------|---------------------------------------------|-----------|------------------------------------|------------|----------|-----|------|-------|

| Parameter                                                       |                              | Symbol                                                 | Min                                         | Max       | Min                                | Max        | Min      | Max | Unit | Notes |

| CAS#-to-CAS# comm                                               | nand delay                   | <sup>t</sup> CCD                                       |                                             | М         | IN = 4CK;                          | MAX = N    | I/A      | •   | CK   |       |

| Auto precharge write charge time                                | te recovery + pre-           | <sup>t</sup> DAL                                       | Ŋ                                           | MIN = WR  | + <sup>t</sup> RP/ <sup>t</sup> Cl | ( (AVG); I | MAX = N/ | Ά   | CK   |       |

| MODE REGISTER SET                                               | <sup>t</sup> MRD             |                                                        | М                                           | IN = 4CK; | MAX = N                            | I/A        |          | CK  |      |       |

| MODE REGISTER SET                                               | Γ command up-                | tMOD                                                   | MI                                          | N = great | er of 12C                          | K or 15ns  | ; MAX =  | N/A | CK   |       |

| MULTIPURPOSE REG<br>end to mode registe<br>purpose register exi | er set for multi-            | <sup>t</sup> MPRR                                      |                                             | М         | IN = 1CK;                          | MAX = N    | I/A      |     | CK   |       |

|                                                                 |                              | (                                                      | Calibrati                                   | on Timir  | ng                                 |            |          |     |      |       |

| ZQCL command:<br>Long calibration                               | POWER-UP and RESET operation | <sup>t</sup> ZQ <sub>INIT</sub>                        | 512                                         | _         | 512                                | _          | 512      | _   | CK   |       |

| time                                                            | Normal opera-<br>tion        | <sup>t</sup> ZQ <sub>OPER</sub>                        | 256                                         | _         | 256                                | _          | 256      | _   | CK   |       |

| ZQCS command: Sho<br>time                                       | <sup>t</sup> ZQCS            | 64                                                     | _                                           | 64        | _                                  | 64         | _        | CK  |      |       |

|                                                                 | ,                            | Initiali                                               | zation a                                    | nd Reset  | t Timing                           | !          | !        | '   | •    | !     |

| Exit reset from CKE command                                     | <sup>t</sup> XPR             | MIN = greater of 5CK or ${}^{t}$ RFC + 10ns; MAX = N/A |                                             |           |                                    |            |          | CK  |      |       |

| Begin power supply supplies stable                              | ramp to power                | <sup>t</sup> VDDPR                                     | MIN = N/A; MAX = 200                        |           |                                    |            |          |     | ms   |       |

| RESET# LOW to pow                                               | ver supplies stable          | <sup>t</sup> RPS                                       |                                             | Ŋ         | MIN = 0; 1                         | MAX = 20   | 0        |     | ms   |       |

| RESET# LOW to I/O a                                             | and R <sub>TT</sub> High-Z   | <sup>t</sup> IOZ                                       |                                             | N         | IIN = N/A                          | ; MAX = 2  | 20       |     | ns   | 35    |

|                                                                 |                              |                                                        | Refres                                      | h Timing  |                                    |            |          |     | •    | •     |

| REFRESH-to-ACTIVAT<br>command period                            | TE or REFRESH                | <sup>t</sup> RFC                                       |                                             | MIN       | N = 160; N                         | ЛАX = 70,  | ,200     |     | ns   |       |

| Maximum refresh                                                 | T <sub>C</sub> ≤ 85°C        | -                                                      |                                             |           | 64                                 | (1X)       |          |     | ms   | 36    |

| period                                                          | T <sub>C</sub> > 85°C        |                                                        |                                             |           | 32                                 | (2X)       |          |     | ms   | 36    |

| Maximum average                                                 | T <sub>C</sub> ≤ 85°C        | <sup>t</sup> REFI                                      |                                             |           | 7.8 (64r                           | ns/8192)   |          |     | μs   | 36    |

| periodic refresh                                                | T <sub>C</sub> > 85°C        |                                                        |                                             |           | 3.9 (32r                           | ns/8192)   |          |     | μs   | 36    |

|                                                                 |                              | 9                                                      | elf Refr                                    | esh Timi  | ng                                 |            |          |     |      |       |

| Exit self refresh to conquiring a locked DLI                    | <sup>t</sup> XS              | MIN = greater of 5CK or ${}^{t}RFC + 10ns$ ; MAX = N/A |                                             |           |                                    |            |          | CK  |      |       |

| Exit self refresh to coing a locked DLL                         | ommands requir-              | <sup>t</sup> XSDLL                                     | MIN = <sup>t</sup> DLLK (MIN);<br>MAX = N/A |           |                                    |            |          |     | CK   | 28    |

| Minimum CKE low p<br>self refresh entry to<br>timing            |                              | <sup>t</sup> CKESR                                     | $MIN = {}^{t}CKE (MIN) + CK; MAX = N/A$     |           |                                    |            |          |     | CK   |       |

#### **Table 11: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)**

| Notes 1–8 apply to the                                   | ne entire table                                                                                                                                   |                        |                                           | <b>5</b> 4455                                                |                      |                     |         |                 |      |       |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------|--------------------------------------------------------------|----------------------|---------------------|---------|-----------------|------|-------|

|                                                          |                                                                                                                                                   |                        |                                           | 3-1600                                                       |                      | 3-1800              |         | 3-2000          |      |       |

| Parameter                                                |                                                                                                                                                   | Symbol                 | Min                                       | Max                                                          | Min                  | Max                 | Min     | Max             | Unit | Notes |

| Valid clocks after sell power-down entry                 | f refresh entry or                                                                                                                                | <sup>t</sup> CKSRE     | M                                         | MIN = greater of 5CK or 10ns; MAX = N/A                      |                      |                     |         |                 | CK   |       |

| Valid clocks before s<br>power-down exit, o              | •                                                                                                                                                 | <sup>t</sup> CKSRX     | М                                         | IN = grea                                                    | ter of 5Cl           | or 10ns;            | MAX = N | N/A             | CK   |       |

|                                                          |                                                                                                                                                   | P                      | ower-Do                                   | own Timi                                                     | ing                  |                     |         |                 |      | ·     |

| CKE MIN pulse widt                                       | h                                                                                                                                                 | <sup>t</sup> CKE (MIN) |                                           | r of 3CK<br>625ns                                            |                      | of 3CK<br>5ns       |         | r of 3CK<br>5ns | CK   |       |

| Command pass disal                                       | ole delay                                                                                                                                         | <sup>t</sup> CPDED     |                                           |                                                              | = 1;<br>= N/A        |                     |         | = 2;<br>= N/A   | CK   |       |

| Power-down entry texit timing                            | o power-down                                                                                                                                      | <sup>t</sup> PD        |                                           | MIN = <sup>t</sup> CKE (MIN);<br>MAX = 9 × <sup>t</sup> REFI |                      |                     |         |                 | CK   |       |

| Begin power-down<br>CKE registered HIGH                  | er-down period prior to tANPD WL - 1CK                                                                                                            |                        |                                           |                                                              |                      |                     | CK      |                 |      |       |

|                                                          | down entry period: ODT ei-<br>nchronous or asynchronous PDE Greater of <sup>t</sup> ANPD or <sup>t</sup> RFC - REFRESH command to CKE<br>LOW time |                        |                                           |                                                              |                      |                     | CK      |                 |      |       |

| Power-down exit pe<br>synchronous or asyn                |                                                                                                                                                   | PDX                    |                                           | <sup>t</sup> ANPD + <sup>t</sup> XPDLL                       |                      |                     |         |                 |      |       |

|                                                          |                                                                                                                                                   | Power-Do               | wn Ent                                    | ry Minim                                                     | um Timi              | ng                  |         |                 |      | !     |

| ACTIVATE command entry                                   | l to power-down                                                                                                                                   | <sup>t</sup> ACTPDEN   |                                           | MIN                                                          | I = 1                |                     | MIN     | I = 2           | CK   |       |

| PRECHARGE/PRECHA                                         |                                                                                                                                                   | <sup>t</sup> PRPDEN    | MIN = 1                                   |                                                              |                      | MIN = 2             |         | CK              |      |       |

| REFRESH command entry                                    | to power-down                                                                                                                                     | <sup>t</sup> REFPDEN   |                                           | MIN                                                          | l = 1                |                     | MIN     | I = 2           | CK   | 37    |

| MRS command to po                                        | ower-down entry                                                                                                                                   | <sup>t</sup> MRSPDEN   |                                           |                                                              | MIN = <sup>t</sup> M | OD (MIN             | )       |                 | CK   |       |

| READ/READ with au                                        |                                                                                                                                                   | <sup>t</sup> RDPDEN    |                                           |                                                              | MIN = R              | L + 4 + 1           |         |                 | CK   |       |

| WRITE command to power-down entry                        | BL8 (OTF, MRS)<br>BC4OTF                                                                                                                          | <sup>t</sup> WRPDEN    |                                           |                                                              |                      | VL + 4 +<br>< (AVG) |         |                 | CK   |       |

|                                                          | BC4MRS                                                                                                                                            | <sup>t</sup> WRPDEN    |                                           |                                                              |                      | VL + 2 +<br>< (AVG) |         |                 | CK   |       |

| WRITE with auto precharge com-                           |                                                                                                                                                   |                        |                                           | M                                                            | IN = WL +            | 4 + WR -            | + 1     |                 | CK   |       |

| mand to power-<br>down entry                             | tWRAPDEN                                                                                                                                          | MIN = WL + 2 + WR + 1  |                                           |                                                              |                      |                     | CK      |                 |      |       |

|                                                          |                                                                                                                                                   | Pov                    | ver-Dow                                   | n Exit Ti                                                    | ming                 |                     |         |                 |      |       |

| DLL on, any valid co<br>off to commands no<br>locked DLL | <sup>t</sup> XP                                                                                                                                   |                        | MIN = greater of 3CK or 6ns;<br>MAX = N/A |                                                              |                      |                     |         | CK              |      |       |

#### Table 11: Electrical Characteristics and AC Operating Conditions for Speed Extensions (Continued)

| Notes 1–8 apply to the entire table                                                  | gDDR3-1600 gDDR3-1800 gDDR3-2000 |                    |           |                                   |          |      |     |      |        |

|--------------------------------------------------------------------------------------|----------------------------------|--------------------|-----------|-----------------------------------|----------|------|-----|------|--------|

| Parameter                                                                            | Symbol                           | Min                | Max       | Min                               | Max      |      |     | Unit | Notes  |

| Precharge power-down with DLL off to commands requiring a locked DLL                 | tXPDLL                           |                    |           | reater of 10CK or 24ns; MAX = N/A |          |      |     |      | 28     |

|                                                                                      |                                  | ODT                | Timing    |                                   |          |      |     |      |        |

| R <sub>TT</sub> synchronous turn-on delay                                            | ODTL on                          |                    |           |                                   | CK       | 38   |     |      |        |