# **Technical Note**

## Transitioning Designs From DDR3 8Gb SDP 1CS to 8Gb DDP 1CS

### Introduction

This technical note explains how to migrate a PCB design that uses a Micron 8Gb DDR3L product from a 90 series single-die 96-ball package to a 100 series dual-die 96-ball package.

For complete specifications, see the data sheet for each device. This technical note does not include memory controller firmware changes required to move from the single-die package (SDP) to the dual-die package (DDP). Customers are advised to resimulate the system for signal integrity (SI) confirmation.

The following table shows the single-die and dual-die part numbers and essential differences between the devices.

|                     | Device                |                                               |  |  |  |

|---------------------|-----------------------|-----------------------------------------------|--|--|--|

| Architecture        | MT41K512M16HA (SDP)   | MT41K512M16VRN (DDP),<br>MT41K512M16VRP (DDP) |  |  |  |

| Die configuration   | 64 Meg x 16 x 8 banks | 64 Meg x 8 x 8 banks                          |  |  |  |

| Density per package | 8Gb                   | 8Gb                                           |  |  |  |

| Die per package     | 1                     | 2                                             |  |  |  |

| Ranks (CS_n)        | 1                     | 1                                             |  |  |  |

| Refresh count       | 8K                    | 8K                                            |  |  |  |

| Row address         | A[15:0]               | A[15:0]                                       |  |  |  |

| Bank address        | BA[2:0]               | BA[2:0]                                       |  |  |  |

| Column address      | A[9:0]                | A[9:0]                                        |  |  |  |

| Page size/die       | 2КВ                   | 1KB                                           |  |  |  |

#### **Table 1: DDR3L Device Details**

#### **Ball Assignments**

Ballout and assignments are the same for the 8Gb DDR3L SDP and DDP devices; however, when replacing an SDP device with a DDP device on the same system board, we recommend resimulating the system and verifying all termination settings and values. A system firmware change to adjust the controller and DRAM DQ/DQS drive strength may be required depending on system SI simulation results.

For information on how to help verify these design changes and confirm SI, see Micron technical notes TN-41-13: Point to Point Design Support and TN-52-02: Point-to-Point System Design Layout and Routing Tips.

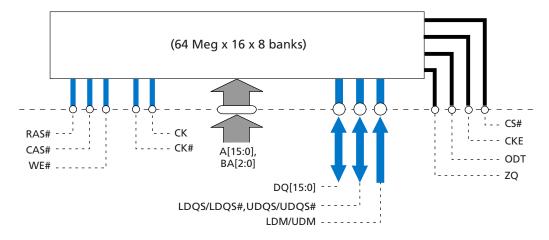

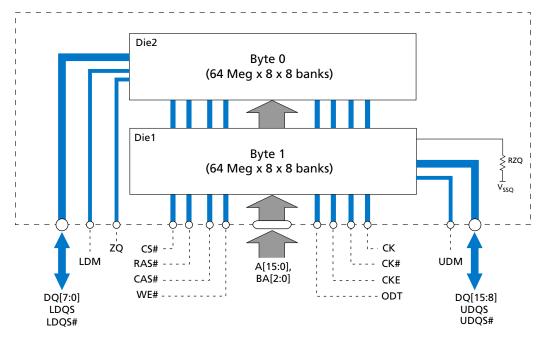

## **Block Diagrams**

The block diagrams for the 8Gb DDR3L SDP and the DDP devices are shown in the figures below. Note that the DDP package has one internal RZQ resister and one ZQ pin out. External ballouts for both the SDP and DDP packages are the same.

Figure 1: Functional Block Diagram for 8Gb 1CS SDP (64 Meg x 16 x 8 Banks)

#### Figure 2: Functional Block Diagram for 8Gb 1CS DDP (2 x 64 Meg x 8 x 8 Banks)

## **Package Dimensions**

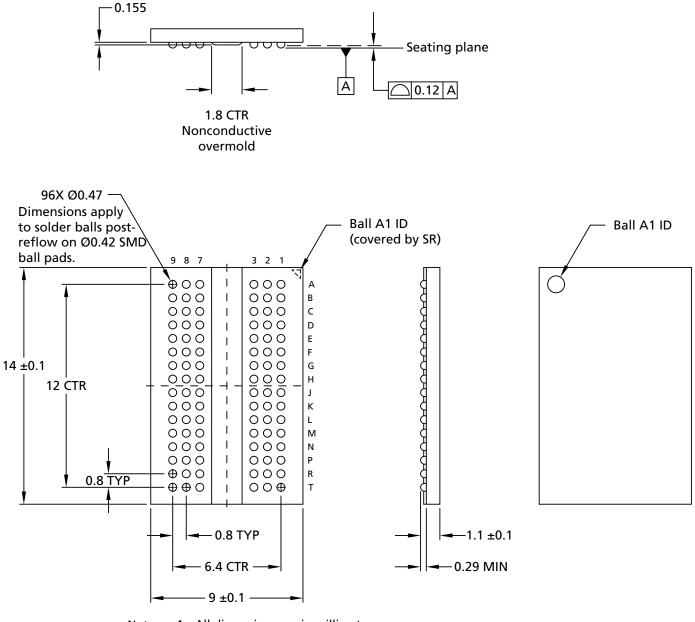

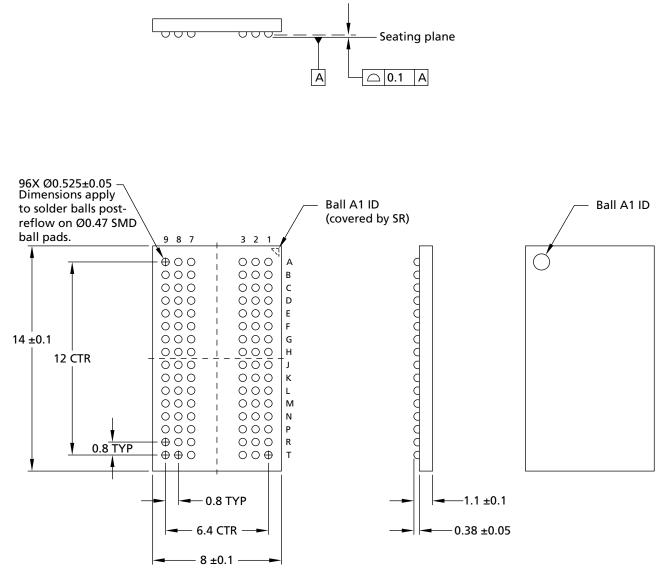

The package dimensions for the 8Gb DDR3L SDP and DDP devices are showed in the following figures, and the differences are summarized in the following table. The ball size increase for the DDP device is required to meet automotive solder join reliability (SJR) requirements. See Micron's customer service note CSN-33, a general BGA manufacturer's user guide, for information on how to easily integrate both leading-edge and legacy Micron ball grid array (BGA) packages into your manufacturing processes.

#### **Table 2: Package Dimension Comparison**

|                       | Package (unit mm) |                         |  |  |  |

|-----------------------|-------------------|-------------------------|--|--|--|

| Package Code          | HA (SDP)          | VRN (DDP) and VRP (DDP) |  |  |  |

| Dimension             | 9 x 14            | 8 x 14                  |  |  |  |

| Thickness (with ball) | 1.1 ±0.1          | 1.1 ±0.1                |  |  |  |

| Solder ball           | 96 x Ø0.47        | 96 x Ø0.525 ±0.05       |  |  |  |

| SMD ball pad          | Ø0.42             | Ø0.47                   |  |  |  |

| Ball height           | 0.29 MIN          | 0.381 ±0.05             |  |  |  |

#### Figure 3: 8Gb SDP 96-Ball FBGA - x16 (HA)

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SAC302 (96.8% Sn, 3% Ag, 0.2% Cu).

#### Figure 4: 8Gb DDP 96-Ball FBGA – x16 (VRN, VRP)

Notes: 1. All dimensions are in millimeters

- 2. VRN material composition: Pb-free SAC302 (96.8% Sn, 3% Ag, 0.2% Cu)

- 3. VRP material composition: Pb-free SAC Q (92.45% Sn, 4% Ag, 0.5% Cu, 3% Bi, 0.05%)

## **Electrical Specifications**

The differences in thermal impedance, input/output capacitance and electrical specifications between the 8Gb DDR3 SDP and DDP devices are shown in the respective device data sheets. However, when migrating from the 8Gb DDR3L SDP device to the DDP device there are timing changes that should be noted. These changes are shown in the following tables.

#### **DDR3L 8Gb Timing Changes**

#### Table 3: Configurations and Page Size

| Parameter         | 8Gb SDP               | 8Gb DDP              |  |

|-------------------|-----------------------|----------------------|--|

| Die configuration | 64 Meg x 16 x 8 banks | 64 Meg x 8 x 8 banks |  |

| Refresh count     | 8K                    | 8K                   |  |

| Row address       | 64K (A[15:0])         | 64K (A[15:0])        |  |

| Bank address      | 8 (BA[2:0])           | 8 (BA[2:0])          |  |

| Column address    | 1K (A[9:0])           | 1K (A[9:0])          |  |

| Die page size     | 2КВ                   | 1КВ                  |  |

#### **Table 4: Command Timing**

| Parameter                                      | Symphol          | SDP (DDF      | SDP (DDR3L-1866) |               | DDP (DDR3L-1866) |          |

|------------------------------------------------|------------------|---------------|------------------|---------------|------------------|----------|

| Farameter                                      | Symbol           | Min           | Max              | Min           | Max              | Unit     |

| ACTIVATE-to-ACTIVATE<br>minimum command period | <sup>t</sup> RRD | MIN = greater | of 4CK or 6ns    | MIN = greater | of 4CK or 5ns    | CK or ns |

| Four ACTIVATE<br>windows                       | <sup>t</sup> FAW | 35            | _                | 27            | _                | ns       |

#### Table 5: REFRESH Timing

| Parameter                                        | Symbol                 | DDR3 | Unit   |      |

|--------------------------------------------------|------------------------|------|--------|------|

|                                                  |                        | Min  | Max    | Unit |

| REFRESH-to-ACTIVATE or REFRESH<br>command period | <sup>t</sup> RFC – 4Gb | 260  | 70,200 | ns   |

|                                                  | <sup>t</sup> RFC – 8Gb | 350  | 70,200 | ns   |

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000

www.micron.com/products/support Sales inquiries: 800-932-4992

Micron and the Micron logo are trademarks of Micron Technology, Inc.

All other trademarks are the property of their respective owners.

This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein. Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for DRAM category:

Click to view products by Micron manufacturer:

Other Similar products are found below :

CT51264BF160B M366S0924FTS-C7A00 AS4C16M32MD1-5BCN HM514100AZ-80 IS42VM16400M-75BLI K4S560432C-TC75 K4S641632H-UC60 AS4C16M32MD1-5BIN AS4C64M8D1-5TCN ATCA-7360-MEM-4G MN41C4256A-07 IS43LR16800G-6BLI MT48LC8M16A2F4-6A IT:L DEMT46H128M16LFCK6ITA W972GG6KB-25 TR S27KL0641DABHB020 AS4C64M16D1A-6TCN AS4C256M8D2-25BIN AS4C64M8D1-5BCN AS4C128M16MD2-25BCN AS4C8M16D1-5BCN AS4C64M32MD2-25BCN AS4C128M16MD2A-25BIN AS4C64M8D1-5BCN AS4C128M16MD2-25BCN IS43LR16800G-6BL MT52L512M32D2PF-107 WT:B TR W971GG6SB-18 AS4C64M16D3B-12BINTR MT44K16M36RB-125E:A TR MT44K16M36RB-107E:A TR AS4C128M8D2A-25BIN AS4C128M8D2A-25BCN MT40A256M16LY-062E:F NT5AD256M16D4-HR AS4C256M16D3C-93BCN AS4C128M16D3LC-12BIN AS4C128M16D3LC-12BCN AS4C64M32MD1A-5BIN MT40A512M8SA-062E:F TR IS45S32800J-7TLA2 AS4C256M16D3LC-12BCN IS66WVH32M8DALL-166B1LI AS4C16M16SB-6TIN AS4C16M16SB-7TCN K4B2G1646F-BCNB AS4C2M32SA-6TINTR AS4C16M16SB-6BIN MT48LC64M8A2P-75:C TR AS4C512M16D4-75BIN