1

# **3V-5.5V, 3.5A Step Down PWM Switching Regulator**

# **Description**

LX7175 is a step-down PWM Switching Regulator IC with integrated high side P-CH and low side N-CH MOSFETs. The IC operates using a hysteretic control topology with a full load switching frequency of 1.4MHz allowing small output filter components while maintaining excellent dynamic load response.

The operational input voltage range of LX7175 is from 3V to 5.5V and it has two modes of operation selected externally by MODE pin. When MODE pin is high, it operates in continuous PWM operation and when it is tied low, it operates in Power Save Mode (PSM) with automatic transition between PWM and PSM mode depending on the load current. This allows the converter's efficiency to remain high when load current drops.

In the shutdown mode, the IC's current consumption is reduced to less than  $1\mu A$  and the output capacitor is discharged.

Other features of the part are: a) cycle-by-cycle current limit followed by latch off, b) thermal protection with hysteresis, c) internal digital soft start, d) and Power Good function.

### **Features**

- 3.5A Step-down Regulator

- Operational Input Supply Voltage Range: 3V-5.5V

- Integrated PMOS and NMOS

- Load Current from zero to 3.5A

- 1.4MHz Switching Frequency

- SKIP Pulse to Improve Light Load Efficiency

- Open VReg Type 0 LV Compatible

- Input UVLO Protection

- Enable Pin

- Power Good

- Internal Soft-start

- Cycle-by-Cycle Over Current Protection

- Latch Off Operation Under Output Short.

- RoHS Compliant for Pb-free

### **Applications**

- Small Battery Operated Devices

- HDD

- Set-Top Box

- LCD TV's

- Notebook/Netbook

- Routers

- Video Cards

- PC Peripherals

- PoE Powered Devices

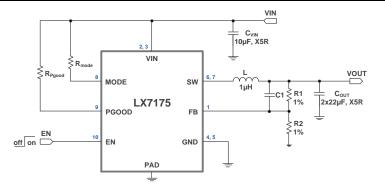

Figure 1 · Typical Application of LX7175

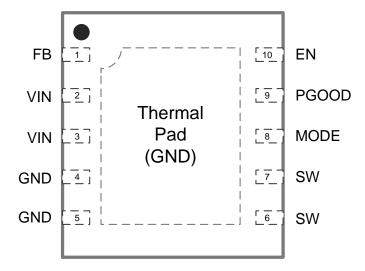

# Pin Configuration and Pinout

Figure 2 · Pinout DFN 3x3 10L Top View

Marking: Line1 7175

Line2 Date / Lot Code

Line3 \* MSC (\* is the pin 1 dot )

# **Ordering Information**

| Ambient<br>Temperature | Туре                  | Package     | Part Number  | Packaging Type |

|------------------------|-----------------------|-------------|--------------|----------------|

| 10°C to 95°C           | RoHS Compliant,       | DFN 3X3 10L | LX7175CLD    | Bulk / Tube    |

| -10 C to 85 C          | -10°C to 85°C Pb-free |             | LX7175CLD-TR | Tape and Reel  |

# Pin Description

| Pin Number | Pin Designator | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | FB             | Voltage feedback pin. Connect to the output terminal through a resistor divider network to set the output voltage of the regulator to the desired voltage.                                                                                                                                                                                                                                                                                                                                             |

| 2, 3       | VIN            | Input voltage terminal of the regulator. A minimum of 10µF, X5R type ceramic capacitor must be connected as close as possible from this pin to GND plane to insure proper operation.                                                                                                                                                                                                                                                                                                                   |

| 4, 5       | GND            | Ground pins for the power stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6, 7       | SW             | Switch-node pin. Connect the output inductor between this pin and output capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8          | MODE           | When this pin is connected to GND, the chip will go into variable frequency hysteretic mode that gradually reduces switching frequency as the load is reduced. When it is connected to VIN, it operates in constant frequency hysteretic mode, and will remain in continuous conduction mode. In this mode the low side MOSFET is not turned off when the current in the inductor reverses direction to pull current from the load.                                                                    |

| 9          | PGOOD          | Power-good pin. This is an open-drain output and should be connected to a voltage rail (for example, VIN) with an external pull-up resistor. During the power on sequence, this pin switches from Low to High state when the FB voltage exceeds the power good threshold and the internal soft start has finished its operation. It will be pulled low, when the FB falls below the power good threshold minus the hysteresis. It will turn back on, when the pull FB rises again above the threshold. |

| 10         | EN             | Pulling this pin higher than 2V will enable the regulator. When pulled low, the regulator will turn off.                                                                                                                                                                                                                                                                                                                                                                                               |

|            | Thermal PAD    | For good thermal connection, this PAD must be connected using thermal VIAs to the GND plane and to the LAND pattern of the IC.                                                                                                                                                                                                                                                                                                                                                                         |

# **Microsemi**

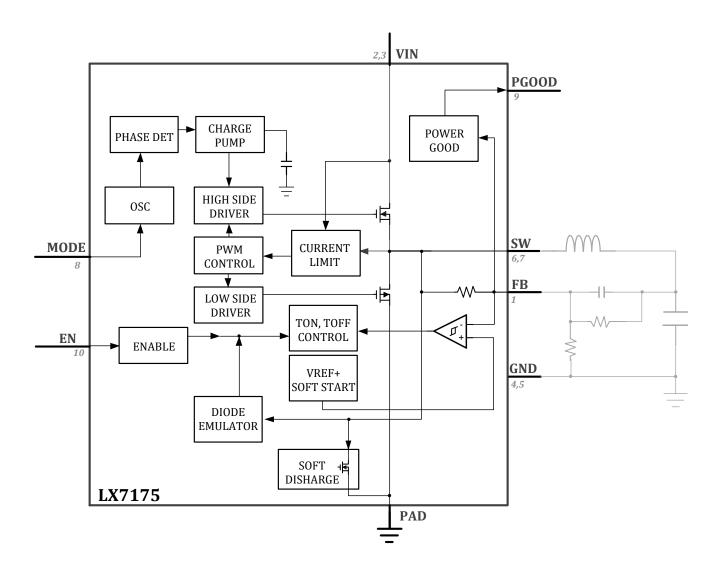

# **Block Diagram**

Figure 3 · Simplified Block Diagram of LX7175

# **Absolute Maximum Ratings**

| Parameter                                            | Min  | Max          | Units |

|------------------------------------------------------|------|--------------|-------|

| VIN, EN, FB, PGOOD, MODE to GND                      | -0.3 | 7            | V     |

| SW to GND                                            | -0.3 | 7            | V     |

| SW to GND (Shorter than 15ns)                        | -4   | 7            | V     |

| Maximum Junction Temperature                         |      | 150          | °C    |

| Storage Temperature                                  | -65  | 150          | °C    |

| Peak Package Solder Reflow Temperature (40s, reflow) |      | 260 (+0, -5) | °C    |

Note: Performance is not necessarily guaranteed over this entire range. These are maximum stress ratings only. Exceeding these ratings, even momentarily, can cause immediate damage, or negatively impact long-term operating reliability

# **Operating Ratings**

|                     | Min | Max | Units |

|---------------------|-----|-----|-------|

| VIN                 | 3.0 | 5.5 | V     |

| V <sub>OUT</sub>    | 0.8 | 3.3 | V     |

| Ambient Temperature | -10 | 85  | °C    |

| Output Current      | 0   | 3.5 | Α     |

# **Thermal Properties**

| Thermal Resistance | Тур  | Units |

|--------------------|------|-------|

| $\theta_{JA}$      | 41.2 | °C/W  |

Note: The  $\theta_{JA}$  number assumes no forced airflow. Junction Temperature is calculated using  $T_J = T_A + (PD \times \theta_{JA})$ . In particular,  $\theta_{JA}$  is a function of the PCB construction. The stated number above is for a four-layer board in accordance with JESD-51 (JEDEC).

### **Electrical Characteristics**

Note: The following specifications apply over the operating ambient temperature of -10°C  $\leq$  T<sub>A</sub>  $\leq$  85°C except where otherwise noted with the following test conditions: 3.0 < VIN < 5.5V. Typical parameters refer to T<sub>J</sub> = 25°C, VIN = 5V.

| Symbol          | Parameter                     | Test Condition                    | Min | Тур | Max | Units |

|-----------------|-------------------------------|-----------------------------------|-----|-----|-----|-------|

| Operating       | g Current                     |                                   |     |     |     |       |

| IQ              | Input Current                 | I <sub>LOAD</sub> = 0, MODE = GND |     | 200 | 500 | μΑ    |

| I <sub>IN</sub> | Input Current at Shut<br>Down | EN = GND, T <sub>A</sub> = 25°C   |     | 0.1 | 1   | μΑ    |

| Symbol              | Parameter                      | Test Condition                                                                                    |                         | Min   | Тур   | Max   | Units     |

|---------------------|--------------------------------|---------------------------------------------------------------------------------------------------|-------------------------|-------|-------|-------|-----------|

| VIN INPU            | T UVLO                         |                                                                                                   |                         |       | ı     | l.    | I.        |

| VIN                 | Under Voltage Lockout          | VIN rising                                                                                        |                         |       | 2.4   | 2.8   | V         |

| V <sub>HYS</sub>    | UVLO Hysteresis                |                                                                                                   |                         |       | 250   |       | mV        |

| FEEDBA              | CK                             |                                                                                                   |                         |       |       | •     |           |

|                     | Feedback Voltage               | T <sub>A</sub> = 25°C                                                                             |                         | 0.788 | 0.800 | 0.812 | V         |

| $V_{REF}$           | Internal Reference             | 0 < T <sub>J</sub> < 125°C                                                                        |                         | 0.782 |       | 0.818 | V         |

| I <sub>FB</sub>     | FB Pin Input Current           |                                                                                                   |                         |       |       | 10    | nA        |

|                     |                                | VIN from 3V to 5.5V, MODE                                                                         | = High,                 |       |       |       |           |

|                     | Line Regulation                | $I_{LOAD} = 0.1A, V_{OUT} = 1V,$                                                                  |                         |       | 0.065 |       | %         |

|                     |                                | $L = 0.68 \mu H, C_{OUT} = 44 \mu F. G$                                                           | BD                      |       |       |       |           |

|                     |                                | VIN = 5V, MODE = High $I_{LOAD} = 0$ to 3.5A,                                                     | V <sub>OUT</sub> = 1V   |       | 0.06  |       | %/A       |

|                     | Load Regulation                | L = $0.68\mu H$ , $C_{OUT} = 44\mu F$ .<br>GBD                                                    | V <sub>OUT</sub> = 3.3V |       | 0.08  |       | 70/71     |

|                     | Load Nogalation                | VIN = 5V, MODE = Low $I_{LOAD}$ = 0.2A to 3.5A,                                                   | V <sub>OUT</sub> = 1V   |       | 0.075 |       | %/A       |

|                     |                                | L = $0.68\mu H$ , $C_{OUT} = 44\mu F$ .<br>GBD                                                    | V <sub>OUT</sub> = 3.3V |       | 0.11  |       | 70/71     |

|                     | Transient Response             | Load from 0.1A to 1.5A, Tr = V <sub>OUT</sub> = 1V, L = 0.68µH, C <sub>OUT</sub> MODE = High. GBD |                         | ±35   |       | mV    |           |

| FB UVLO             |                                |                                                                                                   |                         |       | l     | l .   | I         |

| V <sub>FBULVO</sub> | FB UVLO Threshold              |                                                                                                   |                         |       | 40%   | 50%   | $V_{REF}$ |

| OUTPUT              | DEVICE                         |                                                                                                   |                         |       | l     | l .   | I         |

| R <sub>DSON_H</sub> | R <sub>DSON</sub> of High Side |                                                                                                   |                         |       | 55    | 100   | mΩ        |

| R <sub>DSON_L</sub> | R <sub>DSON</sub> of High Side |                                                                                                   |                         |       | 40    | 65    | mΩ        |

|                     |                                |                                                                                                   | VIN = 5V.               | 4.5   | 5.9   | 7.3   |           |

| l <sub>L</sub>      | Current Limit                  | 0 < TJ< 125°C. GBD                                                                                | VIN = 3V.               | 3.89  | 5.3   | 6.74  | Α         |

| T <sub>SH</sub>     | Thermal Shut Down<br>Threshold | GBD                                                                                               |                         | 140   | 163   | 185   | °C        |

| T <sub>H</sub>      | Hysteresis                     | GBD                                                                                               |                         |       | 27    |       | °C        |

| OSCILLA             | TOR                            |                                                                                                   |                         |       |       |       |           |

| f                   | Switching Frequency            | MODE = High                                                                                       |                         | 1.25  | 1.4   | 1.65  | MHz       |

| F <sub>HYST</sub>   | Switching Frequency            | In Boundary Conduction Mode, In Hysteretic Mode (The PLL is off)                                  |                         | 0.3   | 0.445 | 0.6   | MHz       |

| D <sub>MAX</sub>    | Maximum Duty Cycle             |                                                                                                   | 70                      |       |       | %     |           |

| SOFT ST             | ART                            |                                                                                                   |                         |       |       |       |           |

| T <sub>SS</sub>     | Soft Start Time                | From EN going high to V <sub>OUT</sub> regulation.                                                | reaches                 | 0.8   | 1.4   | 1.8   | ms        |

| Symbol              | Parameter                                    | Test Condition                                                     | Min | Тур  | Max | Units |

|---------------------|----------------------------------------------|--------------------------------------------------------------------|-----|------|-----|-------|

| MODE                |                                              |                                                                    | 1   |      | I   |       |

| M <sub>VIH</sub>    | Input High                                   |                                                                    | 1.1 |      |     | V     |

| M <sub>VIL</sub>    | Input Low                                    |                                                                    |     |      | 0.4 | V     |

| $M_{\text{VIH}}$    | Input Bias                                   |                                                                    |     | 0.01 | 1   | μA    |

| EN INPU             | Т                                            |                                                                    |     |      |     |       |

| $EN_{VIH}$          | Input High                                   |                                                                    | 1.1 |      |     | V     |

| EN <sub>VIL</sub>   | Input Low                                    |                                                                    |     |      | 0.4 | V     |

| EN <sub>H</sub>     | Hysteresis                                   |                                                                    |     | 0.1  |     | V     |

| EN <sub>II</sub>    | Input Bias Current                           |                                                                    |     | 0.01 | 1   | μΑ    |

| POWER-              | GOOD                                         |                                                                    |     |      |     |       |

| $V_{PG}$            | Power-good Transition<br>High Threshold      | $V_{\text{FB}}$ rising, in percentage of output voltage set-point. |     | 83   |     | %     |

| $V_{PGHY}$          | Hysteresis                                   | Either V <sub>FB</sub> rising or falling                           |     | 40   |     | mV    |

| P <sub>GRDSON</sub> | Power-good Internal<br>FET R <sub>DSON</sub> | VIN = 5V, 0 < T <sub>J</sub> < 125°C                               |     |      | 100 | Ω     |

|                     | PGOOD FET Leakage<br>Current                 |                                                                    |     | 0.01 | 1   | μA    |

|                     | PGOOD Internal Glitch<br>Filter              |                                                                    |     | 5    |     | μs    |

| OUTPUT              | DISCHARGE                                    |                                                                    | •   |      |     | •     |

|                     | Internal Discharge<br>Resistor               |                                                                    | 80  | 300  | 600 | Ω     |

| GBD Guar            | anteed by design, not produc                 | tion tested.                                                       | •   | •    |     | •     |

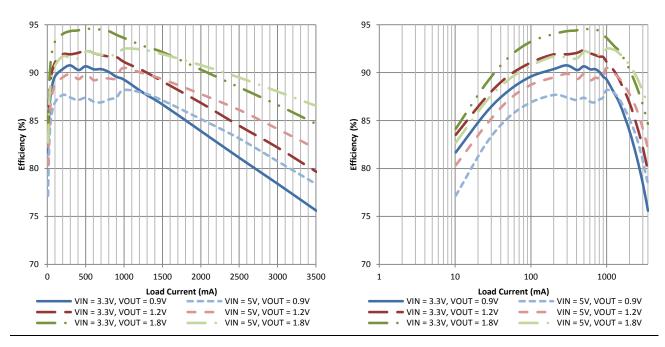

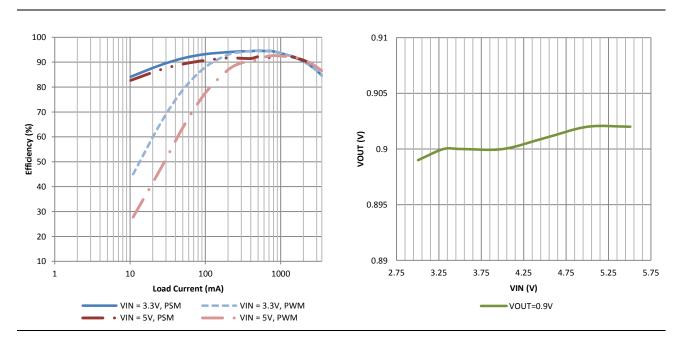

# Typical Performance Curves (Efficiency & Line Regulation)

Figure 4 · PSM Mode Efficiency

Figure 5 · PSM Mode Efficiency in Log Scale

Figure 6 · PSM vs. PWM Efficiency with Vout=1.8V

Figure 7 · Line Regulation  $V_{OUT}$  = 0.9V ( $V_{OUT}$  vs. VIN)

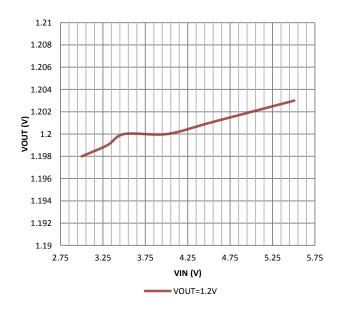

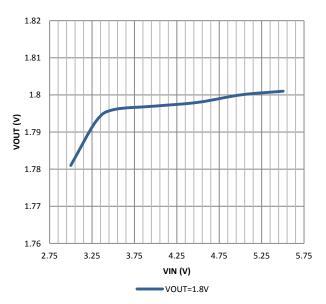

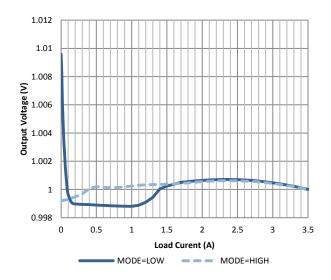

# Typical Performance Curves (Line Regulation & Load Regulation)

Figure 8 · Line Regulation Vout = 1.2V (Vout vs. VIN)

Figure 9 · Line Regulation Vout = 1.8V (Vout vs. VIN)

Figure 10 · Load Regulation VIN = 5V, V<sub>OUT</sub> = 1.0V (V<sub>OUT</sub> vs. Load Current)

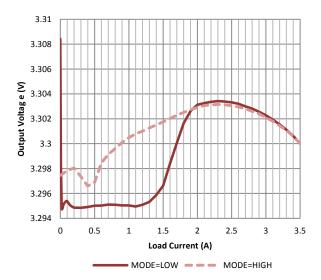

Figure 11 · Load Regulation VIN = 5V, V<sub>OUT</sub> = 3.3V (V<sub>OUT</sub> vs. Load Current)

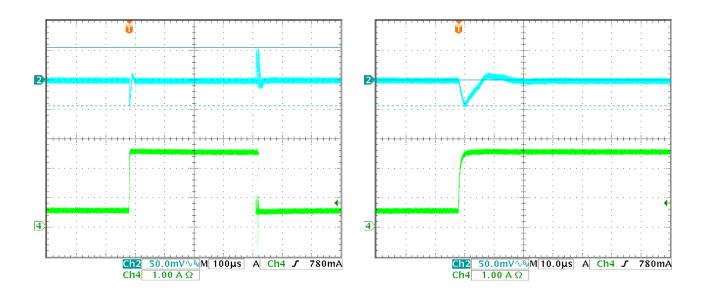

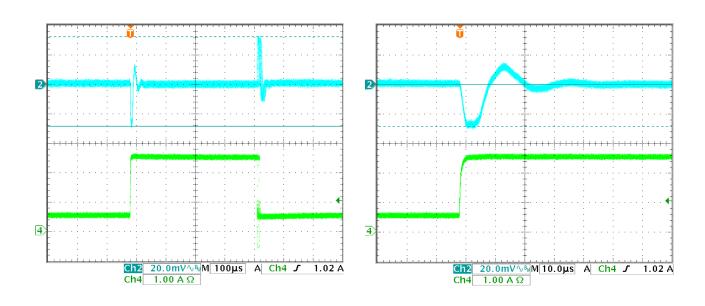

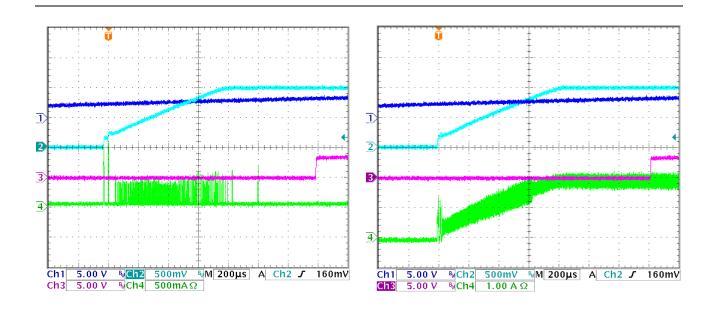

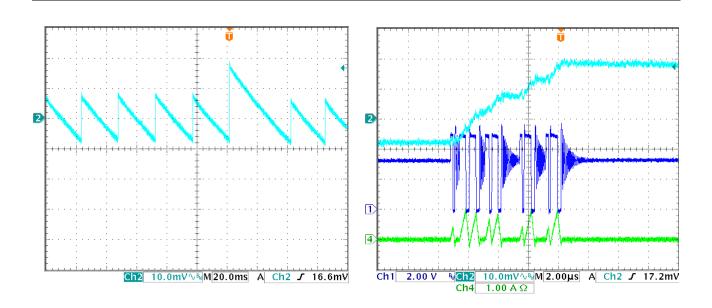

# Typical Performance Curves (Load Transient - VIN = 5V, VOUT = 1V)

Figure 12 · L = 0.68 $\mu$ H, C<sub>OUT</sub>=44 $\mu$ F CH2: V<sub>OUT</sub>, CH4: I<sub>L</sub>

Figure 13 · L = 0.68 $\mu$ H, C<sub>OUT</sub>=44 $\mu$ F, Rising Edge CH2: V<sub>OUT</sub>, CH4: I<sub>L</sub>

Figure 14 · L = 0.68 $\mu$ H, C<sub>OUT</sub>=154 $\mu$ F CH2: V<sub>OUT</sub>, CH4: I<sub>L</sub>

Figure 15 · L = 0.68 $\mu$ H, C<sub>OUT</sub>=154 $\mu$ F Rising Edge CH2: V<sub>OUT</sub>, CH4: I<sub>L</sub>

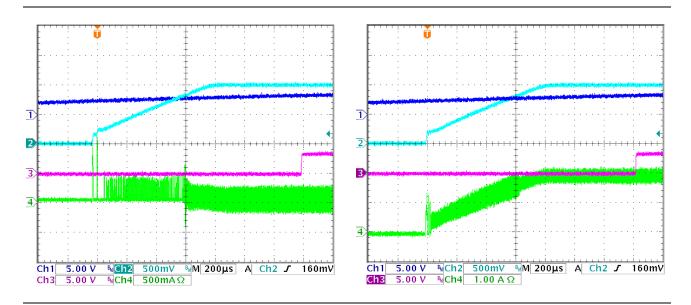

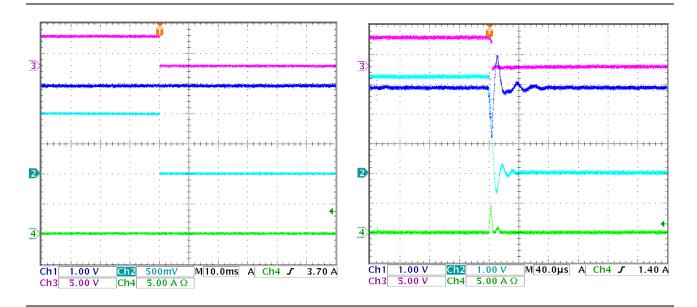

# Typical Performance Curves (Start Up - VIN = 5V, Vout = 1V)

Figure 16  $\cdot$  Power up with no load, MODE = High

CH1: VIN, CH2: VOUT, CH3: PGOOD,

CH4: Inductor Current

Figure 17 · Power up with resistive load, MODE = High

CH1: VIN, CH2: VOUT, CH3: PGOOD,

CH4: Inductor Current

Figure 18 · Power up with no load, MODE = Low

CH1: VIN, CH2: VOUT, CH3: PGOOD,

CH4: Inductor Current

Figure 19 · Power up with resistive load

CH1: VIN, CH2: VOUT, CH3: PGOOD,

CH4: Inductor Current

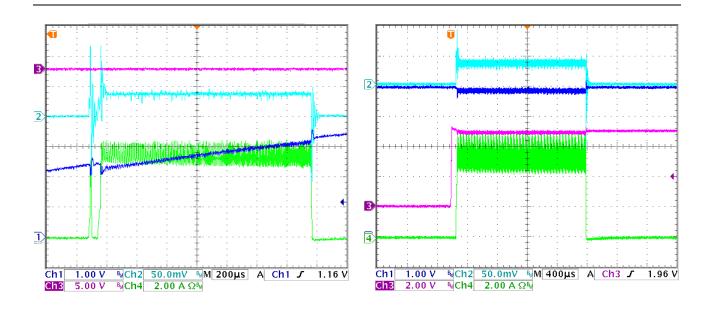

# Typical Performance Curves (Short Condition)

Figure 20 · Output Short 5V input 1V output

CH1: VIN, CH2: VOUT, CH3: PGOOD,

CH4: Inductor Current

Figure 21 · Output Short 5V input 3.3V output

CH1: VIN, CH2: V<sub>OUT</sub>, CH3: PGOOD, CH4: Inductor Current

Figure 22 · Power into Short from VIN, VIN = 5V

CH1: VIN, CH2: VOUT, CH3: PGOOD,

CH4: Inductor Current

Figure  $23 \cdot Power into Short from EN, EN = VIN = 5V$

CH1: VIN, CH2: V<sub>OUT</sub>, CH3: PGOOD,

CH4: Inductor Current

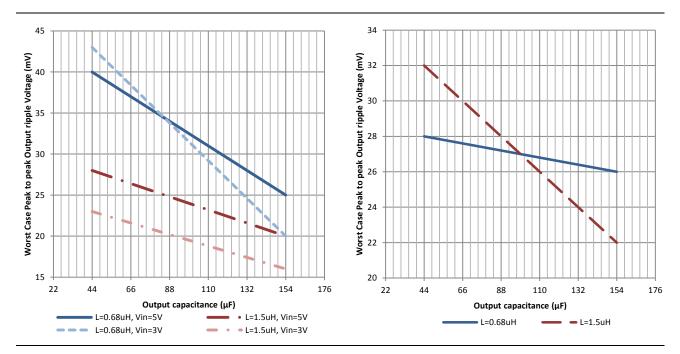

# Typical Performance Curves (Output Voltage Ripple)

Figure 24 · No Load Peak to Peak Output Ripple

$V_{OUT} = 1V$

Figure 25 · No Load Peak to Peak Output Ripple  $VIN = 5V, \ V_{OUT} = 3.3V$

Figure 26 · No Load Peak to Peak Output Ripple

CH2:  $V_{OUT}$ VIN = 5V,  $V_{OUT}$  = 3.3V, L = 0.68 $\mu$ H,  $C_{OUT}$  = 154 $\mu$ F

Figure 27 · Figure 26 Rising Edge Zoom In

CH1: SW, CH2:  $V_{OUT}$ , CH4: Inductor Current VIN = 5V,  $V_{OUT}$  = 3.3V, L = 0.68 $\mu$ H,  $C_{OUT}$  = 154 $\mu$ F

# Theory of Operation / Application Information

### **Basic Operation**

The operation of the controller consists of comparing the  $V_{FB}$  voltage to an internal reference. When the  $V_{FB}$  voltage is lower than the  $V_{REF}$ , the upper switch turns on. When the  $V_{FB}$  voltage is higher than  $V_{REF}$ , the upper switch turns off and the lower switch turns on. An internal ramp and clock signal are used to stabilize the switching frequency and keep the  $V_{FB}$  immune to the output capacitor, Co, value or parasitic components (i.e. ESR, ESL).

### **Setting of the Output Voltage**

The values of R1 and R2 are chosen so according to the following equation:

$$V_{OUT} = \left(\frac{R1}{R2} + 1\right) \times V_{REF}$$

### **Startup**

The reference is ramped up from zero voltage to 0.8V in 1.4ms. During this time, the PGOOD is pulled low. When the reference reaches 0.8V, signaling the end of the soft start cycle, the PGOOD pin will go high within 5µS.

#### **Over Current Protection**

The IC has the ability to protect against all types of short circuit conditions. It has cycle by cycle short protection that turns off the upper MOSFET and ends the cycle when the current exceeds the OCP threshold. When this occurs, the off-time is at least 200ns before the upper FET is turned on again. This will clamp the current at the peak current threshold.

If the load requires more than the peak current threshold, the output voltage will drop since the current is clamped. If the output drops below the feedback UVLO threshold, the device will latch off. The enable pin can be cycled to restart the converter.

During the soft start sequence the current protection mechanism is different. If the peak current threshold is exceeded during soft start, the upper FET is turned off for approximately  $1\mu$ s. After  $1\mu$ s, the upper FET is turned back on. This will limit the peak output current at the peak current threshold. During soft start the feedback UVLO alarm is not active, so in the event of a short, the peak current will continue to trip until the end of the soft start period. After soft start, the feedback UVLO alarm will be active and the latch-off event will occur.

### **Output Component Selection Table**

The table below shows the recommended resistor and feedforward capacitor values for a given output inductor and output capacitor value. See Figure 1 for the schematic location of R1, R2 and C1.

| VIN | V <sub>OUT</sub> | L      | C <sub>OUT</sub>      | R1    | R2    | C1     |

|-----|------------------|--------|-----------------------|-------|-------|--------|

|     |                  | 1.5µH  | 154µF (7x22µF)        |       |       | 180 pF |

|     |                  | 0.68µH | 154με (7ΧΖΖμε)        |       |       | 100 pF |

| 5V  | 1V               | 1.5µH  |                       | 24.9k | 100k  | 68 pF  |

|     |                  | 1μH    | 44μF (2x22μF)         |       |       | 47pF   |

|     |                  | 0.68µH |                       |       |       | 33 pF  |

|     |                  | 1.5µH  | 154uE (7x22uE)        | 100k  |       | 330 pF |

|     |                  | 0.68µH | 154µF (7x22µF)        |       | 32.4k | 220 pF |

| 5V  | 3.3V             | 1.5µH  | 100k<br>44µF (2x22µF) |       |       | 150 pF |

|     |                  | 1μH    |                       |       |       | 120pF  |

|     |                  | 0.68µH |                       |       |       | 100 pF |

| 3V  | 1V               | 1.5µH  | 154µF (7x22µF)        | 24.9k | 100k  | 180pF  |

| 31  | I V              | 1μH    | 44μF (2x22μF)         | 24.9k | 100k  | 47pF   |

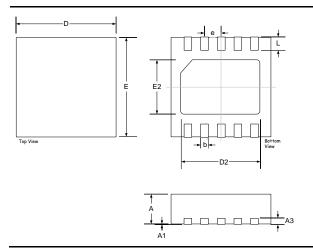

### DFN 3x3 10L PACKAGE OUTLINE DIMENSIONS

| Dim   | MILLIM   | MILLIMETERS |            | HES    |  |

|-------|----------|-------------|------------|--------|--|

| Dilli | MIN      | MAX         | MIN        | MAX    |  |

| Α     | 0.70     | 0.80        | 0.0276     | 0.0315 |  |

| A1    | 0        | 0.05        | 0          | 0.0019 |  |

| А3    | 0.20     | REF         | 0.0079 REF |        |  |

| b     | 0.18     | 0.30        | 0.0071     | 0.0118 |  |

| D     | 3.00 BSC |             | 0.118      | 1 BSC  |  |

| D2    | 2.25     | 2.50        | 0.0886     | 0.0984 |  |

| е     | 0.50 BSC |             | 0.019      | 7 BSC  |  |

| Е     | 3.00     | BSC         | 0.1181 BSC |        |  |

| E2    | 1.50     | 1.75        | 0.0591     | 0.0689 |  |

| L     | 0.30     | 0.50        | 0.0118     | 0.0197 |  |

Figure 28 · Package Dimensions

Note: Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm (.006") on any side. Lead dimension shall not include solder coverage

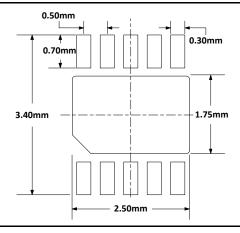

### LAND PATTERN RECOMMENDATION

Figure 29 · Package Footprint

#### Disclaimer

This PCB land pattern recommendation is based on information available to Microsemi by its suppliers. The actual land pattern to be used could be different depending on the materials and processes used in the PCB assembly, end user must account for this in their final layout. Microsemi makes no warranty or representation of performance based on this recommended land pattern.

**PRODUCTION DATA** – Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1(949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2013 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for microsemi manufacturer:

Other Similar products are found below:

APT100GF60JU3 APT2X101DL40J APT2X60D100J APT35GA90BD15 APT36GA60BD15 ARF477FL MT90869AG2 1N5280B

1N5663A 1N5772 1N6317 JAN1N6461 JANTX1N6462US SG2842M 1N6311US 1N6663US APT30M19JVFR Core429-SA M2S025VFG400 AX2000-FG896 JAN2N3439 JANTX1N5651A JANTX1N5804US MSD75-08 SG3524D SM64TQ-ACTEL-1 SM68P-ACTEL

CDLL4625 VSC8514XMK-11 AGL1000V2-CS281I AGL400V2-FGG144 APT50GF120JRDQ3 APT2X100D100J APT10025JVFR

APA300-CQ208B APT8014L2FLLG 1N5711UBD 1N6336US AFS600-FG256I AX500-FGG484I A3PE3000L-1FG896I SG3526BN

BR230-290B2-28V-021M M2S090TS-EVAL-KIT A3P030-QNG68I A2F500M3G-FGG256 JANTX1N827-1 JANTX1N6638U

JANTX1N4104D-1 JANS1N5811US