# M2S090TS-EVAL-KIT SmartFusion2 Security Evaluation Kit

**User Guide**

## **Table of Contents**

| 1 – Introduction                                       | 5   |

|--------------------------------------------------------|-----|

| SmartFusion2 Security Evaluation Kit Contents          | 5   |

| SmartFusion2 Security Evaluation Kit Web Resources     | 5   |

| Board Description                                      |     |

| ·                                                      |     |

| 2 – Installation and Settings                          | 9   |

| Software Settings                                      | 9   |

| Hardware Settings                                      | 9   |

| SmartFusion2 Power Sources                             | 11  |

| 3 – Key Components Description and Operation           | 13  |

| Powering Up the Board                                  |     |

| Current Measurement                                    |     |

| Memory Interface                                       |     |

| SERDES0 Interface                                      |     |

| USB Interface                                          |     |

| Marvell PHY (88E1340S)                                 |     |

| Programming                                            |     |

| FTDI Interface                                         |     |

| I <sup>2</sup> C Port Header                           |     |

| System Reset                                           |     |

| Clock Oscillator                                       |     |

| User Interface                                         | 23  |

| GPIO Header Pin Out                                    |     |

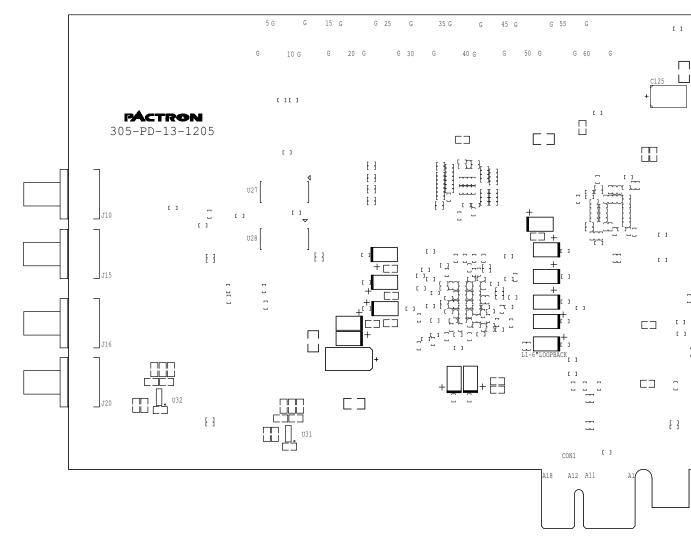

| 4. Phyline                                             | 0.7 |

| 4 – Pin List                                           | 27  |

| 5 - Board Components Placement                         | 41  |

| 6 - Demo Design                                        | 45  |

| M2S090TS-EVAL-KIT Board Demo Design                    |     |

| 7 Menufacturing Test                                   | 47  |

| 7 – Manufacturing Test                                 |     |

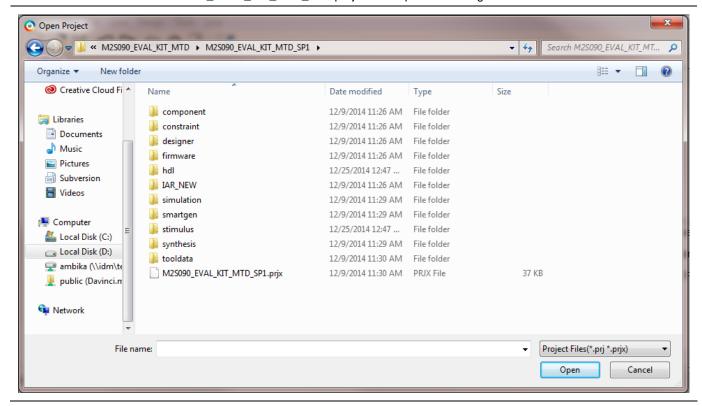

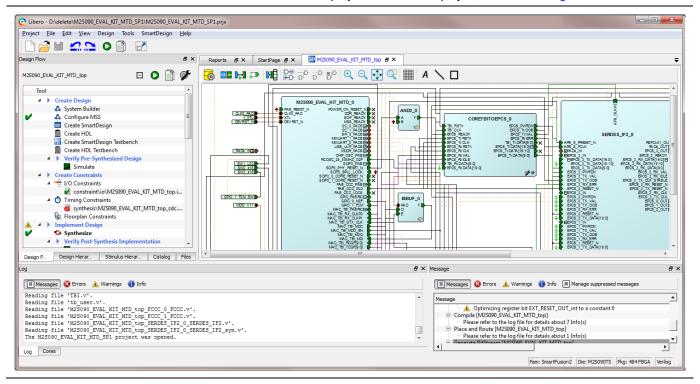

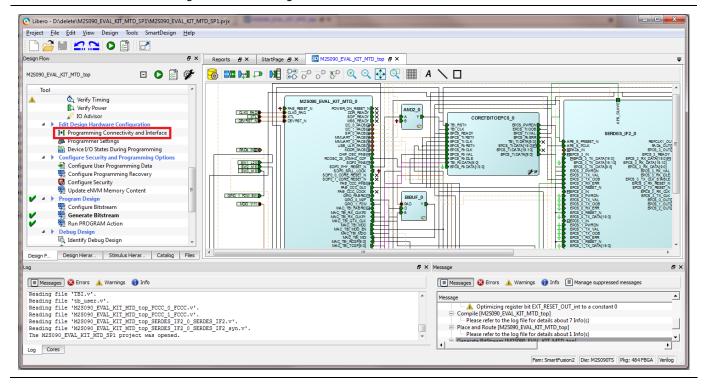

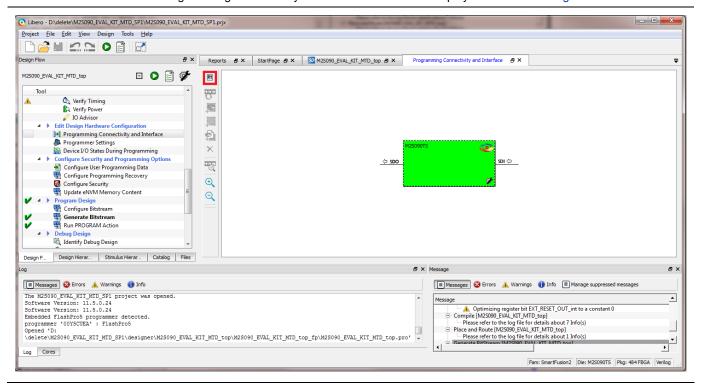

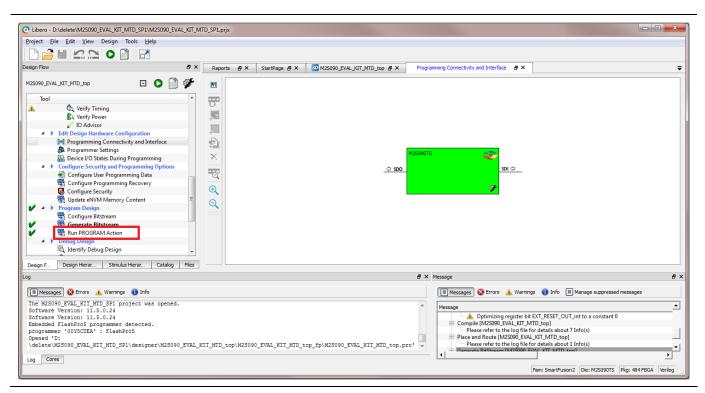

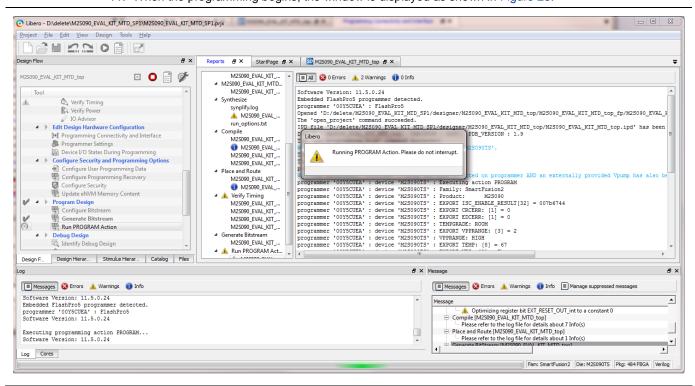

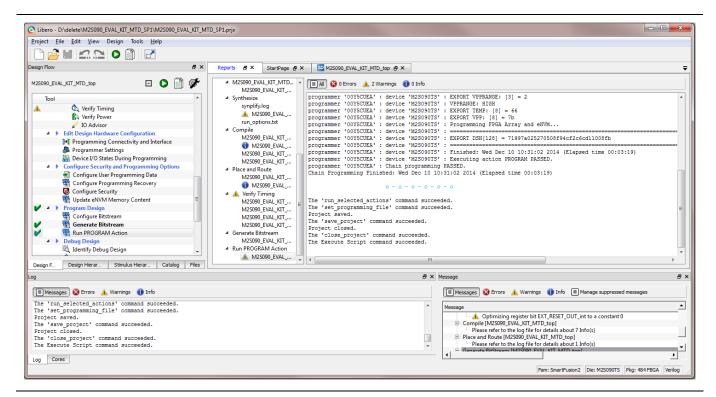

| Programming M2S090TS-EVAL-KIT                          |     |

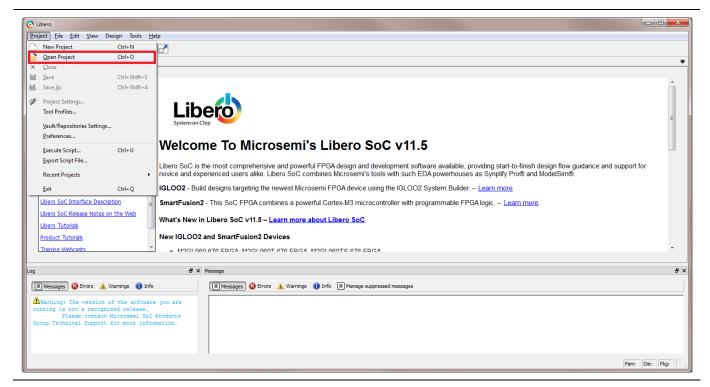

| Installing Libero v11.5 or Later                       |     |

| Power Supply Validation                                |     |

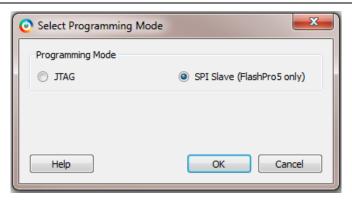

| SPI Slave Programming (FlashPro5) on M2S090TS EVAL KIT |     |

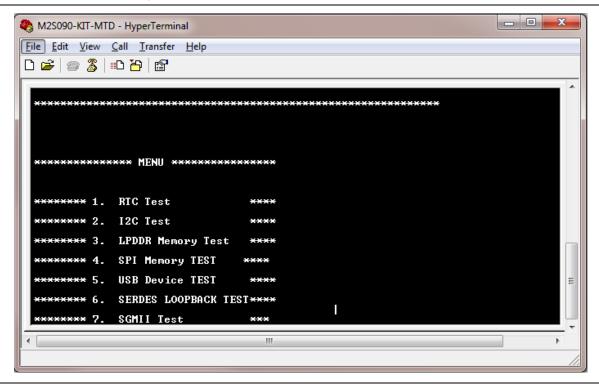

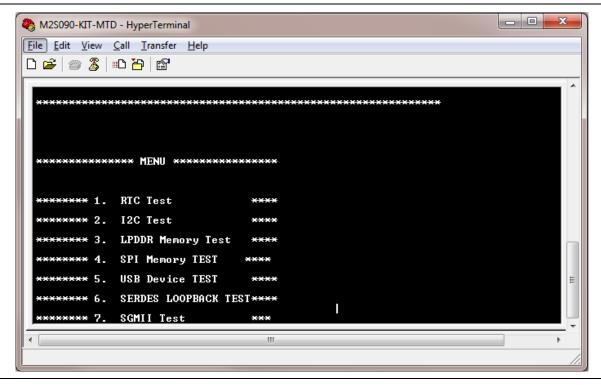

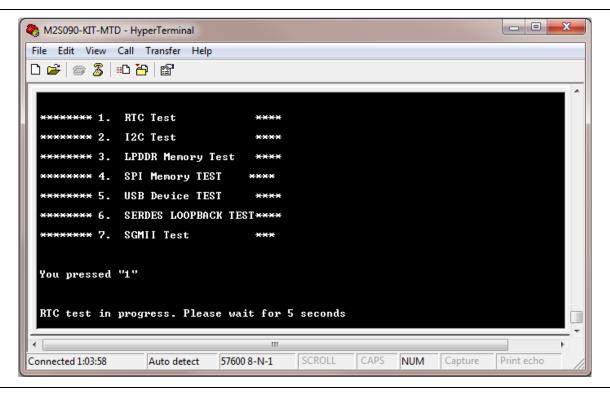

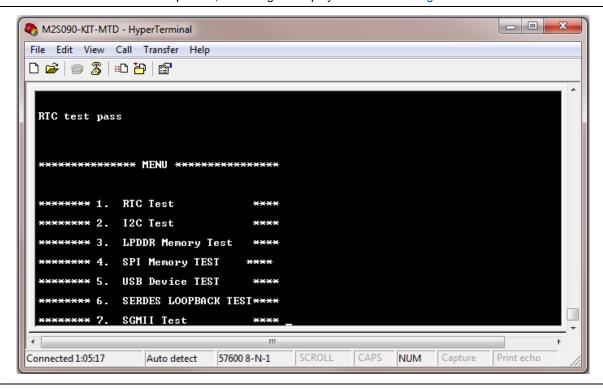

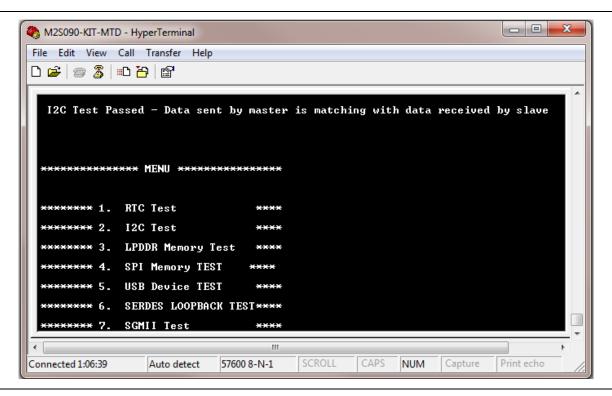

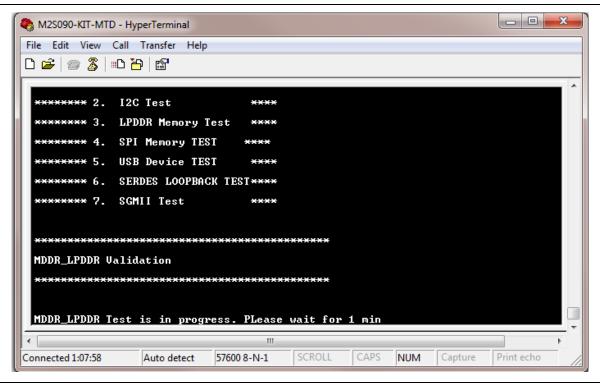

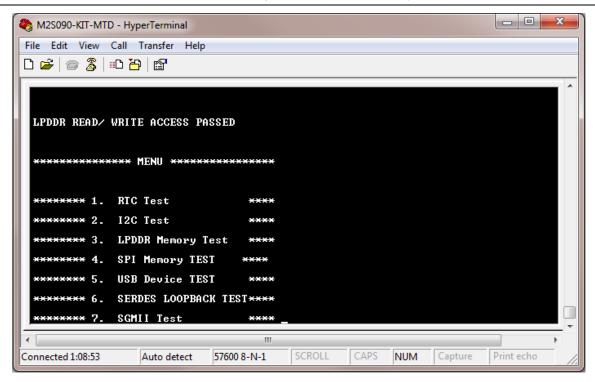

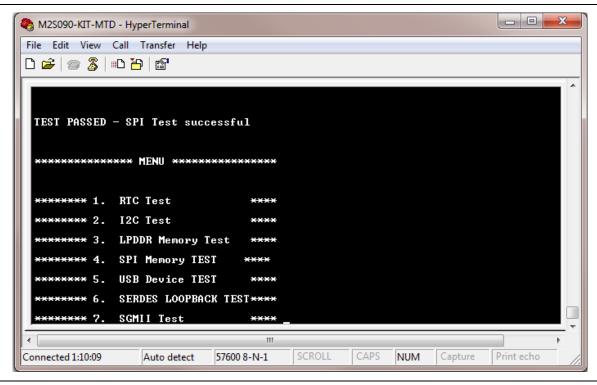

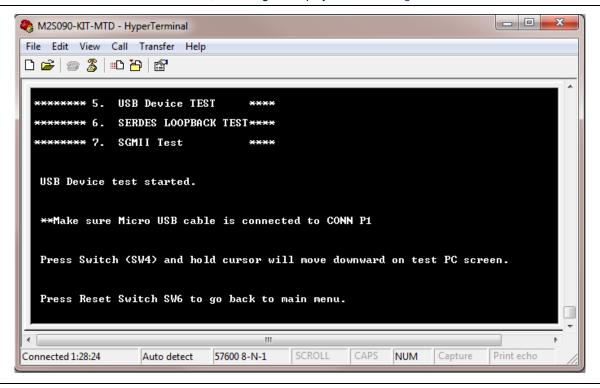

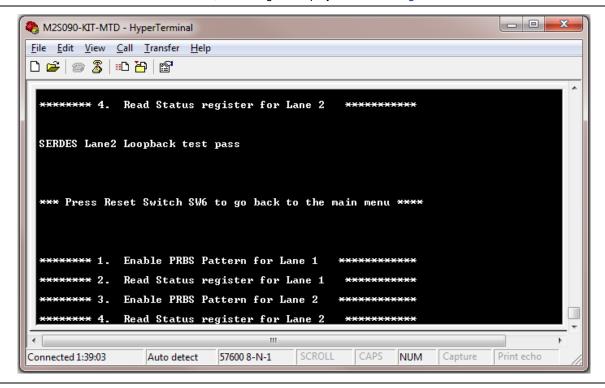

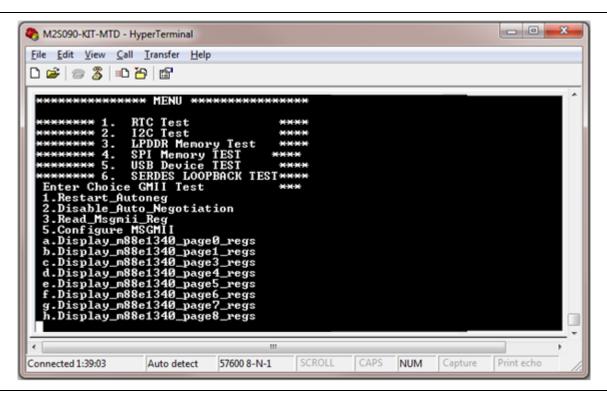

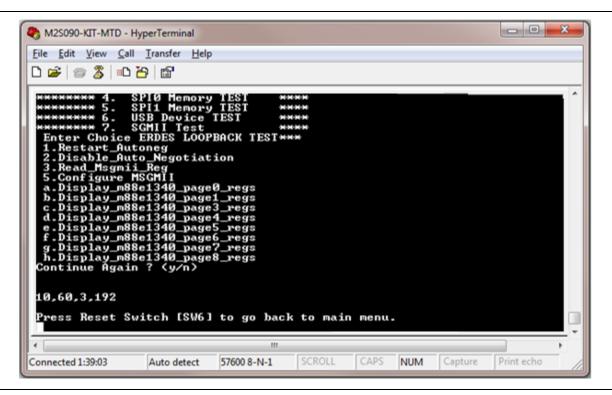

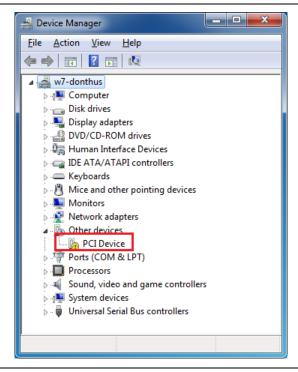

| Running the Manufacturing Test                         | 53  |

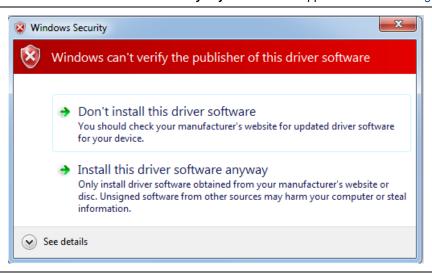

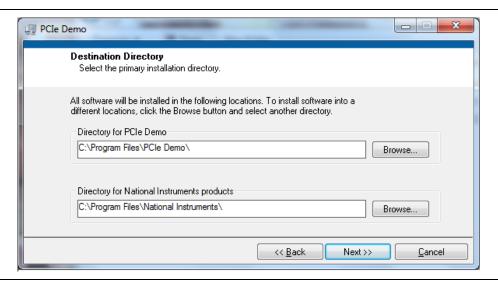

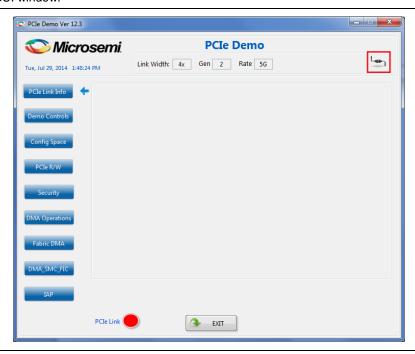

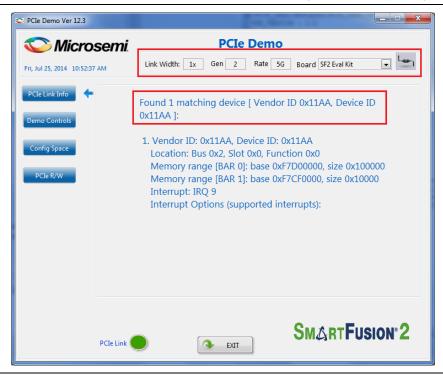

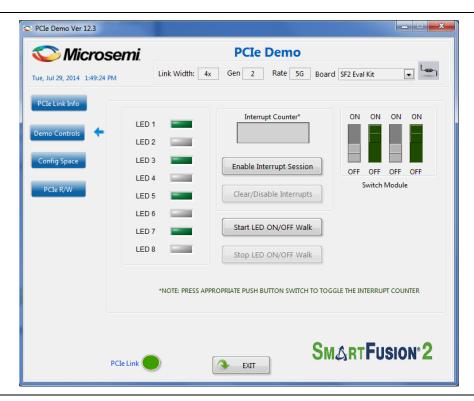

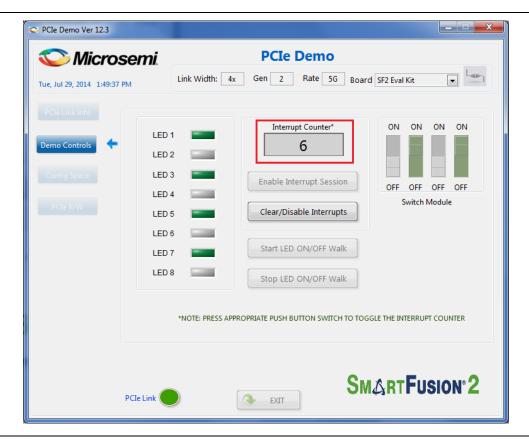

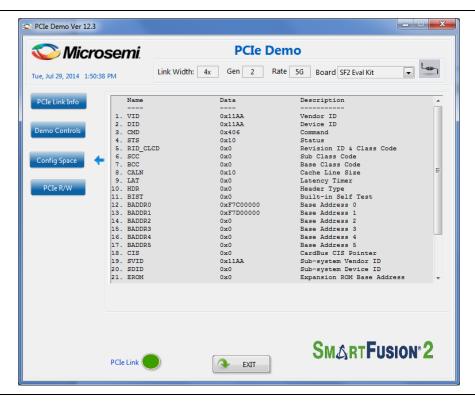

| Appendix 1 – Running the PCIe Demo Design on Windows   | 69  |

| Connecting the Board to the Host PC                    | 69  |

| Running the Demo Design                                | 70  |

#### Table of Contents

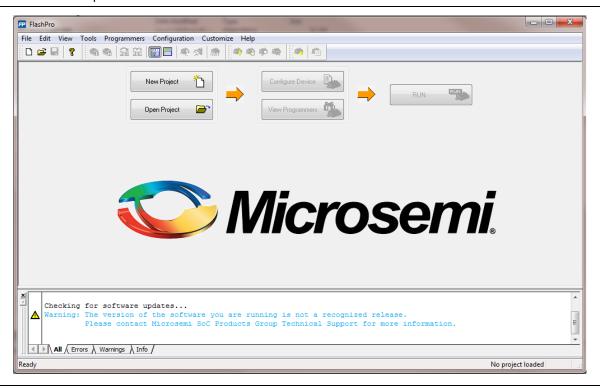

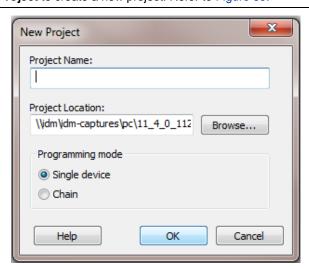

| Appendix 2 – FPGA Programming using FlashPro4    | 81 |

|--------------------------------------------------|----|

| Board Setup                                      | 81 |

| Programming the Device using Embedded FlashPro4  | 82 |

| List of Changes                                  | 85 |

| Product Support                                  | 87 |

| Customer Service                                 | 87 |

| Customer Technical Support Center                | 87 |

| Technical Support                                | 87 |

| Website                                          | 87 |

| Contacting the Customer Technical Support Center | 87 |

| ITAR Technical Support                           | 88 |

## 1 - Introduction

The SmartFusion<sup>©</sup>2 system-on-chip (SoC) field programmable gate array (FPGA) Security Evaluation Kit (M2S090TS-EVAL-KIT) is restriction of hazardous substances (RoHS) compliant and enables you to develop applications that involve the following:

- Data security

- Motor control

- System management

- Industrial automation

- High-speed serial I/O applications:

- Peripheral component interconnect express (PCIe)

- Serial gigabit media independent interface (SGMII)

- User customizable serial interfaces

## SmartFusion2 Security Evaluation Kit Contents

Table 1 lists the M2S090TS-EVAL-KIT contents.

Table 1 Kit Contents

| Quantity | Description                                                                     |

|----------|---------------------------------------------------------------------------------|

| 1        | SmartFusion2 Security Evaluation Board with the 90 K LE M2S090TS-1FGG484 device |

| 1        | 12 V/2 A Wall-Mounted Power Adapter                                             |

| 1        | FlashPro4 JTAG programmer                                                       |

| 1        | USB 2.0 A-Male to Mini-B cable for UART/power interface (up to 1 A) to PC       |

| 1        | Quickstart Card                                                                 |

| 1        | Free one-year Libero SoC Platinum Software License (v11.5 or later)             |

| 1        | PCIe Control Plane Demo Design already programmed on the device                 |

Note: The SmartFusion2 device can be programmed using on board SPI Slave (FlashPro5) mode or external FlashPro4 programmer. SoftConsole debugging cannot be performed using SPI Slave mode. FlashPro4 programmer is required to develop/debug the embedded applications with SoftConsole, Identity, or SmartDebug tool.

## SmartFusion2 Security Evaluation Kit Web Resources

M2S090TS-EVAL-KIT web resources are available at:

www.microsemi.com/products/fpga-soc/design-resources/dev-kits/SmartFusion2/smartfusion2-evaluation-kit#overview

## **Board Description**

The M2S090TS-EVAL-KIT offers a full-featured Evaluation Board for SmartFusion2 SoC FPGAs. This board has the following features integrated on a single chip:

- Reliable flash-based FPGA fabric

- 166 MHz ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor

- · Advanced security processing accelerators

- Digital signal processing (DSP) blocks

#### 1 - Introduction

- Static random-access memory (SRAM)

- Embedded non-volatile memory (eNVM)

- High-performance communication interfaces

The SmartFusion2 Security Evaluation board has numerous standard interfaces such as:

- An RJ45 for 10/100/1000 Ethernet

- One full-duplex serializer/deserializer (SERDES) lane through sub-miniature version A (SMA) connectors

- A 64-bit GPIO Header

- · Various connectors for serial peripheral interface (SPI) support

The SmartFusion2 memory management system supports 512 Mb on-board low-power double data rate (LPDDR) SDRAM memory and 64 Mb SPI flash memory. The SERDES block can be accessed using the PCIe edge connector or high-speed SMA connectors.

The board supports the M2S090TS device in an FGG484 package. The PCB has eight layers and manufactured with FR4 dielectric material.

#### **Block Diagram**

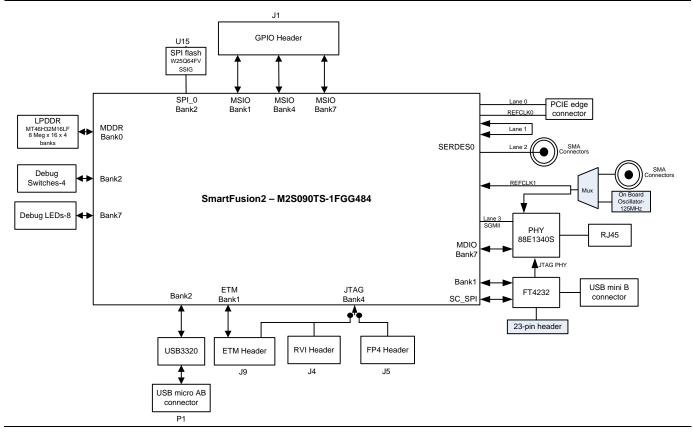

Figure 1 shows the SmartFusion2 Security Evaluation Kit block diagram:

Figure 1 SmartFusion2 Security Evaluation Kit Block Diagram

#### **Board Overview**

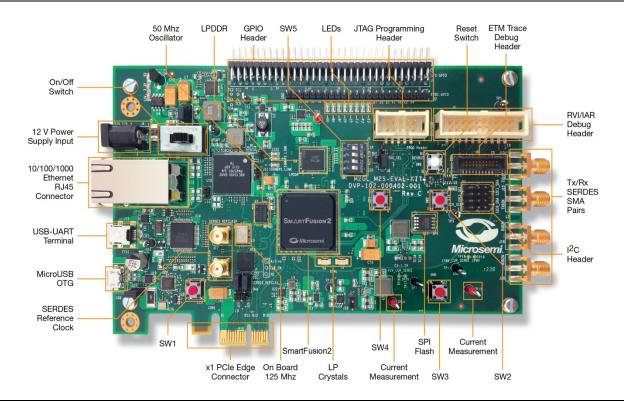

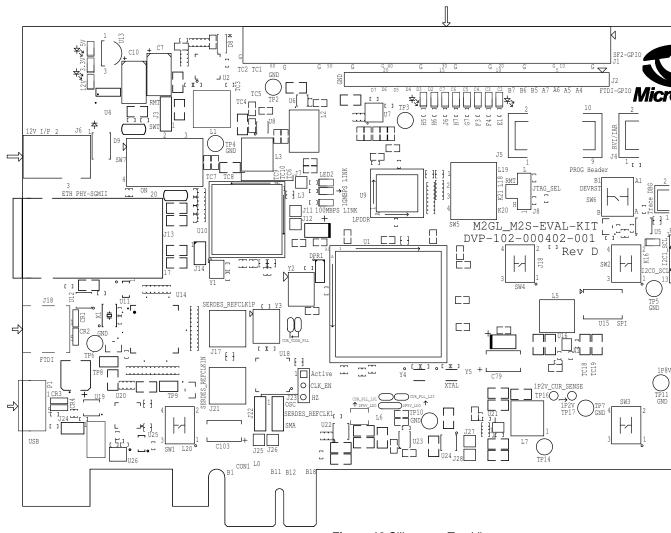

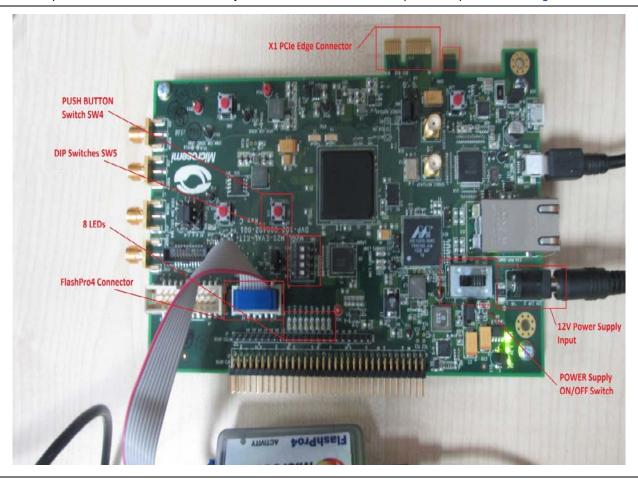

Figure 2 shows the snapshot of the SmartFusion2 Security Evaluation board with engineering silicon.

Figure 2 SmartFusion2 Security Evaluation Board

Note: Microsemi® recommends using SMA Male to SMA Male Precision Cable 12 Inch length using PE-SR405FLJ Coax, RoHS with SmartFusion2 Security Evaluation Kit. For more information, refer to www.pasternack.com/sma-male-sma-male-pe-sr405flj-cable-assembly-pe39429-12-p.aspx

## **Board Key Components**

Table 2 shows key components of the SmartFusion2 Security Evaluation Kit.

Table 2 SmartFusion2 Security Evaluation Kit Components

| Name                                                                                                           | Description                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SmartFusion2                                                                                                   | M2S090TS-1FGG484 with data security feature                                                                                                                                                                                                            |  |

| On Board 125 MHz                                                                                               | 125 MHz clock oscillator(differential output)                                                                                                                                                                                                          |  |

| x1 PCIe edge connector                                                                                         | PCI Express edge connector with one lane                                                                                                                                                                                                               |  |

| SW1, SW2, SW3, and SW4 switches                                                                                | Push button switches for user interface debugging applications.                                                                                                                                                                                        |  |

| SERDES reference clock connectors                                                                              | J17 and J21 - External clock is sourced through SMA connectors.                                                                                                                                                                                        |  |

| MicroUSB OTG                                                                                                   | P1 - USB Micro AB connector, interfacing with the high-speed USB2.0 ULPI transceiver chip USB3320, interfacing with FPGA pins of the SmartFusion2 MSS.                                                                                                 |  |

| USB-UART terminal                                                                                              | J18 - FTDI programmer interface to program the external SPI flash.                                                                                                                                                                                     |  |

| 10/100/1000 Ethernet<br>RJ45 Connector                                                                         | J13 - RJ45 connector (Ethernet jack with magnetic) interfacing with Marvell 10/100/1000 BASE-T PHY chip 88E1340S in SGMII mode, interfacing with the Ethernet port of the SmartFusion2 MSS (on-chip MAC and external PHY).                             |  |

| 12 V power supply input                                                                                        | J6 - The board is powered by a 12 V power source using an external +12 V/2 A DC jack.                                                                                                                                                                  |  |

| On/Off Switch                                                                                                  | SW7 - Power ON or OFF switch from external DC Jack, +12 V DC.                                                                                                                                                                                          |  |

| 50 MHz Oscillator                                                                                              | 50 MHz clock oscillator                                                                                                                                                                                                                                |  |

| Low-Power DDR (LPDDR)                                                                                          | 512 Mb (MT46H32M16LF – 8 Meg x 16 x 4 banks) for storing the data bits.                                                                                                                                                                                |  |

| GPIO header                                                                                                    | J1 - General purpose input/output (GPIO) header for multi standard I/O (MSIO) signals to be routed.                                                                                                                                                    |  |

| SW5 Four DIP switches for test and navigation.                                                                 |                                                                                                                                                                                                                                                        |  |

| Light-emitting diodes                                                                                          | Eight active low LEDs that are connected to some of the user I/Os for debugging.                                                                                                                                                                       |  |

| (LEDs)                                                                                                         | Three active high LEDs that are used for power supply indication.                                                                                                                                                                                      |  |

| JTAG programming header                                                                                        | J5 - The SmartFusion2 device on the Evaluation Kit can be programmed using a FlashPro4 programmer. FlashPro4 can be used to program the SmartFusion2 device. Programming header for FlashPro4 programmer to program and debug the SmartFusion2 device. |  |

| Reset Switch                                                                                                   | SW6 - Push-button system reset for the SmartFusion2 device.                                                                                                                                                                                            |  |

| Embedded trace macro (ETM) debug header                                                                        | J9 - ETM header for debugging.                                                                                                                                                                                                                         |  |

| RVI/IAR debug header                                                                                           | J4 - RVI header for application programming and debugging with Keil ULINK or IAR J-Link.                                                                                                                                                               |  |

| Tx/Rx SERDES SMA pairs  J10 - SERDES0 TXD2 P  J15 - SERDES0 TXD2 N  J16 - SERDES0 RXD2 P  J20 - SERDES0 RXD2 N |                                                                                                                                                                                                                                                        |  |

| I <sup>2</sup> C header                                                                                        | H1 - Two I <sup>2</sup> C ports routed to header                                                                                                                                                                                                       |  |

| Current measurement                                                                                            | TP14 - 1.2 V current sensing test point.                                                                                                                                                                                                               |  |

| SPI flash                                                                                                      | 64 Mb SPI flash Winbond electronics W25Q64FVSSIG connected to SPI port 0 of the SmartFusion2 microcontroller subsystem (MSS).                                                                                                                          |  |

| LP crystals                                                                                                    | Y4 and Y5 are 32.768 KHz crystal oscillators.                                                                                                                                                                                                          |  |

## 2 - Installation and Settings

## **Software Settings**

Download and install the latest release of Microsemi Libero<sup>®</sup> System-on-Chip (SoC) software v11.5 or later from the Microsemi website and register for a free Platinum software one year license. The Libero v11.5 or later installer has FlashPro4 drivers. For instructions on how to install Libero and SoftConsole, refer to the *Libero Installation and Licensing Guide*.

For instructions on how to download and install Microsemi DirectCores, SGCores, and driver firmware cores, refer to *Installing IP Cores and Drivers User Guide*. These must be installed on the PC where the Libero software is installed while designing with Microsemi FPGAs.

## Hardware Settings

#### Jumpers, Switches, LEDs, and DIP Switch Settings

The recommended default jumpers, switches, LEDs, and DIP switch settings are defined in Table 3 through Table 5.

- Table 3 Jumper Settings

- Table 4 LEDs

- Table 5 Test Points

Connect the jumpers with the default settings to evaluate the pre-programmed demo design. Table 3 shows the jumpers settings.

Note: Location of all the jumpers and test points are searchable in Figure 18 (page 42) and Figure 19 (page 43) of 5

— Board Components Placement section.

Table 3 Jumper Settings

| Jumper                                                        | Description                                                       | Pin                                                                                                                           | Default<br>Settings |

|---------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Jumper to select switch-side Mux inputs of A or B to the line |                                                                   | Pin 1-2 (Input A to the line side) that is on board 125 MHz differential clock oscillator output will be routed to line side. | Close               |

| J23                                                           | side.                                                             | Pin 2-3 (Input B to the line side) that is external clock required to source through SMA connectors to the line side.         | Open                |

|                                                               | Jumper to select the output                                       | Pin 1-2 (Line side output enabled)                                                                                            | Close               |

| J22                                                           | enable control for the line side outputs.                         | Pin 2-3 (Line side output disabled)                                                                                           | Open                |

| J24                                                           | Jumper to provide the VBUS supply to USB when using in Host mode. |                                                                                                                               | Open                |

|                                                               | JTAG selection jumper to                                          | Pin 1-2 FP4 for SoftConsole/FlashPro                                                                                          | Close               |

|                                                               | select between RVI header or FlashPro4 header for                 | Pin 2-3 RVI for Keil ULINK™/IAR J-Link®                                                                                       | Open                |

| application debug.                                            |                                                                   | Pin 2-4 for Toggling JTAG_SEL signal remotely using GPIO capability of FT4232 chip.                                           | Open                |

|                                                               | Jumpers to select either SW2                                      | Pin 1-2 for Manual power switching using SW7 switch.                                                                          | Close               |

| J3                                                            | input or signal ENABLE_FT4232 from FT4232H chip.                  | Pin 2-3 for Remote power switch using GPIO capability of FT4232 chip.                                                         | Open                |

Table 4 shows the power supply and Ethernet LEDs.

#### Table 4 LEDs

| LED         | Description                                                         |  |

|-------------|---------------------------------------------------------------------|--|

| DS1 - Green | 5 V rail.                                                           |  |

| DS2 - Green | 3.3 V rail.                                                         |  |

| DS3 - Green | 12 V power source.                                                  |  |

| DS5 - Green | Connected to parallel LED output port 0 (P0_LED[0]) of Marvell PHY. |  |

| DS4 - Green | Connected to parallel LED output port 0 (P0_LED[2]) of Marvell PHY. |  |

| DS6 - Green | Connected to parallel LED output port 0 (P0_LED[3]) of Marvell PHY. |  |

Table 5 shows the USB, ground, and other test points.

#### Table 5 Test Points

| Test Point                                  | Description                                                      |

|---------------------------------------------|------------------------------------------------------------------|

| TP8                                         | USB switch I/O for DP signal.                                    |

| TP9                                         | USB switch I/O for DM signal.                                    |

| TP1, TP2, TP4, TP5,<br>TP6, TP7, TP10, TP11 | GND                                                              |

| TP3                                         | Test point for DDR_VTT                                           |

| TP12                                        | Test point to measure the voltage at TP12 with reference to GND. |

| TP14                                        | 1.2 V current sensing test point                                 |

| TP15                                        | 1.8 V current sensing test point                                 |

| TP16, TP17                                  | Test points across current sense resistor 0.05 Ohms for 1.2 V    |

| TP18, TP19                                  | Test points across current sense resistor 0.05 Ohms for 1.8 V    |

## **SmartFusion2 Power Sources**

All the power supply devices used in the SmartFusion2 Security Evaluation Kit are Microsemi devices. For more information on power supply devices refer to <a href="https://www.microsemi.com/product-directory/ics/853-power-management">www.microsemi.com/product-directory/ics/853-power-management</a>

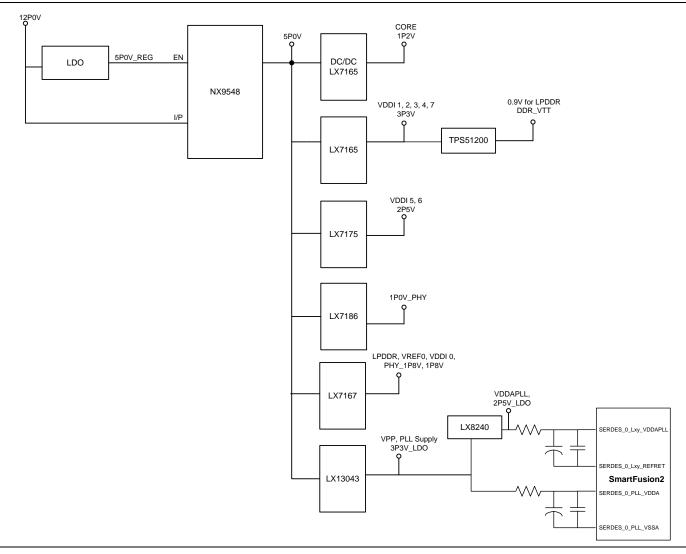

Figure 3 shows Voltage rails (12 V, 5 V, 3.3 V, 2.5 V, 1.8 V, 1.5 V, and 1.0 V) available in the SmartFusion2 Security Evaluation Kit.

Figure 3 Voltage Rails in the SmartFusion2 Security Evaluation Kit

## I/O Voltage Rails

Table 6 shows the major power supplies for normal operation of the SmartFusion2 Security Evaluation Kit.

#### Table 6 I/O Voltage Rails

| SmartFusion2 Bank | I/O Rail | Voltage |

|-------------------|----------|---------|

| Bank0             | VDDI0    | 1.8 V   |

| Bank2             | VDDI2    | 3.3 V   |

| Bank3             | VDDI3    | 3.3 V   |

| Bank4             | VDDI4    | 3.3 V   |

| Bank5             | VDDI5    | 3.3 V   |

| Bank6             | VDDI6    | 2.5 V   |

| Bank7             | VDDI7    | 2.5 V   |

| Bank 8            | VDDI8    | 3.3 V   |

## 3 - Key Components Description and Operation

This section describes the key component interfaces of the SmartFusion2 Security Evaluation Kit. For device datasheets, refer to: http://www.microsemi.com/products/fpga-soc/design-resources/dev-kits/smartfusion2-kits

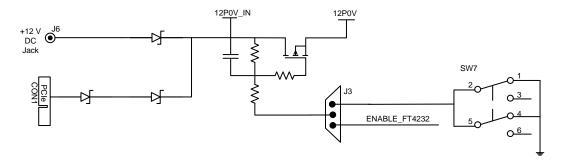

## Powering Up the Board

The board is powered by a 12 V source using an external +12 V/2 A DC jack or PCIe connector, as shown in Figure 4. Protection mechanism enables the external DC jack supply.

When both the power sources are ON, board takes power from the external DC jack as Diode D3 becomes reverse biased and path will be open for 12P0\_PCIE. When the external DC voltage is not present, the board can be powered up using the PCIe connector.

Figure 4 Powering Up the Board

## **Current Measurement**

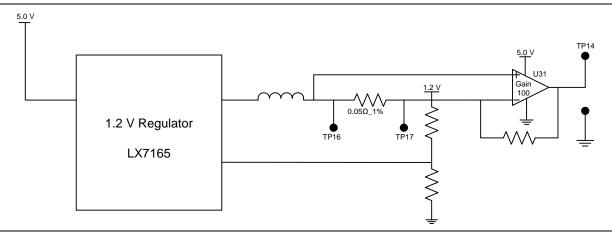

#### 1.2 V Current Sensing for Normal Operation

For applications which require current measurement, a high precision operational amplifier circuitry (U31 with gain 100) is provided on the board to measure the output voltage at test point TP14.

The following steps describe how to measure the core power:

- 1. Measure the output voltage (V<sub>OUT</sub>) at TP14.

- 2.  $I = (V_{OUT}/5)$

- 3. Core power consumed, P= (1.2 V)\*I

For example, when the voltage measured across TP14 is 0.5 V then the consumed core power is 0.12 W.

Figure 5 shows the on board core power measurement circuitry.

Figure 5 Core Power Measurement Circuitry

#### 1.2 V Current Sensing for Flash\*Freeze

The SmartFusion2 device consumes very less power in Flash\*Freeze mode. The voltage across the sense resistor  $(0.05 \ \Omega)$  must be measured directly using a precision digital multi-meter that can read sub milli-volts. Use TP16 and TP17 test points to directly measure the voltage across the 1.2 V sense resistor.

To convert the voltage measured across sense resistor to power, use the following equation:

$$Power = (\frac{voltage\_measured\_in\_milli\_volts}{0.05}) * 1.2$$

$$EQ1$$

Note: Accuracy is ± 10%.

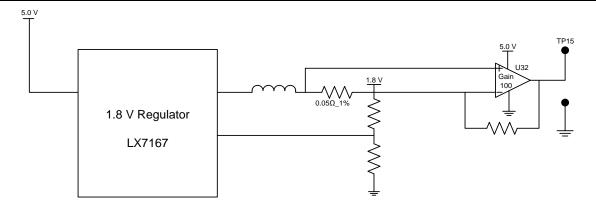

#### 1.8 V Current Sensing

For applications which require current measurement, a high precision Operational Amplifier circuitry (U32 with gain 100) is provided on the board to measure the output voltage at test point TP15.

The following steps describe how to measure the core power:

- 1. Measure the output voltage (Vout) at TP15.

- 2.  $I = (V_{OUT}/5)$

- 3. Core power consumed, P = (1.8 V)\*I

For example, when the voltage measured across TP15 is 0.5 V then the consumed core power is 0.18 W.

Figure 6 shows the on board 1.8 V power measurement circuitry.

Figure 6 1.8 V Power Measurement Circuitry

Note: Accuracy is ± 10%.

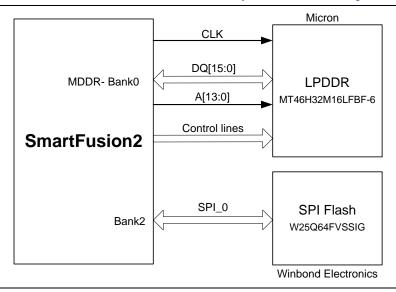

## **Memory Interface**

Dedicated I/Os are provided for the MSS DDR and fabric DDR for the SmartFusion2 device. Apart from the dedicated I/Os, regular I/Os can also be used to connect to other memory devices. Refer to Figure 7.

Figure 7 SmartFusion2 Memory Interface

#### LPDDR SDRAM

An individual chip with 512 Mb LPDDR SDRAM memory is provided as flexible volatile memory for user applications. The LPDDR interface is implemented in bank 0.

Following are the LPDDR SDRAM specifications:

- MT46H32M16LF 8 Meg x 16 x 4 banks

- Density: 512 Mb

- Data rate: LPDDR 16-bit at 400 Mbps = 6.4 Gbps

Note: For more information, refer to page 3 of Board Level Schematics document (provided separately).

#### **SPI Serial Flash**

Following are the SPI Flash specifications:

Density: 64 MbVoltage: 2.7 V - 3.6 VFrequency: 104 MHz

Supports: SPI modes 0 and 3

SmartFusion2 MSS - SPI0 interfaced to SPI flash

Note: For more information, refer to page 8 of Board Level Schematics document (provided separately).

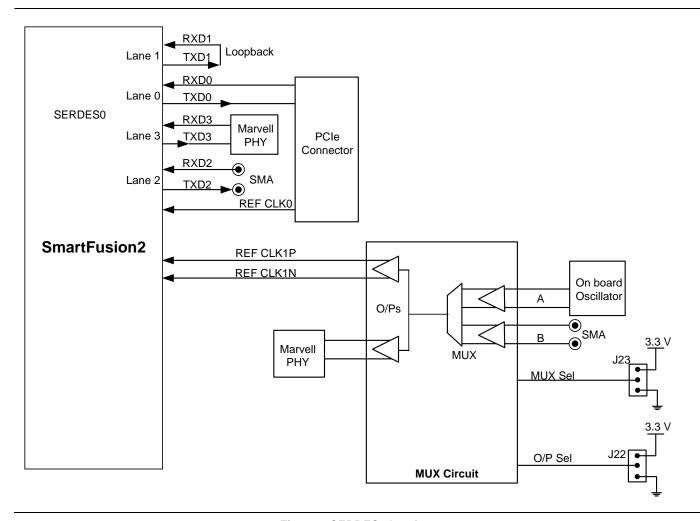

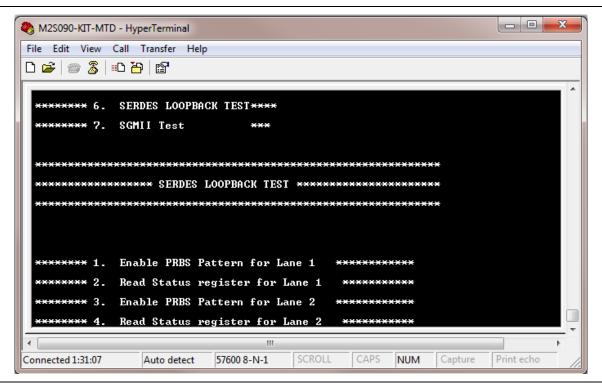

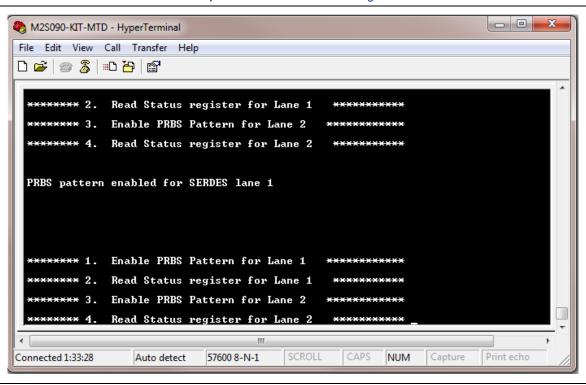

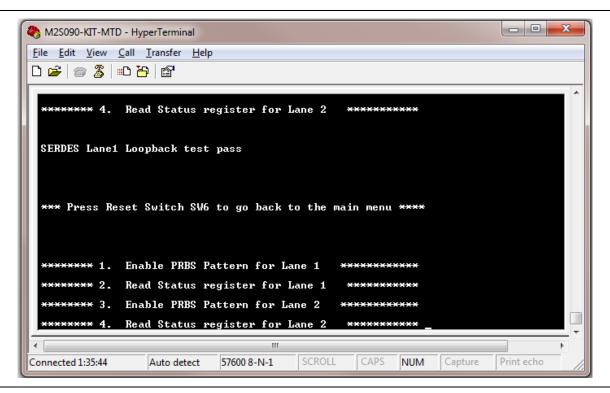

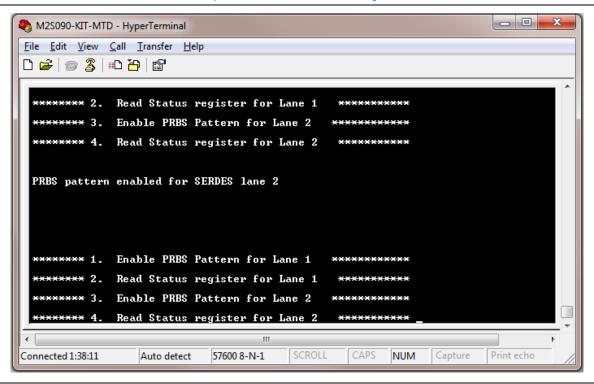

### **SERDESO Interface**

The SERDES0 has four lanes connected as below:

- 1. Lane 0 is directly routed to the PCIe connector.

- TX Pad → trace → AC Coupling→trace → via (to bottom layer) → trace → PCle connector pad

- RX Pad → trace → PCle connector pad

- 2. Lane 1 is used for loopback testing. This path is routed between the TX and RX pads with a 6 inch trace and 2 vias.

- TX Pad → via (to Bottom layer) → trace → AC Coupling → trace → via (to top layer) → RX pad

- 3. Lane 2 routed to SMA connectors.

#### 3 - Key Components Description and Operation

- TX Pad → trace → AC Coupling→trace → SMA connector pad

- RX Pad → trace → via (to bottom layer) → trace → via (to top layer) → SMA connector Pad

- 4. Lane 3 is routed to Marvell PHY (88E1340S).

- TX pad → trace→ AC Coupling → trace → via → trace routed in (6th layer) → via (to top layer) → Marvel PHY pin

- RX pad → via → trace routed in 6th layer → via (to top layer) → trace → AC Coupling

→ trace → Marvel PHY pin

The SERDES0 reference clock 0 is routed directly from the PCIe connector to the SmartFusion2 device.

The SERDES0 reference clock 1 is routed from the onboard 125 MHz clock oscillator and optionally routed from SMA connectors through LVDS Mux/Buffer chip.

Expected SERDES reference clock specifications:

- Voltage level: 3.3 (± 0.3)V

- Differential LVDS

- Symmetry: 50% (± 10%)

- Rise/Fall Time: 1 ns Max @ 20% to 80% of supply (3.3 V)

- ➤ Output Voltage Levels: 0 = 0.90 Minimum, 1.10 Typical

- 1 = 1.43 Typical, 1.60 Maximum

- Differential Output Voltage: 247 mV Minimum, 454 mV Maximum

Figure 8 SERDES0 Interface

For more information on J22 and J23 jumpers, refer to Table 3.

#### Note:

- SERDES0 TXD pairs are capacitively coupled to the SmartFusion2 device. Series AC coupling capacitors are used to provide common mode voltage independence.

- The AC coupling capacitors are not provided for SERDES 0 RXD signals. The mating board must have the AC coupling capacitors.

- For more information, refer to page 4 of Board Level Schematics document (provided separately).

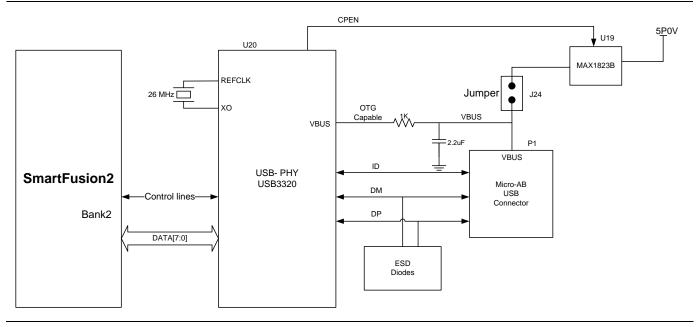

### **USB** Interface

The SMSC USB3320 is a high-speed USB 2.0 ULPI transceiver. It supports the optional OTG protocol.

Figure 9 USB Interface

Note: For more information, refer to page 10 of Board Level Schematics document (provided separately).

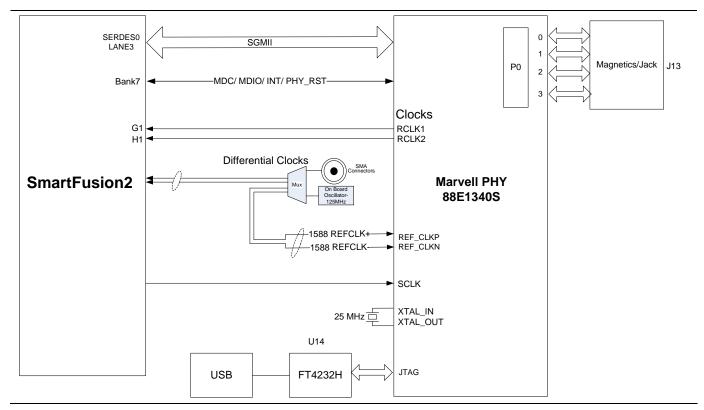

## Marvell PHY (88E1340S)

The SmartFusion2 Security Evaluation Kit uses the Marvell Alaska PHY device (88E1340S) for Ethernet communications at 10/100/1000 Mbps. The 88E1340S device has four independent Giga Bit Ethernet transceivers. However, the board uses only one transceiver. Each transceiver performs all the physical layer functions for 10BASE-T, 100BASE-TX, and 1000BASE-T full-duplex or half-duplex Ethernet on the CAT5 twisted pair cable. The PHY device is connected to a user-provided Ethernet cable through an RJ45 connector with built-in magnetics.

The 88E1340S device supports the quad SGMII for direct connection to a SmartFusion2 chip. Refer to Figure 10. It is configured through the CONFIG [3:0] and CLK\_SEL [1:0] registers.

CLK\_SEL [1:0] is used to select the reference clock input option. On board, the status of the CLK\_SEL0 register is High and CLK\_SEL1 is Low. REF\_CLK is the 125 MHz reference differential clock input. It consists of LVDS differential inputs with a 100  $\Omega$  differential internal termination resistor.

- RCLK Giga Bit recovered clock

- SCLK 25 MHz synchronous input reference clock

- Expected reference clock (REF\_CLK) specifications

- Voltage level: 3.3 (± 0.3)V

- Differential LVDS

- Symmetry: 50% (± 10%)

- Rise/Fall Time: 1 ns Max 20% to 80% of supply (3.3 V)

- Output Voltage Levels: 0 = 0.90 Minimum, 1.10 Typical

- 1 = 1.43 Typical, 1.60 Maximum

- Differential Output Voltage: 247 mV Minimum, 454 mV Maximum

Figure 10 SmartFusion2 Marvell PHY Interface

Note: For more information, refer to page 11 and 12 of Board Level Schematics document (provided separately).

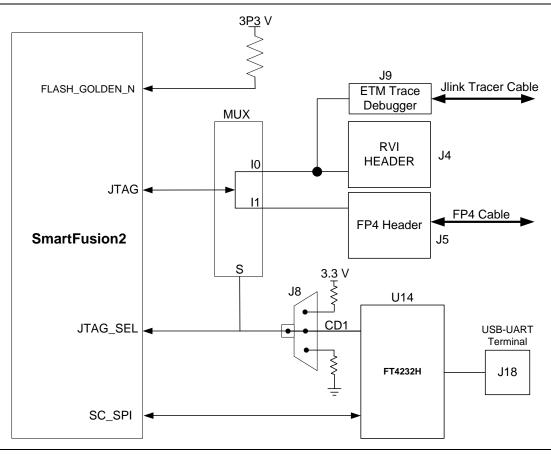

## **Programming**

The SmartFusion2 device can be programmed through the SPI Slave/JTAG interface. Figure 11 shows various ways of SmartFusion2 programming. Refer to Appendix 2 – FPGA Programming using FlashPro4 section for programming the device using SPI Slave interface.

Figure 11 SmartFusion2 Programming Interface

**JTAG\_SEL**: JTAG\_SEL is used to switch between FlashPro4 header (High) and RVI header or ETM header (Low). For more information on J8 jumper, refer to Table 3.

**RVI Header**: A 10×2 RVI header is provided on the board for debugging. This header allows plugging in the Keil ULINK debugger or IAR J-Link debugger.

**FlashPro4 Programming Header**: The SmartFusion2 device on the Evaluation Kit can be programmed using on board SPI Slave (FlashPro5) or external FlashPro4 programmer. In addition, the FlashPro4 programmer is used to debug the software using SoftConsole.

#### Note:

- For more information, refer to page 13 of Board Level Schematics document (provided separately).

- For more details, refer to the SmartFusion2 Programming User Guide.

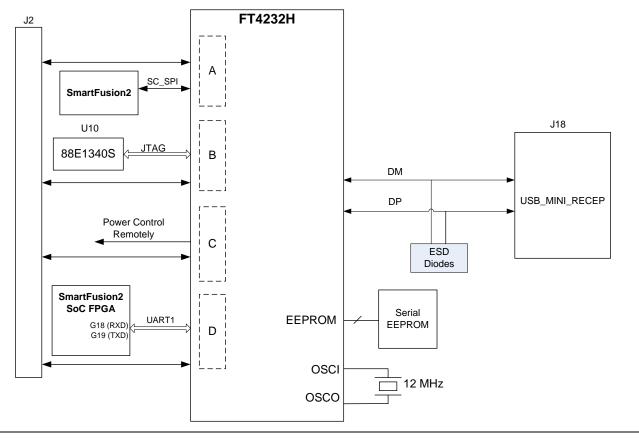

## **FTDI** Interface

Following are the FT4232H chip features:

- USB 2.0 high-speed (480 Mbps) to UART/MPSSE IC.

- Single-chip USB to quad serial ports with different configurations.

- Entire USB protocol is handled on the chip. USB specific firmware programming is not required.

- USB 2.0 high-speed (480 Mbps) and full Speed (12 Mbps) compatible.

- Two MPSSE on channel A and channel B, to simplify synchronous serial protocol (USB to JTAG, I2C, SPI, or bit-bang) design.

- Fully assisted hardware or X-On or X-Off software handshaking.

- +1.8 V (chip core) and +3.3 V I/O interfacing (+5 V tolerant).

Figure 12 FTDI Interface

Note: For more information, refer to page 14 of Board Level Schematics document (provided separately).

## I<sup>2</sup>C Port Header

Table 7 shows the two I<sup>2</sup>C ports routed to header – H1:

Table 7 I2C Port Header

| Pin Number | SmartFusion2 Pin Name                                      | Board Signal Name | Header - H1 |

|------------|------------------------------------------------------------|-------------------|-------------|

| G16        | MSIO61NB2/I2C_0_SCL/GPIO_31_B/USB_<br>DATA1_C              | I2C0_SCL          | 10, 14      |

| G17        | MSIO61PB2/I2C_0_SDA/GPIO_30_B/USB_<br>DATA0_C              | I2C0_SDA          | 11, 15      |

| R22        | MSIO11NB3/CCC_NE1_CLKI0/I2C_1_SCL/<br>GPIO_1_A/USB_DATA4_A | I2C1_SCL          | 2, 6        |

| P22        | MSIO11PB3/CCC_NE0_CLKI0/I2C_1_SDA/<br>GPIO_0_A/USB_DATA3_A | I2C1_SDA          | 3, 7        |

Note: For more information, refer to page 8 of Board Level Schematics document (provided separately).

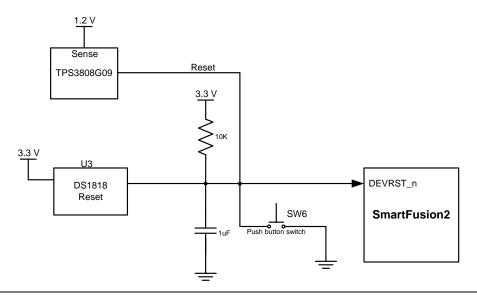

## System Reset

The DEVRST\_N signal (active low) is asserted in the following cases:

- When you press the SW6 (push-button switch) switch

- When the power supply level 3.3 V or 1.2 V falls below the threshold level

DEVRST\_N is an input-only reset pad that allows assertion of a full reset to the chip at any time.

Figure 13 System Reset Interface

Note: For more information, refer to page13 of Board Level Schematics document (provided separately).

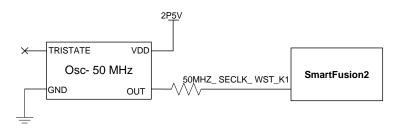

## **Clock Oscillator**

#### **50 MHz Clock Source**

A 50 MHz clock oscillator with an accuracy of +/-50 ppm is available on the board, refer to Figure 14. This clock oscillator is connected to the FPGA fabric to provide a system reference clock.

An on-chip SmartFusion2 PLL can be configured to generate a wide range of high precision clock frequencies.

#### Table 8 50 MHz Clock

| SmartFusion2 Security<br>Evaluation Kit | SmartFusion2 -<br>Package No | SmartFusion2 Pin Name     |

|-----------------------------------------|------------------------------|---------------------------|

| 50MHZ_ SECLK_ WST_K1                    | K1                           | MSIOD178PB7/CCC_SW0_CLKI0 |

Figure 14 50 MHz Clock Oscillator Interface

Note: For more information, refer to page 6 of Board Level Schematics document (provided separately).

#### **Different Clock Sources**

Following are the different clock sources used in the SmartFusion2 Security Evaluation Kit:

- 125 MHz clock oscillator. For more information refer to SERDESO Interface.

- 32.768 KHz crystal oscillators for main and auxiliary oscillators of SmartFusion2.

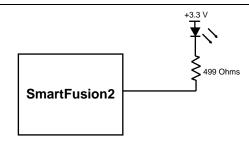

#### **User Interface**

#### **User LEDs**

The board has eight active low LEDs, which are connected to the SmartFusion2 device. Table 9 shows the on board user LEDs.

Table 9 LEDs

| SmartFusion2 Security<br>Evaluation Board Pin | SmartFusion2 - Package Pin<br>Number | SmartFusion2 Device Pin Name |

|-----------------------------------------------|--------------------------------------|------------------------------|

| LED0 - Yellow                                 | E1                                   | MSIO143PB8                   |

| LED1 – Yellow                                 | F4                                   | MSIO145NB8                   |

| LED2 – Green                                  | F3                                   | MSIO145PB8                   |

| LED3 – Green                                  | G7                                   | MSIO146NB8                   |

| LED4 – Red                                    | H7                                   | MSIO146PB8                   |

| LED5 – Red                                    | J6                                   | MSIO148NB8                   |

| LED6 – Blue                                   | H6                                   | MSIO148PB8                   |

| SmartFusion2 Security<br>Evaluation Board Pin | SmartFusion2 - Package Pin<br>Number | SmartFusion2 Device Pin Name |

|-----------------------------------------------|--------------------------------------|------------------------------|

| LED7 - Blue                                   | H5                                   | MSIO150NB8                   |

Figure 15 LEDs Interface

Note: For more information, refer to page 15 of Board Level Schematics document (provided separately).

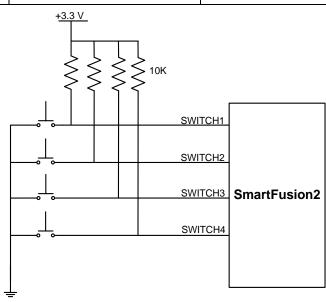

#### **Push-Button Switches**

The SmartFusion2 Security Evaluation Kit comes with five push-button tactile switches that are connected to the SmartFusion2 device. Table 10 shows the on board push-button switches.

Table 10 Push-Button Switches

| SmartFusion2 Security<br>Evaluation Board Pin | SmartFusion2 - Package Pin<br>Number | SmartFusion2 Device Pin Name  |

|-----------------------------------------------|--------------------------------------|-------------------------------|

| SWITCH1                                       | L20                                  | MSIO17NB3/SPI_1_SS0/GPIO_13_A |

| SWITCH2                                       | K16                                  | MSIO23NB3/SPI_1_SS1/GPIO_14_A |

| SWITCH3                                       | K18                                  | MSIO24PB3/SPI_1_SS2/GPIO_15_A |

| SWITCH4                                       | J18                                  | MSIO24NB3/SPI_1_SS3/GPIO_16_A |

| SW6                                           | R15                                  | DEVRST_N                      |

Figure 16 Switches Interface

Note: For more information, refer to page 15 of Board Level Schematics document (provided separately).

#### Slide Switches-DPDT

SW7 - Power ON or OFF switch from external DC Jack, +12 V DC.

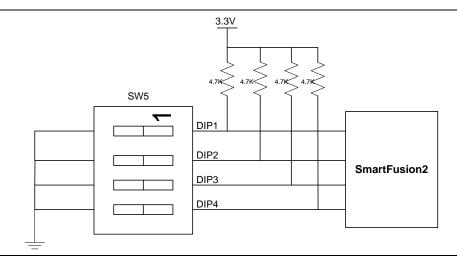

#### **DIP Switch-SPST**

SW5 - A DIP switch that has four connections to the SmartFusion2 device. Table 11 shows the onboard DIP switches.

Table 11 DIP Switches

| SmartFusion2 Security<br>Evaluation Board Pin | SmartFusion2 - Package Pin<br>Number | SmartFusion2 Device Pin Name  |

|-----------------------------------------------|--------------------------------------|-------------------------------|

| DIP1                                          | L19                                  | MSIO18PB3/SPI_1_SS4/GPIO_17_A |

| DIP2                                          | L18                                  | MSIO18NB3/SPI_1_SS5/GPIO_18_A |

| DIP3                                          | K21                                  | MSIO19PB3/SPI_1_SS6/GPIO_23_A |

| DIP4                                          | K20                                  | MSIO19NB3/SPI_1_SS7/GPIO_24_A |

Figure 17 SPST Interface

Note: For more information, refer to page 15 of Board Level Schematics document (provided separately).

## **GPIO Header Pin Out**

Bank 4, bank 7, and bank 1 signals are routed to the GPIO header for user applications. Table 12 shows the GPIO header pin out details.

Table 12 GPIO Header PinOut

| GPIO<br>Header-<br>J1 | SmartFusion2 – U1 |                          | GPIO<br>Header-<br>J1 | SmartFusion2 – U1 |            |

|-----------------------|-------------------|--------------------------|-----------------------|-------------------|------------|

| Pin<br>Number         | Package<br>Number | Pin Name                 | Pin<br>Number         | Package<br>Number | Pin Number |

| 1                     | AB15              | MSIO213PB5/VCCC_SE1_CLKI | 2                     |                   | 3P3V       |

| 3                     | AA15              | MSIO213NB5               | 4                     |                   | VSS        |

| 5                     |                   | VSS                      | 6                     | AA16              | MSIO222PB5 |

| 7                     | AB18              | MSIO230PB5               | 8                     | AA17              | MSIO222NB5 |

| GPIO<br>Header-<br>J1 | SmartFusion2 – U1 |                                            | GPIO<br>Header-<br>J1 | SmartFusion2 – U1 |            |

|-----------------------|-------------------|--------------------------------------------|-----------------------|-------------------|------------|

| Pin<br>Number         | Package<br>Number | Pin Name                                   | Pin<br>Number         | Package<br>Number | Pin Number |

| 9                     | AB19              | MSIO230NB5                                 | 10                    |                   | VSS        |

| 11                    |                   | vss                                        | 12                    | AB17              | MSIO221PB5 |

| 13                    | Y18               | MSIO228PB5                                 | 14                    | AA18              | MSIO221NB5 |

| 15                    | Y19               | MSIO228NB5                                 | 16                    |                   | VSS        |

| 17                    |                   | vss                                        | 18                    | Y17               | MSIO226PB5 |

| 19                    | W16               | MSIO224PB5                                 | 20                    | W17               | MSIO226NB5 |

| 21                    | V16               | MSIO224NB5                                 | 22                    |                   | VSS        |

| 23                    |                   | vss                                        | 24                    | U14               | MSIO218PB5 |

| 25                    | C22               | MSIO60PB2/MMUART_0_RXD/GPIO_28_B/USB_STP_C | 26                    | U15               | MSIO218NB5 |

| 27                    | B22               | MSIO60NB2/MMUART_0_CLK/GPIO_29_B/USB_NXT_C | 28                    |                   | VSS        |

| 29                    |                   | vss                                        | 30                    | V13               | MSIO211PB5 |

| 31                    | Y15               | MSIO216PB5                                 | 32                    | V14               | MSIO211NB5 |

| 33                    | W15               | MSIO216NB5                                 | 34                    |                   | VSS        |

| 35                    |                   | VSS                                        | 36                    | G5                | MSIO98PB8  |

| 37                    | F5                | MSIO132PB8                                 | 38                    | G6                | MSIO131NB8 |

| 39                    | F6                | MSIO132NB8                                 | 40                    |                   | VSS        |

| 41                    |                   | VSS                                        | 42                    | E4                | MSIO138PB8 |

| 43                    | C4                | MSIO127PB8                                 | 44                    | E5                | MSIO138NB8 |

| 45                    | D5                | MSIO127NB8                                 | 46                    |                   | VSS        |

| 47                    |                   | VSS                                        | 48                    | C3                | MSIO129PB8 |

| 49                    | B2                | MSIO136PB8                                 | 50                    | В3                | MSIO129NB8 |

| 51                    | A2                | MSIO136NB8                                 | 52                    |                   | VSS        |

| 53                    |                   | VSS                                        | 54                    | C1                | MSIO140PB8 |

| 55                    | D1                | MSIO142PB8                                 | 56                    | B1                | MSIO140NB8 |

| 57                    | D2                | MSIO142NB8                                 | 58                    |                   | VSS        |

| 59                    |                   | VSS                                        | 60                    | D3                | MSIO134PB8 |

| 61                    |                   | 3P3V                                       | 62                    | D4                | MSIO134NB8 |

| 63                    |                   | 3P3V                                       | 64                    |                   | VSS        |

## 4 - Pin List

Table 13 lists the pins for SmartFusion2 M2S090TS-FGG484 devices.

Note: \*D21- Pin cannot be used as a fabric output and it is only an Input.

Table 13 Pin List update with latest of M2S090TS-FGG484

| Package Pin | M2S090TS-FGG484 Pin Name                |

|-------------|-----------------------------------------|

| A1          | vss                                     |

| A2          | MSIO136NB8                              |

| A3          | DDRIO99NB1                              |

| A4          | DDRIO99PB1                              |

| A5          | DDRIO98NB1                              |

| A6          | DDRIO92NB1/GB4/CCC_NW1_CLKI2            |

| A7          | DDRIO89PB1/MDDR_DQ_ECC1                 |

| A8          | DDRIO89NB1/MDDR_DQ_ECC0                 |

| A9          | DDRIO87NB1/MDDR_DQ1                     |

| A10         | DDRIO84PB1/MDDR_DM_RDQS0                |

| A11         | DDRIO84NB1/MDDR_DQ4                     |

| A12         | DDRIO81PB1/MDDR_DQ8                     |

| A13         | DDRIO81NB1/MDDR_DQ9                     |

| A14         | DDRIO77PB1/GB12/CCC_NE1_CLKI2/MDDR_DQ12 |

| A15         | DDRIO77NB1/MDDR_DQ13                    |

| A16         | DDRIO72PB1/MDDR_CLK                     |

| A17         | DDRIO72NB1/MDDR_CLK_N                   |

| A18         | DDRIO71PB1/MDDR_BA0                     |

| A19         | DDRIO71NB1/MDDR_BA1                     |

| A20         | DDRIO67NB1/MDDR_ADDR6                   |

| A21         | DDRIO64PB1/MDDR_ADDR10                  |

| A22         | VSS                                     |

| AA1         | VSS                                     |

| AA2         | SERDES_0_TXD0_N                         |

| AA3         | VSS                                     |

| AA4         | SERDES_0_TXD1_N                         |

| AA5         | VSS                                     |

| AA6         | SERDES_0_TXD2_N                         |

| AA7         | VSS                                     |

| AA8         | SERDES_0_TXD3_N                         |

| AA9         | VSS                                     |

| AA10        | MSIO198PB5                              |

| Package Pin | M2S090TS-FGG484 Pin Name     |

|-------------|------------------------------|

| AA11        | MSIO203PB5                   |

| AA12        | MSIO204PB5                   |

| AA13        | MSIO209PB5/VCCC_SE0_CLKI     |

| AA14        | vss                          |

| AA15        | MSIO213NB5                   |

| AA16        | MSIO222PB5                   |

| AA17        | MSIO222NB5                   |

| AA18        | MSIO221NB5                   |

| AA19        | VDDI5                        |

| AA20        | XTLOSC_AUX_EXTAL             |

| AA21        | XTLOSC_MAIN_EXTAL            |

| AA22        | JTAGSEL                      |

| AB1         | vss                          |

| AB2         | SERDES_0_TXD0_P              |

| AB3         | vss                          |

| AB4         | SERDES_0_TXD1_P              |

| AB5         | vss                          |

| AB6         | SERDES_0_TXD2_P              |

| AB7         | vss                          |

| AB8         | SERDES_0_TXD3_P              |

| AB9         | vss                          |

| AB10        | MSIO198NB5                   |

| AB11        | MSIO203NB5                   |

| AB12        | VDDI5                        |

| AB13        | MSIO208PB5/CCC_SW1_CLKI3     |

| AB14        | MSIO208NB5                   |

| AB15        | MSIO213PB5/VCCC_SE1_CLKI     |

| AB16        | VSS                          |

| AB17        | MSIO221PB5                   |

| AB18        | MSIO230PB5                   |

| AB19        | MSIO230NB5                   |

| AB20        | XTLOSC_AUX_XTAL              |

| AB21        | XTLOSC_MAIN_XTAL             |

| AB22        | VSS                          |

| B1          | MSIO140NB8                   |

| B2          | MSIO136PB8                   |

| B3          | MSIO129NB8                   |

| B4          | VSS                          |

| B5          | DDRIO98PB1                   |

| B6          | DDRIO92PB1/GB0/CCC_NW0_CLKI3 |

| Package Pin | M2S090TS-FGG484 Pin Name                   |

|-------------|--------------------------------------------|

| B7          | DDRIO91NB1/MDDR_DQS_ECC_N                  |

| B8          | VDDi1                                      |

| В9          | DDRIO87PB1/MDDR_DQ0                        |

| B10         | vss                                        |

| B11         | DDRIO85PB1/MDDR_DQS0                       |

| B12         | VDDI1                                      |

| B13         | DDRIO79PB1/GB8/CCC_NE0_CLKI3/MDDR_DQS1     |

| B14         | vss                                        |

| B15         | DDRIO74PB1/MDDR_CKE                        |

| B16         | VDDI1                                      |

| B17         | DDRIO70NB1/MDDR_ADDR0                      |

| B18         | vss                                        |

| B19         | DDRIO67PB1/MDDR_ADDR5                      |

| B20         | VDDI1                                      |

| B21         | DDRIO64NB1/MDDR_ADDR11                     |

| B22         | MSIO60NB2/MMUART_0_CLK/GPIO_29_B/USB_NXT_C |

| C1          | MSIO140PB8                                 |

| C2          | VDDI8                                      |

| C3          | MSIO129PB8                                 |

| C4          | MSIO127PB8                                 |

| C5          | DDRIO97PB1                                 |

| C6          | VDDI1                                      |

| C7          | DDRIO91PB1/MDDR_DQS_ECC                    |

| C8          | vss                                        |

| C9          | DDRIO88NB1                                 |

| C10         | VDDI1                                      |

| C11         | DDRIO85NB1/MDDR_DQS0_N                     |

| C12         | vss                                        |

| C13         | DDRIO79NB1/MDDR_DQS1_N                     |

| C14         | VDDI1                                      |

| C15         | DDRIO74NB1/MDDR_CS_N                       |

| C16         | DDRIO70PB1/MDDR_BA2                        |

| C17         | DDRIO68PB1/MDDR_ADDR3                      |

| C18         | DDRIO68NB1/MDDR_ADDR4                      |

| C19         | DDRIO66NB1/MDDR_ADDR7                      |

| C20         | DDRIO66PB1/MDDR_ODT                        |

| C21         | vss                                        |

| C22         | MSIO60PB2/MMUART_0_RXD/GPIO_28_B/USB_STP_C |

| D1          | MSIO142PB8                                 |

| D2          | MSIO142NB8                                 |

| Package Pin | M2S090TS-FGG484 Pin Name                  |

|-------------|-------------------------------------------|

| D3          | MSIO134PB8                                |

| D4          | MSIO134NB8                                |

| D5          | MSIO127NB8                                |

| D6          | DDRIO97NB1                                |

| D7          | MDDR_IMP_CALIB                            |

| D8          | DDRIO90NB1/MDDR_DM_RDQS_ECC               |

| D9          | DDRIO88PB1/CCC_NW1_CLKI3                  |

| D10         | DDRIO83PB1/MDDR_DQ5                       |

| D11         | DDRIO83NB1/MDDR_DQ6                       |

| D12         | DDRIO80PB1/MDDR_DQ10/CCC_NE0_CLKI2        |

| D13         | DDRIO80NB1/MDDR_DQ11                      |

| D14         | DDRIO76PB1/CCC_NE1_CLKI3/MDDR_DQ14        |

| D15         | VSS                                       |

| D16         | DDRIO69PB1/MDDR_ADDR1                     |

| D17         | VDDI1                                     |

| D18         | DDRIO62PB1/MDDR_ADDR14                    |

| D19         | VSS                                       |

| D20         | DDRIO63NB1/MDDR_ADDR13                    |

| D21         | MSI59NB2/MMUART_0_TXD/GPIO_27_B/USB_DIR_C |

| D22         | FLASH_GOLDEN_N                            |

| E1          | MSIO143PB8                                |

| E2          | MSIO143NB8                                |

| E3          | VSS                                       |

| E4          | MSIO138PB8                                |

| E5          | MSIO138NB8                                |

| E6          | VSS                                       |

| E7          | DDRIO93PB1/MDDR_TMATCH_ECC_OUT            |

| E8          | DDRIO90PB1/MDDR_TMATCH_ECC_IN             |

| E9          | VSS                                       |

| E10         | DDRIO86NB1/MDDR_DQ3                       |

| E11         | VDDI1                                     |

| E12         | DDRIO82PB1/MDDR_DQ7                       |

| E13         | DDRIO76NB1/MDDR_DQ15                      |

| E14         | VSS                                       |

| E15         | DDRIO73PB1/MDDR_RESET_N                   |

| E16         | DDRIO69NB1/MDDR_ADDR2                     |

| E17         | DDRIO65PB1/MDDR_ADDR8                     |

| E18         | DDRIO62NB1/MDDR_ADDR15                    |

| E19         | DDRIO63PB1/MDDR_ADDR12                    |

| E20         | VDDI2                                     |

| Package Pin | M2S090TS-FGG484 Pin Name                     |

|-------------|----------------------------------------------|

| E21         | MSIO58NB2/MMUART_0_DCD/GPIO_22_B             |

| E22         | MSIO58PB2/MMUART_0_RI/GPIO_21_B              |

| F1          | VDDI8                                        |

| F2          | MSIO152NB8                                   |

| F3          | MSIO145PB8                                   |

| F4          | MSIO145NB8                                   |

| F5          | MSIO132PB8                                   |

| F6          | MSIO132NB8                                   |

| F7          | VDDI1                                        |

| F8          | DDRIO93NB1/CCC_NW0_CLKI2                     |

| F9          | VDDI1                                        |

| F10         | DDRIO86PB1/MDDR_DQ2                          |

| F11         | VSS                                          |

| F12         | DDRIO82NB1/MDDR_TMATCH_0_OUT                 |

| F13         | VDDI1                                        |

| F14         | DDRIO75PB1/MDDR_RAS_N                        |

| F15         | DDRIO73NB1/MDDR_CAS_N                        |

| F16         | VSS                                          |

| F17         | DDRIO65NB1/MDDR_ADDR9                        |

| F18         | MSIO57NB2/MMUART_0_DSR/GPIO_20_B             |

| F19         | MSIO57PB2/MMUART_0_CTS/GPIO_19_B/USB_DATA7_C |

| F20         | MSIO56NB2/MMUART_0_DTR/GPIO_18_B/USB_DATA6_C |

| F21         | MSIO56PB2/MMUART_0_RTS/GPIO_17_B/USB_DATA5_C |

| F22         | VDDI2                                        |

| G1          | MSIO156NB8                                   |

| G2          | MSIO152PB8                                   |

| G3          | MSIO154NB8                                   |

| G4          | VDD18                                        |

| G5          | MSIO131PB8                                   |

| G6          | MSIO131NB8                                   |

| G7          | MSIO146NB8                                   |

| G8          | CCC_NW1_PLL_VSSA                             |

| G9          | CCC_NW1_PLL_VDDA                             |

| G10         | VREF                                         |

| G11         | VREF                                         |

| G12         | DDRIO78PB1/MDDR_TMATCH_0_IN                  |

| G13         | DDRIO78NB1/MDDR_DM_RDQS1                     |

| G14         | DDRIO75NB1/MDDR_WE_N                         |

| G15         | VREF                                         |

| G16         | MSIO61NB2/I2C_0_SCL/GPIO_31_B/USB_DATA1_C    |

| Package Pin | M2S090TS-FGG484 Pin Name                                        |

|-------------|-----------------------------------------------------------------|

| G17         | MSIO61PB2/I2C_0_SDA/GPIO_30_B/USB_DATA0_C                       |

| G18         | MSIO55NB2/MMUART_1_RXD/GPIO_26_B/USB_DATA3_C                    |

| G19         | MSIO55PB2/GB14/VCCC_SE1_CLKI/MMUART_1_CLK/GPIO_25_B/USB_DATA4_C |

| G20         | vss                                                             |

| G21         | MSIO53NB2/MMUART_1_DCD/GPIO_16_B                                |

| G22         | MSIO53PB2/CCC_NE1_CLKI1/MMUART_1_RI/GPIO_15_B                   |

| H1          | MSIO156PB8/GB6/CCC_NW1_CLKI1                                    |

| H2          | VSS                                                             |

| H3          | MSIO154PB8                                                      |

| H4          | MSIO150PB8                                                      |

| H5          | MSIO150NB8                                                      |

| H6          | MSIO148PB8                                                      |

| H7          | MSIO146PB8                                                      |

| H8          | CCC_NW0_PLL_VDDA                                                |

| H9          | vss                                                             |

| H10         | VDD                                                             |

| H11         | vss                                                             |

| H12         | VDDI1                                                           |

| H13         | vss                                                             |

| H14         | VDDI1                                                           |

| H15         | CCC_NE0_PLL_VDDA                                                |

| H16         | MSS_MDDR_PLL_VDDA                                               |

| H17         | MSS_MDDR_PLL_VSSA                                               |

| H18         | VDDI2                                                           |

| H19         | MSIO54NB2/MMUART_1_TXD/GPIO_24_B/USB_DATA2_C                    |

| H20         | MSIO54PB2/GB10/VCCC_SE0_CLKI/USB_XCLK_C                         |

| H21         | MSIO51NB2/MMUART_1_DTR/GPIO_12_B                                |

| H22         | MSIO51PB2/MMUART_1_RTS/GPIO_11_B                                |

| J1          | MSIO158PB8/CCC_NW1_CLKI0                                        |

| J2          | MSIO158NB8                                                      |

| J3          | MSIO157PB8/GB2/CCC_NW0_CLKI1                                    |

| J4          | MSIO157NB8                                                      |

| J5          | VSS                                                             |

| J6          | MSIO148NB8                                                      |

| J7          | VDDI8                                                           |

| J8          | CCC_NW0_PLL_VSSA                                                |

| J9          | VDD                                                             |

| J10         | VSS                                                             |

| J11         | VDD                                                             |

| J12         | VSS                                                             |

| Package Pin | M2S090TS-FGG484 Pin Name                       |

|-------------|------------------------------------------------|

| J13         | VDD                                            |

| J14         | VSS                                            |

| J15         | CCC_NE0_PLL_VSSA                               |

| J16         | CCC_NE1_PLL_VSSA                               |

| J17         | CCC_NE1_PLL_VDDA                               |

| J18         | MSIO24NB3/SPI_1_SS3/GPIO_16_A                  |

| J19         | MSIO52NB2/MMUART_1_DSR/GPIO_14_B               |

| J20         | MSIO52PB2/CCC_NE0_CLKI1/MMUART_1_CTS/GPIO_13_B |

| J21         | VDDI2                                          |

| J22         | MSIO20NB3/GB13/VCCC_SE1_CLKI/GPIO_26_A         |

| K1          | MSIOD178PB7/CCC_SW0_CLKI0                      |

| K2          | MSIOD178NB7                                    |

| K3          | VDDI7                                          |

| K4          | MSIOD175PB7/GB5/CCC_SW1_CLKI1                  |

| K5          | MSIOD175NB7                                    |

| K6          | MSIO159PB8/CCC_NW0_CLKI0                       |

| K7          | MSIO159NB8                                     |

| K8          | MSIOD176PB7/GB1/CCC_SW0_CLKI1                  |

| K9          | VSS                                            |

| K10         | VDD                                            |

| K11         | VSS                                            |

| K12         | VDD                                            |

| K13         | VSS                                            |

| K14         | VDD                                            |

| K15         | MSIO22NB3/SPI_0_SS2/GPIO_9_A/USB_DATA6_A       |

| K16         | MSIO23NB3/SPI_1_SS1/GPIO_14_A                  |

| K17         | MSIO23PB3/SPI_0_SS3/GPIO_10_A/USB_DATA7_A      |

| K18         | MSIO24PB3/SPI_1_SS2/GPIO_15_A                  |

| K19         | VSS                                            |

| K20         | MSIO19NB3/SPI_1_SS7/GPIO_24_A                  |

| K21         | MSIO19PB3/SPI_1_SS6/GPIO_23_A                  |

| K22         | MSIO20PB3/GB9/VCCC_SE0_CLKI/GPIO_25_A          |

| L1          | vss                                            |

| L2          | MSIOD179PB7                                    |

| L3          | MSIOD179NB7                                    |

| L4          | MSIOD180PB7                                    |

| L5          | MSIOD180NB7                                    |

| L6          | VDDI7                                          |

| L7          | MSIOD177NB7                                    |

| L8          | MSIOD176NB7                                    |

| Package Pin | M2S090TS-FGG484 Pin Name                 |

|-------------|------------------------------------------|

| L9          | VDD                                      |

| L10         | VSS                                      |

| L11         | VDD                                      |

| L12         | VSS                                      |

| L13         | VDD                                      |

| L14         | VSS                                      |

| L15         | VPP                                      |

| L16         | MSIO22PB3/SPI_0_SS1/GPIO_8_A/USB_DATA5_A |

| L17         | VDDI3                                    |

| L18         | MSIO18NB3/SPI_1_SS5/GPIO_18_A            |

| L19         | MSIO18PB3/SPI_1_SS4/GPIO_17_A            |

| L20         | MSIO17NB3/SPI_1_SS0/GPIO_13_A            |

| L21         | MSIO17PB3/SPI_1_SDO/GPIO_12_A            |

| L22         | VSS                                      |

| M1          | MSIOD185NB7                              |

| M2          | MSIOD183NB7                              |

| M3          | MSIOD183PB7                              |

| M4          | VSS                                      |

| M5          | MSIOD181PB7                              |

| M6          | MSIOD181NB7                              |

| M7          | MSIOD177PB7/CCC_SW1_CLKI0                |

| M8          | MSIOD188NB7                              |

| M9          | VSS                                      |

| M10         | VDD                                      |

| M11         | VSS                                      |

| M12         | VDD                                      |

| M13         | VSS                                      |

| M14         | VDD                                      |

| M15         | VPPNVM                                   |

| M16         | MSIO14PB3/SPI_0_SS4/GPIO_19_A            |

| M17         | MSIO14NB3/SPI_0_SS5/GPIO_20_A            |

| M18         | MSIO15PB3/SPI_0_SS6/GPIO_21_A            |

| M19         | MSIO15NB3/SPI_0_SS7/GPIO_22_A            |

| M20         | VDDI3                                    |

| M21         | MSIO16PB3/SPI_1_CLK                      |

| M22         | MSIO16NB3/SPI_1_SDI/GPIO_11_A            |

| N1          | MSIOD185PB7                              |

| N2          | VDDI7                                    |

| N3          | MSIOD184PB7                              |

| N4          | MSIOD184NB7                              |

| Package Pin | M2S090TS-FGG484 Pin Name                               |

|-------------|--------------------------------------------------------|

| N5          | MSIOD182PB7                                            |

| N6          | MSIOD182NB7                                            |

| N7          | vss                                                    |

| N8          | MSIOD188PB7                                            |

| N9          | VDD                                                    |

| N10         | VSS                                                    |

| N11         | VDD                                                    |

| N12         | VSS                                                    |

| N13         | VDD                                                    |

| N14         | VSS                                                    |

| N15         | VSSNVM                                                 |

| N16         | MSIO8PB3/CAN_RX/GPIO_3_A/USB_DATA1_A                   |

| N17         | MSIO8NB3/CAN_TX_EN_N/GPIO_4_A/USB_DATA2_A              |

| N18         | VSS                                                    |

| N19         | MSIO12PB3/SPI_0_CLK/USB_XCLK_A                         |

| N20         | MSIO12NB3/SPI_0_SDI/GPIO_5_A/USB_DIR_A                 |

| N21         | MSIO13PB3/SPI_0_SDO/GPIO_6_A/USB_STP_A                 |

| N22         | MSIO13NB3/SPI_0_SS0/GPIO_7_A/USB_NXT_A                 |

| P1          | MSIOD187PB7                                            |

| P2          | MSIOD187NB7                                            |

| P3          | MSIOD186NB7                                            |

| P4          | MSIOD186PB7                                            |

| P5          | VDDI7                                                  |

| P6          | MSIOD189PB7                                            |

| P7          | MSIOD189NB7                                            |

| P8          | SERDES_0_VDD                                           |

| P9          | VSS                                                    |

| P10         | VDD                                                    |

| P11         | VSS                                                    |

| P12         | VDD                                                    |

| P13         | VSS                                                    |

| P14         | VDD                                                    |

| P15         | VPP                                                    |

| P16         | MSIO7NB3/CAN_TX/GPIO_2_A/USB_DATA0_A                   |

| P17         | MSIO6PB3/USB_DATA6_B                                   |

| P18         | MSIO6NB3                                               |

| P19         | SC_SPI_SDO                                             |

| P20         | SC_SPI_SS                                              |

| P21         | vss                                                    |

| P22         | MSIO11PB3/CCC_NE0_CLKI0/I2C_1_SDA/GPIO_0_A/USB_DATA3_A |

| Package Pin | M2S090TS-FGG484 Pin Name                               |

|-------------|--------------------------------------------------------|

| R1          | MSIOD190NB7                                            |

| R2          | MSIOD190PB7                                            |

| R3          | MSIOD191PB7                                            |

| R4          | MSIOD191NB7                                            |

| R5          | vss                                                    |

| R6          | CCC_SW0_PLL_VSSA                                       |

| R7          | CCC_SW1_PLL_VDDA                                       |

| R8          | SERDES_0_L01_VDDAIO                                    |

| R9          | vss                                                    |

| R10         | VSS                                                    |

| R11         | VDD                                                    |

| R12         | VSS                                                    |

| R13         | VDD                                                    |

| R14         | VSS                                                    |

| R15         | DEVRST_N                                               |

| R16         | MSIO7PB3                                               |

| R17         | MSIO1PB3/USB_XCLK_B                                    |

| R18         | MSIO1NB3/USB_DIR_B                                     |

| R19         | VDDI3                                                  |

| R20         | SC_SPI_CLK                                             |

| R21         | SC_SPI_SDI                                             |

| R22         | MSIO11NB3/CCC_NE1_CLKI0/I2C_1_SCL/GPIO_1_A/USB_DATA4_A |

| T1          | MSIOD193NB6/SERDES_0_REFCLK0_N                         |

| T2          | VSS                                                    |

| T3          | MSIOD192NB7                                            |

| T4          | MSIOD192PB7                                            |

| T5          | CCC_SW0_PLL_VDDA                                       |

| T6          | SERDES_0_PLL_VSSA                                      |

| T7          | CCC_SW1_PLL_VSSA                                       |

| Т8          | SERDES_0_PLL_VDDA                                      |

| Т9          | SERDES_0_VDD                                           |

| T10         | SERDES_0_L23_VDDAIO                                    |

| T11         | NC                                                     |

| T12         | NC                                                     |

| T13         | MSIO210NB5                                             |

| T14         | VDDI5                                                  |

| T15         | VSS                                                    |

| T16         | MSIO232NB5                                             |

| T17         | vss                                                    |

| T18         | MSIO2PB3/USB_STP_B                                     |

| Package Pin | M2S090TS-FGG484 Pin Name       |

|-------------|--------------------------------|

| T19         | MSIO2NB3/USB_NXT_B             |

| T20         | MSIO5PB3/USB_DATA4_B           |

| T21         | MSIO5NB3/USB_DATA5_B           |

| T22         | VDDI3                          |

| U1          | MSIOD193PB6/SERDES_0_REFCLK0_P |

| U2          | VDDI6                          |

| U3          | MSIOD194PB6/SERDES_0_REFCLK1_P |

| U4          | MSIOD194NB6/SERDES_0_REFCLK1_N |

| U5          | SERDES_0_L01_REXT              |

| U6          | SERDES_0_L01_REFRET            |

| U7          | SERDES_0_L01_VDDAPLL           |

| U8          | SERDES_0_L23_VDDAPLL           |

| U9          | VPP                            |

| U10         | MSIO199PB5                     |

| U11         | MSIO199NB5                     |

| U12         | VSS                            |

| U13         | MSIO210PB5/GB11/VCCC_SE0_CLKI  |

| U14         | MSIO218PB5                     |

| U15         | MSIO218NB5                     |

| U16         | MSIO232PB5                     |

| U17         | MSIO234NB5                     |

| U18         | MSIO238NB5                     |

| U19         | MSIO0PB3                       |

| U20         | VSS                            |

| U21         | MSIO4NB3/USB_DATA3_B           |

| U22         | MSIO4PB3/USB_DATA2_B           |

| V1          | VSS                            |

| V2          | VSS                            |