# UG0726 User Guide PolarFire FPGA Board Design

a **MICROCHIP** company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com www.microsemi.com

©2021 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi | on Hist        | tory                                    | 1  |

|---|--------|----------------|-----------------------------------------|----|

|   | 1.1    |                | n 10.0                                  |    |

|   | 1.2    |                | ា 9.0                                   |    |

|   | 1.3    |                | n 8.0                                   |    |

|   | 1.4    |                | n 7.0                                   |    |

|   |        |                |                                         |    |

|   | 1.5    |                | 1 6.0                                   |    |

|   | 1.6    |                | n 5.0                                   |    |

|   | 1.7    |                | 1 4.0                                   |    |

|   | 1.8    |                | n 3.0                                   |    |

|   | 1.9    |                | n 2.0                                   |    |

|   | 1.10   | Revision       | n 1.0                                   | 2  |

| 2 | PolarF | ire FP         | GA Board Design                         | 3  |

|   | 2.1    | Designir       | ng the Board                            | 3  |

|   | 2.2    | Power S        | Supplies                                | 4  |

|   |        | 2.2.1          | PolarFire Decoupling Capacitors         | 5  |

|   |        | 2.2.2          | Power-Supply Topology                   |    |

|   |        | 2.2.3          | Unused Power Supply                     |    |

|   |        | 2.2.4          | Pin Assignment Tables                   |    |

|   | 2.3    |                | :h                                      |    |

|   | 2.4    |                | Oold Coording                           |    |

|   |        | 2.4.1<br>2.4.2 | Cold Sparing  Hot Socketing (GPIO Only) |    |

|   | 2.5    |                | Thot Socketting (Gr To Only)            |    |

|   | 2.6    |                |                                         |    |

|   | 2.0    |                |                                         |    |

|   |        |                |                                         |    |

|   | 2.8    | 2.8.1          | Programming                             |    |

|   |        | 2.8.2          | SPI Master Mode Programming             |    |

|   |        | 2.8.3          | SPI Slave Mode Programming              |    |

|   |        | 2.8.4          | Special Pins                            |    |

|   | 2.9    | Transce        | iver                                    | 22 |

|   |        | 2.9.1          | Reference Clock                         | 22 |

|   | 2.10   | MIPI Ha        | rdware Design Guidelines                | 22 |

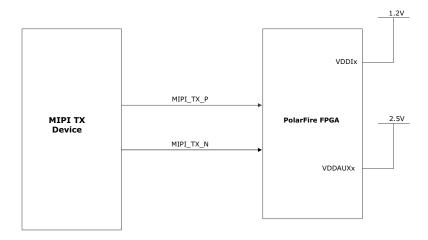

|   |        | 2.10.1         | MIPI RX                                 |    |

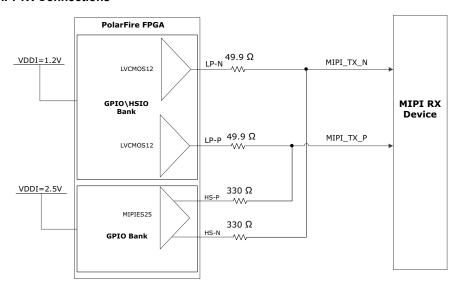

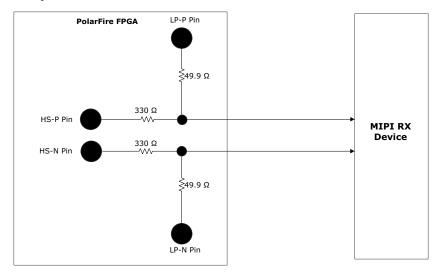

|   |        | 2.10.2         | MIPI TX                                 |    |

|   | 2.11   |                | DC Coupling                             |    |

|   | 2.12   | Brownou        | ut Detection                            | 24 |

| 3 | Board  | Design         | n Checklist                             | 25 |

|   | 3.1    | Prerequ        | isites                                  | 25 |

|   | 3.2    | Design (       | Checklist                               | 25 |

|   | 3.3    | •              | Checklist                               |    |

| 4 | Annen  | ndix. G        | eneral Layout Design Practices          | 29 |

| • | 4.1    |                |                                         |    |

|   | 4.1    |                | iver                                    |    |

|   | 4.2    |                | Lavout Considerations                   |    |

# **Figures**

| Figure 1  | Power Supplies                                                   | 4  |

|-----------|------------------------------------------------------------------|----|

| Figure 2  | Example Power-Supply Topology                                    |    |

| Figure 3  | Option 1 for unused Connections                                  |    |

| Figure 4  | Option 2 for Unused Connections                                  |    |

| Figure 5  | Cold Sparing                                                     |    |

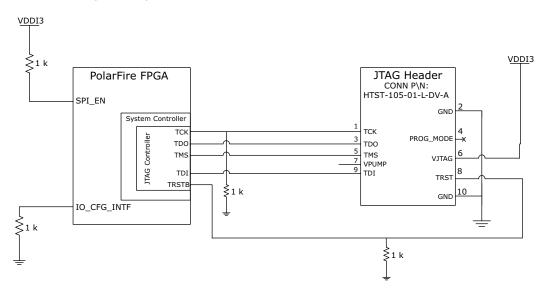

| Figure 6  | JTAG Programming                                                 |    |

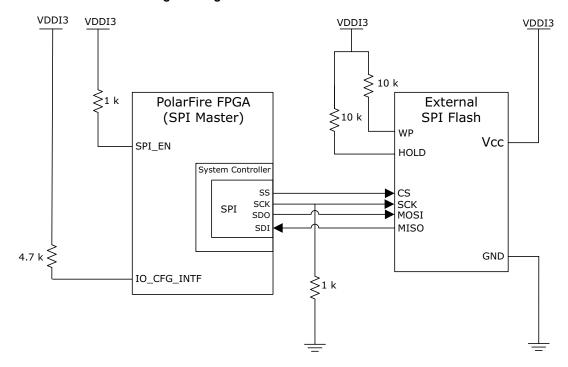

| Figure 7  | SPI Master Mode Programming                                      |    |

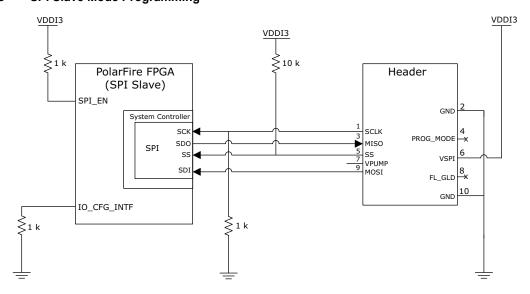

| Figure 8  | SPI Slave Mode Programming                                       |    |

| Figure 9  | MIPI RX Connection                                               |    |

| Figure 10 | MIPI TX Connections                                              | 23 |

| Figure 11 | MIPI TX Layout                                                   | 29 |

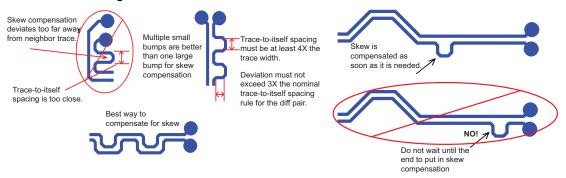

| Figure 12 | Skew Matching                                                    | 30 |

| Figure 13 | Example of Asymmetric and Symmetric Differential Pairs Structure | 30 |

| Figure 14 | Ground Planes for Reference                                      |    |

| Figure 15 | Via Illustration                                                 | 31 |

| Figure 16 | Non-Functional Pads of Via                                       |    |

| Figure 17 | Via-to-Via Pitch                                                 |    |

| Figure 18 | GND Via or Return Via                                            |    |

| Figure 19 | Capacitor Pad Reference Plane                                    | 33 |

# **Tables**

| Table 1  | Supply Pins                                                               |     |

|----------|---------------------------------------------------------------------------|-----|

| Table 2  | Power-Supply Decoupling Capacitors—MPF300T - FCG1152/FCG784 (1mm)         |     |

| Table 3  | Power-Supply Decoupling Capacitors—MPF300T - FCG1152/FCG784/FCG484 (1 mm) | . 6 |

| Table 4  | Power-Supply Decoupling Capacitors—MPF300T - FCVG484 (0.8mm)              |     |

| Table 5  | Power-Supply Decoupling Capacitors—MPF300T - FCSG536 (0.5mm)              |     |

| Table 6  | Power-Supply Decoupling Capacitors—MPF200T - FCVG484 (0.8 mm)             |     |

| Table 7  | Power-Supply Decoupling Capacitors—MPF200T - FCG784/FCG484 (1mm)          |     |

| Table 8  | Power-Supply Decoupling Capacitors—MPF200T - FCSG536 (0.5 mm)             | . ( |

| Table 9  | Power-Supply Decoupling Capacitors—MPF200T - FCSG325 (0.5 mm)             | 1(  |

| Table 10 | Power-Supply Decoupling Capacitors—MPF100T - FCSG325 (0.5 mm)             | 1(  |

| Table 11 | Power-Supply Decoupling Capacitors—MPF100T - FCVG484 (0.8 mm)             | 11  |

| Table 12 | Power-Supply Decoupling Capacitors—MPF100T - FCG484 (1 mm)                | 12  |

| Table 13 | Recommended Decoupling Capacitors For PolarFire Devices                   | 12  |

| Table 14 | Power Regulators                                                          |     |

| Table 15 | Power Sequencing                                                          | 16  |

| Table 16 | Over-Voltage Tolerance                                                    | 17  |

| Table 17 | RC Oscillator Count                                                       | 18  |

| Table 18 | JTAG Pins                                                                 | 19  |

| Table 19 | SPI Master Mode Programming Pins                                          | 2(  |

| Table 20 | Transceiver Support in PolarFire Devices                                  | 22  |

| Table 21 | Design Checklist                                                          |     |

| Table 22 | Layout Checklist                                                          | 27  |

## 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the current publication.

#### 1.1 Revision 10.0

The following is a summary of changes made in this revision.

- Updated the device variant to MPF300T in table title, see Table 2, page 5.

- Added more information in new footnotes for VDD and VDDA in Table 1, page 4.

- Added footnote in Table 2, page 5 to Table 12, page 12 to specify the objective of decoupling capacitors.

- Updated I/O Glitch, page 15 and Table 15, page 16 for power-up and power-down sequencing requirements for mitigating I/O glitch.

#### 1.2 **Revision 9.0**

The following is a summary of changes made in this revision.

- Updated the glitch information in I/O Glitch, page 15.

- Updated Figure 5, page 17 to power VDDI3 (JTAG Bank) required for cold sparing.

## **1.3** Revision 8.0

The following is a summary of changes made in this revision.

- Updated the glitch information in I/O Glitch, page 15.

- Added more information on the VDDI and VDDAUX in Power Supplies, page 4.

## 1.4 **Revision 7.0**

The following is a summary of the changes made in this revision:

- · Added MIPI Hardware Design Guidelines, page 22.

- · Added reset guidelines in Reset, page 18.

- · Added power-supply decoupling capacitors for the following device packages:

- MPF200T-FCG484 (0.8 mm), see Table 7, page 8.

- MPF200T-FCSG536 (0.5 mm), see Table 8, page 9.

- MPF200T-FCG325 (0.5 mm), see Table 9, page 10.

- MPF100T-FCG325 (0.5 mm), see Table 10, page 10.

- MPF100T-FCG484 (0.8 mm), see Table 11, page 11.

## 1.5 **Revision 6.0**

The following is a summary of the changes made in revision 6.0 of this document:

- Reference Voltage (V<sub>REFx</sub>)information updated in Power Supplies, page 4.

- · Added basic information about Pin Assignment Tables, page 15.

- Power-Supply Decoupling Capacitors—MPF300T FCG1152/FCG784/FCG484 updated in Table 3, page 6.

- Power-Supply Decoupling Capacitors—MPF500T FCG1152/FCG784 (1mm), Power-Supply Decoupling Capacitors—MPF200T - FCG784/FCG484 (1mm), and MPF100T - FCG484 (1mm) added in Table 2, page 5, Table 6, page 8, and Table 12, page 12 respectively.

- Added MIPI Hardware Design Guidelines, page 22.

- Added Reset, page 18.

## 1.6 Revision 5.0

The following is a summary of the changes made in revision 5.0 of this document:

- Details of power supply decoupling capacitors for MPF300-FCG1152, MPF300-FCG484, MPF300-FCG784, MPF300-FCVG484, and MPF300-FCSG536 devices were updated. For more information, see Table 3, page 6, Table 4, page 6, and Table 5, page 7.

- XCVR\_REF and VDD\_XCVR\_CLK supply pins details were added. For more information, see Power Supplies, page 4).

- Information about VDDIx and VDDAUXx power supplies was updated. For more information, see Unused Power Supply, page 14.

- A note about the power supply constraint of VDDI3 and VDD\_XCVR\_CLK pins was added. For more

information, see Power Supplies, page 4.

- Details of decoupling capacitors in PolarFire devices were added. For more information, see Table 13, page 12.

- Additional information about VDDIx, VDDAUXx, and VDD\_XCVR\_CLK pins was added. For more

information, see Unused Power Supply, page 14.

- The design checklist for XCVR pins was updated. For more information, see Table 21, page 25.

- Information about VREF was added to core power supply operation details. For more information, see Power Supplies, page 4.

- Information about cold sparing was updated. For more information, see Cold Sparing, page 16.

- JTAG pin details were updated. For more information, see Table 18, page 19.

- The SPI master mode programming connectivity diagram was updated. For more information, see Figure 7, page 20.

- Information about device reset was updated. For more information, see Reset, page 18.

- DDR3 and DDR4 placement and routing guidelines were removed. These guidelines are available in UG0676: PolarFire FPGA DDR Memory Controller User Guide.

#### 1.7 **Revision 4.0**

Revision 4.0 was published in September 2017. The sections *Termination Schemes* and *PCB Capacitor Placement and Mounting Techniques* were removed from this document.

#### 1.8 **Revision 3.0**

Following is a summary of changes made in revision 3.0 of this document:

- Added the Board Design Checklist chapter. For more information, see Board Design Checklist, page 25.

- · Added the Special Pins, page 21 section in the PolarFire FPGA Board Design, page 3 chapter.

- Updated the Power-up sequence for core supplies. For more information, see Power Supplies, page 4 and Power-Supply Topology, page 13.

- Removed a note related to XCVR\_TX and RX signals under the Unused Power Supply, page 14 section.

- Updated the VDDI pin name from VDDIx to VDDI3 in the Device Programming section. For more information, see Device Programming, page 19.

## 1.9 **Revision 2.0**

Following was a summary of changes made in revision 2.0 of this document:

- Values in the Power-Supply Decoupling Capacitors—MPF300-FCG484 table were updated.

- Values and parameters were updated in the SPI Master Mode Programming Pins table. For more information, see Table 19, page 20.

- Updated Figure 2. For more information, see Figure 2, page 13.

#### 1.10 **Revision 1.0**

The first publication of this document.

## 2 PolarFire FPGA Board Design

Good board design practices are required to achieve expected performance from both PCBs and PolarFire<sup>®</sup> devices. High-quality and reliable results depend on minimizing noise levels, preserving signal integrity, meeting impedance and power requirements, and using appropriate transceiver protocols. These guidelines must be treated as a supplement to the standard board-level design practices.

This document is intended for readers who are familiar with the PolarFire device, experienced in digital board design, and know about the electrical characteristics of systems. It discusses power supplies, high-speed interfaces, various control interfaces, and the associated peripheral components of PolarFire FPGAs.

## 2.1 Designing the Board

PolarFire FPGAs are flash-based FPGAs that support various high-speed memory interfaces such as DDR3/DDR4, lowest power 12.7 Gbps transceiver (XCVR), built-in low-power dual PCIe Gen2, and fabric I/O such as high-speed I/O (HSIO) and general-purpose I/O (GPIO).

Subsequent sections discuss the following:

- Power Supplies, page 4

- User I/O, page 16

- Clocks, page 18

- Reset, page 18

- Device Programming, page 19

- Transceiver, page 22

- AC and DC Coupling, page 24

- Brownout Detection, page 24

## 2.2 Power Supplies

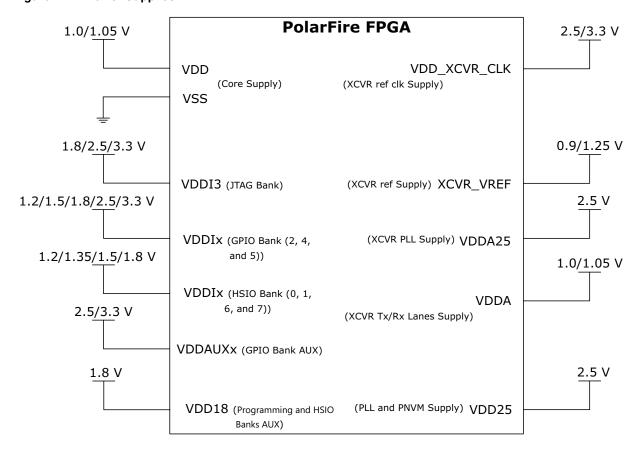

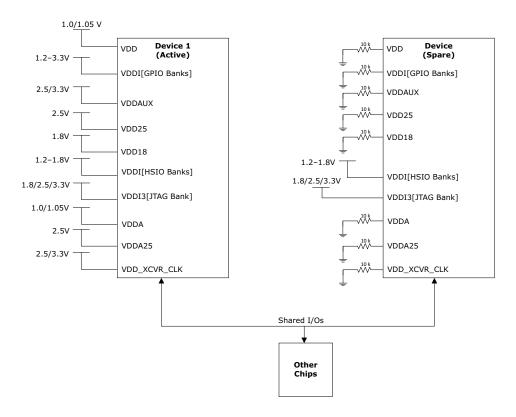

The following illustration shows the typical power supply requirements for PolarFire devices, and the recommended connections of power rails when every part of the device is used in a system. For information on decoupling capacitors associated with individual power supplies, see PolarFire Decoupling Capacitors, page 5.

Figure 1 • Power Supplies

For the device to operate successfully, power supplies must be free from unregulated spikes and the associated grounds must be free from noise. All overshoots and undershoots must be within the absolute maximum ratings provided in the *DS0141: PolarFire FPGA Datasheet*.

The following table lists the various power supplies required for PolarFire FPGAs.

Table 1 • Supply Pins

| Name              | Description                                                |

|-------------------|------------------------------------------------------------|

| XCVR_VREF         | Voltage reference for transceivers                         |

| VDD_XCVR_CLK      | Power to input buffers for the transceiver reference clock |

| VDDA25            | Power to the transceiver PLL                               |

| VDDA <sup>1</sup> | Power to the transceiver TX and RX lanes                   |

| VSS               | Core digital ground                                        |

| VDD <sup>2</sup>  | Device core digital supply                                 |

| VDDI3 (JTAG Bank) | Power to JTAG bank pins                                    |

Table 1 • Supply Pins (continued)

| Name               | Description                                    |

|--------------------|------------------------------------------------|

| VDDIx (GPIO Banks) | Power to GPIO bank pins                        |

| VDDIx (HSIO Banks) | Power to HSIO bank pins                        |

| VDD25              | Power to corner PLLs and PNVM                  |

| VDD18              | Power to programming and HSIO auxiliary supply |

| VDDAUXx            | Power to GPIO auxiliary supply                 |

- VDDA—This supply can be powered to 1.0V or 1.05V. For more information, see tables 4-2 in DS0141: PolarFire FPGA Datasheet. This is a quiet supply for the device. One method would be to use a Linear regulator to ensure the supply is quiet.

- 2. VDD —This supply can be powered to 1.0V or 1.05V. For more information, see tables 4-2 in *DS0141: PolarFire FPGA Datasheet*.

- V<sub>REFx</sub>—is the reference voltage for DDR3 and DDR4 signals. VREF voltages can be generated internally and externally.

- Internal VREF not subjected to PCB and package inductance and capacitance loss. These

changes provide the highest performance and can be programmed as required by DDR

controller.

- External VREF—is fixed and cannot be programed as required. The PCB and package inductance and capacitance impact the V<sub>REF</sub> performance.

If VDDI and VDDAUX need to be configured to the same voltage (2.5V or 3.3V), ensure both VDDI and VDDAUX are supplied from the same regulator. Do not use different regulators to source these rails. This prevents any voltage variations between VDDI and VDDAUX. In this case, the board must not supply the VDDI and VDDAUX from individual voltage supplies.

When a GPIO bank requires the VDDI to be less than 2.5V (1.2V, 1.5V, or 1.8V), the VDDAUX for that bank must be tied to 2.5V supply irrespective of the VDDI supply. The VDDI requires a separate supply for the specific I/O type (1.5V or 1.8V).

**Note:** The on-chip power-on reset circuitry requires the V<sub>DD</sub>, V<sub>DD18</sub>, and V<sub>DD25</sub> supplies to ramp monotonically from 0 V to the minimum recommended operating voltage.

For a detailed pin description, see *UG0722: PolarFire FPGA Packaging and Pin Descriptions User Guide*.

## 2.2.1 PolarFire Decoupling Capacitors

The following table lists the requirement of all decoupling capacitors for the MPF300-FCG1152 device.

Table 2 • Power-Supply Decoupling Capacitors —MPF300T - FCG1152/FCG784 (1mm)

|                                  |        |       |        | Cerami | ic     |       |         | Tantalum |

|----------------------------------|--------|-------|--------|--------|--------|-------|---------|----------|

| Pin Name                         | 4.7 nF | 10 nF | 0.1 μF | 1 μF   | 4.7 μF | 10 μF | F 47 μF | 330 µF   |

| $V_{DD}$                         |        |       | 4      |        |        |       |         | 3        |

| $V_{DD}$ $V_{DD18}$              |        |       | 2      |        |        |       | 2       |          |

| V <sub>DD25</sub>                |        |       | 5      |        |        | 1     |         |          |

| V <sub>DDA</sub>                 | 3      | 1     | 6      |        |        |       | 2       |          |

| V <sub>DDA25</sub>               |        |       | 4      |        |        |       | 1       |          |

| V <sub>DDIO3</sub>               |        |       | 2      |        |        | 1     |         |          |

| V <sub>DDAUXx</sub> <sup>2</sup> |        |       | 2      |        |        |       | 1       |          |

| GPIO Bank <sup>3</sup>           |        |       | 2      |        |        |       | 1       |          |

Table 2 • Power-Supply Decoupling Capacitors 1—MPF300T - FCG1152/FCG784 (1mm) (continued)

|                        |        |       |        | Ceram | ic     |       |       | Tantalum |

|------------------------|--------|-------|--------|-------|--------|-------|-------|----------|

| Pin Name               | 4.7 nF | 10 nF | 0.1 μF | 1 μF  | 4.7 µF | 10 μF | 47 μF | 330 μF   |

| HSIO Bank <sup>4</sup> |        |       | 2      |       |        |       | 1     |          |

| VDD_XCVR_CLK           |        |       | 2      |       |        | 1     |       |          |

| XCVR_VREF              |        |       | 2      |       |        |       |       |          |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA.

Please follow the recommended operational conditions as per DS0141: PolarFire FPGA Datasheet.

- 2. Required Decoupling Capacitor for each VDDAUXx.

- 3. Required Decoupling Capacitor for each GPIO bank.

- 4. Required Decoupling Capacitor for each HSIO bank.

The following table lists the requirement of all decoupling capacitors for the MPF300T-FCG1152/784/484 (1 mm).

Table 3 • Power-Supply Decoupling Capacitors 1—MPF300T - FCG1152/FCG784/FCG484 (1 mm)

|                                  |        |       |        | Ceramic |        |       |       | Tantalum |

|----------------------------------|--------|-------|--------|---------|--------|-------|-------|----------|

| Pin Name                         | 4.7 nF | 10 nF | 0.1 μF | 1 μF    | 4.7 µF | 10 μF | 47 μF | 330 μF   |

| $V_{DD}$                         |        |       | 4      |         |        |       |       | 2        |

| V <sub>DD18</sub>                |        |       | 2      |         |        |       | 2     |          |

| $V_{DD25}$                       |        |       | 5      |         |        |       | 1     |          |

| $V_{DDA}$                        | 3      | 1     | 6      |         |        |       | 1     |          |

| $V_{\text{DDA25}}$               |        |       | 4      |         |        |       | 1     |          |

| V <sub>DDAUXx</sub> <sup>2</sup> |        |       | 5      |         |        |       | 1     |          |

| V <sub>DDIO3</sub>               |        |       | 2      |         |        | 1     |       |          |

| GPIO Bank <sup>3</sup>           |        |       | 2      |         |        |       | 1     |          |

| HSIO Bank <sup>4</sup>           |        |       | 2      |         |        |       | 1     |          |

| VDD_XCVR_CLK                     |        |       | 2      |         |        | 1     |       |          |

| XCVR_VREF                        |        |       | 2      |         |        |       |       |          |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire FPGA Datasheet.

- 2. Required Decoupling Capacitor for each VDDAUXx.

- 3. Required Decoupling Capacitor for each GPIO bank.

- 4. Required Decoupling Capacitor for each HSIO bank.

The following table lists the requirement of all decoupling capacitors for the MPF300-FCVG484 (0.8mm) device.

Table 4 • Power-Supply Decoupling Capacitors 1—MPF300T - FCVG484 (0.8mm)

|                   |      |        |       |        | Ceram | nic    |       |       | Tantalum |

|-------------------|------|--------|-------|--------|-------|--------|-------|-------|----------|

| Pin Name          | 1 nF | 2.2 nF | 10 nF | 0.1 μF | 1 μF  | 4.7 µF | 10 μF | 47 µF | 330 μF   |

| V <sub>DD</sub>   |      |        |       | 4      | 1     |        |       |       | 2        |

| V <sub>DD18</sub> |      |        |       | 2      |       |        |       | 2     |          |

| V <sub>DD25</sub> |      |        |       | 5      |       |        | 1     |       |          |

Table 4 • Power-Supply Decoupling Capacitors 1—MPF300T - FCVG484 (0.8mm) (continued)

|                                  | Ceramic |        |       |             |        |       |       |        |  |

|----------------------------------|---------|--------|-------|-------------|--------|-------|-------|--------|--|

| Pin Name                         | 1 nF    | 2.2 nF | 10 nF | 0.1 μF 1 μF | 4.7 µF | 10 μF | 47 μF | 330 µF |  |

| $V_{DDA}$                        |         | 2      | 2     | 1           |        |       | 1     |        |  |

| V <sub>DDA25</sub>               | 1       |        |       | 1           |        |       | 1     |        |  |

| V <sub>DDAUXx</sub> <sup>2</sup> |         |        |       | 2           |        |       | 1     |        |  |

| V <sub>DDIO3</sub>               |         |        |       | 2           |        | 1     |       |        |  |

| GPIO Bank <sup>3</sup>           |         |        |       | 2           |        |       | 1     |        |  |

| HSIO Bank <sup>4</sup>           |         |        |       | 2           |        |       | 1     |        |  |

| VDD_XCVR_CLK                     |         |        |       | 2           |        | 1     |       |        |  |

| XCVR_VREF                        |         |        |       | 2           |        |       |       |        |  |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire FPGA Datasheet.

The following table lists the requirement of all decoupling capacitors for the MPF300-FCSG536 (0.5mm) device.

Table 5 • Power-Supply Decoupling Capacitors 1—MPF300T - FCSG536 (0.5mm)

|      |        |       |        | Cerami                          | ic                                                                                                                                                                                                                                                                  |                                   |                                                                                                                                                                                                                                                    | Tantalum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|--------|-------|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 nF | 2.2 nF | 10 nF | 0.1 μF | 1 μF                            | 4.7 µF                                                                                                                                                                                                                                                              | 10 μF                             | 47 μF                                                                                                                                                                                                                                              | 330 µF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |        |       | 4      | 1                               |                                                                                                                                                                                                                                                                     |                                   |                                                                                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |        | 1     | 2      |                                 |                                                                                                                                                                                                                                                                     |                                   | 2                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 5      |                                 |                                                                                                                                                                                                                                                                     | 1                                 |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2    | 3      | 1     | 1      |                                 |                                                                                                                                                                                                                                                                     |                                   | 1                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1    |        |       | 1      |                                 |                                                                                                                                                                                                                                                                     |                                   | 1                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 2      |                                 |                                                                                                                                                                                                                                                                     |                                   | 1                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 2      |                                 |                                                                                                                                                                                                                                                                     | 1                                 |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 2      |                                 |                                                                                                                                                                                                                                                                     |                                   | 1                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 2      |                                 |                                                                                                                                                                                                                                                                     |                                   | 1                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 2      |                                 |                                                                                                                                                                                                                                                                     | 1                                 |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 2      |                                 |                                                                                                                                                                                                                                                                     |                                   |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        |       | 1      | 4 1 2 5 2 3 1 1 1 2 2 2 2 2 2 2 | 1 nF     2.2 nF     10 nF     0.1 μF     1 μF       4     1       5     5       2     3     1     1       1     1     2       2     2     2       2     2     2       2     2     2       2     2     2       2     2     2       2     2     2       2     2     2 | 4 1 1 2 5 2 3 1 1 1 2 2 2 2 2 2 2 | 1 nF     2.2 nF     10 nF     0.1 μF     1 μF     4.7 μF     10 μF       4     1     1     2     1       5     5     1     1       2     3     1     1     1       1     1     2     1       2     2     1       2     2     1       2     2     1 | 1 nF         2.2 nF         10 nF         0.1 μF         1 μF         4.7 μF         10 μF         47 μF           4         1         2         2         2           5         1         1         1         1           2         3         1         1         1         1         1           1         1         2         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire FPGA Datasheet.

<sup>2.</sup> Required Decoupling Capacitor for each VDDAUXx.

<sup>3.</sup> Required Decoupling Capacitor for each GPIO bank.

<sup>4.</sup> Required Decoupling Capacitor for each HSIO bank.

<sup>2.</sup> Required Decoupling Capacitor for each VDDAUXx.

<sup>3.</sup> Required Decoupling Capacitor for each GPIO bank.

<sup>4.</sup> Required Decoupling Capacitor for each HSIO bank.

Table 6 • Power-Supply Decoupling Capacitors 1—MPF200T - FCG784/FCG484 (1mm)

|                                  |        |       |        | Cerami | ic     |       |       | Tantalum |

|----------------------------------|--------|-------|--------|--------|--------|-------|-------|----------|

| Pin Name                         | 4.7 nF | 10 nF | 0.1 μF | 1 μF   | 4.7 µF | 10 μF | 47 μF | 330 μF   |

| $V_{DD}$                         |        | 2     | 2      |        |        |       |       | 2        |

| V <sub>DD18</sub>                |        |       | 2      |        |        |       | 2     |          |

| V <sub>DD25</sub>                |        |       | 5      |        |        | 1     |       |          |

| $V_{DDA}$                        | 3      | 1     | 6      |        |        |       | 1     |          |

| V <sub>DDA25</sub>               |        |       | 4      |        |        |       | 1     |          |

| V <sub>DDIO3</sub>               |        |       | 2      |        |        | 1     |       |          |

| V <sub>DDAUXx</sub> <sup>2</sup> |        |       | 2      |        |        |       | 1     |          |

| GPIO Bank <sup>3</sup>           |        |       | 2      |        |        |       | 1     |          |

| HSIO Bank <sup>4</sup>           |        |       | 2      |        |        |       | 1     |          |

| VDD_XCVR_CLK                     |        |       | 2      |        |        | 1     |       |          |

| XCVR_VREF                        |        |       | 2      |        |        |       |       |          |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire FPGA Datasheet.

The following table lists the requirement of all decoupling capacitors for the MPF200T-FCG484 (0.8 mm) device

Table 7 • Power-Supply Decoupling Capacitors 1—MPF200T - FCVG484 (0.8 mm)

| Din Name               |      |        |        |       | Ceramic |      |        |       |       | Tantalum |

|------------------------|------|--------|--------|-------|---------|------|--------|-------|-------|----------|

| Pin Name               | 1 nF | 2.2 nF | 4.7 nF | 10 nF | 0.1 μF  | 1 μF | 4.7 μF | 10 μF | 47 μF | 330 μF   |

| $V_{DD}$               |      |        |        |       | 4       | 1    |        |       |       | 2        |

| V <sub>DD18</sub>      |      |        |        |       | 2       |      |        |       | 2     |          |

| V <sub>DD25</sub>      |      |        |        |       | 5       |      |        | 1     |       |          |

| $V_{DDA}$              |      | 2      |        | 2     | 1       |      |        |       | 1     |          |

| V <sub>DDA25</sub>     | 1    |        |        |       | 1       |      |        |       | 1     |          |

| V <sub>DDIO3</sub>     |      |        |        |       | 2       |      |        | 1     |       |          |

| VDDAUXx <sup>2</sup>   |      |        |        |       | 2       |      |        |       | 1     |          |

| GPIO Bank <sup>3</sup> |      |        |        |       | 2       |      |        |       | 1     |          |

| 4<br>HSIO Bank         |      |        |        |       | 2       |      |        |       | 1     |          |

| VDD_XCVR_CLK           |      |        |        |       | 2       |      |        | 1     |       |          |

| XCVR_VREF              |      |        |        |       | 2       |      |        |       |       |          |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire FPGA Datasheet.

<sup>2.</sup> Required Decoupling Capacitor for each VDDAUXx.

<sup>3.</sup> Required Decoupling Capacitor for each GPIO bank.

<sup>4.</sup> Required Decoupling Capacitor for each HSIO bank.

<sup>2.</sup> Required Decoupling Capacitor for each VDDAUXx.

<sup>3.</sup> Required Decoupling Capacitor for each GPIO bank.

<sup>4.</sup> Required Decoupling Capacitor for each HSIO bank.

The following table lists the requirement of all decoupling capacitors for the MPF200T-FCSG536 (0.5 mm) device.

Table 8 • Power-Supply Decoupling Capacitors 1—MPF200T - FCSG536 (0.5 mm)

| Din Nama               |      | ·      |        |       | Cera   | mic  | ·      |       |       | Tantalum |

|------------------------|------|--------|--------|-------|--------|------|--------|-------|-------|----------|

| Pin Name               | 1 nF | 2.2 nF | 4.7 nF | 10 nF | 0.1 μF | 1 μF | 4.7 µF | 10 μF | 47 µF | 330 µF   |

| V <sub>DD</sub>        |      |        |        |       | 4      | 1    |        |       |       | 2        |

| V <sub>DD18</sub>      |      |        |        |       | 2      |      |        |       | 2     |          |

| V <sub>DD25</sub>      |      |        |        |       | 5      |      |        | 1     |       |          |

| $V_{DDA}$              | 2    | 3      |        | 1     | 1      |      |        |       | 1     |          |

| V <sub>DDA25</sub>     | 1    |        |        |       | 1      |      |        |       | 1     |          |

| V <sub>DDIO3</sub>     |      |        |        |       | 2      |      |        | 1     |       |          |

| VDDAUXx <sup>2</sup>   |      |        |        |       | 2      |      |        |       | 1     |          |

| GPIO Bank <sup>3</sup> |      |        |        |       | 2      |      |        |       | 1     |          |

| 4<br>HSIO Bank         |      |        |        |       | 2      |      |        |       | 1     |          |

| VDD_XCVR_CLK           |      |        |        |       | 2      |      |        | 1     |       |          |

| XCVR_VREF              |      |        |        |       | 2      |      |        |       |       |          |

<sup>1.</sup> The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per *DS0141: PolarFire FPGA Datasheet*.

<sup>2.</sup> Required Decoupling Capacitor for each VDDAUXx.

<sup>3.</sup> Required Decoupling Capacitor for each GPIO bank.

<sup>4.</sup> Required Decoupling Capacitor for each HSIO bank.

The following table lists the requirement of all decoupling capacitors for the MPF200T-FCG325 (0.5 mm) device.

Table 9 • Power-Supply Decoupling Capacitors 1—MPF200T - FCSG325 (0.5 mm)

| Pin Name               |      |        |        |       | Ceram  | ic   |        |       |       | Tantalum |

|------------------------|------|--------|--------|-------|--------|------|--------|-------|-------|----------|

|                        | 1 nF | 2.2 nF | 4.7 nF | 10 nF | 0.1 μF | 1 μF | 4.7 µF | 10 μF | 47 µF | 330 µF   |

| V <sub>DD</sub>        |      |        |        |       | 4      | 1    |        |       |       | 2        |

| V <sub>DD18</sub>      |      |        |        |       | 2      |      |        |       | 2     |          |

| V <sub>DD25</sub>      |      |        |        |       | 5      |      |        | 1     |       |          |

| V <sub>DDA</sub>       |      | 1      | 1      | 1     | 1      |      |        |       | 1     |          |

| V <sub>DDA25</sub>     | 1    |        |        |       | 1      |      |        |       | 1     |          |

| V <sub>DDIO3</sub>     |      |        |        |       | 2      |      |        | 1     |       |          |

| VDDAUXx <sup>2</sup>   |      |        |        |       | 2      |      |        |       | 1     |          |

| GPIO Bank <sup>3</sup> |      |        |        |       | 2      |      |        |       | 1     |          |

| HSIO Bank              |      |        |        |       | 2      |      |        |       | 1     |          |

| VDD_XCVR_CLK           |      |        |        |       | 2      |      |        | 1     |       |          |

| XCVR_VREF              |      |        |        |       | 2      |      |        |       |       |          |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire FPGA Datasheet.

- 2. Required Decoupling Capacitor for each VDDAUXx.

- 3. Required Decoupling Capacitor for each GPIO bank.

- 4. Required Decoupling Capacitor for each HSIO bank.

The following table lists the requirement of all decoupling capacitors for the MPF100T-FCSG325 (0.5 mm) device.

Table 10 • Power-Supply Decoupling Capacitors 1—MPF100T - FCSG325 (0.5 mm)

|                        |      |        |        |       | Ceramio | •    |        |       |       | Tantalum |

|------------------------|------|--------|--------|-------|---------|------|--------|-------|-------|----------|

| Pin Name               | 1 nF | 2.2 nF | 4.7 nF | 10 nF | 0.1 μF  | 1 μF | 4.7 μF | 10 μF | 47 μF | 330 µF   |

| V <sub>DD</sub>        |      |        |        |       | 4       | 1    |        |       |       | 1        |

| V <sub>DD18</sub>      |      |        |        |       | 2       |      |        |       | 2     |          |

| V <sub>DD25</sub>      |      |        |        |       | 5       |      |        | 1     |       |          |

| $V_{DDA}$              |      | 1      | 1      | 1     | 1       |      |        |       | 1     |          |

| V <sub>DDA25</sub>     | 1    |        |        |       | 1       |      |        |       | 1     |          |

| V <sub>DDIO3</sub>     |      |        |        |       | 2       |      |        | 1     |       |          |

| VDDAUXx <sup>2</sup>   |      |        |        |       | 2       |      |        |       | 1     |          |

| GPIO Bank <sup>3</sup> |      |        |        |       | 2       |      |        |       | 1     |          |

| HSIO Bank <sup>4</sup> |      |        |        |       | 2       |      |        |       | 1     |          |

| VDD_XCVR_CLK           |      |        |        |       | 2       |      |        | 1     |       |          |

| XCVR_VREF              |      |        |        |       | 2       |      |        |       |       |          |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed

on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective

power delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire

FPGA Datasheet.

<sup>2.</sup> Required Decoupling Capacitor for each VDDAUXx.

- 3. Required Decoupling Capacitor for each GPIO bank.

- 4. Required Decoupling Capacitor for each HSIO bank.

The following table lists the requirement of all decoupling capacitors for the MPF100T-FCVG484 (0.8 mm) device.

Table 11 • Power-Supply Decoupling Capacitors —MPF100T - FCVG484 (0.8 mm)

|                        |      |        |        |       | Ceramic |      |        |       |       | Tantalum |

|------------------------|------|--------|--------|-------|---------|------|--------|-------|-------|----------|

| Pin Name               | 1 nF | 2.2 nF | 4.7 nF | 10 nF | 0.1 μF  | 1 μF | 4.7 µF | 10 μF | 47 μF | 330 μF   |

| $V_{DD}$               |      |        |        |       | 4       | 1    |        |       |       | 1        |

| V <sub>DD18</sub>      |      |        |        |       | 2       |      |        |       | 2     |          |

| V <sub>DD25</sub>      |      |        |        |       | 5       |      |        | 1     |       |          |

| V <sub>DDA</sub>       |      | 2      |        | 2     | 1       |      |        |       | 1     |          |

| V <sub>DDA25</sub>     | 1    |        |        |       | 1       |      |        |       | 1     |          |

| V <sub>DDIO3</sub>     |      |        |        |       | 2       |      |        | 1     |       |          |

| VDDAUXx <sup>2</sup>   |      |        |        |       | 2       |      |        |       | 1     |          |

| GPIO Bank <sup>3</sup> |      |        |        |       | 2       |      |        |       | 1     |          |

| 4<br>HSIO Bank         |      |        |        |       | 2       |      |        |       | 1     |          |

| VDD_XCVR_CLK           |      |        |        |       | 2       |      |        | 1     |       |          |

| XCVR_VREF              |      |        |        |       | 2       |      |        |       |       |          |

The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed

on a different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power

delivery to the FPGA. Please follow the recommended operational conditions as per DS0141: PolarFire FPGA

Datasheet.

- 2. Required Decoupling Capacitor for each VDDAUXx.

- 3. Required Decoupling Capacitor for each GPIO bank.

- 4. Required Decoupling Capacitor for each HSIO bank.

Table 12 • Power-Supply Decoupling Capacitors—MPF100T - FCG484 (1 mm)

|                                  | •      | •     |        | Ceram | ic     |       |       | Tantalun |

|----------------------------------|--------|-------|--------|-------|--------|-------|-------|----------|

| Pin Name                         | 4.7 nF | 10 nF | 0.1 μF | 1 μF  | 4.7 µF | 10 μF | 47 μF | 330 µF   |

| $V_{DD}$                         |        | 2     | 2      |       |        |       |       | 1        |

| V <sub>DD18</sub>                |        |       | 2      |       |        |       | 2     |          |

| V <sub>DD25</sub>                |        |       | 5      |       |        | 1     |       |          |

| $V_{DDA}$                        | 3      | 1     | 6      |       |        |       | 1     |          |

| V <sub>DDA25</sub>               |        |       | 4      |       |        |       | 1     |          |

| V <sub>DDIO3</sub>               |        |       | 2      |       |        | 1     |       |          |

| V <sub>DDAUXx</sub> <sup>1</sup> |        |       | 2      |       |        |       | 1     |          |

| GPIO Bank <sup>2</sup>           |        |       | 2      |       |        |       | 1     |          |

| HSIO Bank <sup>3</sup>           |        |       | 2      |       |        |       | 1     |          |

| VDD_XCVR_CLK                     |        |       | 2      |       |        | 1     |       |          |

| XCVR_VREF                        |        |       | 2      |       |        |       |       |          |

| VDD_XCVR_CLK<br>XCVR_VREF        |        |       |        |       |        | 1     |       |          |

- 1. Required Decoupling Capacitor for each VDDAUXx.

- 2. Required Decoupling Capacitor for each GPIO bank.

- 3. Required Decoupling Capacitor for each HSIO bank.

**Note:** The guidelines are provided on how to effectively decouple only the FPGA device. If the power source is placed on different PCB or delivered through interconnects (flex cables or connectors), please ensure an effective power delivery to the FPGA. Please follow the recommended operational conditions as per *DS0141: PolarFire FPGA Datasheet*.

Decoupling capacitors other than those listed in the previous tables can be used if the physical sizes of capacitors meet or exceed the performance of the network given in this example. Substitution would require analyzing the resulting power distribution system's impedance versus frequency to ensure that no resonant impedance spikes the result. See Figure 1, page 4 for power supply design.

For more information about the internal package capacitance for power supplies associated with PolarFire packages, see section 2.4.2.1 section of *UG0722: PolarFire FPGA Packaging and Pin Descriptions User Guide*.

The following table lists the required decoupling capacitors for PolarFire packages.

**Table 13 • Recommended Decoupling Capacitors For PolarFire Devices**

| De-Cap Value | Part Number        | Package | Description                        |

|--------------|--------------------|---------|------------------------------------|

| 0.1 μF       | GRM155R71C104KA88D | 0402    | For 1 mm package                   |

| 10 nF        | GRM15XR11C103KA86  | 0402    | For 1 mm package                   |

| 4.7 nF       | GRM155R11H472KA01  | 0402    | For 1 mm package                   |

| 10 μF        | GRM21BR71A106KE51  | 0805    | Bulk Caps (for 0.5, 0.8, and 1 mm) |

| 47 μF        | GRM31CR61A476KE15  | 1206    | Bulk Caps (for 0.5, 0.8, and 1 mm) |

| 330 µF       | T495D337K010ATE150 | 2917    | Bulk Caps (for 0.5, 0.8, and 1 mm) |

| 1 nF         | GRM033R71C102KA01  | 0201    | For 0.8/0.5 mm package             |

| 2.2 nF       | GRM033R71A103KA01  | 0201    | For 0.8/0.5 mm package             |

| 10 nF        | GRM033R71A103KA01  | 0201    | For 0.8/0.5 mm package             |

| 0.1 μF       | GRM033C71C104KE14  | 0201    | For 0.8/0.5 mm package             |

**Note:** The user can use equivalent capacitor values from a different vendor. For more information about Packaging Decoupling Capacitors, see *UG0722: PolarFire FPGA Packaging and Pin Descriptions User Guide.*

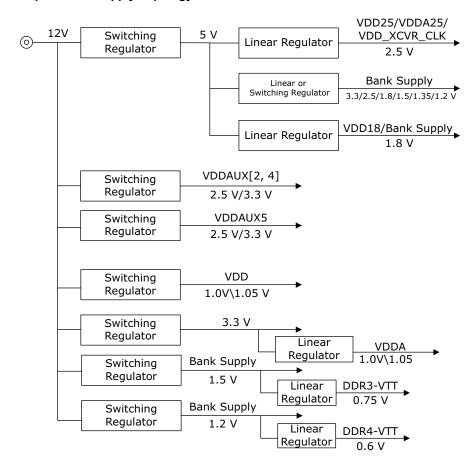

## 2.2.2 Power-Supply Topology

PolarFire FPGAs require multiple power supplies. Figure 2, page 13 shows a power supply topology example for generating the required power supplies from a single 12 V source. This example is based on the PolarFire MPF300-FCG1152 device with DDR3 and DDR4 interfaces.

Figure 2 • Example Power-Supply Topology

The following table lists the suggested Microchip power regulators for PolarFire FPGA voltage rails.

Table 14 • Power Regulators

| Part Number      | Description                                                                                 | Current                                                                                                                                                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIC24055YJL-TR   | IC REG BUCK ADJ 12A SYNC 28QFN                                                              | 12A                                                                                                                                                                                                                                                                                |

| MIC45212-2YMP-T1 | DC DC CONVERTER 0.8-5.5V 77W                                                                | 14A                                                                                                                                                                                                                                                                                |

| MIC24055YJL-TR   | IC REG BUCK ADJ 12A SYNC 28QFN                                                              | 12A                                                                                                                                                                                                                                                                                |

| MIC24046YFL-TR   | IC REG BUCK PROG 5A SYNC 20VQFN                                                             | 5A                                                                                                                                                                                                                                                                                 |

| MIC23303YML-T5   | IC REG BUCK ADJ 3A SYNC 12DFN                                                               | 3A                                                                                                                                                                                                                                                                                 |

| MIC23303YML-T5   | IC REG BUCK ADJ 3A SYNC 12DFN                                                               | 3A                                                                                                                                                                                                                                                                                 |

| MIC23303YML-T5   | IC REG BUCK ADJ 3A SYNC 12DFN                                                               | 3A                                                                                                                                                                                                                                                                                 |

|                  | MIC24055YJL-TR MIC45212-2YMP-T1 MIC24055YJL-TR MIC24046YFL-TR MIC23303YML-T5 MIC23303YML-T5 | MIC24055YJL-TR IC REG BUCK ADJ 12A SYNC 28QFN MIC45212-2YMP-T1 DC DC CONVERTER 0.8-5.5V 77W MIC24055YJL-TR IC REG BUCK ADJ 12A SYNC 28QFN MIC24046YFL-TR IC REG BUCK PROG 5A SYNC 20VQFN MIC23303YML-T5 IC REG BUCK ADJ 3A SYNC 12DFN MIC23303YML-T5 IC REG BUCK ADJ 3A SYNC 12DFN |

Table 14 • Power Regulators (continued)

| Voltage rail                   | Part Number    | Description                     | Current |

|--------------------------------|----------------|---------------------------------|---------|

| VDDAUX5                        | MIC23303YML-T5 | IC REG BUCK ADJ 3A SYNC 12DFN   | 3A      |

| VTT_DDR4 (0.6V)                | MIC5166YML-TR  | IC PWR SUP 3A HS DDR TERM 10MLF | 3A      |

| VTT_DDR3 (0.75V)               | MIC5166YML-TR  | IC PWR SUP 3A HS DDR TERM 10MLF | 3A      |

| VDDIO (1.8V)                   | MIC24046YFL-TR | IC REG BUCK PROG 5A SYNC 20VQFN | 5A      |

| VDDA (1.0V)                    | MIC69502WR     | IC REG LINEAR POS ADJ 5A SPAK-7 | 5A      |

| VDD25, VDDA25,<br>VDD_XCVR_CLK | MIC69502WR     | IC REG LINEAR POS ADJ 5A SPAK-7 | 5A      |

| VDD18                          | MIC69502WR     | IC REG LINEAR POS ADJ 5A SPAK-7 | 5A      |

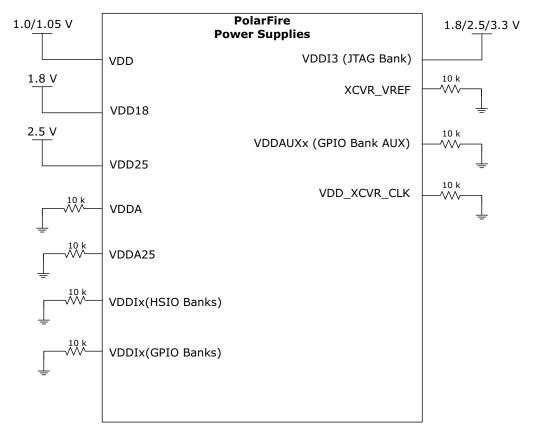

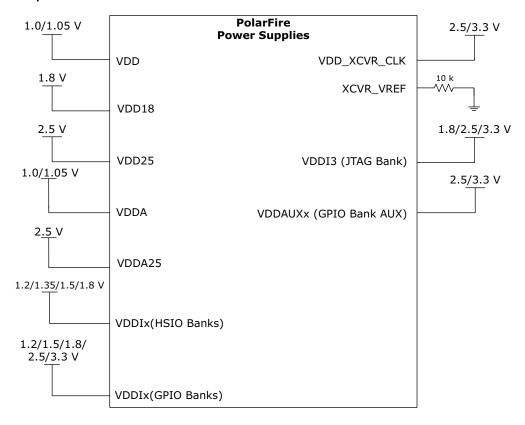

## 2.2.3 Unused Power Supply

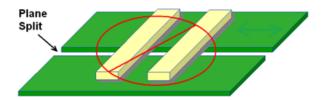

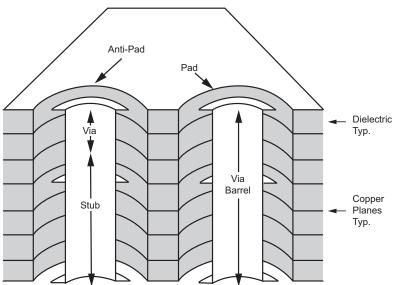

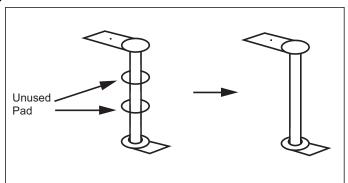

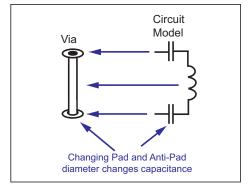

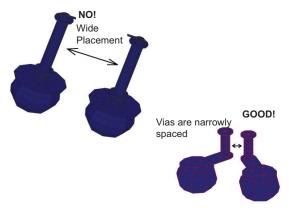

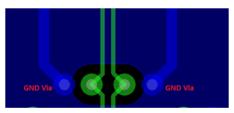

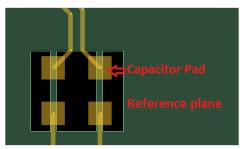

Figure 3, page 14 shows how power supplies may be configured when not in use and also to reduce leakage and power for the system.