# DC-20 GHz Programmable Binary Prescaler

#### **Features**

- Wide Operating Range: DC-20 GHz

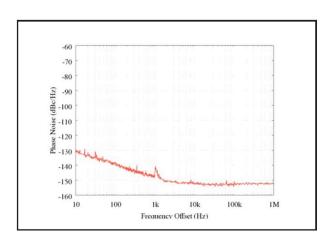

- Low SSB Phase Noise: -153 dBc @ 10 kHz

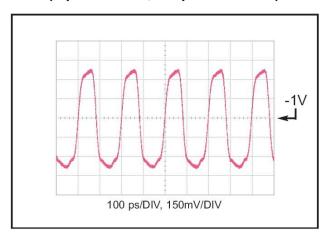

- Large Output Swings: >1 V ppk/side

- Single-Ended and/or Differential Operation

- Low power consumption: 0.6 W

- 4x4 QFN package

- 3 Dividers-in-One

## **Description**

The UXC20P is a low noise programmable prescaler featuring either divide-by-2, divide-by-4, or divide-by-8 division ratios. The device features differential inputs and outputs, adjustable output swing and high input sensitivity. The control inputs are CMOS and LVTTL compatible. The UXC20P is packaged in a 24 pin, 4 mm x 4 mm leadless surface mount package.

## **Application**

The UXC20P can be used as a general purpose, fixed modulus prescaler in high frequency PLLs. The low phase noise of the divider makes it ideal for generating low jitter, synchronous clocks in telecom applications.

#### **Pad Metallization**

The QFN package pad metallization consists of a Ni/Pd/Au plating over a Cu(c194) leadframe.

#### Key Specifications ( $T = 25^{\circ}C$ ):

Vee = -3.3 V, lee = 165 mA,  $Zo=50\Omega$

| Parameter  | Description                      | Min | Тур  | Max |

|------------|----------------------------------|-----|------|-----|

| Fin (GHz)  | Input Frequency                  | DC* | -    | 20  |

| Pin (dBm)  | Nominal Input Power              | -10 | 0    | 10  |

| Pout (dBm) | Nominal Output Power             | -5  | 5    | -   |

| £ (dBc/Hz) | SSB Phase Noise @10 kHz Offset   | -   | -153 | -   |

| PDC (mW)   | DC Power Dissipation             | -   | 430  | -   |

| θjc (°C/W) | Junction-Case Thermal Resistance | -   | 20   | -   |

<sup>\*</sup> Low frequency limit dependent on input edge speed

# **Frequency Divider Application**

## **Return Loss of Differential Input Ports**

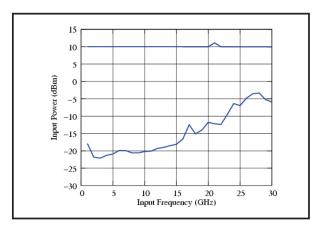

**Input Sensitivity Window**

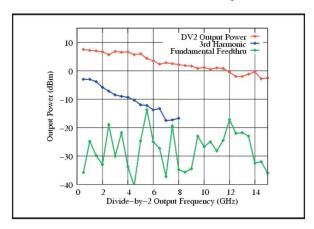

Divide-by-(8/3) Output (Input: 10 GHz; Output: 3.75 GHz)

## **Return Loss of Differential Output Ports**

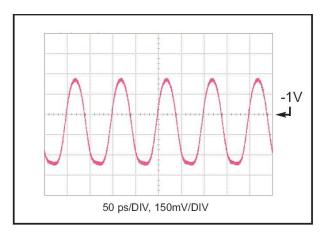

Divide-by-2 Output (Input: 10 GHz; Output: 5 GHz)

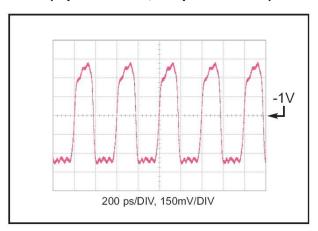

Divide-by-2048 Output (Input: 10 GHz; Output: 4.9 MHz)

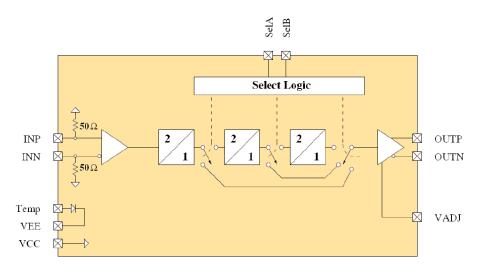

# **Functional Block Diagram**

**Table 1: Pin Description**

| Port Name | Description                         | Notes                                            |

|-----------|-------------------------------------|--------------------------------------------------|

| INP       | Prescaler Input, Positive Terminal  | CML signal levels                                |

| INN       | Prescaler Input, Negative Terminal  | CML signal levels                                |

| OUTP      | Prescaler Output, Positive Terminal | Requires DC return path to VCC                   |

| OUTN      | Prescaler Output, Negative Terminal | Requires DC return path to VCC                   |

| VADJ      | Output Amplitude Control            | Tie to VCC via resistor, refer to text for value |

| SelA      | Divider Select Control Line         | Divider Select, See Table 1, defaults to logic 0 |

| SelB      | Divider Select Control Line         | Divider Select, See Table 1, defaults to logic 0 |

| Temp      | Temperature Diode                   | Optional Temperature diode, refer to text        |

| VCC       | RF & DC Ground                      | -                                                |

| VEE       | -3.3 V @ 165 mA                     | Negative Supply Voltage                          |

**Table 2: Divider Mode Select Logic**

| SelA | SelB | Mode        | DC Current |

|------|------|-------------|------------|

| 0    | 0    | Not Valid   | -          |

| 1    | 0    | Divide-by-8 | 165 mA     |

| 1    | 1    | Divide-by-2 | 150 mA     |

**Table 3: Control Voltages**

| State          | Bias Condition | Comment                |

|----------------|----------------|------------------------|

| Low (logic 0)  | VEE @ 0 mA     | Default condition (in- |

| High (logic 1) | VCC @ 1 mA     | ternally pulled low)   |

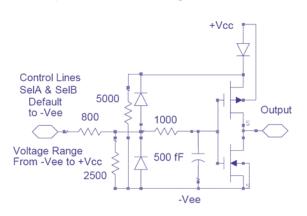

## **Simplified Control Logic Schematic**

## **Application Notes**

#### **Divider Mode:**

The UXC20P supports four division ratios controlled by two select lines which are compatible with CMOS/LVTTL signaling levels. Table 1 lists the four states for the given logic levels on the SelA and SelB select lines. For any of the four modes, circuitry which is not used is automatically powered down to reduce power consumption.

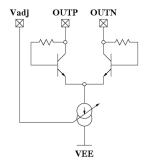

## **Divider Outputs:**

The equivalent circuit of the divider outputs is shown on the below. The outputs require a DC return path capable of handling ~35 mA per side. If DC coupling is employed, the DC resistance of the receiving circuits should be ~50  $\Omega$  (or less) to VCC to prevent excessive common mode voltage from saturating the prescaler outputs. If AC coupling is used, the perfect embodiment is shown in figure 2. The discrete R/L/C elements should be resonance free up to the maximum frequency of operation for broadband applications.

The output amplitude can be adjusted over a 1.5:1 range by one of the two methods The Vadj pin voltage can be set to VCC for maximum amplituded or VCC-1.3 V for an amplitude ~2/3 the max swing. Voltages between these two values will produce a linear change in output swing. Alternatively, users can use a 1k potentiometer or fixed resistor tied between Vadj and VCC. Resistor values approaching 0 ohms will lead to the maximum swing, while values approaching 1k will lead to the minimum output swing. Users who only need/want the maximum swing should simply tie Vadj to VCC.

## **Equivalent Circuit of Output Buffer**

## **Recommended Circuit for AC Coupled Outputs**

$$C = \frac{L}{R \cdot R}$$

OUT

$$R = 50 \Omega$$

$$L = \frac{R}{2 \cdot \pi \cdot f_{low}}$$

$$VCC$$

$$f_{low} = lowest freq of interest$$

## **Low Frequency Operation:**

Low frequency operation is limited by external bypass capacitors and the slew rate of the input clock. The next paragraph shows the calculations for the bypass capacitors. If DC coupled, the device operates down to DC for square-wave inputs. Sine-wave inputs are limited to ~50 MHz due to the 10 dBm max input power limitation.

The values of the coupling capacitors for the high-speed inputs and outputs (I/O's) are determined by the lowest frequency the IC will be operated at.

$$C >> \frac{1}{2 \cdot \pi \cdot 50\Omega \cdot f_{lowest}}$$

For example to use the device below 30 kHz, coupling capacitors should be larger than 0.1uF.

## **Temperature Diode:**

An optional on chip temperature diode is provided for users interested in evaluating the IC's temperature. A single resistor to VCC establishes a nominal current thru the diode. The voltage developed across the temperature pin (pin 8) referenced to VEE (pin 9) can then be used to indicate the surface temperature of the IC. The plot below was obtained by forcing a fixed current thru the diode for an unbiased device at multiple temperatures and fitting a line to the data to allow extrapolation over a range of temperatures.

# Diode Voltage vs Temp for 2 Bias Currents

## Package Heatsink:

The package backside provides the primary heat conduction path and should be attached to a good heatsink on the PC board to maximize performance. User PC boards should maximize the contact area to the package paddle and contain an array of vias to aid thermal conduction to either a backside heatsink or internal copper planes.

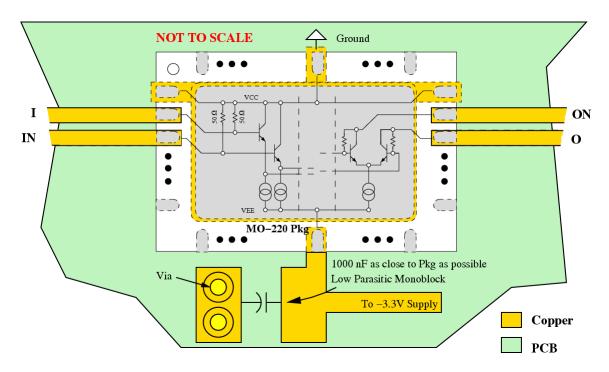

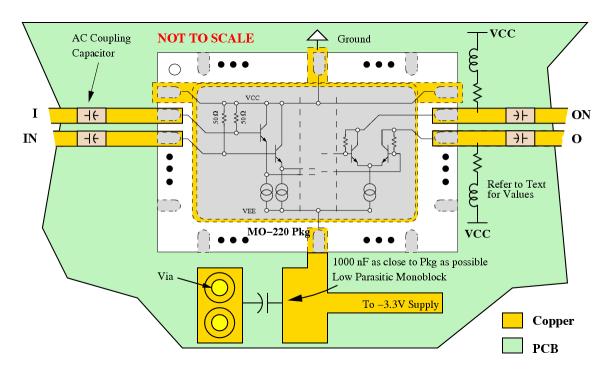

## IC Assembly:

The device is designed to operate with either single-ended or differential inputs. Figures 4, 5 & 6 show the IC assembly diagrams for positive and negative supply voltages. In either case the supply should be capacitively bypassed to the ground to provide a good AC ground over the frequency range of interest. The backside of the chip should be connected to a good thermal heat sink.

All RF I/O's are connected to VCC through on-chip termination resistors. This implies that when VCC is not DC grounded (as in the case of positive supply), the RF I/O's should be AC coupled through series capacitors unless the connecting circuit can generate the correct levels through level shifting.

## CML Logic Levels for DC Coupling (T = $25^{\circ}$ C):

Assuming 50 Ω Terminations at Inputs and Outputs

|        | Parameter               |                            |                             | Minimum      | Typical     | Maximum     |

|--------|-------------------------|----------------------------|-----------------------------|--------------|-------------|-------------|

| Input  | Differential {          | ſ                          | Logic Input <sub>high</sub> | Vcc          | Vcc         | Vcc         |

|        |                         | ι                          | Logic Input <sub>low</sub>  | Vcc - 0.05 V | Vcc - 0.3 V | Vcc - 1 V   |

|        | Single {                | Į                          | Logic Input <sub>high</sub> | Vcc + 0.05 V | Vcc + 0.3 V | Vcc + 1 V   |

|        |                         | ι                          | Logic Input <sub>low</sub>  | Vcc - 0.05 V | Vcc - 0.3 V | Vcc - 1 V   |

| Output | Differential & Single { | Ş                          | Logic Input <sub>high</sub> | Vcc - 0.9 V  | Vcc – 0.6 V | Vcc – 0.5 V |

|        |                         | Logic Input <sub>low</sub> | Vcc – 1.3 V                 | Vcc – 1.6 V  | Vcc – 1.7 V |             |

## **Differential vs. Single-Ended:**

The UXC20P is fully differential to maximize signal-to-noise ratios for high-speed operation. High speed inputs are terminated to VCC with on-chip resistors (refer to functional block diagram for specific resistor values). The maximum DC voltage on any terminal must be limited to V max to prevent damaging the termination resistors with excessive current. Regardless of bias conditions, the following equation should be satisfied when driving the inputs differentially:

where Vdm is the differential input signal and Vcm is the common-mode voltage.

In addition to the maximum input signal levels, single-ended operation imposes additional restrictions: the average DC value of the waveform at IC should be equal to VCC for single-ended operation. In practice, this is easily achieved with a single capacitor on the input acting as a DC block. The value of the capacitor should be large enough to pass the lowest frequencies of interest. Use the positive terminals for single-ended operation while terminating the negative terminal to VCC.

Note that a potential oscillation mechanism exists if both inputs are static and have identical DC voltages; a small DC offset on either input is sufficient to prevent possible oscillations. Tying unused inputs directly to VCC shorts out the internal  $50~\Omega$  bias resistor, imposing a DC offset sufficient to prevent oscillations. Driving the differential inputs with DC blocks, or driving the single-ended inputs without terminating unused inputs, is not recommended without taking additional steps to eliminate the potential oscillation issues.

## Positive Supply (AC Coupling) Low Parasitic Monoblock 1000 nF as close to Pkg as possible **PCB** Copper To +3.3V Supply VCC AC Coupling Capacitor Refer to Text for Values 0 ON + 46 IN <del>)</del>|-16 0 . MO-220 Pkg VCC NOT TO SCALE

Biasing recommendations for positive supply with AC coupling applications

## **Negative Supply (DC Coupling)**

Biasing recommendations for negative supply with DC coupling applications

## **Negative Supply (AC Coupling)**

Biasing recommendations for negative supply with AC coupling applications

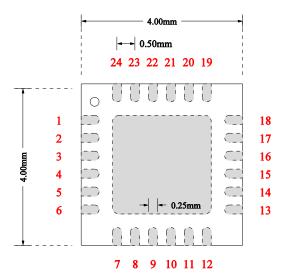

#### **UXC20P Physical Characteristics**

Pkg size: 4.00 x 4.00 mm

Pkg size tolerance: +/- 0.25 mm

Pkg thickness: 0.9 +/- 0.1 mm

Pad dimensions: 0.25 x 0.4 mm

Center paddle: 2.2 x 2.2 mm

JEDEC designator: MO-220

**Top View**

**Table 4: UXC20P Pin Definition**

|                                | Function                 | Notes                                             |

|--------------------------------|--------------------------|---------------------------------------------------|

| 1,3,5,6,7,13,15,17,19,20 (Vcc) | RF and DC Ground         | 0 V (+3.3 V when using positive supply)           |

| 9,23,24 (Vee)                  | Negative Supply Voltage  | Nominally -3.3 V (0 V when using positive supply) |

| 2 (INP)                        | Divider Input            | Positive Terminal of differential output          |

| 4 (INN)                        | Divider Input            | Negative Terminal of differential output          |

| 8 (Temp)                       | Temperature Diode        | IC Surface temperature, Refer to text             |

| 12,11,10 (NC)                  | No Connect               | -                                                 |

| 14 (VADJ)                      | Output Amplitude Control | Tie to VCC for max swing. Refer to text           |

| 16 (OUTP)                      | Divider Output           | Positive Terminal of differential output          |

| 18 (OUTN)                      | Divider Output           | Negative Terminal of differential output          |

| 21 (SelB)                      | Divider Mode             | Divider Select Line, Refer to Table 1             |

| 22 (SeIA)                      | Divider Mode             | Divider Select Line, Refer to Table 1             |

| Paddle                         | Package Paddle           | Tie to heatsink, Refer to text                    |

**Table 5: Absolute Maximum Ratings**

| Parameter                 | Value      | Unit |

|---------------------------|------------|------|

| Supply Voltage (VCC-VEE)  | 4          | ٧    |

| RF Input Power (INP, INN) | 10         | dBm  |

| Operating Temperature     | -40 to 85  | °C   |

| Storage Temperature       | -85 to 125 | °C   |

| Junction Temperature      | 125        | °C   |

The information contained herein is believed to be accurate and is provided "AS IS, WHERE IS", with all faults and the entire risk associated with its use being entirely with the user. Microsemi makes no representation with respect to the merchantability of the products or their suitability or fitness for any particular purpose or use. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

Information contained in this document is proprietary to Microsem. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Prescaler category:

Click to view products by Microsemi manufacturer:

Other Similar products are found below:

UXN14M9P MX1DS10P UXN14M32K HMC492LP3TR HMC434TR HMC433TR HMC394LP4TR MC12093MNR4G NB7N017MMNG HMC437MS8GTR HMC434SRJZ-EP-PT ADMV2101BRHZ HMC365S8G HMC362S8G ADF5000BCPZ ADF5001BCPZ ADF5002BCPZ HMC988LP3ETR HMC361G8 HMC361S8G HMC361S8GETR HMC363G8 HMC363S8G HMC363S8GETR HMC365G8 HMC365S8GETR HMC437MS8G HMC447LC3 HMC447LC3TR HMC492LP3ETR HMC492LP3 HMC493LP3E HMC494LP3E HMC983LP5ETR HMC433 HMC432ETR HMC434ETR HMC432 HMC794LP3E HMC859LC3 HMC983LP5E HMC438MS8GTR HMC437MS8GETR HMC438MS8G HMC438MS8GETR HMC438MS8GETR MC12026ADG MC12093DG MC12093DR2G HMC361S8GE