# Precision 1:2 LVPECL Fanout Buffer with On-Chip Input Termination

**Data Sheet**

April 2014

#### **Features**

#### Inputs/Outputs

- Accepts differential or single-ended input

- LVPECL, LVDS, CML, HCSL, LVCMOS

- On-chip input termination resistors and biasing for AC coupled inputs

- · Two precision LVPECL outputs

- Operating frequency up to 750 MHz

#### **Power**

- Option for 2.5 V or 3.3 V power supply

- Core current consumption of 49 mA

- On-chip Low Drop Out (LDO) Regulator for superior power supply rejection

#### **Performance**

Ultra low additive jitter of 40 fs

# Ordering Information ZL40201LDG1 16 Pin QFN Trays ZL40201LDF1 16 Pin QFN Tape and Reel Matte Tin

Package size: 3 x 3 mm -40°C to +85°C

#### **Applications**

- · General purpose clock distribution

- Low jitter clock trees

- · Logic translation

- · Clock and data signal restoration

- Wired communications: OTN, SONET/SDH, GE, 10 GE, FC and 10G FC

- PCI Express generation 1/2/3 clock distribution

- Wireless communications

- High performance microprocessor clock distribution

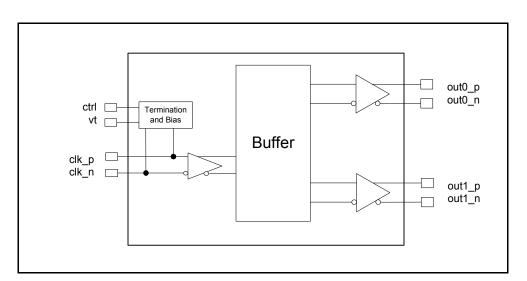

Figure 1 - Functional Block Diagram

# **Table of Contents**

| Features                                 |    |

|------------------------------------------|----|

| Inputs/Outputs                           |    |

| Power                                    |    |

| Performance                              |    |

| Applications                             |    |

| Change Summary                           |    |

| 1.0 Package Description                  |    |

| 2.0 Pin Description                      |    |

| 3.0 Functional Description               | 6  |

| 3.1 Clock Inputs                         |    |

| 3.2 Clock Outputs                        |    |

| 3.3 Device Additive Jitter               | 14 |

| 3.4 Power Supply                         |    |

| 3.4.1 Sensitivity to power supply noise  |    |

| 3.4.2 Power supply filtering             |    |

| 3.4.3 PCB layout considerations          |    |

| 4.0 AC and DC Electrical Characteristics | 16 |

| 5.0 Performance Characterization         | 19 |

| 6.0 Typical Behavior                     | 20 |

| 7.0 Package Thermal Characteristics      | 22 |

| 8 0 Mechanical Drawing                   |    |

# **List of Figures**

| Figure 1 - Functional Block Diagram                                | 1    |

|--------------------------------------------------------------------|------|

| Figure 2 - Pin Connections                                         | 5    |

| Figure 3 - Simplified Diagram of Input Stage                       | 6    |

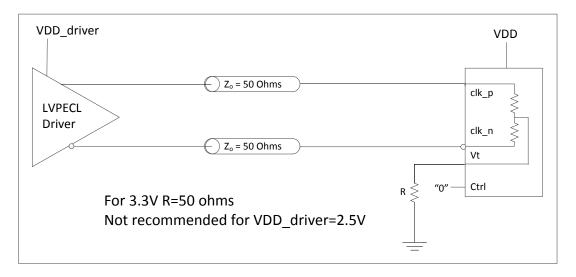

| Figure 4 - Clock Input - LVPECL - DC Coupled                       |      |

| Figure 5 - Clock Input - LVPECL - AC Coupled                       | 7    |

| Figure 6 - Clock Input - LVDS - DC Coupled                         | 8    |

| Figure 7 - Clock Input - LVDS - AC Coupled                         | 8    |

| Figure 8 - Clock Input - CML- AC Coupled                           | 9    |

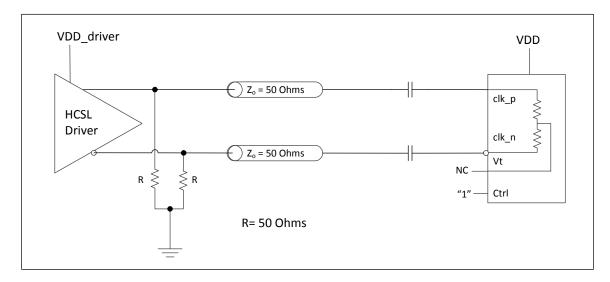

| Figure 9 - Clock Input - HCSL- AC Coupled                          | 9    |

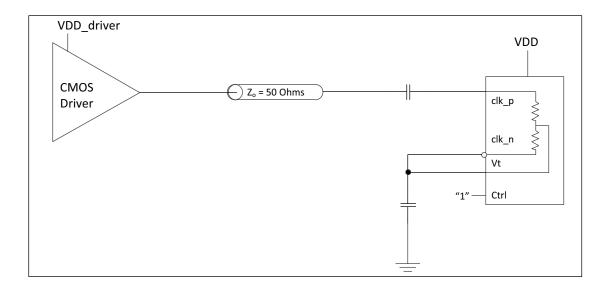

| Figure 10 - Clock Input - AC-coupled Single-Ended                  | . 10 |

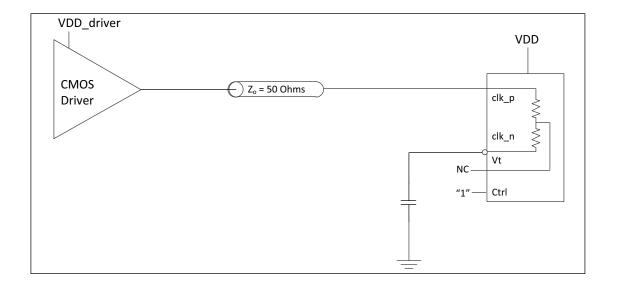

| Figure 11 - Clock Input - DC-coupled 3.3V CMOS                     | . 10 |

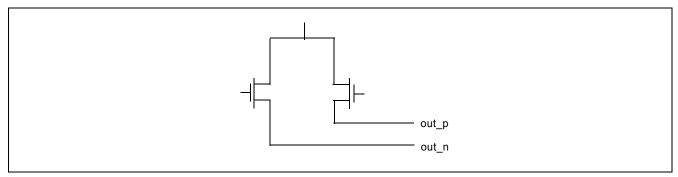

| Figure 12 - Simplified Output Driver                               | . 11 |

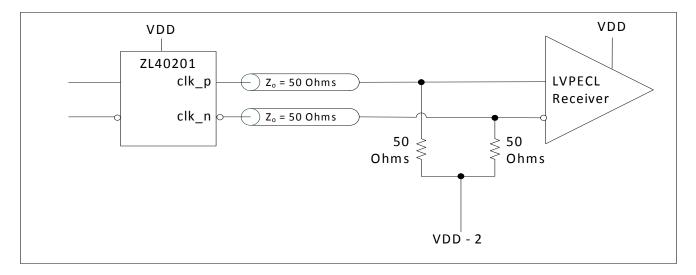

| Figure 13 - LVPECL Basic Output Termination                        | . 11 |

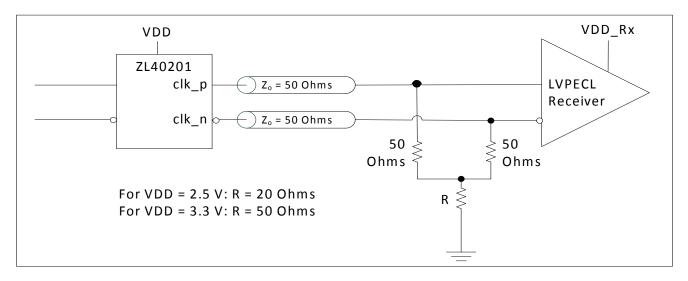

| Figure 14 - LVPECL Parallel Output Termination                     | . 12 |

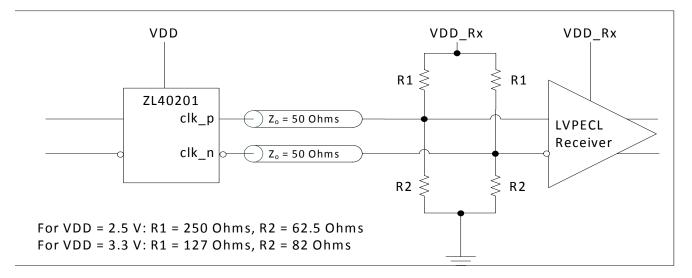

| Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination | . 12 |

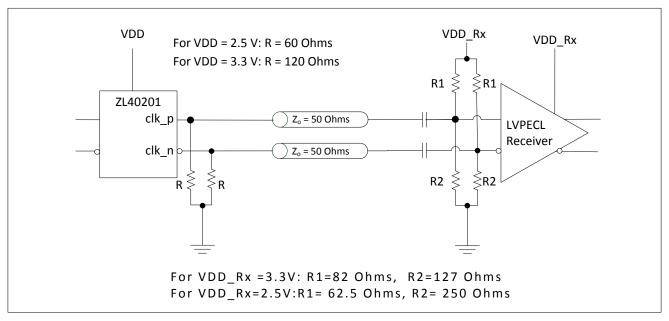

| Figure 16 - LVPECL AC Output Termination                           | . 13 |

| Figure 17 - LVPECL AC Output Termination for CML Inputs            | . 13 |

| Figure 18 - Additive Jitter                                        | . 14 |

| Figure 19 - Decoupling Connections for Power Pins                  | . 15 |

| Figure 20 - Differential Voltage Definition                        | . 17 |

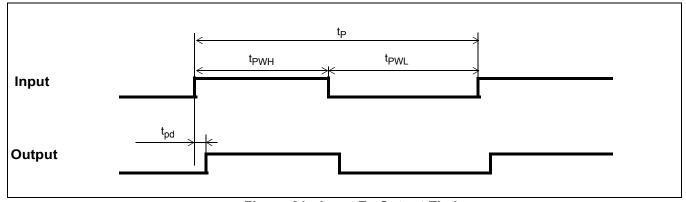

| Figure 21 - Input To Output Timing                                 | 18   |

# **Change Summary**

#### Below

| Page | Item                  | Change                                                                                                                                                           |

|------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Applications          | Added PCI Express clock distribution.                                                                                                                            |

| 5    | Pin Description       | Added exposed pad to Pin Description.                                                                                                                            |

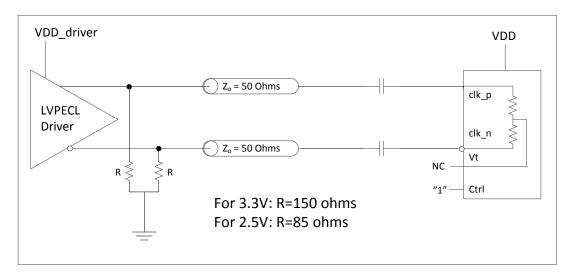

| 7    | Figure 4 and Figure 5 | Removed 22 Ohm series resistors from Figure 4 and 5. These resistors are not required; however, there is no impact to performance if the resistors are included. |

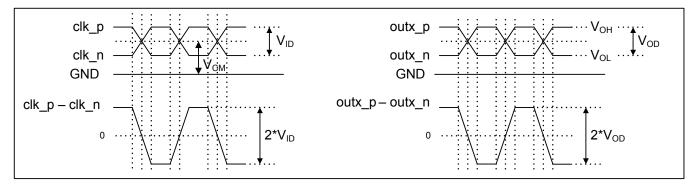

| 17   | Figure 20             | Clarification of V <sub>ID</sub> and V <sub>OD</sub> .                                                                                                           |

Below are the changes from the November 2012 issue to the February 2013 issue:

| Page | Item     | Change                                                                       |

|------|----------|------------------------------------------------------------------------------|

| 7    | Figure 4 | Changed text to indicate the circuit is not recommended for VDD_driver=2.5V. |

# 1.0 Package Description

The device is packaged in a 16 pin QFN

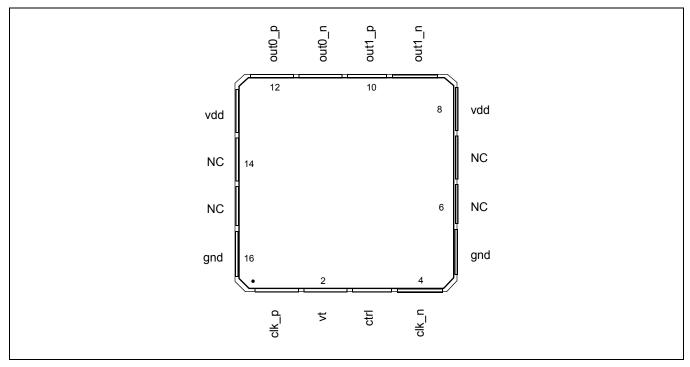

Figure 2 - Pin Connections

# 2.0 Pin Description

| Pin#            | Name           | Description                                                                                                                                                                                                                                   |

|-----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4            | clk_p, clk_n,  | Differential Input (Analog Input). Differential (or singled ended) input signals. For all input signal configuration see "Clock Inputs" on page 6                                                                                             |

| 12, 11,         | out0_p, out0_n | Differential Output (Analog Output). Differential outputs.                                                                                                                                                                                    |

| 10, 9           | out1_p, out1_n |                                                                                                                                                                                                                                               |

| 8, 13           | vdd            | <b>Positive Supply Voltage.</b> 2.5 $V_{DC}$ or 3.3 $V_{DC}$ nominal.                                                                                                                                                                         |

| 5, 16           | gnd            | Ground. 0 V.                                                                                                                                                                                                                                  |

| 2               | vt             | On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohm termination resistors.  See "Clock Inputs" on page 6 for more information.                                                                                        |

| 3               | ctrl           | Digital Control for On-Chip Input Termination (Input). Selects differential input mode; 0: DC coupled modes 1: AC coupled differential modes These pins are internally pulled down to GND. See "Clock Inputs" on page 6 for more information. |

| 6, 7,<br>14, 15 | NC             | No Connection. Leave unconnected.                                                                                                                                                                                                             |

| Exposed Pad     |                | Device GND.                                                                                                                                                                                                                                   |

#### 3.0 Functional Description

The ZL40201 is an LVPECL clock fan out buffer with two identical output clock drivers capable of operating at frequencies up to 750MHz.

The ZL40201 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40201 can accept DC or AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.

The ZL40201 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.

The device block diagram is shown in Figure 1; its operation is described in the following sections.

#### 3.1 Clock Inputs

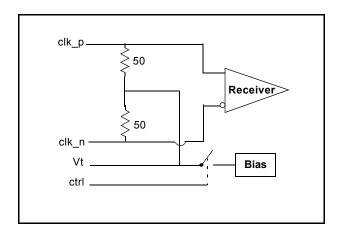

The device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.

Figure 3 - Simplified Diagram of Input Stage

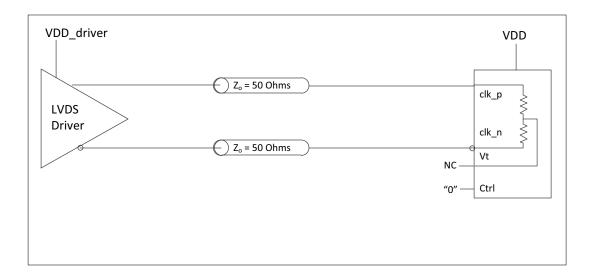

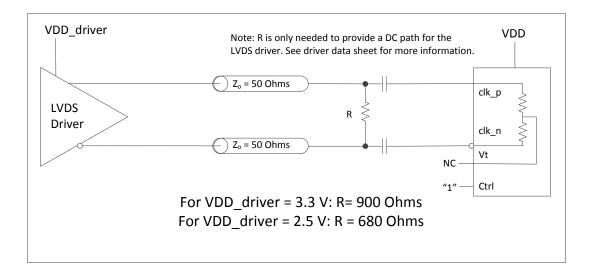

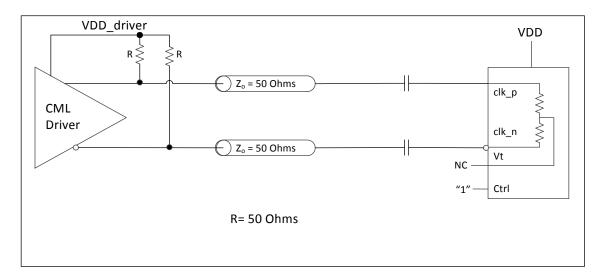

This following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the *Vt* and *ctrl* pins in each case.

In the following diagrams where the  $\it ctrl$  pin is "1" and the  $\it Vt$  pin is not connected, the  $\it Vt$  pin can be instead connected to  $\it V_{DD}$  with a capacitor. The same capacitor can also help in Figure 4 between  $\it Vt$  and  $\it V_{DD}$ . This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.

Figure 4 - Clock Input - LVPECL - DC Coupled

Figure 5 - Clock Input - LVPECL - AC Coupled

Figure 6 - Clock Input - LVDS - DC Coupled

Figure 7 - Clock Input - LVDS - AC Coupled

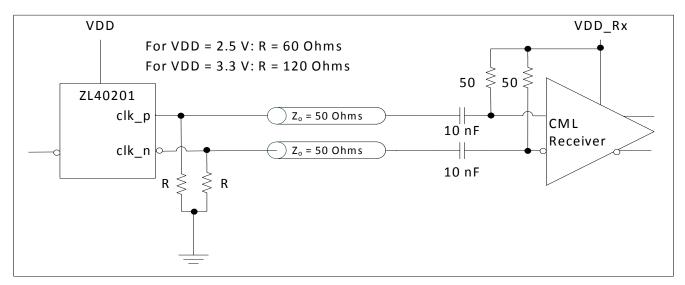

Figure 8 - Clock Input - CML- AC Coupled

Figure 9 - Clock Input - HCSL- AC Coupled

Figure 10 - Clock Input - AC-coupled Single-Ended

Figure 11 - Clock Input - DC-coupled 3.3V CMOS

#### 3.2 Clock Outputs

LVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a different device with the same inputs and LVDS outputs.

Figure 12 - Simplified Output Driver

The methods to terminate the ZL40201 LVPECL drivers are shown in the following figures.

Figure 13 - LVPECL Basic Output Termination

Figure 14 - LVPECL Parallel Output Termination

Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination

Figure 16 - LVPECL AC Output Termination

Figure 17 - LVPECL AC Output Termination for CML Inputs

#### 3.3 Device Additive Jitter

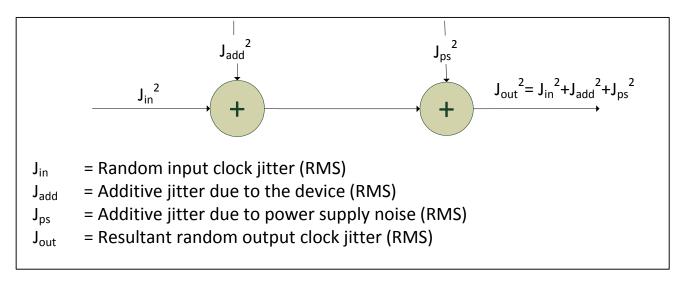

The ZL40201 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40201 is random and as such it is not correlated to the jitter of the input clock signal.

The square of the resultant random RMS jitter at the output of the ZL40201 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive random jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 18.

Figure 18 - Additive Jitter

#### 3.4 Power Supply

This device operates with either a 2.5V supply or 3.3V supply.

#### 3.4.1 Sensitivity to power supply noise

Power supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40201 is equipped with a low drop out (LDO) power regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The LDO regulator on the ZL40201 allows this device to have superior performance even in the presence of external noise sources. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.

The performance of these clock buffers in the presence of power supply noise is detailed in ZLAN-403, "Power Supply Rejection in Clock Buffers" which is available from Applications Engineering.

#### 3.4.2 Power supply filtering

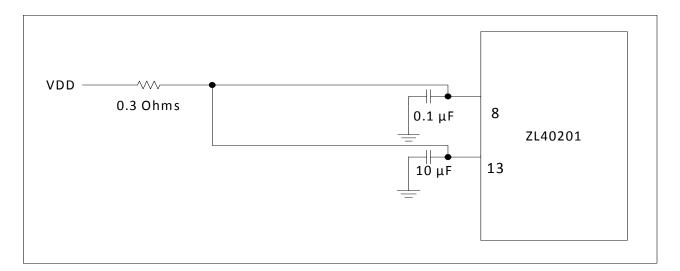

For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 19.

- 10 μF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating

- 0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating

- · Capacitors should be placed next to the connected device power pins

- a 0.3 ohm resistor is recommended for the filter shown in Figure 19

Figure 19 - Decoupling Connections for Power Pins

#### 3.4.3 PCB layout considerations

The power nets in Figure 19 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.

#### 4.0 AC and DC Electrical Characteristics

#### **Absolute Maximum Ratings\***

|   | Parameter                  | Sym.               | Min. | Max.     | Units |

|---|----------------------------|--------------------|------|----------|-------|

| 1 | Supply voltage             | V <sub>DD_R</sub>  | -0.5 | 4.6      | V     |

| 2 | Voltage on any digital pin | V <sub>PIN</sub>   | -0.5 | $V_{DD}$ | V     |

| 3 | LVPECL output current      | l <sub>out</sub>   |      | 30       | mA    |

| 4 | Soldering temperature      | Т                  |      | 260      | °C    |

| 5 | Storage temperature        | T <sub>ST</sub>    | -55  | 125      | °C    |

| 6 | Junction temperature       | Tj                 |      | 125      | °C    |

| 7 | Voltage on input pin       | V <sub>input</sub> |      | $V_{DD}$ | V     |

| 8 | Input capacitance each pin | C <sub>p</sub>     |      | 500      | fF    |

<sup>\*</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

\* Voltages are with respect to ground (GND) unless otherwise stated

#### **Recommended Operating Conditions\***

|   | Characteristics           | Sym.           | Min.  | Тур. | Max.  | Units |

|---|---------------------------|----------------|-------|------|-------|-------|

| 1 | Supply voltage 2.5 V mode | $V_{DD25}$     | 2.375 | 2.5  | 2.625 | V     |

| 2 | Supply voltage 3.3 V mode | $V_{DD33}$     | 3.135 | 3.3  | 3.465 | V     |

| 3 | Operating temperature     | T <sub>A</sub> | -40   | 25   | 85    | °C    |

<sup>\*</sup> Voltages are with respect to ground (GND) unless otherwise stated

#### **DC Electrical Characteristics - Current Consumption**

|   | Characteristics                                                 | Sym.                   | Min. | Тур. | Max. | Units | Notes                               |

|---|-----------------------------------------------------------------|------------------------|------|------|------|-------|-------------------------------------|

| 1 | Supply current LVPECL drivers - unloaded                        | I <sub>dd_unload</sub> |      | 49   |      | mA    | Unloaded                            |

| 2 | Supply current LVPECL drivers - loaded (all outputs are active) | I <sub>dd_load</sub>   |      | 88   |      | mA    | Including power to $R_L = 50\Omega$ |

#### DC Electrical Characteristics - Inputs and Outputs - for 3.3 V Supply

|   | Characteristics                             | Sym.             | Min.                | Тур. | Max.                | Units | Notes                 |

|---|---------------------------------------------|------------------|---------------------|------|---------------------|-------|-----------------------|

| 1 | CMOS control logic high-level input voltage | V <sub>CIH</sub> | 0.7*V <sub>DD</sub> |      |                     | V     |                       |

| 2 | CMOS control logic low-level input voltage  | $V_{CIL}$        |                     |      | 0.3*V <sub>DD</sub> | ٧     |                       |

| 3 | CMOS control logic Input leakage current    | I <sub>IL</sub>  |                     | 1    |                     | μΑ    | $V_I = V_{DD}$ or 0 V |

| 4 | Differential input common mode voltage      | V <sub>CM</sub>  | 1.1                 |      | 2.0                 | V     |                       |

| 5 | Differential input voltage difference       | V <sub>ID</sub>  | 0.25                |      | 1                   | V     |                       |

#### DC Electrical Characteristics - Inputs and Outputs - for 3.3 V Supply

|   | Characteristics                     | Sym.            | Min.                      | Тур. | Max.                      | Units | Notes |

|---|-------------------------------------|-----------------|---------------------------|------|---------------------------|-------|-------|

| 6 | Differential input resistance       | $V_{IR}$        | 80                        | 100  | 120                       | ohm   |       |

| 7 | LVPECL output high voltage          | V <sub>OH</sub> | V <sub>DD</sub> -<br>1.40 |      |                           | V     |       |

| 8 | LVPECL output low voltage           | V <sub>OL</sub> |                           |      | V <sub>DD</sub> -<br>1.62 | V     |       |

| 9 | LVPECL output differential voltage* | V <sub>OD</sub> | 0.5                       |      | 0.9                       | V     |       |

<sup>\*</sup> Parameter measured from 125 to 750 MHz

#### DC Electrical Characteristics - Inputs and Outputs - for 2.5 V Supply

|   | Characteristics                             | Sym.             | Min.                      | Тур. | Max.                      | Units    | Notes                 |

|---|---------------------------------------------|------------------|---------------------------|------|---------------------------|----------|-----------------------|

| 1 | CMOS control logic high-level input voltage | V <sub>CIH</sub> | 0.7*V <sub>DD</sub>       |      |                           | V        |                       |

| 2 | CMOS control logic low-level input voltage  | V <sub>CIL</sub> |                           |      | 0.3*V <sub>DD</sub>       | <b>V</b> |                       |

| 3 | CMOS control logic Input leakage current    | I <sub>IL</sub>  |                           | 1    |                           | μΑ       | $V_I = V_{DD}$ or 0 V |

| 4 | Differential input common mode voltage      | V <sub>CM</sub>  | 1.1                       |      | 1.6                       | V        |                       |

| 5 | Differential input voltage difference       | $V_{ID}$         | 0.25                      |      | 1                         | <b>V</b> |                       |

| 6 | Differential input resistance               | $V_{IR}$         | 80                        | 100  | 120                       | ohm      |                       |

| 7 | LVPECL output high voltage                  | V <sub>OH</sub>  | V <sub>DD</sub> -<br>1.40 |      |                           | <b>V</b> |                       |

| 8 | LVPECL output low voltage                   | V <sub>OL</sub>  |                           |      | V <sub>DD</sub> -<br>1.62 | V        |                       |

| 9 | LVPECL output voltage differentia*I         | V <sub>OD</sub>  | 0.4                       |      | 0.9                       | V        |                       |

<sup>\*</sup> Parameter measured from 125 to 750 MHz

Figure 20 - Differential Voltage Definition

#### AC Electrical Characteristics\* - Inputs and Outputs (see Figure 21) - for 3.3 V supply.

|   | Characteristics                         | Sym.                                | Min. | Тур. | Max. | Units   | Notes |

|---|-----------------------------------------|-------------------------------------|------|------|------|---------|-------|

| 1 | Maximum Operating Frequency             | 1/t <sub>p</sub>                    |      |      | 750  | MHz     |       |

| 2 | input to output clock propagation delay | t <sub>pd</sub>                     | 0    | 1    | 2    | ns      |       |

| 3 | output to output skew                   | t <sub>out2out</sub>                |      | 50   | 100  | ps      |       |

| 4 | part to part output skew                | t <sub>part2part</sub>              |      | 80   | 300  | ps      |       |

| 5 | Output clock Duty Cycle degradation     | t <sub>PWH</sub> / t <sub>PWL</sub> | -2   | 0    | 2    | Percent |       |

| 6 | LVPECL Output Slew Rate                 | r <sub>sl</sub>                     | 0.75 | 1.2  |      | V/ns    |       |

<sup>\*</sup> Supply voltage and operating temperature are as per Recommended Operating Conditions

#### AC Electrical Characteristics\* - Inputs and Outputs (see Figure 21) - for 2.5 V supply.

|   | Characteristics                         | Sym.                                | Min. | Тур. | Max. | Units   | Notes |

|---|-----------------------------------------|-------------------------------------|------|------|------|---------|-------|

| 1 | Maximum Operating Frequency             | 1/t <sub>p</sub>                    |      |      | 750  | MHz     |       |

| 2 | input to output clock propagation delay | t <sub>pd</sub>                     | 0    | 1    | 2    | ns      |       |

| 3 | output to output skew                   | t <sub>out2out</sub>                |      | 50   | 100  | ps      |       |

| 4 | part to part output skew                | t <sub>part2part</sub>              |      | 80   | 300  | ps      |       |

| 5 | Output clock Duty Cycle degradation     | t <sub>PWH</sub> / t <sub>PWL</sub> | -2   | 0    | 2    | Percent |       |

| 6 | LVPECL Output Slew Rate                 | r <sub>sl</sub>                     | 0.75 | 1.2  |      | V/ns    |       |

<sup>\*</sup> Supply voltage and operating temperature are as per Recommended Operating Conditions

Figure 21 - Input To Output Timing

#### 5.0 Performance Characterization

#### Additive Jitter at 2.5 V\*

|   | Output Frequency (MHz) | Jitter<br>Measurement<br>Filter | Typical<br>(fs) | Notes |

|---|------------------------|---------------------------------|-----------------|-------|

| 1 | 125                    | 12 kHz - 20 MHz                 | 105             |       |

| 2 | 212.5                  | 12 kHz - 20 MHz                 | 108             |       |

| 3 | 311.04                 | 12 kHz - 20 MHz                 | 96              |       |

| 4 | 425                    | 12 kHz - 20 MHz                 | 79              |       |

| 5 | 500                    | 12 kHz - 20 MHz                 | 69              |       |

| 6 | 622.08                 | 12 kHz - 20 MHz                 | 56              |       |

| 7 | 750                    | 12 kHz - 20 MHz                 | 41              |       |

<sup>\*</sup>The values in this table were taken with an aproximate slew rate of 0.8 V/ns.

#### Additive Jitter at 3.3\*V

|   | Output Frequency (MHz) | Jitter<br>Measurement<br>Filter | Typical<br>(fs) | Notes |

|---|------------------------|---------------------------------|-----------------|-------|

| 1 | 125                    | 12 kHz - 20 MHz                 | 108             |       |

| 2 | 212.5                  | 12 kHz - 20 MHz                 | 108             |       |

| 3 | 311.04                 | 12 kHz - 20 MHz                 | 97              |       |

| 4 | 425                    | 12 kHz - 20 MHz                 | 79              |       |

| 5 | 500                    | 12 kHz - 20 MHz                 | 69              |       |

| 6 | 622.08                 | 12 kHz - 20 MHz                 | 56              |       |

| 7 | 750                    | 12 kHz - 20 MHz                 | 40              |       |

<sup>\*</sup>The values in this table were taken with an aproximate slew rate of 0.8 V/ns.

#### Additive Jitter from a Power Supply Tone\*

| Carrier frequency | Parameter        | Typical | Units  | Notes |

|-------------------|------------------|---------|--------|-------|

| 125MHz            | 25 mV at 100 kHz | 132     | fs RMS |       |

| 750MHz            | 25 mV at 100 kHz | 82      | fs RMS |       |

<sup>\*</sup> The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V<sub>DD</sub> = 3.3 V. The magnitude of the interfering tone is measured at the DUT.

## 6.0 Typical Behavior

0.5 0.4 0.3 0.2 0.1 Voltage 0 -0.1 -0.2 -0.3 -0.4 -0.5 0 15 5 10 20 Time (ns)

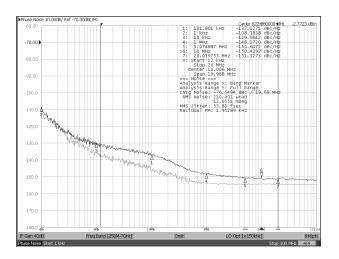

Typical Phase Noise at 622.08 MHz

Typical Waveform at 155.52 MHz

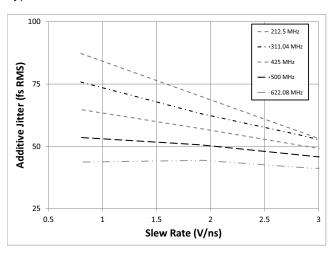

Input Slew Rate versus Additive Jitter

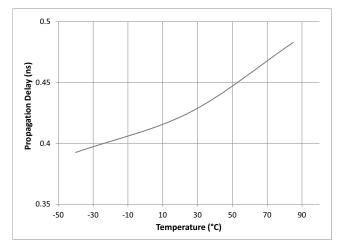

Propagation Delay versus Temperature

Note: This is for a single device. For more details see the characterization section.

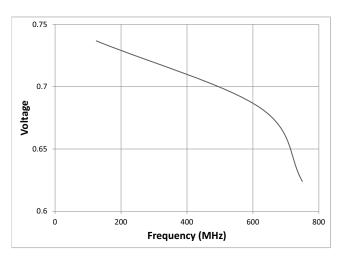

V<sub>OD</sub> versus Frequency

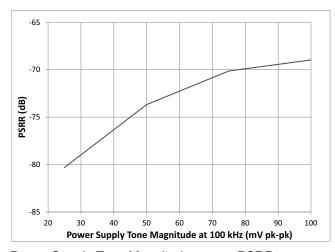

Power Supply Tone Magnitude versus PSRR (at 100 kHz) at 125 MHz

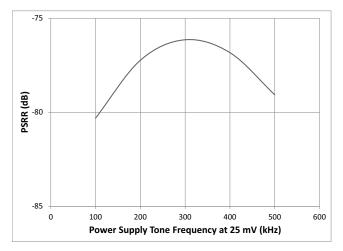

Power Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz

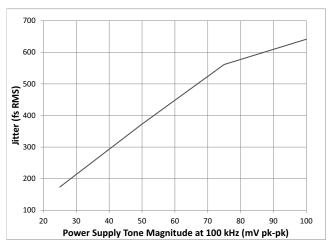

Power Supply Tone Magnitude versus Additive Jitter (at 100 kHz) at 125 MHz

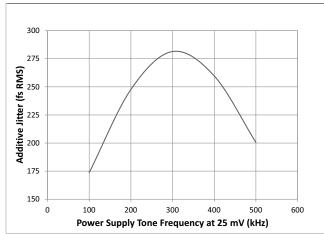

Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHz

# 7.0 Package Thermal Characteristics

#### **Thermal Data**

| Parameter                              | Symbol            | Test Condition              | Value                | Unit |

|----------------------------------------|-------------------|-----------------------------|----------------------|------|

| Junction to Ambient Thermal Resistance | Θ <sub>JA</sub>   | Still Air<br>1 m/s<br>2 m/s | 67.9<br>61.6<br>58.1 | °C/W |

| Junction to Case Thermal Resistance    | Θ <sub>JC</sub>   | Still Air                   | 44.1                 | °C/W |

| Junction to Board Thermal Resistance   | $\Theta_{JB}$     | Still Air                   | 23.2                 | °C/W |

| Maximum Junction Temperature*          | T <sub>jmax</sub> |                             | 125                  | °C   |

| Maximum Ambient Temperature            | T <sub>A</sub>    |                             | 85                   | °C   |

$<sup>^{\</sup>star}$  Proper thermal management must be practiced to ensure that  $T_{j\text{max}}$  is not exceeded.

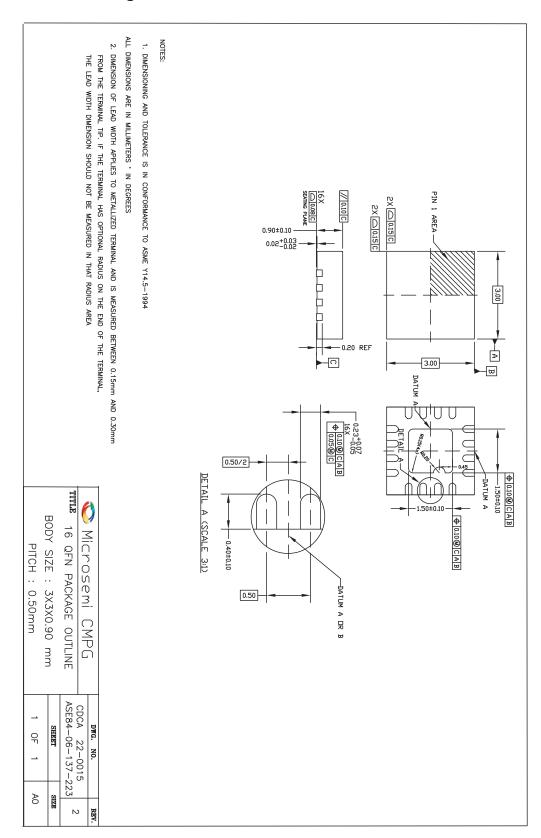

### 8.0 Mechanical Drawing

Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively "Microsemi") is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.

This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi's conditions of sale which are available on request.

For more information about all Microsemi products visit our website at www.microsemi.com

TECHNICAL DOCUMENTATION - NOT FOR RESALE

Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Buffer category:

Click to view products by Microsemi manufacturer:

Other Similar products are found below:

MPC962309EJ-1H NB4N121KMNG IDT49FCT805ASO MK2308S-1HILF PL133-27GI-R NB3L02FCT2G NB3L03FCT2G

ZL40203LDG1 ZL40200LDG1 ZL40205LDG1 9FG1200DF-1LF 9FG1001BGLF PI49FCT20802QE NB7L1008MNG NB7L14MN1G

PI49FCT20807QE PI6C4931502-04LIEX ZL80002QAB1 PI6C4931504-04LIEX PI6C10806BLEX ZL40226LDG1 ZL40219LDG1

8T73S208B-01NLGI SY75578LMG PI49FCT32805QEX PL133-27GC-R CDCV304PWG4 MC10LVEP11DG MC10EP11DTG

MC100LVEP11DG MC100E111FNG MC100EP11DTG NB6N11SMNG NB7L14MMNG NB6L11MMNG NB6L14MMNR2G

NB6L611MNG NB3N111KMNR4G ADCLK944BCPZ-R7 ZL40217LDG1 NB7LQ572MNG HMC940LC4BTR ADCLK946BCPZ-REEL7

ADCLK946BCPZ ADCLK905BCPZ-R2 ADCLK905BCPZ-R7 ADCLK905BCPZ-WP ADCLK907BCPZ-R2 ADCLK907BCPZ-WP

ADCLK914BCPZ-R2