# MD1321/2/4 1MHz, 40μA, Rail-to-Rail I/O CMOS Operational Amplifiers

#### **FEATURES**

- Low Cost

- Rail-to-Rail Input and Output 0.8mV Typical V<sub>OS</sub>

- Unity Gain Stable

- Gain-Bandwidth Product: 1MHz

- Very Low Input Bias Current: 10pA

- Supply Voltage Range: 2.1V to 5.5V

- Input Voltage Range:

- -0.1V to +5.6V with  $(V_{DD} V_{SS}) = 5.5V$

- Low Supply Current: 40μA/Amplifier

- Small Packaging

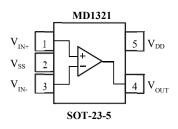

MD1321 Available in SOT-23-5

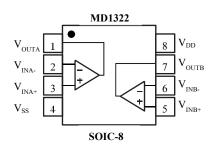

MD1322 Available in SOIC-8

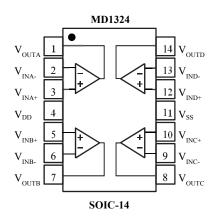

MD1324 Available in SOIC-14

### **APPLICATIONS**

- ASIC Input or Output Amplifier

- Sensor Interface

- Piezoelectric Transducer Amplifier

- Medical Instrumentation

- Mobile Communication

- Audio Output

- Portable Systems

- Smoke Detectors

- Notebook PC

- PCMCIA Cards

- Battery-Powered Equipment

- DSP Interface

### PRODUCT DESCRIPTION

The MD1321 (single), MD1322 (dual) and MD1324 (quad) are low cost, rail-to-rail input and output voltage feedback amplifiers. They have a wide input common mode voltage range and output voltage swing, and take the minimum operating supply voltage down to 2.1V. The maximum recommended supply voltage is 5.5V. It is specified over the extended -40  $^{\circ}$ C to +85  $^{\circ}$ C temperature range.

The MD1321/2/4 provides 1MHz bandwidth at a low current consumption of  $40\mu A$  per amplifier. Very low input bias currents of 10pA enable MD1321/2/4 to be used for integrators, photodiode amplifiers, and piezoelectric sensors. Rail-to-rail input and output are useful to designers for buffering ASIC in single-supply systems.

Applications for this series of amplifiers include safety monitoring, portable equipment, battery and power supply control, and signal conditioning and interfacing for transducers in very low power systems.

The MD1321 is available in the Green SOT-23-5 Package. The MD1322 comes in the Green SOIC-8 package. The MD1324 comes in the Green SOIC-14 package.

## PIN CONFIGURATIONS (TOP VIEW)

### **ORDER INFORMATION**

| MODEL  | ORDER NUMBER | PACKAGE<br>DESCRIPTION | PACKAGE OPTION      | MARKING<br>INFORMATION |

|--------|--------------|------------------------|---------------------|------------------------|

| MD1321 |              | SOT23-5                | Tape and Reel, 3000 |                        |

| MD1322 |              | SOIC-8                 | Tape and Reel, 4000 |                        |

| MD1324 |              | SOIC-14                | Tape and Reel, 4000 |                        |

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>DD</sub> to V <sub>SS</sub> | 6V                                 |

|----------------------------------------------------|------------------------------------|

| Common Mode Input Voltage                          | $V_{SS}$ - 0.3V to $V_{DD}$ + 0.3V |

| Storage Temperature Range                          | 65°C to +150°C                     |

| Junction Temperature                               | 150℃                               |

| Operating Temperature Range                        | -40°C to +85°C                     |

| Package Thermal Resistance @ 7 | $\Gamma_{\rm A} = +25^{\circ}{\rm C}$ |

|--------------------------------|---------------------------------------|

| SOIC-8, θJA                    | 125°C/W                               |

| Lead Temperature (Soldering    | 10sec)260℃                            |

#### NOTE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ESD**, Electrostatic Discharge Protection

| Symbol | Parameter            | Condition | Minimum Level | Unit |

|--------|----------------------|-----------|---------------|------|

| HBM    | Human Body Model ESD |           | 4             | kV   |

| MM     | Machine Model ESD    |           | 300           | V    |

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are At  $T_A$ =25 °C,  $V_{DD}$  = +5V,  $V_{SS}$  = GND,  $R_L$  = 100k $\Omega$  connected to  $V_{DD}/2$ , and  $V_{OUT}$  =  $V_{DD}/2$ .

| <b>PARAMETER</b>                | SYMBOL                   | CONDITIONS                                                             |   | MIN   | TYP      | MAX | UNITS  |  |

|---------------------------------|--------------------------|------------------------------------------------------------------------|---|-------|----------|-----|--------|--|

| INPUT CHARACTERISTICS           |                          |                                                                        |   | •     |          |     |        |  |

| I                               | ***                      | $V_{CM} = V_{DD}/2$                                                    |   |       | 0.8      | 5   | mV     |  |

| Input Offset Voltage            | $V_{OS}$                 | $V_{CM} = V_{DD}/2$                                                    | • |       |          | 6.6 |        |  |

| Input Bias Current              | $I_B$                    |                                                                        |   |       | 10       |     | pA     |  |

| Input Offset Current            | $I_{OS}$                 |                                                                        |   |       | 10       |     | pA     |  |

| Input Offset Voltage Drift      | $\Delta V_{OS}/\Delta_T$ |                                                                        |   |       | 2        |     | μV/°C  |  |

| Input Common Mode Voltage Range | $V_{CM}$                 | $V_{\mathrm{DD}} = 5.5 \mathrm{V}$                                     |   |       | -0.1-5.6 |     | V      |  |

| Common Mode Rejection Ratio     | CMRR                     | $V_{\rm DD} = 5.5 \text{V}, V_{\rm CM} = -0.1 \text{V to } 4 \text{V}$ |   |       | 76       |     | dB     |  |

| 0 1 11 11 0:                    |                          | $R_L = 100k\Omega$ , $V_{OUT} = 2.5V$                                  |   |       | 95       |     | dB     |  |

| Open-Loop Voltage Gain          | $A_{ m OL}$              | $R_L = 100 k\Omega$ , $V_{OUT} = +0.2 V$ to $+4.8 V$                   |   |       | 93       |     | dB     |  |

| OUTPUT CHARACTERIST             | ICS                      |                                                                        |   | I.    |          |     |        |  |

|                                 | $V_{\mathrm{OH}}$        | $R_L = 100k\Omega$                                                     |   | 4.980 | 4.995    |     | V      |  |

|                                 | $V_{OL}$                 | $R_L = 100k\Omega$                                                     |   | 25    | 5        |     | mV     |  |

| Output Voltage Swing from Rail  | V <sub>OH</sub>          | $R_L = 10k\Omega$                                                      |   | 4.970 | 4.994    |     | V      |  |

|                                 | $V_{OL}$                 | $R_L = 10k\Omega$                                                      |   | 35    | 6        |     | mV     |  |

| _                               | I <sub>SOURCE</sub>      |                                                                        |   |       | 40       |     | 1 .    |  |

| Output Current                  | I <sub>SINK</sub>        | $R_{\rm L} = 10\Omega$ to $V_{\rm DD}/2$                               |   |       | 40       |     | mA     |  |

| POWER SUPPLY                    |                          |                                                                        |   | I.    |          |     |        |  |

| O W.1. P                        |                          |                                                                        |   | 2.1   |          |     | V      |  |

| Operating Voltage Range         |                          |                                                                        | • | 2.5   |          | 5.5 | V      |  |

| Power Supply Rejection Ratio    | PSRR                     | $V_{DD} = +2.5 \text{V to } +5.5 \text{V}, V_{CM} = +0.5 \text{V}$     |   |       | 85       |     | dB     |  |

|                                 | $I_Q$                    |                                                                        |   |       | 40       |     |        |  |

| Quiescent Current/Amplifier     |                          |                                                                        | • | 35    |          | 80  | μΑ     |  |

| DYNAMIC PERFORMANC              | $E (C_L = 100)$          | oF)                                                                    |   |       |          |     |        |  |

| Gain-Bandwidth Product          | GBP                      |                                                                        |   |       | 1        |     | MHz    |  |

| Phase Margin                    | PM                       | $R_L = 100k\Omega, C_L = 100pF$                                        |   |       | 45       |     | 0      |  |

| Harmonic Distortion             | HD2                      | $f = 10kHz, G = +1, R_L = 100k, V_{OUT} = 2V_{PP}$                     |   |       | >80      |     | dBc    |  |

|                                 | HD3                      | $f = 10kHz, G = +1, R_L=100k, V_{OUT}=2V_{PP}$                         |   |       | >80      |     |        |  |

| Slew Rate                       | SR                       | G = +1, 2V Output Step                                                 |   |       | 0.64     |     | V/µs   |  |

| Settling Time to 0.1%           | $t_{\rm s}$              | G = +1, 2V Output Step                                                 |   |       | 6        |     | μs     |  |

| Overload Recovery Time          |                          | $V_{\text{IN}} \cdot G = V_{\text{DD}}$                                |   |       | 2.5      |     | μs     |  |

| NOISE PERFORMANCE               |                          | 1                                                                      | 1 |       |          |     | 1      |  |

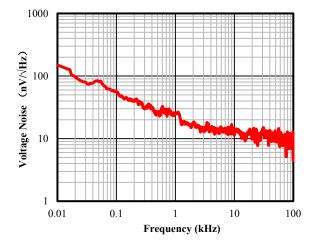

| Voltage Noise Density           | e <sub>n</sub>           | f=1kHz                                                                 |   |       | 30       |     | nV/√Hz |  |

|                                 |                          | f = 10kHz                                                              |   |       | 20       |     | nV/√Hz |  |

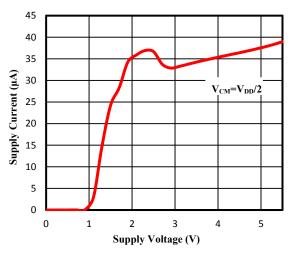

At  $T_A = +25$ °C,  $V_{DD} = +5V$ ,  $V_{SS} = GND$ , and  $R_L = 100k\Omega$  connected to  $V_{DD}/2$ , unless otherwise specified.

Figure 1. Supply Current vs. Supply Voltage

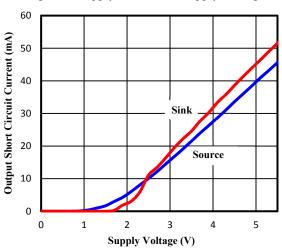

Figure 3. Output Short Circuit Current vs. Supply Voltage

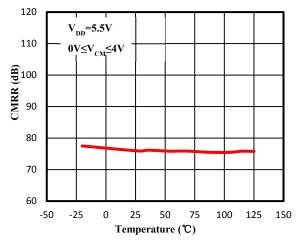

Figure 5. CMRR vs. Temperature

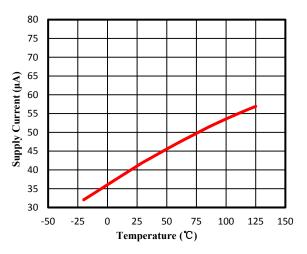

Figure 2. Supply Current vs. Temperature

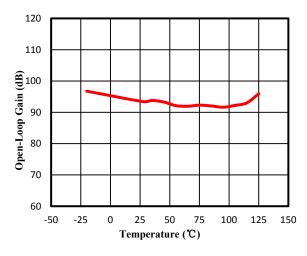

Figure 4. Open-Loop Gain vs. Temperature

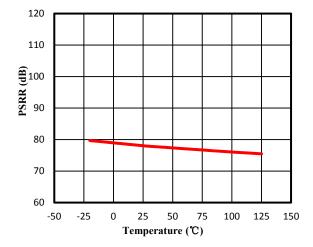

Figure 6. PSRR vs. Temperature

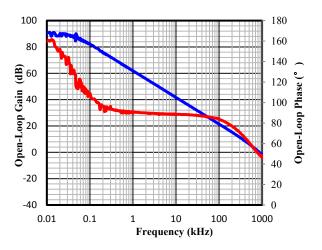

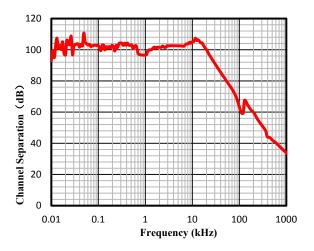

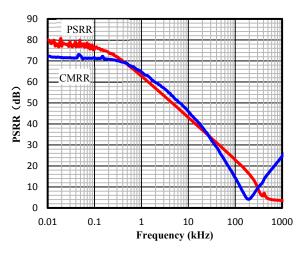

At  $T_A = +25$ °C,  $V_{DD} = +5V$ ,  $V_{SS} = GND$ , and  $R_L = 100k\Omega$  connected to  $V_{DD}/2$ , unless otherwise specified.

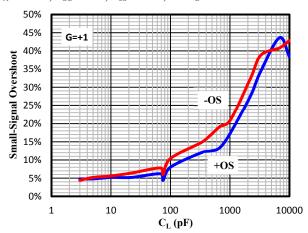

Figure 7. Small-Signal Overshoot vs. Load Capacitance

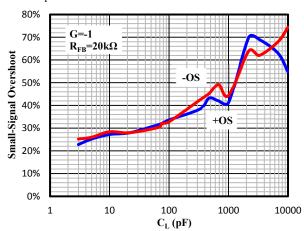

Figure 8. Small-Signal Overshoot vs. Load Capacitance

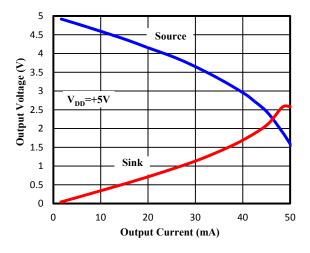

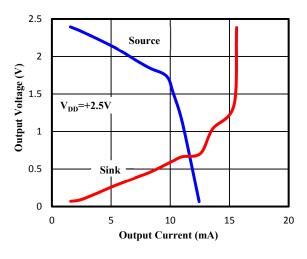

Figure 9. Output Voltage vs. Output Current

Figure 10. Output Voltage vs. Output Current

Figure 11. Input Voltage Noise Spectral Density vs. Frequency

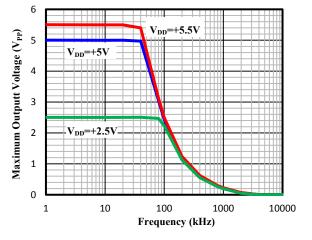

Figure 12. Maximum Output Voltage vs. Frequency

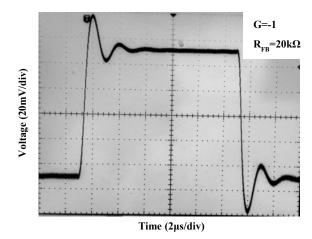

At  $T_A$  = +25 °C,  $V_{DD}$  = +5V,  $V_{SS}$  = GND, and  $R_L$  = 100k $\Omega$  connected to  $V_{DD}/2$ , unless otherwise specified

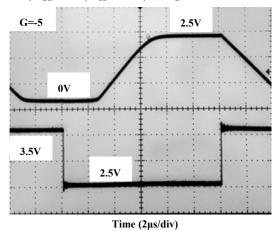

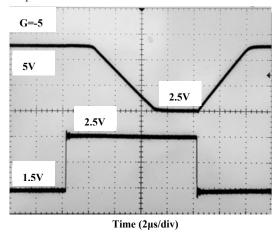

Figure 13. Positive Overload Recovery Time

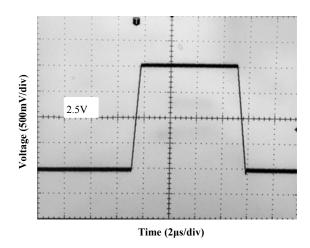

Figure 15. Phase Reversal

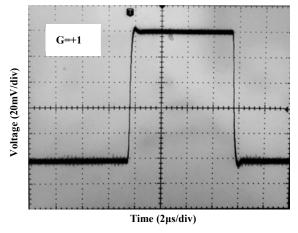

Figure 17. Small-Signal Step Response

Figure 14. Negative Overload Recovery Time

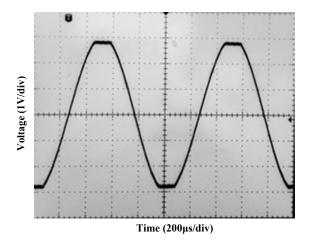

Figure 16. Large-Signal Step Response

Figure 18. Small-Signal Step Response

At  $T_A$  = +25 °C,  $V_{DD}$  = +5 V,  $V_{SS}$  = GND, and  $R_L$  = 100k $\Omega$  connected to  $V_{DD}/2$ , unless otherwise specified.

Figure 19. Gain and Phase vs. Frequency

Figure 21. Channel Separation vs. Frequency

Figure 20. CMRR and PSRR vs. Frequency

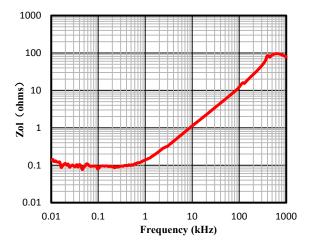

Figure 22. Zol vs. Frequency

#### APPLICATION INFORMATION

MD1321/2/4 are CMOS, rail-to-rail input and output voltage feedback amplifiers designed for general purpose applications.

#### **Operating Voltage**

The MD1321/2/4 are specified over a power-supply range of  $\pm 2.1 \text{V}$  to  $\pm 5.5 \text{V}$  ( $\pm 1.05 \text{V}$  to  $\pm 2.75 \text{V}$ ), Supply voltages higher than 6V (absolute maximum) can permanently damage the amplifier.

Parameters that vary over supply voltage or temperature are shown in the typical characteristics section of this datasheet.

#### Rail-to-Rail Input

The input stage of the amplifiers is a true rail-to-rail architecture, allowing the input common-mode voltage range of the op amp to extend to both positive and negative supply rails. This maximizes the usable voltage range of the amplifier, an important feature for single-supply and low voltage applications. This rail-to-rail input range is achieved with a complementary input stage—an NMOS input differential pair in parallel with a PMOS differential pair. The NMOS pair is active at the upper end of the common-mode voltage range, typically  $V_{\rm DD}-1.2V$  to  $100 {\rm mV}$  above the positive supply, while the PMOS pair is active for inputs from  $100 {\rm mV}$  below the negative supply to approximately  $V_{\rm DD}-1.2V$ .

#### Rail-to-Rail Output

A class AB output stage with common-source transistors is used to achieve rail-to-rail output. The maximum output voltage swing is proportional to the output current, and larger currents will limit how close the output voltage can get to the proximity of the output voltage to the supply rail. This is a characteristic of all rail-to-rail output amplifiers. See the typical performance characteristic Figure 9, Output Voltage Swing vs. Output Current.

#### **Capacitive Loads**

The MD1321/2/4 op amps can directly drive large capacitive loads. As the load capacitance increases, the feedback loop's phase margin decreases and the closed-loop's bandwidth is reduced. This produces gain peaking in the frequency response, with overshoot and ringing in the step response. While a op amp in unity gain configuration (G = +1 V/V) is most susceptible to the effects of capacitive loading.

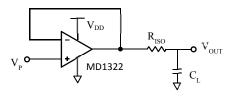

When driving large capacitive loads with the MD1321/2/4 amplifiers (e.g., > 100pF when G = +1 V/V), a small series resistor at the output ( $R_{ISO}$  in Figure 23) improves the feedback

Figure 23. Driving Large Capacitive Loads loop's phase margin (stability) by making the output load resistive at higher frequencies.

#### **PCB Surface Leakage**

In Applications where low input bias current is critical, PC board surface leakage effects need to be considered. Surface leakage is caused by humidity, dust or other contamination on the board. Under low humidity conditions, a typical resistance between nearby traces is  $10^{12} \Omega$ . A 5V difference would cause 5pA of current to flow; which is similar to the MD1321/2/4 op amps' bias current at  $\pm 25^{\circ}$ C ( $\pm 10$ pA, typical).

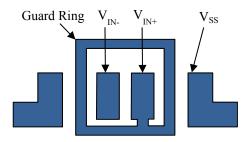

The best way to reduce surface leakage is to use a guard ring around sensitive pins (or traces). The guard ring is biased at the same voltage as the sensitive pin. An example of this type of layout is shown in Figure 24.

- 1. Non-inverting Gain and Unity-Gain Buffer:

- Connect the non-inverting pin (V<sub>IN+</sub>) to the input with a wire that does not touch the PCB surface.

- b) Connect the guard ring to the inverting input pin  $(V_{\text{IN-}})$ . This biases the guard ring to the Common Mode input voltage.

- 2. Inverting Gain and Transimpedance Gain Amplifiers (convert current to voltage, such as photo detectors):

- a) Connect the guard ring to the non-inverting input pin  $(V_{IN+})$ . This biases the guard ring to the same reference voltage as the op amp (e.g.,  $V_{DD}/2$  or ground).

- b) Connect the inverting pin (V<sub>IN-</sub>) to the input with a wire that does not touch the PCB surface.

Figure 24. Example Guard Ring Layout for Inverting Gain

### TYPICAL APPLICATION

#### **Differential Amplifier**

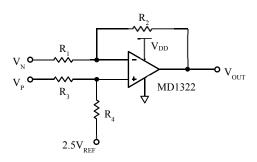

The circuit shown in Figure 25 performs the difference function. If the resistor ratios are equal to  $(R_4 / R_3 = R_2 / R_1)$ , then  $V_{OUT} = (V_P - V_N) \times R_2 / R_1 + V_{REF}$ .

Figure 25. Differential Amplifier

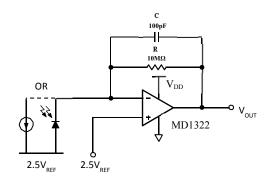

#### **Photodiode Application**

The MD1321/2/4 have very high impedance with an input bias current typically around 10 pA. This characteristic allows the MD1321/2/4 op amp to be used in photodiode applications and other applications that require high input impedance. Note that the MD1321/2/4 have significant voltage offset that can be removed by capacitive coupling or software calibration.

Figure 26 illustrates a photodiode or current measurement application. The feedback resistor is limited to  $10~\text{M}\Omega$  to avoid

excessive output offset. In addition, a resistor is not needed on the noninverting input to cancel bias current offset because the bias current-related output offset is not significant when compared to the voltage offset contribution. For best performance, follow the standard high impedance layout techniques, which include the following:

- Shielding the circuit.

- Cleaning the circuit board.

- Putting a trace connected to the noninverting input around the inverting input.

- Using separate analog and digital power supplies.

Figure 26. High Input Impedance Application—Photodiode

Amplifier

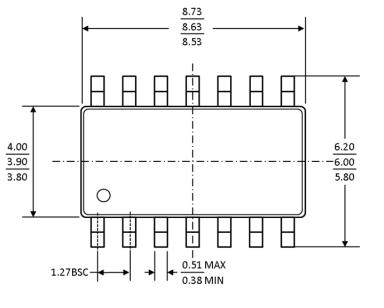

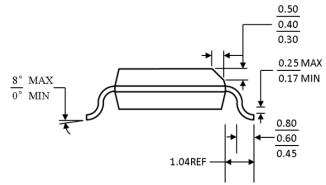

### PACKAGE OUTLINE DIMENSIONS

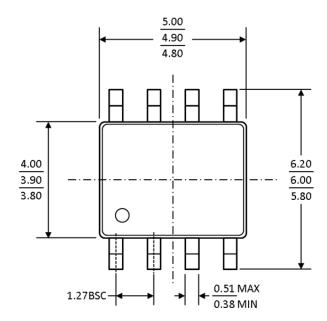

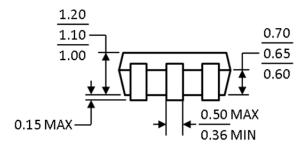

### COMPLIANT TO JEDEC STANDARD MS-012-AA

Figure 27 8-Lead Small Outline Package [SOIC]

Dimensions shown in millimeters

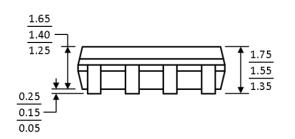

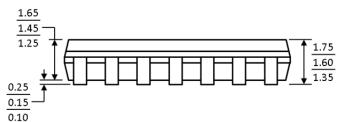

### PACKAGE OUTLINE DIMENSIONS

## COMPLIANT TO JEDEC STANDARD MO-178-AA

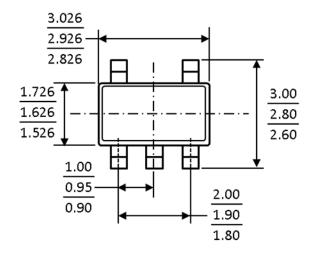

Figure 28 5-Lead Small Outline Transistor Package [SOT-23]

Dimensions shown in millimeters

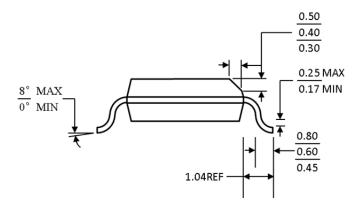

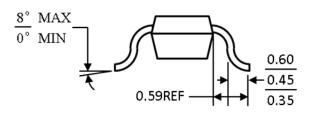

### PACKAGE OUTLINE DIMENSIONS

#### **COMPLIANT TO JEDEC STANDARD MS-012-AB**

Figure 29 14-Lead Small Outline Package [SOIC]

Dimensions shown in millimeters

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Operational Amplifiers - Op Amps category:

Click to view products by Mingda manufacturer:

Other Similar products are found below:

430227FB AZV831KTR-G1 UPC451G2-A UPC824G2-A LT1678IS8 042225DB 058184EB UPC822G2-A UPC258G2-A NCS5651MNTXG NCV33202DMR2G NJM324E NTE925 5962-9080901MCA\* AP4310AUMTR-AG1 HA1630D02MMEL-E HA1630S01LPEL-E SCY33178DR2G NJU77806F3-TE1 NCV5652MUTWG NCV20034DR2G LM2902EDR2G NTE778S NTE871 NTE924 NTE937 MCP6V16UT-E/OT MCP6V17T-E/MS MCP6V19T-E/ST SCY6358ADR2G LTC2065IUD#PBF NCS20282FCTTAG LM4565FVT-GE2 EL5420CRZ-T7A TSV791IYLT TSV772IQ2T TLV2772QPWR NJM2100M-TE1 NJM4556AM-TE1 MCP6487-E/SN MCP6487-E/MS AS324MTR-E1 AS358MMTR-G1 MCP6232T-EMNY MCP662-E/MF TLC081AIP TLC082AIP TLE2074ACDW TLV07IDR TLV2170IDGKT