# eMMC 32GB MKEV032GCB-SS510 Specification

V1.0 May 10, 2019

## Contents

| 1. | Forev | vord6                        |  |

|----|-------|------------------------------|--|

| 2. | Revis | ion History7                 |  |

| 3. | State | ment of Scope                |  |

| 4. | Gene  | ral Description9             |  |

|    | 4.1.  | Product list9                |  |

|    | 4.2.  | Feature9                     |  |

| 5. | Funct | tional Description11         |  |

| 6. | Produ | uct Specifications           |  |

|    | 6.1.  | Performance (Typical Value)  |  |

|    | 6.2.  | Electrical Characteristics   |  |

|    | 6.3.  | Product Architecture14       |  |

|    | 6.4.  | Operational Environment15    |  |

| 7. | Packa | age Configurations17         |  |

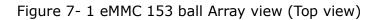

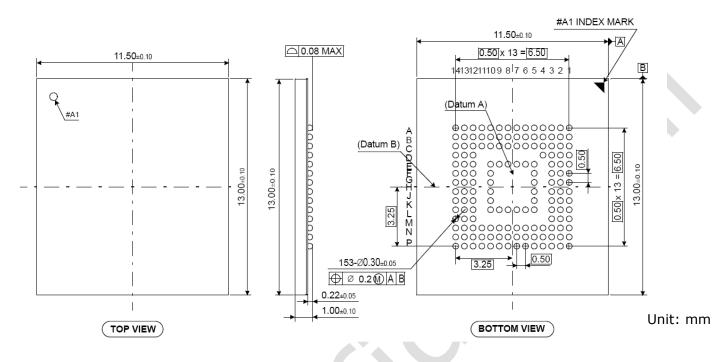

|    | 7.1.  | eMMC 153 Ball Array view17   |  |

|    | 7.2.  | eMMC Pin Description         |  |

|    | 7.3.  | eMMC Pin Assignment          |  |

|    | 7.4.  | 153 Ball Pin Configuration   |  |

| 8. | Usag  | e Overview21                 |  |

|    | 8.1.  | General Description          |  |

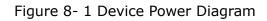

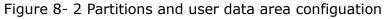

|    | 8.2.  | Partition Management21       |  |

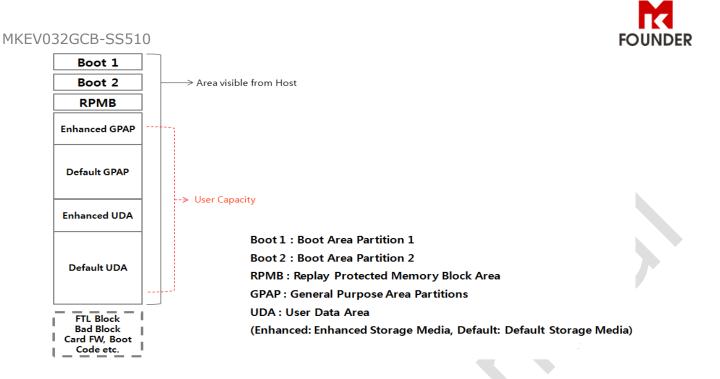

|    | 8.3.  | Boot operation mode23        |  |

|    | 8.4.  | Device identification mode25 |  |

|     | 8.5.  | Interrupt mode25                                         |  |

|-----|-------|----------------------------------------------------------|--|

|     | 8.6.  | Data transfer mode26                                     |  |

|     | 8.7.  | High Priority Interrupt28                                |  |

|     | 8.8.  | High-speed mode selection28                              |  |

|     | 8.9.  | HS200 timing mode selection29                            |  |

|     | 8.10. | HS400 timing mode selection                              |  |

|     | 8.11. | Bus width selection                                      |  |

| 9.  | Timin | g                                                        |  |

|     | 9.1.  | Time Out                                                 |  |

|     | 9.2.  | Bus Timing                                               |  |

|     | 9.3.  | High-Speed e•MMC interface timing                        |  |

|     | 9.4.  | Backward compatible e•MMC interface timing               |  |

|     | 9.5.  | Bus Timing for DAT Signals During 2X Data Rate Operation |  |

|     | 9.6.  | Bus Timing Specification in HS200 mode35                 |  |

|     | 9.7.  | Bus Timing Specification in HS400 mode38                 |  |

|     | 9.8.  | H/W Reset operation42                                    |  |

|     | 9.9.  | Power-up sequence                                        |  |

| 10. | Devic | e Register                                               |  |

|     | 10.1. | CID Register                                             |  |

|     | 10.2. | OCR Register                                             |  |

|     | 10.3. | CSD Register45                                           |  |

|     | 10.4. | Extended CSD Register46                                  |  |

# **List of Figures**

| FIGURE 6- 1 BUS SIGNAL LEVELS    | 13 |

|----------------------------------|----|

| FIGURE 6- 2 PRODUCT ARCHITECTURE | 14 |

| FIGURE 7- 1 EMMC 153 BALL ARRAY VIEW (TOP VIEW)1 | 7 |

|--------------------------------------------------|---|

| FIGURE 7- 2 EMMC 153 BALL PIN CONFIGURATION      | 0 |

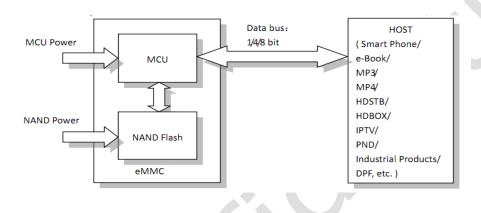

| FIGURE 8- 1 DEVICE POWER DIAGRAM                       | 21 |

|--------------------------------------------------------|----|

| FIGURE 8- 2 PARTITIONS AND USER DATA AREA CONFIGUATION | 22 |

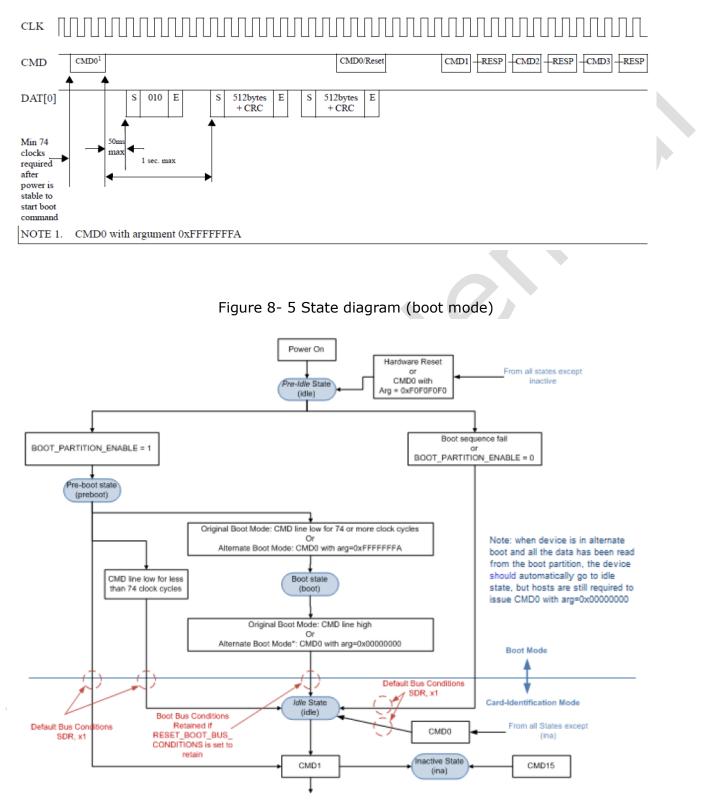

| FIGURE 8- 3 BOOT OPERATION MODE                        | 23 |

| FIGURE 8- 4 STATE DIAGRAM (ALTERNATIVE BOOT MODE)      | 24 |

| FIGURE 8- 5 STATE DIAGRAM (BOOT MODE)                  | 24 |

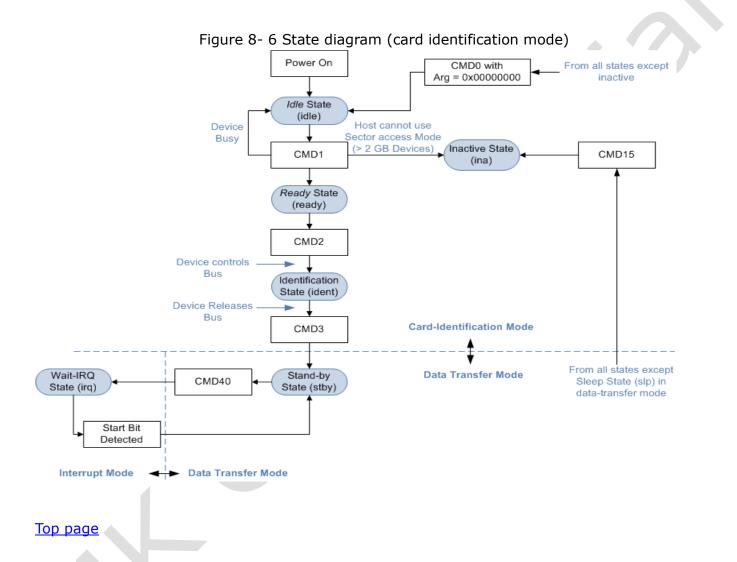

| FIGURE 8- 6 STATE DIAGRAM (CARD IDENTIFICATION MODE)   | 25 |

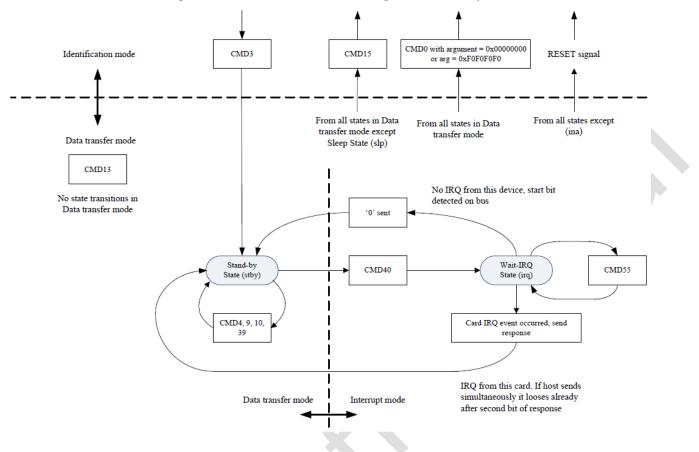

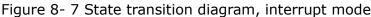

| FIGURE 8- 7 STATE TRANSITION DIAGRAM, INTERRUPT MODE   | 26 |

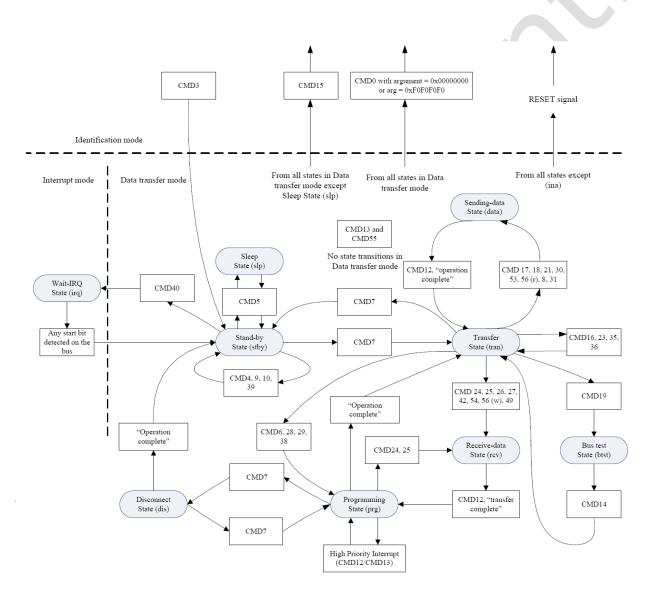

| FIGURE 8- 8 STATE DIAGRAM (DATA TRANSFER MODE)         | 27 |

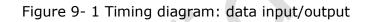

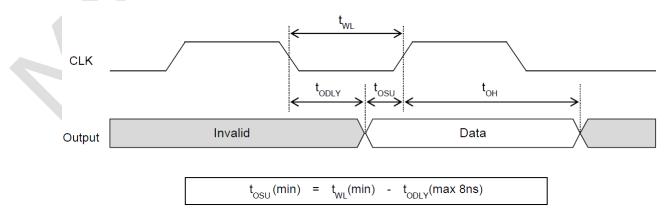

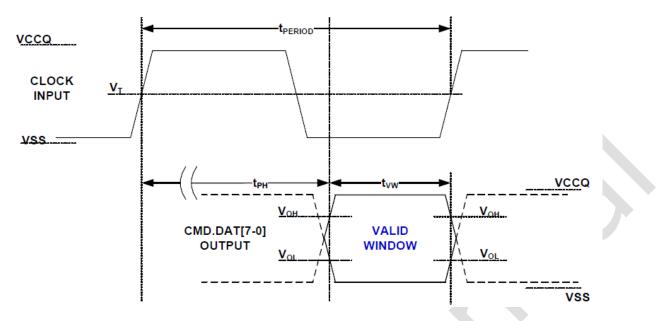

| FIGURE 9- 1 TIMING DIAGRAM: DATA INPUT/OUTPUT                        | 31 |

|----------------------------------------------------------------------|----|

| FIGURE 9- 2 OUTPUT TIMING                                            | 33 |

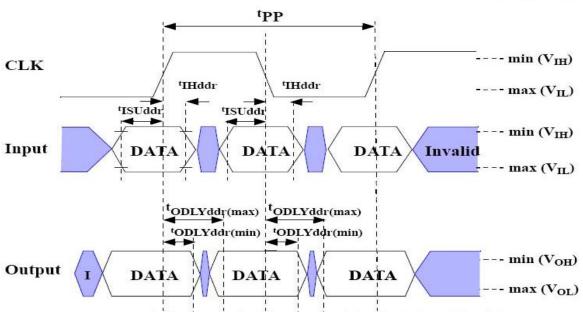

| FIGURE 9- 3 TIMING DIAGRAM: DATA INPUT/OUTPUT IN DUAL DATA RATE MODE | 34 |

# **List of Table**

| TABLE 4- 1 EMMC PRODUCT LIST                           | 9 |

|--------------------------------------------------------|---|

|                                                        |   |

| TABLE 6- 1 PERFORMANCE (TYPICAL VALUE)                 |   |

| TABLE 6- 2 ELECTRICAL CHARACTERISTICS- GENERAL         |   |

| TABLE 6- 3 POWER SUPPLY VOLTAGE                        |   |

| TABLE 6- 4 SUPPLY CURRENT                              |   |

| TABLE 6- 5 INTERNAL RESISTANCE AND DEVICE CAPACITANCE  |   |

| TABLE 6- 6 BUS SIGNAL LEVELS                           |   |

| TABLE 6- 7 PRODUCT ARCHITECTURE                        |   |

| TABLE 6- 8 OPERATIONAL ENVIRONMENT                     |   |

|                                                        |   |

| TABLE 7- 1 EMMC PIN DESCRIPTION                        |   |

| TABLE 7- 2 EMMC PIN ASSIGNMENT                         |   |

|                                                        |   |

| TABLE 8- 1 PARTITION CONFIGURATION TABLE               |   |

|                                                        |   |

| TABLE 9- 1 TIME OUT TABLE                              |   |

| TABLE 9- 2 HIGH SPEED MODE TIMING                      |   |

| TABLE 9- 3 BACKWARD-COMPATIBLE DEVICE MODE TIMING      |   |

| TABLE 9- 4 HIGH-SPEED DUAL DATA RATE INTERFACE TIMINGS |   |

|                                                        |   |

| TABLE 10- 1 CID TABLE                                  |   |

| TABLE 10- 2 OCR TABLE                                  |   |

| TABLE 10- 3 CSD TABLE                                  |   |

| TABLE 10- 4 EXTENDED CSD TABLE                         |   |

|                                                        |   |

### 1. Foreword

This document has been produced by MKEV032GCB-SS510, should the company modifies the contents of this specification, it will be re-released with an identifying change of release date and an increase in revision number as follows:

Revision mn.xy, where:

- mn the first two digit are incremented for major changes of substance, e.g., functional changes.

- xy the second two digits are incremented when minor changes have been incorporated into the specification, i.e., enhancements, corrections, updates, etc.

Top page

### 2. Revision History

| Revision        | Date       | Modified By | Description     |

|-----------------|------------|-------------|-----------------|

| 1.0             | 2019/05/10 | Ian Lin     | Initial release |

| <u>Top page</u> |            |             |                 |

|                 |            |             |                 |

# MKEV032GCB-SS510 3. Statement of Scope

This Datasheet document is described the eMMC MKEV032GCB-SS510 of methods and abstractions of reliability. The contents include the concept and measurement methodologies.

Top page

#### MKEV032GCB-SS510 **4. General Description**

MKEV032GCB-SS510 e•MMC is an embedded storage solution designed in a BGA package form. The operation of e•MMC is compatible with e•MMC 5.1 which is an industry standard.

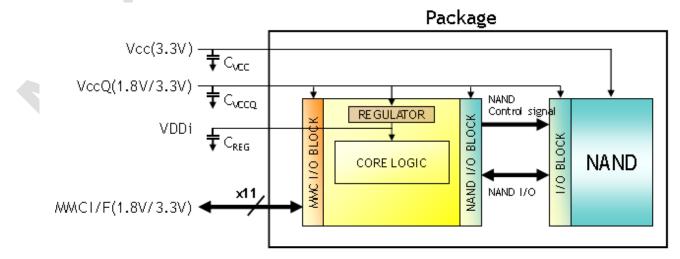

The e•MMC consists of NAND flash and a controller. 3.3V supply voltage is required for the NAND area (VCC) , whereas 1.8V or 3.3V dual supply voltage is supported for the interface.

There are several advantages of e•MMC. It is easy to be used on the standard interface, which allows the easy and widely used integration with general CPU. Any revision or amendment of NAND is invisible to the host as the embedded e•MMC controller insulates NAND technology from the host. It means that the host can support the newest processing flash without updating its hardware or software.

MKEV032GCB-SS510 e•MMC has high performance at a competitive-cost, high quality and low power consumption. e•MMC provides capacities from 4GB to 64GB.

### 4.1. Product list

Table 4- 1 eMMC product list

| Capacities | Part Number | Flash Type  | User Density | Package Size<br>(mm) | Package<br>Type |

|------------|-------------|-------------|--------------|----------------------|-----------------|

| 32GB       | MKEV032GCB- | 256Gb TLCx1 | 91.5 %       | 11.5x13x1.0          | 153FBGA         |

|            | SS510       |             |              |                      |                 |

Top page

### 4.2. Feature

- Compatible to JEDEC Embedded Multi-Media Card (e•MMC) Electrical Standard (5.1)

- Data bus width: 1bit, 4bit and 8bit.

- Power-down safeguard

- Hardware ECC engine

- Unique firmware backup mechanism

- Global wear leveling to expend NAND flash endurance

- > IDA (Initial Data Accelerating)

- Backward Compatible with JEDEC standard

- Supports HS400 mode

Top page

### 5. Functional Description

MKEV032GCB-SS510 e•MMC with powerful L2P NAND Flash management algorithm provides unique functions:

- Host independence from details of operating NAND flash.

- Internal ECC to correct defect in NAND flash.

- Power-down safeguard.

To prevent from false operating, a mechanism named power-down safeguard is added in the e•MMC. In the case of sudden power-losing, the e•MMC would work properly when it gets power again.

Global wear leveling.

To achieve the best stability and device endurance, this e•MMC equips the Global Wear Leveling algorithm. It ensures that not only normal area, but also the frequently accessed area, such as FAT, would be programmed and erased evenly.

IDA (Initial Data Accelerating)

IDA may accelerate the Initial data written to the e•MMC, saving the time up to 50% off in the downloading process.

### **6. Product Specifications**

### 6.1. Performance (Typical Value)

```

Table 6- 1 Performance (Typical Value)

```

| Part Number          | Capacity Operation |    | Mode  |        | Sequ<br>(Mi | ained<br>Iential<br>B/s) |

|----------------------|--------------------|----|-------|--------|-------------|--------------------------|

|                      |                    |    |       | (MB/s) | Read        | Write                    |

| MKEV032GCB-<br>SS510 | 32GB               | IO | HS400 | 120    | 260         | 18                       |

Test Condition: Bus width x8, 200MHz DDR, 512KB data transfer, w/o file system overhead, measured on internal board.

<u>Top page</u>

### 6.2. Electrical Characteristics

#### General

Table 6- 2 Electrical Characteristics- General

| Parameter                                                                                               | Symbol     | Test<br>Conditions | Min. | Max.                  | Unit |

|---------------------------------------------------------------------------------------------------------|------------|--------------------|------|-----------------------|------|

| Peak voltage on all lines                                                                               | -          | -                  | -0.5 | V <sub>CCQ</sub> +0.5 | V    |

| A                                                                                                       | Il Inputs  |                    |      |                       |      |

| Input Leakage Current (before initialization sequence1 and/or the internal pull up resistors connected) | -          | -                  | -100 | 100                   | μA   |

| Input Leakage Current (after initialization sequence and the internal pull up resistors disconnected)   | -          | -                  | -2   | 2                     | μA   |

| Α                                                                                                       | Il Outputs |                    |      |                       |      |

| Output Leakage Current (before initialization sequence)                                                 | -          | -                  | -100 | 100                   | μA   |

| Output Leakage Current (after initialization sequence)                                                  | -          | -                  | -2   | 2                     | μA   |

Note\*:

Initialization sequence is defined in Power-Up chapter of JEDEC/MMCA Standard.

#### **Power Supply Voltage**

Table 6- 3 Power Supply Voltage

| Parameter               | Symbol | Min. | Max. | Unit | Remark |

|-------------------------|--------|------|------|------|--------|

| Supply voltage 1 (NAND) | Vcc    | 2.7  | 3.6  | V    |        |

| Supply valtage 2 (I/O)  | N      | 2.7  | 3.6  |      |        |

| Supply voltage 2 (I/O)  | Vccq   | 1.7  | 1.95 | V    |        |

### **Supply Current**

Table 6- 4 Supply Current

| Paran     | neter | Symbol | Interleave        | Mode  | VccQ | ICCQ<br>(Max) | Unit |

|-----------|-------|--------|-------------------|-------|------|---------------|------|

|           |       |        |                   | SDR   | 1.8V | 100           | mA   |

|           |       |        |                   | SDR   | 3.3V | 100           |      |

|           |       |        | Non               | DDR   | 1.8V | 115           | m۸   |

|           | Read  | IROP   | Interleave        | DDR   | 3.3V | 120           | mA   |

|           |       |        |                   | HS200 | 1.8V | 150           | mA   |

| Operation |       |        |                   | HS400 | 1.8V | 250           | mA   |

| (RMS)     | Write | IWOP   | Non<br>Interleave | SDR   | 1.8V | 60            | mA   |

|           |       |        |                   |       | 3.3V | 60            |      |

|           |       |        |                   | DDR   | 1.8V | 75            |      |

|           |       |        |                   | DDR   | 3.3V | 80            | mA   |

|           |       |        |                   | HS200 | 1.8V | 120           | mA   |

|           |       |        |                   | HS400 | 1.8V | 120           | mA   |

### Internal resistance and Device capacitance

Table 6- 5 Internal resistance and Device capacitance

| Parameter                               | Symbol  | Test | Min | Max | Unit |

|-----------------------------------------|---------|------|-----|-----|------|

| Single device capacitance               | CDEVICE |      |     | 6   | pF   |

| Internal pull up resistance DAT1 – DAT7 | Rint    |      | 10  | 150 | KΩ   |

### **Bus Signal Levels**

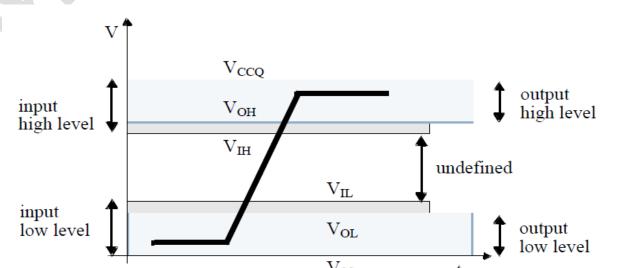

Figure 6- 1 Bus Signal Levels

#### Table 6- 6 Bus Signal Levels

| Parameter           | Symbol                           | Test<br>Conditions                  | Min.                    | Max.                    | Unit |  |  |

|---------------------|----------------------------------|-------------------------------------|-------------------------|-------------------------|------|--|--|

| Open-Drain Mode B   | Open-Drain Mode Bus Signal Level |                                     |                         |                         |      |  |  |

| Output HIGH voltage | V <sub>OH</sub>                  | $I_{OH} = -100 u A$                 | VccQ - 0.2              |                         | V    |  |  |

| Output LOW voltage  | Vol                              | I <sub>OL</sub> = 2mA               |                         | 0.3                     | V    |  |  |

| Push-Pull Mode Bu   | s Signal Le                      | vel (High-Volta                     | ige)                    |                         |      |  |  |

| Output HIGH voltage | V <sub>OH</sub>                  | IOH = -100uA @<br>VDD min           | 0.75*V <sub>cc</sub> Q  |                         | V    |  |  |

| Output LOW voltage  | Vol                              | IOL = 100uA @<br>VDD min            |                         | 0.125* VccQ             | V    |  |  |

| Input HIGH voltage  | VIH                              |                                     | 0.625* VccQ             | VccQ + 0.3              | V    |  |  |

| Input LOW voltage   | VIL                              |                                     | Vss - 0.3               | 0.25* VccQ              | V    |  |  |

| Push-Pull Mode Bu   | s Signal Le                      | vel (Dual-Volta                     | ge)                     |                         |      |  |  |

| Output HIGH voltage | Vон                              | I <sub>OH</sub> = -2mA @<br>VDD min | VccQ - 0.45             |                         | V    |  |  |

| Output LOW voltage  | Vol                              | I <sub>OL</sub> = 2mA @<br>VDD min  | 5                       | 0.45                    | V    |  |  |

| Input HIGH voltage  | VIH                              |                                     | 0.65* V <sub>cc</sub> Q | V <sub>CC</sub> Q + 0.3 | V    |  |  |

| Input LOW voltage   | VIL                              |                                     | Vss - 0.3               | 0.35* VccQ              | V    |  |  |

Top page

### 6.3. Product Architecture

Figure 6- 2 Product Architecture

#### Table 6- 7 Product Architecture

| Parameter                         | Symbol | Unit | Min. | Тур.    | Max. |

|-----------------------------------|--------|------|------|---------|------|

| VDDi capacitor value              | Creg   | uF   | 0.1  | 1       | 2.2  |

| V <sub>CC</sub> capacitor value   | Cvcc   | uF   | -    | 2.2+0.1 | -    |

| V <sub>cc</sub> Q capacitor value | Cvccq  | uF   | -    | 2.2+0.1 | -    |

Note\*:

e•MMC recommends that the minimum value should be usually applied as the value of CREG; CREG shall be compliant with X5R/X7R of EIA standard or B of JIS standard.

Top page

### 6.4. Operational Environment

Table 6- 8 Operational Environment

| Mode                      | Temperature   |

|---------------------------|---------------|

| Operating                 | -25℃ to 85℃   |

| Storage without operation | -40°C to 85°C |

| Top page |  |

|----------|--|

|          |  |

16 / 44

### 7. Package Configurations

### 7.1. eMMC 153 Ball Array view

Top page

### 7.2. eMMC Pin Description

Table 7-1 eMMC Pin Description

| Pin<br>Number | Name | Pin<br>Number | Name | Pin<br>Number | Name | Pin<br>Number | Name |

|---------------|------|---------------|------|---------------|------|---------------|------|

| A3            | DAT0 | C2            | VDDi | 35            | VSS  | N4            | VCCQ |

| A4            | DAT1 | C4            | VSSQ | J10           | VCC  | N5            | VSSQ |

| A5            | DAT2 | C6            | VCCQ | К5            | RSTN | P3            | VCCQ |

| A6            | VSS  | E6            | VCC  | K8            | VSS  | P4            | VSSQ |

| B2            | DAT3 | E7            | VSS  | К9            | VCC  | P5            | VCCQ |

| B3            | DAT4 | F5            | VCC  | M4            | VCCQ | P6            | VSSQ |

| B4            | DAT5 | G5            | VSS  | M5            | CMD  |               |      |

| B5            | DAT6 | H5            | DS   | M6            | CLK  |               |      |

| B6            | DAT7 | H10           | VSS  | N2            | VSSQ |               |      |

Note\*:

**NC**: No Connect, can be connected to ground or left floating.

**RFU**: Reserved for Future Use, should be left floating for future use.

VSF: Vendor Specific Function, shall be left floating.

Top page

### 7.3. eMMC Pin Assignment

Table 7- 2 eMMC Pin Assignment

| Signal  | Description                                                                       |

|---------|-----------------------------------------------------------------------------------|

| СГОСК   | Each cycle of the clock directs a transfer on the command line and on the data    |

| (CLK)   | lines. The frequency can vary between the minimum and the maximum clock           |

|         | frequency.                                                                        |

|         | This signal is a bidirectional command channel used for device initialization and |

|         | command transfer.                                                                 |

| COMMAND | The CMD Signal has 2 operation modes: open drain, for initialization, and push-   |

| (CMD)   | pull, for command transfer.                                                       |

|         | Commands are sent from the host to the device, and responses are sent from        |

|         | the device to the host.                                                           |

|             | These are bidirectional data signal. The DAT signals operate in push-pull mode. |

|-------------|---------------------------------------------------------------------------------|

|             | By default, after power-up or RESET, only DAT0 is used for data transfer. The   |

|             | controller can configure a wider data bus for data transfer withers using DAT   |

| DATA        | [3:0] (4bit mode) or DAT [7:0] (8bit mode).                                     |

| (DAT0-DAT7) | Includes internal pull-up resistors for data lines DAT [7:1]. Immediately after |

|             | entering the 4-bit mode, the device disconnects the internal pull-up resistors  |

|             | on the DAT1 and DAT2 lines.(The DAT3 line internal pull-up is left              |

|             | connected.)Upon entering the 8bit mode, the device disconnects the internal     |

|             | pull-up on the DAT1, DAT2, and DAT[7:4] lines.                                  |

| RESET       | Hardware Reset Input                                                            |

| (RSTN)      |                                                                                 |

| DS          | Data Strobe: Return Clock signal used in HS400 mode                             |

| VCCQ        | VCCQ is the power supply line for host interface, have two power mode: High     |

|             | power mode:2.7V~3.6V; Lower power mode:1.7V~1.95V                               |

| VCC         | VCC is the power supply line for internal flash memory, its power voltage range |

| VCC         | is:2.7V~3.6V                                                                    |

| VDDi        | VDDi is internal power node, not the power supply. Connect 0.1uF or 1uF         |

|             | capacitor VDDi to ground                                                        |

| VSS,VSSQ    | Ground lines.                                                                   |

|             |                                                                                 |

Note\*: All other pins are not connected [NC] and can be connected to GND or left floating.

### 7.4. 153 Ball Pin Configuration

Figure 7-2 eMMC 153 ball Pin Configuration

11.5mm×13mm×1.0mm Package Dimension

### 8. Usage Overview

### 8.1. General Description

The e•MMC can be operated in 1, 4, or 8-bit mode. NAND flash memory is managed by a controller inside, which manages ECC, wear leveling and bad block management. e•MMC provides easy integration with the host process that all flash management hassles are invisible to the host.

Top page

### 8.2. Partition Management

The embedded device offers also the possibility of configuring by the host additional split local memory partitions with independent addressable space starting from logical address 0x0000000 for different usage models. Default size of each Boot Area Partition is 128 KB and can be changed by Vendor Command as multiple of 128KB. Boot area partition size is calculated as (128KB \* BOOT\_SIZE\_MULTI) The size of Boot Area Partition 1 and 2 cannot be set independently and is set as same value Boot area partition which is enhanced partition. Therefore memory block area scan is classified as follows:

- > Factory configuration supplies boot partitions.

- The host is free to configure one segment in the User Data Area to be implemented as enhanced storage media, and to specify its starting location and size in terms of Write Protect Groups. The attributes of this Enhanced User Data Area can be programmed only once during the device life-cycle (one-time programmable).

Up to four General Purpose Area Partitions can be configured to store user data or sensitive data, or for other host usage models. The size of these partitions is a multiple of the write protect group. Size and attributes can be programmed once in device life-cycle (one-time programmable). Each of the General Purpose Area Partitions can be implemented with enhanced technological features.

Table 8- 1 Partition Configuration Table

| Boot1 Size | Boot2 Size | RPMB Size |

|------------|------------|-----------|

| 4MB        | 4MB        | 4MB       |

Top page

### 8.3. Boot operation mode

In boot operation mode, the master can read boot data from the slave (device) by keeping CMD line low or sending CMD0 with argument + 0xFFFFFFA, before issuing CMD1. The data can be read from either boot area or user area depending on register setting.

### 8.4. Device identification mode

While in device identification mode the host resets the device, validates operation voltage range and access mode, identifies the device and assigns a Relative device Address (RCA) to the device on the bus. All data communication in the Device Identification Mode uses the command line (CMD) only.

### 8.5. Interrupt mode

The interrupt mode on the system enables the master (host) to grant the transmission allowance to the slaves (card) simultaneously. This mode reduces the polling load for the host and hence, the power consumption of the system, while maintaining adequate responsiveness of the host to a card request for service. Supporting interrupt mode is an option, both for the host and the card.

#### Top page

### 8.6. Data transfer mode

All data communication in the Data Transfer Mode is point-to point between the host and the selected card (using addressed commands). All addressed commands get acknowledged by a response on the CMD line.

While the card is in Stand-by State, CMD7 is used to select the card and put it into the Transfer State by including card's relative address in the argument. If the card was previously selected and was in Transfer State its connection with the host is released and it will move back to the Stand-by State when deselected by CMD7 with any address in the argument that is not equal to card's own relative address. When CMD7 is issued with the reserved relative card address "0x0000", the card is put back to Stand-by State. Reception of CMD7 with card's own relative address while the card is in Transfer State is ignored by the card and may be treated as an Illegal Command. After the card is assigned an RCA it will not respond to identification commands — CMD1, CMD2, or CMD3.

While the card is in Disconnect State, CMD7 is used to select the card and put it into the Programming State by including card's relative address in the argument. If the card was previously selected and was in Programming State its connection with the host is released and it will move back to the Disconnect State when deselected by CMD7 with any address in the argument that is not equal to card's own relative address. Reception of CMD7 with card's own relative address while the card is in Programming State is ignored by the card and may be treated as an Illegal Command.

Top page

### 8.7. High Priority Interrupt

The high priority interrupt (HPI) mechanism enables servicing high priority requests, by allowing the device to interrupt a lower priority operation before it is actually completed, within OUT\_OF\_INTERRUPT \_TIME timeout. Host may need to repeat the interrupted operation or part of it to complete the original request. The HPI command may have one of two implementations in the device:

- CMD12 based on STOP\_TRANSMISSION command when the HPI bit in its argument is set.

- CMD13 based on SEND\_STATUS command when the HPI bit in its argument is set.

Host shall check the read-only HPI\_IMPLEMENTATION bit in HPI\_FEATURES (EXT\_CSD byte [503]) and use the appropriate command index accordingly.

| CMD Index                           | Name                                                                                    | Is interruptible? |

|-------------------------------------|-----------------------------------------------------------------------------------------|-------------------|

| CMD24                               | WRITE_BLOCK                                                                             | Yes               |

| CMD25                               | WRITE_MULTIPLE_BLOCK                                                                    | Yes               |

| CMD38                               | ERASE                                                                                   | Yes               |

| CMD6                                | SWITCH, byte BKOPS_START, any value                                                     | Yes               |

| CMD6                                | SWITCH, byte SANITIZE_START, any value                                                  | Yes               |

| CMD6                                | CMD6 SWITCH, byte POWER_OFF_NOTIFICATION, value<br>POWER OFF LONG or SLEEP NOTIFICATION |                   |

| CMD6                                | CMD6 SWITCH, byte POWER_OFF_NOTIFICATION, other values                                  |                   |

| CMD6                                | CACHE_CTRL when used for turning the cache OFF                                          | Yes               |

| CMD6                                | FLUSH_CACHE                                                                             | Yes               |

| CMD6 SWITCH, other bytes, any value |                                                                                         | No                |

| All others                          |                                                                                         | No                |

#### <u>Top page</u>

### 8.8. High-speed mode selection

After the host verifies that the Device complies with version 4.0, or higher, of this standard, it has to enable the high speed mode timing in the Device, before changing the clock frequency to a frequency between 26MHz and 52MHz. For the host to change to a higher clock frequency, it has to enable the high speed interface timing. The host uses the SWITCH command to write 0x01 to the HS\_TIMING byte, in the Modes segment of the EXT\_CSD register. If the host tries to write an

invalid value, the HS\_TIMING byte is not changed, the high speed interface timing is not enabled, and the SWITCH\_ERROR bit is set.

#### Top page

### 8.9. HS200 timing mode selection

HS200 is valid only at VCCQ= 1.8 V.

The bus width is set to SDR 4bit or SDR 8bit in HS200 mode.

After the host initializes the device, it must verify that the device supports the HS200 mode by reading the DEVICE\_TYPE field in the Extended CSD register. Then it may enable the HS200 timing mode in the device, before changing the clock frequency to a frequency higher than 52MHz.

After power-on or software reset(CMD0), the interface timing of the device is set as the default "Backward Compatible Timing". Device shall select HS200 Timing mode if required and perform the Tuning process if needed.

#### Top page

### 8.10.HS400 timing mode selection

The valid IO Voltage for HS400 is 1.8V for VCCQ.

The bus width is set to only DDR 8bit in HS400 mode.

HS400 supports the same commands as DDR52.

After the host initializes the device, host check whether the device supports the HS400 mode by reading the DEVICE\_TYPE field in the Extended CSD register. Then it enables the HS400 mode in the device before changing the clock frequency to a frequency higher than 52 MHz. After poweron or software reset (CMD0), the interface timing of the device is set as the default "Backward Compatible Timing".

### 8.11.Bus width selection

After the host has verified the functional pins on the bus it should change the bus width configuration accordingly, using the SWITCH command. The bus width configuration is changed by writing to the BUS\_WIDTH byte in the Modes Segment of the EXT\_CSD register (using the SWITCH command to do so). After power-on, or software reset, the contents of the BUS\_WIDTH byte is 0x00.

If the host tries to write an invalid value, the BUS\_WIDTH byte is not changed and the SWITCH\_ERROR bit is set. This register is written only.

### 9. Timing

### 9.1. Time Out

Table 9- 1 Time Out Table

| Timing parameter                           | Value  |

|--------------------------------------------|--------|

| Read timeout                               | 100 ms |

| Write timeout                              | 350 ms |

| Erase timeout                              | 600 ms |

| Force erase timeout                        | 3 min  |

| Trim timeout                               | 300 ms |

| Partition switching time out (after init ) | 30 ms  |

Top page

### 9.2. Bus Timing

Data must always be sampled on the rising edge of the clock

### 9.3. High-Speed e•MMC interface timing

| Parameter                                                 | Symbol                             | Min. | Max.              | Unit | Remark                                      |  |  |  |

|-----------------------------------------------------------|------------------------------------|------|-------------------|------|---------------------------------------------|--|--|--|

| Clock CLK <sup>(1)</sup>                                  |                                    |      |                   |      |                                             |  |  |  |

| Clock frequency Data Transfer<br>Mode (PP) <sup>(2)</sup> | f <sub>PP</sub>                    | 0    | 52 <sup>(3)</sup> | MHz  | $C_{L} \leq 30 pF$<br>Tolerance:<br>+100KHz |  |  |  |

| Clock frequency Identification<br>Mode(OD)                | Fod                                | 0    | 400               | KHz  | Tolerance: +20KHz                           |  |  |  |

| Clock low time / Clock high<br>time                       | tw∟∕twн                            | 6.5  | -                 | ns   | C∟ ≤ 30pF                                   |  |  |  |

| Clock rise time / Clock fall<br>time                      | t <sub>TLH</sub> /t <sub>THL</sub> | -    | 3                 | ns   | C <sub>L</sub> ≤ 30pF                       |  |  |  |

| Inputs CMD, DAT (referenced to CLK)                       |                                    |      |                   |      |                                             |  |  |  |

| Input set-up time                                         | tısu                               | 3    | -                 | ns   | C∟ ≤ 30pF                                   |  |  |  |

| Input hold time                                           | tıн                                | 3    | -                 | ns   | C∟ ≤ 30pF                                   |  |  |  |

| Outputs CMD, DAT (referenced                              | d to CLK)                          |      |                   |      |                                             |  |  |  |

| Output delay time during data                             | todly                              | -    | 13.7              | ns   | C∟ ≤ 30pF                                   |  |  |  |

| Output hold time toн                                      |                                    | 2.5  | -                 | ns   | C∟ ≤ 30pF                                   |  |  |  |

| Signal rise time <sup>(5)</sup>                           | t <sub>rise</sub>                  | -    | 3                 | ns   | C∟ ≤ 30pF                                   |  |  |  |

| Signal fall time                                          | t <sub>fall</sub>                  | -    | 3                 | ns   | C∟ ≤ 30pF                                   |  |  |  |

| Table | 9- | 2 | Hiah | speed | mode | timina |

|-------|----|---|------|-------|------|--------|

| Table | 2  | ~ | Ingn | Specu | mouc | unning |

Note\*:

- 1) CLK timing is measured at 50% of VccQ.

- 2) e•MMC shall support the full frequency range from 0-26MHz, or 0-52MHz.

- 3) e•MMC can operate as high-speed interface timing at 26MHz clock frequency.

- 4) CLK rise and fall times are measured by min(VIH) and max(VIL).

- 5) Inputs CMD,DAT rise and fall times area measured by min(VIH) and max(VIL), and outputs CMD, DAT rise and fall times are measured by min(VOH) and max(VOL).

Top page

### **9.4.** Backward compatible e•MMC interface timing

| Parameter                                                 | Symbol Min. Max |   | Max. | Unit | Remark    |  |  |  |

|-----------------------------------------------------------|-----------------|---|------|------|-----------|--|--|--|

| Clock CLK <sup>(2)</sup>                                  |                 |   |      |      |           |  |  |  |

| Clock frequency Data Transfer<br>Mode (PP) <sup>(3)</sup> | f <sub>PP</sub> | 0 | 26   | MHz  | C∟ ≤ 30pF |  |  |  |

| Clock frequency Identification<br>Mode(OD)                | fod             | 0 | 400  | KHz  |           |  |  |  |

Table 9- 3 backward-compatible device mode timing

| Symbol                             | Min.                                                              | Max.                                                                                                          | Unit                                                                                                                                                                                                                   | Remark                                                                                                                                                                                           |

|------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| twı/twн                            | 10                                                                | -                                                                                                             | ns                                                                                                                                                                                                                     | C∟ ≤ 30pF                                                                                                                                                                                        |

| t <sub>TLH</sub> /t <sub>THL</sub> | -                                                                 | 10                                                                                                            | ns                                                                                                                                                                                                                     | $C_L \leq 30 pF$                                                                                                                                                                                 |

| to CLK)                            |                                                                   |                                                                                                               |                                                                                                                                                                                                                        |                                                                                                                                                                                                  |

| t <sub>ISU</sub>                   | 3                                                                 | -                                                                                                             | ns                                                                                                                                                                                                                     | C <sub>L</sub> ≤ 30pF                                                                                                                                                                            |

| t <sub>IH</sub>                    | 3                                                                 | -                                                                                                             | ns                                                                                                                                                                                                                     | $C_{L} \leq 30 pF$                                                                                                                                                                               |

| to CLK)                            |                                                                   |                                                                                                               |                                                                                                                                                                                                                        |                                                                                                                                                                                                  |

| tosu                               | -                                                                 | 13.7                                                                                                          | ns                                                                                                                                                                                                                     | C∟ ≤ 30pF                                                                                                                                                                                        |

| t <sub>он</sub>                    | 2.5                                                               | -                                                                                                             | ns                                                                                                                                                                                                                     | C∟ ≤ 30pF                                                                                                                                                                                        |

|                                    | twL/twH<br>tTLH/tTHL<br>to CLK)<br>tISU<br>tIH<br>to CLK)<br>toSU | twL/twн     10       trLH/tTHL     -       to CLK)     3       tISU     3       tIH     3       to CLK)     - | twl/twh       10       -         tml/tml       -       10         tml/tml       -       10         to CLK)       3       -         tISU       3       -         tIH       3       -         to CLK)       -       13.7 | twL/twн     10     -     ns       tTLH/tTHL     -     10     ns       to CLK)     -     10     ns       tISU     3     -     ns       tIH     3     -     ns       to CLK)     -     13.7     ns |

Note\*:

- 1) The e•MMC must always start with the backward-compatible interface timing. The timing mode can be switched to high-speed interface timing by the host sending the SWITCH command (CMD6) with the argument for high-speed interface select.

- 2) CLK timing is measured at 50% of VccQ

- For compatibility with e•MMCs that support the v4.2 standard or earlier, host should not use

>26MHz before switching to high-speed interface timing.

- 4) tosu and  $t_{OH}$  are defined as values from clock rising edge. However, the e•MMC device will utilize clock falling edge to output data in backward compatibility mode. Therefore, it is recommended for hosts either to set  $t_{WL}$  value as long as possible within the range which will not go over  $t_{CK}$ - $t_{OH}$ (min) in the system or to use slow clock frequency, so that host could have data set up margin for the device.

use slow clock frequency, so that host could have data set up margin for the device.

MKEV032GCB-SS510 e•MMC device utilize clock falling edge to output data in backward compatibility mode.

Host should optimize the timing in order to have data set up margin as follows.

Figure 9- 2 Output timing

Top page

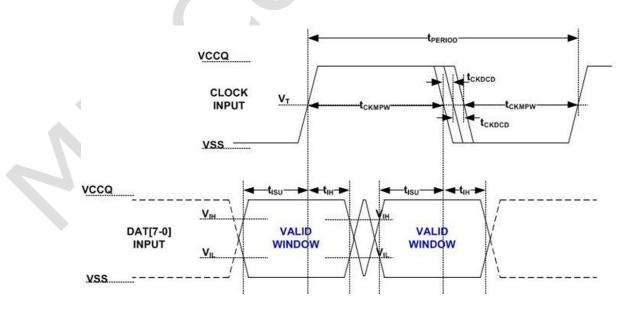

### 9.5. Bus Timing for DAT Signals During 2X Data Rate Operation

These timings applies to the DAT [7:0] signals only when the device is configured for dual data mode operation. In this dual data mode, the DAT signals operates synchronously of both the rising and the falling edges of CLK. the CMD signal still operates synchronously of the rising edge of CLK and therefore complies with the bus timing specified in High-speed interface timing or Backward-compatible interface timing.

Figure 9- 3 Timing diagram: data input/output in dual data rate mode

In DDR mode data on DAT[7:0] lines are sampled on both edges of the clock (not applicable for CMD line)

Table9- 4 High-speed dual data rate interface timings

| Parameter                                   | Symbol              | Min. | Max. | Unit | Remark                          |  |  |  |

|---------------------------------------------|---------------------|------|------|------|---------------------------------|--|--|--|

| Clock CLK <sup>(1)</sup>                    |                     |      |      |      |                                 |  |  |  |

| Clock duty cycle                            |                     | 45   | 55   | %    | Includes jitter, phase<br>noise |  |  |  |

| Inputs DAT (referenced to CLK-DDR mode)     |                     |      |      |      |                                 |  |  |  |

| Input set-up time                           | t <sub>ISUDDR</sub> | 2.5  | -    | ns   | C∟ ≤ 20 pF                      |  |  |  |

| Input hold time                             | t <sub>IHDDR</sub>  | 2.5  | -    | ns   | C <sub>L</sub> ≤ 20 pF          |  |  |  |

| Outputs DAT (referenced to CLK-DDR mode)    |                     |      |      |      |                                 |  |  |  |

| Output delay time during data<br>transfer   | todlyddr            | 1.5  | 7    | ns   | C <sub>L</sub> ≤ 20 pF          |  |  |  |

| Signal rise time(all signal) <sup>(2)</sup> | t <sub>RISE</sub>   | -    | 2    | ns   | C∟ ≤ 20 pF                      |  |  |  |

| Signal fall time (all signal)               | t <sub>FALL</sub>   | -    | 2    | ns   | C <sub>L</sub> ≤ 20 pF          |  |  |  |

Note\*:

- 1) CLK timing is measured at 50% of VccQ.

- 2) Inputs CMD, DAT rise and fall times are measured by min (VIH) and max (VIL), and outputs CMD, DAT rise and fall times are measured by min (VOH) and max (VOL).

Top page

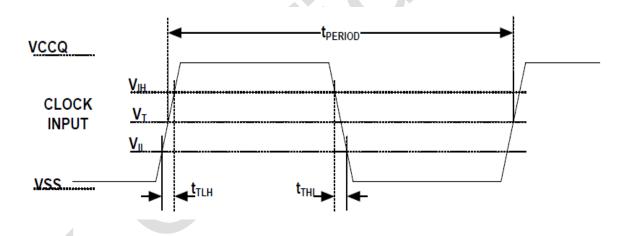

### 9.6. Bus Timing Specification in HS200 mode

#### **HS200** Clock Timing

Host CLK Timing in HS200 mode shall conform to the timing specified in following figure and Table. CLK input shall satisfy the clock timing over all possible operation and environment conditions. CLK input parameters should be measured while CMD and DAT lines are stable high or low, as close as possible to the Device. The maximum frequency of HS200 is 200MHz. Hosts can use any frequency up to the maximum that HS200 mode allows.

NOTE 1 VIH denote VIH(min.) and VIL denotes VIL(max.).

NOTE 2 VT=0.975V - Clock Threshold, indicates clock reference point for timing measurements.

| - |                           |      |                  |      |                                                                                                                                                                                         |

|---|---------------------------|------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Symbol                    | Min. | Max.             | Unit | Remark                                                                                                                                                                                  |

|   | <sup>t</sup> PERIOD       | 5    |                  | ns   | 200MHz (Max.), between rising edges                                                                                                                                                     |

|   | <sup>t</sup> ТLH,<br>tTHL |      | 0.2 *<br>tPERIOD | ns   | <sup>t</sup> TLH, <sup>t</sup> THL < 1ns (max.) at 200MHz,<br>CDEVICE=6pF,The absolute maximum<br>value of <sup>t</sup> TLH, <sup>t</sup> THL is 10ns regardless<br>of clock frequency. |

|   | Duty Cycle                | 30   | 70               | %    |                                                                                                                                                                                         |

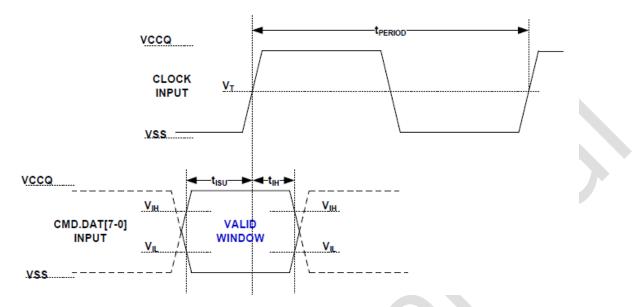

### **HS200** Device Input Timing

NOTE1 tISU and tIH are measured at VIL(max.) and VIH(min.) NOTE2 VIH denote VIH(min.) and VIL denotes VIL(max.).

| Symbol           | Min. | Max. | Unit | Remark        |

|------------------|------|------|------|---------------|

| <sup>t</sup> ISU | 1.40 |      | ns   | Cdevice ≤ 6pF |

| <sup>t</sup> IH  | 0.8  |      | ns   | Cdevice ≤ 6pF |

#### HS200 Device Output Timing

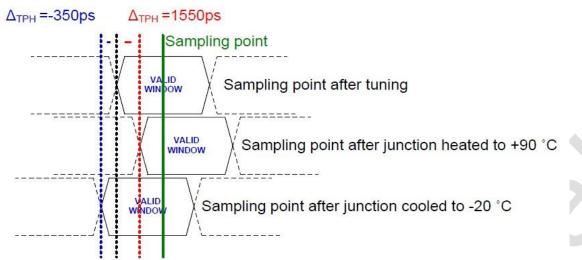

tPH parameter is defined to allow device output delay to be longer than tPERIOD. After initialization, the tPH may have random phase relation to the clock. The Host is responsible to find the optimal sampling point for the Device outputs, while switching to the HS200 mode. While setting the sampling point of data, a long term drift, which mainly depends on temperature drift, should be considered. The temperature drift is expressed by  $\Delta$ TPH. Output valid data window (tVW) is available regardless of the drift ( $\Delta$ TPH) but position of data window varies by the drift.

NOTE VOH denotes VOH(min.) and VOL denotes VOL(max.).

| Symbol | Min.                  | Max.                  | Unit | Remark                                                                                                                                                                                                                                                        |

|--------|-----------------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tPH    | 0                     | 2                     | UI   | Device output momentary phase from<br>CLK input to CMD or DAT lines output.<br>Does not include a long term<br>temperature drift.                                                                                                                             |

| ΔTPH   | -350<br>(ΔT = -20 °C) | +1550<br>(ΔT = 90 °C) | ps   | Delay variation due to temperature<br>change after tuning. Total allowable<br>shift of output valid window (TVW) from<br>last system Tuning procedure $\Delta$ TPH is<br>2600ps for $\Delta$ T from -25 °C to 125 °C<br>during operation.                     |

| tVW    | 0.575                 |                       | UI   | tVW =2.88ns at 200MHz Using test<br>circuit in following figure including skew<br>among CMD and DAT lines created by<br>the Device. Host path may add Signal<br>Integrity induced noise, skews, etc.<br>Expected tVW at Host input is larger<br>than 0.475UI. |

## **Δ**<sub>TPH</sub> consideration

### **Implementation Guide:**

Host should design to avoid sampling errors that may be caused by the  $\Delta$ TPH drift.

It is recommended to perform tuning procedure while Device wakes up, after sleep. One simple way to overcome the  $\Delta$ TPH drift is by reduction of operating frequency.

#### <u>Top page</u>

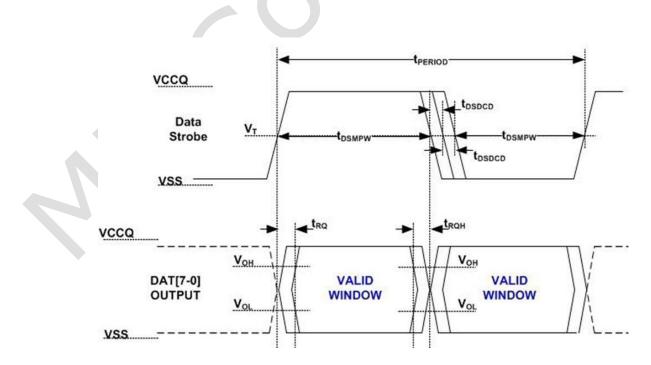

## 9.7. Bus Timing Specification in HS400 mode

### **HS400 Input Timing**

The CMD input timing for HS400 mode is the same as CMD input timing for HS200 mode.

Note : VIH denote VIH(min) and VIL denotes VIL(max)

| Parameter                     | Symbol         | Min.  | Max. | Unit | Remark                                                                                            |

|-------------------------------|----------------|-------|------|------|---------------------------------------------------------------------------------------------------|

| Input CLK                     |                |       |      |      |                                                                                                   |

| Cycle time data transfer mode | tPERIOD        | 5     | -    | ns   | 200MHz(Max), between rising edges<br>With respect to VT                                           |

| Slew rate                     | SR             | 1.125 | -    | V/ns | With respect to $V_{IH}$ / $V_{IL}$                                                               |

| Duty cycle<br>distortion      | tCKDCD         | 0.0   | 0.3  | ns   | Allowable deviation from an ideal 50% duty cycle. With respect to VT Includes jitter, phase noise |

| Minimum pulse<br>width        | tCKMPW         | 2.2   | -    | ns   | With respect to VT                                                                                |

| Input DAT(refe                | renced to CLK) |       |      |      |                                                                                                   |

| Input set-up<br>time          | tISUddr        | 0.4   | -    | ns   | CDevice<=6pF<br>With respect to VIH /VIL                                                          |

| Input hold time               | tIHddr         | 0.4   | -    | ns   | CDevice<=6pF<br>With respect to VIH /VIL                                                          |

| Slew rate                     | SR             | 1.125 | -    | V/ns | With respect to VIH /VIL                                                                          |

**DER**

FC

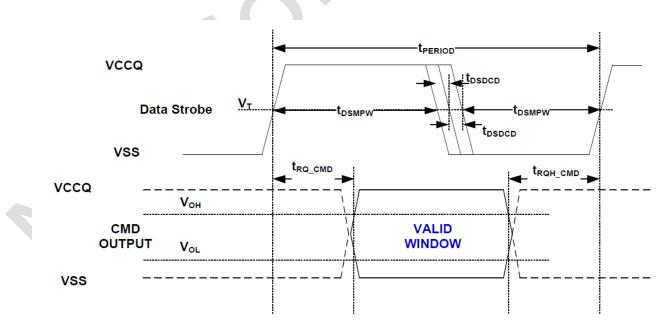

## **HS400 Device Output Timing**

The Data Strobe is used to read data in HS400 mode. The Data Strobe is toggled only during data read or CRC status response.

Note : VOH denotes VOH(min) and VOL denotes VOL(max)

| Parameter                     | Symbol           | Min.    | Max. | Unit | Remark                                                                                                                        |  |

|-------------------------------|------------------|---------|------|------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Data Strobe                   |                  |         |      |      |                                                                                                                               |  |

| Cycle time data transfer mode | tPERIOD          | 5       | -    | ns   | 200MHz(Max), between rising edges<br>With respect to VT                                                                       |  |

| Slew rate                     | SR               | 1.125   | -    | V/ns | With respect to VOH/VOL and HS400                                                                                             |  |

| Duty cycle<br>distortion      | tDSDCD           | 0.0     | 0.2  | ns   | Allowable deviation from the input<br>CLK duty cycle distortion(tCKDCD)<br>With respect to VT Includes jitter,<br>phase noise |  |

| Minimum pulse<br>width        | tDSMPW           | 2.0     | -    | ns   | With respect to VT                                                                                                            |  |

| Output DAT(ref                | ferenced to Data | Strobe) |      |      |                                                                                                                               |  |

| Output skew                   | tRQ              | -       | 0.4  | ns   | With respect to VOH /VOL and HS400                                                                                            |  |

| Output hold<br>skew           | tRQH             | -       | 0.4  | ns   | With respect to VOH /VOL and HS400                                                                                            |  |

| Slew rate                     | SR               | 1.125   | -    | V/ns | With respect to VOH /VOL and HS400                                                                                            |  |

## HS400 Device Command Output Timing

The Data Strobe is used to response of any command in HS400 mode.

Note : VOH denotes VOH(min) and VOL denotes VOL(max)

| FOUNDER FOUNDER               |                  |             |      |      |                                                                                                                               |  |

|-------------------------------|------------------|-------------|------|------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                     | Symbol           | Min.        | Max. | Unit | Remark                                                                                                                        |  |

| Data Strobe                   |                  |             |      |      |                                                                                                                               |  |

| Cycle time data transfer mode | tPERIOD          | 5           | -    | ns   | 200MHz(Max), between rising edges<br>With respect to VT                                                                       |  |

| Slew rate                     | SR               | 1.125       | -    | V/ns | With respect to VOH/VOL and HS400 reference load                                                                              |  |

| Duty cycle distortion         | tDSDCD           | 0.0         | 0.2  | ns   | Allowable deviation from the input<br>CLK duty cycle distortion(tCKDCD)<br>With respect to VT Includes jitter,<br>phase noise |  |

| Minimum pulse<br>width        | tDSMPW           | 2.0         | -    | ns   | With respect to VT                                                                                                            |  |

| CMD Response                  | (referenced to I | Data Strobe | e)   |      |                                                                                                                               |  |

| Output<br>skew(CMD)           | tRQ_CMD          | -           | 0.4  | ns   | With respect to VOH /VOL and HS400 reference                                                                                  |  |

| Output hold<br>skew(CMD)      | tRQH_CMD         | -           | 0.4  | ns   | With respect to VOH /VOL and HS400 reference                                                                                  |  |

| Slew rate                     | SR               | 1.125       | -    | V/ns | With respect to VOH /VOL and HS400 reference                                                                                  |  |

FC

FP

## HS400 Capacitance

The Data Strobe is used to read data in HS400 mode. The Data Strobe is toggled only during data read or CRC s

| Parameter                                | Symbol           | Min. | Тур. | Max. | Unit | Remark |

|------------------------------------------|------------------|------|------|------|------|--------|

| Pull-up resistance for CMD               | R <sub>CMD</sub> | 4.7  | -    | 100  | KΩ   |        |

| Pull-up resistance for DAT0-7            | R <sub>DAT</sub> | 10   | -    | 100  | KΩ   |        |

| Pull-down resistance for Data            | Rds              | 10   | -    | 100  | KΩ   |        |

| Internal pull up resistance<br>DAT1-DAT7 | R <sub>int</sub> | 10   | -    | 150  | KΩ   |        |

| Bus signal line capacitance              | C∟               | -    | -    | 13   | pF   |        |

| Single Device capacitance                | CDEVICE          | -    | -    | 6    | pF   |        |

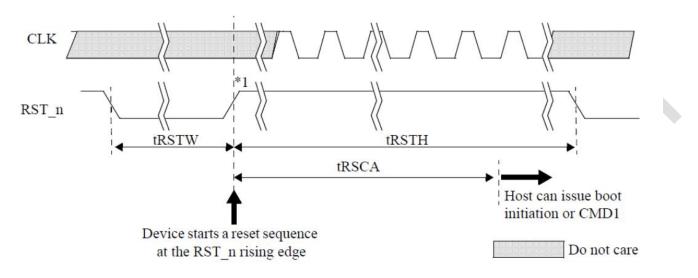

## 9.8. H/W Reset operation

Device will detect the rising edge of RST\_n signal to trigger internal reset sequence.

Note1: Device will detect the rising edge of RST\_n signal to trigger internal reset sequence

### **H/W Reset Timings**

| Parameter                         | Symbol | Test Conditions | Min.             | Max. | Unit    |

|-----------------------------------|--------|-----------------|------------------|------|---------|

| RST_n pulse width                 | tRSTW  |                 | 1                |      | $\mu$ S |

| RST_n to Command time             | tRSCA  |                 | 200 <sup>1</sup> |      | $\mu$ S |

| RST_n high period (interval time) | tRSTH  | · ·             | 1                |      | $\mu$ S |

1) 74 cycles of clock signal required before issuing CMD1 or CMD0 with argument 0xFFFFFFA

2) During the device internal initialization sequence right after power on, device may not be able to detect RST\_n signal, because the device may not complete loading RST\_n\_ENABLE bits of the extended CSD register into the controller yet.

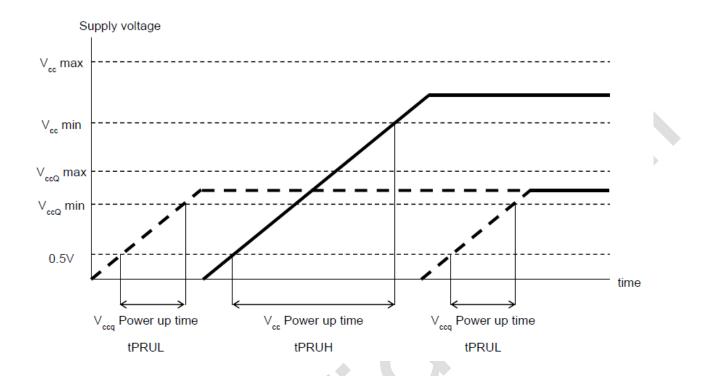

## 9.9. Power-up sequence

## **Power-up parameter**

| Parameter                | Symbol | Test Conditions | Min.       | Max.  | Remark |

|--------------------------|--------|-----------------|------------|-------|--------|

| Supply power-up for 3.3V | tPRUH  | •               | $5\mu m s$ | 35 ms |        |

| Supply power-up for 1.8V | tPRUL  |                 | 5 µ s      | 25 ms |        |

# 10. Device Register

## 10.1. CID Register

The Card Identification (CID) register is 128 bits wide. It contains the card identification information used during the card identification phase. Every individual flash or I/O card shall have a unique identification number. Every type of ROM cards (defined by content) shall have a unique identification number. The structure of the CID register is defined in the following sections.

| Name                  | Field | Width | CID-slice | CID Value                    |

|-----------------------|-------|-------|-----------|------------------------------|

| Manufacture ID        | MID   | 8     | [127:120] | EAh                          |

| Reserved              | -     | 6     | [119:114] | Oh                           |

| Card/BGA              | CBX   | 2     | [113:112] | 01h                          |

| OEM/Application ID    | OID   | 8     | [111:104] | 0Eh                          |

| Product name          | PNM   | 48    | [103:56]  | 53 50 65 4D 4D<br>43(SPeMMC) |

| Product revision      | PRV   | 8     | [55:48]   | 10h                          |

| Product serial number | PSN   | 32    | [47:16]   | Serial number                |

| Manufacturing date    | MDT   | 8     | [15:8]    | Manufacturing date           |

| CRC7 checksum         | CRC   | 7     | [7:1]     | CRC                          |

| Not used, always '1'  | -     | 1     | [0:0]     | 1h                           |

#### Table 10- 1 CID Table

### <u>Top page</u>

## 10.2. OCR Register

The 32-bit operation conditions register stores the VCCQ voltage profile of the e•MMC In addition, this register includes a status information bit. This status bit is set if the e•MMC power up procedure has been finished. The OCR register shall be implemented by e•MMC.

#### Table 10- 2 OCR Table

| OCR bit | VCCQ voltage window | eMMC                                 |

|---------|---------------------|--------------------------------------|

| [31]    | power up status b   | it (busy)*                           |

| [30:29] | Access Mode         | 00b (byte mode)<br>10b (sector mode) |

| [28:24] | Reserved            | 0 0000ь 📉                            |

| [23:15] | 2.7V - 3.6V         | 1 1111 1111 b                        |

| [14:8]  | 2.0V – 2.6V         | 000 0000b                            |

| [7]     | 1.7V~1.95V          | 1b                                   |

| [6:0]   | Reserved            | 000 0000b                            |

Note\*:

This bit is set to LOW if the e•MMC has not finished the power up routine. The supported voltage range is coded as shown in table.

#### Top page

## 10.3. CSD Register

The Card-Specific Data (CSD) register provides information on how to access the card contents. The CSD defines the data format, error correction type, maximum data access time; data transfer speed, whether the DSR register can be used etc. The programmable part of the register (entries marked by W or E, see below) can be changed by CMD27. The type of the CSD Registry entries coded as follows:

| Name                         | Field                  | Width | Cell<br>Type | CSD-<br>slice | CSD<br>Value |

|------------------------------|------------------------|-------|--------------|---------------|--------------|

| CSD structure                | CSD_STRUCTURE          | 2     | R            | [127:126]     | 3h           |

| System specification version | SPEC_VERS              | 4     | R            | [125:122]     | 4h           |

| Reserved                     | -                      | 2     | R            | [121:120]     | 0h           |

| Data read access-time 1      | TAAC                   | 8     | R            | [119:112]     | 7Fh          |

| Data read access-time 2      | NSAC                   | 8     | R            | [111:104]     | 8h           |

| Max. data transfer rate      | TRAN_SPEED             | 8     | R            | [103:96]      | 32h          |

| Device command classes       | CCC                    | 12    | R            | [95:84]       | 5F5h         |

| Max. read data block length  | READ_BL_LEN            | 4     | R            | [83:80]       | 9h           |

| Partial block read allowed   | READ_BL_PARTIAL        | 1     | R            | [79]          | 0h           |

| Write block misalignment     | WRITE_BLK_MISALIG<br>N | 1     | R            | [78]          | 0h           |

| Read block misalignment      | READ_BLK_MISALIGN      | 1     | R            | [77]          | 0h           |

| DSR implemented              | DSR_IMP                | 1     | R            | [76]          | 0h           |

Table 10- 3 CSD Table

| MKEV032GCB-SS510               | 1                 |       |              |               | FOUNDER      |

|--------------------------------|-------------------|-------|--------------|---------------|--------------|

| Name                           | Field             | Width | Cell<br>Type | CSD-<br>slice | CSD<br>Value |

| Reserved                       | -                 | 2     | R            | [75:74]       | 0h           |

| Device size                    | C_SIZE            | 12    | R            | [73:62]       | FFFh         |

| Max. read current @ VDD min    | VDD_R_CURR_MIN    | 3     | R            | [61:59]       | 6h           |

| Max. read current @ VDD max    | VDD_R_CURR_MAX    | 3     | R            | [58:56]       | 6h           |

| Max. write current @ VDD min   | VDD_W_CURR_MIN    | 3     | R            | [55:53]       | 6h           |

| Max. write current @ VDD max   | VDD_W_CURR_MAX    | 3     | R            | [52:50]       | 6h           |

| Device size multiplier         | C_SIZE_MULT       | 3     | R            | [49:47]       | 7h           |

| Erase group size               | ERASE_GRP_SIZE    | 5     | R            | [46:42]       | 1Fh          |

| Erase group size multiplier    | ERASE_GRP_MULT    | 5     | R            | [41:37]       | 1Fh          |

| Write protect group size       | WP_GRP_SIZE       | 5     | R            | [36:32]       | Fh           |

| Write protect group enable     | WP_GRP_ENABLE     | 1     | R            | [31]          | 1h           |

| Manufacturer default ECC       | DEFAULT_ECC       | 2     | R            | [30:29]       | 0h           |

| Write speed factor             | R2W_FACTOR        | 3     | R            | [28:26]       | 5h           |

| Max. write data block length   | WRITE_BL_LEN      | 4     | R            | [25:22]       | 9h           |

| Partial block write allowed    | WRITE_BL_PARTIAL  | 1     | R            | [21]          | 0h           |

| Reserved                       | -                 | 4     | R            | [20:17]       | 0h           |

| Content protection application | CONTENT_PROT_APP  | 1     | R            | [16]          | 0h           |

| File format group              | FILE_FORMAT_GRP   | 1     | R/W          | [15]          | 0h           |

| Copy flag (OTP)                | СОРҮ              | 1     | R/W          | [14]          | 0h           |

| Permanent write protection     | PERM_WRITE_PROTEC | 1     | R/W          | [13]          | 0h           |

| Temporary write protection     | TMP_WRITE_PROTECT | 1     | R/W/E        | [12]          | 0h           |

| File format                    | FILE_FORMAT       | 2     | R/W          | [11:10]       | 0h           |

| ECC code                       | ECC               | 2     | R/W/E        | [9:8]         | 0h           |

| CRC                            | CRC               | 7     | R/W/E        | [7:1]         | 0h           |

| Not used, always '1'           | -                 | 1     | -            | [0]           | 1h           |

#### <u>Top page</u>

## **10.4. Extended CSD Register**

The Extended CSD register defines the card properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the card capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the card is working in. These modes can be changed by the host by means of the SWITCH command.

Multi bytes field is interpreted in little endian byte order.

| R:       | Read only.                                                          |

|----------|---------------------------------------------------------------------|

| W:       | One time programmable and not readable.                             |

| R/W:     | One time programmable and readable.                                 |

| W/E:     | Multiple writable with value kept after power failure, H/W reset    |

|          | assertion and any CMD0 reset and not readable.                      |

| R/W/E:   | Multiple writable with value kept after power failure, H/W reset    |

|          | assertion and any CMD0 reset and readable.                          |

| R/W/C_P: | Writable after value cleared by power failure and HW/rest assertion |

|          | (the value not cleared by CMD0 reset) and readable.                 |

| R/W/E_P: | Multiple writable with value reset after power failure, H/W reset   |

|          | assertion and any CMD0 reset and readable.                          |

| W/E_P:   | Multiple writable with value reset after power failure, H/W reset   |

|          | assertion and any CMD0 reset and not readable.                      |

| assertion and a                       | any CMDU reset and not     | readable | 2.           |              |       |  |  |

|---------------------------------------|----------------------------|----------|--------------|--------------|-------|--|--|

|                                       |                            |          |              |              |       |  |  |

| Table 10- 4 Extended CSD Table        |                            |          |              |              |       |  |  |

| Name                                  | Field                      | Size     | Cell<br>Type | CSD<br>Slice | Value |  |  |

| Reserved                              | -                          | 6        | TBD          | [511:506]    | 0h    |  |  |

| Extend Security Command Error         | EXT_SECURITAY              | 1        | R            | [505]        | 0h    |  |  |

| Supported Command Sets                | S_CMD_SET                  | 1        | R            | [504]        | 1h    |  |  |

| HPI features                          | HPI_FEATURES               | 1        | R            | [503]        | 1h    |  |  |

| Background operations support         | BKOPS_SUPPORT              | 1        | R            | [502]        | 1h    |  |  |

| Max packed read commands              | MAX_PACKED_READS           | 1        | R            | [501]        | Ah    |  |  |

| Max packed write commands             | MAX_PACKED_WRITES          | 1        | R            | [500]        | Ah    |  |  |

| Data Tag Support                      | DATA_TAG_SUPPORT           | 1        | R            | [499]        | 1h    |  |  |

| Tag Unit Size                         | TAG_UNIT_SIZE              | 1        | R            | [498]        | 5h    |  |  |

| Tag Resources Size                    | TAG_RES_SIZE               | 1        | R            | [497]        | 1h    |  |  |

| Context management capabilities       | CONTEXT_CAPABILITI<br>ES   | 1        | R            | [496]        | 5h    |  |  |

| Large Unit size                       | LARGE_UNIT_SIZE_M1         | 1        | R            | [495]        | 7h    |  |  |

| Extended partitions attribute support | EXT_SUPPORT                | 1        | R            | [494]        | 3h    |  |  |

| Supported modes                       | SUPPORTED_MODES            | 1        | R            | [493]        | 3h    |  |  |

| FFU features                          | FFU_FEATURES               | 1        | R            | [492]        | 1h    |  |  |

| Operation codes timeout               | OPERATION_CODE_TI<br>MEOUT | 1        | R            | [491]        | 40h   |  |  |

### Table 10- 4 Extended CSD Table

| MKEV032GCB-SS510                            | FOUN                                              |      |              |              |         |

|---------------------------------------------|---------------------------------------------------|------|--------------|--------------|---------|

| Name                                        | Field                                             | Size | Cell<br>Type | CSD<br>Slice | Value   |

| FFU Argument                                | FFU_ARG                                           | 4    | R            | [490:487]    | 0h      |

| Barrier support                             | BARRIER_SUPPORT                                   | 1    | R            | [486]        | 0h      |

| Reserved                                    | -                                                 | 177  | TBD          | [485:309]    | ALL"0"  |

| CMD Queuing Support                         | CMDQ_SUPPORT                                      | 1    | R            | [308]        | 1h      |

| CMD Queuing Depth                           | CMDQ_DEPTH                                        | 1    | R            | [307]        | 1Fh     |

| Reserved                                    | -                                                 | 1    | TBD          | [306]        | 0h      |

| Number of FW sectors correctly programmed   | NUMBER_OF_FW_SEC<br>TORS_CORRECTLY_PR<br>OGRAMMED | 4    | R            | [305:302]    | Oh      |