# 700 V Non-Isolated Off-Line Regulator Up to 120 mA Output Current

The Future of Analog IC Technology

#### NOT RECOMMENDED FOR NEW DESIGNS. REFER TO MP172A

#### DESCRIPTION

MP172 is a primary-side regulator that provides accurate constant voltage (CV) regulation without an opto-coupler. It supports buck, boost, buck-boost, and flyback topologies. It has an integrated 700 V MOSFET to simplify the structure and reduce costs. These features make it an ideal regulator for off-line, low-power applications, such as home appliances and standby power.

MP172 is a green-mode-operation regulator. Both the peak current and the switching frequency decrease as the load decreases. This feature provides excellent efficiency at light load and improves the overall average efficiency.

MP172 has various protection features including thermal shutdown (TSD), VCC undervoltage lockout (UVLO), overload protection (OLP), short-circuit protection (SCP), and openloop protection.

MP172 is available in a small TSOT23-5 package and SOIC-8 package.

#### **FEATURES**

- Primary-Side CV Control, Supporting Buck, Boost, Buck-Boost, and Flyback Topologies

- Integrated 700 V MOSFET and Current Source

- < 30 mW No-Load Power Consumption</li>

- Up to 3 W Output Power

- Maximum DCM Output Current Less than 80 mA

- Maximum CCM Output Current Less than 120 mA

- Low VCC Operating Current

- Frequency Foldback

- Limited Maximum Frequency

- Peak-Current Compression

- Internally Biased VCC

- TSD, UVLO, OLP, SCP, Open-Loop Protection

#### APPLICATIONS

- Home Appliances, White Goods, and Consumer Electronics

- Industrial Controls

- Standby Power

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

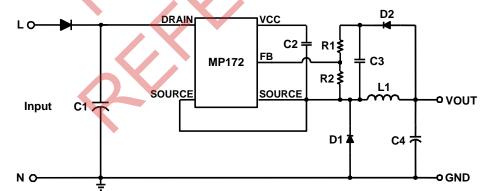

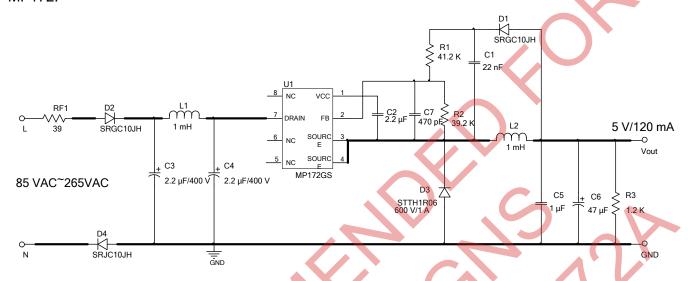

### TYPICAL APPLICATION

© 2021 MPS. All Rights Reserved.

# NOT RECOMMENDED FOR NEW DESIGNS. REFER TO MP172A ORDERING INFORMATION

| Part Number | Package  | Top Marking |

|-------------|----------|-------------|

| MP172GJ*    | TSOT23-5 | See Below   |

| MP172GS**   | SOIC-8   | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP172GJ-Z).

# TOP MARKING (TSOT23-5)

| APKY

APK: product code of MP172GJ; Y: year code;

# **TOP MARKING (SOIC-8)**

MP172 LLLLLLL MPSYWW

MP172: part number; LLLLLLL: lot number; MPS: MPS prefix: Y: year code; WW: week code:

# **PACKAGE REFERENCE**

| TOP VIEW                     | TOP VIEW                                                                                                                    |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| VCC 1 5 DRAIN  FB 2 4 SOURCE | VCC 1         O         8 NC           FB 2         7 DRAIN           SOURCE 3         6 NC           SOURCE 4         5 NC |

| TSOT23-5                     | SOIC-8                                                                                                                      |

<sup>\*\*</sup> For Tape & Reel, add suffix -Z (e.g. MP172GS-Z).

| ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup> DRAIN to SOURCE ( $T_J$ =+25°C)0.3 V to 700 V All other pins0.3 V to 6.5 V Continuous power dissipation ( $T_A$ = +25°C) <sup>(2)</sup> TSOT23-5 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage temperature60°C to +150°C <b>Recommended Operating Conditions</b> (3)  Operating junction temp (T <sub>J</sub> )40°C to +125°C  Operating VCC range                              |

| Thermal Resistance <sup>(4)</sup> | $\theta_{JA}$ | <b>Ө</b> ЈС |   |

|-----------------------------------|---------------|-------------|---|

| TSOT23-5                          | 100           | .55 °C/W    | / |

| SOIC-8                            | 96            | . 45 °C/W   | I |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature TA. The maximum allowance continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowance power dissipation will produce an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuit protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

VCC = 5.5 V, T<sub>J</sub> = -40°C~125°C, min and max are guaranteed by characterization, typical is tested under 25°C, unless otherwise specified.

| Parameter                                                    | Symbol              | Condition                               | Min  | Тур  | Max  | Units |  |

|--------------------------------------------------------------|---------------------|-----------------------------------------|------|------|------|-------|--|

| Start-up Current Source and Internal Mo                      | OSFET (DR           | AIN)                                    |      |      |      |       |  |

| Internal regulator supply current                            | regulator           | VCC = 4 V; V <sub>Drain</sub> = 100 V   | 2.2  | 4.1  | 6    | mA    |  |

| DRAIN leakage current                                        | Leak                | VCC = 5.8 V; V <sub>Drain</sub> = 400 V | X    | 10   | 17   | μA    |  |

| Breakdown voltage                                            | $V_{(BR)DSS}$       | T <sub>J</sub> = 25°C                   | 700  |      |      | V     |  |

| On resistance                                                | Ron                 | T <sub>J</sub> = 25°C                   |      | 16   | 20   | Ω     |  |

| Supply Voltage Management (VCC)                              |                     |                                         |      |      |      |       |  |

| VCC level (increasing) where the internal regulator stops    | VCC <sub>OFF</sub>  |                                         | 5.4  | 5.7  | 6    | V     |  |

| VCC level (decreasing) where the internal regulator turns on | VCCon               |                                         | 5.1  | 5.5  | 5.8  | V     |  |

| VCC regulator on and off hysteresis                          |                     |                                         | 130  | 250  |      | mV    |  |

| VCC level (decreasing) where the IC stops                    | VCC <sub>stop</sub> |                                         | 3    | 3.4  | 3.6  | V     |  |

| VCC level (decreasing) where the protection phase ends       | VCC <sub>pro</sub>  |                                         | 2    | 2.5  | 2.8  | V     |  |

| Internal IC consumption                                      | Icc                 | $f_s = 36 \text{ kHz}, D = 64\%$        |      |      | 720  | μΑ    |  |

| Internal IC consumption (no switching)                       | Icc                 |                                         |      |      | 200  | μΑ    |  |

| Internal IC consumption, latch-off phase                     | ICCLATCH            | VCC = 5.3 V                             |      | 16   | 24   | μA    |  |

| Internal Current Sense                                       |                     |                                         | 7    |      |      |       |  |

| Peak current limit                                           | I <sub>Limit</sub>  | T <sub>J</sub> = 25°C                   | 188  | 210  | 232  | mA    |  |

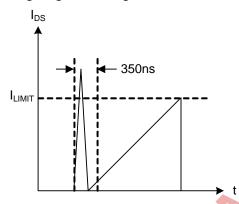

| Leading-edge blanking                                        | <b>₹</b> LEB1       | <b>/</b> ( )                            |      | 350  |      | ns    |  |

| SCP threshold                                                | ISCP                | T <sub>J</sub> = 25°C                   | 330  | 400  | 510  | mA    |  |

| Leading-edge blanking for SCP (1)                            | $	au_{LEB2}$        |                                         |      | 180  |      | ns    |  |

| Feedback Input (FB)                                          |                     |                                         |      |      |      |       |  |

| Minimum off time                                             | $	au_{minoff}$      |                                         | 7.5  | 10   | 12.5 | μs    |  |

| Maximum on time                                              | $	au_{manon}$       |                                         | 13   | 18   | 23   | μs    |  |

| Primary MOSFET feedback turn-on threshold                    | V <sub>FB</sub>     |                                         | 2.45 | 2.55 | 2.65 | V     |  |

| OLP feedback trigger threshold                               | V <sub>FB_OLP</sub> |                                         | 1.64 | 1.74 | 1.84 | V     |  |

| OLP delay time                                               | τolp                | f <sub>s</sub> = 36 kHz                 |      | 175  |      | ms    |  |

| Open-loop detection                                          | Vold                |                                         | 0.4  | 0.5  | 0.6  | V     |  |

| Thermal Shutdown                                             |                     |                                         |      |      |      |       |  |

| Thermal shutdown threshold (1)                               |                     |                                         |      | 150  |      | °C    |  |

| Thermal shutdown recovery hysteresis (1)                     |                     |                                         |      | 30   |      | °C    |  |

#### NOTE:

<sup>1)</sup> This parameter is guaranteed by design.

#### TYPICAL CHARACTERISTICS

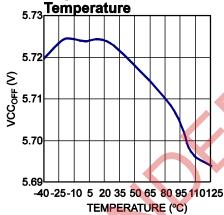

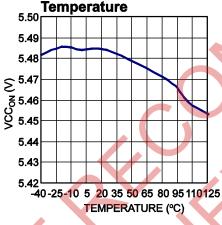

VCC Increasing Level at which the Internal Regulator Stops vs.

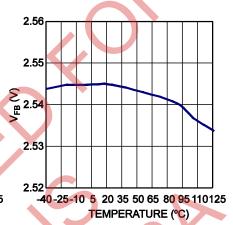

Feedback Voltage vs. Temperature

VCC Decreasing Level at which the Internal Regulator Turns On vs.

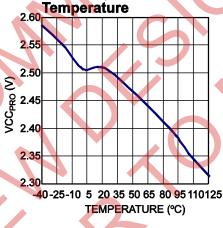

VCC Decreasing Level at which the Protection Phase Ends vs.

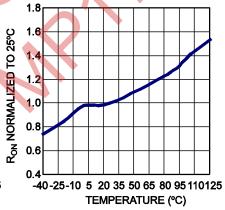

On State Resistance vs. Temperature

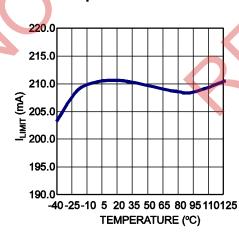

Peak Current Limit vs. Temperature

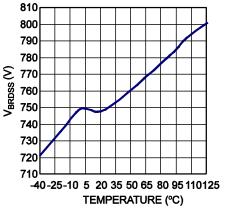

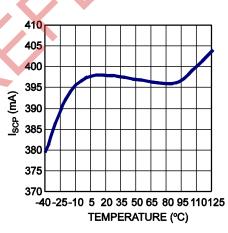

SCP Point vs. Temperature

Minimum Off Time vs. Temperature

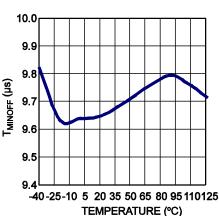

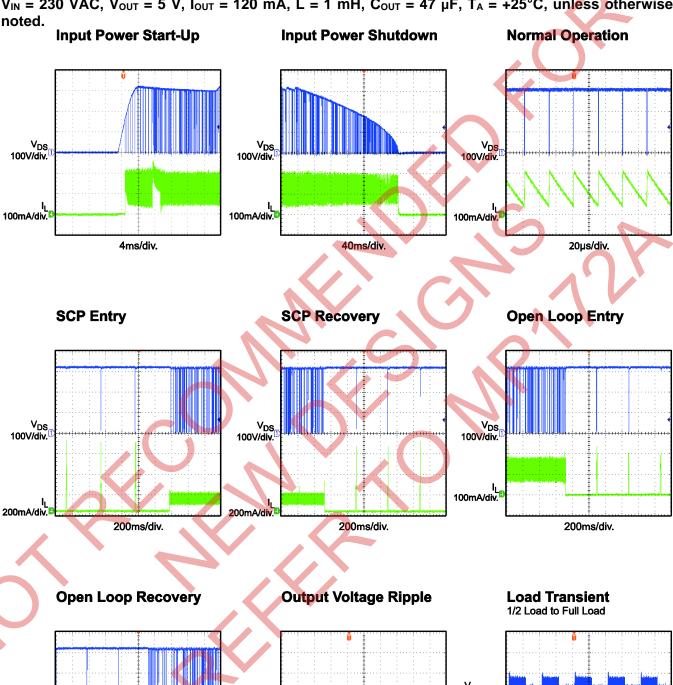

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 230 \text{ VAC}$ ,  $V_{OUT} = 5 \text{ V}$ ,  $I_{OUT} = 120 \text{ mA}$ , L = 1 mH,  $C_{OUT} = 47 \mu\text{F}$ ,  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.

6

# **PIN FUNCTIONS**

| Pin #<br>TSOT23-5 | Pin #<br>SOIC8 | Name   | Description                                                        |

|-------------------|----------------|--------|--------------------------------------------------------------------|

| 1                 | 1              | VCC    | Control circuit power supply.                                      |

| 2                 | 2              | FB     | Regulator feedback.                                                |

| 3,4               | 3,4            | SOURCE | Internal power MOSFET source and ground reference for VCC and FB.  |

| 5                 | 7              | DRAIN  | Internal power MOSFET drain and high-voltage current source input. |

|                   | 5,6,8          | NC     | No connection.                                                     |

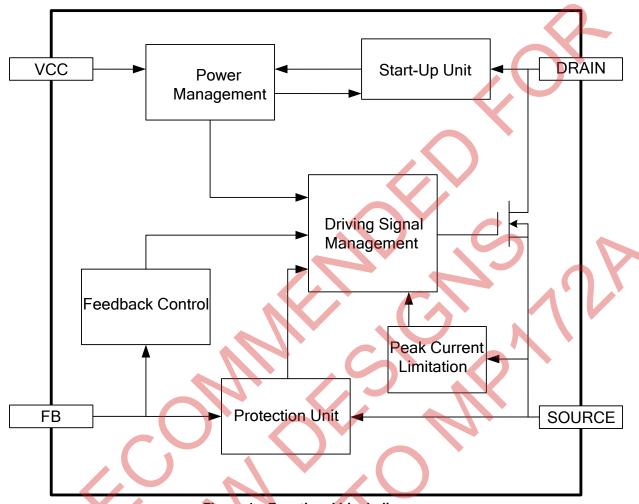

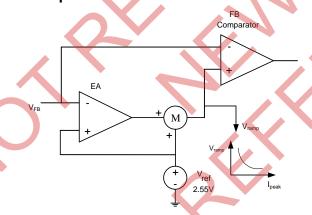

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1—Functional block diagram

#### **OPERATION**

MP172 is a green-mode-operation regulator: The peak current and the switching frequency both decrease with a decreasing load. As a result, it offers excellent light-load efficiency and improves overall average efficiency. Also, the regulator incorporates multiple features and operates with a minimum number of external components.

The MP172 acts as a fully integrated regulator when used in buck topology (see Typical Application on page 1).

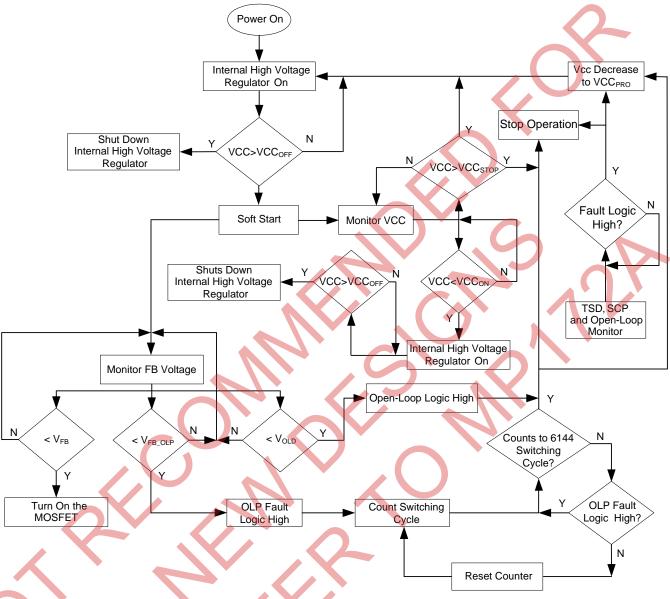

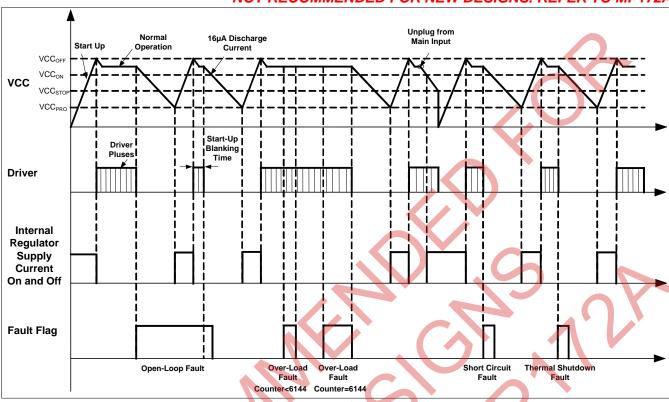

#### Start-Up and Under-Voltage Lockout

The internal high-voltage regulator self-supplies the IC from DRAIN. When VCC voltage reaches VCC<sub>OFF</sub>, the IC starts switching, and the internal high-voltage regulator turns off. The internal high-voltage regulator turns on to charge the external VCC capacitor when the VCC voltage falls below VCC<sub>ON</sub>. A small capacitor (in the low  $\mu F$  range) maintains the VCC voltage and thus lowers the capacitor cost.

The IC stops switching when the VCC voltage drops blow VCC<sub>stop</sub>.

Under fault conditions—such as OLP, SCP, and TSD—the IC stops switching and an internal current source discharges the VCC capacitor. The internal high-voltage regulator will not charge the VCC capacitor until the VCC voltage drops below VCC<sub>pro</sub>. The re-start time can be estimated using Equation (1).

$$\tau_{\text{restart}} = C_{\text{VCC}} \times \left( \frac{\text{VCC} - \text{VCC}_{\text{pro}}}{I_{\text{CCLATCH}}} + \frac{\text{VCC}_{\text{OFF}} - \text{VCC}_{\text{PRO}}}{I_{\text{regulator}}} \right)$$

(1)

#### Soft Start (SS)

The IC stops operation when the VCC voltage drops below VCC<sub>stop</sub>; the IC begins operation when VCC charges to VCC<sub>OFF</sub>. Every time the chip starts operation, there is a soft-start period. The soft start prevents the inductor current from overshooting by limiting the minimum off time.

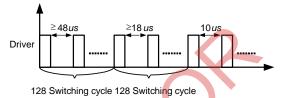

MP172 adopts a 2 phase minimum off time limit soft start. Each soft-start phase retains 128 switching cycles. During the soft start, the off time limit gradually shortens from 48 µs to 18 µs and finally reaches the normal operation off time limit (see Figure 2).

Figure 2— $\tau_{minoff}$  at start-up

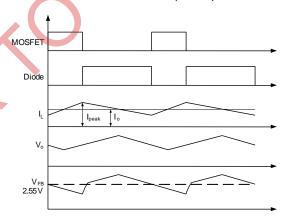

#### Constant Voltage (CV) Operation

The MP172 regulates the output voltage by monitoring the sampling capacitor.

At the beginning of each cycle, the integrated MOSFET turns on while the feedback voltage drops below the 2.55 V reference voltage, which indicates insufficient output voltage. The peak current limitation determines the on period. After the on period elapses, the integrated MOSFET turns off. The sampling capacitor (C3) voltage is charged to the output voltage when the freewheeling diode (D1) turns on. This way, the sampling capacitor (C3) samples and holds the output voltage for output regulation. sampling capacitor (C3) voltage decreases when the L1 inductor current falls below the output current. When the feedback voltage falls below the 2.55 V reference voltage, a new switching cycle begins. Figure 3 shows this operation in continuous conduction mode (CCM).

Figure 3— V<sub>FB</sub> vs. V<sub>O</sub>

Equation (2) determines the output voltage:

$$Vo = 2.55V \times \frac{R1 + R2}{R2}$$

(2)

#### Frequency Foldback and **Peak Current** Compression

The MP172 remains highly efficient at light-load conditions by reducing the switching frequency automatically.

Under light-load or no-load conditions, the output voltage drops very slowly, which increases the **MOSFET** off time. the frequency Thus, decreases along with the load.

The switching frequency is determined with Equation (3) and Equation (4):

$$f_s = \frac{(V_{in} - V_o)}{2L(I_{peak} - I_o)} \cdot \frac{V_o}{V_{in}}, \text{ for CCM}$$

(3)

$$f_s = \frac{2(V_{in} - V_O)}{LI_{peak}^2} \cdot \frac{I_o V_o}{V_{in}}, \text{ for DCM}$$

(4)

As the peak current limit decreases from 210 mA, the off time increases. In standby mode, the frequency and the peak current are both minimized, allowing for a smaller dummy load. As a result, the peak current compression helps reduce no-load consumption. The peak current limit can be estimated from Equation (5) where  $\tau_{\rm off}$  is the off time of the power module:

$$I_{\text{Peak}} = 210\text{mA} - (0.8\text{mA}/\mu\text{s}) \times (\tau_{\text{off}} - 10\mu\text{s})$$

(5)

#### **EA Compensation**

Figure 4—EA and ramp compensation

MP172 has an internal error amplifier (EA) compensation loop. It samples the feedback voltage 6 µs after the MOSFET turns off and regulates the output based on the 2.55 V reference voltage.

#### **Ramp Compensation**

An internal ramp compensation circuit improves the load regulation. As shown in Figure 4, a voltage sinking source is added to pull down the reference voltage of the feedback comparator. The ramp compensation is relative to the MOSFET off time, and increases exponentially as the off time increases. The compensation is about 1mV/µs under min off time switching condition.

#### Over-Load Protection (OLP)

The maximum output power of the MP172 is limited by the maximum switching frequency and the peak current limit. If the load current is too large, the output voltage drops, causing the FB voltage to drop.

When the FB voltage drops below V<sub>FB OLP</sub>, it is considered an error flag, and the timer starts. If the timer reaches 170 ms (fs = 36 kHz), OLP occurs. This timer duration avoids triggering OLP when the power supply starts up or the load transitions. The power supply should start up in less than 170 ms (fs = 36 kHz). The OLP delay time is calculated using Equation (6):

$$\tau_{\text{Delay}} \approx 170 \text{ms} \times \frac{36 \text{kHz}}{f_s}$$

(6)

#### Short-Circuit Protection (SCP)

The MP172 monitors the peak current and shuts down when the peak current rises above the SCP threshold through short-circuit protection. The power supply resumes operation with the removal of the fault.

#### Thermal Shutdown (TSD)

To prevent thermal induced damage, the MP172 stops switching when the junction temperature exceeds 150°C. During thermal shutdown (TSD), the VCC capacitor is discharged to VCC<sub>pro</sub>, and the internal high-voltage regulator re-charges. MP172 recovers when the iunction temperature drops below 120°C.

#### **Open-Loop Detection**

If  $V_{FB}$  is less than 0.5 V, the IC stops switching, and a re-start cycle begins. During a soft start, the open-loop detection is blanked.

#### Leading-Edge Blanking

An internal leading-edge blanking (LEB) unit avoids premature switching pulse termination due to a turn-on spike. A turn-on spike is caused by parasitic capacitance and reverse recovery of the freewheeling diode. During the blanking time, the current comparator is disabled and cannot turn off the external MOSFET. Figure 5 shows the leading-edge blanking.

Figure 5—Leading-edge blanking

© 2021 MPS. All Rights Reserved.

### APPLICATION INFORMATION

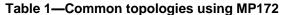

#### **Topology Options**

The MP172 can be used in common topologies such as buck, boost, buck-boost, and flyback (see Table 1).

Component selection below is based on the typical application of MP173 (see it on page 1).

## **Component Selection**

#### **Input Capacitor**

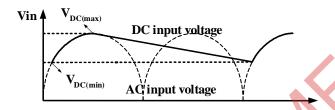

The input capacitor supplies the DC input voltage for the converter. Figure 6 shows the typical DC bus voltage waveform of a half-wave rectifier and a full-wave rectifier.

Figure 6—Input voltage waveform

Typically, the use of a half-wave rectifier requires an input capacitor rated at 3  $\mu$ F/W for the universal input condition. When using a full-wave rectifier, an input capacitor is chosen between 1.5~2  $\mu$ F/W for the universal input condition. A half-wave rectifier is recommended for a < 2 W output application, otherwise use a full-wave rectifier.

Under very low input voltage, the inductor current ramps up slowly; it may not reach the current limit during  $\tau_{manon}$ , so the MOSFET on time should be less than the minimum value of  $\tau_{manon}$ .

#### Inductor

The MP172 has a minimum off-time limit that determines the maximum power output. A power inductor with a larger inductance increases the maximum power. Using a very small inductor may cause failure at full load. Estimate the

maximum power using Equation (7) and Equation (8):

$$P_{\text{omax}} = V_{\text{o}}(I_{\text{peak}} - \frac{V_{\text{o}}\tau_{\text{minoff}}}{2L}), \text{ for CCM}$$

(7)

$$P_{\text{omax}} = \frac{1}{2}LI_{\text{peak}}^2 \cdot \frac{1}{\tau_{\text{minoff}}}, \text{ for DCM}$$

(8)

For mass production, tolerance on the parameters (such as peak current limitation and the minimum off time) should be taken into consideration.

# Freewheeling Diode

Select a diode with a maximum reverse-voltage rating greater than the maximum input voltage and a current rating determined by the output current.

The reverse recovery of the freewheeling diode affects the efficiency and circuit operation during a CCM condition, so use an ultra-fast diode such as the EGC10JH.

## **Output Capacitor**

The output capacitor is required to maintain the DC output voltage. Estimate the output voltage ripple using Equation (9) and Equation (10):

$$V_{\text{CCM\_ripple}} = \frac{\Delta i}{8f_s C_o} + \Delta i \cdot R_{\text{ESR}}, \text{ for CCM}$$

(9)

$$V_{\text{DCM\_ripple}} = \frac{I_o}{f_s C_o} \cdot \left(\frac{I_{pk} - I_o}{I_{pk}}\right)^2 + I_{pk} \cdot R_{ESR}, \text{ for DCM (10)}$$

It is recommended to use ceramic, tantalum, or low ESR electrolytic capacitors to reduce the output voltage ripple.

#### **Feedback Resistors**

The resistor divider determines the output voltage. Choose appropriate R1 and R2 values to maintain  $V_{FB}$  at 2.55 V. An excessively large value for R2 should be avoided.

# **Sampling Capacitor**

The sampling capacitor (C3) samples and holds the output voltage for feedback. With R1 and R2 fixed, a small sampling capacitor result in poor regulation at light loads, and large sampling capacitor affect the circuit operation. Roughly estimate an optimal capacitor value using Equation (11):

$$\frac{1}{2} \frac{V_o}{R_1 + R_2} \cdot \frac{C_o}{I_o} \le C_{FB} \le \frac{V_o}{R_1 + R_2} \cdot \frac{C_o}{I_o}$$

(11)

#### **Dummy Load**

A dummy load is required to maintain the load regulation. This ensures there is sufficient inductor energy to charge the sample and hold capacitor to detect the output voltage. Normally a 3 mA dummy load is needed and can be adjusted according to the regulated voltage. There is a compromise between small, no-load consumption and good, no-load regulation, especially for applications that require 30 mW no-load consumption. Use a Zener to reduce no-load consumption if no-load regulation is not a concern.

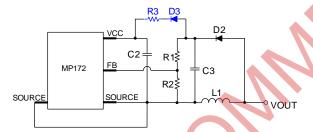

#### **Auxiliary VCC Supply**

Figure 7—Auxiliary Vcc supply circuit

For applications with  $V_0$  above 7 V, the MP172 achieves the 30 mW no-load power requirement. In order to do this, the chip requires an external VCC supply to reduce overall power consumption (see Figure 7).

This auxiliary VCC supply is derived from the resistor connected between C2 and C3. C3 should be set larger than the value recommended above. D3 is used in case VCC interferes with FB. R3 is determined using Equation (12):

$$R3 \approx \frac{V_o - V_{FW} - 5.8V}{I_S} \tag{12}$$

Where  $I_S$  is the VCC consumption under a noload condition, and  $V_{FW}$  is the forward voltage drop of D3. Because  $I_S$  varies in different applications, R3 should be adjusted to meet the application's specific  $I_S$ . In a particular configuration,  $I_S$  is measured at about 200  $\mu$ A.

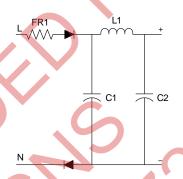

#### **Surge Performance**

An appropriate input capacitor value should be chosen to obtain good surge performance. Figure 8 shows the half-wave rectifier. Table 2 shows the capacitance required under normal conditions for different surge voltages. FR1 is a 20  $\Omega/2$  W fused resistor, and L1 is 1 mH for this recommendation.

Figure 8—Half-wave rectifier

Table 2—Recommended capacitance

| Surge<br>Voltage | 500 V | 1000 V | 2000 V |

|------------------|-------|--------|--------|

| C1               | 1 µF  | 2.2 µF | 3.3 µF |

| C2               | 1 µF  | 2.2 µF | 3.3 µF |

# **PCB Layout Guidelines**

Efficient PCB layout is critical for reliable operation, good EMI, and thermal performance. Please follow the guidelines below to optimize performance.

- Minimize the loop area formed by the input capacitor, IC, freewheeling diode, inductor, and output capacitor.

- Place the power inductor far away from the input filter while keeping the loop area to the inductor at a minimum (see example below).

- Place a capacitor valued at several hundred pF between FB and SOURCE as close to the IC as possible.

- 4) Connect the exposed pads or large copper area with DRAIN to improve thermal performance.

Top layer

Bottom layer

## **Design Example**

Table 3 shows a design example for the following application guideline specifications:

Table 3—Design example

| V <sub>IN</sub> | 85 VAC to 265 VAC |  |  |

|-----------------|-------------------|--|--|

| Vout            | 5 V               |  |  |

| louт            | 120 mA            |  |  |

The detailed application schematic is shown in Figure 9. The typical performance and circuit waveforms have been shown in the "Typical Performance Characteristics" section. For additional device applications, please refer to the related evaluation board datasheets.

# TYPICAL APPLICATION CIRCUITS

Figure 9 shows a typical application example of a 5 V, 120 mA non-isolated power supply using the MP172.

Figure 9—Typical application at 5 V, 120 mA

© 2021 MPS. All Rights Reserved.

# **FLOW CHART**

#### NOT RECOMMENDED FOR NEW DESIGNS. REFER TO MP172A

UVLO, SCP, OLP, OTP and Open-Loop Protections are Auto Restart

Figure 10—Control flow chart

Figure 11—Signal evolution in the presence of a fault

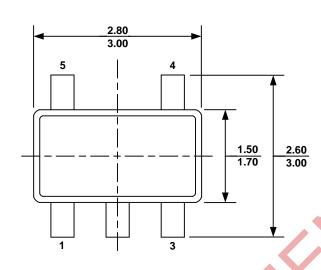

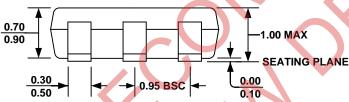

## **PACKAGE INFORMATION**

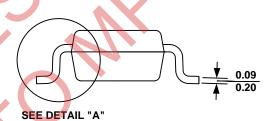

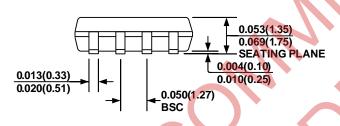

#### **TSOT23-5**

**TOP VIEW**

RECOMMENDED LAND PATTERN

**SIDE VIEW**

# FRONT VIEW

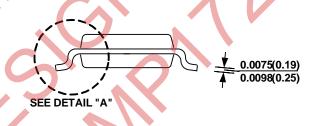

DETAIL "A"

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-193, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

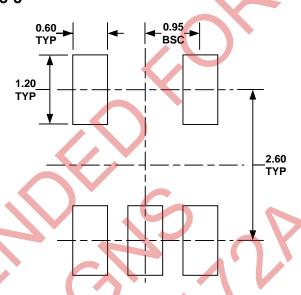

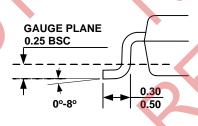

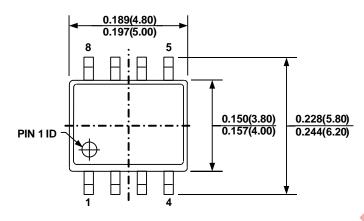

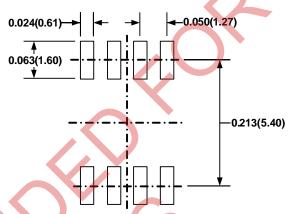

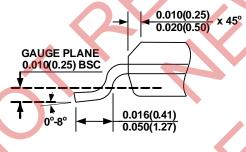

### **PACKAGE INFORMATION**

#### SOIC-8

**TOP VIEW**

RECOMMENDED LAND PATTERN

**FRONT VIEW**

SIDE VIEW

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES DIMENSION IN BRACKET IS IN MILLIMETERS

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH PROTRUSIONS OR GATE BURRS

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS012, VARIATION AA

- 6) DRAWING IS NOT TO SCALE

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for AC/DC Converters category:

Click to view products by Monolithic Power Systems manufacturer:

Other Similar products are found below:

FSFR2100US BP5722A12 ICE3AR0680VJZ ICE3AR2280CJZ ICE3BR0680JZ ICE3BR2280JZ SEA01 BP5055-12 BP5718A12

ICE2QR4780Z NCP1124BP100G AP3983EP7-G1 ICE2QR4765 TEA19363T/1J AP3125CMKTR-G1 ICE3AR10080CJZ SC1076P065G

47132 47220 47225 APR3415BMTR-G1 NCP1126BP100G HF500GP-40 TNY179PN ICE3AR10080JZXKLA1 BM2P0361-Z

BM2P249Q-Z BM521Q25F-GE2 INN3164C-H107-TL HR1001CGS-P HR1001LGS-P BM2P131X-Z BM2P161X-Z BM2P181X-Z

BM2P201X-Z BM2P241X-Z LNK576DG-TL INN3278C-H215-TL INN3278C-H217-TL INN3678C-H605-TL TNY263PN TNY286PG

TNY287PG TNY288DG-TL TNY288PG MP100GN HR1000AGS ICE2QR2280Z1XKLA1 ICE2QS02GXUMA1 ICE3A1065ELJFKLA1