# DESCRIPTION

The MP2617A / MP2617B is a monolithic switch mode battery charger with power path management for single-cell Li-ion batteries in a wide range of tablet and other portable devices. It integrates a synchronous BUCK regulator to provide regulated voltage for powering the system output and at the same time charging the battery. This device supports both USB and high power DC adapter input. In USB mode, the input current limit can be programmed to 450mA or 825mA via the logic pins to cover the USB2.0 and USB3.0 specifications. When the adapter input is present, the input current can also be limited in order to avoid overloading of the DC adapter. Input current limit can be programmed up to 3A.

The smart power path management allows MP2617A and MP2617B to regulate the system voltage for powering an external load and battery independently charging the and simultaneously. This allows immediate system operation even under missing or deeply discharged battery. When the input current limit is reached, the system load is satisfied in priority, then the charger will take the remaining current to charge the battery. Additionally, the smart power path control allows an internal connection from battery to the system in order to supplement additional power to the load in the event the system power demand increases over the input limited power or the input is removed.

The MP2617A / MP2617B features high integration with all the power switches integrate inside. No external MOSFET, blocking diodes, or current sense resistor is required.

Two status monitor output pins are provided to indicate the battery charge status and power source status. Other features include trickle charge, battery temperature monitoring, timer and thermal limiting regulation on chip.

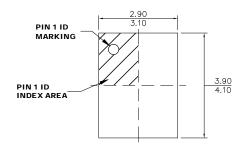

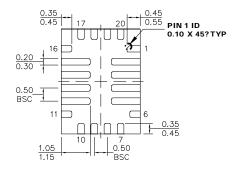

The MP2617A / MP2617B is available in QFN 3mmx4mm package.

# MP2617A, MP2617B 3A Switching Charger with NVDC Power Path Management For Single Cell Li+ Battery

# FEATURES

- 4V to 10V Operating Input Voltage

- Smart Power Path Management

- Five Control Loops: Input Current Limit, Input Voltage Limit, Constant Charge Current, Terminal Battery Control and Thermal Fold-Back.

- 1.6MHz Switching Frequency

- Programmable Input Current Limit

- Programmable Charge Current

- Single Input for USB and AC adapter

- Cover USB2.0 and USB3.0 Input Specification

- Fully Integrated Power Switches

- No External Blocking Diode and Sense Resistor Required

- Charging Operation Indicator

- Built-in Programmable Charging Timer

- Thermal Limiting Regulation on Chip

- Battery Temperature Monitor

- Tiny Package Features Small Size.

# **APPLICATIONS**

- Smart Phone

- E-Book

- GPS

- Portable Media Player

- Portable Hand-held Solution

- Tablet PC

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

mes

MP2617A, MP2617B - SINGLE CELL SWITCHING CHARGER WITH POWER PATH

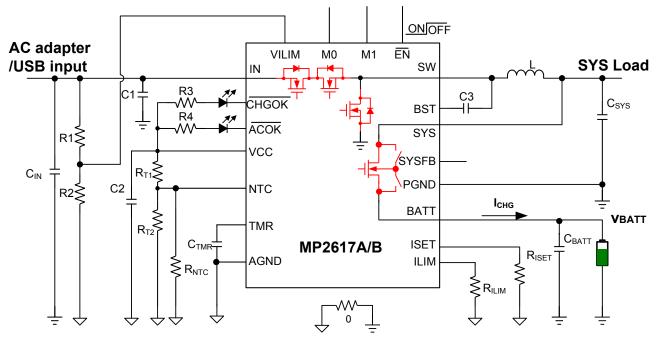

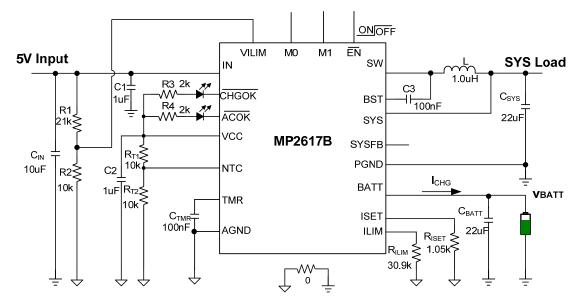

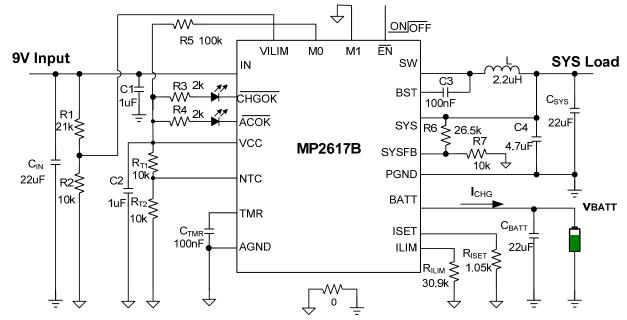

# TYPICAL APPLICATION

MP2617A

MP2617B

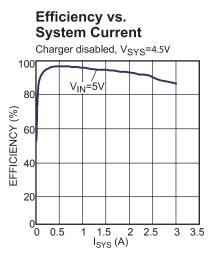

# Efficiency vs. System Current

MP2617 Family Table

| Features                    | MP2617A | MP2617B |

|-----------------------------|---------|---------|

| Battery Charge Full Voltage | 4.35V   | 4.2V    |

| Part Number | Package          | Top Marking |

|-------------|------------------|-------------|

| MP2617AGL*  | QFN-20 (3mmx4mm) | MP2617A     |

| MP2617BGL   | QFN-20 (3mmx4mm) | MP2617B     |

# **ORDERING INFORMATION**

\* For Tape & Reel, add suffix -Z (e.g. MP2617AGL-Z);

### **TOP VIEW** IUM TMR VUM VCC 89 69 68 63 BST 1 C16 NTC ISET SW BATT IN 14 13 SW SYS PGND 12 SYSFB (11 AGND ΕN 6 7 8 9 ž Ξ **CHGOK** ACOK

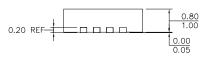

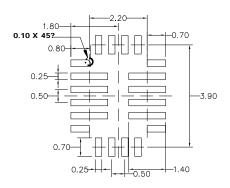

# PACKAGE REFERENCE

# **PIN FUNCTIONS**

| Package<br>Pin # | Name  | Description                                                                                                                                                                                              |

|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | BST   | Bootstrap. A capacitor is connected between SW and BST pin to form a floating supply across the power switch driver to drive the power switch's gate above the supply voltage.                           |

| 3                | IN    | Power input of the IC from adapter or USB.                                                                                                                                                               |

| 2,4              | SW    | Switch output.                                                                                                                                                                                           |

| 5                | PGND  | Power ground.                                                                                                                                                                                            |

| 6                | ĒN    | Function logic control pin of the IC. Logic low to enable the part and logic high to disable the part.                                                                                                   |

| 7                | MO    | Mode Select Input Pin, in combination with M1 pin, setting the input current limit mode.                                                                                                                 |

| 8                | M1    | Mode Select Input Pin, in combination with M0 pin, setting the input current limit mode.                                                                                                                 |

| 9                | CHGOK | Open drain output. It is pulled low during charging. And it is pulled high through an external resistor to VCC to indicate charge completed.                                                             |

| 10               | ACOK  | Open drain output. It is pulled low to indicate the presence of a valid input power supply. Otherwise, it is pulled high through an external resistor to VCC to indicate invalid input or removed input. |

| 11               | AGND  | Analog ground.                                                                                                                                                                                           |

| 12               | SYSFB | SYS voltage program pin. Connect a resistor divider from the pin to SYS and AGND to program the system output voltage. Leave the pin float to disable the function.                                      |

| 13               | SYS   | DC-DC regulator output to power the system load and charge the battery.                                                                                                                                  |

| 14               | BATT  | Positive battery terminal.                                                                                                                                                                               |

| 15               | ISET  | Charge current program pin. A resistor from the pin to AGND can program the charge current during CC charge. Float the pin will disable the charge function.                                             |

| 16               | NTC   | Thermistor input. Connect a resistor from this pin to VCC and the thermistor from this pin to ground. The thermistor is usually inside the battery pack.                                                 |

| 17               | ILIM  | Input current limit program pin. A resistor from the pin to AGND can program the input current limit with adapter input.                                                                                 |

| 18               | TMR   | Set timer out period. Connect TMR pin to AGND to disable the internal timer.                                                                                                                             |

| 19               | VLIM  | Input voltage clamp program pin.                                                                                                                                                                         |

| 20               | VCC   | Supply voltage of the IC.                                                                                                                                                                                |

# ABSOLUTE MAXIMUM RATINGS (1)

| IN, SW                          | 0.3V to +20V                         |

|---------------------------------|--------------------------------------|

| BATT, SYS                       | 0.3V to +6V                          |

| BST                             | 0.3V to +26V                         |

| All Other Pins                  | 0.3V to +6V                          |

| Continuous Power Dissipation (T | <sub>A</sub> = +25°C) <sup>(2)</sup> |

| QFN20 3mmx4mm                   | 2.6W                                 |

| Junction Temperature            | 150°C                                |

| Lead Temperature                | 260°C                                |

| Storage Temperature             | –65°C to 150°C                       |

## Recommended Operating Conditions <sup>(3)</sup>

Supply Voltage V<sub>IN</sub>..... 4.0V to 10V Operating Junction Temp. (T<sub>J</sub>) ....-40°C to +125°C Thermal Resistance (4)  $\theta_{JA}$  $\theta_{JC}$

QFN-20 (3mmx4mm)......48......11...°C/W

Notes: 1)

Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the 2) maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{\text{JA}},$  and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = (T<sub>J</sub>  $(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its 3) operating conditions.4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 5.0V,  $T_A$  = 25°C, unless otherwise noted.

| Parameters                               | Symbol                            | Condition                                                 | Min   | Тур                         | Мах   | Units |

|------------------------------------------|-----------------------------------|-----------------------------------------------------------|-------|-----------------------------|-------|-------|

| Input Power (IN)                         |                                   | · · · · · · · · · · · · · · · · · · ·                     |       |                             |       |       |

| IN Operating Range                       | VIN                               |                                                           | 4.0   |                             | 10    | V     |

| IN Under Voltage Lockout                 |                                   | Rising                                                    | 3.65  | 3.8                         | 3.95  | V     |

| Threshold                                |                                   | Falling                                                   | 3.35  | 3.5                         | 3.65  | V     |

|                                          |                                   | Rising                                                    | 240   | 280                         | 320   | mV    |

| IN vs. BATT Threshold                    |                                   | Falling                                                   | 40    | 70                          | 120   | mV    |

| BST Voltage Threshold                    | V <sub>BST</sub> -V <sub>SW</sub> | Rising                                                    | 2.55  | 2.9                         | 3.25  | V     |

| Bor voltage micshold                     | V B31-V 3W                        | Hysteresis                                                |       | 150                         |       | mV    |

| Switching Frequency                      |                                   |                                                           | 1.4   | 1.6                         | 1.8   | MHz   |

|                                          |                                   | USB2.0 Mode                                               | 400   | 450                         | 500   | mA    |

|                                          |                                   | USB3.0 Mode                                               | 750   | 825                         | 900   | mA    |

|                                          |                                   | Default Mode                                              | 1840  | 2000                        | 2160  | mA    |

| Input Current Limit                      | lin                               | Programmable Mode, R <sub>ILIM</sub> =23k<br>(MP2617B)    | 1840  | 2000                        | 2160  | mA    |

|                                          |                                   | Programmable Mode, RILIM=22.47k<br>(MP2617A)              | 1840  | 2000                        | 2160  | mA    |

|                                          |                                   | Programmable Mode,<br>RILIM=48k (MP2617A)                 | 900   | 950                         | 1000  | mA    |

| Input Current Limit Reference<br>Voltage | VILIM                             |                                                           | 1.1   | 1.14                        | 1.18  | V     |

| High-side NMOS On Resistance             | RH_DS(ON)                         | Include the BLOCK FET                                     |       | 120                         | 130   | mΩ    |

| Low-side NMOS On Resistance              | $R_{L\_DS(ON)}$                   |                                                           |       | 80                          | 100   | mΩ    |

| High-side NMOS Peak Current<br>limit     |                                   |                                                           | 3.8   | 4.8                         | 5.8   | А     |

| Input Voltage Clamp Threshold            | V <sub>VLIM</sub>                 | Voltage on VLIM                                           | 1.49  | 1.52                        | 1.55  | V     |

|                                          |                                   | Charger Enabled, USB2.0 Mode                              |       | 2.4                         | 5     | mA    |

|                                          |                                   | Charger Enabled, USB3.0 Mode                              |       | 2.8                         | 5     | mA    |

| Input Quiescent Current                  | I <sub>IN</sub>                   | Charger Enable, Programmable Mode                         |       | 3.8                         | 5     | mA    |

|                                          |                                   | Charger Enabled, Default Mode                             |       | 3.8                         | 5     | mA    |

|                                          |                                   | Disabled, EN=0V                                           |       | 3                           | 5     | uA    |

| SYS to IN reverse current blocking       |                                   | SYS=SW=4.5V,VIN=0V, monitor VIN<br>leakage                |       | 0.01                        | 0.2   | uA    |

| SYS Output (MP2617A)                     |                                   | ·                                                         |       | · ·                         |       | ·     |

| Minimum SYS Regulation<br>Voltage        | Vsys                              | SYS voltage @ V <sub>BATT</sub> ≤3.4V, SYSFB<br>float     | 3.45  | 3.6                         | 3.75  | V     |

| SYS Regulation Voltage                   | Vsys                              | 3.4V <v<sub>BATT≤4.2V, SYSFB float<br/>BATT Float</v<sub> | 3.5   | V <sub>BATT</sub> +<br>0.2V | 4.63  | V     |

|                                          | - 510                             | User Programmed by SYSFB                                  | 4.22  |                             | 4.63  | V     |

| SYS Reference Voltage                    | $V_{\text{SYS}_{\text{REF}}}$     |                                                           | 1.135 | 1.152                       | 1.170 | V     |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5.0V,  $T_A$  = 25°C, unless otherwise noted.

| Parameters                                 | Symbol           | Condition                                                                              | Min   | Тур                                             | Мах       | Units |

|--------------------------------------------|------------------|----------------------------------------------------------------------------------------|-------|-------------------------------------------------|-----------|-------|

| SYS Output (MP2617B)                       |                  |                                                                                        |       |                                                 |           |       |

| Minimum SYS Regulation Voltage             | Vsys             | SYS voltage @ V <sub>BATT</sub> ≤3.4V,<br>SYSFB float                                  | 3.45  | 3.6                                             | 3.75      | V     |

| SYS Regulation Voltage                     | V <sub>SYS</sub> | 3.4V <v<sub>BATT≤4.2V, SYSFB float<br/>BATT Float</v<sub>                              | 3.5   | V <sub>BATT</sub> +<br>0.2V                     | 4.5       | V     |

| 5 5                                        |                  | User Programmed by SYSFB                                                               | 4.08  |                                                 | 4.4       | V     |

| SYS Reference Voltage V <sub>SYS_REF</sub> |                  |                                                                                        | 1.135 | 1.152                                           | 1.170     | V     |

| Battery Discharge                          |                  |                                                                                        |       |                                                 |           |       |

| BATT to SYS Resistance                     |                  | VIN=0V, ISYS=200mA, VBATT=4.2V                                                         |       | 40                                              | 50        | mΩ    |

|                                            |                  | V <sub>SYS</sub> >V <sub>BATT</sub> -800mV, V <sub>BATT</sub> =4.2V                    | 4     | 5                                               | 6         | Α     |

| BATT to SYS Current Limit                  |                  | SYS short                                                                              |       | 230                                             |           | mA    |

| Battery Charger Voltage Spec (M            | /IP2617A)        |                                                                                        |       |                                                 |           |       |

|                                            |                  | V <sub>BATT</sub> >V <sub>RECH</sub> , I <sub>CHG</sub> ≤I <sub>BF</sub> , SYSFB float | 4.328 | 4.35                                            | 4.372     | V     |

| Terminal Battery Voltage                   | VBATT            | V <sub>SYS</sub> <4.2V Programmed by SYSFB Pin                                         |       | V <sub>SYS</sub> -<br>0.04 x<br>I <sub>BF</sub> |           | V     |

|                                            |                  | SYSFB Float                                                                            | 4.04  | 4.14                                            | 4.24      | V     |

| Recharge Threshold at $V_{BATT}$           | VRECH            | SYSFB programmed                                                                       | 3.99  | 4.09                                            | 4.19      | V     |

| Recharge Hysteresis                        |                  |                                                                                        | 0.00  | 85                                              |           | mV    |

| Trickle Charge Threshold                   |                  |                                                                                        | 3.01  | 3.11                                            | 3.21      | V     |

| Trickle Charger Hysteresis                 |                  |                                                                                        |       | 200                                             | -         | mV    |

| Battery Charger Voltage Spec (N            | /IP2617B)        |                                                                                        |       |                                                 |           | 1     |

|                                            | ,                | VBATT>VRECH, ICHG≤IBF, SYSFB float                                                     | 4.179 | 4.2                                             | 4.221     | V     |

| Terminal Battery Voltage                   | VBATT            | V <sub>SYS</sub> <4.2V Programmed by<br>SYSFB Pin                                      |       | V <sub>SYS</sub> -<br>0.04 x<br>I <sub>BF</sub> |           | V     |

|                                            |                  | SYSFB Float                                                                            | 3.9   | 4.0                                             | 4.1       | V     |

| Recharge Threshold at VBATT                | VRECH            | SYSFB programmed                                                                       | 3.85  | 3.95                                            | 4.05      | V     |

| Recharge Hysteresis                        |                  |                                                                                        |       | 85                                              |           | mV    |

| Trickle Charge Threshold                   |                  |                                                                                        | 2.9   | 3                                               | 3.1       | V     |

| Trickle Charger Hysteresis                 |                  |                                                                                        |       | 200                                             |           | mV    |

| Battery Charger Current Spec               |                  |                                                                                        |       |                                                 |           |       |

| Trickle Charge Current                     | ITRICKLE         |                                                                                        |       | 10%                                             |           | Icc   |

| Termination Charger Current                | I <sub>BF</sub>  |                                                                                        | 5%    | 10%                                             | 15%       | Icc   |

| IBF Maximum Limit                          |                  |                                                                                        |       | 150                                             | 200       | mA    |

| Constant Current Mode Charge               |                  | R <sub>ISET</sub> =760                                                                 | 2.475 | 2.75                                            | 3.02<br>5 | А     |

| Current                                    | Icc              | R <sub>ISET</sub> =1.53k                                                               | 1.26  | 1.4                                             | 1.54      | Α     |

|                                            |                  | R <sub>ISET</sub> =4.6k                                                                | 0.405 | 0.450                                           | 0.495     | Α     |

# ELECTRICAL CHARACTERISTICS (continued)

# $V_{IN}$ = 5.0V, $T_A$ = 25°C, unless otherwise noted.

| Parameters                            | Symbol           | Condition                                                    | Min  | Тур                         | Max  | Units |

|---------------------------------------|------------------|--------------------------------------------------------------|------|-----------------------------|------|-------|

| ISET Reference Voltage                |                  |                                                              | 1.1  | 1.15                        | 1.2  | V     |

| Detter (1)/1 O                        |                  | Rising                                                       | 2.4  | 2.6                         | 2.8  | V     |

| Battery UVLO                          |                  | Falling                                                      | 2.2  | 2.4                         | 2.6  | V     |

| Idea Diode Regulation Voltage         | V <sub>SYS</sub> | Supplement Mode                                              |      | V <sub>BATT</sub> -<br>65mV |      | mV    |

| BATT Leakage Current                  | Ibatt            | V <sub>BATT</sub> =4.2V, SYS float,<br>V <sub>IN</sub> =PGND |      | 20                          | 30   | μA    |

| ACOK, CHGOK                           |                  |                                                              |      |                             |      |       |

| ACOK, CHGOK Pin Output<br>Low Voltage |                  | Sinking 5mA                                                  |      | 270                         | 350  | mV    |

| ACOK, CHGOKPin Leakage<br>Current     |                  | Connected to 3.3V                                            |      | 0.1                         | 0.5  | μA    |

| Timer                                 | •                |                                                              | •    |                             |      |       |

| Trickle Charge Time                   |                  | Стмк=0.1µF, Існд=1А                                          |      | 45                          |      | Min   |

| Total Charge Time                     |                  | Стмк=0.1µF, Існд=1А                                          |      | 6.5                         |      | Hour  |

| Negative Temperature Coeffic          | ient (NTC)       | Control                                                      |      |                             |      |       |

| NTC Low Temp Rising<br>Threshold      | VTHL             | R <sub>NTC</sub> =NCP18XH103F 0°C                            | 63   | 65                          | 67   | %Vcc  |

| Hysteresis on Low Temp<br>Threshold   |                  |                                                              |      | 35                          |      | mV    |

| NTC High Temp Falling<br>Threshold    | VTHH             | R <sub>NTC</sub> =NCP18XH103F, 50°C                          | 32   | 33.5                        | 35   | %Vcc  |

| Hysteresis on High Temp<br>Threshold  |                  |                                                              |      | 70                          |      | mV    |

| VCC Supply                            |                  |                                                              |      |                             |      |       |

|                                       |                  | Rising                                                       | 3.15 | 3.35                        | 3.55 | V     |

| VCC UVLO                              |                  | Falling                                                      | 2.8  | 3                           | 3.2  | V     |

| VCC Output Voltage                    |                  | 0mA <i<sub>VCC&lt;25mA, V<sub>IN</sub>=6V</i<sub>            | 4.3  | 4.5                         | 4.6  | V     |

| VCC Output Current Limit              |                  |                                                              |      | 40                          |      | mA    |

| Logic                                 |                  |                                                              |      |                             |      |       |

| EN Input Low Voltage                  |                  |                                                              |      |                             | 0.4  | V     |

| EN Input High Voltage                 |                  |                                                              | 1.5  |                             |      | V     |

|                                       |                  | EN =4V                                                       |      | 4                           | 8    |       |

| EN Input Current                      |                  | EN =0V                                                       | -0.5 | -0.1                        |      | μA    |

|                                       |                  | Logic High                                                   | 1.5  |                             |      | V     |

| M0, M1                                |                  | Logic Low                                                    |      |                             | 0.4  | V     |

# ELECTRICAL CHARACTERISTICS (continued)

## VIN = 5.0V, TA = 25°C, unless otherwise noted.

| Parameters                | Symbol | Condition | Min | Тур | Мах | Units |

|---------------------------|--------|-----------|-----|-----|-----|-------|

| Protection                |        |           |     |     |     |       |

| Thermal Limit Temperature |        |           |     | 120 |     | °C    |

| Thermal Shutdown          |        |           |     | 150 |     | О°    |

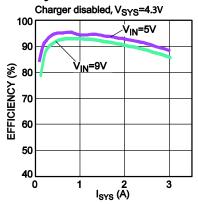

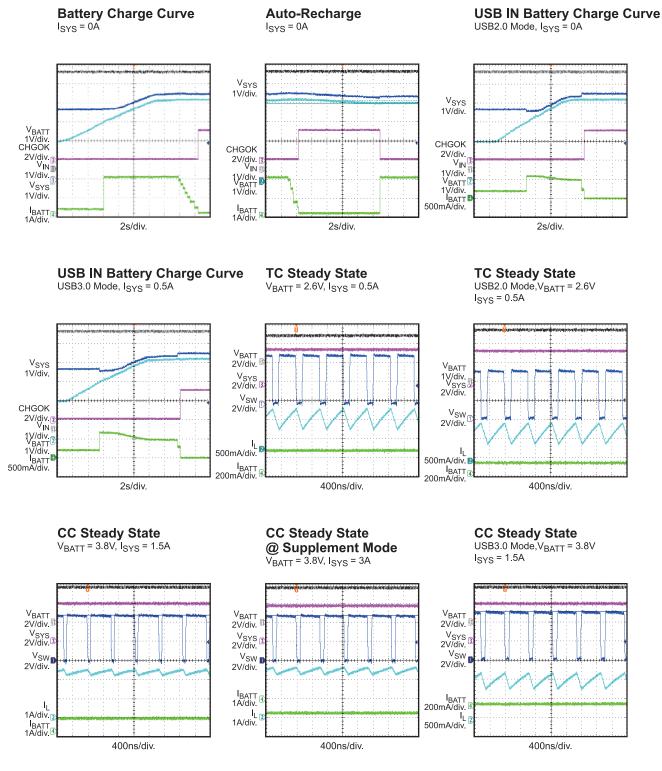

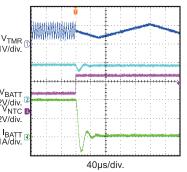

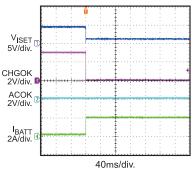

# **TYPICAL PERFORMANCE CHARACTERISTICS**

크노크

$V_{IN}$  = 5.0V,  $V_{BATT}$  = Full Range, Default Mode,  $I_{IN}$  Limit=2A,  $V_{SYS}$ =4.4V, R6 and R7 are float,  $I_{CHG}$ =2A,  $V_{IN}$  Clamp=4.5V, L = 1.2 µH,  $T_A$  = +25°C, Test in MP2617B, unless otherwise noted.

MP2617A, MP2617B Rev. 1.24 www.MonolithicPower.com 4/26/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

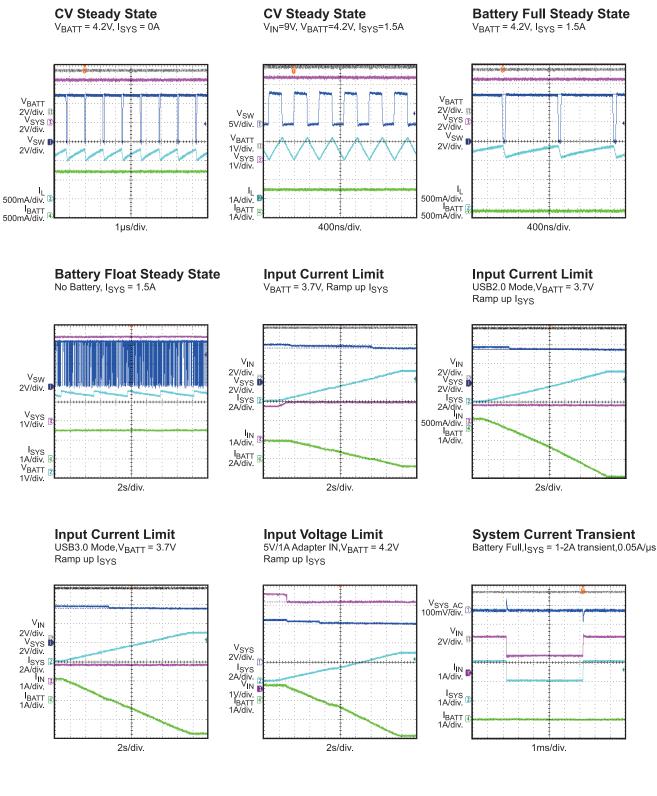

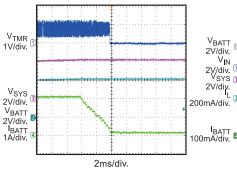

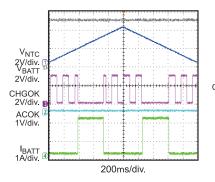

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

근토

$V_{IN}$  = 5.0V,  $V_{BATT}$  = Full Range, Default Mode,  $I_{IN}$  Limit=2A,  $V_{SYS}$ =4.4V, R6 and R7 are float,  $I_{CHG}$ =2A,  $V_{IN}$  Clamp=4.5V, L = 1.2  $\mu$ H,  $T_A$  = +25°C, Test in MP2617B, unless otherwise noted.

MP2617A, MP2617B Rev. 1.24 4/26/2019 MPS Prop www.MonolithicPower.com

26/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

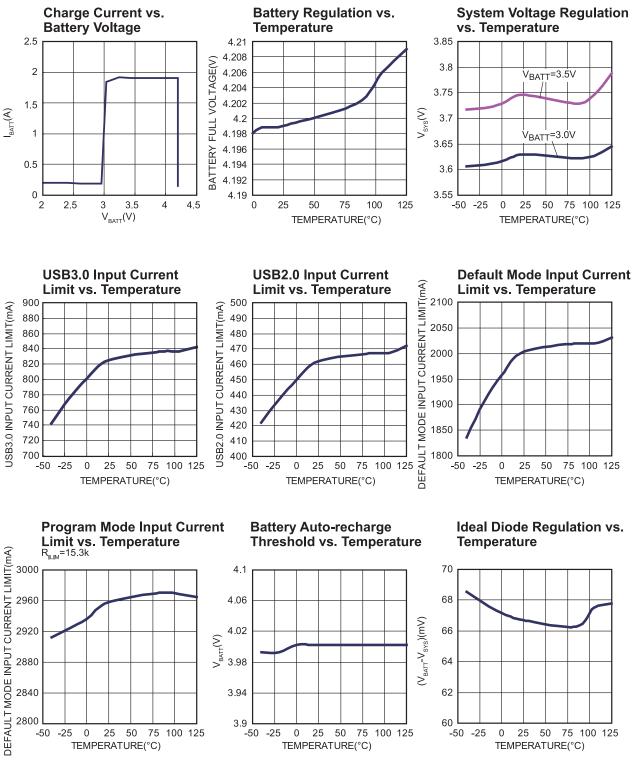

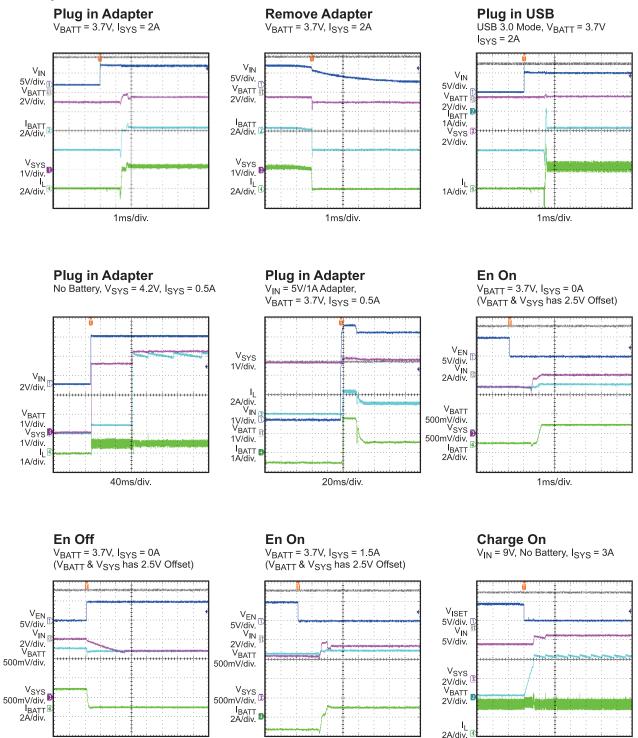

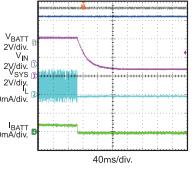

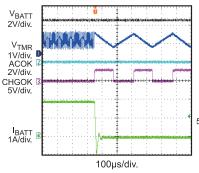

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

ᆜᅳ

$V_{IN}$  = 5.0V,  $V_{BATT}$  = Full Range, Default Mode,  $I_{IN}$  Limit=2A,  $V_{SYS}$ =4.4V, R6 and R7 are float,  $I_{CHG}$ =2A, L = 1.2 µH,  $T_A$  = +25°C, Test in MP2617B, unless otherwise noted.

MP2617A, MP2617B Rev. 1.24 4/26/2019 MPS Prop

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

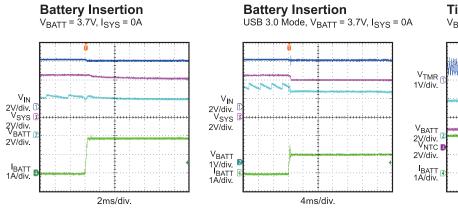

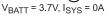

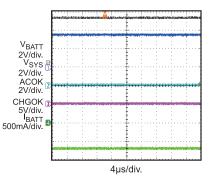

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 5.0V,  $V_{BATT}$  = Full Range, Default Mode,  $I_{IN}$  Limit=2A,  $V_{SYS}$ =4.4V, R6 and R7 are float,  $I_{CHG}$ =2A, L = 1.2 µH,  $T_A$  = +25°C, Test in MP2617B, unless otherwise noted.

4ms/div.

MP2617A, MP2617B Rev. 1.24 4/26/2019 MPS Prop

1ms/div.

Rev. 1.24 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

1ms/div.

© 2019 MPS. All Rights Reserved.

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

VIN = 5.0V, VBATT = Full Range, Default Mode, IIN Limit=2A, VSYS=4.4V, R6 and R7 are float, ICHG=2A, L = 1.2  $\mu$ H, T<sub>A</sub> = +25°C, Test in MP2617B, unless otherwise noted.

### Time Suspend @ NTC Fault V<sub>BATT</sub> = 3.8V, I<sub>SYS</sub> = 0A, C<sub>TMR</sub> = 150pF

Timer Refreshed @ Battery Full Thermal Shutdown V<sub>BATT</sub> = 4.2V, I<sub>SYS</sub> = 0A, C<sub>TMR</sub> = 150pF

ᆜ느

$V_{BATT} = 3.7V, I_{SYS} = 0A$ Increase the Ambier Temperature slowly

Indication @ Charge On/Off

#### Indication @ Timer Out $V_{BATT}$ = 3.7V, $I_{SYS}$ = 0A

Indication @ Supplement  $V_{BATT} = 3.7V, I_{SYS} = 0A$

# **OPERATION**

## Introduction

The MP2617A and MP2617B is a switching charger IC, with integrated smart power path management for powering the system and charging a single cell battery simultaneously and independently.

The MP2617A and MP2617B includes input DC-DC step down converter for wide range of DC sources and USB inputs. It has precision average input current limit to make maximum use of the allowable input power. This feature allows fast charging when powering from an USB port, and ensures the input current never exceeds the input power specification especially when the input power comes from a USB port. Additionally, the input current limit threshold can be programmed by logic inputs or a resistor to ground from the ILIM pin.

The MP2617A and MP2617B implements an onchip 40m $\Omega$  MOSFET which works as a fullfeatured linear charger with trickle charge, high accuracy constant current and constant voltage charge, charge termination, auto recharge, NTC monitor, built-in timer control, charge status indication, and thermal protection. The charge current can be programmed by an external resistor connected from the ISET pin to AGND. The IC limits the charge current when the die temperature exceeds 120°C.

The  $40m\Omega$  MOSFET works as an ideal diode to connecting the battery to the system load when the input power is not enough to power the system load. When the input is removed, the  $40m\Omega$  MOSFET is turned on allowing the battery to power up the system.

With smart power path management, the system load is satisfied in priority then the remaining current is used to charge the battery. The MP2617A and MP2617B will reduce charging current or even use power from the battery to satisfy the system load when its demand is over the input power capacity.

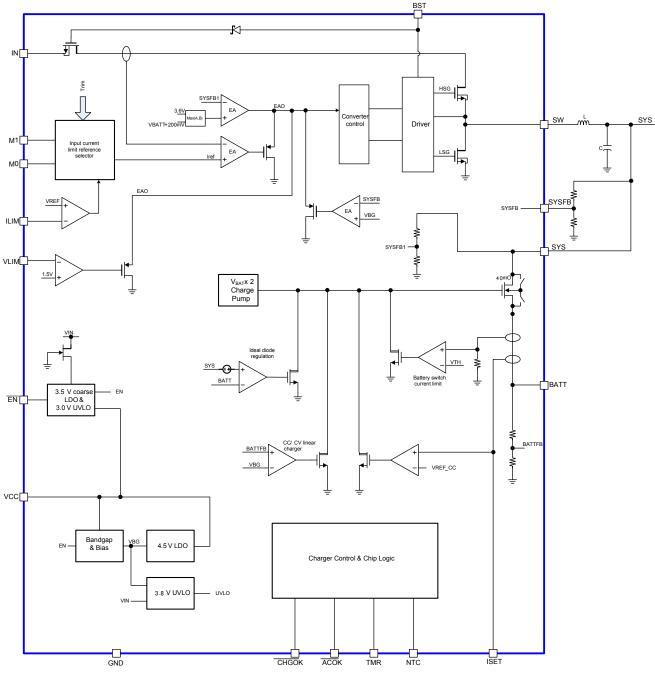

Figure 1 shows the function block diagram of the MP2617A and MP2617B.

### **DC-DC Step Down Converter**

The DC-DC converter is a 1.6MHz step-down switching regulator to provide the input power to the SYS, which drives

the combination of the system load and battery charger. The regulator contains input current measurement and control scheme to ensure the average input current remains below the level programmed via ILIM pin or logic inputs M0&M1. This meets the adapter capacity limit or stays in compliance with USB specification.

When the input voltage is higher than UVLO and 280mV higher than the battery voltage, input voltage OK signal is active ( $\overrightarrow{ACOK}$  turns low) and the DC-DC converter soft-starts. If the input power is sufficient to supply the combination of the system load and battery charger, and the input current limit loop is not triggered. The converter output voltage V<sub>SYS</sub> will be regulated:

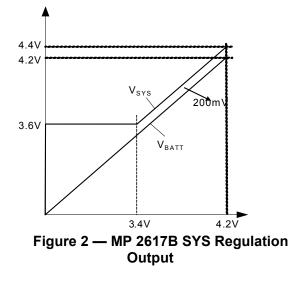

1) If BATT>3.4V,  $V_{SYS}$  is approximately 0.2V above the battery voltage to minimize the power loss of the battery charger during fast charging.

2) If BATT<3.4V,  $V_{SYS}$  is fixed at 3.6V to power the system immediately even when a drained battery is inserted to be charged. Figure 2 shows the relationship of  $V_{SYS}$  vs.  $V_{BATT}$ .

System voltage can also be regulated to any value between 4.08V to 4.4V in MP2617B (4.22V to 4.63V in MP2617A) by using a resistor divider on the SYSFB pin. This is shown as R6 and R7 in Figure 10. If the SYSFB is left floating, the system program is invalid, and  $V_{SYS}$  is regulated as Figure 2.

The converter adopts fixed off-time control to extend the duty cycle (close to 100%) when the input of the converter is close to  $V_{SYS}$ .

www.MonolithicPower.com

Close to 100% duty operation, BST refresh operation makes sure the driver voltage of the HS will be charged by turning on the LS until negative IL hit a threshold. If the input power is insufficient to supply the combination of the system load and battery charger, the DC-DC converter will limit the total power requirement by restricting the input voltage, input current and the peak current through the MOSFET. The power path management will reduce the charge current to satisfy the external system load in priority. According to this feature, the USB specification is always satisfied first. Even if the charge current is set larger than the USB input current limit, the real charge current will be reduced as needed.

## **Input Limit State**

If the input power is insufficient to supply the combination of the system load and battery charger, the MP2617A and MP2617B implements three input limit control loops to reduce the charge current and satisfy the external system load in priority. The input in this case might be limited as follows: input current limit, input voltage limit and DC-DC peak current limit.

Input Current Limit: When the input current is higher than the programmed input current limit the input current limit loop takes the control of the converter and regulates the input current at constant value. When the battery voltage is over 3.4V, the output voltage (V<sub>SYS</sub>) will drop down according to the increase of the system current, and the charge current drops down after the BATT-to-SYS switch (40mΩ MOSFET) is fully on according to V<sub>SYS</sub> dropping down. During this process, the system voltage is slightly higher than V<sub>BATT</sub>. When the battery voltage is lower than 3.4V, to maintain the minimum system voltage and ensure the system operation, the input current limit control will pull down the charge current directly to reduce the load of the converter so that the system current is satisfied in priority.

Input Voltage Limit: A resistor divider from IN pin to VLIM pin to AGND is used for the input voltage limit control. When the voltage on VLIM pin hits the reference voltage of 1.52V, the output of the input voltage limit error amplifier will drop in to control the operation duty. In this mode, the input voltage will be clamped according to the value set by the resistor divider. The control to the system voltage and charge current is the same as the one explained in the input current limit. Charge current drops down to satisfy the system current request first. This feature provides a second protection to the input power and ensures the safe operation of the input adapter. Even if a wrong adapter is inserted, the MP2617A and MP2617B can continue operation, providing the maximum power to its load. User can program the input voltage limit value through the resistor divider from IN to VLIM to AGND.

Peak Current Limit: The peak current of the high side switch of the DC-DC converter is sensed during every cycle, it is compared to the reference 4.8A. If the peak current hits the threshold, the peak current limit mode is triggered. The control of the charge current is the same with the above two limits.

## Input Current Limit Setting

The current at ILIM is a precise fraction of the adapter input current. When a programming resistor is connected from ILIM to AGND, the voltage on ILIM represents the average input current of the PWM converter. And the input current approaches the programmed limit, ILIM voltage reaches 1.14V.

The average input current limit can be set through the resistor connecting from ILIM to AGND according to the following expression:

$$I_{IN\_LIM} = 1.14 \times \frac{40000}{R_{ILIM}(k\Omega)}$$

(mA)

When USB input, the input current limit is set internally and the programmed value is invalid. The MP2617A and MP2617B provides typical of 450mA input current limit for USB2.0 specification and a typical of 825mA for USB3.0 specification respectively.

The user can choose to set the input current limit through the two logic pins M0 and M1 as shown in Table 2 according to its input specification.

MP2617A, MP2617B Rev. 1.24

www.MonolithicPower.com

4/26/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

When both M0 and M1 pins are float, they are pulled to the logic high, under this condition, the input current is limited to a default value of 2A.

| MO         | M1         | Mode              |  |  |  |  |

|------------|------------|-------------------|--|--|--|--|

| Low        | Low        | USB2.0 Mode       |  |  |  |  |

| Low        | High       | USB3.0 Mode       |  |  |  |  |

| High       | Low        | Programmable Mode |  |  |  |  |

| High/Float | High/Float | Default Mode      |  |  |  |  |

## Table 2—Input Current Limit Setting

### Input Voltage Limit Setting

The input voltage can be limited at a value set by a resistor divider from IN pin to VLIM pin to AGND according to the following expression (Typical Application Circuit):

$$V_{IN\_LIM} = 1.52 \times \frac{R1 + R2}{R2} (V)$$

When the voltage on VLIM pin drops and hits the reference voltage 1.52V, the input voltage will be clamped to the setting value.

## **Battery Charger**

The MP2617A and MP2617B completes charge operation consist of trickle charge, automatic charge termination, charge status indication, timer control, NTC indication, automatic recharge, and thermal limiting.

When the PWM converter is out of soft start, the battery charge cycle begins, the MP2617A and MP2617B first determines if the battery is deeply discharged. If the battery voltage is lower than the trick charge threshold (typical 3.0V), the battery charger starts in "trickle charge mode". The trickle charge current is limited to 10% of the programmed charge current until the battery voltage reaches 3.0V. If the charge stays in the "trickle charging mode" for longer than "trickle charge timer period", the "timer out" condition is triggered, the charge is terminated and CHGOK will start blinking to indicate that the battery is unresponsive. When the battery voltage is above 3.0V, the charger is operating at "constant current mode." The current delivered to the battery will try to reach the value programmed by the ISET pin. Depending on the available input power and system load conditions, the battery charger may or may not be able to charge at the full programmed rate. The system load is always

satisfied first over the battery charge current. If the system load requirement is low, the battery can be charged at full constant current.

When the battery voltage reaches the battery full threshold, the charger enters the "constant voltage mode" operation.

## End of Charge (EOC) and Indication

In constant voltage charge mode, the battery voltage is regulated at 4.2V (MP2617B) and 4.35V (MP2617A) (when SYSFB is float or SYS is programmed higher than battery full threshold) and the charge current decreases naturally. Once the charge current hits the battery full threshold  $I_{BF}$  (1/10 programmed charge current), the battery is fully charged and charge cycle is terminated.

If the charge current drops below  $I_{BF}$  because of any limit condition, the MP2617A and MP2617B will come out of CV mode, and the charge full detection is invalid.

A safe timer starts at the beginning of each new charge cycle and it monitors if the whole charge period is within the programmed time limit. After each charge cycle, when the battery is indicated as full, the timer counter will be reset. If the time is expired while the charging is still on going, the timer will force the MP2617A and MP2617B to

terminate charging CHGOK is blinking to indicate the fault condition.

If system voltage is programmed lower than 4.2V (MP2617B) and 4.35V (MP2617A) by the resistor divider at the SYSFB pin, the battery will be charged most close to  $V_{SYS}$  until the charge current reaches the  $I_{BF}$  threshold.

### Automatic Recharge

Once the battery charge cycle is completed, the MP2617A and MP2617B turns off indicating the battery full status. During this process, the battery power may be consumed by the system load or self discharge. If the input power is always on, to ensure the battery not to be exhausted. the new charge cvcle will automatically begin when the battery voltage falls below the auto-recharge threshold  $V_{RCHG}$  when the SYSFB is float, and 50mV lower if the SYSFB is connected to a resistor divider. The timer will re-start when the auto-recharge cycle begins.

During the charge off state when the battery is fully charged, if the input power is recycled, or the EN signal is refreshed, the charge cycle will re-start and the timer will refresh even if the battery voltage is above the auto-recharge threshold.

### **Charge Current Setting**

The charge current of the MP2617A and MP2617B is programmed using a single resistor from ISET pin to ground. The program resistor and charge current are calculated using the following equations:

$$I_{CHG} = 1.15 \times \frac{1800}{R_{SET}(k\Omega)} (mA)$$

At either constant current mode or constant voltage mode, the voltage at the ISET pin is proportional to the actual charge current delivered to the battery,  $I_{BATT}$ . The charge current can be calculated by monitoring the ISET pin voltage with the following formula:

$$I_{BATT} = \frac{V_{ISET}}{1.15} \times I_{CHG}$$

Additionally, the actual battery charge current may be lower than the programmed current due to limited input power available and prioritization of the system load.

Battery charge full current threshold  $I_{BF}$  is set internally at 10% of the programmed charge current. However,  $I_{BF}$  has a 150mA maximum limit which can not be exceeded.

### **Ideal Diode Mode**

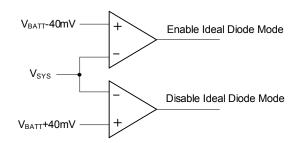

If the system current requirement increases over the preset limit of the PWM converter, the additional current will be drawn from the battery via the BATT-to-SYS switch. To avoid very large currents being drawn from the battery which might affect the reliability of the device, the MP2625B controls the charge switch to work at the ideal diode mode regulating V<sub>SYS</sub> to V<sub>BATT</sub>-65mV when V<sub>SYS</sub> is 40mV lower than V<sub>BATT</sub> is detected. Only when V<sub>SYS</sub> is 40mV higher than V<sub>BATT</sub>, the charger switch exits the ideal diode mode, and the charge cycle softly restarts.

# Figure 3— Ideal Diode Mode Enable/Disable

## Logic Control

The MP2617A and MP2617B have two separate enable control pins.

$\overline{EN}$  is a logic control pin that controls the operation of the whole IC. When  $\overline{EN}$  is low, the IC is enabled and the PWM converter output

powers the system and the charger. When  $\overline{\text{EN}}$  is high, both the PWM converter and the charger are disabled. The BATT to SYS switch turns fully on to connect the battery to power the system.

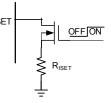

The ISET pin can be also used to control the operation of the charger. Setting ISET pin floating will disable the charger function while the output of PWM converter will continue supply power to system. On the other hand, a resistor from ISET to AGND will enable the charging at the programmed charge current.

The logic control of the ISET pin of the MP2617A and MP2617B can be realized as Figure 4. In this way, the user can choose logic low to be "off" signal or logic high to be "on" signal with a N-MOSFET.

Figure 4— ISET Logic Control

# Input Power Status Indication (ACOK)

An internal under voltage lockout circuit monitors the input voltage and keeps the IC in off state until the input rises over the rising threshold (3.8V). When the input voltage decreases below threshold (3.5V), the IC will turn off, and the

MP2617A, MP2617B Rev. 1.24 www.MonolithicPower.com 4/26/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

system load will be powered by the battery automatically. ACOK is an open-drain, active-low output that indicates the status of input power. The input is considered valid when the input voltage is over the UVLO rising threshold, and 310mV higher than the battery voltage to ensure both the converter and the charger can operate normally. If the input voltage from an adapter or

T E C

from a USB port is indicated OK, ACOK will turn low.

During EN off or thermal shutdown conditions,

the ACOK turns high to indicate no power is provided by the input to the system. The ACOK signal indicates if input supplies power to the system load or not. Any other condition can not

affect the ACOK indication as long as the input power is present.

## Charge Status Indication (CHGOK)

CHGOK is an open-drain, active-low output that

indicates the status of charge. CHGOK will be low during normal charging operation, turn high after charge full, and blink if a fault condition happens including NTC fault (battery temperature invalid) and timer out (bad battery).

In the event of a fault condition, CHGOK switches at 6Hz with the 50% duty cycle and enter "blinking" mode. The user should check the application circuit to find out the root cause of the fault condition if the "blinking" signal is asserted.

For no battery condition, CHGOK is blinking according to the transition between charging and charge full. The blinking frequency is determined by the cycle of charge and discharge of the output capacitor.

When the charge current to the battery is low or in the event the battery is in supplement mode

caused by the insufficient input power, CHGOK keeps low to avoid providing false charge full indication.

Table 2 shows the ACOK and CHGOK status under different charge conditions.

| Tab  | Table 2—Onarger Otatus Indication |                                                      |  |  |  |  |  |  |

|------|-----------------------------------|------------------------------------------------------|--|--|--|--|--|--|

| ACOK | CHGOK                             | Charger Status                                       |  |  |  |  |  |  |

| low  | low                               | In charging, supplement mode                         |  |  |  |  |  |  |

| low  | high                              | End of charge, ISET disable charger only.            |  |  |  |  |  |  |

| low  | blinking at<br>6Hz                | NTC fault, timer out                                 |  |  |  |  |  |  |

| high | high                              | V <sub>IN</sub> absent, EN disable, thermal shutdown |  |  |  |  |  |  |

### Table 2—Charger Status Indication

## Timer Setting

The MP2617A and MP2617B uses an internal timer to terminate charge if the timer times out. The timer duration is programmed by an external capacitor at the TMR pin and related to the real charge current ( $I_{BATT}$ ).

$$t_{Cycle} = \frac{C_{TMR} \times 0.73 \times 2}{\frac{I_{BATT}}{40000} + 1 \times 10^{-6}} (s)$$

The trickle mode charge time is:

$$t_{\text{Trickle TMR}} = 45055 \times t_{\text{Cycle}}(s)$$

If a  $C_{TMR}$  (0.1µF) is connected, the trickle charge current is 0.1A, the trickle charge time is about 31 minutes.

The total charge time is:

$$t_{\text{Total TMR}} = 3407871 \times t_{\text{Cycle}}(s)$$

If a  $C_{TMR}$  (0.1µF) is connected, the CC charge current is 1A, the CC charge time is about 5.3 hours.

As a result of power path management control, charge current might vary during normal operation, under this condition, the MP2617A and MP2617B automatically takes into account this variation and adjust the timer period accordingly.

When the charge current is set larger than 1A, the safe timer period is reduced accordingly with the same TMR capacitor. If the charge current is reduced because of insufficient input power, the timer period is increased proportionally by the same rate at which the charge current is reduced. If charge is stopped due to high system load, the timer is temporarily suspended.

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

This feature avoids indicating a false trigger indication for bad battery indication when there is little charge current delivered to the battery as a result of the insufficient input power. When the timer out condition occurs, the MP2617A and MP2617B terminates the charge at once and

CHGOK blinks to indicate the fault status. If one of the following events happens, the timer is refreshed and the MP2617A and MP2617B restarts the charge cycle.

- Input re-startup

- Refresh EN /ISET signal

- Auto-Recharge

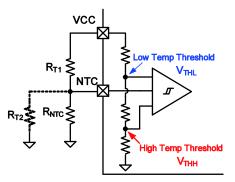

## **NTC Thermistor**

The NTC pin allows MP2617A and MP2617B to sense the battery temperature using the Negative Thermal Coefficient (NTC) thermistor usually available in the battery pack to ensure safe operating environment of the battery. A resistor with appropriate value should be connected from VCC to NTC and the NTC resistor is from NTC pin to AGND. The voltage on NTC pin is determined by the resistor divider whose divide ratio as the different resistance of the NTC thermistor depends on the ambient temperature of the battery.

The MP2617A and MP2617B has an internal NTC voltage comparator to set the upper and lower limit of the divide ratio. If NTC pin voltage falls out of this range it means the temperature is outside the safe operating range,

As a result, the MP2617A and MP2617B will stop charging and report it on indication pins. Charging will automatically resume after the temperature falls back into the safe range.

## **Thermal Protection**

The MP2617A and MP2617B implements thermal protection to prevent the thermal damage to the IC or surrounding components. An internal thermal sense and feedback loop will automatically decrease the charge current when the die-temperature rises to about 120°C. This function is referred as charge current thermal fold-back. This feature protects the MP2617A and MP2617B from excessive temperature due to high power operation or high ambient thermal conditions. Another benefit of this feature is charge current can be set according to the requirement rather than worst-case conditions for a given application with the assurance of safe operation. The MP2617A and MP2617B will stop charging if the junction temperature rises above 150°C as the IC enters thermal shutdown protection.

## **Battery Discharge Protection**

When the input power is removed or invalid, the system load will draw power from the battery via the battery switch. Under this condition, the battery switch is fully on to minimize the power loss. The MP2617A and MP2617B integrates battery discharge protection. If the battery discharge current is larger than the discharge current limit threshold IDIS (5A), the current will be regulated at the preset limited value. And if the current increases further, the SYS voltage starts to decrease. When V<sub>SYS</sub> drops to about 800mV lower than V<sub>BATT</sub>, SYS short condition is detected. Under this condition, the discharge current is limited at 230mA. In the event of a short from system to GND the discharge current from the battery to the system is also limited to 230mA. Furthermore, battery voltage UVLO is always monitored. If the battery voltage is lower than the battery UVLO threshold, the battery switch is turned off immediately. This feature makes sure the battery from over-discharged.

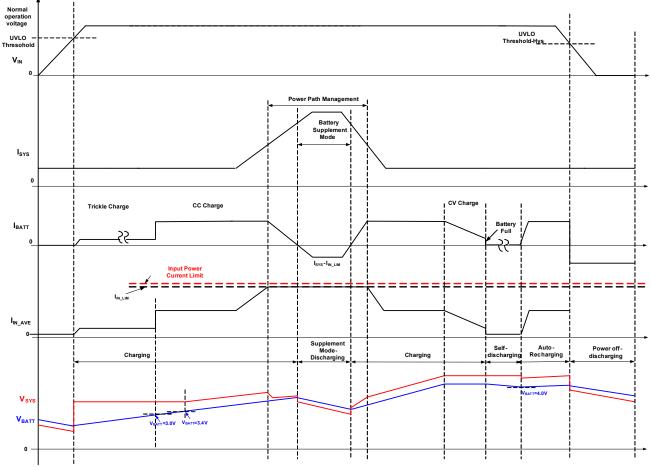

## **Dynamic Power Path Management (DPPM)**

In the presence of a valid input source, the PWM converter will supply the current to both the system and the battery charger.

The voltage  $V_{SYS}$  is regulated based on the value of the battery voltage. When  $V_{BATT}$  is higher than 3.4V,  $V_{SYS}$  is regulated 200mv above  $V_{BATT}$  to charge the battery. When  $V_{BATT}$  is lower than 3.4V, to ensure the system can still be powered up even with a drained battery connected,  $V_{SYS}$  is regulated at constant 3.6V.

When the input source is overloaded, either the current exceeds the input current limit or the voltage falls below the input voltage limit, the MP2617A and MP2617B then reduces the charge current until the input current falls below the input current limit and the input voltage rises above the input voltage limit. If the system current increases beyond the power allowed by

the input source, additional power will be drawn from the battery via an on-chip  $40m\Omega$  MOSFET working as an ideal diode.

Additionally, if the input source is removed, the MP2617A and MP2617B will turn on the  $40m\Omega$  MOSFET allowing the battery to power the

system load to keep the operation of the portable device.

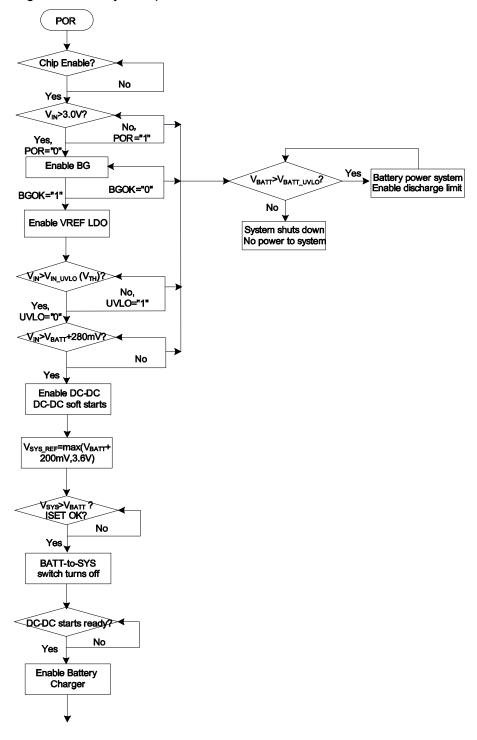

# **Operation Flow Chart**

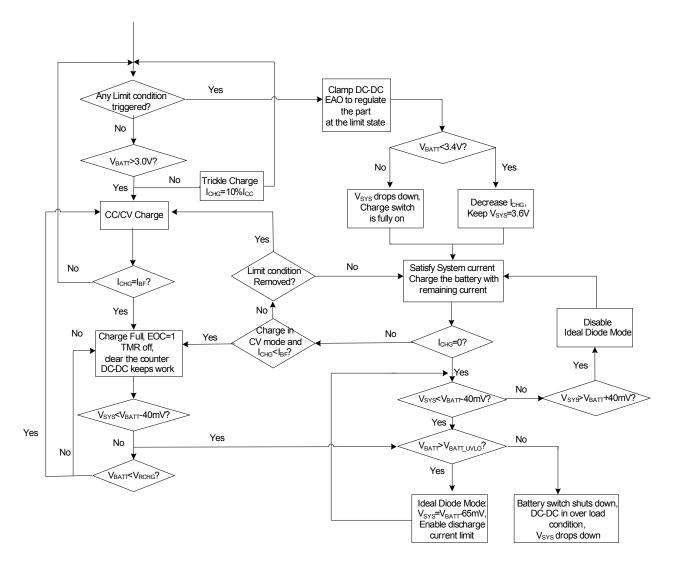

Taking the MP2617B for example, Figure 5 shows the operation flow chart of the MP2617B while Figure 6 shows the operation process.

MP2617A, MP2617B Rev. 1.24 www.MonolithicPower.com 4/26/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

کا ا

Figure 5— MP2617B Operation Flow Chart under No Fault Condition

크노

Figure 6— MP2617B Operation Process under No Fault Condition

# **APPLICATION INFORMATION**

# **COMPONENT SELECTION**

## Setting the Input Current Limit

First the input current limit can be set by the M0 and M1 pins refer to the Table 1, the exact current value in minimum, typical and maximum is listed in the EC table.

Under program mode, connect a resistor from the ILIM pin to AGND to program the input current limit for different input ports. The relationship between the input current limit and setting resistor is as Equation (1) which is shown in following again:

$$I_{\text{IN}\_\text{LIM}} = 1.14 \times \frac{40000}{R_{\text{ILIM}}(k\Omega)} (\text{mA})$$

(1)

For MP2617A/B, IILIM is not over 3A.

The tolerance is  $\pm 8\%$  of the input current limit setting.

So for a required minimum input current limit value, just calculate its typical value first, then calculate the setting resistor based on Equation (1). Also the maximum value can be calculated according to the tolerance. 1% accuracy resistor is used for this setting. Also, for a given resistor of  $R_{ILIM}$ , the input current limit can be calculated. Following table is an example:

| Resistor | R <sub>iLIM</sub><br>(kΩ) | l <sub>IN_LIM</sub><br>(mA) | 8%      | -8%     |

|----------|---------------------------|-----------------------------|---------|---------|

| Тур.     | 54.9                      | 830.601                     | 897.049 | 764.153 |

| Min.     | 54.351                    | 838.991                     | 906.11  | 771.872 |

| Max.     | 55.449                    | 822.377                     | 888.168 | 756.587 |

Table 3: Example of RILIM setting

Therefore, if customer selected a 54.9k in 1% accuracy resistor for the input current limit setting, then the typical input current limit value is 830.6mA, the minimum is 756.6mA and the maximum is 906mA.

### Setting the Charge Current

R<sub>ISET</sub> connecting from the ISET pin to AGND sets the charge current (I<sub>CHG</sub>). The relationship between the charge current and setting resistor is as Equation (2) which is shown in following again:

$$I_{CHG} = 1.15 \times \frac{1800}{R_{SET}(k\Omega)}$$

(mA) (2)

For example, if the typical  $I_{CHG}$  is designed as 2A, then the  $R_{SET}$  is calculated at  $1.05k\Omega$ . The tolerance of the  $I_{CHG}$  setting is  $\pm 10\%$ . If the minimum or maximum charge current is required, first the typical value should be calculated according to the tolerance. After that, calculate the resistor according to formula (2). 1% accuracy resistor is used for this setting.

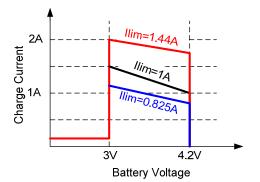

For a given setting resistor, the charge current can be calculated by the same way did in the input current limit setting. Usually in USB mode, the charge current is always set over the USB input limit specification. Then the MP2625 regulates the input current constant at the limitation value. Thus the real CC charge current is not the setting value, it varies with different input and battery voltages.

The maximum CC charge value can be calculated as:

$$I_{CC_MAX} = \frac{V_{IN} \times I_{ILIM} \times \eta}{V_{TC}} (A)$$

(3)

Where V<sub>TC</sub> is trickle charge threshold (3V) and  $\eta$  is the current charge efficiency. Assume V<sub>IN</sub>=5.5V, I<sub>ILIM</sub>=1A, suppose  $\eta$ =83%, thus I<sub>CC\_MAX</sub>=1.52A.

Figure 7 shows a calculating charge current curve by limiting the input current limit.

## Figure 3—I<sub>CHG</sub> Variation with Different Input Current Limit

## Setting the Input Voltage Limit

The input clamp voltage is set using a resistive voltage divider from the input voltage to VLIM pin. The voltage divider divides the input voltage down to the limit voltage by the ratio:

$$V_{\text{VLIM}} = V_{\text{IN}\_\text{LIM}} \times \frac{\text{R2}}{\text{R1} + \text{R2}} (V)$$

(4)

www.MonolithicPower.com

6/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

Thus the input voltage is:

$$V_{\text{IN}\_\text{LIM}} = V_{\text{VLIM}} \times \frac{\text{R1} + \text{R2}}{\text{R2}} (\text{V})$$

(5)

The voltage clamp reference voltage  $V_{VLIM}$  is 1.52V, and a typical value for R2 can be  $10k\Omega$ . With this value, R1 can be determined by:

$$R1 = R2 \times \frac{V_{IN\_LIM} - V_{VLIM}}{V_{VLIM}}(V)$$

(6)

For example, for a 4.65V input limit voltage, R2 is  $10k\Omega$ , and R1 is  $20.6k\Omega$ .

The minimum value and the maximum value of the input voltage limit can be calculated according to the accuracy of the resistor and the tolerance of  $V_{VLIM}$ . 1% accuracy resistors are used for R1 and R2.

### Setting the System Voltage

The system voltage can be regulated to any value between 4.08V to 4.4V (MP2617B) by the resistor divider on SYSFB pin as R6 and R7 in Figure 10.

$$V_{SYS} = V_{SYS\_REF} \times \frac{R6 + R7}{R7}$$

(7)

Where V<sub>SYS\_REF</sub> is 1.152V, the reference voltage of SYS. With a typical value for R7, 10k $\Omega$ , R6 can be determined by:

$$R6 = R7 \times \frac{V_{SYS} - V_{SYS\_REF}}{V_{SYS\_REF}} (V)$$

(8)

For example, for a 4.2V system voltage, R7 is  $10k\Omega$ , and R6 is  $26.5k\Omega$ . 1% resistors are selected for the R5 and R6.

Be noted that, the minimum  $V_{SYS}$  is limited to be higher than the maximum value of the autorecharge threshold which is 4.05V.

### Selecting the Inductor

Inductor selection trades off among cost, size, and efficiency. A lower inductance value corresponds to a smaller size, but results in hiaher ripple currents. hiaher magnetic hysteretic losses, and higher output capacitances. From a practical standpoint, the inductor ripple current does not exceed 30% of the maximum load current under worst cases conditions. For example, if the I<sub>CHG</sub> is setting to 3A in MP2617B, then,  $\Delta I_{L}$  is general set at 0.9A.

However, for the light load condition, the inductor ripple current will be very small which may cause unstable operation due to the peak current mode control of the IC. For stable operation, the experienced minimum limit value for inductor current ripple is 0.5A. Therefore, the inductor current ripple is the maximum one of 30% times  $I_{CHG}$  and 0.5A.

And the inductance can be calculated according to Equation (9):

$$L = \frac{V_{IN} - V_{SYS}}{\Delta I_{L MAX}} \frac{V_{SYS}}{V_{IN} \times f_{S}(MHz)} (\mu H)$$

(9)

The peak current of the inductor is calculated as Equation (10):

$$I_{\text{PEAK}} = I_{\text{LOAD}(\text{MAX})} \times (1 + \frac{\text{\%ripple}}{2}) (\text{mA})$$

(10)

Where  $V_{IN}$ ,  $V_{SYS}$ , and  $f_S$  are the typical input voltage, the output voltage, and the switching frequency, respectively.

Following Table 4 provides the selection guide of the inductance based on different input voltage.

| SPEC            | Inductance Selection                                                                                      |                  |           |      |                            |      |                         |

|-----------------|-----------------------------------------------------------------------------------------------------------|------------------|-----------|------|----------------------------|------|-------------------------|

| V <sub>IN</sub> | $V_{IN} - V_{SYS}$ $V_{SYS}$                                                                              | L <sub>MIN</sub> | $L_{MAX}$ | L    | Saturation                 | DCR  | Package                 |

| <b>∨</b> IN     | $L \equiv \frac{1}{1}$                                                                                    | (µH)             | (µH)      | (µH) | Current (A) <sup>(5)</sup> | (mΩ) | Fackage                 |

| 5V              |                                                                                                           | 0.367            | 1.25      | 1.0  | >3.95                      | <50  | Application<br>Required |

| 9V              | ΔI <sub>L</sub> =max (0.3*I <sub>CHG</sub> ,0.5A)<br>ΔI <sub>LMIN</sub> =0.5A<br>ΔI <sub>LMAX</sub> =0.9A | 1.5              | 2.8       | 2.2  | >3.95                      | <50  | Application<br>Required |

Table 4: Inductance Selection Guide under different Input Voltage

NOTE:

5) Saturation Current of the inductor should be higher than the IPEAK, add 0.5A margin here.

### Selecting the Input Capacitor

The input capacitor C1 from the typical application circuit absorbs the maximum ripple current from the PWM converter, which is given by

$$I_{\text{RMS}_{\text{MAX}}} = I_{\text{CC}_{\text{MAX}}} \times \frac{\sqrt{V_{\text{TC}} \times (V_{\text{IN}_{\text{MAX}}} - V_{\text{TC}})}}{V_{\text{IN}_{\text{MAX}}}} (A) (11)$$

For Icc\_MAX=2A, VTC=3V, VIN\_MAX=10V, the maximum ripple current is 1A. Select the input capacitors so that the temperature rise due to the ripple current does not exceed 10°C. Use ceramic capacitors with X5R or X7R dielectrics because of their low ESR and small temperature coefficients.

For most applications, use a  $10\mu$ F capacitor. Besides, usually a small cap with at least  $1\mu$ F (C1) from IN to GND is required to be put as much close as possible to the IC. For the input voltage is high to 10V, consider the spike when input insert, select the input capacitors (both the 22uF and 1uF) in 25V rating.

## **Selecting the Output Capacitor**

The output capacitor  $C_{SYS}$  from the typical application circuit is in parallel with the SYS load.  $C_{SYS}$  absorbs the high-frequency switching ripple current and smoothes the output voltage. Its impedance must be much less than that of

the system load to ensure it properly absorbs the ripple current.

Use a ceramic capacitor because it has lower ESR and smaller size that allows us to ignore the ESR of the output capacitor. Thus, the output voltage ripple is given by:

$$\Delta r = \frac{\Delta V_{SYS}}{V_{SYS}} = \frac{1 - \frac{V_{SYS}}{V_{IN}}}{8 \times C2 \times f_S^2 \times L}\%$$

(12)

In order to guarantee the  $\pm 0.5\%$  system voltage accuracy, the maximum output voltage ripple must not exceed 0.5% (e.g. 0.1%). The maximum output voltage ripple occurs at the minimum system voltage and the maximum input voltage.

The output capacitor can be calculated with Equation (13):

$$C_{SYS} = \frac{1 - \frac{V_{SYS\_MIN}}{V_{IN}}}{8 \times f_{S}^{2} \times L \times \Delta r}$$

(13)

When SYSFB pin is floating, output voltage ripple is the main concern to select the output capacitor ( $C_{SYS}$ ), refer to Table 5 for detail selection guide about the SYS capacitance selection under typical inputs.

| SPEC            | SYS Capacitance (C <sub>SYS</sub> ) Selection                                              |                                                                      |                                                                        |                               |                         |  |

|-----------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------|-------------------------|--|

| V <sub>IN</sub> | $C_{SYS} = \frac{1 - \frac{V_{SYS}}{V_{IN}}}{8 \times f_{S}^{2} \times L \times \Delta r}$ | C <sub>SYS_MIN</sub> (µF) <sup>6)</sup><br>When SYSFB is<br>Floating | C <sub>SYS_MIN</sub> (µF) <sup>6)</sup><br>When SYSFB<br>is Programmed | Temperature<br>Characteristic | Package                 |  |

| 5V              | δ×ι <sub>s</sub> ×L×Δι<br>Δr=0.1%                                                          | 13.6                                                                 | 20                                                                     | X5R;X7R                       | Application<br>Required |  |

| 9V              | L=1μΗ @V <sub>IN</sub> =5V<br>L=2.2μΗ @V <sub>IN</sub> =9V                                 | 13.3                                                                 | 20                                                                     | X5R;X7R                       | Application<br>Required |  |

## **Table 5: SYS Capacitance Selection Guide**

NOTE:

For different voltage rating, capacitance will have different DC bias characteristic. Suppose a general condition, capacitance drops 40% under V<sub>SYS</sub>=4.4V under 10V rating, and 50% at 6.3V rating.

When SYSFB is programmed using external resistors, the control loop function is changed. A zero point is added around the cross over frequency of the DC gain, and this may result in the phase margin varied a lot, which may cause the unstable operation. To avoid this condition, a minimum capacitance requirement should be satisfied to make the pole point to compensate the zero point. This minimum capacitance is 20uF for a general application.

So, for the SYSFB programmed condition, the  $C_{SYS}$  should be selected as max ( $C_{SYS\_MIN}$ , 20uF),  $C_{SYS\_MIN}$  is calculated from the formula of equation (13), as shown in Table 5. For better stability margin, select a 47uF ceramic capacitor with 6.3V and above voltage rating as the output capacitor in this case.

### **Resistor Choose for NTC Sensor**

Figure 8 shows an internal resistor divider reference circuit to limit the low temperature threshold and high temperature threshold at 65%·VCC and 33.5%·VCC, respectively. For a given NTC thermistor, select appropriate R<sub>T1</sub> and R<sub>T2</sub> to set the NTC window:

$$\frac{R_{T2}/R_{NTC\_Cold}}{R_{T1} + R_{T2}/R_{NTC\_Cold}} = \frac{V_{THL}}{VCC} = 65\%$$

(14)

$$\frac{R_{T2}//R_{NTC\_Hot}}{R_{T1} + R_{T2}//R_{NTC\_Hot}} = \frac{V_{THH}}{VCC} = 33.5\%$$

(15)

$R_{NTC\_Hot}$  is the value of the NTC resistor at high temperature of the required temperature operation range, and  $R_{NTC\_Cold}$  is the value of the NTC resistor at low temperature.

The two resistors,  $R_{T1}$  and  $R_{T2}$ , allow the high temperature limit and low temperature limit to be programmed independently. With this feature, the MP2625B can fit most type of NTC resistor and different temperature operation range requirements.

$R_{\text{T1}}$  and  $R_{\text{T2}}$  values depend on the type of the NTC resistor:

$$R_{T2} = \frac{0.3 \times R_{NTC\_Cold} \times R_{NTC\_Hot}}{0.1225 \times R_{NTC\_Cold} - 0.4225 \times R_{NTC\_Hot}}$$

(16)

$$R_{T1} = \frac{0.3 \times R_{NTC\_Hot} \times R_{NTC\_Cold}}{0.2275 \times (R_{NTC\_Cold} - R_{NTC\_Hot})}$$

(17)

For example, for the thermistor NCP18XH103,

it has the following electrical characteristic:

At 0°C,  $R_{NTC_{Cold}} = 27.445 k\Omega$ ;

At 50°C,  $R_{NTC_{Hot}} = 4.1601 k\Omega$ .

The following equations are derived assuming that the NTC window is between 0°C and 50°C. According to the above equations to calculate  $R_{T1}$ =7.15k $\Omega$  and  $R_{T2}$ =25.5k $\Omega$ .

Figure 4—NTC Function Block

## **PCB Layout Guideline**

It is important to pay special attention to the PCB layout to meet specified noise, efficiency and stability requirements. The following design considerations can improve circuit performance:

1) Route the power stage adjacent to their grounds. Aim to minimize the high-side switching node (SW, inductor), trace lengths in the high-current paths and the current sense resistor trace.

Keep the switching node short and away from all small control signals, especially the feedback network.

Place the input capacitor as close as possible to the IN and PGND pins.

Place the output inductor close to the IC and connect the output capacitor between the inductor and PGND of the IC.

2) For high-current applications, the balls for the power pads (IN, SW, SYS, BATT and PGND) should be connected to as much copper in the board as possible. This improves thermal performance because the board conducts heat away from the IC.

MP2617A, MP2617B Rev. 1.24

www.MonolithicPower.com

4/26/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

3) The PCB should have a ground plane connected directly to the return of all components through vias (two vias per capacitor for power-stage capacitors, one via per capacitor for small-signal components). It is also recommended to put vias inside the PGND pads for the IC, if possible. A star ground design approach is typically used to keep circuit block currents isolated (high-power/low-power small-signal) which reduces noise-coupling and ground-bounce issues. A single ground plane for this design gives good results. With this small layout and a single ground plane, there is no ground-bounce issue, and having the components segregated minimizes coupling between signals.

# **TYPICAL APPLICATION CIRCUITS**

Figure 9: Typical Charge Application Circuit for 5V input with NTC Resistor Fixed

| Qty | Ref                                 | Value | Description                                      | Package | Manufacture |

|-----|-------------------------------------|-------|--------------------------------------------------|---------|-------------|

| 1   | Cin                                 | 10µF  | Ceramic Capacitor;10V;<br>X5R or X7R             | 1206    | Any         |

| 1   | C1                                  | 1µF   | Ceramic Capacitor;10V;<br>X5R or X7R             | 0603    | Any         |

| 1   | C2                                  | 1µF   | Ceramic Capacitor;6.3V;<br>X5R or X7R            | 0603    | Any         |

| 1   | C3                                  | 100nF | Ceramic Capacitor;16V;<br>X5R or X7R             | 0603    | Any         |

| 1   | CTMR                                | 100nF | Ceramic Capacitor;6.3V;<br>X5R or X7R            | 0603    | Any         |

| 2   | C <sub>SYS</sub> ,C <sub>BATT</sub> | 22µF  | Ceramic Capacitor;10V;<br>X5R or X7R             | 1206    | Any         |

| 2   | Rt1,Rt2                             | 10k   | Film Resistor;1%                                 | 0603    | Any         |

| 1   | L1                                  | 1.0µH | Inductor;1.0uH;Low<br>DCR;I <sub>SAT</sub> >2.8A | SMD     | Any         |

Table 6: The Key BOM of Figure 9.

# **TYPICAL APPLICATION CIRCUITS**

Figure 10: Typical Charge Application Circuit for 9V Input and 1.5A Input Current Limit

| Qty | Ref        | Value | Description                                    | Package | Manufacture |

|-----|------------|-------|------------------------------------------------|---------|-------------|

| 1   | CIN        | 22µF  | Ceramic Capacitor;16V;<br>X5R or X7R           | 1206    | Any         |

| 1   | C1         | 1µF   | Ceramic Capacitor;16V;<br>X5R or X7R           | 0603    | Any         |

| 1   | C2         | 1µF   | Ceramic Capacitor;<br>6.3V; X5R or X7R         | 0603    | Any         |

| 1   | C3         | 100nF | Ceramic Capacitor;25V;<br>X5R or X7R           | 0603    | Any         |

| 1   | C4         | 4.7µF | Ceramic Capacitor;<br>10V; X5R or X7R          | 0603    | Any         |