# MP2664

500mA, 5V USB, I<sup>2</sup>C-Controlled Battery Charger with Power Path Management for Single-Cell Li-Ion Battery in QFN Package

### DESCRIPTION

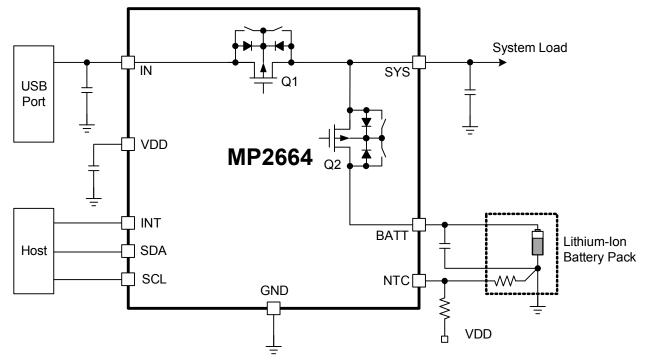

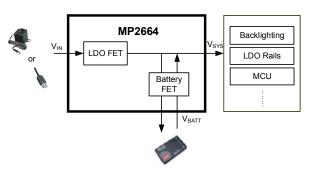

The MP2664 is a highly integrated, single-cell, Li-ion/Li-polymer battery charger with system power path management for space-limited, portable applications. The MP2664 uses input power from either an AC adapter or a USB port to supply the system load and charge the battery independently. The charger features constant current pre-charge, constant current fast charge (CC) and constant voltage (CV) regulation, charge termination, and autorecharge.

The power path management function ensures continuous power to the system by automatically selecting the input, the battery, or both to power the system. This power stage features a low dropout regulator from the input to the system and a  $100m\Omega$  switch from the battery to the system. Power path management separates the charging current from the system load, which allows for proper charge termination and keeps the battery in full-charge mode.

The MP2664 provides system short-circuit protection (SCP) by limiting the current from the input to the system and the battery to the system. This feature is especially critical for preventing the Li-ion battery from being damaged by excessively high currents. An onchip battery under-voltage lockout (UVLO) cuts off the path between the battery and the system the battery voltage drops below the programmable battery UVLO threshold, which prevents the Li-ion battery from being overdischarged. An integrated I<sup>2</sup>C control interface allows the MP2664 to program the charging parameters, such as input current limit, input minimum voltage regulation, charging current, battery regulation voltage, safety timer, and battery UVLO.

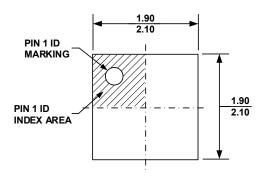

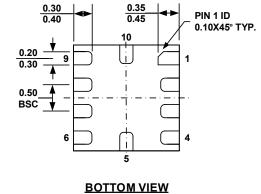

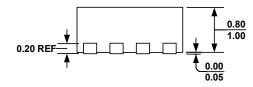

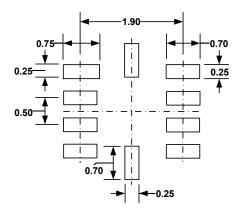

The MP2664 is available in a QFN-10 (2mmx2mm) package.

### FEATURES

- Fully Autonomous Charger for Single-Cell Li-Ion/Li-Polymer Batteries

- Complete Power Path Management for Simultaneously Powering the System and Charging the Battery

- ±0.5% Charging Voltage Accuracy

- 13V Maximum Voltage for the Input Source

- I<sup>2</sup>C Interface for Setting Charging Parameters and Status Reporting

- Fully Integrated Power Switches and No External Blocking Diode Required

- Built-In Robust Charging Protection Including Battery Temperature Monitoring and Programmable Timer

- PCB Over-Temperature Protection (OTP)

- System Reset Function

- Built-In Battery Disconnection Function

- Thermal Limiting Regulation On-Chip

- Available in a QFN-10 (2mmx2mm) Package

# **APPLICATIONS**

- Wearable Devices

- Smart Handheld Devices

- Fitness Accessories

- Smartwatches

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

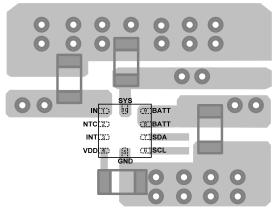

# **TYPICAL APPLICATION**

### ORDERING INFORMATION

| Part Number*    | Package          | Top Marking |

|-----------------|------------------|-------------|

| MP2664GG-xxxx** | QFN-10 (2mmx2mm) | See Below   |

| EVKT-MP2664     | Evaluation Kit   |             |

\* For Tape & Reel, add suffix -Z (e.g. MP2664GG-xxxx-Z).

\*\*"xxxx" is the register setting option. The factory default is "0000". This content can be viewed in the I<sup>2</sup>C register map. Please contact an MPS FAE to obtain an "xxxx" value.

### **TOP MARKING**

### HVY

### $\mathbf{LLL}$

HV: Product code of MP2664GG Y: Year code LLL: Lot number

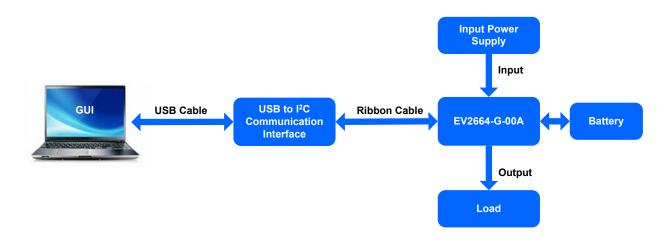

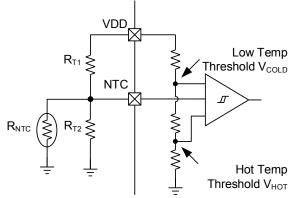

## **EVALUATION KIT EVKT-MP2664**

EVKT-MP2664 Kit contents: (Items below can be ordered separately)

| # | Part Number        | Item                                                                                                 | Quantity |

|---|--------------------|------------------------------------------------------------------------------------------------------|----------|

| 1 | EV2664-G-00A       | MP2664 evaluation board                                                                              | 1        |

| 2 | EVKT-USBI2C-02-Bag | Includes one USB to I <sup>2</sup> C communication interface device, one USB cable, one ribbon cable | 1        |

| 3 | Online resources   | Include Datasheet, User guide, Product brief, and GUI                                                | 1        |

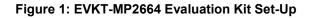

## PACKAGE REFERENCE

# **PIN FUNCTIONS**

| Pin # | Name | I/O   | Description                                                                                                                                                                                                                                                                                                                                                 |  |

|-------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | IN   | Power | <b>Input power.</b> Place a ceramic capacitor from IN to GND, as close to the IC as possible.                                                                                                                                                                                                                                                               |  |

| 2     | NTC  | I     | <b>Temperature-sense input.</b> Connect a negative temperature coefficient thermistor to NTC. Program the hot and cold temperature window with a resistor divider from VDD to NTC to GND. The charge is suspended when NTC is out of range.                                                                                                                 |  |

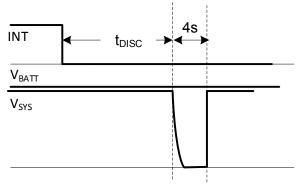

| 3     | INT  | I/O   | <b>Interrupt signal.</b> INT can send the charging status and fault interruption to the host. INT can also disconnect the system from the battery. Pull INT from high to low for >16s.The battery FET is off and turns on automatically after >4s regardless of the INT state. The external pull-up resistor at INT must not be smaller than $300k\Omega$ . |  |

| 4     | VDD  | Power | <b>Internal control power supply.</b> Connect a ceramic capacitor from VDD to GND. No external load is allowed.                                                                                                                                                                                                                                             |  |

| 5     | GND  | Power | Ground.                                                                                                                                                                                                                                                                                                                                                     |  |

| 6     | SCL  | I     | $I^2$ <b>C</b> interface clock. Connect SCL to the logic rail through a 10kΩ resistor.                                                                                                                                                                                                                                                                      |  |

| 7     | SDA  | I/O   | I <sup>2</sup> C interface data. Connect SDA to the logic rail through a 10kΩ resistor.                                                                                                                                                                                                                                                                     |  |

| 8, 9  | BATT | Power | <b>Battery.</b> Place a ceramic capacitor from BATT to GND, as close to the IC as possible.                                                                                                                                                                                                                                                                 |  |

| 10    | SYS  | Power | <b>System power supply.</b> Place a ceramic capacitor from SYS to GND, as close to the IC as possible.                                                                                                                                                                                                                                                      |  |

## **ABSOLUTE MAXIMUM RATINGS** (1)

| V <sub>IN</sub><br>All other pins to GND     |                |

|----------------------------------------------|----------------|

| Continuous power dissipation (T <sub>A</sub> |                |

|                                              |                |

| Junction temperature                         |                |

| Lead temperature (solder)                    |                |

| Storage temperature6                         | 65°C to +150°C |

|                                              |                |

### **Recommended Operating Conditions** <sup>(3)</sup>

| Supply voltage (V <sub>IN</sub> )          | 4.35V to 5.5V             |

|--------------------------------------------|---------------------------|

|                                            | (USB input)               |

| I <sub>IN</sub>                            |                           |

| I <sub>SYS</sub>                           | Up to 3.2A <sup>(5)</sup> |

| I <sub>CHG</sub>                           | Up to 455mA               |

| VBATT                                      | Up to 4.545V              |

| Operating junction temp (T <sub>J</sub> )4 | 0°C to +125°C             |

#### Thermal Resistance (4) $\theta_{JA}$ $\theta_{JC}$

QFN-10 (2mmx2mm)...... 80 ..... 16 ..... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{\text{D}}$  (MAX) = (T\_{\text{J}} (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- Measured on JESD51-7, 4-layer PCB. 4)

- 5) Guaranteed by design.

# **ELECTRICAL CHARACTERISTICS**

### $V_{IN}$ = 5.0V, $V_{BATT}$ = 3.5V, $T_A$ = 25°C, unless otherwise noted.

| Parameter                    | Symbol                                                    | Condition                                                              | Min  | Тур  | Max  | Units |

|------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|------|------|------|-------|

| Input Source and Battery P   |                                                           |                                                                        |      |      |      |       |

| Input operation voltage      | VIN                                                       |                                                                        | 4.35 | 5    | 5.5  | V     |

| Battery input voltage (6)    | VBATT                                                     |                                                                        |      |      | 4.5  | V     |

| Input over-voltage           | Max ave                                                   | Input rising threshold                                                 | 5.85 | 6    | 6.15 | V     |

| protection trigger threshold | protection trigger threshold VIN_OVP Input rising thresho |                                                                        | 5.65 | 0    | 0.15 | v     |

| Input over-voltage           |                                                           |                                                                        |      | 350  |      | mV    |

| protection recover threshold |                                                           |                                                                        |      | 550  |      | IIIV  |

| Input under-voltage lockout  | VIN_UVLO                                                  | Input rising threshold                                                 | 3.8  | 3.9  | 4    | V     |

| threshold                    | VIN_UVLO                                                  |                                                                        | 5.0  | 5.5  | -    | v     |

| Input under-voltage lockout  |                                                           |                                                                        |      | 170  |      | mV    |

| threshold hysteresis         |                                                           |                                                                        |      | 170  |      | 111.0 |

| Input vs. battery voltage    | VHDRM                                                     | Input rising vs. battery                                               | 100  | 130  | 160  | mV    |

| headroom threshold           |                                                           | input rising vs. battery                                               | 100  | 150  | 100  | 1117  |

| Input vs. battery voltage    |                                                           |                                                                        |      |      |      |       |

| headroom threshold           |                                                           |                                                                        |      | 85   |      | mV    |

| hysteresis                   |                                                           |                                                                        |      |      |      |       |

| Battery under-voltage        |                                                           | I <sup>2</sup> C programmable range                                    | 2.4  |      | 3.1  | V     |

| lockout threshold            | VBATT_UVLO                                                | Falling, programmable, REG01h,                                         | 2.6  | 2.8  | 3    | V     |

|                              |                                                           | bits[2:0] = 100                                                        | 2.0  | 2.0  | 5    | v     |

| Battery under-voltage        |                                                           |                                                                        |      | 210  |      | mV    |

| threshold hysteresis         |                                                           |                                                                        |      | 210  |      | 111.0 |

| Battery over-voltage         | VEATT OVE                                                 | Rising, higher than VBATT REG                                          |      | 130  |      |       |

| protection threshold         | rotection threshold VBATT_OVP Rising, higher than VBAT    |                                                                        |      | 150  |      | mV    |

| Battery over-voltage         |                                                           |                                                                        |      | 70   |      | III V |

| protection hysteresis        |                                                           |                                                                        |      | 10   |      |       |

| Power Path Management        | •                                                         |                                                                        |      |      |      |       |

| System regulation voltage    | V <sub>SYS_REG</sub>                                      | V <sub>IN</sub> = 5.5V, I <sub>SYS</sub> = 10mA, I <sub>CHG</sub> = 0A | 4.55 | 4.65 | 4.75 | V     |

|                              |                                                           | REG00h, bits[2:0] = 000 - 85mA                                         | 65   | 75   | 85   |       |

| Input ourrent limit          |                                                           | REG00h, bits[2:0] = 001 - 130mA                                        | 102  | 116  | 130  | mA    |

| Input current limit          | IIN_LIM                                                   | REG00h, bits[2:0] = 100 - 265mA                                        | 230  | 247  | 265  |       |

|                              |                                                           | REG00h, bits[2:0] = 111 - 455mA                                        | 400  | 428  | 455  |       |

| Input minimum voltage        | V                                                         | I <sup>2</sup> C programmable range                                    | 3.88 |      | 5.08 | V     |

| regulation                   | V <sub>IN_MIN</sub>                                       | I <sup>2</sup> C setting V <sub>IN MIN</sub> = 4.20V                   | 4.1  | 4.2  | 4.3  |       |

| IN to SYS switch on          | <b>D</b>                                                  | (-5)(1) = 100mA                                                        |      | 200  | 400  |       |

| resistance                   | Ron_Q1                                                    | V <sub>IN</sub> = 5V, I <sub>SYS</sub> = 100mA                         |      | 300  | 400  | mΩ    |

|                              |                                                           | V <sub>IN</sub> = 5.5V, CEB = 0, charge                                |      | 620  |      |       |

| Include and a second         |                                                           | enabled, I <sub>CHG</sub> = 0A, I <sub>SYS</sub> = 0A                  |      | 630  |      |       |

| Input quiescent current      | $I_{IN_Q}$                                                | V <sub>IN</sub> = 5.5V, CEB = 1, charge                                |      | 500  |      | μA    |

|                              |                                                           | disabled                                                               |      | 500  |      |       |

|                              |                                                           | $V_{IN} = 5V, CEB = 0, I_{SYS} = 0A,$                                  |      | 22   |      |       |

|                              |                                                           | $V_{BATT} = 4.3V$                                                      |      | 32   |      | μA    |

|                              |                                                           | $V_{IN} = 0V, CEB = 1, I_{SYS} = 0A,$                                  |      |      |      |       |

|                              |                                                           | V <sub>BATT</sub> = 4.35V, disable PCB OTP                             |      |      | 10   |       |

|                              |                                                           | function, do not include the                                           |      | 11   | 13   | μA    |

|                              |                                                           | current from external NTC resistor                                     |      |      |      |       |

| Battery quiescent current    | Ibatt_q                                                   | $V_{IN} = 0V, CEB = 1, I_{SYS} = 0A,$                                  |      |      |      |       |

|                              |                                                           | $V_{BATT} = 4.35V$ , enable PCB OTP                                    |      |      | 24   |       |

|                              |                                                           | function, do not include the                                           |      | 20   | 24   | μA    |

|                              |                                                           | current from external NTC resistor                                     |      |      |      |       |

|                              |                                                           |                                                                        |      |      | 1    | 1     |

|                              |                                                           | $V_{BATT} = 4.5V, V_{IN} = V_{SYS} = GND,$                             |      | 4    | 5.5  | μA    |

# ELECTRICAL CHARACTERISTICS (continued)

### $V_{IN}$ = 5.0V, $V_{BATT}$ = 3.5V, $T_A$ = 25°C, unless otherwise noted.

| Parameter                                      | Symbol             | Condition                                                                          | Min   | Тур  | Max                | Units |

|------------------------------------------------|--------------------|------------------------------------------------------------------------------------|-------|------|--------------------|-------|

| Battery FET on resistance                      | Ron_q2             | $V_{IN} < 2V, V_{BATT} = 3.5V,$<br>$I_{SYS} = 100mA$                               |       | 100  | 150                | mΩ    |

| Battery current regulation in discharge mode   | Ірсне              | I <sup>2</sup> C programmable range                                                | 400   |      | 3200 (6)           | mA    |

| Battery FET switch leakage                     |                    | $V_{BATT}$ = 4.5V, $V_{IN}$ = $V_{SYS}$ = GND, disconnect mode                     |       |      | 1                  | μA    |

| SYS reverse to BATT switch leakage             |                    | V <sub>SYS</sub> = 6V, V <sub>IN</sub> = 4.5V,<br>V <sub>BATT</sub> = GND, CEB = 1 |       |      | 1                  | μA    |

| Battery FET disconnect by                      | t <sub>INT</sub>   | INT pull-low lasting time to turn off the battery FET                              |       | 16   |                    | S     |

| INT <sup>(6)</sup>                             |                    | Battery FET off lasting time<br>before turn-on                                     |       | 4    |                    |       |

| Battery Charger                                |                    |                                                                                    |       |      |                    |       |

| Battery charge voltage                         |                    | I <sup>2</sup> C programmable range                                                | 3.6   |      | 4.545              | V     |

| regulation                                     | VBATT_REG          | REG04h, bits[7:2] = 101000                                                         | 4.179 | 4.2  | 4.221              |       |

| regulation                                     |                    | REG04h, bits[7:2] = 110010                                                         | 4.328 | 4.35 | 4.372              |       |

|                                                |                    | $V_{IN} = 5V, V_{BATT} = 3.8V, I^2C$<br>programmable range                         | 8     |      | 535 <sup>(6)</sup> | mA    |

| Fast charge current                            |                    | $V_{IN} = 5V, V_{BATT} = 3.8V,$<br>ICC_SETTING = 93mA                              | 88    | 93   | 98                 |       |

| Fast charge current                            | lcc                | $V_{IN} = 5V, V_{BATT} = 3.8V,$<br>ICC_SETTING = 246mA                             | 232   | 248  | 263                |       |

|                                                |                    | V <sub>IN</sub> = 5V, V <sub>BATT</sub> = 3.8V,<br>I <sub>CC_SETTING</sub> = 399mA | 376   | 401  | 440                |       |

| Junction temperature regulation <sup>(6)</sup> | T <sub>J_REG</sub> | REG06h, bits[1:0] = 11 - 120°C                                                     |       | 120  |                    | °C    |

| ~                                              |                    | I <sup>2</sup> C programmable range                                                | 6     |      | 27                 | mA    |

| Pre-charge current                             | IPRE               | I <sub>PRE_SETTING</sub> = 6mA,<br>REG03h, bits[1:0] = 00                          | 2.5   | 4.7  |                    | mA    |

|                                                |                    | I <sub>PRE_SETTING</sub> = 20mA, REG03h,<br>bits[1:0] = 10                         | 14    | 18   | 22                 | mA    |

|                                                |                    | I <sub>CC_SETTING</sub> ≤ 263mA, (REG02h,<br>bit[4] = 0), REG03h, bits[1:0] = 00   | 5     | 7    | 9                  | mA    |

|                                                |                    | I <sub>CC_SETTING</sub> ≤ 263mA, (REG02h,<br>bit[4] = 0), REG03h, bits[1:0] = 01   | 10    | 13.5 | 17                 | mA    |

|                                                |                    | I <sub>CC_SETTING</sub> ≤ 263mA, (REG02h,<br>bit[4] = 0), REG03h, bits[1:0] = 10   | 16    | 20   | 24                 | mA    |

| Charge termination current                     | I                  | I <sub>CC_SETTING</sub> ≤ 263mA, (REG02h,<br>bit[4] = 0), REG03h, bits[1:0] = 11   | 22    | 27   | 32                 | mA    |

| threshold                                      | I <sub>TERM</sub>  | I <sub>CC_SETTING</sub> ≤ 280mA, (REG02h,<br>bit[4] = 1), REG03h, bits[1:0] = 00   | 10    | 13.5 | 17                 | mA    |

|                                                |                    | I <sub>CC_SETTING</sub> ≤ 280mA, (REG02h,<br>bit[4] = 1), REG03h, bits[1:0] = 01   | 22    | 27   | 32                 | mA    |

|                                                |                    | Icc_setting ≤ 280mA, (REG02h,<br>bit[4] = 1), REG03h, bits[1:0] = 10               | 34    | 42   | 49                 | mA    |

|                                                |                    | Icc_setting ≤ 280mA, (REG02h,<br>bit[4] = 1), REG03h, bits[1:0] = 11               | 46    | 55   | 64                 | mA    |

| Charge termination current                     | 1                  | Icc_setting ≤ 263mA, (REG02h,<br>bit[4] = 0), REG03h, bits[1:0] = 10               |       |      |                    |       |

| threshold hysteresis                           | Iterm_hys          | Icc_setting ≤ 280mA, (REG02h,<br>bit[4] = 0), REG03h, bits[1:0] = 10               |       |      |                    |       |

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

### **ELECTRICAL CHARACTERISTICS** (continued) $V_{IN} = 5.0V, V_{BATT}=3.5V, T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                                          | Symbol                  | Condition                                | Min        | Тур        | Max        | Units |

|--------------------------------------------------------------------|-------------------------|------------------------------------------|------------|------------|------------|-------|

| Pre-charge to fast charge threshold                                | VBATT_PRE               | VBATT rising, set VBATT_PRE = 3V         | 2.8        | 3          | 3.1        | V     |

| Pre-charge to fast charge threshold hysteresis                     |                         |                                          |            | 90         |            | mV    |

| Auto-recharge battery voltage threshold                            | VRECH                   | REG04h, bit[0] = 0<br>REG04h, bit[0] = 1 | 120<br>260 | 160<br>300 | 200<br>365 | mV    |

| Thermal Protection                                                 |                         |                                          |            |            |            |       |

| Thermal shutdown threshold (6)                                     | TJ_SHDN                 | Rising                                   |            | 150        |            | °C    |

| Thermal shutdown hysteresis <sup>(6)</sup>                         |                         |                                          |            | 20         |            | °C    |

| NTC output current                                                 | INTC                    | CEB = 0, NTC = 3V                        | -100       | 0          | +100       | nA    |

| NTC cold temperature rising threshold                              | Vcold                   | As a percentage of VDD                   | 63         | 65         | 67         | %     |

| NTC cold temperature rising threshold hysteresis                   |                         |                                          |            | 30         |            | mV    |

| NTC hot temperature falling threshold                              | Vнот                    | As a percentage of VDD                   | 31         | 33         | 35         | %     |

| NTC hot temperature falling threshold hysteresis                   |                         |                                          |            | 70         |            | mV    |

| NTC hot temperature falling threshold for PCB OTP                  | V <sub>НОТ_РСВ</sub>    | As a percentage of V <sub>DD</sub>       | 30         | 32         | 34         | %     |

| NTC hot temperature falling<br>threshold hysteresis for<br>PCB OTP |                         |                                          |            | 85         |            | mV    |

| Logic I/O Pin Characteristic                                       | <b>S</b> <sup>(6)</sup> |                                          |            |            |            |       |

| Low logic voltage threshold                                        | VL                      |                                          |            |            | 0.4        | V     |

| High logic voltage threshold                                       | V <sub>H</sub>          |                                          | 1.3        |            |            | V     |

| I <sup>2</sup> C Interface (SDA, SCL) <sup>(6)</sup>               |                         |                                          |            |            |            |       |

| Input high voltage level                                           | VIH                     | V <sub>PULL_UP</sub> = 1.8V, SDA and SCL | 1.3        |            |            | V     |

| Input low voltage level                                            | VIL                     | V <sub>PULL_UP</sub> = 1.8V, SDA and SCL |            |            | 0.4        | V     |

| Output low voltage level                                           | Vol                     | Isink = 5mA                              |            |            | 0.4        | V     |

| I <sup>2</sup> C clock frequency                                   | Fscl                    |                                          |            |            | 400        | kHz   |

| <b>Clock Frequency and Watc</b>                                    | hdog Timer              | •                                        |            |            |            |       |

| Clock frequency                                                    | FCLK                    |                                          |            | 32         |            | kHz   |

| Watchdog timer                                                     | twdt                    | Programmable, REG05h,<br>bits[5:4] = 11  |            | 160        |            | s     |

#### Note:

6) Guaranteed by design.

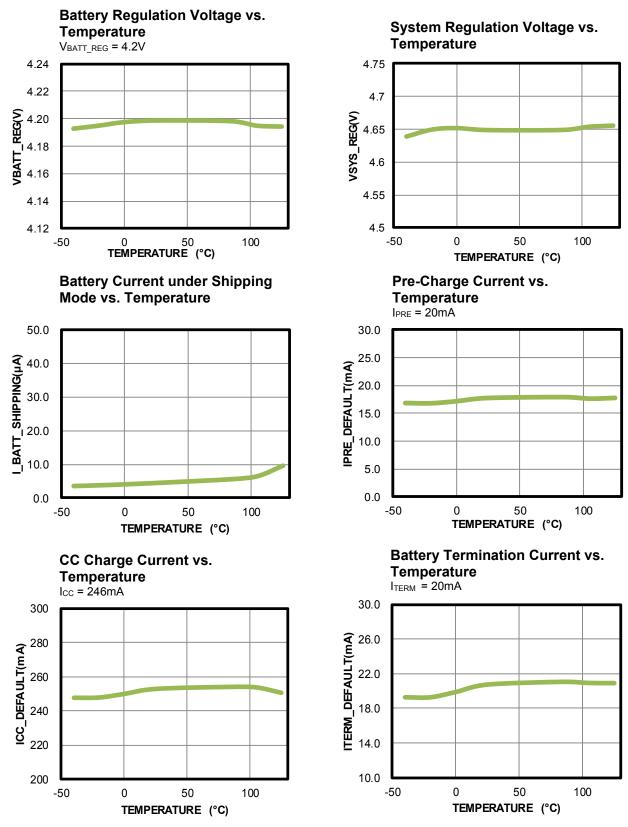

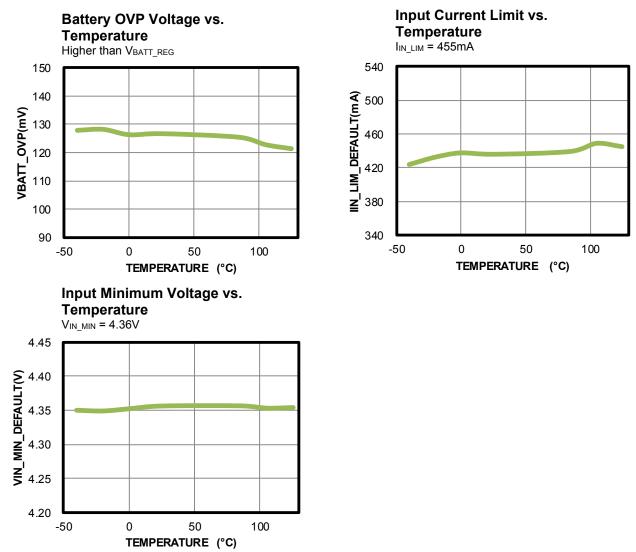

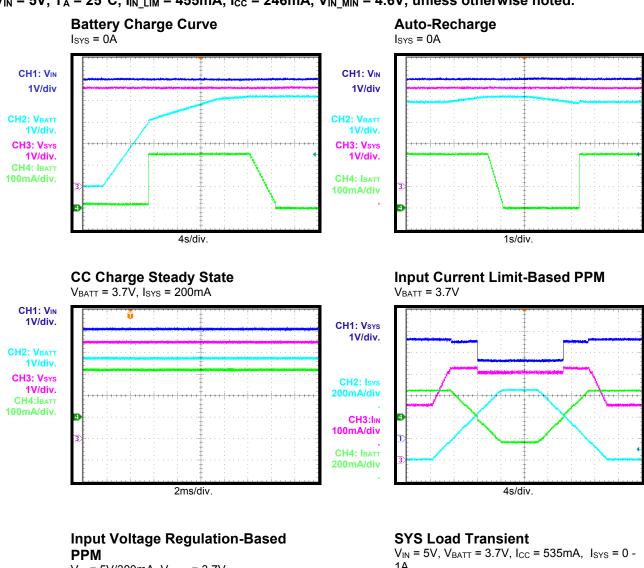

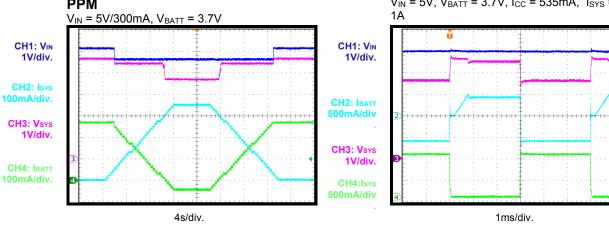

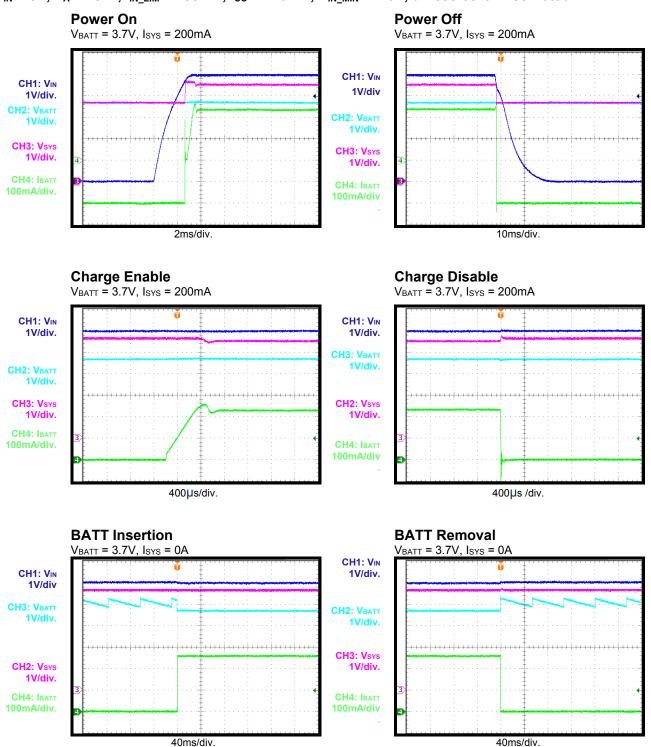

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN}$  = 5V,  $T_A$  = 25°C,  $I_{IN\_LIM}$  = 455mA,  $I_{CC}$  = 246mA,  $V_{IN\_MIN}$  = 4.6V, unless otherwise noted.

MP2664 Rev. 1.1 6/3/2021 MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

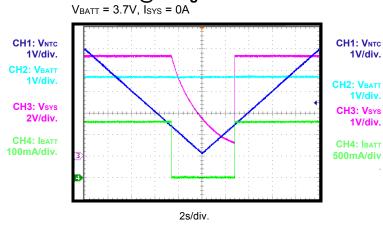

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_A = 25^{\circ}C$ ,  $I_{IN\_LIM} = 455mA$ ,  $I_{CC} = 246mA$ ,  $V_{IN\_MIN} = 4.6V$ , unless otherwise noted.

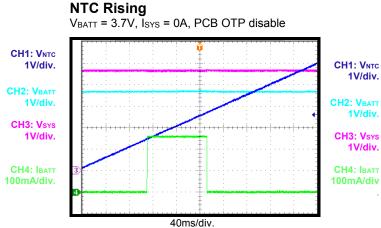

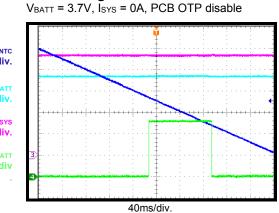

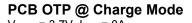

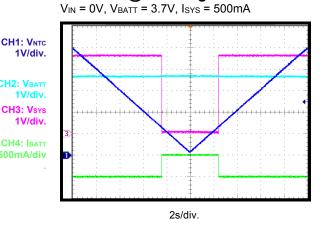

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C,  $I_{IN\_LIM}$  = 455mA,  $I_{CC}$  = 246mA,  $V_{IN\_MIN}$  = 4.6V, unless otherwise noted.

MP2664 Rev. 1.1 6/3/2021

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

11

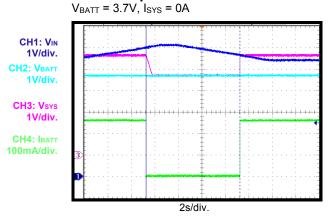

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_A = 25^{\circ}C$ ,  $I_{IN\_LIM} = 455mA$ ,  $I_{CC} = 246mA$ ,  $V_{IN\_MIN} = 4.6V$ , unless otherwise noted.

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN} = 5V$ ,  $T_A = 25^{\circ}C$ ,  $I_{IN\_LIM} = 455mA$ ,  $I_{CC} = 246mA$ ,  $V_{IN\_MIN} = 4.6V$ , unless otherwise noted.

**NTC Falling**

PCB OTP @ Discharge Mode

### **VIN OVP Operation**

mps

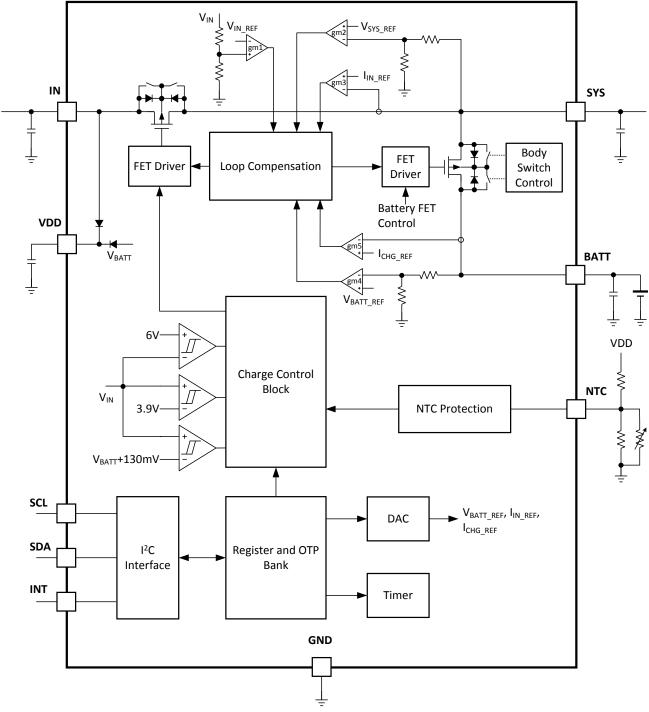

# FUNCTIONAL BLOCK DIAGRAM

Figure 2: Function Block Diagram

## **OPERATION**

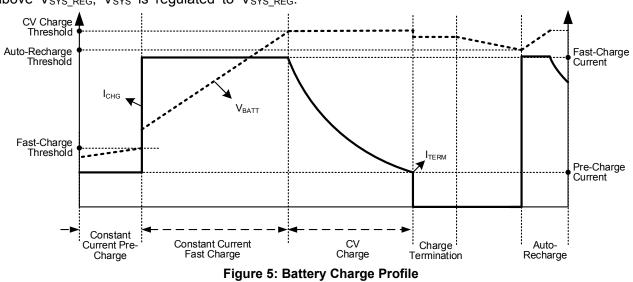

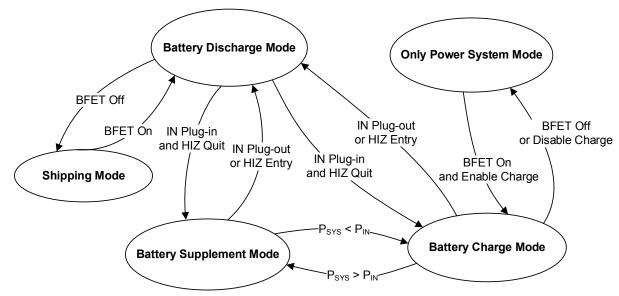

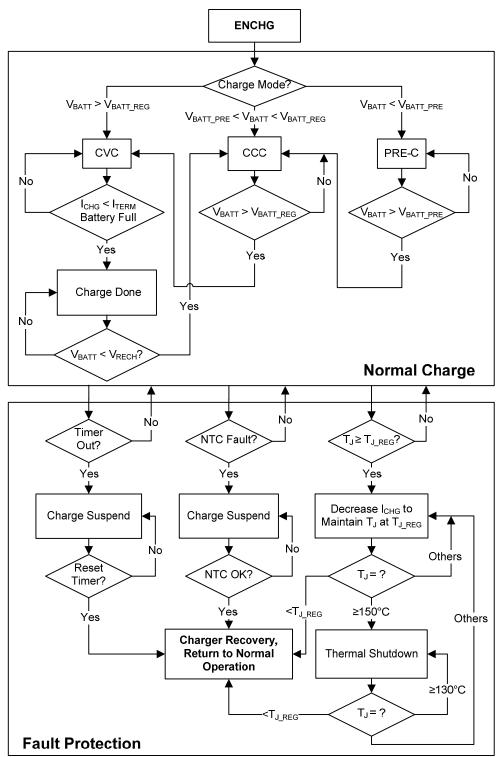

The MP2664 is an I<sup>2</sup>C-controlled, single-cell, Liion or Li-polymer battery charger with complete power path management. The full-charge function features constant current pre-charge (PRE-C), constant current fast-charge (CC) and constant voltage (CV) regulation, charge termination, auto-recharge, and a built-in timer. The power path function allows the input source to power the system and charge the battery simultaneously. If there is a conflict in meeting both the system load and battery charging current, the IC reduces the charging current automatically or uses the battery as a supplemental power to satisfy the system load.

The IC integrates a  $300m\Omega$  low-dropout (LDO) FET between IN and SYS and a  $100m\Omega$  battery FET between SYS and BATT.

In charging mode, the on-chip  $100m\Omega$  battery FET works as a full-featured linear charger with constant current pre-charging, constant current fast-charging and constant-voltage charging, charge termination, auto-recharging, NTC monitoring, built-in timer control, and thermal protection. The charge current can be programmed via the l<sup>2</sup>C interface. The IC limits the charge current when the die temperature exceeds the thermal regulation threshold (120°C default).

In supplement mode, the  $100m\Omega$  battery FET is fully turned on to connect the battery to the system load when the input power is not enough to power the system load. When the input is removed, the  $100m\Omega$  battery FET is also fully turned on, allowing the battery to power up the system.

When the system load is satisfied, the remaining current is used to charge the smart power path management battery. The IC reduces the charging current or uses power from the battery to satisfy the system load when its demand is over the input power capacity.

Figure 3 shows the power path management structure of the MP2664.

Figure 3: Power Path Management Structure

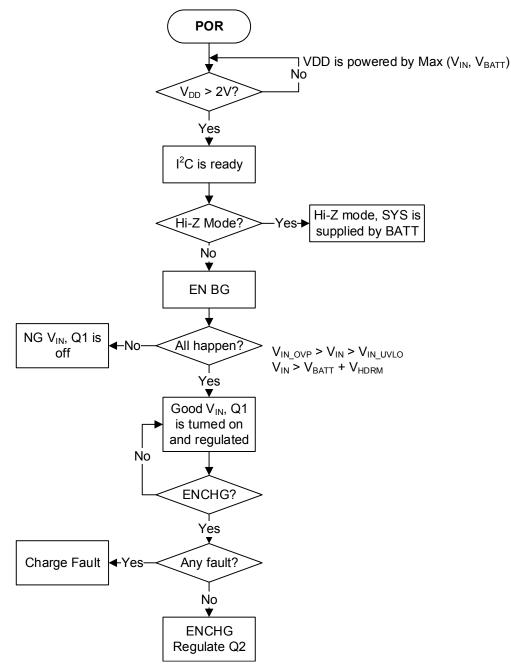

### **Power Supply**

The internal bias circuit of the IC is powered from IN or BATT, whichever voltage is higher. When IN or BATT exceeds the respective under-voltage lockout (UVLO) threshold, the sleep comparator, battery depletion comparator, and the battery FET driver are active. The I<sup>2</sup>C interface is ready for communication, and all registers are reset to the default value. The host can access all registers.

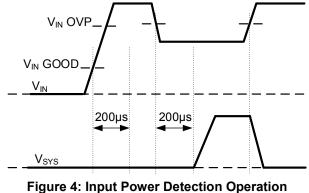

### Input OVP and UVLO

The MP2664 has an input over-voltage protection (OVP) threshold and an input UVLO threshold. Once the input voltage ( $V_{IN}$ ) exits the normal input voltage range, the Q1 FET is turned off immediately.

When  $V_{IN}$  is identified as a good source, a 200µs immunity timer becomes active. If  $V_{IN}$  is still sufficient until the 200µs timer expires, the system starts up. Otherwise, Q1 remains off.

Figure 4 depicts the operation profile.

Profile

### **Power Path Management**

The IC employs a direct power path structure with the battery FET, which decouples the system from the battery and allows for separate control between the system and the battery. The system is given priority to start up even with a deeply discharged or missing battery. When the input power is available, even with a depleted battery, the system voltage ( $V_{SYS}$ ) is always regulated to  $V_{SYS\_REG}$  by the integrated LDO FET.

The direct power structure is composed of a frond-end LDO FET between IN and SYS and a battery FET between SYS and BATT (see Figure 3). The LDO FET and battery FET can be controlled by the  $I^2C$ .

| FET On/Off                   | Hi-Z Mode and Charge Contr |              |  |

|------------------------------|----------------------------|--------------|--|

| Changed By<br>Control        | Set EN_HIZ to 1            | Set CEB to 1 |  |

| LDO FET                      | OFF                        | Х            |  |

| Battery FET<br>(charging)    | х                          | OFF          |  |

| Battery FET<br>(discharging) | х                          | х            |  |

Table 1: FET Control by I<sup>2</sup>C

The input LDO (using an LDO FET) provides power to the system, which drives the system load directly and charges the battery through the battery FET.

For the system voltage control, when  $V_{IN}$  is above  $V_{SYS\_REG}$ ,  $V_{SYS}$  is regulated to  $V_{SYS\_REG}$ .

When  $V_{IN}$  is below  $V_{SYS\_REG}$ , the LDO FET is fully on with the input current limit.

#### **Battery Charge Profile**

The IC provides three main charging phases: constant current pre-charge, constant current fast-charge, and constant-voltage charge (see Figure 5).

- 1. Phase 1 (constant current pre-charge): The IC is able to pre-charge the deeply depleted battery safely until the battery voltage (V<sub>BATT</sub>) reaches the pre-charge to the fast-charge pre-charge threshold The  $(V_{BATT PRE}).$ current is programmable via REG03h, bits[1:0]. If V<sub>BATT\_PRE</sub> is not reached before the pre-charge timer (1hr) expires, the charge cvcle is stopped. and а corresponding timeout fault signal is asserted.

- <u>Phase 2 (constant current fast charge)</u>: When V<sub>BATT</sub> exceeds V<sub>BATT\_PRE</sub>, the IC enters a constant current fast-charge phase. The fast-charge current can be programmable via REG02h, bits[4:0].

- <u>Phase 3 (constant-voltage charge)</u>: When V<sub>BATT</sub> rises to the pre-programmable charge full voltage (V<sub>BATT\_REG</sub>) set via REG04h, bits[7:2], the charge mode changes from CC mode to CV mode, and the charge current begins to taper off.

Assuming that the termination function  $(EN_TERM)$  is set via REG05h, bit[6] = 1, the charge cycle is considered to be complete when the following conditions are valid:

- The charge current (I<sub>BATT</sub>) reaches the end of charge (EOC) current threshold (I<sub>TERM</sub>), and the 2.5ms delay timer is initiated.

- During the 2.5ms delay period, I<sub>BATT</sub> is always smaller than I<sub>TERM</sub> + I<sub>TERM\_HYS</sub>.

The charge status is marked as complete once the 2.5ms delay timer expires.

The charge current is terminated at the same time if TERM\_TMR is set via REG05h, bit[0] = 0; otherwise, the charge current continues tapering off.

If  $EN_TERM = 0$ , the termination function is disabled, and the above actions will not occur (see Table 2).

Table 2: Termination Function Selection Table

| EN TERM | TERM TMR | After I <sub>BATT</sub><br>Iterm in C |                  |

|---------|----------|---------------------------------------|------------------|

|         |          | Operation                             | Charge<br>Status |

| 0       | х        | Keep CV<br>charge                     | Charge           |

| 1       | 0        | Charge complete                       | Charge complete  |

| 1       | 1        | Keep CV<br>charge                     | Charge complete  |

During the charging process, the actual charge current may be less than the register setting due to other loop regulations, such as dynamic power management (DPM) regulation (input voltage, input current) or thermal regulation. If the input current ( $I_{IN}$ ) or  $V_{IN}$  reach their limits during the CV charge, the charge-full termination is not influenced when the charge current is not as close to the EOC current specification.

A new charge cycle starts once all of the following conditions are valid:

- The input power is recycled

- Battery charging is enabled by the I<sup>2</sup>C

- Auto-recharge kicks in

- No thermistor fault at NTC

- No safety timer fault

- No battery over-voltage

- BATT FET is not forced to turn off

### Automatic Recharge

When the battery is fully charged and the charging is terminated, the battery may be discharged due to system consumption or self-discharge. When  $V_{BATT}$  is discharged below the recharge threshold and  $V_{IN}$  is still in the operation range, the IC begins another new charging cycle automatically without having to restart the charging cycle manually.

The auto-recharge function is valid only when  $EN_TERM = 1$  and  $TERM_TMR = 0$ .

### Battery Over-Voltage Protection (OVP)

The IC is designed with a built-in battery overvoltage (OV) limit about 130mV above  $V_{\text{BATT}_{REG}}$ . When a battery OV event occurs, the IC suspends charging immediately and asserts a fault.

# Input Current and Input Voltage-Based Power Management

To meet the input source (typically USB) maximum current-limit specification, the IC uses input current-based power management by monitoring  $I_{IN}$  continuously. The total  $I_{IN}$  limit can be programmed via the  $I^2C$  to prevent the input source from overloading.

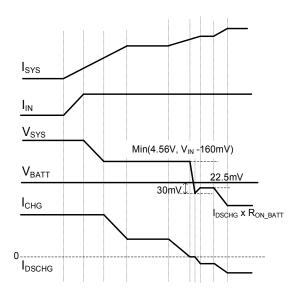

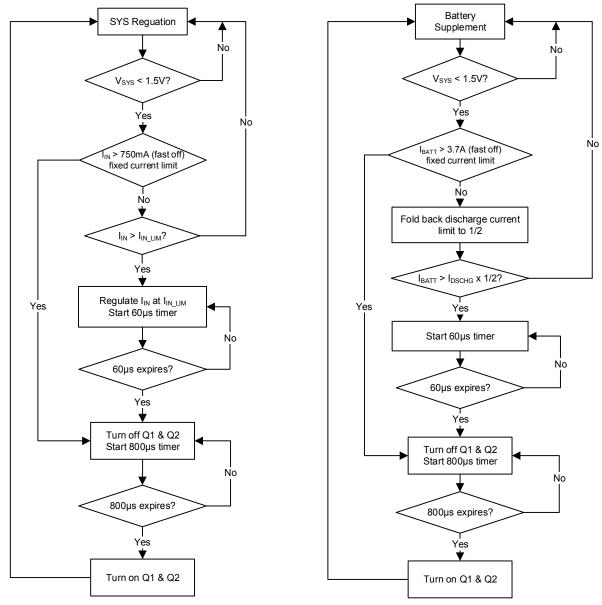

If the pre-set  $I_{IN}$  limit is greater than the input source rating, back-up  $V_{IN}$ -based power management also works to prevent the input source from being overloaded. If either the  $I_{IN}$  limit or the  $V_{IN}$  limit is reached, the Q1 FET between IN and SYS are regulated so that the total input power is limited. As a result,  $V_{SYS}$  drops. Once the system declines to the minimum value of 4.56V or  $V_{IN}$  -160mV, the charge current is reduced to prevent  $V_{SYS}$  from dropping further.

Voltage-based DPM regulates  $V_{IN}$  to  $V_{IN\_MIN}$  when the load is over the input power capacity.  $V_{IN\_MIN}$  set via the I<sup>2</sup>C should be at least 400mV higher than  $V_{BATT\_REG}$  to ensure stable operation of the regulator.

.1 MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

### **Battery Supplement Mode**

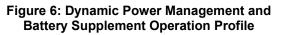

The charge current is reduced to keep the I<sub>IN</sub> or  $V_{IN}$  in regulation when DPM occurs. If the charge current is 0A and the input source is still overloaded due to a heavy system load, then  $V_{SYS}$  starts to fall off. Once  $V_{SYS}$  falls below V<sub>BATT</sub>, the IC enters battery supplement mode. When V<sub>SYS</sub> is 30mV below V<sub>BATT</sub>, ideal diode mode is enabled. The battery FET is regulated to maintain  $V_{BATT}$  -  $V_{SYS}$  at 22.5mV. If the supplement current I<sub>DSCHG</sub> x R<sub>ON\_BATT</sub> is above 22.5mV, the battery FET is fully turned on to keep the ideal forward voltage. When the system load decreases, once V<sub>SYS</sub> exceeds V<sub>BATT</sub> + 20mV, ideal diode mode is disabled. Figure 6 shows the dynamic power management and battery supplement mode operation profile.

When  $V_{IN}$  is not available, the IC operates in discharge mode, and the battery FET is always fully on to reduce loss.

### **Battery Regulation Voltage**

The battery voltage for the constant-voltage regulation phase is  $V_{BATT\_REG}$ . When  $V_{BATT\_REG}$  is

4.2V, it has a  $\pm 0.5\%$  accuracy across the ambient temperature range of 0°C to 50°C. When the battery is removed, the battery voltage is between V<sub>BATT\_REG</sub> - V<sub>RECH</sub> and V<sub>BATT\_REG</sub>.

#### **Thermal Regulation and Thermal Shutdown**

The IC continuously monitors the internal junction temperature to maximize power delivery and prevent the chip from overheating. When the internal junction temperature reaches the preset limit of T<sub>J REG</sub> (default 120°C), the IC reduces the charge current to prevent higher dissipation. multiple power The thermal regulation thresholds from 60°C to 120°C help the system design meet the thermal requirement in different applications. The junction temperature regulation threshold can be set via REG06h, bits[1:0].

If the junction temperature reaches 150°C, both Q1 and Q2 are turned off.

#### Negative Temperature Coefficient (NTC) Temperature Sensor

NTC allows the IC to sense the battery temperature using the thermistor (typically available in the battery pack) to ensure a safe operating environment for the chip. A resistor with an appropriate value should be connected from VDD to NTC, and the thermistor should be connected from NTC to ground. The voltage on NTC is determined by the resistor divider, whose divide ratio depends on the temperature. The IC sets a predetermined upper and lower bound of the divide ratio internally for NTC cold and NTC hot. In the MP2664, the I<sup>2</sup>C default setting is the PCB OTP. The function can be changed through the I<sup>2</sup>C (see Table 3).

#### Table 3: NTC Function Selection Table

| l <sup>2</sup> C | Control    | Function |  |  |

|------------------|------------|----------|--|--|

| EN_NTC           | EN_PCB OTP | Function |  |  |

| 0                | х          | Disabled |  |  |

| 1                | 1          | NTC      |  |  |

| 1                | 0          | PCB OTP  |  |  |

When PCB OTP is selected, if the NTC voltage  $(V_{NTC})$  is below the NTC hot threshold, both the LDO FET and battery FET are turned off. The PCB OTP fault sets the NTC FAULT status (REG08h, bit[1]) to 1 to indicate the fault. Operation resumes once  $V_{NTC}$  exceeds the NTC hot threshold.

The NTC function only works in charge mode. Once  $V_{NTC}$  goes out of the divide ratio (the temperature is outside the safe operating range), the IC stops the charging and reports it on the status bits. Charging resumes automatically once the temperature returns to within the safe range.

### Safety Timer

The IC provides both a pre-charge and a fastcharge safety timer to prevent extended charging cycles due to abnormal battery conditions. The safety timer is 1 hour when VBATT is below VBATT PRE. The fast-charge safety timer begins when the battery enters constant current fast charging. The fast-charge safety timer can be programmed via the I<sup>2</sup>C. The safety timer feature can be disabled via the  $I^2C$ .

The following actions can restart the safety timer:

- A new charge cycle is initiated .

- Charge enable toggling •

- Hi-Z disable toggling

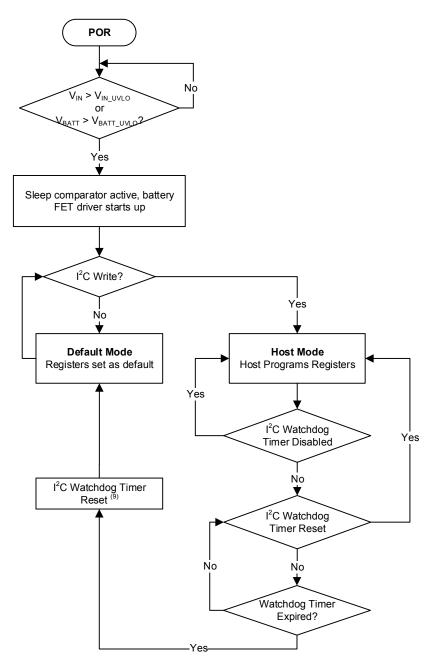

### Host Mode and Default Mode

The IC is a host-controlled device. After the power-on reset (POR), the IC starts in the watchdog timer expiration state or default mode. All of the registers are in the default settings.

Any write to the IC changes it to host mode. All charge parameters are programmable. If the watchdog timer (REG05h, bits[5:4]) is not disabled, the host must reset the watchdog timer regularly by writing 1 to the REG01h, bit[6] before the watchdog timer expires to keep the device in host mode. Once the watchdog timer expires, the IC returns to default mode. The watchdog timer limit can also be programmed or disabled by the host control. When there is no V<sub>IN</sub>, the watchdog timer is suspended (see Figure 19 on page 31).

The operation can also be changed to default mode when one of the following conditions occur:

- Refresh input without battery •

- Re-insert battery with no VIN •

- Register reset REG01h, bit[7] is reset

### **Battery Discharge Function**

If battery is connected and the input source is missing, the battery FET is fully on once V<sub>BATT</sub> is above the  $V_{BATT UVLO}$  threshold. The  $100m\Omega$ battery FET minimizes conduction loss during discharge. The quiescent current of the IC is as low as 11µA in this mode. The low on resistance and low quiescent current help extend the running time of the battery.

### **Over-Discharge Current Protection**

The IC has an over-discharge current protection in discharge mode and supplement mode. Once exceeds the programmable IBATT discharge current limit (default 2A), the battery FET turns off after a 60µs delay, and the MP2664 enters hiccup mode in over-current protection (OCP). The discharge current can be programmed high to 3.2A via the I<sup>2</sup>C. If the discharge current goes high to reach the internal fixed current limit (about 3.7A), the battery FET is turned off and starts hiccup mode immediately.

Similarly, when  $V_{BATT}$ falls below the programmable V<sub>BATT UVLO</sub> threshold (default 2.8V), the battery FET is turned off to prevent over-discharge.

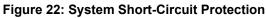

### System Short-Circuit Protection (SCP)

The MP2664 features SYS node short-circuit protection (SCP) for the IN to SYS path and the BATT to SYS path.

V<sub>SYS</sub> is monitored continuously. If V<sub>SYS</sub> is below 1.5V, the system (SCP) for the IN to SYS path and the BATT to SYS path are active. IDSCHG is decreased to half of its original value.

1) IN to SYS path: Once I<sub>IN</sub> exceeds the protection threshold, both the LDO FET and the battery FET are turned off immediately, and the IC enters hiccup mode. Otherwise, the max current limit and the setting input current limit are not reached, and  $I_{IN}$  is regulated at I<sub>IN LIM</sub>.

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

Hiccup mode also starts after a 60µs delay. The hiccup mode interval is 800µs.

<u>BATT to SYS path:</u> Once I<sub>BATT</sub> exceeds the 3.7A protection threshold, both the LDO FET and the battery FET are turned off immediately, and the IC enters hiccup mode. When the battery discharge current limit threshold is reached, hiccup mode starts after a 60µs delay. The hiccup mode interval is 800µs.

If a system short-circuit occurs when both the input and battery are present, the protection mechanism of both paths work, with the faster one dominating the hiccup operation (see Figure 22 on page 34).

### Interrupt to Host (INT)

The IC has an alert mechanism that can output an interrupt signal via INT to notify the system of the operation by outputting a 256µs low-state INT pulse. Any of the below events can trigger the INT output:

- Good input source detected(PG\_STAT)

- Charge completed

- Charging status change

- Any fault in REG08h (watchdog timer fault, input fault, thermal fault, safety timer fault, battery OVP fault, NTC fault)

When any fault occurs, the IC sends out an INT pulse and latches the fault state in REG08h. After the IC exits the fault state, the fault bit can be released to 0 after the host reads REG08h. The NTC fault is not latched and always reports the current thermistor conditions.

Note that the INT needs the external pull-up resistor for its open-drain connection. The resistance should not be below  $300k\Omega$ .

### Battery Disconnect Function

In applications where the battery is not removable, it is essential to disconnect the battery from the system for two reasons: to prevent excessive capacity discharge when the device is in shipping or storage mode, and to allow the system power to reset.

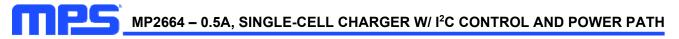

The MP2664 provides both shipping mode and system reset mode for different application requirements.

Register bit FET\_DIS (REG06h, bit[5]), allows the IC to enter shipping mode. During normal operation, the battery FET is turned on, and this bit is 0. If this bit is set to 1 via the I<sup>2</sup>C, the battery FET is turned off and the MP2664 enters shipping mode. The FET\_DIS bit is reset to 0 automatically after the battery FET is turned off (see Figure 7).

The IC can exit shipping mode by pulling INT down. When the IC is in shipping mode and only the battery is present, pull INT down by pushing the push button (PB) to wake the MP2664 up from shipping mode (see Table 4 on page 21).

Figure 7: Time Delay from When FET\_DIS Is Written to 1 to the Battery FET Turning Off

Table 4: Exit the Shipping Mode with BATT Present Only

|        | INT Signal                                    | IC Exits<br>Shipping Mode |

|--------|-----------------------------------------------|---------------------------|

| Case 1 | INT = low twice with the rising edge >600ns   | At once                   |

| Case 2 | INT = low once with the rising edge >600ns    | After 4s                  |

| Case 3 | INT = low for 4s                              | After 4s                  |

| Case 4 | INT = low with the<br>rising edge in ms level | At once                   |

The MP2664 can also wake up from shipping mode when a valid  $V_{IN}$  powers on (see Table 5). After  $V_{IN}$  is preset, the MP2664 pulls INT low to indicate the event "Good input source detected" if  $V_{IN}$  is in the operating range. Then, the MP2664 can be woken up from shipping mode by the INT signal (see Figure 8).

Table 5: Exiting Shipping Mode when  $V_{IN}$  Powers On

|        | INT Signal                                    | IC Exits<br>Shipping Mode |

|--------|-----------------------------------------------|---------------------------|

| Case 1 | INT = low twice with the rising edge >600ns   | At once                   |

| Case 2 | INT = low once with the rising edge >600ns    | After 4s                  |

| Case 3 | INT = low with the<br>rising edge in ms level | At once                   |

If FET\_DIS is set to 1 during shipping mode, the IC can wake up after keeping INT low for 4s. In this case, the FET\_DIS bit cannot be reset to 0 automatically, it must be reset to 0 manually via the  $I^2C$ .

The IC can use INT to cut off the path from the battery to the system when a system reset is needed.

Once the logic at INT is set to low for more than 16s, the battery is disconnected from the system by turning off the battery FET.

The off state lasts for 4s, and then the battery FET is turned on automatically. The system is powered by the battery again. During the 4s off period, the INT pin voltage level can be high or low. The IC can reset the system by controlling INT (see Figure 9).

Figure 8: INT Signal during V<sub>IN</sub> Power On

Figure 9: System Reset Function Operation Profile

### I<sup>2</sup>C Serial Interface

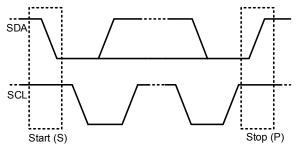

The IC uses an I<sup>2</sup>C serial interface for flexible charging parameter setting and instantaneous device status reporting. The I<sup>2</sup>C is a two-wire serial interface with two bus lines required: a serial data line (SDA) and a serial clock line (SCL). Both SDA and SCL lines are open-drain and need to be connected to the positive supply voltage via a pull-up resistor.

The IC operates as a slave device, receiving control inputs from the master device such as a micro-controller. The SCL line is always driven by the master device. The I<sup>2</sup>C interface supports both standard mode (up to 100 kbit/s), and fast mode (up to 400 kbit/s).

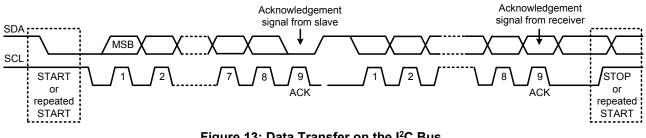

All transactions begin with a start (S) command and are terminated by a stop (P) command. Start and stop commands are always generated by the master. A high to low transition on the SDA line while SCL is high defines a start command. A low to high transition on the SDA line when the SCL is high defines a stop command.

Figure 10: START and STOP Conditions

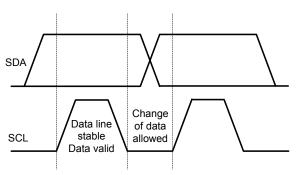

For data validity, the data on the SDA line must be stable during the high period of the clock. The high or low state of the SDA line can only change when the clock signal on the SCL line is low. Every byte on the SDA line must be 8 bits long. The number of bytes to be transmitted per transfer is unrestricted. Data is transferred with the most significant bit (MSB) first.

Figure 11: Bit Transfer on the I<sup>2</sup>C Bus

Each byte has to be followed by an acknowledge (ACK) bit, which is generated by the receiver, to signal to the transmitter that the byte was successfully received.

The ACK signal is defined as the transmitter releasing the SDA line during the acknowledge clock pulse so that the receiver can pull the SDA line low. This line remains low during the high period of the 9th clock pulse.

If SDA line is high during the 9th clock pulse, this is defined as the not acknowledge (NACK) signal. The master can then generate either a stop to abort the transfer or a repeated start (Sr) to start a new transfer.

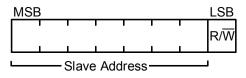

After the start signal, a slave address is sent. This address is 7 bits long, followed by an 8th data direction bit (bit R/W). A 0 indicates a transmission (write), and a 1 indicates a request for data (read). The address bit arrangement is shown below.

Figure 12: 7-Bit Address

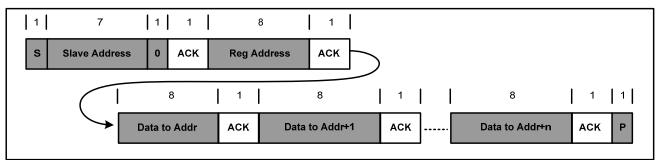

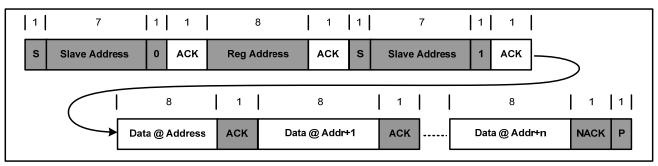

See Figure 13, Figure 14, Figure 15, Figure 16, and Figure 17 on page 23 for detailed signal sequences.

## Figure 13: Data Transfer on the I<sup>2</sup>C Bus

| 1 | 7             | 1 | 1   | 8           | 1   | 8            | 1   | 1 |

|---|---------------|---|-----|-------------|-----|--------------|-----|---|

| s | Slave Address | 0 | АСК | Reg Address | АСК | Data Address | АСК | Р |

### Figure 14: Single Write

| 1 7             | 1 | 1   | 8           | 1   | 1 | 7             | 1 | 1   | 8    | 1   1  |

|-----------------|---|-----|-------------|-----|---|---------------|---|-----|------|--------|

| S Slave Address | 0 | АСК | Reg Address | АСК | S | Slave Address | 1 | ACK | Data | NACK P |

### Figure 15: Single Read

#### Figure 16: Multi-Write

#### Figure 17: Multi-Read

# I<sup>2</sup>C REGISTER MAP

IC Address: 09h (reserved some trim options)

### Input Source Control Register/Address: 00h (Default: 0100 1111)

| Bit         | Symbol                  | Description                            | Read/Write | Default                                                        |  |

|-------------|-------------------------|----------------------------------------|------------|----------------------------------------------------------------|--|

| Bit 7       | EN_HIZ <sup>(7)</sup>   | 0: Disable<br>1: Enable                | R/W        | Disable (0)                                                    |  |

| Input Minim | um Voltage Regulation   | n                                      |            |                                                                |  |

| Bit 6       | Vin_min [3]             | 640mV                                  |            |                                                                |  |

| Bit 5       | Vin_min [2]             | 320mV                                  |            | Offset: 3.88V<br>Range: 3.88V - 5.08V<br>Default: 4.60V (1001) |  |

| Bit 4       | Vin_min [1]             | 160mV                                  | R/W        |                                                                |  |

| Bit 3       | Vin_min [0]             | 80mV                                   |            |                                                                |  |

| Input Curre | nt Limit                |                                        |            |                                                                |  |

| Bit 2       | I <sub>IN_LIM</sub> [2] | 000: 85mA<br>001: 130mA<br>010: 175mA  |            | 455mA (111)                                                    |  |

| Bit 1       | Iin_lim [1]             | 011: 220mA<br>100: 265mA               | R/W        |                                                                |  |

| Bit 0       | Iin_lim [0]             | 101: 310mA<br>110: 355mA<br>111: 455mA |            |                                                                |  |

Note:

7) This bit only controls the on and off of the LDO FET.

### Power-On Configuration Register/Address: 01h (Default: 0000 0100)

| Bit         | Symbol                                   | Description                           | Read/Write | Default                  |

|-------------|------------------------------------------|---------------------------------------|------------|--------------------------|

| Bit 7       | Register reset                           | 0: Keep current setting<br>1: Reset   | R/W        | Keep current setting (0) |

| Bit 6       | I <sup>2</sup> C watchdog timer<br>reset | 0: Normal<br>1: Reset                 | R/W        | Normal (0)               |

| Bit 5       | Reserved                                 |                                       | R/W        | Reserved                 |

| Bit 4       | Reserved                                 |                                       | R/W        | Reserved                 |

| Charger Co  | onfiguration                             |                                       |            |                          |

| Bit 3       | CEB                                      | 0: Charge enable<br>1: Charge disable | R/W        | Charge enable (0)        |

| Battery UVI | _O Threshold                             |                                       |            |                          |

| Bit 2       | VBATT_UVLO [2]                           | 0.4V                                  |            | Offset: 2.4V             |

| Bit 1       | VBATT_UVLO [1]                           | 0.2V                                  | R/W        | Range: 2.4V - 3.1V       |

| Bit 0       | VBATT_UVLO [0]                           | 0.1V                                  |            | Default: 2.8V (100)      |

| Bit     | Symbol               | Description | Read/Write | Default                           |  |

|---------|----------------------|-------------|------------|-----------------------------------|--|

| Bit 7   | Reserved             |             | R/W        | Reserved                          |  |

| Bit 6   | Reserved             |             | R/W        | Reserved                          |  |

| Bit 5   | Reserved             |             | R/W        | Reserved                          |  |

| Fast-Ch | arge Current Setting | ·           | ·          |                                   |  |

| Bit 4   | Icc [4]              | 272mA       |            |                                   |  |

| Bit 3   | Icc [3]              | 136mA       |            | Offset: 8mA<br>Range: 8mA - 535mA |  |

| Bit 2   | Icc [2]              | 68mA        | R/W        |                                   |  |

| Bit 1   | Icc [1]              | 34mA        |            | Default: 246mA<br>(01110)         |  |

| Bit 0   | I <sub>CC</sub> [0]  | 17mA        |            |                                   |  |

### Charge Current Control Register/Address: 02h (Default: 0000 1110)

### Pre-Charge/Termination Current/Address: 03h (Default: 0100 1010)

| Bit        | Symbol                  | Description             | Read/Write | Default                                                                                            |

|------------|-------------------------|-------------------------|------------|----------------------------------------------------------------------------------------------------|

| Bit 7      | Reserved                |                         | R/W        | Reserved                                                                                           |

| BATT to S  | YS Discharge Current Li | mit                     |            |                                                                                                    |

| Bit 6      | Ідзенд [3]              | 1600mA                  |            | Offset: 200mA                                                                                      |

| Bit 5      | Idschg [2]              | 800mA                   | DAAK       | Range: 400mA - 3.2A<br>Valid range: 0001 -                                                         |

| Bit 4      | I <sub>DSCHG</sub> [1]  | 400mA                   | R/W        | 1111<br>Default: 2000mA<br>(1001)                                                                  |

| Bit 3      | Idschg [0]              | 200mA                   |            |                                                                                                    |

| PCB OTP    | Enable                  |                         | -          |                                                                                                    |

| Bit 2      | EN_PCB OTP              | 0: Enable<br>1: Disable | R/W        | Enable(0)                                                                                          |

| Pre-Charge | e Current               |                         |            |                                                                                                    |

| Bit 1      | I <sub>PRE</sub> [1]    | 14mA                    |            | Offset: 6mA                                                                                        |

| Bit 0      | Ipre [0]                | 7mA                     | R/W        | Range: 6mA - 27mA<br>Default: 20mA (10)<br>I <sub>PRE</sub> [1:0] also sets<br>termination current |

| Bit         | Symbol                                                    | Description          | Read/Write | Default                             |  |  |  |  |

|-------------|-----------------------------------------------------------|----------------------|------------|-------------------------------------|--|--|--|--|

| Battery Reg | Battery Regulation Voltage                                |                      |            |                                     |  |  |  |  |

| Bit 7       | VBATT_REG [5]                                             | 480mV                |            |                                     |  |  |  |  |

| Bit 6       | VBATT_REG [4]                                             | 240mV                |            | Offset: 3.60V                       |  |  |  |  |

| Bit 5       | VBATT_REG [3]                                             | 120mV                | R/W        | Range: 3.60V -<br>4.545V            |  |  |  |  |

| Bit 4       | VBATT_REG [2]                                             | 60mV                 |            | 4.343V<br>Default: 4.2V<br>(101000) |  |  |  |  |

| Bit 3       | VBATT_REG [1]                                             | 30mV                 |            |                                     |  |  |  |  |

| Bit 2       | VBATT_REG [0]                                             | 15mV                 |            |                                     |  |  |  |  |

| Pre-Charge  | e to Fast Charge Thres                                    | hold                 |            |                                     |  |  |  |  |

| Bit 1       | VBATT_PRE                                                 | 0: 2.8V<br>1: 3.0V   | R/W        | 3.0V (1)                            |  |  |  |  |

| Battery Red | Battery Recharge Threshold (below V <sub>BATT_REG</sub> ) |                      |            |                                     |  |  |  |  |

| Bit 0       | VRECH                                                     | 0: 150mV<br>1: 300mV | R/W        | 300mV (1)                           |  |  |  |  |

### Charge Voltage Control Register/Address: 04h (Default: 1010 0011)

### Charge Termination/Timer Control Register/Address: 05h (Default: 0100 1010)

| Bit                     | Symbol                                                                                                                    | Description                                         | Read/Write | Default            |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|--------------------|--|--|--|--|

| Bit 7                   | Reserved                                                                                                                  |                                                     | R/W        | Reserved           |  |  |  |  |

| Terminatior             | n Setting (the terminati                                                                                                  | on is allowed or not)                               |            |                    |  |  |  |  |

| Bit 6                   | EN_TERM                                                                                                                   | 0: Disable<br>1: Enable                             | R/W        | Enable (1)         |  |  |  |  |

| I <sup>2</sup> C Watchd | og Timer Limit                                                                                                            |                                                     |            |                    |  |  |  |  |

| Bit 5                   | WATCHDOG [1]                                                                                                              | 00: Disable timer<br>01: 40s<br>10: 80s<br>11: 160s | R/W        | Disable timer (00) |  |  |  |  |

| Bit 4                   | WATCHDOG [0]                                                                                                              |                                                     |            |                    |  |  |  |  |

| Safety Time             | Safety Timer Setting                                                                                                      |                                                     |            |                    |  |  |  |  |

| Bit 3                   | EN_TIMER                                                                                                                  | 0: Disable<br>1: Enable                             | R/W        | Enable timer (1)   |  |  |  |  |

| Fast-Charg              | e Timer                                                                                                                   |                                                     |            |                    |  |  |  |  |

| Bit 2                   | CHG_TMR [1]                                                                                                               | 00: 3hrs<br>01: 5hrs                                | R/W        | 5hrs (01)          |  |  |  |  |

| Bit 1                   | CHG_TMR [0]                                                                                                               | 10: 8hrs<br>11: 12hrs                               | 10,00      | Shi's (UT)         |  |  |  |  |

|                         | Termination Timer Control (when TERM_TMR is enabled, the IC will not suspend the charge current after charge termination) |                                                     |            |                    |  |  |  |  |

| Bit 0                   | TERM_TMR                                                                                                                  | 0: Disable<br>1: Enable                             | R/W        | Disable (0)        |  |  |  |  |

| Bit        | Symbol                 | Description                                                                                           | Read/Write | Default    |

|------------|------------------------|-------------------------------------------------------------------------------------------------------|------------|------------|

| Bit 7      | Reserved               |                                                                                                       | R/W        | Read/write |

| Bit 6      | TMR2X_EN               | 0: Disable 2X extended safety<br>timer during PPM<br>1: Enable 2X extended safety<br>timer during PPM | R/W        | Enable (1) |

| Bit 5      | FET_DIS <sup>(8)</sup> | 0: Enable<br>1: Turn off                                                                              | R/W        | Enable (0) |

| Bit 4      | Reserved               |                                                                                                       | R/W        | (0)        |

| Bit 3      | EN_NTC                 | 0: Disable<br>1: Enable                                                                               | R/W        | Enable (1) |

| Bit 2      | Reserved               |                                                                                                       | R/W        |            |

| Thermal Re | egulation Threshold    |                                                                                                       |            |            |

| Bit 1      | T <sub>J_REG</sub> [1] | 00: 60°C<br>01: 80°C                                                                                  | R/W        | 120°C (11) |

| Bit 0      | T <sub>J_REG</sub> [0] | 10: 100°C<br>11: 120°C                                                                                |            |            |

### Miscellaneous Operation Control Register/Address: 06h (Default: 0100 1011)

Note:

8) This bit only controls the turn off function of the battery FET, including the charging and discharging.

#### System Status Register/Address: 07h (Default: 0000 0000)

| Bit      | Symbol       | Description                                          | Read/Write | Default                                                |  |

|----------|--------------|------------------------------------------------------|------------|--------------------------------------------------------|--|

| Bit 7    | Reserved     |                                                      | R          | Reserved                                               |  |

| Revision | ·            |                                                      | ·          | ·                                                      |  |

| Bit 6    | Rev [1]      | Devision number                                      | D          | (00)                                                   |  |

| Bit 5    | Rev [0]      | Revision number                                      | R          | (00)                                                   |  |

| Bit 4    | CHG_STAT [1] | 00: Not charging<br>01: Pre-charge                   | R          | Not charging (00)                                      |  |

| Bit 3    | CHG_STAT [0] | 10: Charge<br>11: Charge done                        |            |                                                        |  |

| Bit 2    | PPM_STAT     | 0: No PPM<br>1: In PPM                               | R          | No PPM (0)<br>(no power-path<br>management<br>happens) |  |

| Bit 1    | PG_STAT      | 0: Power fail<br>1: Power good                       | R          | Power fail (0)                                         |  |

| Bit 0    | THERM_STAT   | 0: No thermal regulation<br>1: In thermal regulation | R          | No thermal regulation (0)                              |  |

| Bit   | Symbol         | Description                                        | Read/Write | Default    |

|-------|----------------|----------------------------------------------------|------------|------------|

| Bit 7 | Reserved       |                                                    | R          | Reserved   |

| Bit 6 | WATCHDOG_FAULT | 0: Normal<br>1: Watchdog timer expiration          | R          | Normal (0) |

| Bit 5 | VIN_FAULT      | 0: Normal<br>1: Input fault (OVP or bad<br>source) | R          | Normal (0) |

| Bit 4 | THEM_SD        | 0: Normal<br>1: Thermal shutdown                   | R          | Normal (0) |

| Bit 3 | BAT_FAULT      | 0: Normal<br>1: Battery OVP                        | R          | Normal (0) |

| Bit 2 | STMR_FAULT     | 0: Normal<br>1: Safety timer expiration            | R          | Normal (0) |

| Bit 1 | NTC_FAULT [1]  | 0: Normal<br>1: NTC hot                            | R          | Normal (0) |

| Bit 0 | NTC_FAULT [0]  | 0: Normal<br>1: NTC cold                           | R          | Normal (0) |

### Fault Register/Address: 08h (Default: 0000 0000)

### **ONE-TIME PROGRAMMABLE MAP**