# 36V, 6A Peak, Buck-Boost Converter with I<sup>2</sup>C Interface for Power Delivery

# **DESCRIPTION**

The MP4245 is a buck-boost converter with four integrated power switches. The device can deliver up to 6A of output current at certain input-voltage supply ranges, with excellent load and line regulation.

The MP4245 is suitable for USB power delivery (USB PD) applications. It can work with an external USB PD controller through the I<sup>2</sup>C interface. The I<sup>2</sup>C interface and two-time programmable multiple-time programmable (MTP) memory provide flexible features.

Fault condition protections includes constant current (CC) limiting, output over-voltage protection (OVP), and thermal shutdown (TSD).

The MP4245 requires a minimal number of readily available, standard external components, and is available in a QFN-21 (4mmx5mm) package.

#### **FEATURES**

- Supports 60W Buck-Boost or 6A Peak I<sub>OUT</sub>

- Wide 4V to 36V Operating Input Voltage Range

- 1V to 23V Output Voltage Range

- 250kHz, 350kHz, or 420kHz Selectable Frequency or SYNC Input

- 12mΩ/24mΩ/14mΩ/14mΩ Low R<sub>DS(ON)</sub> for Switches A, B, C, and D

- Selectable Frequency Spread Spectrum

- Line Drop Compensation

- Accurate Constant Current (CC) Output Current Limit

- I<sup>2</sup>C Interface and MTP (PMBus Compatible):

- PFM/PWM Mode, Current Limit, Output Voltage, Frequency Spread Spectrum, and Line Drop Compnsation

- CRC Calculation for MTP Integrity

- Load-Shedding Alert

- EN Shutdown Active Discharge

- Available in a QFN-21 (4mmx5mm)

Package with Wettable Flanks

#### **APPLICATIONS**

- USB Type-C with PD Charging Only Ports

- 12V Bus Voltage Supplies

- Wireless Charging

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

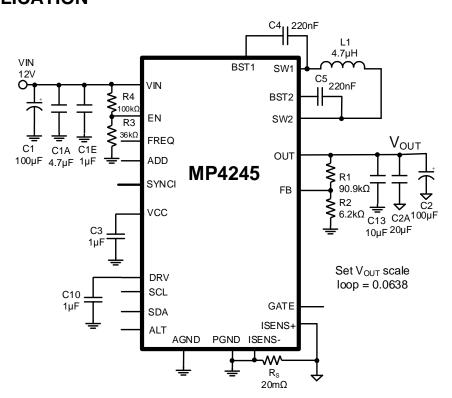

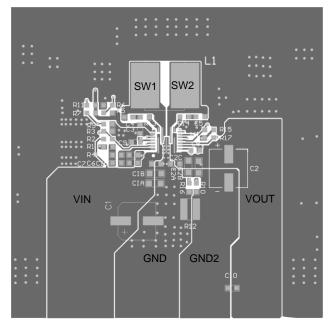

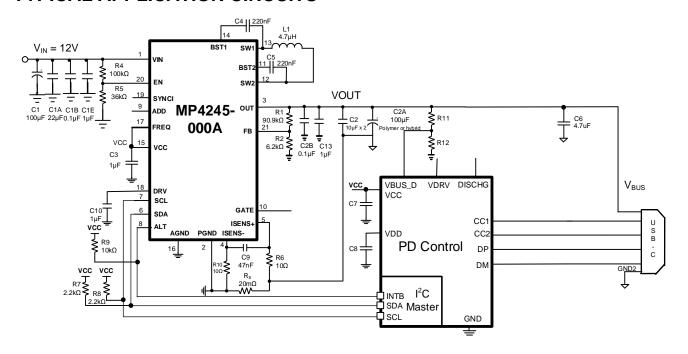

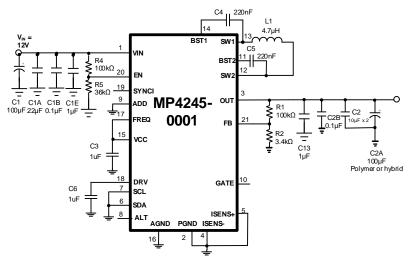

# **TYPICAL APPLICATION**

#### ORDERING INFORMATION

| Part Number*      | Package          | Top Marking | MSL Rating |

|-------------------|------------------|-------------|------------|

| MP4245GVE-xxxx *  | QFN-21 (4mmx5mm) | See Below   |            |

| MP4245GVE-0000 ** | QFN-21 (4mmx5mm) | See Below   | 1          |

| MP4245GVE-0001 ** | QFN-21 (4mmx5mm) | See Below   |            |

| EVKT-MP4245       | Evaluation kit   |             |            |

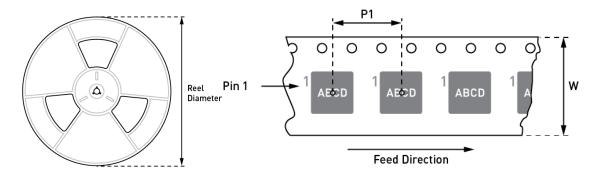

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP4245GVE-xxxx-Z).

#### **TOP MARKING**

MPSYWW MP4245 LLLLLL E

MPS: MPS prefix Y: Year code WW: Week code MP4245: part number LLLLL: Lot number E: Wettable lead flank

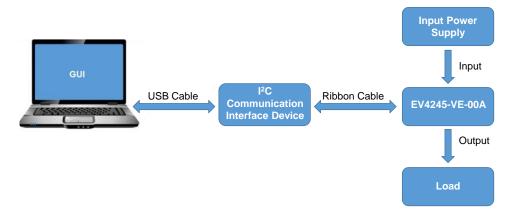

#### **EVALUATION KIT EVKT-MP4245**

EVKT-MP4245 kit contents (items below can be ordered separately):

| # | Part Number        | Item                                                                                | Quantity |

|---|--------------------|-------------------------------------------------------------------------------------|----------|

| 1 | EV4245-VE-00A      | MP4245 evaluation board                                                             | 1        |

| 2 | EVKT-USBI2C-02 bag | Includes USB to $I^2C$ communication interface, one USB cable, and one ribbon cable | 1        |

| 3 | MP4245GVE-0001-Z   | IC with default configuration                                                       | 2        |

#### Order directly from MonolithicPower.com or our distributors.

Figure 1: EVKT-MP4245 Evaluation Kit Set-Up

<sup>\*\* &</sup>quot;xxxx" is the configuration code identifier for the register setting stored in the MTP. Each "x" can be a hexadecimal value between 0 and F. The MP4245GVE-0000 is the default version.

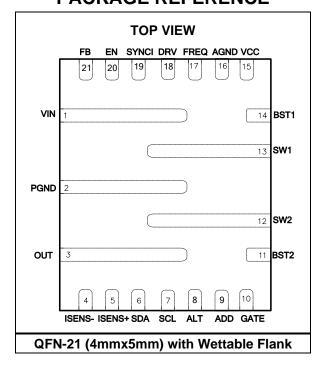

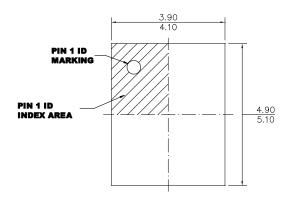

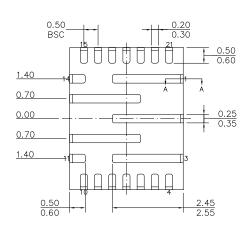

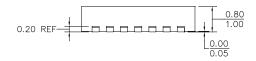

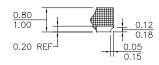

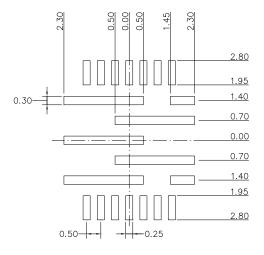

# **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| Pin # | Name   | Description                                                                                                                                                                                                                                                                                                   |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN    | <b>Supply voltage.</b> The MP4245 operates from a 4V to 36V input voltage. An input capacitor $(C_{IN})$ prevents large voltage spikes at the input. Place $C_{IN}$ as close to the IC as possible. VIN is the drain of the first half-bridge's internal power device. VIN supplies power to the entire chip. |

| 2     | PGND   | <b>Power ground.</b> PGND requires extra consideration during PCB layout. Connect PGND to GND with copper traces and vias.                                                                                                                                                                                    |

| 3     | OUT    | Buck-boost mode output pin.                                                                                                                                                                                                                                                                                   |

| 4     | ISENS- | <b>Negative node of the current-sense signal input.</b> Place a current-sense resistor between the PGND pin and the USB port's GND pin. Connect the ISENS- pin to the PGND side. The sensed signal is used for buck-boost constant current (CC) limiting.                                                     |

| 5     | ISENS+ | <b>Positive node of current-sense signal input.</b> Place a current-sense resistor between the PGND pin and the USB port's GND pin. Connect the ISENS+ pin to the USB port's GND. The sensed signal is used for buck-boost constant current (CC) limiting.                                                    |

| 6     | SDA    | I <sup>2</sup> C data line.                                                                                                                                                                                                                                                                                   |

| 7     | SCL    | I <sup>2</sup> C clock signal input.                                                                                                                                                                                                                                                                          |

| 8     | ALT    | <b>PMBus alert pin.</b> Open drain output, active low. Pull ALT up to an external supply with a $10k\Omega$ resistor.                                                                                                                                                                                         |

| 9     | ADD    | I <sup>2</sup> C slave address set pin. Connect a different resistor from the ADD pin to ground to set eight different I <sup>2</sup> C addresses. The internal ADC reads this pin's voltage to lock the I <sup>2</sup> C address during start-up. ADD has an internal 20μA current source.                   |

| 10    | GATE   | Gate drive pin to drive external MOSFET.                                                                                                                                                                                                                                                                      |

| 11    | BST2   | <b>Bootstrap.</b> A 220nF capacitor is connected between SW2 and BST2 to form a floating supply across the high-side switch driver.                                                                                                                                                                           |

| 12    | SW2    | Switch 2 output. Use a wide PCB trace to make the SW2 connection.                                                                                                                                                                                                                                             |

| 13    | SW1    | Switch 1 output. Use a wide PCB trace to make the SW1 connection.                                                                                                                                                                                                                                             |

| 14    | BST1   | <b>Bootstrap.</b> A 220nF capacitor is connected between SW1 and BST1 to form a floating supply across the high-side switch driver.                                                                                                                                                                           |

| 15    | VCC    | Internal 5V LDO regulator output. Decouple VCC with a 1µF capacitor.                                                                                                                                                                                                                                          |

| 16    | AGND   | <b>Analog ground.</b> Connect AGND to PGND, then connect AGND to the VCC capacitor's ground node.                                                                                                                                                                                                             |

| 17    | FREQ   | <b>Frequency selection pin.</b> Float the FREQ pin to set the frequency to 350kHz. Pull FREQ to ground set the frequency to 250kHz. Pull FREQ to 5V to set the frequency to 420kHz.                                                                                                                           |

| 18    | DRV    | 5.5V to 6.5V adjustable LDO output. 1mA load capability. DRV starts up at the same time as VCC. Add a 1µF decoupling capacitor to DRV.                                                                                                                                                                        |

| 19    | SYNCI  | <b>SYNC clock input.</b> Apply a clock on this pin to sync the switching frequency to the external clock. The allowable frequency for the external clock is 250kHz, 350kHz, or 420kHz. If SYNC is not used, it is recommended to connect SYNCI to GND.                                                        |

| 20    | EN     | Enable control pin. Apply a logic high voltage on this pin to enable the IC, pull EN to logic low to disable the IC. EN has an internal $2M\Omega$ pull-down resistor.                                                                                                                                        |

| 21    | FB     | <b>Feedback pin.</b> Connect FB to the tap of an external resistor divider from the output to GND to set the output voltage.                                                                                                                                                                                  |

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply voltage ( $V_{IN}$ )0.4V to +40V $V_{SW1/2}$ 0.3V (-5V for <10ns) to $V_{IN}$ + 0.3V (+43V for <10ns) |

|--------------------------------------------------------------------------------------------------------------|

|                                                                                                              |

| $V_{BST1/2}$ $V_{SW1/2} + 5.5V$                                                                              |

| Vout0.3V to +24V                                                                                             |

| VDRV0.3V to +6.75V                                                                                           |

| VEN0.3V to +10V (2)                                                                                          |

| All other pins0.3V to +5.5V                                                                                  |

| Continuous power dissapation ( $T_A = 25^{\circ}C$ ) (3) (6)                                                 |

| QFN-21 (4mmx5mm) 5.08W                                                                                       |

| Junction temperature150°C                                                                                    |

| Lead temperature260°C                                                                                        |

| Storage temperature65°C to +150°C                                                                            |

| FSD Ratings (4)                                                                                              |

#### ESD Katings (4)

| Human body model (HBM)   | ±2000V    |

|--------------------------|-----------|

| Charged device model (CD | OM) ±750V |

### Recommended Operating Conditions (5)

Operating input voltage range ...........4V to 36V Operation output voltage range .........1V to 23V Output power and current........60W or 6A peak Operating junction temp (T<sub>J</sub>)....-40°C to +125°C

| Thermal Resistance   | $oldsymbol{	heta}$ JA | $\boldsymbol{\theta}$ JC |      |

|----------------------|-----------------------|--------------------------|------|

| EV4245-VE-00A (6)    | 24.6                  | 6.3                      | °C/W |

| QFN-21 (4mmx5mm) (7) | 44                    | 9                        | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- About the details on the EN pin's absolute maximum rating, see the Enable Control (EN) section on page 18.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 4) HBM, per JEDEC specification JESD22-A114; CDM, per JEDEC specification JESD22-C101, AEC specification AEC-Q100-011. JEDEC document JEP155 states that 500V HBM allows for safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process. HBM with regard to GND.

- The device is not guaranteed to function outside of its operating conditions.

- 6) Measured on EV4245-VE-00A, 4-layer PCB, 55mmx55mm.

- 7) Measured on JESD51-7, 4-layer PCB. The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{EN}$  = 5V,  $T_J$  = -40°C to +125°C, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                                  | Symbol                 | Condition                                                                                                | Min   | Тур   | Max   | Units    |  |

|------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------|-------|-------|-------|----------|--|

| Supply current (shutdown)                                  | IQ_STD                 | V <sub>EN</sub> = 0V                                                                                     |       | 1     | 30    | μΑ       |  |

| Supply current (quiescent)                                 | ΙQ                     | Not switching, PFM mode                                                                                  |       | 300   |       | μΑ       |  |

| EN rising threshold                                        | V <sub>EN_RISING</sub> | V <sub>OUT</sub> enabled                                                                                 | -5%   | 1.6   | +5%   | V        |  |

| EN hysteresis                                              | V <sub>EN_HYS</sub>    |                                                                                                          |       | 200   |       | mV       |  |

| EN pull-down resistor                                      | REN                    | $V_{EN} = 2V$                                                                                            |       | 2     |       | МΩ       |  |

| Thermal shutdown (8)                                       | T <sub>STD</sub>       |                                                                                                          |       | 160   |       | °C       |  |

| Thermal hysteresis <sup>(8)</sup>                          | T <sub>STD_HYS</sub>   |                                                                                                          |       | 20    |       | °C       |  |

| VCC regulator                                              | Vcc                    |                                                                                                          | 5     | 5.25  | 5.5   | V        |  |

| VCC load regulation                                        | Vcc_log                | Icc = 50mA                                                                                               |       | 2     | 10    | %        |  |

| DRV regulator output                                       | $V_{DRV}$              | I <sup>2</sup> C-adjustable                                                                              | 5.75  | 6.0   | 6.25  | <b>V</b> |  |

| DRV load regulation                                        | Vcc_log                | Icc = 1mA                                                                                                |       | 2.5   | 8     | %        |  |

| V <sub>IN</sub> under-voltage lockout rising threshold     | V <sub>IN_UVLO</sub>   |                                                                                                          | 3.1   | 3.3   | 3.5   | ٧        |  |

| V <sub>IN</sub> under-voltage lockout threshold hysteresis | Vuvlo_HYS              |                                                                                                          |       | 300   |       | mV       |  |

| FB reference voltage                                       | V <sub>FB0</sub>       | Scale loop = 0.08, set V <sub>OUT</sub> = 1.25V                                                          | 0.092 | 0.100 | 0.108 | V        |  |

|                                                            | V <sub>FB1</sub>       | Scale loop = 0.08, set Vout = 5V                                                                         | -2%   | 0.400 | +2%   | V        |  |

|                                                            | V <sub>FB2</sub>       | Scale loop = 0.08, set Vout = 9V                                                                         | -1.5% | 0.720 | +1.5% | V        |  |

|                                                            | V <sub>FB3</sub>       | Scale loop = 0.08, set Vout = 20V                                                                        | -1.5% | 1.600 | +1.5% | V        |  |

| Switch A on resistance                                     |                        |                                                                                                          |       | 12    | 25    |          |  |

| Switch B on resistance                                     | Proven                 |                                                                                                          |       | 24    | 50    | mΩ       |  |

| Switch C on resistance                                     | R <sub>DS(ON)</sub>    |                                                                                                          |       | 14    | 30    | 11152    |  |

| Switch D on resistance                                     |                        |                                                                                                          |       | 14    | 30    |          |  |

| Output over-voltage protection                             | V <sub>OVP_R</sub>     |                                                                                                          | 116   | 121   | 126   | %        |  |

| Output OVP recovery                                        | V <sub>OVP_F</sub>     |                                                                                                          |       | 110   |       | %        |  |

| Conitab la alcana                                          |                        | $V_{EN} = 0V$ , $V_{SW1} = 36V$ , $V_{SW2} = 22V$ , $T_J = 25^{\circ}C$                                  |       |       | 1     |          |  |

| Switch leakage                                             | SW <sub>LKG</sub>      | V <sub>EN</sub> = 0V, V <sub>SW1</sub> = 36V, V <sub>SW2</sub> = 22V,<br>T <sub>J</sub> = -40°C to+125°C |       |       | 30    | μA       |  |

|                                                            | fsw <sub>1</sub>       | FREQ = GND                                                                                               | 180   | 250   | 320   |          |  |

| Oscillator frequency                                       | f <sub>SW2</sub>       | FREQ pin floating                                                                                        | 260   | 350   | 440   | kHz      |  |

|                                                            | f <sub>SW3</sub>       | FREQ = VCC                                                                                               | 330   | 420   | 510   |          |  |

|                                                            | fsync1                 | FREQ = GND                                                                                               | 220   | 250   | 280   | kHz      |  |

| Frequency sync in                                          | f <sub>SYNC2</sub>     | FREQ pin floating                                                                                        | 310   | 350   | 390   | kHz      |  |

|                                                            | f <sub>SYNC3</sub>     | FREQ = VCC                                                                                               | 370   | 420   | 470   |          |  |

| Frequency dithering span (8)                               | fdithering             |                                                                                                          |       | ±12   |       | %        |  |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $V_{EN}$  = 5V,  $T_J$  = -40°C to +125°C, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                   | Symbol                 | Condition                                                              | Min   | Тур  | Max   | Units |

|---------------------------------------------|------------------------|------------------------------------------------------------------------|-------|------|-------|-------|

| Soft-start time                             | tss                    | Output from 10% to 90%, VREF = 0.4V, constant slew rate for other VREF |       | 1.4  |       | ms    |

| Minimum on time (8)                         | t <sub>ON_MIN_BT</sub> |                                                                        |       | 80   |       | ns    |

| ISENS OC threshold                          | l <sub>OC1</sub>       | OC threshold = 1A, $R_{SENS} = 20m\Omega$                              | 17    | 20   | 23    | mV    |

| ISENS OC INTESHOID                          | l <sub>OC2</sub>       | OC threshold = 3.6A, $R_{SENS} = 20m\Omega$                            | -5%   | 72   | +5%   | mV    |

| GND short to battery ISENS threshold        | Isc                    | OC threshold = 20A, $R_{SENS} = 20m\Omega$                             |       | 420  |       | mV    |

| Short to battery retry delay                | t <sub>SBP</sub>       |                                                                        |       | 1    |       | s     |

| Gate pull-down resistance                   | RGATE                  |                                                                        |       | 7    | 20    | Ω     |

|                                             |                        | CC limit set-up value = 3.6A                                           |       | 23   |       |       |

| High-side A current limit (8)               | I <sub>LIMIT1</sub>    | 1.6A < CC limit set-up value < 3.6A                                    |       | 19   |       | Α     |

|                                             |                        | CC limit set-up value < 1.6A                                           |       | 15   |       |       |

| Low-side B valley limit                     | I <sub>LIMIT2</sub>    | Switch B                                                               |       | 11.5 |       | Α     |

| ADD pin source current                      | I <sub>ADD</sub>       | Only works during start-up.                                            | -1.5% | 20   | +1.5% | μΑ    |

| ADD address 1                               | ADD1                   | R <sub>ADD</sub> = GND, 61h                                            |       |      | 0.18  |       |

| ADD address 2                               | ADD2                   | $R_{ADD} = 15k\Omega$ , 62h                                            | 0.25  |      | 0.38  |       |

| ADD address 3                               | ADD3                   | $R_{ADD} = 25.5k\Omega, 63h$                                           | 0.45  |      | 0.59  |       |

| ADD address 4                               | ADD4                   | $R_{ADD} = 35.7k\Omega$ , 64h                                          | 0.66  |      | 0.79  | V     |

| ADD address 5                               | ADD5                   | $R_{ADD} = 45.3k\Omega, 65h$                                           | 0.87  |      | 0.99  |       |

| ADD address 6                               | ADD6                   | $R_{ADD} = 56k\Omega$ , 66h                                            | 1.07  |      | 1.20  |       |

| ADD address 7                               | ADD7                   | R <sub>ADD</sub> = V <sub>CC</sub> , 67h                               | 1.28  |      |       |       |

| Alert pull-low resistance                   | R <sub>ALERT</sub>     |                                                                        |       | 8    | 20    | Ω     |

| Alert leakage                               | LKGALERT               | Pull up with 5V                                                        |       | 100  |       | nA    |

| I <sup>2</sup> C Interface Specifications ( | HS Mode)               |                                                                        |       |      | •     | •     |

| Input logic high                            | V <sub>IH</sub>        | I <sup>2</sup> C pulled up to VDD (can be between 1.8V and 5V)         | 1.4   |      |       | V     |

| Input logic low                             | V <sub>IL</sub>        |                                                                        |       |      | 0.4   | V     |

| SDA output voltage logic low                | Vout_L                 |                                                                        |       |      | 0.4   | V     |

| SCL clock frequency                         | f <sub>SCL</sub>       |                                                                        |       | 400  | 1000  | kHz   |

| SCL high time                               | tніgн                  |                                                                        | 60    |      |       | ns    |

| SCL low time                                | t <sub>LOW</sub>       |                                                                        | 160   |      |       | ns    |

| Data set-up time                            | tsu_dat                |                                                                        | 10    |      |       | ns    |

| Data hold time                              | thd_dat                |                                                                        | 0     | 60   |       | ns    |

| Set-up time for (repeated) start condition  | tsu_sta                |                                                                        | 160   |      |       | ns    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $V_{EN}$  = 5V,  $T_J$  = -40°C to +125°C, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                          | Symbol                 | Condition | Min    | Тур    | Max    | Units            |

|----------------------------------------------------|------------------------|-----------|--------|--------|--------|------------------|

| Hold time for (repeated) start condition           | t <sub>HD_STA</sub>    |           | 160    |        |        | ns               |

| Bus Free Time between a start and a stop condition | t <sub>BUF</sub>       |           | 160    |        |        | ns               |

| Set-up time for stop condition                     | tsu_sто                |           | 160    |        |        | ns               |

| Rise Time of SCL and SDA                           | <b>t</b> <sub>R</sub>  |           | 10     |        | 300    | ns               |

| Fall Time of SCL and SDA                           | t⊧                     |           | 10     |        | 300    | ns               |

| Pulse width of suppressed spike                    | <b>t</b> sp            |           | 0      |        | 50     | ns               |

| Capacitance for each bus line                      | Св                     |           |        |        | 400    | рF               |

| PMBus Status Threshold                             |                        |           | ·      |        |        |                  |

| VOUT_OV_FAULT_RISING                               | VOUT <sub>OV_F_R</sub> |           | 116%   | 121%   | 126%   | V <sub>OUT</sub> |

| VOUT_OV_FAULT_FALLING                              | VOUT <sub>OV_F_F</sub> |           | 105%   | 110%   | 115%   | Vout             |

| VOUT_OV_WARNING_RING                               | VOUT <sub>OV_W_R</sub> |           | 103.5% | 108.5% | 113.5% | Vout             |

| VOUT_OV_WARNING_FALLING                            | VOUT <sub>OV_W_F</sub> |           | 99.5%  | 104.5% | 109.5% | V <sub>OUT</sub> |

| VOUT_UV_WARNING_RISING                             | VOUT <sub>UV_W_R</sub> |           | 81%    | 86%    | 91%    | Vout             |

| VOUT_UV_WARNING_FALLING                            | VOUT <sub>UV_W_F</sub> |           | 69.5%  | 74.5%  | 79.5%  | Vout             |

| VOUT_UV_FAULT_RISING                               | VOUT <sub>UV_F_R</sub> |           | 56%    | 61%    | 66%    | Vout             |

| VOUT_UV_FAULT_FALLING                              | VOUT <sub>UV_F_F</sub> |           | 44.5%  | 49.5%  | 54.5%  | V <sub>OUT</sub> |

| VIN_OV_FAULT_RISING                                | VIN <sub>OV_F_R</sub>  |           |        | 40     |        | >                |

| VIN_OV_FAULT_FALLING                               | VIN <sub>OV_F_F</sub>  |           |        | 38     |        | V                |

| VIN_OV_WARNING_RISING                              | VIN <sub>OV_W_R</sub>  |           |        | 38     |        | V                |

| VIN_OV_WARNING_FALLING                             | VIN <sub>OV_W_F</sub>  |           |        | 36     |        | V                |

| VIN_UV_WARNING_RISING                              | VIN <sub>UV_W_R</sub>  |           |        | 3.7    |        | V                |

| VIN_UV_WARNING_FALLING                             | VIN <sub>UV_W_F</sub>  |           |        | 3.4    |        | V                |

| VIN_UV_FAULT_RSING                                 | VIN <sub>UV_F_R</sub>  |           |        | 3.4    |        | V                |

| VIN_UV_FAULT_FALLING                               | VIN <sub>UV_F_F</sub>  |           |        | 3.1    |        | V                |

#### Notes:

8) Guaranteed by characterization testing.

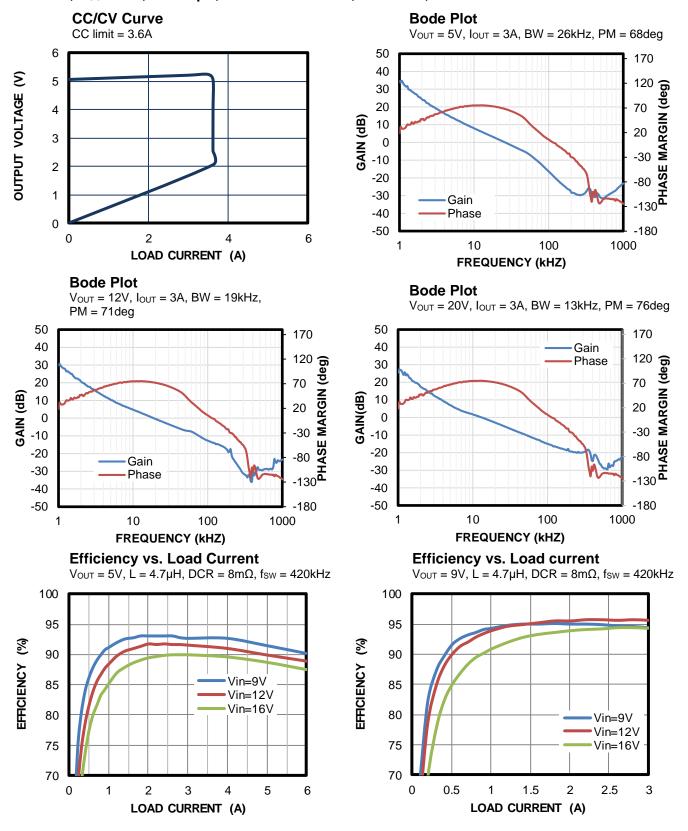

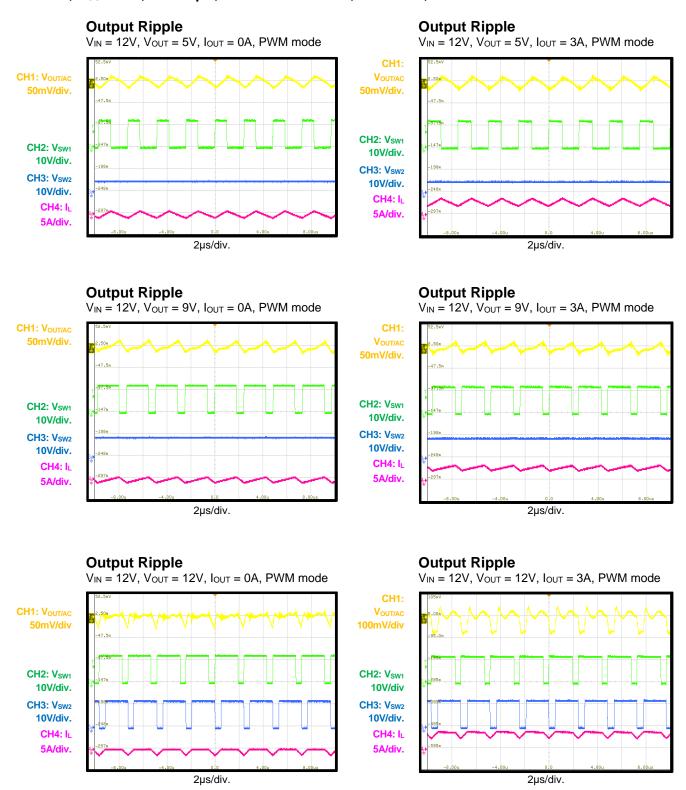

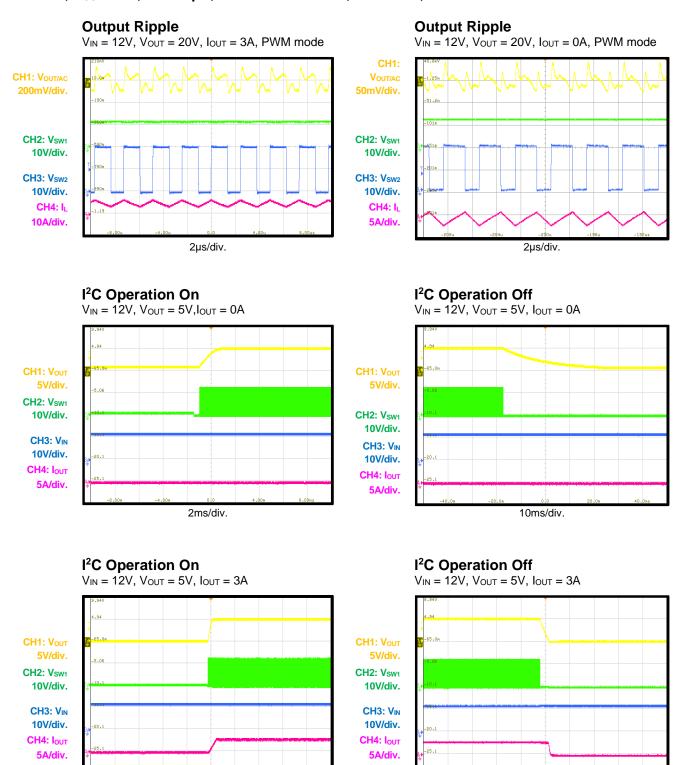

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ , L = 4.7µH, forced PWM mode,  $T_A = 25$ °C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ , L = 4.7 $\mu$ H, forced PWM mode,  $T_A = 25$ °C, unless otherwise noted.

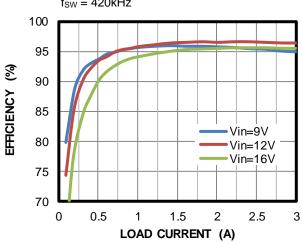

#### **Efficiency vs. Load Current**

$V_{OUT} = 15V$ ,  $L = 4.7\mu H$ ,  $DCR = 8m\Omega$ ,  $f_{SW} = 420kHz$

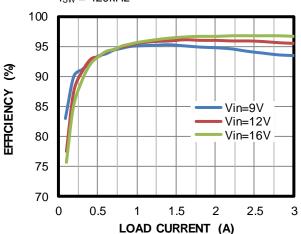

#### Efficiency vs. Load Current

$V_{OUT} = 20V$ ,  $L = 4.7\mu H$ , DCR =  $8m\Omega$ ,  $f_{SW} = 420kHz$

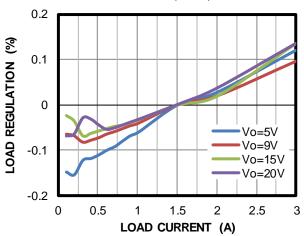

### Load Regulation vs. Load Current

$V_{\text{IN}}$  = 12V, no line drop compensation

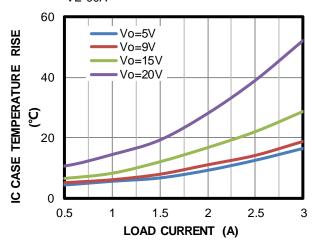

#### **Thermal Rise**

$V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 420kHz, based on the EV4245-VE-00A

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

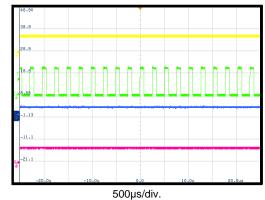

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, forced PWM mode,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, forced PWM mode,  $T_A$  = 25°C, unless otherwise noted.

500µs/div.

13

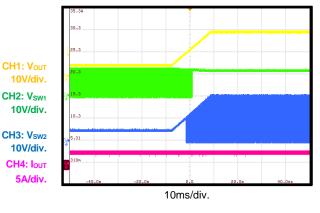

10ms/div.

CH1: Vout

CH2: Vsw1

CH3: V<sub>SW2</sub>

10V/div.

10V/div.

10V/div. CH4: I<sub>OUT</sub>

5A/div.

CH1: Vout

CH2: V<sub>SW1</sub>

CH3: V<sub>SW2</sub>

10V/div.

CH4: Iout

10A/div.

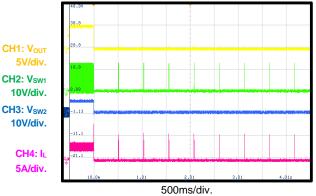

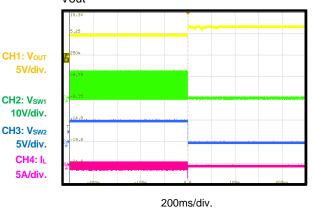

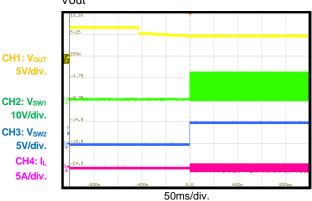

CH1: Vout 5V/div.

CH2: V<sub>SW1</sub> 10V/div.

CH3: V<sub>SW2</sub> 10V/div. CH4: IL

5A/div.

10V/div.

10V/div.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

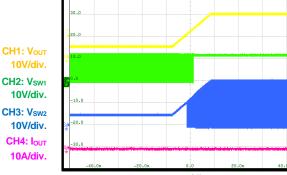

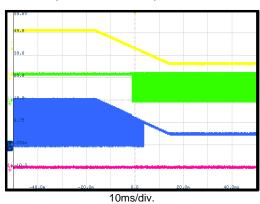

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, forced PWM mode,  $T_A$  = 25°C, unless otherwise noted.

#### **Output Voltage Transition**

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$  to 20V,  $I_{OUT} = 0A$

#### **Output Voltage Transition**

$V_{IN} = 12V$ ,  $V_{OUT} = 20V$  to 5V,  $I_{OUT} = 0A$

# 10ms/div.

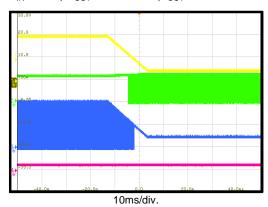

### **Output Voltage Transition**

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$  to 20V,  $I_{OUT} = 3A$

#### **Output Voltage Transition**

$V_{IN} = 12V$ ,  $V_{OUT} = 20V$  to 5V,  $I_{OUT} = 3A$

CH3: Vsw2 10V/div. CH4: Iout

5A/div.

# **Short Circuit Protection Entry**

$V_{IN} = 12V$ ,  $V_{OUT}=5V$ ,  $I_{OUT} = 3A$ , 500ms hiccup off time

#### **Short Circuit Protection Recovery**

$V_{IN} = 12V$ ,  $V_{OUT}=5V$ ,  $I_{OUT} = 3A$ , 500ms hiccup off time

14

MP4245 Rev. 1.0

10/19/2021

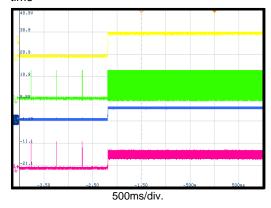

CH1: Vout

CH2: Vsw<sub>1</sub>

CH3: V<sub>SW2</sub>

10V/div.

CH4: Iout

CH1: Vout

200mV/div

CH4: Iout

1A/div.

5A/div.

10V/div.

5V/div.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, forced PWM mode,  $T_A$  = 25°C, unless otherwise noted.

#### **Constant Current Limit Protection**

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, CR Load = 1 $\Omega$ , output current limit = 3A

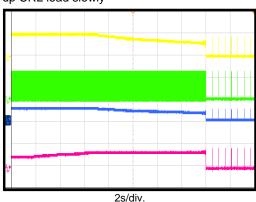

#### **CRL Load OCP**

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, CC current limit = 3A, ramp up CRL load slowly

5V/div. CH2: Vsw<sub>1</sub> 10V/div.

CH1: Vout

CH3: V<sub>SW2</sub> 10V/div. CH4: Iout 5A/div.

#### **OVP Entry**

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 0A$ , Force 7V on Vout

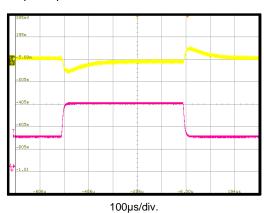

#### **Load Transient Response**

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 1.5A$  to 3A, no line drop compensation

**OVP Recovery**

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 0A$ , Force 7V on Vout

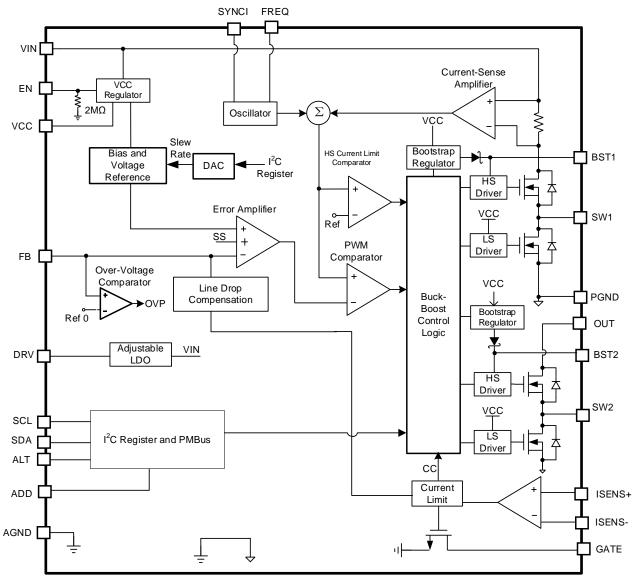

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

© 2021 MPS. All Rights Reserved.

#### **OPERATION**

The MP4245 is a buck-boost converter with four integrated power MOSFET switches. The device can deliver up to 6A of output current at certain input voltage supply ranges, with excellent load and line regulation.

The MP4245 works with fixed-frequency control logic to provide fast transient response for all operation modes: buck, boost, and buck-boost. There is one special buck-boost control strategy that provides high efficiency across the full input voltage range, and smooths the transient response between different modes.

#### **Buck-Boost Operation**

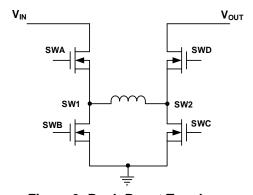

The MP4245 can regulate the output voltage  $(V_{OUT})$  above, below, or equal to the input voltage  $(V_{IN})$ . Figure 3 shows a buck-boost power structure with one inductor and four switches (SWA, SWB, SWC, and SWD).

Figure 3: Buck-Boost Topology

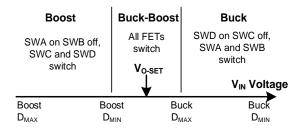

Buck mode, boost mode, and buck-boost mode can have different  $V_{\text{IN}}$  inputs (see Figure 4).

Figure 4: Buck-Boost Operation Range

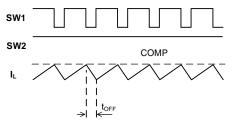

### Buck Mode ( $V_{IN} > V_{OUT}$ )

When  $V_{\text{IN}}$  exceeds  $V_{\text{OUT}}$ , the MP4245 works in buck mode. In buck mode, switch A (SWA) and switch B (SWB) switch for buck regulation. Meanwhile, switch C (SWC) is off, and switch D (SWD) stays on to conduct the inductor current.

In each cycle, SWA turns on to conduct the inductor current. SWA remains on until the inductor current reaches the COMP voltage ( $V_{\text{COMP}}$ ) through  $R_{\text{SENSE}}$ , then SWB turns on with a calculated off time to conduct the inductor current. An internal oscillator controls the SWA off time to maintain a fixed frequency. The COMP signal is an error amplifier (EA) output from the  $V_{\text{OUT}}$  feedback and internal FB reference voltage. This means that  $V_{\text{COMP}}$  controls the inductor current to supply the output terminal voltage. Figure 5 shows the buck mode waveform.

Figure 5: Buck Waveform

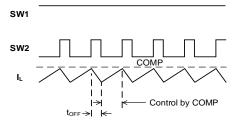

#### Boost Mode (V<sub>IN</sub> < V<sub>OUT</sub>)

When  $V_{\text{IN}}$  is significantly lower than  $V_{\text{OUT}}$ , the MP4245 works in boost mode. In boost mode, SWC and SWD switch for the boost regulation. SWB is off, and SWA remains on to conduct the inductor current.

In each cycle, SWC turns on to conduct the inductor current. When the inductor current rises and triggers the control signal on COMP, SWC turns off and SWD turns on. SWC turns off for a fixed off time before turning on again, and SWD turns on for the current freewheel. An internal oscillator controls the SWC off time to maintain a fixed frequency. Then SWC turns on and off repeatedly to regulate the current to match the COMP signal. The COMP voltage controls the inductor current to supply the output terminal voltage in boost mode. Figure 6 shows the boost work waveform.

Figure 6: Boost Waveform

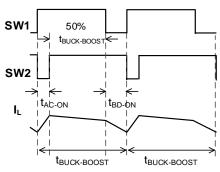

#### Buck-Boost Mode ( $V_{IN} \approx V_{OUT}$ )

When  $V_{IN}$  is almost equal to  $V_{OUT}$ , the converter cannot provide enough energy to the load in buck mode due to SWA's minimum off time. In boost mode, the converter supplies too much power to the load due to SWC's minimum on time. Under these conditions, the MP4245 adopts buck-boost control to regulate the output (see Figure 7).

Figure 7: Buck-Boost Waveform

If V<sub>IN</sub> is almost equal to V<sub>OUT</sub>, buck-boost mode activates. The MOSFET turn-on sequence is as follows:

- SWA and SWC

- 2. SWA and SWD

- 3. SWD and SWB

Through this process, the inductor current can reach the COMP voltage requirement, and supply enough current to the output.

The SWA and SWD turn-on time is fixed to about 50% of the buck-boost operation frequency. If buck mode nearly reaches the minimum off time, the IC enters buck-boost mode. If V<sub>IN</sub> is about 15% above V<sub>OUT</sub> in buck-boost mode, the IC changes to buck mode. If V<sub>IN</sub> is about 10% below V<sub>OUT</sub>, the IC enters boost mode. When boost mode nearly reaches the minimum on time, the IC enters buck-boost mode.

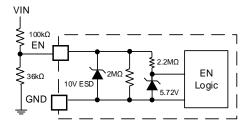

#### **Enable Control (EN)**

The MP4245 has enable (EN) control. The EN pin has two thresholds. The first threshold is when EN > 0.7V, and VCC is enabled. The second threshold is when EN > 1.6V, and the chip starts to operate normally. The EN pin is clamped internally using a 10V series Zener diode (see Figure 8). Connect the EN input pin through two resistor dividers to the V<sub>IN</sub> supply and GND. The EN rising threshold is 1.6V, so V<sub>IN</sub> must exceed 6.05V to enable the circuit. If the

EN pin is directly connected to VIN when V<sub>IN</sub> exceeds 6V, do not add a capacitor exceeding 1nF to EN.

Figure 8: EN Internal Circuit

#### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. The UVLO comparator monitors the input voltage. The UVLO rising threshold is 3.3V; its falling threshold is 3.0V.

#### Internal Soft Start (SS)

Soft start (SS) prevents the converter's output voltage from overshooting during start-up. When the chip starts up, the internal circuitry generates an SS voltage (Vss) that ramps up from 0V to 5V. When  $V_{SS}$  is below the reference voltage ( $V_{REF}$ ), the error amplifier uses V<sub>SS</sub> as the reference. When V<sub>SS</sub> exceeds V<sub>REF</sub>, the error amplifier uses V<sub>REF</sub> as the reference.

If the output of the MP4245 is pre-biased to a certain voltage during start-up, the IC disables the switching of both the high-side and low-side MOSFETs until the voltage on the internal SS capacitor exceeds the internal feedback voltage.

#### Constant Current (CC) Mode Over-Current-Protection (OCP)

The MP4245 senses the ground current with the ISENS+ and ISENS- pins. If I<sub>OUT</sub> exceeds the set current limit threshold, the MP4245 enters constant current (CC) limit mode. In this mode, the current amplitude is limited. As the load resistance is reduced, the output voltage drops until the feedback voltage falls below the undervoltage (UV) threshold.

If a UV condition is triggered and soft start is ready, the MP4245 enters hiccup mode to periodically restart the part. This protection mode is especially useful when the output is deadshorted to ground. This greatly reduces the

average short circuit current, alleviates thermal issues, and protects the regulator. Once the over-current (OC) condition is removed, the MP4245 exits hiccup mode and resumes normal operation.

When  $V_{\text{OUT}}$  is set above 6.4V, the MP4245's hiccup UV threshold is about 2.7V. When  $V_{\text{OUT}}$  is set below 6.4V, the hiccup UV threshold is about 50% of the feedback reference value.

#### **Peak and Valley Current Limit**

Besides the output CC limit, the MP4245 also has an SWA peak and SWB valley current limit. The peak current limit is related to the CC limit set-up. When the CC limit increases, the peak current limit increases as well. The valley current limit is fixed, and does not change with the CC limit

In buck mode and buck-boost mode, both the SWA peak current limit and valley current limit are functional.

In boost mode, only the SWA peak current limit is monitored. In this scenario, the SWA peak current limit is about 23A when  $V_{\text{IN}} = 5V$ ,  $V_{\text{OUT}} = 20V$ ,  $I_{\text{OUT}} = 3A$ ,  $f_{\text{SW}} = 420\text{kHz}$ , and the CC limit = 3.6A.

#### **Output Over-Voltage Protection (OVP)**

The MP4245 has output over-voltage protection (OVP). If the output exceeds 121% of  $V_{REF}$ , all switches (SWA, SWB, SWC, and SWD) turn off. The discharge path from OUT to ground turns on. When the FB voltage drops to 110% of  $V_{REF}$ , the IC resumes normal operation.

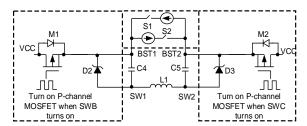

#### Floating Driver and Bootstrap Charging

An external bootstrap capacitor powers the floating MOSFET driver. This floating driver has its own under-voltage lockout (UVLO) protection. The UVLO rising threshold is 2.2V, with a 150mV hysteresis. The BST1 capacitor voltage is regulated internally by VCC through D2, M1, and C4. The BST2 capacitor voltage is regulated internally by VCC through D3, M2, and C5 (see Figure 9).

Figure 9: Internal Bootstrap Charging Circuit

In buck mode, S2 always turns on, and BST2 is charged up by BST1; in boost mode, S1 always turns on, and BST1 is charged up by BST2.

#### Start-Up and Shutdown

If both VIN and EN exceed their respective thresholds, the chip is enabled. The reference block starts first, generating a stable reference voltage and current. Then the internal regulator is enabled. The regulator provides a stable supply for the remaining circuitries.

Several events can shut down the chip: EN going low, VIN going low, thermal shutdown, and an OPERATION off command being received via the I<sup>2</sup>C. During shutdown, the signaling path is blocked to avoid any fault triggering. Then the COMP voltage and the internal supply rail are pulled down. The floating driver is not subject to this shutdown command.

#### Start-Up Timing for USB PD Applications

If the EN pin is high, the MP4245 powers up VCC, but the default I<sup>2</sup>C operation bit (OPERATION) is set to off for the MP4245-0000.

When a sink device is plugged in, the PD controller sends the I<sup>2</sup>C a command to set OPERATION to on.

#### **EN Shutdown Discharge**

If the EN pin is pulled low or OPERATION is set to off, all switches (SWA, SWB, SWC, and SWD) turn off. Then the device turns on a  $150\Omega$  discharge resistor that is connected from OUT to GND. The discharge path stays on until the FB voltage falls below 50mV.

#### **Gate Pin Logic Table**

Table 1 on page 20 shows the GATE pin's logic table. The secondary current limit is about 20A through a current-sense resistor.

| 7 | ah | ما | 1. | G | TF | Sta | tus |

|---|----|----|----|---|----|-----|-----|

|   |    |    |    |   |    |     |     |

| Condition                        | GATE Status |

|----------------------------------|-------------|

| V <sub>IN</sub> < UVLO threshold | Open drain  |

| EN < UVLO threshold              | Open drain  |

| Operation = off                  | Open drain  |

| I <sub>SENS</sub> > 20A          | 0           |

#### **Configurable Frequency**

There are three configurable frequencies: 250 kHz, 350 kHz, and 420 kHz. The frequency can be synchronized to 250 kHz, 350 kHz, or 420 kHz with a  $\pm 20\%$  tolerance. When synchronized to a certain frequency, the device's default switching frequency should be set at the same level (e.g. float the FREQ pin). To set  $f_{\text{SW}}$  to 350 kHz, use a 350 kHz ( $\pm 20\%$ ) clock to sync the device.

#### **Frequency Spread Spectrum**

If the DITHER\_ENABLE bit is set to 1, the device has a spread spectrum functionality at 250kHz, 350kHz, or 420kHz. The purpose of spread spectrum is to minimize the peak emissions at specific frequencies.

The MP4245 uses a 4kHz triangle wave (125µs rising, 125µs falling) to modulate the internal oscillator. Spread spectrum operation's frequency span is ±12% of the three available frequencies.

The spread spectrum function is determined by the internal I<sup>2</sup>C register setting. When frequency spread spectrum is enabled, the frequency sync input is automatically disabled.

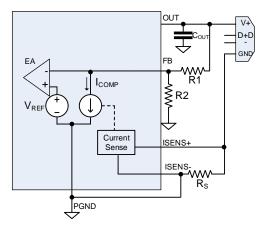

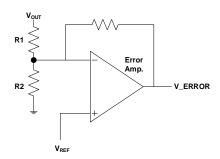

#### **Output Line Drop Compensation**

The MP4245 can compensate an output voltage drop, such as high impedance caused by a long trace, to keep a fairly constant load-side voltage.

The device uses the load current sensed through R<sub>SENSE</sub> to sink a current (I<sub>COMP</sub>) on the FB pin (see Figure 10).

Figure 10: Sinking a Current on FB

I<sub>COMP</sub> can be calculated with Equation (1):

$$I_{COMP} = G \times I_{OUT}$$

(1)

Then V<sub>OUT</sub> can be estimated with Equation (2):

$$V_{OUT} = \left(\frac{R_1}{R_2} + 1\right) \times V_{REF} + R_1 \times G \times I_{OUT}$$

(2)

This means that the line drop compensation amplitude under certain output current conditions is equal to R<sub>1</sub> x G x I<sub>OUT</sub>.

G is the fixed internal gain, but it can be configured by the I<sup>2</sup>C. R<sub>1</sub> can also be used to adjust the line drop compensation amplitude.

#### SYSTEM

#### Load-Shedding vs. Temperature

The MP4245 monitors the die temperature and alerts the host if a certain thermal threshold is reached. The remaining work is done by a PD controller. For example, the PD controller sends out a new source capability message to lower the output power.

The load-shedding temperature threshold can be configured though the I<sup>2</sup>C and MTP via the MFR\_OT\_WARN\_LIMIT register.

#### Thermal Shutdown (TSD)

Thermal shutdown (TSD) prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds 160°C, the entire chip shuts down. When the temperature falls below its lower threshold, (typically 140°C), the chip is enabled and resumes normal operation. The TSD threshold can be configured via the I²C and MTP.

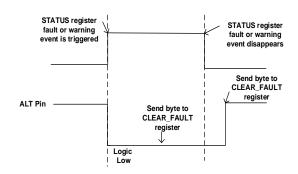

#### **ALT Indication**

The ALT pin is pulled low if a fault or warning event is triggered. If the related STATUS\_MASK register is set to 1, the ALT pin does not respond or pull low if a fault or warning event occurs. Send a byte to the CLEAR\_FAULT (0x03) register to reset the STAUS register value and the ALT pin status. If the fault or warning is still present, the alert cannot be cleared (see Figure 11).

Figure 11: ALT Pin Behaviors

#### I<sup>2</sup>C Timing

The I<sup>2</sup>C is active once VIN and EN both are exceed their under-voltage lockout (UVLO) thresholds.

#### PMBUS INTERFACE

#### **PMBus Serial Interface Description**

The power management bus (PMBus) is an open standard power management protocol that defines a means of communicating with power converters and other devices.

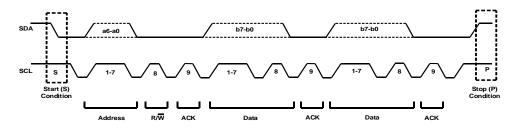

The PMBus is a two-wire, bidirectional serial interface, consisting of a data line (SDA) and a clock line (SCL). When idle, the lines are pulled to an external bus voltage. When connecting to the lines, a master device generates an SCL signal and device address, then arranges the communication sequence. This is based on I<sup>2</sup>C operation principles.

#### **Start and Stop Conditions**

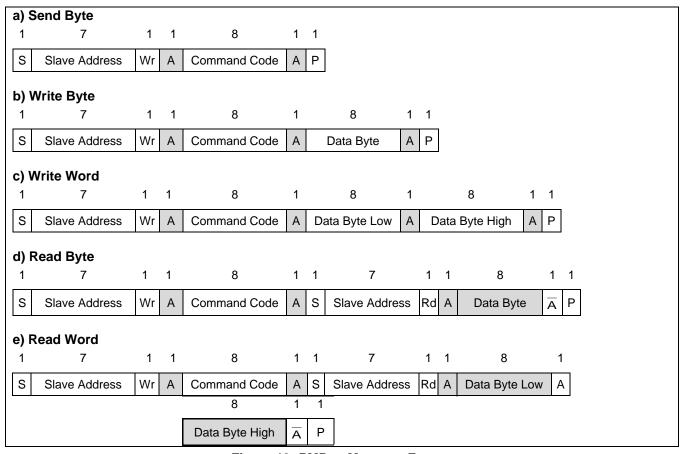

The start and stop conditions are signaled by the master device, and signify the beginning and end of a PMBus transfer, respectively. The start condition (S) is defined as the SDA signal transitioning from high to low while the SCL is high. The stop condition (P) is defined as the SDA signal transitioning from low to high while the SCL is high (see Figure 12).

The master then generates the SCL clocks, and transmits the device address and the read/write direction bit (R/W) on the SDA. Data is transferred in 8-bit bytes by the SDA. Each byte of data is followed by an acknowledge (ACK) bit.

#### **PMBus Update Sequence**

The MP4245 requires a start condition, valid PMBus address, register address byte, and a data byte for a single data update. The device acknowledges that is has received each byte by pulling the SDA line low during the high period of a single clock pulse. A valid PMBus address selects the MP4245. The device performs an update on the falling edge of the LSB byte.

#### **PMBus Bus Message Format**

Figure 13 shows different PMBus operations. Unshaded cells indicate that the bus host is driving the bus actively, and shaded cells indicate that the MP4245 is driving the bus. The symbols are defined below:

- S = Start condition

- Sr = Repeated start condition

- P = Stop condition

- R = Read bit

- W = Write bit

- A = Acknowledge bit (0)

- $\overline{A}$  = Acknowledge bit (1)

"A" represents the acknowledge (ACK) bit. The ACK bit is typically active low (logic 0) if the transmitted byte is received successfully by a device.

Figure 12: Data Transfer across the PMBus

Figure 13: PMBus Message Format

# **REGISTER DESCRIPTION**

# I<sup>2</sup>C/PMBus Register (9)

| CMD Name                                                         | CMD<br>Code | Description                                                                                            | Туре      | Data<br>Format | Unit | MTP       |

|------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------|-----------|----------------|------|-----------|

| OPERATION                                                        | 0x01        | On/off control                                                                                         | R/W Byte  | Reg            |      | Y (1 bit) |

| CLEAR_FAULTS                                                     | 0x03        |                                                                                                        | Send Byte | Reg            |      | Z         |

| WRITE_PROTECT                                                    | 0x10        |                                                                                                        | R/W Byte  | Reg            |      | N         |

| STORE_USER_ALL                                                   | 0x15        | When sending this command, the converter disables V <sub>OUT</sub> then enables it again               | Send Byte | Reg            |      | N         |

| RESTORE_USER_ALL                                                 | 0x16        |                                                                                                        | Send Byte | Reg            |      | N         |

| VOUT_MODE                                                        | 0x20        | Output voltage format and exponent (2 <sup>-10</sup> )                                                 | R Byte    | Reg            |      | N         |

| VOUT_COMMAND                                                     | 0x21        |                                                                                                        | R/W Word  | Linear<br>L16  | V    | Y         |

| VOUT_SCALE_LOOP                                                  | 0x29        |                                                                                                        | R/W Word  | Linear<br>L11  |      | Υ         |

| STATUS_BYTE                                                      | 0x78        |                                                                                                        | R Byte    | Reg            |      | N         |

| STATUS_WORD                                                      | 0x79        |                                                                                                        | R Word    | Reg            |      | N         |

| STATUS_VOUT                                                      | 0x7A        |                                                                                                        | R Byte    | Reg            |      | N         |

| STATUS_INPUT                                                     | 0x7C        |                                                                                                        | R Byte    | Reg            |      | N         |

| STATUS_TEMPERATURE                                               | 0x7D        |                                                                                                        | R Byte    | Reg            |      | N         |

| STATUS CML                                                       | 0x7E        |                                                                                                        | R Byte    | Reg            |      | N         |

| READ_VIN (1/25V <sub>IN</sub> to ADC 10 bit, 0V to 1.638V/1.6mV) | 0x88        | N = -4                                                                                                 | R Word    | Linear<br>L11  | V    | N         |

| READ_VOUT                                                        | 0x8B        | N = -10, not including line drop compensation                                                          | R Word    | Linear<br>L16  | V    | N         |

| READ_IOUT                                                        | 0x8C        | N = -6                                                                                                 | R Word    | Linear<br>L11  | Α    | N         |

| READ_TEMPERATURE                                                 | 0x8D        | N = -1, -55°C to +200°C                                                                                | R Word    | Linear<br>L11  | °C   | N         |

| MFR_MODE_CTRL                                                    | 0xD0        | Selects and enables PWM/PFM, output discharge, hiccup timer, output OVP, dither, and R <sub>SENS</sub> | R/W Byte  | Reg            |      | Y         |

| MFR_CURRENT_LIMIT                                                | 0xD1        | Sets the continuous constant current (CC) limit                                                        | R/W Byte  | Reg            |      | Υ         |

| MFR_LINE_DROP_COMP                                               | 0xD2        | Sets line drop compensation                                                                            | R/W Byte  | Reg            |      | Y         |

| MFR_OT_FAULT_LIMIT                                               | 0xD3        |                                                                                                        | R/W Byte  | Reg            | °C   | Υ         |

| MFR_OT_WARN_LIMIT                                                | 0xD4        |                                                                                                        | R/W Byte  | Reg            | °C   | Υ         |

| MFR_CRC_ERROR_FLAG                                               | 0xD5        | Set high when a CRC error occurs while restoring data to the MTP                                       | R Byte    | Reg            |      | N         |

| MFR_MTP_<br>CONFIGURATION_CODE                                   | 0xD6        | Represents the device                                                                                  | R/W Byte  | Reg            |      | Y         |

| MFR_MTP_REVISION_<br>NUMBER                                      | 0xD7        | 1 Byte, such as "0x01"                                                                                 | R/W Byte  | Reg            |      | Y         |

| MFR_STATUS_MASK                                                  | 0xD8        | Masks the ALT pin indication                                                                           | R/W Byte  | Reg            |      | Υ         |

#### Note:

9) The default register value is based on MP4245-0000.

#### PMBUS COMMAND INTRODUCTION

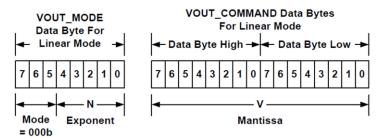

### Linear16 (L16) and Linear11 (L11) Data Formats

Linear16 format is used for the V<sub>OUT</sub> command. For more details, see Figure 14 and the description below.

Figure 14: Linear16 Format

The Mode bits are set to 000b. The voltage can be calculated with Equation (3):

$$Voltage = V \times 2^{N}$$

(3)

Where Voltage is the parameter of interest (in V); V is a 16-bit unsigned binary integer; and N is a 5-bit, two's complement binary integer.

Linear11 format is used for other commands, such as the V<sub>OUT</sub> scale loop and temperature monitoring. For more details, see Figure 15 and the description below.

Figure 15: Linear11 Format

The relationship between Y, N, and the real-world value can be calculated with Equation (4):

$$X = Y \times 2^{N} \tag{4}$$

Where X is the real-world value, Y is an 11-bit, two's complement integer, and N is a 5-bit, two's complement integer.

Devices that use linear format must accept and be able to process any value of N.

#### **OPERATION**

The OPERATION command configures the converter's operation state.

| Bits | Description                                                                                                                                                                  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | This bit sets the on/off state. Note that the EN pin has a higher control priority than this bit. This bit is set to 0 by default.  0: The output is off 1: The output is on |

| 3:0  | Reserved.                                                                                                                                                                    |

#### **CLEAR FAULTS**

The CLEAR\_FAULTS command clears any fault bits that have been set. This command clears all bits in all status registers simultaneously. If the device is asserting the ALT signal at the same time, the device clears its ALT signal output.

The CLEAR\_FAULTS command does not cause any unit that has latched off for a fault condition to restart. If the fault is still present when the bit is cleared, then the fault bit is immediately set again and the host is notified. This command is write-only. There is no data byte for this command.

#### WRITE PROTECT

The WRITE\_PROTECT command controls writing to the PMBus device. The intent of this command is to prevent accidental changes. All supported commands may have their parameters read, regardless of the WRITE PROTECT settings.

| Data Byte Value | Description                                                                                         |

|-----------------|-----------------------------------------------------------------------------------------------------|

| 1000 0000       | Disable all writes except to the WRITE_PROTECT command                                              |

| 0100 0000       | Disable all writes except to the WRITE_PROTECT, OPERATION commands                                  |

| 0010 0000       | Disable all writes except to the WRITE_PROTECT, OPERATION, MFR Registers and VOUT_COMMAND commands. |

| 0000 0000       | Enable writes to all commands. By default the STORE_USER_ALL is write enabled.                      |

#### STORE USER ALL

The STORE\_USER\_ALL command instructs the PMBus device to copy the entire contents of the operating memory (I<sup>2</sup>C register) to the matching locations in the MTP (non-volatile user store memory). Any items in operating memory that do not have matching locations in the user store are ignored.

The output is initially turned off during this operation. After MTP configuration is complete, the device starts up. While storing user memory to MTP, the device initiates a cyclic redundancy check (CRC) calculation, and stores the CRC check result in a 1-byte MTP cell. The MTP can be configured two times.  $V_{IN}$  must exceed 6.5V for MTP configuration.

This command is write-only. There is no data byte for this command.

#### RESTORE\_USER\_ALL

The RESTORE\_USER\_ALL command instructs the PMBus device to copy the entire contents of the non-volatile user store memory (MTP) to the matching locations in the operating memory (I<sup>2</sup>C register). The values in the operating memory are overwritten by the value retrieved from the user store. Any items in user store that do not have matching locations in the operating memory are ignored.

The RESTORE\_USER\_ALL command can be used even if the device is never configured by the MTP. While restoring MTP data to user memory, the device initiates a CRC calculation, and compares the calculated result with the stored CRC result in the MTP cell. The MTP value is restored to the operating memory only when the values match. After the RESTORE\_USER\_ALL process is complete, set the

OPERATION command to off. Set it to on again to refresh the register value. This command is write-only. There is no data byte for this command.

#### **VOUT MODE**

| Command  |   | VOUT_MODE       |   |   |   |   |   |   |  |  |  |  |  |

|----------|---|-----------------|---|---|---|---|---|---|--|--|--|--|--|

| Format   |   | Unsigned binary |   |   |   |   |   |   |  |  |  |  |  |

| Bit      | 7 | 7 6 5 4 3 2 1 0 |   |   |   |   |   |   |  |  |  |  |  |

| Access   | R | R               | R | R | R | R | R | R |  |  |  |  |  |

| Function |   | MODE            |   | N |   |   |   |   |  |  |  |  |  |

| Default  | 0 | 0 0 0 1 0 1 1 0 |   |   |   |   |   |   |  |  |  |  |  |

The MP4245 only supports linear mode. The MODE bits are set to 000b by default. N is fixed to -10.

#### **VOUT COMMAND**

The VOUT\_COMMAND command sets the output voltage. It follows the Linear16 linear data format. The I<sup>2</sup>C voltage scaling slew rate is fixed to 0.04mV/µs (V<sub>REF</sub>). V<sub>OUT</sub> can be calculated with Equation (5):

$$V_{OUT} = V_{REF} x \text{ feedback ratio}$$

(5)

Where the feedback ratio can be estimated with Equation (6):

Feedback ratio =

$$(R1 + R2) / R2$$

(6)

The maximum V<sub>OUT</sub> command is 0x5800.

| Command  |     | VOUT_COMMAND                                                        |     |     |     |     |     |       |         |     |     |     |     |     |     |     |

|----------|-----|---------------------------------------------------------------------|-----|-----|-----|-----|-----|-------|---------|-----|-----|-----|-----|-----|-----|-----|

| Format   |     | Linear16                                                            |     |     |     |     |     |       |         |     |     |     |     |     |     |     |

| Bit      | 15  | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |     |     |     |     |     |       |         |     |     |     |     |     |     |     |

| Access   | R/W | R/W                                                                 | R/W | R/W | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function |     | Data byte high Data byte low                                        |     |     |     |     |     |       |         |     |     |     |     |     |     |     |

| Default  |     |                                                                     | •   | •   | •   | •   |     | 0x140 | 00 (5V) | •   |     | •   | •   | •   | •   |     |

$V_{OUT}$  (in V) can be calculated with Equation (7):

$$V_{OUT}(V) = V \times 2^{-10}$$

(7)

Where V is a 16-bit, unsigned binary integer of VOUT\_COMMAND, bits[15:0], K is related to the feedback ratio, and the output resolution (or minimum step) is 0.8mV / K.

For example, if the feedback resistor ratio is  $V_{OUT}$  /  $V_{FB}$  = 12.5, then K = 1 / 12.5 = 0.08, and the output resolution is 10mV. The internal reference voltage is equal to  $V_{OUT}$  x K. The internal reference voltage ranges between 0.1V and 1.63V, with a 0.8mV step.

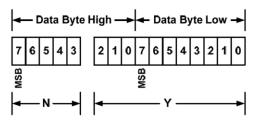

#### VOUT\_SCALE\_LOOP

In typical devices, the output voltage ( $V_{OUT}$ ) is sensed through a voltage resistor divider (see Figure 16). The resistor divider reduces or scales  $V_{OUT}$  so that when  $V_{OUT}$  is correct, the value supplied to the control circuit is equal to the reference voltage. This command has 2 data bytes encoded in Linear11 format. This value is unitless.

Figure 16: Output Voltage Sensing

| Command  |    | VOUT_SCALE_LOOP                       |   |   |   |     |     |     |         |     |     |     |     |     |     |     |

|----------|----|---------------------------------------|---|---|---|-----|-----|-----|---------|-----|-----|-----|-----|-----|-----|-----|

| Format   |    | Linear                                |   |   |   |     |     |     |         |     |     |     |     |     |     |     |

| Bit      | 15 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |   |   |   |     |     |     |         |     |     |     |     |     |     |     |

| Access   | R  | R                                     | R | R | R | R/W | R/W | R/W | R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Function |    | Data byte high Data byte low          |   |   |   |     |     |     |         |     |     |     |     |     |     |     |

| Default  |    |                                       |   |   |   |     |     | 0xB | 052 (0. | 08) |     |     |     |     |     |     |

The V<sub>OUT</sub> scale loop can be estimated with Equation (8):

$$V_{OUT}$$

scale loop =  $X \times 2^{-10}$  (8)

Where X is an 11-bit, unsigned binary integer of VOUT\_SCALE\_LOOP, bits[10:0]; the  $V_{OUT}$  scale loop = R2 / (R1 + R2), and is the reciprocal of the  $V_{OUT}$  scale loop (the default value is 0.08).

If another feedback ratio is used, set VOUT SCALE LOOP to the new value accordingly.

The feedback ratio should be determined based on the required  $V_{OUT}$  resolution. The MP4245's internal reference voltage ranges between 0.1V and 1.638V, with 0.8mV per step. If a 10mV  $V_{OUT}$  resolution is required, the feedback ratio should be 10mV / 0.8mV = 12.5. Then  $VOUT\_SCALE\_LOOP = 1 / 12.5$ , or 0.08. The adjustable  $V_{OUT}$  range is (0.1V to 1.638V) x 12.5, meaning it is between 1.25V and 20.47V.

If the maximum output voltage is 21V in a USB PD application, the feedback ratio can be set to 0.0638 (R1 =  $90.9k\Omega$ , R2 =  $6.2k\Omega$ ) for a larger output range.

The V<sub>OUT</sub> scale loop value must match the real output feedback resistor divider value.

#### STATUS BYTE

The STATUS\_BYTE command returns 1 byte of information with a summary of the most critical fault statuses.

| Bit | Bit Name              | Description                                                                                                                                                 |

|-----|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BUSY                  | Indicates if a fault occurs because the device is busy and unable to respond.                                                                               |

| 6   | OFF                   | This bit asserts if the unit is not providing power to the output. This includes when the device is not enabled to turn on.                                 |

| 5   | VOUT_OV_FAULT         | Indicates if an output over-voltage (OV) fault has occurred.                                                                                                |

| 4   | IOUT_OC_FAULT         | Indicates if an output over-current (OC) fault has occurred. If the devices reaches the constant current (CC) limit or enters hiccup mode, this bit is set. |

| 3   | VIN_UV_FAULT          | Indicates if an input under-voltage (UV) fault has occurred.                                                                                                |

| 2   | TEMPERATURE           | Indicates if a temperature fault or warning has occurred.                                                                                                   |

| 1   | CML                   | Indicates if a communications, memory or logic fault (e.g. an MTP CRC check error) has occurred.                                                            |

| 0   | NONE_OF_THE_<br>ABOVE | Indicates if a fault or warning not listed in bits [7:1] has occurred.                                                                                      |

#### STATUS WORD

The STATUS\_WORD command returns 2 bytes of information with a summary of the MP4245's fault conditions. Based on the information in these bytes, the host can obtain more information by reading the associated status registers.

The lower byte (8 bits) of STATUS WORD shares its register with the STATUS BYTE command.

| Byte | Bit | Status Bit Name       | Description                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|------|-----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|      | 7   | BUSY                  | Indicates if a fault occurs because the device is busy and unable to respond.                                                                                                                                                  |  |  |  |  |  |  |  |

|      | 6   | OFF                   | This bit asserts if the unit is not providing power to the output. This includes when the device is not enabled to turn on.                                                                                                    |  |  |  |  |  |  |  |

|      | 5   | VOUT_OV_FAULT         | Indicates if an output over-voltage (OV) fault has occurred.                                                                                                                                                                   |  |  |  |  |  |  |  |

| Low  | 4   | IOUT_OC_FAULT         | Indicates if an output over-current (OC) fault has occurred. If the devices reaches the constant current (CC) limit or enters hiccup mode, this bit is set.                                                                    |  |  |  |  |  |  |  |

| LOW  | 3   | VIN_UV_FAULT          | Indicates if an input under-voltage (UV) fault has occurred.                                                                                                                                                                   |  |  |  |  |  |  |  |

|      | 2   | TEMPERATURE           | Indicates if a temperature fault or warning has occurred.                                                                                                                                                                      |  |  |  |  |  |  |  |

|      | 1   | CML                   | Indicates if a communications, memory or logic fault (e.g. an MTP CRC check error) has occurred.                                                                                                                               |  |  |  |  |  |  |  |

|      | 0   | NONE_OF_THE_<br>ABOVE | Indicates if a fault or warning not listed in bits [7:1] has occurred.                                                                                                                                                         |  |  |  |  |  |  |  |

|      | 7   | VOUT                  | Indicates if an output voltage (Vout) fault or warning has occurred.                                                                                                                                                           |  |  |  |  |  |  |  |

|      | 6   | IOUT/POUT             | Indicates if an output current (I <sub>OUT</sub> ) fault has occurred. This bit is set if an I <sub>OUT</sub> fault occurs. The MP4245 then enters either hiccup mode or constant current (CC) limiting.                       |  |  |  |  |  |  |  |

|      | 5   | INPUT                 | Reserved.                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| High | 4   | OC_EXIT               | Indicates if I <sub>OUT</sub> exits the CC limit mode. This bit is only set high when I <sub>OUT</sub> changes from CC (before entering hiccup mode) to non-CC. This bit is not set when the device recovers from hiccup mode. |  |  |  |  |  |  |  |

|      | 3   | PG_STATUS#            | If the power good (PG) signal is present, this bit is ignored.                                                                                                                                                                 |  |  |  |  |  |  |  |

|      | 2   | Reserved              | Reserved.                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|      | 1   | OTHER                 | Indicates if a bit in the STATUS_OTHER register is set.                                                                                                                                                                        |  |  |  |  |  |  |  |

|      | 0   | UNKNOWN               | Indicates if a fault type not listed in bits[15:1] of the STATUS_WORD command has been detected.                                                                                                                               |  |  |  |  |  |  |  |