The Future of Analog IC Technology

# DESCRIPTION

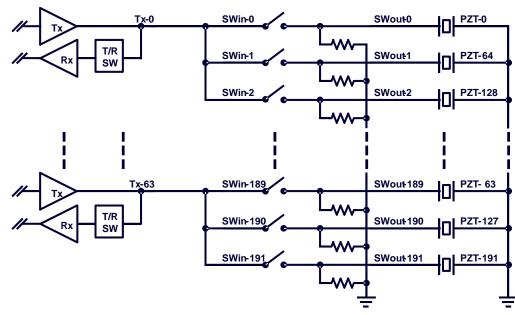

The MP4816A is a 16-channel, high-voltage, single-pole, single-throw, SPST, analog switch with integrated output bleed resistors designed for medical ultrasound imaging applications. The MP4816A is designed to multiplex transmit and receive voltages to and from multiple piezoelectric transducers (PZT).

The output switches are controlled by a 16-bit serial shift register followed by a 16-bit data latch. A data out pin (D<sub>OUT</sub>) is provided to allow for multiple devices to be cascaded together. This helps minimize the number of input/output (I/O) control lines. A logic high in the data latch turns on the corresponding analog switch. A logic low turns off the corresponding analog switch.

The MP4816A does not require any high-voltage supplies. Only two low-voltage supplies are required (3.3V and 10V). The analog switch can block or pass analog voltages up to ±90V with peak currents of up to ±2.0A.

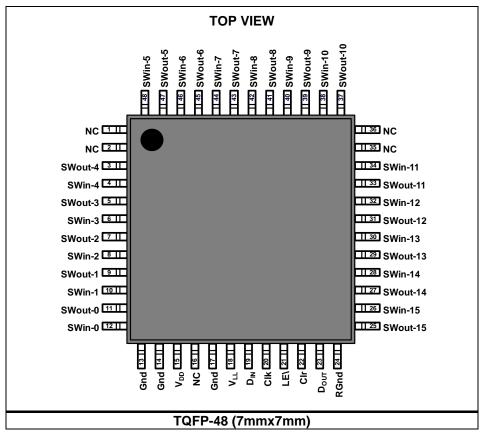

The MP4816A is available in a TQFP-48 (7mmx7mm) package.

# FEATURES

- No High-Voltage Supplies Required •

- 16 Channels

- Up to ±90V Analog Signals

- 12.5Ω Typical Switch Resistance

- ±2.0A Typical Switch Peak Current

- Off-Isolation of -66dB at 5.0MHz

- Integrated Output Bleed Resistor

- 80MHz Clock Frequency •

- Available in a TQFP-48 (7mmx7mm) Package

## APPLICATIONS

- Medical Ultrasound Imaging

- Non-Destructive Testing (NDT)

# TYPICAL APPLICATION

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

#### **ORDERING INFORMATION**

| Part Number | Package           | Top Marking |  |  |

|-------------|-------------------|-------------|--|--|

| MP4816AGFP  | TQFP-48 (7mmx7mm) | See Below   |  |  |

#### **TOP MARKING**

#### MPSYYWW

MP4816A

#### LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP4816A: Product code of MP4816AGFP LLLLLLLL: Lot number

#### **PACKAGE REFERENCE**

#### ABSOLUTE MAXIMUM RATINGS (1)

| Logic supply ( $V_{LL}$ )0.5V to +6.6V<br>Translator supply ( $V_{DD}$ )0.5V to +11V                    |

|---------------------------------------------------------------------------------------------------------|

| Analog signal range (pulsed voltage) (V <sub>SIG</sub> )<br>0V to ±105V                                 |

| Junction temperature150°C<br>Lead temperature260°C                                                      |

| Continuous power dissipation ( $T_A = 25^{\circ}C$ ) <sup>(2)</sup><br>                                 |

| Other pins: Class 2 (JEDEC Standard)<br>CDM: All pins: Class C3 (JEDEC standard)<br>Storage temperature |

| Recommended Operating Conditions <sup>(3)</sup>                                                         |

Logic supply voltage  $(V_{LL})$ ......2.7V to 5.5V Translator supply voltage  $(V_{DD})$ ......9V to 10V Analog signal range  $(V_{SIG})$ .....0 to ±90V Junction temperature  $(T_J)$ ........25°C to +125°C

####

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, resulting in permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## DC ELECTRICAL CHARACTERISTICS

$V_{DD}$  = 10V,  $V_{LL}$  = 5V, unless otherwise noted. <sup>(5)</sup>

|                                              |                     |                                                                                                         | TJ =                     | : 0°C       | T <sub>J</sub> = 25°C    |      |                    | T <sub>J</sub> = 70°C    |             | 11:40 |

|----------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|--------------------------|-------------|--------------------------|------|--------------------|--------------------------|-------------|-------|

| Parameter                                    | Sym                 | Conditions                                                                                              | Min                      | Max         | Min                      | Тур  | Max                | Min                      | Max         | Units |

| Analog signal range                          | Vsig                | Applied to SWin pin                                                                                     | 0                        | ±90         | 0                        |      | ±90                | 0                        | ±90         | V     |

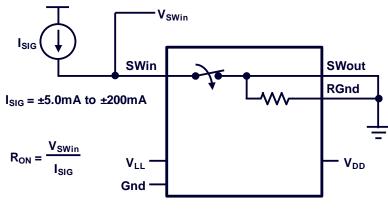

| On registeres                                |                     | I <sub>SIG</sub> = ±5.0mA, SWout =<br>0V. See test circuit 1.                                           |                          | 16          |                          | 12.5 | 19                 |                          | 24          | Ω     |

| On resistance                                | Ron                 | I <sub>SIG</sub> = ±200mA, SWout =<br>0V. See test circuit 1.                                           |                          | 16          |                          | 12.5 | 19                 |                          | 24          |       |

| Small signal on resistance matching          | $\Delta R$ on       | I <sub>SIG</sub> = ±5.0mA, Swout =<br>0V                                                                |                          | -           |                          | 5.0  | -                  |                          | -           | %     |

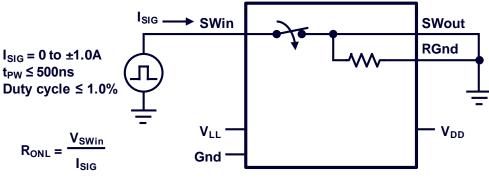

| Large signal on<br>resistance <sup>(6)</sup> | Ronl                | $I_{SIG} = \pm 1.0A$ , $t_{PW} \le 500$ ns, duty cycle $\le 1.0\%$ , SWout = 0V.<br>See test circuit 2. |                          |             |                          | 13   |                    |                          |             | Ω     |

| Switch output peak current <sup>(6)</sup>    | Iswpk               | t <sub>PW</sub> < 100ns, duty cycle <<br>1.0%                                                           |                          |             |                          | ±2.0 |                    |                          |             | А     |

| Output bleed resistor                        | R <sub>BLEED</sub>  | $I_{SIG} = \pm 50 \mu A$                                                                                | 20                       | 50          | 20                       | 30   | 50                 | 20                       | 50          | kΩ    |

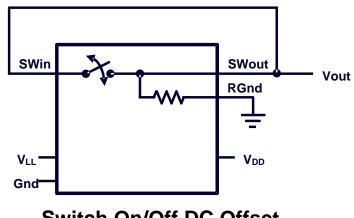

| Switch off DC offset                         | V <sub>DC-OFF</sub> | No load, no V <sub>SIG</sub> .<br>See test circuit 3.                                                   |                          | ±50         |                          |      | ±50                |                          | ±50         | mV    |

| Switch on DC offset                          | Vdc-on              | No load, no V <sub>SIG</sub> .<br>See test circuit 3.                                                   |                          | ±50         |                          |      | ±50                |                          | ±50         | mV    |

| VLL quiescent current                        | ILLQ                | All logic inputs are static                                                                             |                          | 50          |                          |      | 50                 |                          | 50          | μA    |

| V <sub>DD</sub> quiescent current            | I <sub>DDQ</sub>    | All switches on or off,<br>SWin = SWout = ground                                                        |                          | 60          |                          |      | 60                 |                          | 60          | μA    |

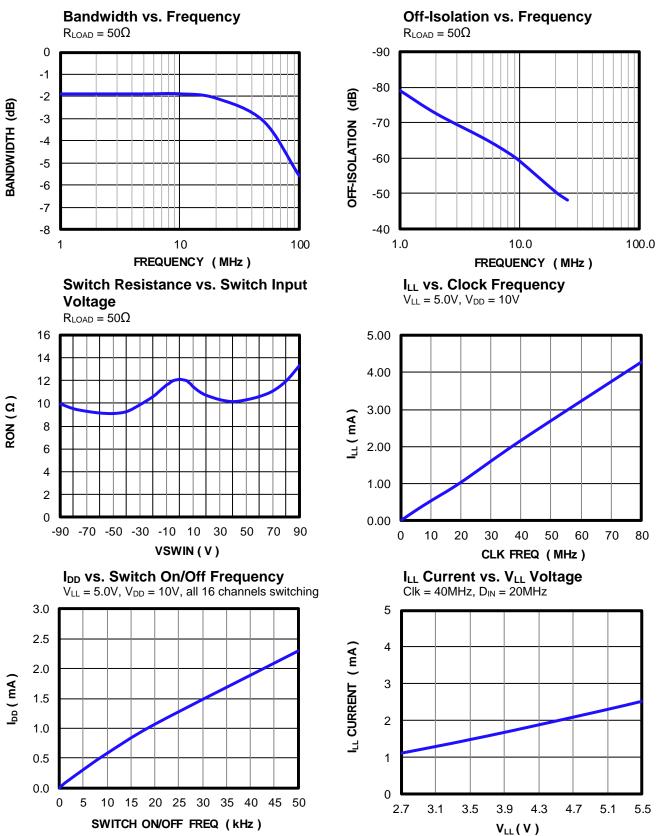

|                                              |                     | f <sub>CLK</sub> = 40MHz, D <sub>IN</sub> =<br>20MHz, LE∖ = H, CIr = L                                  |                          |             |                          | 2.2  | 6                  |                          |             |       |

| VLL average dynamic<br>current               | ILL                 | $f_{CLK} = 80MHz, D_{IN} =$<br>40MHz, LE\ = H, CIr = L<br>$_{(6)}$                                      |                          |             |                          | 4.3  |                    |                          |             | mA    |

| V <sub>DD</sub> average dynamic current      | IDD                 | All output switches are<br>turning on and off at<br>50kHz                                               |                          |             |                          | 2.3  | 4                  |                          |             | mA    |

| Input voltage logic low                      | VIL                 |                                                                                                         | 0                        | $0.2V_{LL}$ | 0                        |      | 0.2V <sub>LL</sub> | 0                        | $0.2V_{LL}$ | V     |

| Input voltage logic high                     | Vih                 |                                                                                                         | 0.8VLL                   | Vll         | $0.8V_{LL}$              |      | VLL                | $0.8V_{LL}$              | VLL         | V     |

| Input current logic low                      | ١ <sub>IL</sub>     |                                                                                                         | -1.0                     |             | -1.0                     |      |                    | -1.0                     |             | μA    |

| Input current logic high                     | Ін                  |                                                                                                         |                          | 1.0         |                          |      | 1.0                |                          | 1.0         | μA    |

| Data out logic low<br>voltage                | V <sub>OL</sub>     | lsink = 10mA                                                                                            |                          | 1.0         |                          |      | 1.0                |                          | 1.0         | V     |

| Data out logic high<br>voltage               | Vон                 | Isource = 10mA                                                                                          | V <sub>LL</sub> -<br>1.0 |             | V <sub>LL</sub> -<br>1.0 |      |                    | V <sub>LL</sub> -<br>1.0 |             | V     |

| Logic input capacitance                      | CIN                 |                                                                                                         |                          | 10          |                          |      | 10                 |                          | 10          | pF    |

#### NOTES:

5) Production test is at 25°C only. 0°C and 70°C limits are guaranteed by design and characterization.

6) Parameters are not tested in mass production, only guaranteed by design or bench characterization.

## **AC ELECTRICAL CHARACTERISTICS**

V<sub>DD</sub> = 10V, V<sub>LL</sub> = 5Vunless otherwise noted. <sup>(5)</sup>

|                                                                                | •                           |                                                            | TJ = | 0°C | T <sub>J</sub> = 25°C |     |     | T <sub>J</sub> = 70°C |     |       |

|--------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|-----|-----------------------|-----|-----|-----------------------|-----|-------|

| Parameter                                                                      | Sym                         | Conditions                                                 | Min  | Max | Min                   | Тур | Max | Min                   | Max | Units |

| Clock frequency (6)                                                            | f <sub>CLK</sub>            | 50% duty cycle                                             |      | 80  | 0                     |     | 80  | 0                     | 80  | MHz   |

| Clock rise time (6)                                                            | tr                          |                                                            |      | 50  |                       |     | 50  |                       | 50  | ns    |

| Clock fall time (6)                                                            | t <sub>f</sub>              |                                                            |      | 50  |                       |     | 50  |                       | 50  | ns    |

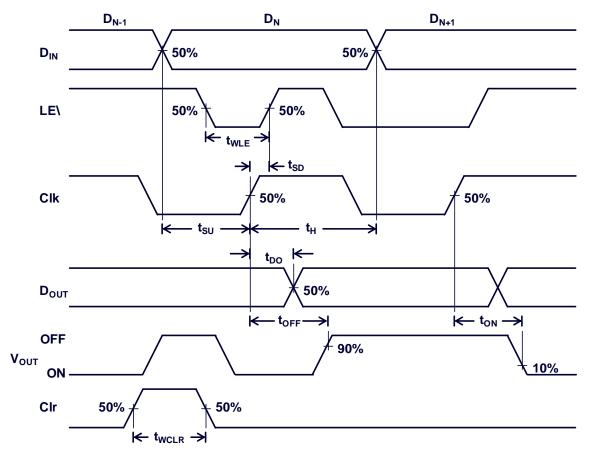

| Set-up time from data<br>to rising edge of clock                               | ts∪                         |                                                            | 3.0  |     | 3.0                   |     |     | 3.0                   |     | ns    |

| Hold time from rising edge of clock to data <sup>(6)</sup>                     | t <sub>H</sub>              |                                                            | 3.0  |     | 3.0                   |     |     | 3.0                   |     | ns    |

| Set-up time before LE\<br>rises <sup>(6)</sup>                                 | tsp                         |                                                            | 6.0  |     | 6.0                   |     |     | 6.0                   |     | ns    |

| LE\ pulse width (6)                                                            | <b>t</b> WLE bar            |                                                            | 6.0  |     | 6.0                   |     |     | 6.0                   |     | ns    |

| Clear pulse width <sup>(6)</sup>                                               | twclr                       |                                                            | 6.0  |     | 6.0                   |     |     | 6.0                   |     | ns    |

| Data out propagation<br>delay time from rising<br>edge of clock <sup>(6)</sup> | t <sub>DOLH,</sub><br>tdohl | 20pF on D <sub>o∪⊤</sub> to ground                         | 4.0  | 8.0 | 4.0                   | 6.0 | 8.0 | 4.0                   | 8.0 | ns    |

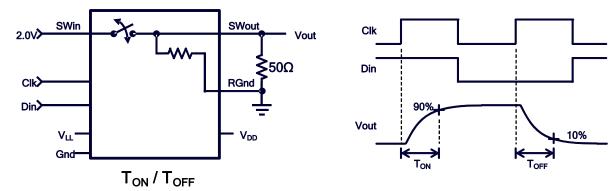

| Output switch turn on time                                                     | T <sub>ON</sub>             | SWin = 2.0V, SWout =                                       |      | 2.0 |                       |     | 2.0 |                       | 2.0 | μs    |

| Output switch turn off time                                                    | TOFF                        | $50\Omega$ to ground. See test circuit 4.                  |      | 2.0 |                       |     | 2.0 |                       | 2.0 | μs    |

| Analog signal slew rate                                                        | dv/dt                       |                                                            |      | 20  |                       |     | 20  |                       | 20  | V/ns  |

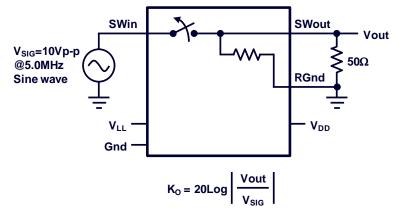

| Off isolation (6)                                                              | Ko                          | freq = $5.0$ MHz, Rload = $50\Omega$ . See test circuit 5. |      |     |                       | -66 |     |                       |     | dB    |

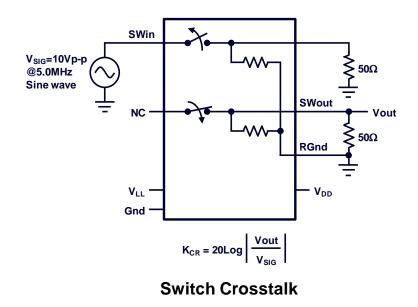

| Switch crosstalk (6)                                                           | Kcr                         | freq = 5.0MHz, Rload =<br>50Ω. See test circuit 6.         |      |     |                       | -60 |     |                       |     | dB    |

| Switch off capacitance                                                         | CsWin-<br>OFF               |                                                            |      |     |                       | 10  |     |                       |     | pF    |

| Switch on capacitance                                                          | Csw-on                      |                                                            |      |     |                       | 13  |     |                       |     | рF    |

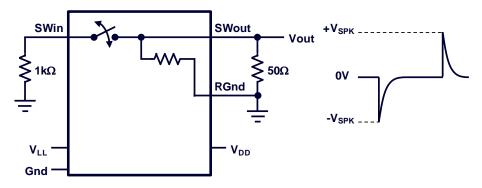

| Positive output voltage spike <sup>(6)</sup>                                   | +V <sub>SPK</sub>           | SWin = $1k\Omega$ to ground,                               |      |     |                       | 16  |     |                       |     | mV    |

| Negative output voltage spike <sup>(6)</sup>                                   | -Vspk                       | SWout = $50\Omega$ to ground.<br>See test circuit 7.       |      |     |                       | -14 |     |                       |     | mV    |

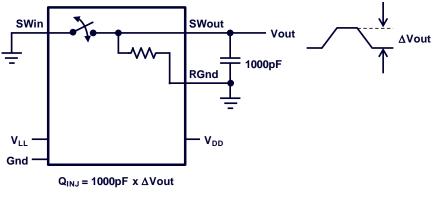

| Output charge injection                                                        | Qinj                        | Cload = 1000pF. See<br>test circuit 8.                     |      |     |                       | 18  |     |                       |     | рС    |

#### NOTES:

Production test is at 25°C only. 0°C and 70°C limits are guaranteed by design and characterization. 5)

Parameters are not tested in mass production, only guaranteed by design or bench characterization. 6)

### **PIN FUNCTIONS**

| Package<br>Pin #    | Name             | Description                                                                                                                                                                                                                               |

|---------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 16,<br>35, 36 | NC               | No internal connections.                                                                                                                                                                                                                  |

| 3                   | SWout-4          | Analog switch output 4. Connect SWout-4 to the piezoelectric transducer.                                                                                                                                                                  |

| 4                   | SWin-4           | Analog switch input 4. Connect SWin-4 to the high-voltage pulser/transmitter.                                                                                                                                                             |

| 5                   | SWout-3          | Analog switch output 3. Connect SWout-3 to the piezoelectric transducer.                                                                                                                                                                  |

| 6                   | SWin-3           | Analog switch input 3. Connect SWin-3 to the high-voltage pulser/transmitter.                                                                                                                                                             |

| 7                   | SWout-2          | Analog switch output 2. Connect SWout-2 to the piezoelectric transducer.                                                                                                                                                                  |

| 8                   | SWin-2           | Analog switch input 2. Connect SWin-2 to the high-voltage pulser/transmitter.                                                                                                                                                             |

| 9                   | SWout-1          | Analog switch output 1. Connect SWout-1 to the piezoelectric transducer.                                                                                                                                                                  |

| 10                  | SWin-1           | Analog switch input 1. Connect SWin-1 to the high-voltage pulser/transmitter.                                                                                                                                                             |

| 11                  | SWout-0          | Analog switch output 0. Connect SWout-0 to the piezoelectric transducer.                                                                                                                                                                  |

| 12                  | SWin-0           | Analog switch input 0. Connect SWin-0 to the high-voltage pulser/transmitter.                                                                                                                                                             |

| 13, 14,<br>17       | GND              | Device ground.                                                                                                                                                                                                                            |

| 15                  | $V_{DD}$         | Translators supply voltage. V <sub>DD</sub> has a 9 - 10V operating range.                                                                                                                                                                |

| 18                  | Vll              | Logic supply voltage. VLL has a 2.7 - 5.5V operating range.                                                                                                                                                                               |

| 19                  | Din              | <b>Logic input.</b> $D_{IN}$ is the data input for the 16-bit serial shift register.                                                                                                                                                      |

| 20                  | Clk              | <b>Logic input.</b> Clk is the clock input for the 16-bit serial shift register. Data is loaded into Clk during the rising edge of the clock.                                                                                             |

| 21                  | LE\              | <b>Logic input.</b> LE\ is the latch enable bar for the 16-bit latch. Logic low on LE\ transfers data from the shift registers to the latches. Logic high on LE\ holds the data in the latches. Refer to the logic truth table on page 9. |

| 22                  | Clr              | <b>Logic input.</b> Clr is the clear input for the 16-bit latch. Logic high on Clr clears the data in the latches by setting them all to 0. Data in the shift register remains unchanged. Refer to the logic truth table on page 9.       |

| 23                  | D <sub>OUT</sub> | <b>Logic output.</b> $D_{OUT}$ is the data output for the 16-bit serial shift register.                                                                                                                                                   |

| 24                  | RGND             | Output bleed resistor ground path.                                                                                                                                                                                                        |

| 25                  | SWout-15         | Analog switch output 15. Connect SWout-15 to the piezoelectric transducer.                                                                                                                                                                |

| 26                  | SWin-15          | Analog switch input 15. Connect SWin-15 to the high-voltage pulser/transmitter.                                                                                                                                                           |

| 27                  | SWout-14         | Analog switch output 14. Connect SWout-14 to the piezoelectric transducer.                                                                                                                                                                |

| 28                  | SWin-14          | Analog switch input 14. Connect SWin-14 to the high-voltage pulser/transmitter.                                                                                                                                                           |

| 29                  | SWout-13         | Analog switch output 13. Connect SWout-13to the piezoelectric transducer.                                                                                                                                                                 |

| 30                  | SWin-13          | Analog switch input 13. Connect SWin-13 to the high-voltage pulser/transmitter.                                                                                                                                                           |

| 31                  | SWout-12         | Analog switch output 12. Connect SWout-12 to the piezoelectric transducer.                                                                                                                                                                |

| 32                  | SWin-12          | Analog switch input 12. Connect SWin-12 to the high-voltage pulser/transmitter.                                                                                                                                                           |

| Package<br>Pin # | Name     | Description                                                                     |

|------------------|----------|---------------------------------------------------------------------------------|

| 33               | SWout-11 | Analog switch output 11. Connect SWout-11 to the piezoelectric transducer.      |

| 34               | SWin-11  | Analog switch input 11. Connect SWin-11 to the high-voltage pulser/transmitter. |

| 37               | SWout-10 | Analog switch output 10. Connect SWout-10 to the piezoelectric transducer.      |

| 38               | SWin-10  | Analog switch input 10. Connect SWin-10 to the high-voltage pulser/transmitter. |

| 39               | SWout-9  | Analog switch output 9. Connect SWout-9 to the piezoelectric transducer.        |

| 40               | SWin-9   | Analog switch input 9. Connect SWin-9 to the high-voltage pulser/transmitter.   |

| 41               | SWout-8  | Analog switch output 8. Connect SWout-8 to the piezoelectric transducer.        |

| 42               | SWin-8   | Analog switch input 8. Connect SWin-8 to the high-voltage pulser/transmitter.   |

| 43               | SWout-7  | Analog switch output 7. Connect SWout-7 to the piezoelectric transducer.        |

| 44               | SWin-7   | Analog switch input 7. Connect SWin-7 to the high-voltage pulser/transmitter.   |

| 45               | SWout-6  | Analog switch output 6. Connect SWout-6 to the piezoelectric transducer.        |

| 46               | SWin-6   | Analog switch input 6. Connect SWin-6 to the high-voltage pulser/transmitter.   |

| 47               | SWout-5  | Analog switch output 5. Connect SWout-5 to the piezoelectric transducer.        |

| 48               | SWin-5   | Analog switch input 5. Connect SWin-5 to the high-voltage pulser/transmitter.   |

# PIN FUNCTIONS (continued)

### **TYPICAL PERFORMANCE CHARACTERISTICS**

02 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

### **TIMING DIAGRAM**

1

#### LOGIC TRUTH TABLE

| Logic Input |    |    |  |     |        |     | S                    | witch Sta | te  |  |      |

|-------------|----|----|--|-----|--------|-----|----------------------|-----------|-----|--|------|

| D0          | D1 | D2 |  | D15 | LE bar | Clr | SW0                  | SW1       | SW2 |  | SW15 |

| L           | -  | -  |  | -   | L      | L   | Off                  | -         | -   |  | -    |

| Н           | -  | -  |  | -   | L      | L   | On                   | -         | -   |  | -    |

| -           | L  | -  |  | -   | L      | L   | -                    | Off       | -   |  | -    |

| -           | Н  | -  |  | -   | L      | L   | -                    | On        | -   |  | -    |

| -           | -  | L  |  | -   | L      | L   | -                    | -         | Off |  | -    |

| -           | -  | Н  |  | -   | L      | L   | -                    | -         | On  |  | -    |

|             |    |    |  |     |        |     |                      |           |     |  |      |

| I           | I  | I  |  |     | I      | I   | I                    | I         | 1   |  | - I  |

| I           | I  | 1  |  | I   | I      | I   | I                    | I         | 1   |  |      |

| I           | I  | I  |  | I   | I      | I   | I                    | I         | I   |  | I.   |

| -           | -  | -  |  | L   | L      | L   | -                    | -         | -   |  | Off  |

| -           | -  | -  |  | Н   | L      | L   | -                    | -         | -   |  | On   |

| Х           | Х  | х  |  | Х   | Н      | L   | Holds previous state |           |     |  |      |

| Х           | Х  | Х  |  | Х   | Х      | Н   | All switches off     |           |     |  |      |

L = logic level low

H = logic level high

x = value does not matter

### **TEST CIRCUITS**

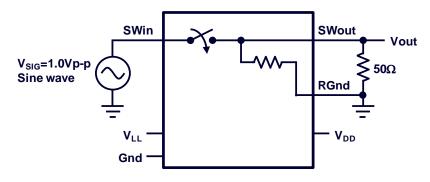

**Test Circuit 1**

Ron

#### **Test Circuit 2**

**Test Circuit 3**

Switch On/Off DC Offset

### **TEST CIRCUITS** (continued)

**Test Circuit 4**

#### **Test Circuit 5**

### **Switch Off-Isolation**

#### **Test Circuit 6**

### **TEST CIRCUITS** (continued)

**Test Circuit 7**

**Output Voltage Spike**

**Test Circuit 8**

**Test Circuit 9**

**Small Signal Bandwidth**

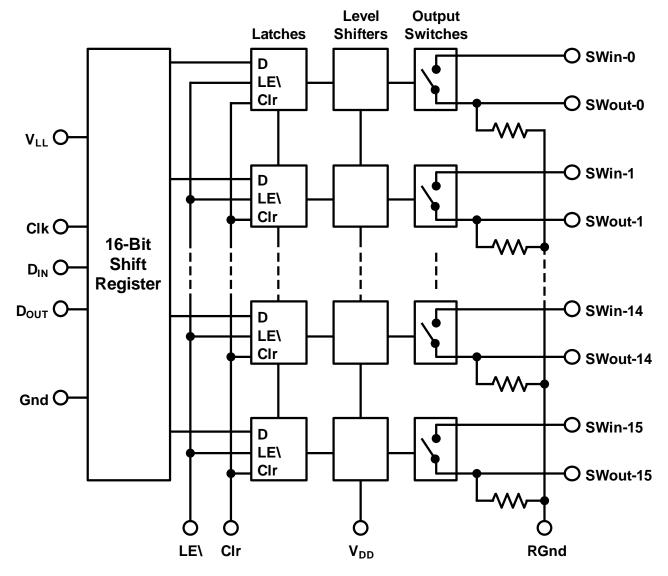

### **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

### **APPLICATION INFORMATION**

The MP4816A is a 16-channel high-voltage, single-pole, single-throw, SPST, analog switch with integrated output bleed resistors designed for medical ultrasound imaging and nondestructive testing (NDT) applications. The MP4816A is designed to multiplex high transmit voltages to selected piezoelectric transducers and multiplex small analog echo signals to selected receivers.

The output switches are controlled by a 16-bit serial shift register followed by a 16-bit data latch. A data out pin ( $D_{OUT}$ ) allows for multiple devices to be cascaded together. This helps minimize the number of input/output (I/O) control lines. A logic high in the data latch turns on the corresponding analog switch. A logic low turns off the corresponding analog switch.

The MP4816A has a unique, patented design that does not require any high-voltage negative or positive supplies. This eliminates:

- the need to generate high-voltage positive and negative supplies.

- the need for high-voltage bypass capacitors next to each device.

- safety concerns on high-voltage buses.

- power-up/-down fault conditions concerns.

#### **Analog Switch**

The analog switches have a typical switch resistance of  $12.5\Omega$ . In the on state, the device can pass transmit voltages up to  $\pm 90V$  with peak currents of up to  $\pm 2.0A$ . In the off state, the device can block voltages up to  $\pm 90V$ .

Each switch has a dedicated input and output pin (SWin and SWout). The transmit voltages must be connected to the SWin pins. The PZT load must be connected to the SWout pins. The SWin and SWout pins are not interchangeable.

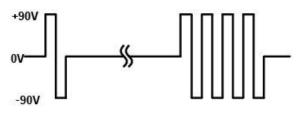

Typical high-voltage transmission waves are short bursts of high-voltage pulses. The burst can consists of single or multiple cycles of 1 -15MHz pulses starting and ending at 0V (see Figure 2).

Figure 2: Typical Tx High Voltage Burst

The SWin input must be close to ground before sending the high-voltage pulses. This allows the internal circuitry to drive the output switches properly.

Transmit voltages greater than  $\pm 5V$  must have frequencies higher than 500kHz. When receiving the echo signals where the voltages are less than  $\pm 0.5V$ , there is no restriction. The switch can pass low-voltage DC signals.

#### Logic Interface

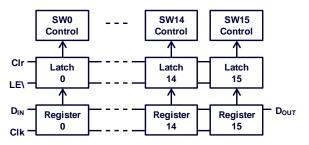

The MP4816A is controlled by a 16-bit serial shift register followed by a 16-bit latch. Data is loaded into the shift register during the rising edge of the clock. No data is transferred during the falling edge. Data is shifted into register 0 and is shifted out from register 15.

Figure 3: Logic Interface Details

Figure 3 shows the logic interface details. In the first clock cycle, the first data bit enters into shift register 0. After 15 more clocked cycles, the first bit is in register 15.

When the latch enable bar (LE\) is low, the data in the shift registers are transferred into the 16bit latch. When LE\ is high, the data in the latches are held. With LE\ high, new data can be shifted into the 16-bit serial shift register without affecting the data in the 16-bit latch. The output switch states follow the data in the 16-bit latch. The CIr pin clears the data in the 16-bit latch only. CIr will not affect the data in the 16-bit serial shift register.

### **APPLICATION INFORMATION**

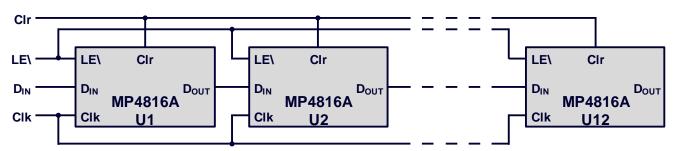

#### Figure 4: Daisy-Chaining 12 MP4816A Devices with a Single Data Input Line

The maximum clock frequency for the MP4816A is 80MHz. The front-end logic control is designed to minimize the number of I/O control lines. A system requiring 192 channels needs  $192 \div 16$  = 12 devices. Figure 4 shows 12 MP4816A devices in a single daisy-chain configuration.

With an 80MHz clock, all 192 channels can be updated in 2.4µs. Only four control lines are required: clock, data in, latch enable bar, and clear. For systems requiring a faster update, multiple data in lines can be used (see Figure 5).

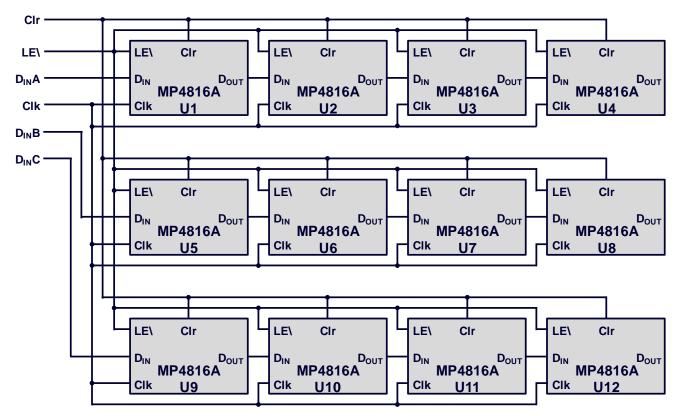

#### Figure 5: Daisy-Chaining MP4816A Devices with Multiple Data Input Lines

Figure 5 is a 192-channel system incorporating three data input lines ( $D_{INA}$ ,  $D_{INB}$ ,  $D_{INC}$ ). Each data input line addresses four MP4816A devices

daisy-chained together. There are now six control lines. With an 80MHz clock, all 192 channels can be updated in 800ns.

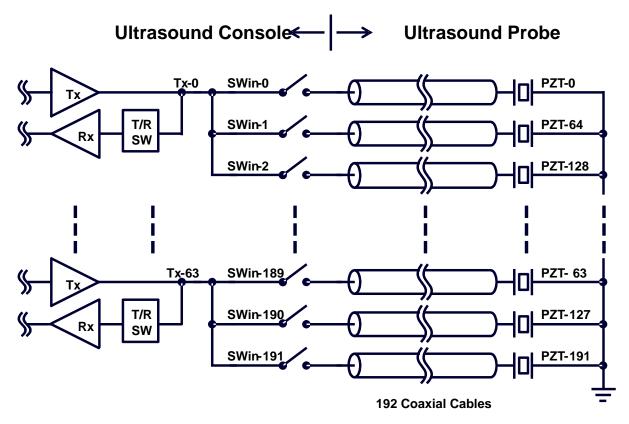

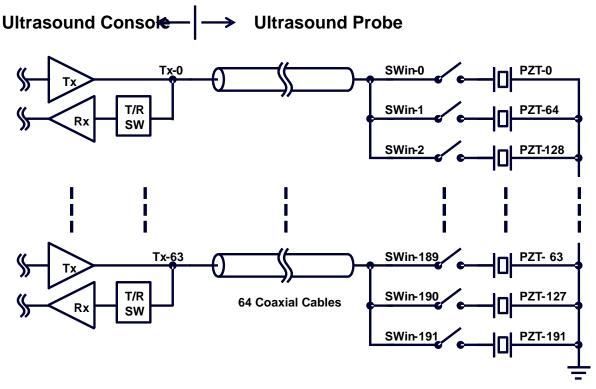

Figure 6 shows where the MP4816A analog switches reside in an ultrasound system. A 1:3 multiplexing configuration is shown as an example. Multiplexing configurations can range from 1:2 to 1:8 or higher. The 1:8 or higher ratios can have slower image frame rates and/or lowerquality images, which are generally used in the lower-end, lower-cost ultrasound market. The MP4816A can be used in any ratio.

The main advantage of using the MP4816A is that it reduces the number of transmitter and receiver circuitries. As shown in Figure 6, without any analog switches, the ultrasound console requires 192 transmitters and receivers to drive an ultrasound probe with 192 PZT elements. With analog switches, only 64 transmitters and receivers are needed. This reduction saves board space, power, and cost, since the transmitter and receiver circuitry can be guite complex. These benefits are especially important for portable ultrasound systems where space, battery life, and weight are all premiums.

Figure 7: MP4816A inside the Ultrasound Probe Head

Figure 7 shows the advantages of putting analog switches inside the probe head, which may be referred to as an active probe. Generally, the probe head is severely space-limited and thermally limited. The housing is waterproof since it must be submersed in alcohol for sterilization. By employing analog switches inside the probe head, the number of coaxial cables can be reduced. Instead of 192 coaxial cables, only 64 coaxial cables are needed for the PZT plus 10 or fewer additional coaxial cables for the supply lines and logic interface.

The reduction of coaxial cables required significantly reduces cost for the probe head. The coaxial cable is by far the most expensive item. Aside from the material cost, the labor to connect the coaxial cables is also guite costly. An added user benefit is that the probe head becomes more maneuverable. The sonographer experiences less fatigue using an active probe. Since the MP4816A does not need any highvoltage supplies, safety concerns about running high-voltage DC lines on the coaxial cables are eliminated, and the minimal power dissipation design eliminates the concern of thermal constraints inside the probe head, and the higher clock speed helps reduce the number of data lines.

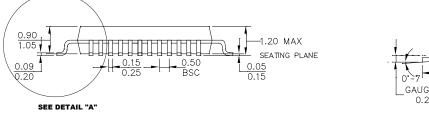

### **PACKAGE INFORMATION**

8.80 9.20 6.85 7.05 -8.20-48 A.A 1.60 PIN 1 ID 1 🖂 0.20 1 6.85 7.05 <u>8.80</u> 9.20 -8.20 0.50 -12 🗖 Π D Π Π **TOP VIEW** RECOMMENDED LAND PATTERN

TQFP-48 (7mmx7mm)

SIDE VIEW

DETAIL "A"

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WITDH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) JEDEC REFERENCE IS MO-143.

- 6) DRAWING IS NOT TO SCALE.

#### **Revision History**

| Revision # | Revision<br>Date | Description                     | Pages Updated |

|------------|------------------|---------------------------------|---------------|

| 1.02       | 07/06/2020       | Changing page 3, "1.0W to 1.47W | Page 3        |

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analogue Switch ICs category:

Click to view products by Monolithic Power Systems manufacturer:

Other Similar products are found below :

FSA3051TMX NLAS4684FCTCG NLAS5223BLMNR2G NLX2G66DMUTCG 425541DB 425528R 099044FB NLAS5123MNR2G PI5A4157CEX PI5A4599BCEX NLAS4717EPFCT1G PI5A3167CCEX SLAS3158MNR2G PI5A392AQE PI5A4157ZUEX PI5A3166TAEX FSA634UCX XS3A1T3157GMX TC4066BP(N,F) DG302BDJ-E3 PI5A100QEX HV2605FG-G HV2301FG-G RS2117YUTQK10 RS2118YUTQK10 RS2227XUTQK10 ADG452BRZ-REEL7 MAX4066ESD+ MAX391CPE+ MAX4730EXT+T MAX314CPE+ BU4066BCFV-E2 MAX313CPE+ BU4S66G2-TR NLASB3157MTR2G TS3A4751PWR NLAST4599DFT2G NLAST4599DTT1G DG300BDJ-E3 DG2503DB-T2-GE1 TC4W53FU(TE12L,F) HV2201FG-G 74HC2G66DC.125 DG3257DN-T1-GE4 ADG619BRMZ-REEL ADG1611BRUZ-REEL7 DG2535EDQ-T1-GE3 LTC201ACN#PBF 74LV4066DB,118 ISL43410IUZ